Thèse n°7890

# EPFL

# Multi-Objective Management of Multiprocessor Systems: From Heuristics to Reinforcement Learning

Présentée le 30 octobre 2020

à la Faculté des sciences et techniques de l'ingénieur Laboratoire des systèmes embarqués Programme doctoral en génie électrique

pour l'obtention du grade de Docteur ès Sciences

par

# Arman IRANFAR

Acceptée sur proposition du jury

Prof. P. Frossard, président du jury Prof. D. Atienza Alonso, directeur de thèse Prof. M. Van Der Schaar, rapporteuse Prof. M. Zapater, rapporteuse Prof. A. Burg, rapporteur

École polytechnique fédérale de Lausanne

2020

I was gratified to be able to answer promptly, and I did. I said I didn't know. — Mark Twain

To my compassionate parents; To my supportive brother; And to my wonderful wife.

# Acknowledgments

Pursuing my PhD at Embedded Systems Laboratory (ESL) under supervision of Prof. David Atienza was a great opportunity. I wish to express my sincere appreciation to him, who has convincingly guided and encouraged me to be professional. Without his persistent support, this PhD dissertation would not have been realized. I would like to take this opportunity to also thank my thesis jury members, Prof. Andreas Burg, Prof. Mihaela Van Der Shcaar, Prof. Pascal Frossard, and Prof. Marina Zapater, for taking their valuable time out of their busy schedule to review this manuscript and providing me with their insightful comments.

Besides, there have been several other people who have helped me a lot during my PhD. First of all, I would like to thank Dr. Marina Zapater who helped me a lot in editing my publications and always supported me. Also, I would like to thank Prof. Katzalin Olcoz, Prof. Jose Flich, Dr. Federico Terraneo, and Prof. Samuel Xavier-de-Souza with whom I had joint collaborations for several publications.

Additionally, I would like to seize this opportunity to acknowledge all my colleagues at ESL, with whom I interacted on a daily basis, making memorable moments, from time-to-time coffee breaks and birthday parties, to all other exciting ESL outdoors activities. Especially, I would like to thank Homeira for organizing lab events and my trips to different conferences in many places in Europe, Asia, and South America; Rodolphe and Mikael for all their beyond-the-imagination supports and efforts in all IT-related issues; Ruben, Adriana, Alexandre, Tomas, Miguel, Pablo, Leila, our post-doctoral fellows, with whom I worked indirectly during my PhD; Soumya, Anthongy, Marina, and Renato for the amazing moments we shared in our office; Dionisije, Halima, Ignacio, Alireza, Marco, Saleh, Una, Niloofar, Gregoir, Arteem, Elizabeta, Yasir, Loris, Lara, Benoit, Szabolcs, Wellington, Damián, Luis, Darong, and André, my colleagues and friends at ESL. I would like to express my especial gratitude to Dr. Amir Aminifar and Ali Pahlevan, for being such great friends and all their insightful comments that led me enhance my research quality.

During these years of living in Switzerland, there were many great Iranian friends who made life with all its ups-and-downs sweet and enjoyable for me. Hereby, I would like to thank them all: Ashkan, Mahsa, Mohammad, Shakiba, Omid, Nastaran, Shayan, and Hamed. Also, I sincerely thank my friends living abroad who always supported me when the road became tough: Amir, Arash, Paniz, Sadegh, and Soheil.

The last but here the most, I would like to express my heartfelt gratitude to my entire family, and particularly, my parents, brother, father-in-law, mother-in-law, and my beloved wife, Shadi.

Lausanne, September 28, 2020

Arman Iranfar

# Abstract

Since the maximum operating frequency of processors started to saturate due to intolerable power dissipation, multiprocessor systems, such as Multiprocessor Systems-on-Chip (MP-SoCs) and multi-core servers, have been playing a key role to meet the performance demand of many applications. The presence of multiple processors poses additional challenges in management of these systems with respect to well-known objectives and constraints including power, performance, temperature, and lifetime reliability. In particular, finding an optimal scheme able to utilize all available design- and run-time techniques, such as thread allocation and migration, consolidation, Dynamic Voltage and Frequency Scaling (DVFS), dynamic power management (DPM), and dynamic thermal management (DTM), is either impractical or infeasible within a reasonable time. Therefore, heuristics are vastly used to obtain the near-optimal or sub-optimal solutions.

Conventional multi-objective management of multiprocessor systems mostly focuses on hot spots as the main factor of lifetime reliability. Nonetheless, for modern multiprocessor systems and workloads, thermal stress, defined as any rapid change of temperature in time or space, has become the dominant factor in determining the Mean Time-To-Failure (MTTF). Together with the advances in multiprocessor systems, cooling technologies have been also progressively improving. As a result, existing DTM policies should adapt to these emerging challenges and technologies to further improve the lifetime reliability.

To address the multi-objective management of multiprocessor systems, I first propose a holistic, yet fast thermal stress-aware heuristic approach. The results demonstrate that the lifetime reliability can increase by up to 47% with only 4% performance degradation if thermal stress mechanisms are properly considered when applying traditional DTM techniques, such as DVFS, processor consolidation, and thread migration. Then, I show how emerging cooling technologies, such as two-phase liquid-cooling thermosyphon, necessitates adapting conventional heuristics to gain the greatest possible advantage from all its potential. The results indicate that if emerging cooling technologies are accompanied by proper DTM techniques, thermal hot spots and thermal stress can further decrease by up to  $10^{\circ}C$  and 45%, respectively, with 45% less cooling power consumption.

Although heuristics are still among the most popular methodologies for multi-objective management of multiprocessor systems, a successful heuristic usually requires in-depth knowledge of the application, workload, and the underlying processing system. Moreover, accurate workload prediction and throughput estimation are keys in efficient proactive power and performance management of multiprocessor platforms. Nevertheless, mastering the com-

#### Abstract

putational demand of certain application domains, where the workload varies rapidly due to the input data (e.g., video coding), is very challenging. To address this problem, I propose a machine learning-based framework for workload prediction and throughput estimation using hardware events available on modern multiprocessor systems. The proposed machine learning framework leverages supervised and unsupervised learning to cluster, classify, and predict workload on multiprocessor systems, achieving 3.4x higher throughput with 15% less power consumption for High Efficiency Video Coding (HEVC), as a test-case application. Traditionally, performance, power, energy, and temperature have been considered as the main design objectives and constraints of multiprocessor systems. However, with the advent of new applications domains, such as real-time video streaming and Deep Learning, Qualityof-Service (OoS), defined in various terms, is added as a new important design objective or constraint. Such additional objectives and constraints and additional runtime design parameters exacerbate the already-existing challenges in management of multiprocessor systems. Besides, these new application models expose several internal design parameters that provide a trade-off between computational complexity, performance, power, and QoS. These parameters, either specified at design time or adaptively tuned at run time, exponentially increase the design space of multi-objective management of multiprocessor systems. Moreover, a comprehensive runtime management of multiprocessor systems should take advantage of all available runtime parameters. One of these important parameters that has been used hardly by conventional DTM and DPM approaches is adaptive cooling, such as adaptive fan speed control. The reason mainly lies in the fact that including such additional parameters eventually results in an extremely large design space which requires novel solutions. In fact, for such problems, heuristics can hardly provide a holistic solution. Also, providing the supervised learning algorithms with sufficient training data representative of the whole design space is infeasible. Reinforcement Learning (RL), on the contrary, is able to dynamically learn from very complicated environments, by adjusting actions based on a continuous feedback from the environment. Consequently, in this thesis, I address runtime management and design space search of large and dynamic environments through RL. In particular, I first propose an RL-based framework to enable proactive fan speed control along with DVFS and workload allocation, providing up to 40% cooling power savings without any thermal constraint violations. Second, I address multimedia workload allocation of HEVC encoder on heterogeneous Systems-on-Chip (SoCs) through RL, achieving 20% higher compared to state of the arts. Then, I propose an RL-based approach that enables joint optimization of application- and systemlevel parameters, improving power consumption, performance, and average temperature of multiprocessor systems by 13%, 15%, and 10%, respectively, while improving the video quality and video compression of HEVC encoders, as a use-case application, by up to 1.19 dB and 24%. Although the well-studied Single-Agent RL (SARL) is very efficient in multi-objective management of multiprocessor systems, given an extremely huge design space, a single learning agent may not be able to sufficiently explore different runtime parameters within a reasonable amount of time. Therefore, I propose a Multi-Agent Reinforcement Learning (MARL) approach for multi-objective runtime management of multiprocessor systems. In this approach, the design space is split into smaller independent sub-spaces such that agents accurately explore the assigned design sub-space, and cooperatively maximize the design objectives. I use HEVC encoder as a test-case application, where MARL can enhance QoS violations by 5x, while speeding up the learning phase by 15x. Finally, there are new applications whose parameters, defined at design time, can significantly affect the QoS and performance. Today, Deep Convolutional Neural Networks (DCNNs) are very popular with hundreds or thousands of application-level design parameters, known as hyperparameters. Thus, I propose a novel MARL-based approach for efficient design space search of DCNNs at design time, such that their internal parameters can be set to the values which ultimately maximize the QoS and performance.

To recap, in this thesis, I reveal several already-existing and emerging challenges in multiobjective management of multiprocessor systems, and address them through novel solutions, from heuristics to RL, depending on the complexity of the problem.

**Keywords:** Multi-core server, Multiprocessor System-on-Chip (MPSoC), multi-objective optimization, dynamic power management (DPM), dynamic thermal management (DTM), liquid cooling, thermal stress, thermal cycling, machine learning (ML), reinforcement learning (RL), Qlearning (QL), Quality-of-Service (QoS), Convolutional Neural Network (CNN), High Efficiency Video Coding (HEVC)

# Zusammenfassung

Seitdem die maximale Operationsfrequenz der Prozessoren in den Sättigungsbereich eintrat, die mit den untragbaren Leistungsverlusten begründet wird, gewannen die Multiprozessoren vor allem die Multiprozessoren auf Platine (MP-CoCs) und Multi-Core-Server an Bedeutung, um die Leistungsanforderungen der neuen Anwendungssystemen zu erfüllen. Der Einsatz von Multiprozessoren führt aber zu neuen Herausförderungen in Systemmanagement, Leistungsreglung, Wärmedämmung und System-Zuverlässigkeit. Besonders ist der Einsatz eines optimalen Schemas zur Einstellung aller Entwurf- und Laufzeitmethoden wie Thread-Zuordnung, Konsolidierung, dynamische Spannung- und Frequenzeingruppierung (DVFS), dynamische Leistungsreglung (DPM) und dynamische Wärmereglung (DTM) entweder unpraktisch oder zeitbezüglich undurchführbar. Daher die Heuristiken werden eingesetzt, um eine nahe-optimale Lösung zu erreichen. Die konventionalen Multi-objektiv Management der Multiprozessorsystemen fokussieren sich am meistens auf die so genannten Hot-Spots, die als Hauptfaktoren der Lebenszeit-Resilienz gelten. Allerdings ist für moderne Multiprozessoren die thermische Belastung (wird als jegliche rapide Änderung der Temperatur in Zeit oder Raum definiert) zu einem dominanten Faktor zur Bestimmung der durchschnittliche Fehlschlag-Zeit (MTTF) geworden. Dabei mit den Entwicklungen in Multiprozessoren sind die Abkühlungstechnologien entwickelt. Daher wird für die zurzeit geltenden DTM-Vorschriften eine Anpassung zur Erfüllung dieser neuen Herausforderungen zur Aneignung dieser neuen Technologien vorausgesetzt, um die Lebenszeit-Zuverlässigkeit der Systeme zu verbessern. Um das Multi-Objektive-Management von Multiprozessorsystemen anzugehen, wird in dieser Arbeit zunächst einen ganzheitlichen und dennoch schnellen heuristischen Ansatz vorgestellt, der sich der thermischen Belastung bewusst ist. Die Ergebnisse zeigen, dass die Lebenszeit-Zuverlässigkeit kann um bis zu 47% erhöht werden, obwohl die Leistung nur um 4% beeinträchtigt wird, wenn die Stressmechanismen bei der Anwendung traditioneller DTM-Techniken, DVFS, Prozessorkonsolidierung und Thread-Migration eingesetzt werden. Dann wird es gezeigt, wie sich Abkühlung Technologien wie das Zweiphasen-Thermosiphon zur Flüssigkeitskühlung eine Anpassung herkömmlicher Heuristiken erfordern, um den größtmöglichen Vorteil aus all ihrem Potenzial zu ziehen. Die Ergebnisse weisen zusätzlich darauf hin, dass, wenn aufkommende Kühltechnologien von geeigneten DTM-Techniken begleitet werden, können die thermischen Brennpunkte und die thermische Belastung weiter um bis zu 10 ± C bzw. 45% abnehmen und das mit 45% weniger Kühlstromverbrauch. Obwohl Heuristiken immer noch zu den beliebtesten Methoden für das Management mit mehreren Zielen gehören, erfordert bei Multiprozessorsystemen eine erfolgreiche Heuristik norma-

#### Zusammenfassung

lerweise fundierte Kenntnisse der Anwendung, der Arbeitslast und des zugrunde liegenden Verarbeitungssystems. Darüber hinaus sind eine genaue Workload-Vorhersage und Durchsatzschätzung die wichtigen Schlüssel für ein effizientes und proaktives Leistungsmanagement von Multiprozessor-Plattformen. Die Beherrschung des Rechenaufwands bestimmter Anwendungsbereiche, in denen die Arbeitslast aufgrund von Änderungen der Eingabedaten (z. B. Videocodierung) schnell variiert, ist sehr herausfordernd. Um dieses Problem anzugehen, wird in dieser Arbeit ein auf maschinellem Lernen basierendes Framework für die Workload-Vorhersage und Durchsatzschätzung mit Hilfe von Hardwareereignissen, die auf modernen Multiprozessorsystemen verfügbar sind, vorgeschlagen. Das vorgeschlagene Framework für maschinelles Lernen nutzt überwachtes und unbeaufsichtigtes Lernen, um die Arbeitslast auf Multiprozessorsystemen zu gruppieren, zu klassifizieren und vorherzusagen. Dabei wird ein 3,4-fach höherer Durchsatz bei 15% weniger Stromverbrauch für HEVC (High Efficiency Video Coding) als Testfallanwendung erzielt. Traditionell werden Leistung, Energie und Temperatur als Hauptentwurfsziele und Einschränkungen von Multiprozessorsystemen betrachtet. Mit dem Aufkommen neuer Anwendungsbereiche wie Echtzeit-Video-Streaming und Deep Learning wird die in verschiedenen Begriffen definierte Quality-of-Service (QoS) als neues wichtiges Entwurfsziel oder neue Einschränkung hinzugefügt. Solche zusätzlichen Ziele und Einschränkungen sowie zusätzliche Laufzeitentwurfsparameter verschärfen die bereits bestehenden Herausforderungen beim Management von Multiprozessorsystemen. Außerdem stellen diese neuen Anwendungsmodelle mehrere interne Entwurfsparameter bereit, die einen Kompromiss zwischen Rechenkomplexität, Leistung und QoS bieten. Diese Parameter, die entweder zur Entwurfszeit spezifiziert oder adaptiv zur Laufzeit angepasst werden, vergrößern der Entwurfsraum für die Verwaltung von Multiprozessorsystemen mit mehreren Objektiven in einer exponentiellen Weise. Darüber hinaus soll ein umfassendes Laufzeitmanagement von Multiprozessorsystemen alle verfügbaren Laufzeitparameter verwenden. Einer dieser wichtigen Parameter, der von herkömmlichen DTM- und DPM-Ansätzen kaum verwendet wurde, ist die adaptive Kühlung, wie beispielsweise die adaptive Steuerung der Lüftergeschwindigkeit. Der Grund liegt hauptsächlich in der Tatsache, dass das Einbeziehen solcher zusätzlichen Parameter letztendlich zu einem extrem großen Entwurfsraum führt, der neuartige Lösungen erfordert. Tatsächlich können Heuristiken für solche Probleme kaum eine ganzheitliche Lösung bieten. Es ist auch nicht möglich, den überwachten Lernalgorithmen ausreichende Trainingsdaten zur Verfügung zu stellen, die für den gesamten Entwurfsraum repräsentativ sind. Im Gegensatz dazu kann Reinforcement Learning (RL) dynamisch aus sehr komplizierten Umgebungen lernen, indem Aktionen basierend auf einem kontinuierlichen Feedback aus der Umgebung angepasst werden. Infolgedessen beschäftige ich mich in dieser Arbeit mit dem Laufzeitmanagement und der Suche nach Entwurfsräumen in großen und dynamischen Umgebungen über RL. Insbesondere schlage ich zunächst ein RL-basiertes Framework vor, das eine proaktive Steuerung der Lüftergeschwindigkeit zusammen mit der DVFS- und Workload-Zuweisung ermöglicht und bis zu 40% Kühlleistung einspart, ohne dass thermische Einschränkungen verletzt werden. Zweitens befasse ich mich mit der multimedialen Arbeitslastverteilung von HEVC-Encodern auf heterogenen Systems-on-Chip (SoCs) über RL, die im Vergleich zum Stand der Technik 20% höher sind. Dann schlage ich einen RL-basierten Ansatz

vor, der eine gemeinsame Optimierung der Parameter auf Anwendungs- und Systemebene ermöglicht, den Stromverbrauch, die Leistung und die Durchschnittstemperatur von Multiprozessorsystemen um 13%, 15% bzw. 10% verbessert und gleichzeitig die Videoqualität und Videokomprimierung von HEVC-Encodern als Anwendungsfallanwendung um bis zu 1,19 dB und 24% verbessert. Obwohl der gut untersuchte Single-Agent RL (SARL) bei der Verwaltung von Multiprozessorsystemen mit mehreren Zielen sehr effizient ist, kann ein einzelner Lernagent angesichts eines extrem großen Entwurfsraums möglicherweise nicht in der Lage sein. verschiedene Laufzeitparameter innerhalb einer angemessenen Menge von Zeit ausreichend zu untersuchen. Daher schlage ich einen MARL-Ansatz (Multi-Agent Reinforcement Learning) für ein multi-zielbasierendes Laufzeitmanagement von Multiprozessorsystemen vor. Bei diesem Ansatz wird der Entwurfsraum in kleinere unabhängige Unterräume aufgeteilt, sodass die Agenten den zugewiesenen Entwurfsunterraum genauer untersuchen und die Entwurfsziele kooperativ maximieren. Ich verwende den HEVC-Encoder als Testfallanwendung bei der MARL, der QoS-Verstöße um das 5-fache verbessern und die Lernphase um das 15-fache beschleunigen kann. Schließlich gibt es neue Anwendungen, deren zur Entwurfszeit definierte Parameter die QoS und Leistung erheblich beeinflussen können. Heutzutage sind Tief Konvolution Nerven Netzwerke (DCNNs) bei hunderten oder tausenden von Entwurfsparametern auf Anwendungsebene, sogenannten Hyperparametern, sehr beliebt. Daher schlage ich einen neuartigen MARL-basierten Ansatz für die effiziente Suche nach Entwurfsräumen von DCNNs zur Entwurfszeit vor, sodass deren interne Parameter auf die Werte eingestellt werden können, die letztendlich die QoS und Leistung maximieren. Zusammenfassend möchte ich in dieser Arbeit einige bereits bestehende und aufkommende Herausforderungen beim Multiobjektivmanagement von Multiprozessorsystemen hervorheben und diese je nach Komplexität des Problems durch neuartige Lösungen von Heuristik bis RL angehen.

| Ac | Acknowledgements i    |        |          |                                                              | i   |

|----|-----------------------|--------|----------|--------------------------------------------------------------|-----|

| Ał | Abstract (English) ii |        |          |                                                              | iii |

| Zι | ısam                  | menfa  | ssung (D | eutsch)                                                      | vii |

| Li | st of                 | Figure | 8        |                                                              | xvi |

| Li | st of                 | Tables |          |                                                              | xx  |

| Ac | rony                  | /ms    |          |                                                              | xxi |

| 1  | Intr                  | oducti | on       |                                                              | 1   |

|    | 1.1                   | Multi  | · ·      | re System-Level Management of Multiprocessor Systems         | 1   |

|    |                       | 1.1.1  |          | nd Performance Management                                    | 2   |

|    |                       |        |          | e Reliability and Thermal Management                         | 3   |

|    |                       |        | C        | [                                                            | 5   |

|    | 1.2                   |        | 0 0 11   | lication Models and Quality of Service Requirements          | 6   |

|    |                       | 1.2.1  |          | Coding                                                       | 6   |

|    |                       | 1.2.2  | -        | earning                                                      | 7   |

|    | 1.3                   |        | -        | re Management of Multiprocessor Systems in Literature        | 7   |

|    | 1.4                   |        |          | butions                                                      | 9   |

|    |                       | 1.4.1  |          | ic Multi-Objective Management of Multiprocessor Systems      | 10  |

|    |                       |        |          | Lifetime Reliability Optimization                            | 10  |

|    |                       | 1 4 0  |          | Adapting to New Cooling Technologies                         | 10  |

|    |                       | 1.4.2  |          | e Learning Framework for Multi-Objective Management          | 11  |

|    |                       | 1.4.3  | Search   | cement Learning for Runtime Management and Design Space      | 12  |

|    |                       |        | 1.4.3.1  | Efficient Proactive Cooling                                  | 12  |

|    |                       |        |          | Workload Allocation on Heterogeneous Multiprocessor Systems  | 13  |

|    |                       |        | 1.4.3.3  | Multi-Objective System- and Application-Level Runtime Man-   | 15  |

|    |                       |        | 1.4.5.5  | agement                                                      | 14  |

|    |                       |        | 1.4.3.4  | Multi-Agent Reinforcement Learning for Multi-Objective Run-  | 14  |

|    |                       |        | 1,1,0,4  | time Management                                              | 15  |

|    |                       |        | 1.4.3.5  | Hyperparameter Optimization of Convolutional Neural Networks | 16  |

|   | 1.5 | Thesis   | s Organization                                                      | 16 |

|---|-----|----------|---------------------------------------------------------------------|----|

| 2 | Heu | ristic 1 | Fhermal-Aware Runtime Management of Multiprocessor Systems          | 19 |

|   | 2.1 | Intro    | luction                                                             | 19 |

|   | 2.2 | Lifetii  | me Reliability Mechanisms                                           | 21 |

|   |     | 2.2.1    | Electromigration (EM)                                               | 21 |

|   |     | 2.2.2    | Stress Migration (SM)                                               | 21 |

|   |     | 2.2.3    | Time-Dependent Dielectric Breakdown (TDDB)                          | 21 |

|   |     | 2.2.4    | Temporal and Spatial Thermal Gradients                              | 22 |

|   |     | 2.2.5    | Thermal Cycling                                                     | 22 |

|   | 2.3 | Trend    | ls in Cooling Methodologies and Technologies                        | 23 |

|   |     | 2.3.1    | Air Cooling                                                         | 23 |

|   |     | 2.3.2    | Single-Phase Liquid Cooling                                         | 23 |

|   |     | 2.3.3    | Two-Phase Liquid Cooling                                            | 24 |

|   |     |          | 2.3.3.1 Immersion Cooling                                           | 24 |

|   |     |          | 2.3.3.2 Thermosyphon                                                | 24 |

|   | 2.4 | State-   | of-the-Art on Multi-Objective Thermal Management                    | 25 |

|   |     | 2.4.1    | Power and Thermal Management                                        | 26 |

|   |     | 2.4.2    | Thermal Stress-Aware Power Management                               | 26 |

|   |     | 2.4.3    | Cooling-Aware Thermal Management                                    | 27 |

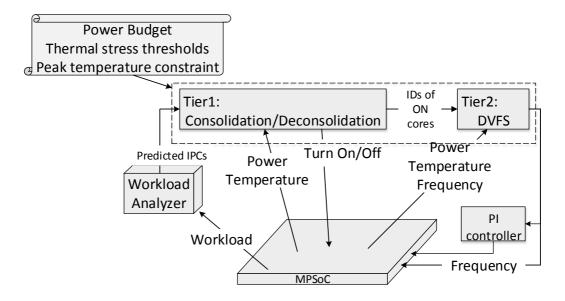

|   | 2.5 | Propo    | osed Thermal Stress-Aware Power and Thermal Management Framework    | 28 |

|   |     | 2.5.1    | Heuristic Core Consolidation and Deconsolidation                    | 30 |

|   |     |          | 2.5.1.1 Consolidation                                               | 30 |

|   |     |          | 2.5.1.2 Deconsolidation                                             | 31 |

|   |     | 2.5.2    | Optimal DVFS                                                        | 32 |

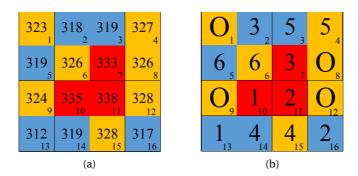

|   |     |          | 2.5.2.1 Determining Spatial Thermal Gradient                        | 32 |

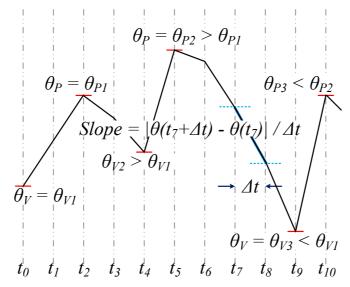

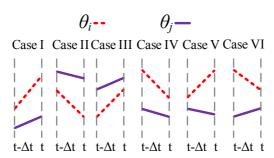

|   |     |          | 2.5.2.2 Defining Thermal Stress Constraints                         | 33 |

|   |     |          | 2.5.2.3 Formulating Spatial Gradients in Thermal Stress Constraints | 36 |

|   |     |          | 2.5.2.4 Convex Optimization Problem                                 | 37 |

|   |     | 2.5.3    | Heuristic DVFS                                                      | 38 |

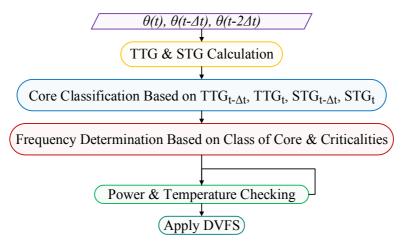

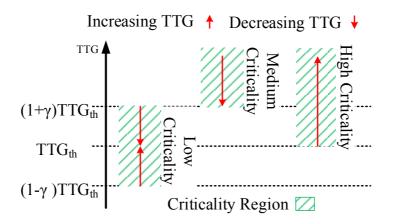

|   |     |          | 2.5.3.1 Core Classification                                         | 39 |

|   |     |          | 2.5.3.2 DVFS                                                        | 40 |

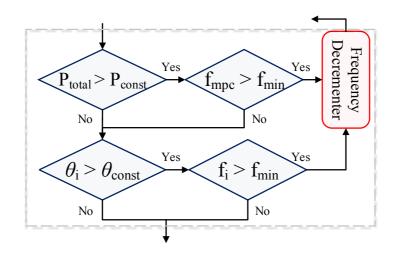

|   |     |          | 2.5.3.3 Power and Temperature Checking                              | 42 |

|   |     | 2.5.4    | Experimental Setup                                                  | 43 |

|   |     | 2.5.5    | Experimental Results                                                | 45 |

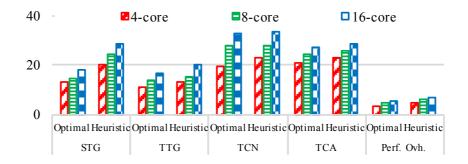

|   |     |          | 2.5.5.1 Thermal Stress Reduction                                    | 45 |

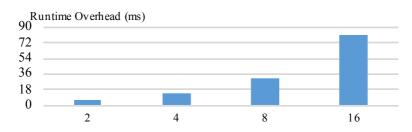

|   |     |          | 2.5.5.2 Comparison of Performance and Runtime Overhead              | 48 |

|   |     |          | 2.5.5.3 Evaluation of Thermal Stress-Aware Power Management         | 50 |

|   | 2.6 | Propo    | osed Workload- and Cooling-Aware Thermal Management                 | 51 |

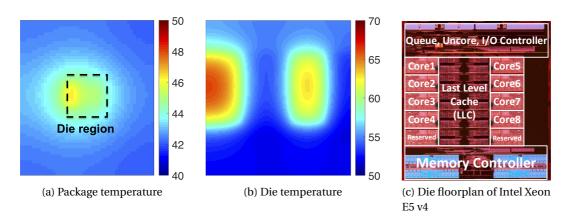

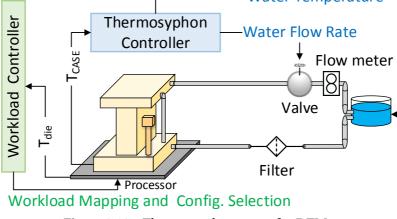

|   |     | 2.6.1    | Overview of System and Power Model                                  | 53 |

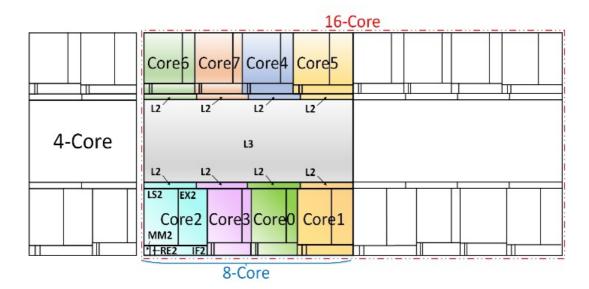

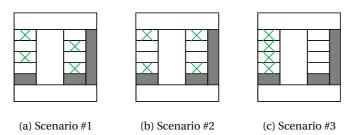

|   |     |          | 2.6.1.1 Server CPU Architecture and Floorplan                       | 53 |

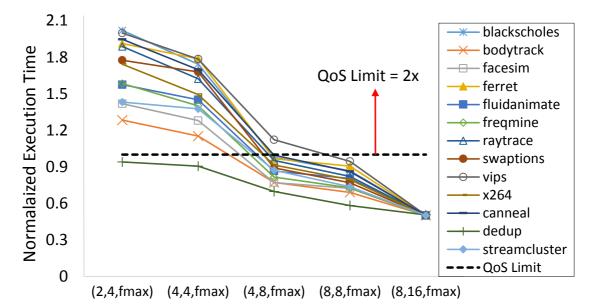

|   |     |          | 2.6.1.2 Workload Configuration and QoS Requirement                  | 54 |

|   |                |       | 2.6.1.3 Power Model of Server Processor                             | 54              |

|---|----------------|-------|---------------------------------------------------------------------|-----------------|

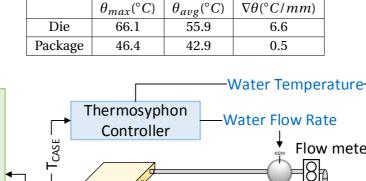

|   |                | 2.6.2 | Design Optimization of Thermosyphon                                 | 56              |

|   |                |       | 2.6.2.1 Thermosyphon Orientation                                    | 56              |

|   |                |       | 2.6.2.2 Refrigerant and Filling Ratio                               | 57              |

|   |                |       | 2.6.2.3 Water Temperature and Flow Rate                             | 57              |

|   |                | 2.6.3 | QoS- and Thermal-Aware Runtime Management                           | 57              |

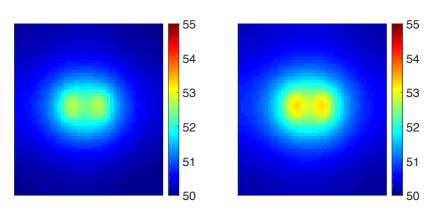

|   |                | 2.6.4 | Experimental Results and Discussion                                 | 59              |

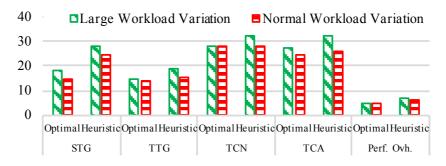

|   |                |       | 2.6.4.1 Thermal Hot Spots and Spatial Gradients                     | 59              |

|   |                |       | 2.6.4.2 Cooling Power                                               | 61              |

|   | 2.7            | Sumn  | nary                                                                | 61              |

| • | 3.6            |       |                                                                     | 00              |

| 3 | <b>Mac</b> 3.1 |       | earning for Runtime Management of Time-Variant Workloads            | <b>63</b><br>63 |

|   | 3.2            |       | Study Application: High Efficiency Video Coding (HEVC)              | 64              |

|   | 5.2            | 3.2.1 |                                                                     | 64              |

|   |                | 3.2.2 | Content and Workload Variation                                      | 65              |

|   |                | 3.2.2 | Workload Parallelization for Multimedia Applications                | 68              |

|   | 3.3            |       | ture Review                                                         | 69              |

|   | 0.0            | 3.3.1 | Machine Learning for Workload and Performance Prediction            | 69              |

|   |                | 3.3.2 | Hardware Event-Based Management of Multiprocessor Systems           | 71              |

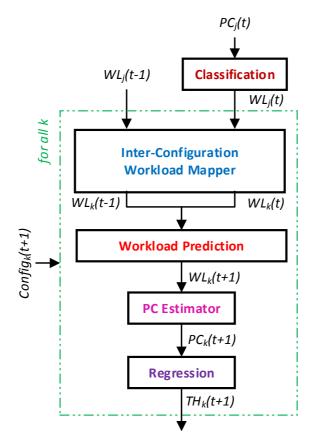

|   | 3.4            |       | osed ML-Based Framework for Power and Performance Management        | 72              |

|   | 0.1            | 3.4.1 | C C                                                                 | 72              |

|   |                | 3.4.2 | Hardware Event-Based ML Framework                                   | 73              |

|   |                | 3.4.3 | Counter Selection                                                   | 74              |

|   |                | 3.4.4 | Workload Clustering and Classification                              | 75              |

|   |                | 3.4.5 | Inter-Configuration Workload Matching and Prediction                | 76              |

|   |                | 3.4.6 | Performance Counter Estimator and Regression Model                  | 77              |

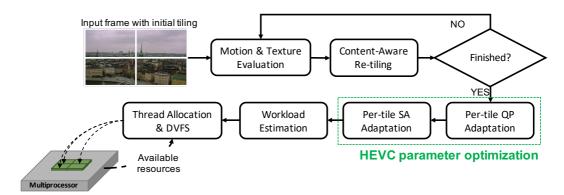

|   | 3.5            | Prope | osed Heuristic Workload-Aware Management for HEVC Encoders          | 78              |

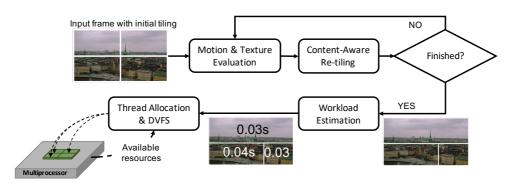

|   |                | 3.5.1 | Motion and Texture Evaluation                                       | 79              |

|   |                | 3.5.2 | Content-Aware Re-tiling                                             | 79              |

|   |                | 3.5.3 | Workload Estimation, Thread Allocation and DVFS                     | 80              |

|   |                |       | 3.5.3.1 Workload Estimation                                         | 80              |

|   |                |       | 3.5.3.2 Thread Allocation and DVFS                                  | 80              |

|   | 3.6            | Exper | imental Setup                                                       | 82              |

|   | 3.7            | Exper | imental Results and Discussion                                      | 83              |

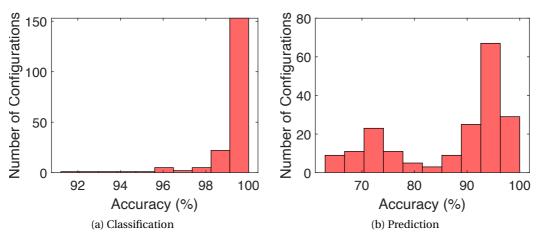

|   |                | 3.7.1 | Performance and Accuracy of Proposed ML Framework                   | 83              |

|   |                |       | 3.7.1.1 Counter Selection                                           | 83              |

|   |                |       | 3.7.1.2 Per-Configuration Workload Clustering and Classification    | 84              |

|   |                |       | 3.7.1.3 Per-Configuration Workload Prediction                       | 84              |

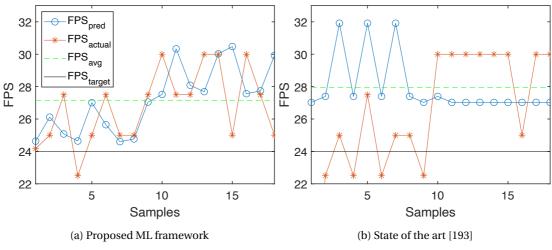

|   |                |       | 3.7.1.4 Throughput Regression                                       | 85              |

|   |                | 3.7.2 | Throughput Estimation Accuracy and Evaluation of Power Minimization | 85              |

|   |                | 3.7.3 | Comparison to Heuristics                                            | 86              |

|   | 3.8  | Sumn    | nary      |                                                              | 87  |

|---|------|---------|-----------|--------------------------------------------------------------|-----|

| 4 | Reiı | nforcei | ment Lea  | rning for Runtime Management and Design Space Search         | 89  |

|   | 4.1  | Intro   | luction . |                                                              | 89  |

|   | 4.2  | Case-   | Study Ap  | plications and Design Space                                  | 91  |

|   |      | 4.2.1   | HEVC E    | ncoder: Run-time Parameters                                  | 91  |

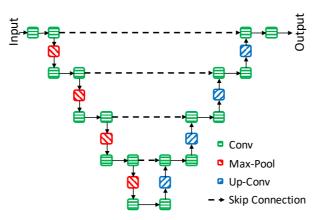

|   |      | 4.2.2   | Convolu   | ıtional Neural Networks (CNNs)                               | 95  |

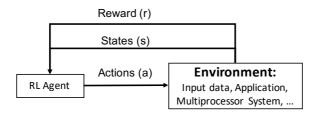

|   | 4.3  | Reinfo  | orcement  | Learning: Background Concepts                                | 97  |

|   |      | 4.3.1   | Model-l   | Based vs. Model-Free RL                                      | 98  |

|   |      | 4.3.2   | Single-A  | Agent vs. Multi-Agent RL                                     | 98  |

|   |      | 4.3.3   | Q-Learr   | ning                                                         | 99  |

|   | 4.4  | Litera  | ture Revi | ew                                                           | 100 |

|   |      | 4.4.1   | RL for R  | untime Management and Design Space Search                    | 100 |

|   |      | 4.4.2   | DTM wi    | th Adaptive Fan Control                                      | 100 |

|   |      | 4.4.3   | Workloa   | ad Allocation of Multimedia Applications                     | 101 |

|   |      | 4.4.4   | HEVC C    | ptimization and Runtime Management                           | 102 |

|   |      | 4.4.5   | CNN Op    | otimization and Design Space Search                          | 104 |

|   | 4.5  | Propo   | sed DTM   | I with Adaptive Fan Speed Control                            | 105 |

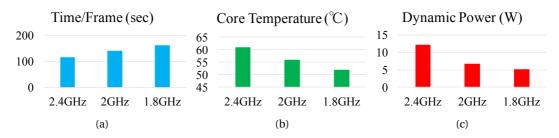

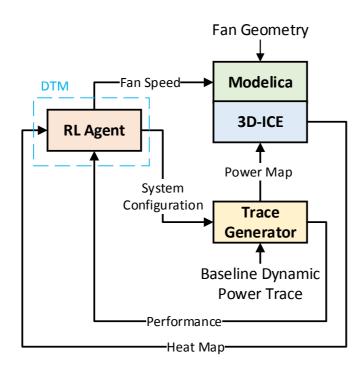

|   |      | 4.5.1   | Experin   | nental Setups                                                | 105 |

|   |      |         | 4.5.1.1   | Simulation Framework and Methodology                         | 107 |

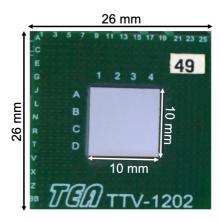

|   |      |         | 4.5.1.2   | Thermal Test Chip                                            | 107 |

|   |      |         | 4.5.1.3   | Heat Sink and Fan                                            | 108 |

|   |      |         | 4.5.1.4   | Power and Performance Model                                  | 108 |

|   |      | 4.5.2   | QL-Base   | ed Dynamic Thermal Management                                | 109 |

|   |      |         | 4.5.2.1   | Actions                                                      | 109 |

|   |      |         | 4.5.2.2   | States                                                       | 110 |

|   |      |         | 4.5.2.3   | Reward Function                                              | 110 |

|   |      |         | 4.5.2.4   | Learning Process                                             | 111 |

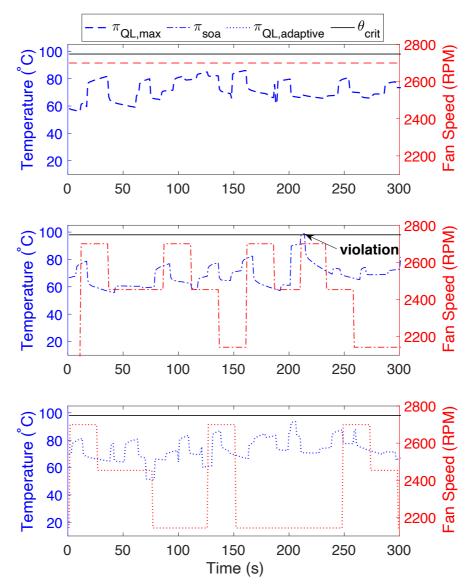

|   |      | 4.5.3   | Experin   | nental Results and Discussion                                | 111 |

|   | 4.6  | Propo   | sed Worl  | doad Allocation of HEVC Streaming on Heterogeneous Systems . | 112 |

|   |      | 4.6.1   | Problen   | Definition                                                   | 114 |

|   |      | 4.6.2   | Propose   | ed Framework                                                 | 115 |

|   |      |         | 4.6.2.1   | States                                                       | 116 |

|   |      |         | 4.6.2.2   | Actions                                                      | 116 |

|   |      |         | 4.6.2.3   | Reward Function                                              | 117 |

|   |      | 4.6.3   | Experin   | nental Results and Discussion                                | 118 |

|   | 4.7  | Propo   |           | Application- and System-Level Runtime Management             |     |

|   |      | 4.7.1   |           | ad Assignment and Migration                                  |     |

|   |      | 4.7.2   |           | ed Runtime Management                                        |     |

|   |      | 4.7.3   |           | ed Quality-Aware Power and Thermal Management                |     |

|   |      |         | 4.7.3.1   | State Definition                                             |     |

|   |      |         | 4.7.3.2   | Action Pool and Action Set Definition                        |     |

|   |      |         |           |                                                              |     |

|     |       | 4.7.3.3  | Reward Function                                              | 128 |

|-----|-------|----------|--------------------------------------------------------------|-----|

|     | 4.7.4 | Experim  | nental Setup                                                 | 131 |

|     |       | 4.7.4.1  | Experimental Platform                                        | 131 |

|     |       | 4.7.4.2  | Compared Approaches                                          | 132 |

|     |       | 4.7.4.3  | Studied Scenario                                             | 132 |

|     | 4.7.5 | Experim  | nental Results                                               | 133 |

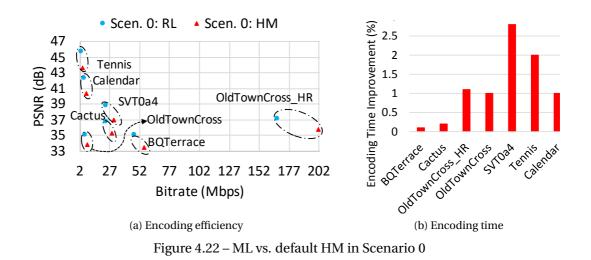

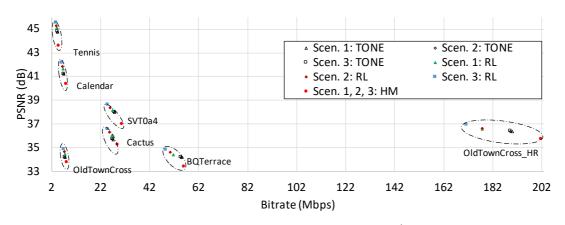

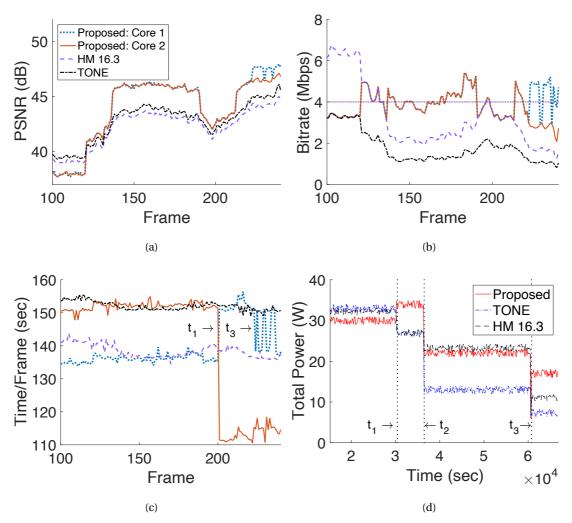

|     |       | 4.7.5.1  | Evaluation of Encoding Efficiency and Time                   | 133 |

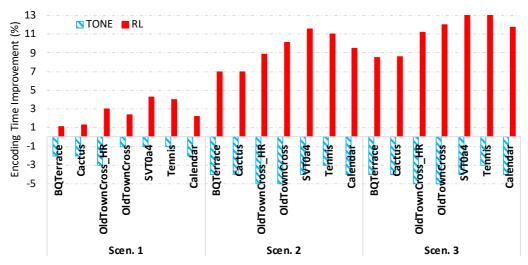

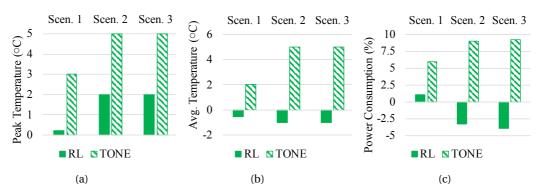

|     |       | 4.7.5.2  | Discussion on Power and Thermal Awareness                    | 136 |

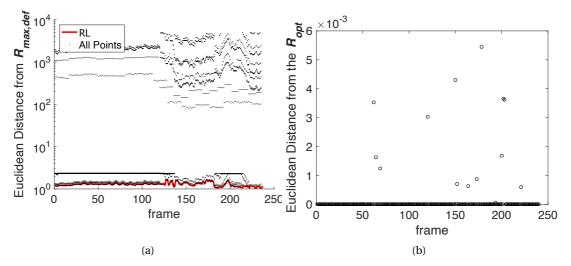

|     |       | 4.7.5.3  | Frame-by-Frame Evaluation of the ML-based Approach           | 137 |

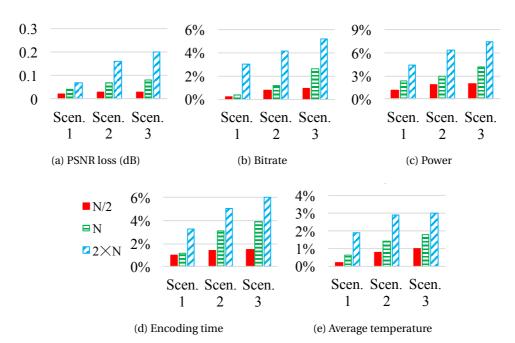

|     |       | 4.7.5.4  | Overhead and Performance of RL-Based Approach                | 137 |

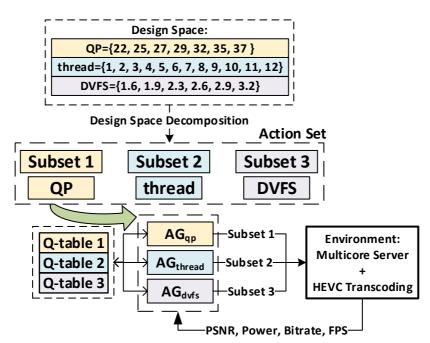

| 4.8 | MARL  | for Runt | ime Management of Multiprocessor Systems                     | 139 |

|     | 4.8.1 | Propose  | ed MARL Approach                                             | 140 |

|     |       | 4.8.1.1  | Agents                                                       | 141 |

|     |       | 4.8.1.2  | Actions                                                      | 141 |

|     |       | 4.8.1.3  | States                                                       | 142 |

|     |       | 4.8.1.4  | Reward Function                                              | 142 |

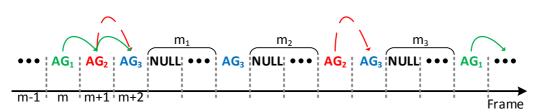

|     | 4.8.2 | Learnin  | g Phases and Learning Rate Function                          | 143 |

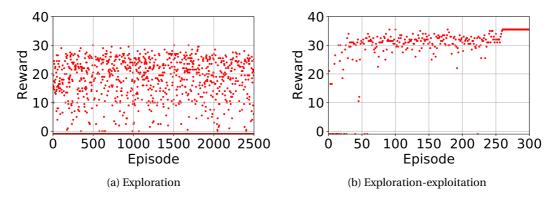

|     |       | 4.8.2.1  | Exploration and Exploration-Exploitation Phases              | 143 |

|     |       | 4.8.2.2  | Learning Rate                                                | 144 |

|     |       | 4.8.2.3  | Exploitation Phase                                           | 145 |

|     | 4.8.3 | Experim  | nental Setup                                                 | 146 |

|     |       | 4.8.3.1  | Case-Study HEVC Encoder                                      |     |

|     |       | 4.8.3.2  | Compared Approaches                                          | 146 |

|     |       | 4.8.3.3  | Experimental Platform                                        | 148 |

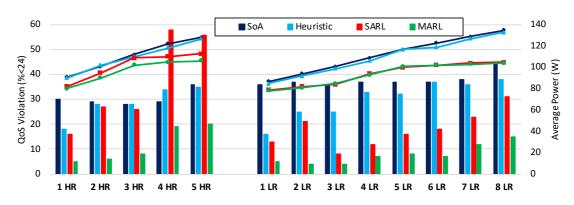

|     | 4.8.4 | Experim  | nental Results                                               | 148 |

|     |       | 4.8.4.1  | Scenario I: Serving Videos of Same Resolutions and Different |     |

|     |       |          | Contents                                                     |     |

|     |       | 4.8.4.2  | Scenario II: Serving Videos of Different Resolutions         |     |

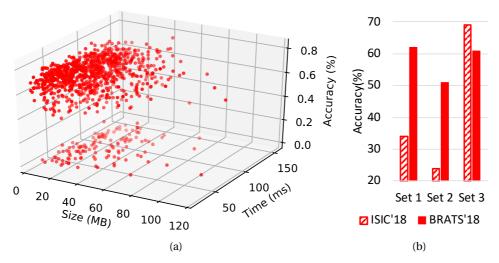

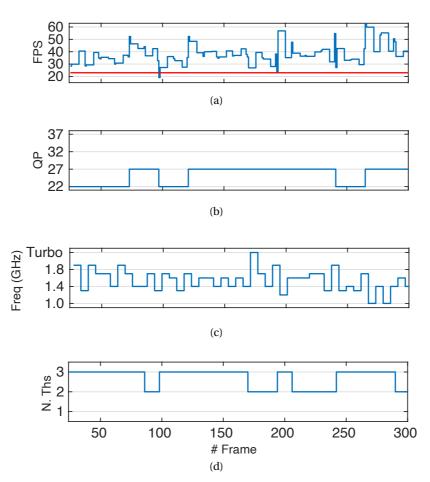

| 4.9 | U     | -        | Search for CNN Optimization                                  |     |

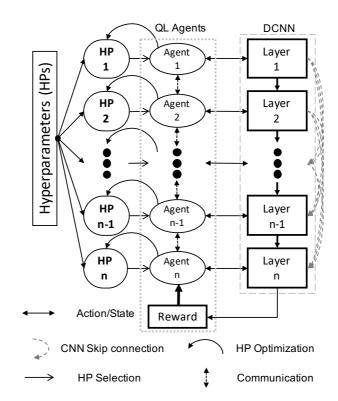

|     | 4.9.1 | Propose  | ed MARL Framework for Hyperparameter Optimization of CNNs    | 152 |

|     |       | 4.9.1.1  | Agents                                                       |     |

|     |       | 4.9.1.2  | Actions                                                      |     |

|     |       | 4.9.1.3  | States                                                       |     |

|     |       | 4.9.1.4  | Multi-agent Q-tables                                         | 156 |

|     |       | 4.9.1.5  | Reward Function                                              | 156 |

|     | 4.9.2 |          | g Process                                                    |     |

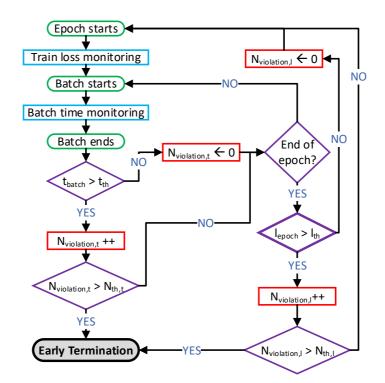

|     |       | 4.9.2.1  | Exploration Phase                                            | 157 |

|     |       | 4.9.2.2  | Q-table Updates                                              | 159 |

|     |       | 4.9.2.3  | Exploration-Exploitation Phase                               | 159 |

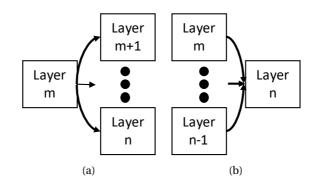

|     |       | 4.9.2.4  | Support for Skip Connections, Residual, Inception, and other |     |

|     |       | н ·      | Unconventional Modules                                       | 160 |

|     | 4.9.3 | Experim  | nental Setup, Test-Case DCNNs, and Datasets                  | 161 |

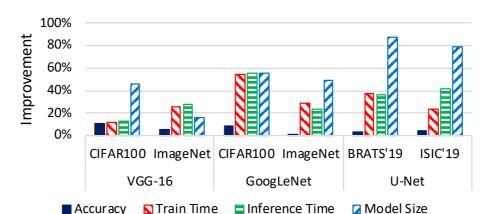

|    |                 | 4.9.4  | Experimental Results and Discussion                                      | 163 |  |  |

|----|-----------------|--------|--------------------------------------------------------------------------|-----|--|--|

|    |                 |        | 4.9.4.1 MARL Convergence                                                 | 163 |  |  |

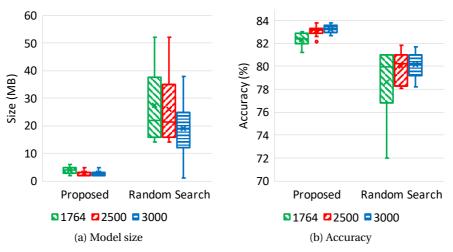

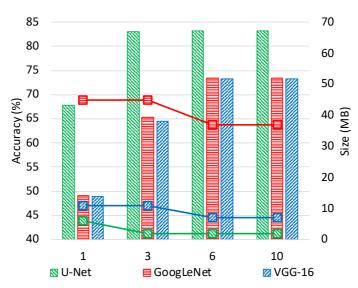

|    |                 |        | 4.9.4.2 Comparison to Random Search and Original Networks                | 164 |  |  |

|    |                 |        | 4.9.4.3 Impact of Number of Episodes in Exploration Phase                | 165 |  |  |

|    |                 |        | 4.9.4.4 Impact of Number of Epochs in Episodes                           | 166 |  |  |

|    | 4.10            | Sumn   | nary                                                                     | 167 |  |  |

| 5  | Con             | clusio | n and Future Work                                                        | 171 |  |  |

|    | 5.1             | Sumn   | nary of Contributions                                                    | 171 |  |  |

|    |                 | 5.1.1  | Heuristic Multi-Objective Management of Multiprocessor Systems           | 171 |  |  |

|    |                 | 5.1.2  | Machine Learning for Runtime Management of Time-Variant Workloads        | 172 |  |  |

|    |                 | 5.1.3  | Reinforcement Learning for Multi-Objective Management of Multipro-       |     |  |  |

|    |                 |        | cessor Systems                                                           | 173 |  |  |

|    | 5.2             | Discu  | ssion on RL Use in Different Optimization Problems                       | 176 |  |  |

|    | 5.3             | Futur  | e Work                                                                   | 177 |  |  |

|    |                 | 5.3.1  | Thermal Stress-Aware Lifetime Reliability of 3D SoCs                     | 177 |  |  |

|    |                 | 5.3.2  | Joint Optimization of Application- and System-Level Parameters in Multi- |     |  |  |

|    |                 |        | Application Platforms                                                    | 177 |  |  |

|    |                 | 5.3.3  | Design Automation of Deep Learning Architectures                         | 178 |  |  |

|    |                 | 5.3.4  | Multi-Objective Runtime Management of Fog Computing Systems              | 178 |  |  |

| Bi | Bibliography 17 |        |                                                                          |     |  |  |

### **Curriculum Vitae**

207

# List of Figures

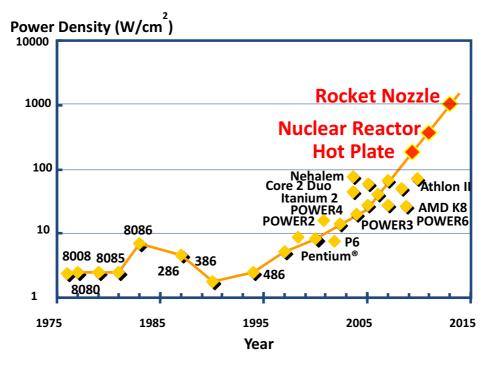

| 1.1  | Power density over time [10]                                                       | 3  |

|------|------------------------------------------------------------------------------------|----|

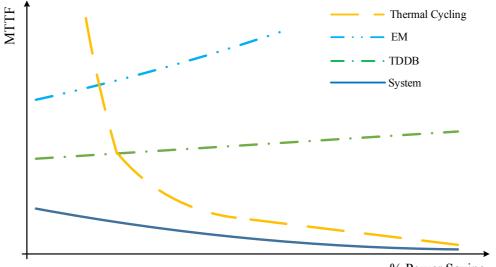

| 1.2  | MTTF vs. percentage of power saving provided by common DPM techniques [11]         | 4  |

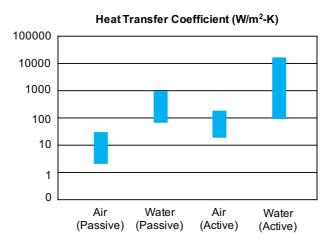

| 1.3  | Heat transfer coefficient of different cooling systems [21]                        | 5  |

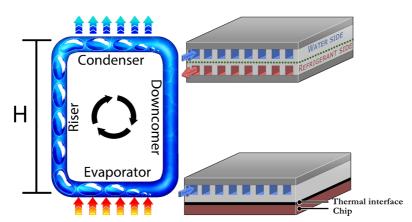

| 2.1  | Working principles of two-phase thermosyphon                                       | 25 |

| 2.2  | Thermosyphon prototype designed and manufactured by Seuret et al. [20]             | 25 |

| 2.3  | TheSPoT framework                                                                  | 29 |

| 2.4  | a) Average core temperature (K), b) Numbering the core pair under spatial stress   |    |

|      | based on the algorithm                                                             | 33 |

| 2.5  | Peak and valley temperatures as well as temporal temperature gradients (Slope).    |    |

|      | For the sake of simplicity, the transition at the beginning of each epoch has been |    |

|      | neglected                                                                          | 34 |

| 2.6  | Six cases for temperature trends of a pair of cores under spatial stress           | 36 |

| 2.7  | Runtime overhead of the optimization solution for different number of cores .      | 38 |

| 2.8  | The proposed flowchart of the heuristic DVFS algorithm in Tier2                    | 38 |

| 2.9  | Regions for different TTG criticality levels                                       | 40 |

| 2.10 | Proposed flowchart of Power and Temperature Checking                               | 44 |

| 2.11 | Floorplan of the 4-core, 8-core, and 16-core processors                            | 45 |

| 2.12 | Number of thermal violations occurred in one run of <i>blackscholes</i> benchmark  |    |

|      | for different number of cores when no thermal stress-aware approach applied .      | 47 |

| 2.13 | Average reductions (%) in STG, TTG, TCF, TCA, and performance overhead for         |    |

|      | TheSPoT compared to SoA [88] for 4-, 8- and 16-core MPSoCs                         | 47 |

| 2.14 | Average reductions (%) in STG, TTG, TCF, TCA, and performance overhead for         |    |

|      | TheSPoT compared with SoA [88] for different workload variations                   | 47 |

| 2.15 | Thermal map (K) obtained from a) [88], b) optimal, and c) heuristic approaches     |    |

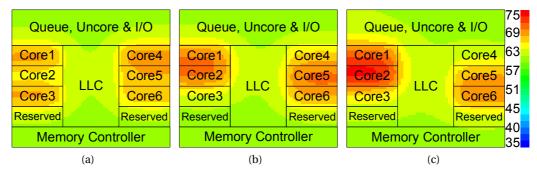

|      | under <i>facesim</i> benchmark for 8-core MPSoC                                    | 50 |

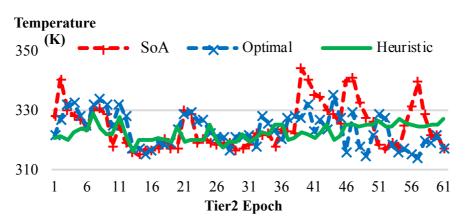

| 2.16 | Average temperature (K) of the first core under <i>facesim</i> benchmark           | 50 |

| 2.17 | Total power consumption (Watts) of the 8-core MPSoC under facesim                  | 51 |

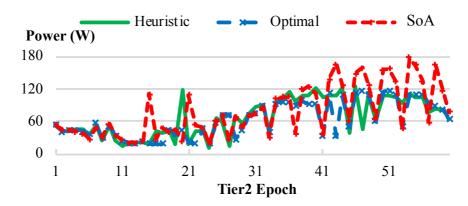

| 2.18 | Die thermal profile vs. package thermal profile when using thermosyphon with       |    |

|      | non-optimized design and workload mapping strategy.                                | 52 |

|      | Thermosyphon setup for DTM                                                         | 53 |

| 2.20 | Execution time normalized to QoS limit for some workload configurations $@f_{max}$ | 55 |

## List of Figures

| 2.21         | Package and die temperature for different orientations of thermosyphon on processor    | 56       |

|--------------|----------------------------------------------------------------------------------------|----------|

| າງງ          | Die thermal profile vs. package thermal profile when using thermosyphon with           | 50       |

| 2.22         | non-optimized design and workload mapping strategy                                     | 58       |

| <b>2 2</b> 3 | Thermal map of the die obtained from a) proposed approach and, b) state of the         | 50       |

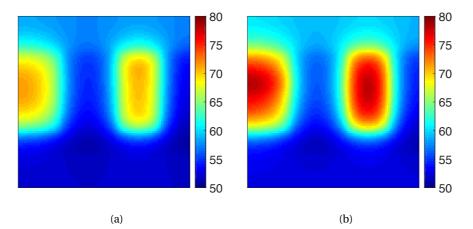

| 2.23         | art                                                                                    | 60       |

|              | alt                                                                                    | 00       |

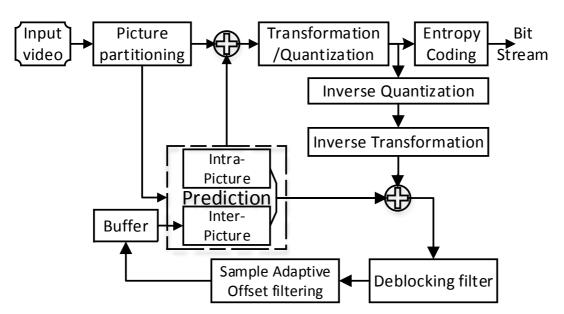

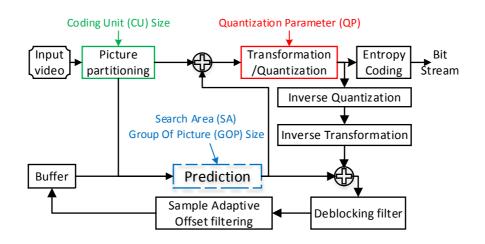

| 3.1          | Simplified HEVC encoder block diagram                                                  | 66       |

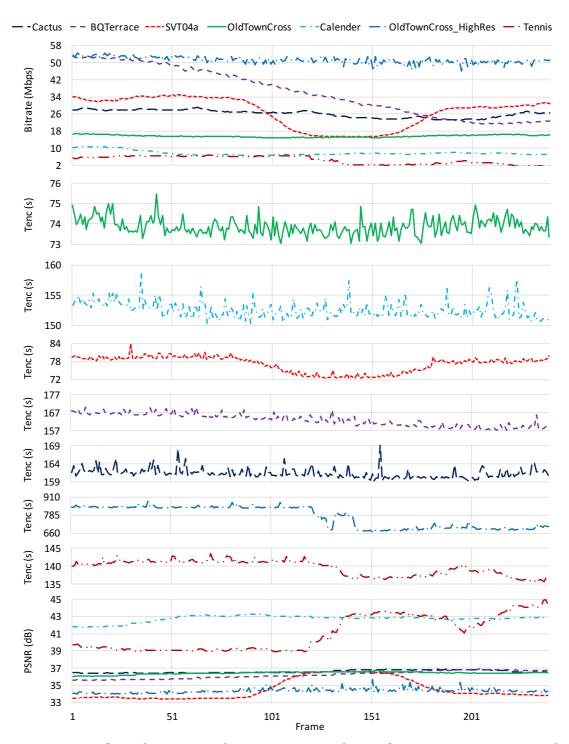

| 3.2          | Per-frame bitrate, encoding time $(T_{enc})$ , and PSNR for seven test sequences with  |          |

|              | Main Intra configuration                                                               | 67       |

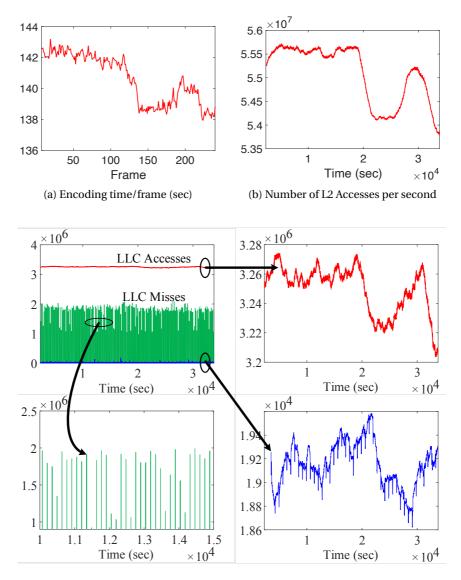

| 3.3          | Number of accesses to L2, accesses to LLC, misses from LLC and encoding                |          |

|              | time/frame for Tennis                                                                  | 69       |

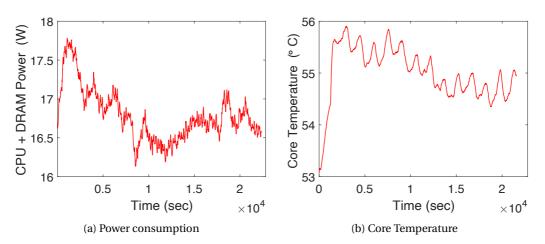

| 3.4          | Content-based power and temperature variation                                          | 70       |

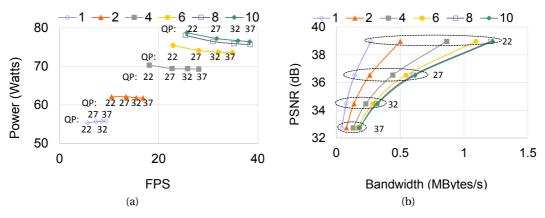

| 3.5          | RD-curves, power, and throughput with respect to number of threads: 1, 2, 4,           |          |

|              | 6, 8, and 10 and QP values: 22, 27, 32, and 37 while encoding a 1080p-video at         |          |

|              | 3.2GHz using Kvazaar with the <i>ultrafast</i> configuration                           | 70       |

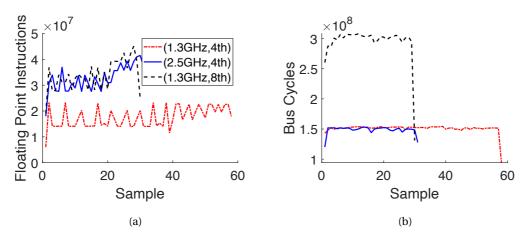

| 3.6          | Number of (a) floating point instructions and, (b) bus cycles, every 400 ms, under     |          |

|              | 3 system configurations: (frequency (GHz), number of threads)                          | 72       |

| 3.7          | Proposed ML-based framework                                                            | 74       |

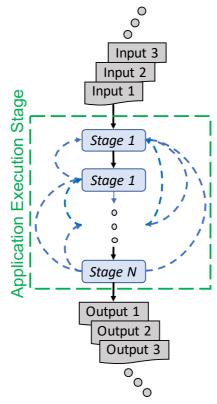

| 3.8          | Example of an application with iterative structure                                     | 75       |

| 3.9          | Proposed heuristic workload estimation, thread allocation, and DVFS for HEVC           |          |

|              | encoding                                                                               | 78       |

| 3.10         | Accuracy of the proposed (a) classification and (b) prediction $\ldots \ldots \ldots$  | 84       |

| 3.11         | Throughput prediction and actual throughput                                            | 85       |

| 4 1          | UEVC and an black discussion and main and main and mation menometers                   | 00       |

| 4.1          | HEVC encoder block diagram and main configuration parameters                           | 92       |

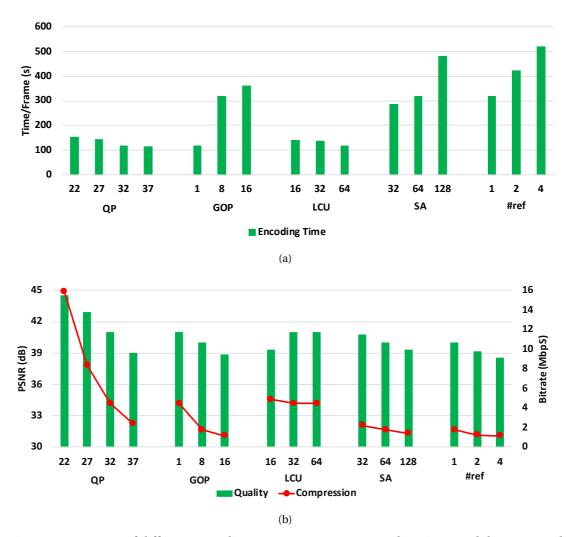

| 4.2          | Impact of different encoding parameters on (a) encoding time, and (b) PSNR             | 02       |

| 4.2          | and bitrate, for the test sequence <i>Tennis</i>                                       | 93       |

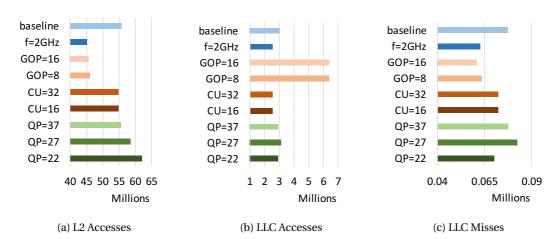

| 4.3          | Average number of accesses to L2, accesses to LLC, and misses from LLC every second    | 94       |

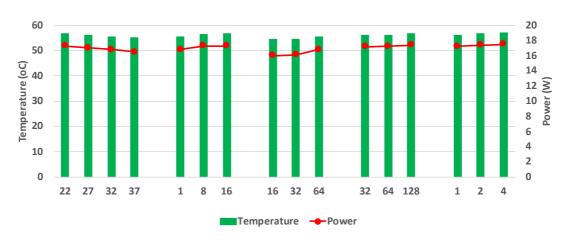

| 4.4          | second Impact of application parameters on CPU power and temperature for <i>Tennis</i> | 94       |

| 4.4          | running on one core                                                                    | 94       |

| 4.5          | Impact of frequency on encoding time, power and temperature, for the test              | 54       |

| 4.5          | sequence <i>Tennis</i> running on one core                                             | 95       |

| 4.6          | A simplified U-Net architecture                                                        | 95<br>96 |

| 4.0<br>4.7   | a) Model size, validation accuracy, and inference time for 1000 different sets of      | 50       |

| 4.7          | hyperparameters for BraTS'18 dataset, b) Accuracy with three different hyperpa-        |          |

|              | rameter sets for BraTS'18 and ISIC'18 datasets                                         | 97       |

| 4.8          | A basic Reinforcement Learning scenario                                                | 98       |

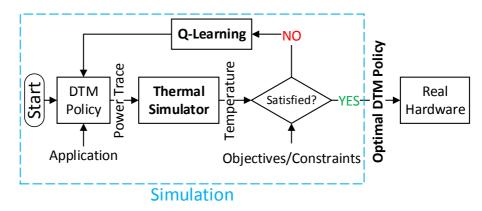

| 4.9          | Simulation framework and methodology for learning process                              | 107      |

|              | Simulation framework and methodology for learning process                              | 107      |

|              | The thermal test chip used for the validation.                                         | 100      |

|              | Number of cores and corresponding mapping                                              |          |

| 4.13 | Comparison of hot spot temperature and fan speed obtained from different           |     |

|------|------------------------------------------------------------------------------------|-----|

|      | approaches                                                                         | 113 |

| 4.14 | Overall view of HEVC streaming on heterogeneous SoC.                               | 114 |

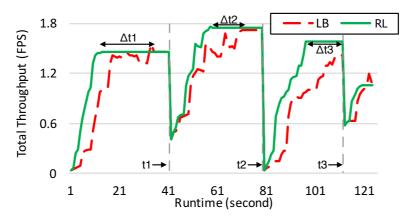

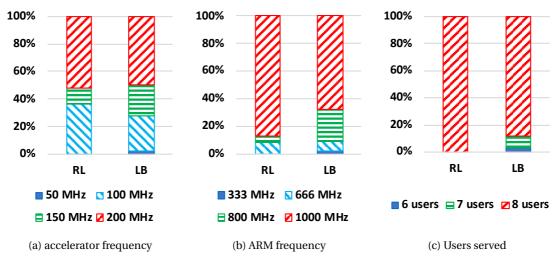

| 4.15 | Total throughput of the proposed RL vs. LB over time                               | 118 |

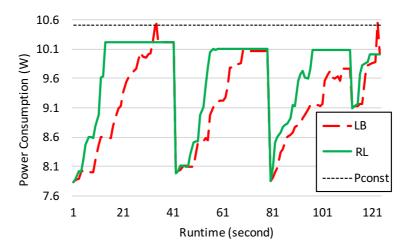

| 4.16 | Power consumption of the proposed RL vs. LB over time.                             | 119 |

| 4.17 | Percentage of time that each frequency is used and number of users served by       |     |

|      | RL and LB.                                                                         | 120 |

| 4.18 | Proposed Approach                                                                  | 121 |

| 4.19 | Average encoding time/frame for different videos when encoded by default Main      |     |

|      | Intra configuration                                                                | 122 |

| 4.20 | RL-based approach block diagram                                                    | 125 |

| 4.21 | Reward functions of a) PSNR, b) bitrate, c) power, d) encoding time, and e)        |     |

|      | temperature                                                                        | 130 |

| 4.22 | ML vs. default HM in Scenario 0                                                    | 133 |

| 4.23 | PSNR vs. bitrate achieved by RL, TONE, and HM* for all test sequences and          |     |

|      | scenarios                                                                          | 134 |

| 4.24 | Encoding time of RL and TONE compared to HM*, for all test sequences and           |     |

|      | scenarios                                                                          | 134 |

| 4.25 | (a) peak temperature, (b) average temperature, and (c) power consumption of        |     |

|      | the proposed approach (RL) and TONE compared to $\mathrm{HM}^*$                    | 135 |

| 4.26 | Thermal map (°C) of the third Scenario for (a) RL and video assignment, (b) only   |     |

|      | RL, and (c) TONE                                                                   | 135 |

| 4.27 | Frame-by-frame results for Tennis: proposed RL-based approach (Core 1 and          |     |

|      | Core 2) versus TONE and HM 16.3 (the best core)                                    | 136 |

| 4.28 | a) Euclidean distance of several solutions from the maximum defined reward         |     |

|      | $R_{max,def}$ , and b) Euclidean distance of ML solution from the optimal reward,  |     |

|      | $R_{opt}$                                                                          | 138 |

| 4.29 | a) PSNR loss (dB), and increase (%) in b) bitrate, c) power, d) encoding time, and |     |

|      | e) average temperature when scaling up the decision interval compared to when      |     |

|      | using $N/N$ interval                                                               | 139 |

| 4.30 | Proposed multi-agent RL approach (MAMUT)                                           | 141 |

| 4.31 | Agent sequence. Arrows show which agents need to look at the Q-table of the        |     |

|      | next agent                                                                         | 142 |

| 4.32 | Proposed heuristic framework for run-time adaptation of HEVC encoder param-        |     |

|      | eters                                                                              | 147 |

| 4.33 | QoS violation (in terms of percentage of frames under QoS threshold) and power     |     |

|      | consumption for the SoA, heuristic, SARL and MARL (MAMUT) encoding differ-         |     |

|      | ent combinations of HR and LR videos.                                              | 149 |

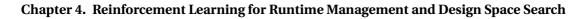

| 4.34 | Traces of actions selected by MAMUT and output FPS for a randomly selected         |     |

|      | video when encoding 5 LR videos.                                                   | 150 |

|      | Overview of proposed MARL-based hyperparameter optimization                        | 153 |

| 4.36 | Schema of proposed MARL-based approach on a 5-layer CNN                            | 155 |

| 4.37 Early termination mechanism                                                  | 157 |

|-----------------------------------------------------------------------------------|-----|

| 4.38 Two types of unconventional connections in modern CNNs: a) one layer feeds   |     |

| multiple layers, b) one layer is fed by multiple layers                           | 161 |

| 4.39 Convergence of proposed MARL-based approach with respect to reward values    | 163 |

| 4.40 Improvement in accuracy, model size, and training/inference time provided by |     |

| MARL-based approach compared to Random Search                                     | 164 |

| 4.41 Impact of number of episodes in exploration phase                            | 166 |

| 4.42 Impact of number of epochs in an episode                                     | 167 |

# List of Tables

| 2.1  | Thermal values                                                                     | 44  |

|------|------------------------------------------------------------------------------------|-----|

| 2.2  | Design parameters of the target multiprocessor system architecture                 | 45  |

| 2.3  | Average reduction in spatial temperature gradient, temporal temperature gra-       |     |

|      | dient, thermal cycle number, and thermal cycle amplitude, and performance          |     |

|      | overhead                                                                           | 46  |

| 2.4  | Total number of thread migrations, and average operating frequencies of on cores   | 49  |

| 2.5  | Temperature comparison: die vs. package                                            | 53  |

| 2.6  | C-states power consumption of Xeon E5 v4 for all 8 cores                           | 55  |

| 2.7  | Comparison between two different designs shown in Figure 2.21                      | 56  |

| 2.8  | Die temperature for three different scenarios of Figure 2.22                       | 58  |

| 2.9  | Thermal hot spot and spatial gradients for different QoS requirements              | 60  |

|      |                                                                                    | ~-  |

| 3.1  | Test sequences                                                                     | 65  |

| 3.2  | Pearson correlation matrix of different performance counters and HEVC encoder      |     |

|      | throughput (FPS)                                                                   | 83  |

| 3.3  | Average throughput estimation error and QoS violations                             | 86  |

| 3.4  | Comparison to the state-of-the-arts (SoA)                                          | 86  |

| 4.1  | Application and system parameters, and corresponding selected values               | 92  |

| 4.2  | State-of-the-arts on hyperparameter optimization and neural architecture search    |     |

|      | of CNNs                                                                            | 106 |

| 4.3  | State definition                                                                   | 110 |

| 4.4  | Schedule of <i>e</i> based on number of actions to be taken                        | 111 |

| 4.5  | Comparison between different policies at two thermal constraints                   | 112 |

| 4.6  | Reference throughput with respect to resolution and search area                    | 117 |

| 4.7  | Number of threads and frequency used in average                                    | 149 |

| 4.8  | Scenario II, average results. Each row reports metric for a sequence of a specific |     |

|      | combination of videos                                                              | 151 |

| 4.9  | Model settings and datasets                                                        | 162 |

| 4.10 | Layers and hyperparameters                                                         | 162 |

| 4.11 | Experimental results: Top-1 accuracy for image classification and Dice coeffi-     |     |

|      | cient for semantic segmentation.                                                   | 165 |

|      |                                                                                    |     |

# Acronyms

ARIMA Auto-Regressive Integrated Moving Average

- ASR Adaptive Search Range

- AVC Advanced Video Coding

- AVFS Adaptive Voltage and Frequency Scaling

- BraTS Brain Tumor Segmentation

- CU Coding Unit

- DCLC Direct Contact Liquid Cooling

- DELC Dual Enclosure-Liquid Cooling

- DPM Dynamic Power Managemnt

- DTM Dynamic Thermal Management

- DVFS Dynamic Voltage and Frequency Scaling

- DVS Dynamic Voltage Scaling

- EM Electromigration

- FPS Frame per Second

- GOP Group of Pictures

- HEVC High Efficiency Video Coding

- HPC High-Performance Computing

- IPC Instruction Per Cycle

- IPMI Intelligent Platform Management Interface

- IPS Instruction Per Second

- ISIC International Skin Imaging Collaboration

#### Acronyms

JCT-VC Joint Collaborative Team on Video Coding LCU Largest Coding Unit LLC Last Level Cache MARL Multi-Agent Reinforcement Learning ML Machine Learning MPSoC Multiprocessor System-on-Chip MTTF Mean Time to Failiure OS **Operating System** PCA Principal Component Analysis PQL Pareto Q-Learning PUE Power Usage Effectiveness PWM Pulse-Width Modulation QL Q-Learning QoS Quality of Service QP **Quantization Parameter** RAPL Running Average Power Limit RL **Reinforcement Learning** RMSE Root Mean Square Error SARL Single-Agent Reinforcement Learning SGD Stochastic Gradient Descent SoC System-on-Chip STG Spatial Thermal Gradient TC **Thermal Cycling** TDDB Time Dependent Dielectric Breakdown TTC Thermal Test Chip TTG **Temporal Thermal Gradient** WPP Wavefront Parallel Processing

xxiv

# 1 Introduction

Since 1990s to early 2000s, clock frequency accounted for more than 80% of the increase in the uniprocessor performance at each technology node [1]. Although performance was the primary design objective since the beginning of the microprocessors era in 1970s, other key aspects, such as energy consumption, power dissipation, and temperature, started to become the main concerns of microprocessor designers. This was mainly due to the fact that with each new generation, microprocessors faced decreased physical dimension and increased number of transistors; thus, scaling the operating frequency ran into the physical barriers [2].

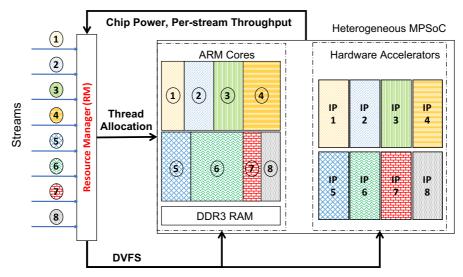

One breakthrough that helped microprocessors to keep up with the ever-increasing demand of performance without a consequent increase in the clock frequency was integrating multiple cores in a processor. With the introduction of multi-core processors, performance, thermal, power, and energy concerns could be temporarily relieved through higher performance by the same operating frequency of microprocessors and more distributed power dissipation across the processor. Nonetheless, as the demand for higher performance kept increasing, Multiprocessor Systems-on-Chip (MPSoCs) were introduced, where multiple processors, each containing one or more cores are integrated on the same SoC (System-on-Chip). The multiprocessor systems term, however, encompasses a variety of different systems, such as MPSoCs, multi-core and multiprocessor servers, GPUs (Graphical Processing Unit) with multiple CUDA and Tensor cores, ZYNQ SoCs, etc. Throughput the remainder of this thesis, by multiprocessor systems, I refer to any system composed of multiple cores or processors, either integrated on the same chip or communicating through any Inter-Processor Communication (IPC) protocols.

# 1.1 Multi-Objective System-Level Management of Multiprocessor Systems

Although multiprocessor systems have been introduced to address the high performance demand while mitigating power dissipation and thermal issues, none of these goals can be achieved in the lack of proper system-level management. Compared to the uniprocessor

systems, multi-objective system-level management of modern multiprocessor systems is more challenging and, if poorly managed, not only the same performance, power and thermal concerns of the uniprocessors persist, but also unprecedented issues and challenges with respect to these design objectives and constraints can arise.

In particular, while workload allocation and scheduling is vital for taking the most advantage of multiprocessor systems, finding the optimal workload mapping and scheduling is known to be NP-hard. Moreover, today's multiprocessors come with a wide range of operating frequency. In order to maximize performance while satisfying the design constraints, such as power consumption and thermal hot spots, the operating frequency should be adjusted according to the performance requirement and these design constraints. Applying this technique, known as Dynamic Voltage and Frequency Scaling (DVFS) [3], becomes even more challenging for modern systems where per-core frequency adjustment is provided for more fine-grained power and performance control. Finally, as a consequence of these new features, power, performance, and lifetime reliability management of multiprocessor systems is more burdensome than any time.

In the following subsections, I provide an overview of different design objectives and constraints considered in the scope of my thesis.

### 1.1.1 Power and Performance Management

According to Amdahl's Law in the multi-core era [4], the maximum speedup (S) achievable through parallelization can be theoretically obtained as follows:

$$S = \frac{1}{1 - f + \frac{f}{n}},$$

(1.1)

where *f* is the fraction of computation that can be parallelized ( $0 \le f \le 1$ ), and *n* represents the number of processors. The speedup per watt of such a multiprocessor system is computed by [5]:

$$\frac{S}{W} = \frac{1}{1 + (n-1)k(1-f)},\tag{1.2}$$

where  $0 \le k \le 1$  is the fraction of power the processor consumes in idle mode. Despite their incompleteness and simplicity for today's modern multiprocessor systems, equations (1.1) and (1.2) indicate that while multiprocessor systems can increase the performance through parallel processing, the average power consumption would grow dramatically, such that  $\frac{S}{W} \rightarrow 0$ . As a result, in spite of the fact that increasing the performance has been traditionally the primary objective for processor designers, nowadays, a joint optimization of power consumption and performance is vital.

Moreover, power consumption has become one of the first-order design constraints in many

Figure 1.1 – Power density over time [10]

multiprocessor systems. For embedded, high performance, and large scale systems, power consumption is the main concern due to battery lifetime, heat dissipation, and electricity billing costs, respectively [6]. More specifically, if the power consumption increases by a factor of 2, battery lifetime of embedded systems may degrade by a factor of 3 [7]. In addition, as a rule of thumb, every 1 W of power in high performance computing systems leads to 1 W of power spent on cooling. Finally, the electricity consumption of data centers across the U.S is estimated to reach 139 billion kWh in 2020 [8, 9] costing an annual bill of around \$20 billion.

### 1.1.2 Lifetime Reliability and Thermal Management

The increase in the speed of multiprocessor systems along with the shrinkage of the feature size at each technology node has led to higher power density and, thus, higher peak and average temperature across the chips. Figure 1.1 shows how over the recent years, the power density of uniprocessors and multiprocessor systems have increased. On one hand, temperature increases super linearly as the power density increases. On the other hand, leakage power and temperature are interrelated through a positive feedback. Therefore, proper thermal management is essential to have a functional multiprocessor system.

Another important issue arising with high power density and, thus, temperature, is the IC (Integrated Circuit) failure rate [12], where a  $10-15^{\circ}C$  difference in temperature may halve the life span. Moreover, the availability of more resources in comparison with uniprocessors leads to more non-uniformity of the temperature profile on multiprocessor systems. Spatial thermal

% Power Saving

Figure 1.2 - MTTF vs. percentage of power saving provided by common DPM techniques [11]

gradients across the chip deteriorate the system reliability and degrade its performance. Also, the variety of the workloads, which could be processed at the same time, may cause large temporal thermal variations at a single point on the chip. More importantly, thermal cycling, as a new dominant failure mechanism, leads to degrading the performance and reliability of modern processors.

Several power management techniques including Dynamic Voltage Scaling [13], task allocation and scheduling [14], and throttling [15, 16] help reducing the chip average temperature by lowering the average power consumption. Although these approaches reduce hard failures corresponding to Electromigration (EM) and Time-Dependent-Dielectric-Breakdown (TDDB), they do not take into account thermal stress as an important factor in lifetime reliability. The study performed by Coskun et al. [17] reveals that the increase in the amount of power saving, which is usually followed by peak and average temperature reduction, improves the mean time-to-failure (MTTF) by reducing the EM and TDDB occurrences, whereas it causes the overall MTTF of the system to fall down, since the MTTF related to thermal cycling decreases faster. Particularly, common DPM (Dynamic Power management) and DTM (dynamic thermal Management) approaches are effective in decreasing the total power consumption and peak/average temperature. Nonetheless, such techniques cause rising and falling of the temperature not only more frequently but also with higher amplitudes, hence, reducing reliability of the system. For instance, for metallic structures, when a thermal cycle amplitude increases from  $10^{\circ}C$  to  $20^{\circ}C$ , the lifetime reliability may decrease by up to 16 times [11]. Figure 1.2 shows how conventional DPM techniques can adversely result in MTTF degradation. This suggests that, if not performed properly, power management techniques may deteriorate the lifetime of multiprocessor systems by aggravating the thermal stress.

Figure 1.3 – Heat transfer coefficient of different cooling systems [21]

### 1.1.3 Cooling

Another important drawback with high power density is the cooling cost. As a rule of thumb, every 1 W of power in IC leads to 1 W of power spent on cooling, if designed for the worst-case scenario [18]. Moreover, IC and system packaging/cooling cost increases super-linearly with power consumption [19]. This increasing cooling cost, consequently, urges processor designers and researchers to seek thermal solutions to keep the temperature lower than a threshold. Nevertheless, cooling is inevitable in today's multiprocessor systems. Each system, however, requires a particular cooling method. In particular, while heat spreaders may be the only option for mobile embedded systems, for high-performance and large-scale computing systems more advanced cooling technologies have to be used. Each of these cooling methods has pros and cons. Inexpensive passive cooling through heat sinks is not effective for high performance computing systems. Fans, as the most common active air cooling system, contribute to higher electricity bill. Liquid cooling provides higher efficiency in heat removal than air cooling, however, it also requires additional power supply. Alternatively, emerging two-phase cooling systems, such as thermosyphons [20], can take advantage of gravity and provide efficient cooling with no extra power consumption in theory, while operating inaudibly.

Figure 1.3 shows the heat transfer coefficient achievable through different cooling systems, with respect to the convection type [21]. In order to achieve efficient heat removal, the thermal profile of multiprocessor systems along with the capabilities of the cooling system need to be studied. Indeed, particular potential of a cooling system may significantly influence the strategies taken in traditional power and thermal management of multiprocessor systems. Moreover, with the advent of new cooling technologies, such as thermosyphon, it is necessary to adapt DTM approaches to their new features.

# 1.2 Emerging Application Models and Quality of Service Requirements

Traditionally, Quality-of-Service (QoS) is known as the desirable performance, in terms of either throughput or latency, for many applications, such as web search and data analytics. However, for many emerging applications, such as bio-medical imaging and video streaming, QoS cannot anymore simply account for performance. Moreover, many new trending application, e.g., multimedia applications, expose several internal parameters through which system-level objectives and constraints can be considerably affected. As a consequence, power, performance, and thermal management of multiprocessor systems can no longer solely rely on conventional design parameters, such as operating frequency and workload allocation, but rather designers need to take into account application-level parameters to jointly optimize along with these well-studied system-level parameters. Obviously, with application-level parameters included in the design space and adding emerging QoS requirements to the design objectives and constraints, multi-objective management of multiprocessor systems becomes more challenging.

### 1.2.1 Video Coding

In 2015, real-time entertainment already accounted for more than 74% of downstream network traffic in North America, with streaming services, including Netflix, YouTube, and Amazon Video, accounting for 57% of the global share [22]. According to The Global Internet Phenomena Report by Sandvine [23], by the end of 2019, 65% of the worldwide mobile traffic was video streaming. The network traffic share of video streaming is expected to experience a new spike as several other video providers, such as Disney+, HBO Max, and Apple, will soon launch their services. Such a shift of services and application was, indeed, predicted by the ITRS in 2009 [24]. For video streaming services and applications performance can keep its common definition, i.e., framerate known as frame per second (FPS), represents the throughput. For real-time streaming, meeting the required FPS (e.g., 24, 30, or 60 Hz, depending on the application) is one of the first-order design objectives, and accounts for the main challenge. However, QoS and Quality-of-Experience (QoE) of the user will also depend on the video quality, usually measured as the Peak Signal-to-Noise ratio, and bitrate. The latter strongly depends on the user end, nonetheless, video providers can play an important role by detecting the user's bandwidth and adjusting the bitrate accordingly. The recent video coding standards such as High Efficiency Video Coding (HEVC), a.k.a x265, and Advanced Video Coding (AVC), a.k.a x264, provide several internal application-level parameters, adjustable at run-time. These parameters can be used to provide a trade-off between the computational complexity and the output video in terms of performance (particularly, throughput), quality and bitrate. On the other hand, the computational complexity can considerably affect the power consumption and thermal profile of the video providers' servers.

The increasing popularity of streaming applications and services implies a shift in the nature of

workloads with which multiprocessor systems need to deal. Multimedia workloads are heavily dependent on the input data (e.g., raw videos). Even though, similar to many applications, multimedia is composed of several sequential or parallel process phases, the amount of CPU workload of each depends on features of the input video frames. The main features include size, amount of motion and complexity of the texture, as well as the temporal and spatial locality between frames and within a frame. On one hand, since the video content can be anything, it is very difficult to accurately predict the next coming frames (hence, upcoming workload) to proactively apply the most appropriate multi-objective management policy. On the other hand, content (input) variation and, thus, workload variation, can be very fast. Therefore, it is essential to have a very low-overhead multi-objective management policy such that it can adapt to the high variant workload in a short amount of time.

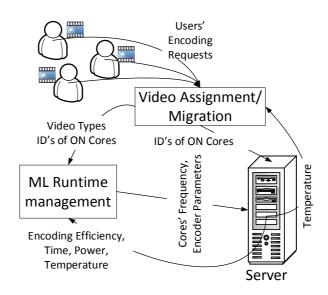

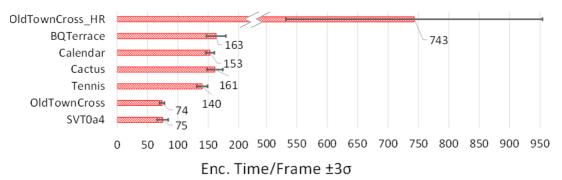

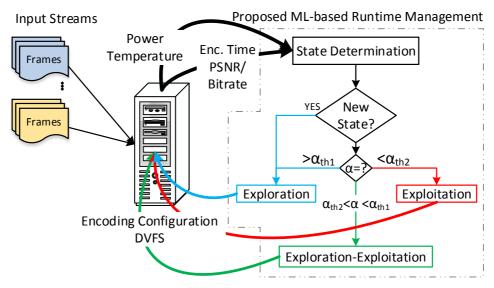

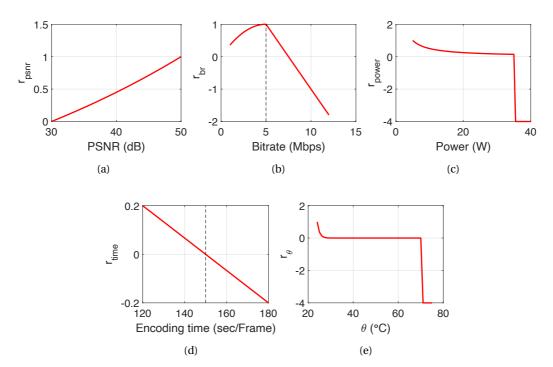

### 1.2.2 Deep Learning