### ColTrain: Co-located DNN training and inference

Présentée le 25 septembre 2020

à la Faculté informatique et communications Laboratoire d'architecture de systèmes parallèles Programme doctoral en informatique et communications

pour l'obtention du grade de Docteur ès Sciences

par

#### Mario Paulo DRUMOND LAGES DE OLIVEIRA

Acceptée sur proposition du jury

Prof. C. Koch, président du jury

Prof. B. Falsafi, Prof. M. Jaggi, directeurs de thèse

Prof. A. Moshovos, rapporteur

Dr M. Papamichael, rapporteur

Prof. J. Larus, rapporteur

## Acknowledgements

Doing a PhD was the hardest thing I have ever done in my entire life, by far. I would never have made it without extensive support from my mentors, who taught me everything I needed to complete this journey and the people who provided me with the moral support I needed to keep going.

First, I am grateful to my advisors, Babak Falsafi and Martin Jaggi. Babak's presence is legendary. I still remember my first meeting with him, how impressed I was with his self-confidence and his direct communication. I knew within ten seconds of talking to him that I needed someone like him to realize any potential I had. I was right. Babak taught me everything: to write, to speak, to think, to present my work, and to interact with the community. He did not stop there. He also taught me to appreciate food, coffee, beer, and even skiing. At some points, when my willpower faltered, Babak pushed across many finish lines. The training that Babak offers changes every aspect of his students' lives, and I am grateful that I received his mentorship. Martin entered my life later during my PhD, in my third year. Martin's steady and calming presence provided a good counterbalance to Babak's aggressiveness. Whenever I needed reassurance, Martin was the right person to look for. Martin also guided me through the world of machine learning, a world I knew nothing about before starting my PhD. With his guidance, I was able to identify good work in a somewhat foreign field. I am very grateful that Martin took time from his busy schedule to help me.

Next, I would like the people who directly contributed to this thesis. First, I would like to thank Jim Larus, Michael Papamichael, Andreas Moshovos, and Christoph Koch for serving in my PhD thesis committee. Their guidance made my thesis better. I would also like to thank Hadi Esmaeilzadeh for participating in my thesis proposal. His relentless grilling helped me

solidify my thesis. I would also like to thank Jim Larus (again) and Paolo Ienne, who served in my candidacy exam committee and provided me with instrumental advice early in my PhD. My closest collaborators were Tao Lin, Ahmet Yüzügüller, and Arash Pourhabibi. I was very fortunate to have them. Without them, I would not have a thesis.

I must also thank the people who contributed to my formation. Karu Sankaralingam, from the University of Wisconsin, was the person who put me on the map. Karu took me into his lab, gave me a very interesting project, MIAOW, and, when it was time for me to apply for grad school, guided me through the process. Without Karu, I would have never made it into EPFL. I also want to thank Alexandros Daglis. Alex was a senior student when I joined the lab. Early in my PhD, he helped me formulate my ideas and with my writing. I also learned a lot from just observing Alex working. On top of everything, Alex is also a very close friend of mine.

My lab mates were instrumental in giving me emotional support and valuable technical feedback. I was fortunate to end up in PARSA, where Babak encourages students to form a strong lab culture. Javier Picorel was the most senior student when I joined the lab. I have never met anyone with such an extensive knowledge of everything systems-related. Javier is also one of the funniest people I have ever met. Arash Pourhabibi was a collaborator and a very close friend. We even lived together for a few years. Those were happy days. Arash's is probably the most patient person I have ever known. Siddharth Gupta and Rishabh Iyer joined the lab later as interns but became my very close friends and my ski buddies. Sid is a doer, the most efficient person I have ever met. Although I cannot forgive Rishabh for defecting from the lab, he is still cool. Rafael Pizarro Solar is probably the most intelligent person I have ever met. Also, the craziest. Working with him was a very joyful and exciting journey. Dmitrii Ustiugov is the most persistent person I have ever met, whenever I think about quitting something, I think about Dmitrii never quitting anything. Nooshin Mirzadeh is a great friend. She really helped me feel at home at PARSA. Hussein Kassir was my FPGA buddy in the lab. We also tavelled a lot together, I keep good memories of those trips. Unfortunately, I could never hang out with Zilu Tian, Ognjen Glamocanin, Simla Harma, Dina Mahmoud, and Pradeep Kathirgamaraja, as much as I wanted, as they arrived as I was leaving. However, their company was still appreciated in the short time we had together. I would also like to thank my senior

students, Cansu Kaynak, Djordje Jevdjic, Stavros Volos, and Onur Kocberber, who I did not get to hang out with as much as I wished, as they were leaving when I arrived at PARSA. Finally, I would like to thank Stephanie Baillargues. Stephanie helped us in everything related to EPFL, going above and beyond to fix our messes. Several times I came to Stephanie in desperation, and she quickly solved all my problems.

I would not have made it without the moral support of my family and friends. My mom and sister, Hilda and Daina, are an inspiration and a reason for me to go on. Without them, I would not have gone to university nor have left Brazil. Being away from my family is painful, but I hope I am making them proud. I love them both very much. Another source of moral support was my wife, Juliette, who had to also endure my grumpiness when things did not go well. She always cheers me up, and her support is the main reason I never quit my PhD. I love her more than anything. My parents-in-law, Maria and Jorge, and my sisters-in-law, Sarah and Stéphanie, gave me a family and a home away from home. I am really thankful for that. Finally, I would like to thank the Swiss people for accepting me in their great country and

Finally, I would like to thank the Swiss people for accepting me in their great country and supporting me through their taxes and EPFL. Switzerland is truly the best place to live in the world, and I was very fortunate to do my PhD here. I hope I get to live the rest of my life here.

## **Abstract**

Deep neural network inference accelerators are deployed at scale to accommodate online services, but face low average load because of service demand variability, leading to poor resource utilization. Unfortunately, reclaiming inference idle cycles is difficult, as no other workload can execute on such custom accelerators. DNN training services offer opportunities to reclaim inference accelerator idle cycles. However, the inference services' tight latency constraints and the training algorithms' dependence on floating-point arithmetic limit the opportunities for piggybacking training services on inference accelerators.

In this thesis, we tackle the challenges that prevent inference DNN accelerators from exposing their idle cycles to training services. We first develop an efficient numeric representation that enables DNN training with accuracy similar to single-precision floating point and energy efficiency similar to 8-bit fixed point. Then, we explore the inference accelerator design space to show that, unlike in current latency-optimal platforms, relaxing latency constraints with ALU arrays that are batching-optimized achieves near-optimal throughput for a given area and power envelope. High throughput inference accelerators maximize the opportunities to piggyback training. Finally, we present Equinox, a family of inference accelerators designed to piggyback training. Equinox employs a uniform encoding and a priority hardware scheduler that processes training requests during inference idle cycles without affecting inference tail latency. Overall, we show that exposing accelerator idle cycles to training services uncovers significant computing power for training services with a small overhead for inference accelerators, improving overall datacenter efficiency.

Keywords: datacenters, deep neural network accelerators, online services, systolic array,

#### Abstract

arithmetic representation, block floating point

### Résumé

Les accélérateurs d'inférence des réseaux neuronaux profonds qui exécutent des services en ligne sont confrontés à de faibles charges moyennes en raison de la variabilité de la demande de services, ce qui entraîne une utilisation réduite des ressources. Malheureusement, il est difficile de récupérer les cycles d'inactivité d'inférence, car aucune autre charge de travail ne peut être exécutée sur de tels accélérateurs personnalisés. Les services d'entraînement des réseaux neuronaux profonds offrent la possibilité de récupérer les cycles d'inactivité des accélérateurs d'inférence. Cependant, les contraintes de latence strictes des services d'inférence et la dépendance des algorithmes d'entraînement à l'arithmétique en virgule flottante limitent les possibilités d'utiliser des services d'entraînement pour récupérer les cycles d'inactivité des accélérateurs d'inférence.

Dans cette thèse, nous abordons les défis qui empêchent les accélérateurs d'inférence des réseaux neuronaux profonds d'exposer leurs cycles inactifs aux services d'entraînement. Nous développons d'abord une représentation numérique efficace qui permet l'entraînement des réseaux neuronaux profonds avec une exactitude similaire à la virgule flottante à simple précision et une efficacité énergétique similaire à la virgule fixe à 8 bits. Ensuite, nous explorons l'espace de conception des accélérateurs d'inférence pour montrer que, contrairement aux plates-formes actuelles de latence optimale, l'assouplissement des contraintes de latence avec des réseaux d'unité arithmétique et logique optimisés par lots permet d'obtenir un débit quasi optimal pour une enveloppe d'aire et de puissance. Les accélérateurs d'inférence à haut débit maximisent les possibilités d'entraînement pour récupérer les cycles d'inactivité des accélérateurs d'inférence. Enfin, nous présentons Equinox, une famille d'accélérateurs d'inférence conçus pour exposer les cycles d'inactivité aux services d'entraînement. Equinox utilise un

codage uniforme et un ordonnanceur prioritaire de matériel qui entrelacent l'entraînement pendant les cycles d'inactivité d'inférence sans affecter la latence de la queue d'inférence. Dans l'ensemble, nous montrons que l'exposition des cycles d'inactivité des accélérateurs d'inférence aux services d'entraînement révèle une importante puissance de calcul pour des services d'entraînement avec une faible surcharge pour les accélérateurs d'inférence, ce qui améliore l'efficacité globale du centre de données.

**Mots clés :** centre de données, accélérateurs des réseaux neuronaux profonds, services en ligne, systolic array, représentation numérique, virgule flottante en bloc

## **Contents**

| Ac | knov    | vledgements                              | i    |

|----|---------|------------------------------------------|------|

| Ał | ostra   | ct                                       | v    |

| Li | st of ] | Figures                                  | xiii |

| Li | st of   | Tables                                   | xv   |

| 1  | Intr    | oduction                                 | 1    |

|    | 1.1     | Challenges in Piggybacking Training      | 2    |

|    | 1.2     | Thesis Goals                             | 3    |

|    | 1.3     | Thesis Contributions                     | 3    |

|    | 1.4     | Thesis Scope                             | 4    |

|    | 1.5     | Thesis Organization                      | 7    |

| 2  | Bac     | kground                                  | 9    |

|    | 2.1     | DNN Workloads                            | 9    |

|    | 2.2     | Physical Constraints in DNN Accelerators | 12   |

|    | 2.3     | DNN Inference Accelerator Design         | 15   |

|    | 2.4     | DNN Training Accelerator Design          | 17   |

| 3  | Hyb     | orid Block Floating Point                | 19   |

|    | 3.1     | Dot Products with BFP Arithmetic         | 21   |

|    | 3.2     | Requirements for Numeric Representation  | 22   |

|    |         | 3.2.1 Minimizing BFP Data Loss           | 24   |

#### **Contents**

|   | 3.3  | BFP Accuracy Analysis                           | 24 |

|---|------|-------------------------------------------------|----|

|   |      | 3.3.1 BFP Dot Product Accuracy                  | 25 |

|   |      | 3.3.2 BFP Sigmoid Derivative Accuracy           | 26 |

|   | 3.4  | Methodology                                     | 28 |

|   |      | 3.4.1 HBFP Simulation on GPU                    | 28 |

|   |      | 3.4.2 Evaluation Setup                          | 28 |

|   | 3.5  | Evaluation                                      | 30 |

|   |      | 3.5.1 HBFP Design Space                         | 30 |

|   |      | 3.5.2 HBFP vs. fp32                             | 31 |

|   | 3.6  | Chapter Summary                                 | 32 |

| 4 | Mod  | leling Accelerator Performance                  | 35 |

|   | 4.1  | Optimizing Latency Constrained DNN Accelerators | 36 |

|   | 4.2  | Analytical Models                               | 38 |

|   | 4.2  | Exploring the Design Space                      | 40 |

|   | 4.3  | Chapter Conclusion                              | 46 |

|   | 7,7  | Chapter Conclusion                              | 10 |

| 5 | The  | Equinox Family of Accelerators                  | 47 |

|   | 5.1  | Piggybacking on Inference                       | 48 |

|   | 5.2  | Accelerator Design                              | 50 |

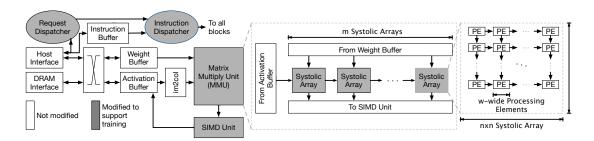

|   |      | 5.2.1 Baseline Inference Accelerator            | 50 |

|   |      | 5.2.2 Enhancements for Training                 | 53 |

|   | 5.3  | Chapter Conclusion                              | 56 |

| 6 | Eval | luating Equinox Accelerators                    | 57 |

|   | 6.1  | Methodology                                     | 57 |

|   |      | 6.1.1 Area and Power                            | 57 |

|   |      | 6.1.2 Simulation                                | 60 |

|   |      | 6.1.3 Equinox Configurations                    | 61 |

|   |      | 6.1.4 Workloads                                 | 61 |

|    | 6.2             | Evalu   | ation                                            | 62 |  |  |

|----|-----------------|---------|--------------------------------------------------|----|--|--|

|    |                 | 6.2.1   | hbfp8 vs. bfloat16                               | 62 |  |  |

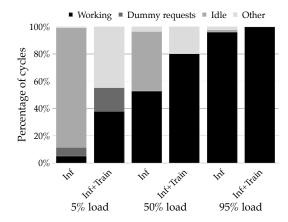

|    |                 | 6.2.2   | Equinox Cycle Breakdown                          | 63 |  |  |

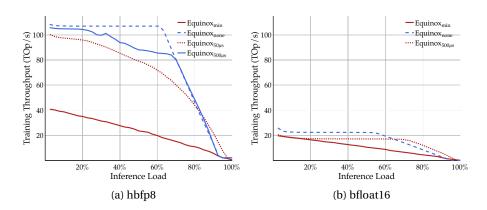

|    |                 | 6.2.3   | Training Throughput                              | 65 |  |  |

|    |                 | 6.2.4   | Workload Sensitivity Analysis                    | 65 |  |  |

|    |                 | 6.2.5   | Synthesis Results                                | 66 |  |  |

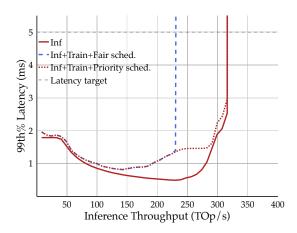

|    |                 | 6.2.6   | Scheduling                                       | 67 |  |  |

|    |                 | 6.2.7   | Adaptive Batching                                | 68 |  |  |

|    | 6.3             | Chap    | ter Conclusion                                   | 70 |  |  |

| _  | D 1             |         |                                                  | -1 |  |  |

| 7  | Keia            | ated wo | ork .                                            | 71 |  |  |

|    | 7.1             | DNN     | Numeric Representations                          | 71 |  |  |

|    |                 | 7.1.1   | Hybrid Accelerators                              | 71 |  |  |

|    |                 | 7.1.2   | Inference with Reduced Precision                 | 72 |  |  |

|    |                 | 7.1.3   | Training with End-to-end Low Precision           | 72 |  |  |

|    |                 | 7.1.4   | Binarized and Ternary Neural Networks            | 73 |  |  |

|    | 7.2             | DNN     | Accelerator Design                               | 74 |  |  |

|    |                 | 7.2.1   | Inference Accelerators                           | 74 |  |  |

|    |                 | 7.2.2   | Training Accelerators                            | 75 |  |  |

|    |                 | 7.2.3   | Data Movement in DNNs                            | 76 |  |  |

|    |                 | 7.2.4   | Scheduling Inference Services                    | 76 |  |  |

|    | 7.3             | Co-lo   | cation of Latency Critical and Best-effort Tasks | 77 |  |  |

| 8  | Con             | cludin  | ng Remarks                                       | 79 |  |  |

|    | 8.1             | Futur   | e Directions                                     | 81 |  |  |

|    |                 | 8.1.1   | Improving DNN Efficiency in Datacenter           | 81 |  |  |

|    |                 | 8.1.2   | Expanding the Scope of ColTraIn                  | 82 |  |  |

|    |                 |         |                                                  |    |  |  |

|    |                 |         |                                                  |    |  |  |

| Bi | Bibliography 85 |         |                                                  |    |  |  |

| 0 - | 4  |    | - 4 - |

|-----|----|----|-------|

| Co  | nı | eı | าธร   |

Curriculum Vitae 95

# **List of Figures**

| 2.1 | DNN operations                                                                     | 11 |

|-----|------------------------------------------------------------------------------------|----|

| 2.2 | Accelerators employing fine-grained ALU arrays                                     | 14 |

| 2.3 | Accelerators employing monolithic matrix multiplication units                      | 15 |

| 3.1 | Relative root mean square error (RRMSE) incurred by the use of BFP dot products,   |    |

|     | compared to single-precision floating point results                                | 27 |

| 3.2 | Relative root mean square error (RRMSE) incurred by the use of BFP sigmoid         |    |

|     | derivatives, compared to single-precision floating point results                   | 27 |

| 3.3 | HBFP design space for various mantissa widths. <i>hbfpX_Y</i> indicates an experi- |    |

|     | ment with With X-bit mantissas and Y-bit weight storage. All dot product opera-    |    |

|     | tions are performed with X-bit arithmetic                                          | 30 |

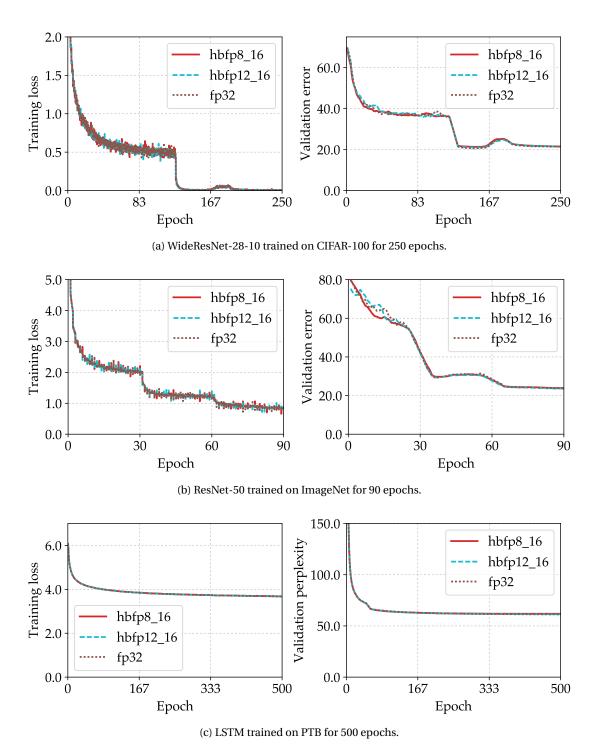

| 3.4 | Comparison between HBFP and FP32. <i>hbfpX_Y</i> indicates an experiment with      |    |

|     | with X-bit mantissas and Y-bit weight storage. All dot product operations are      |    |

|     | performed with X-bit arithmetic                                                    | 33 |

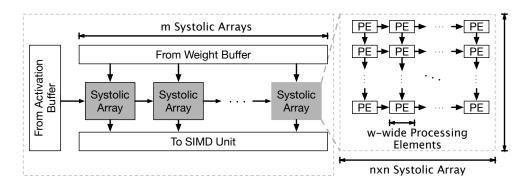

| 4.1 | Equinox matrix multiplication unit                                                 | 37 |

| 4.2 | Comparison between two ALU arrays both consuming roughly the same power.           |    |

|     | The array on the bottom trades off latency to improve throughput by requiring      |    |

|     | batching                                                                           | 37 |

| 4.3 | bfloat16 accelerator design space.                                                 | 44 |

| 4.4 | HBFP accelerator design space                                                      | 45 |

| 5.1 | Block diagram of Equinox                                                           | 50 |

|     |                                                                                    |    |

#### **List of Figures**

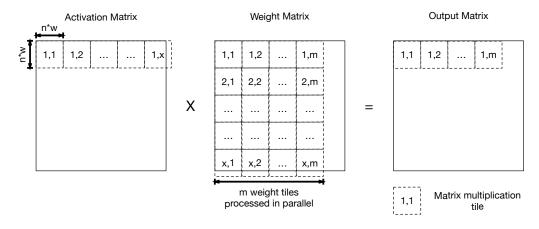

| 5.2 | Division of a matrix multiplication into tiles                                                                         | 51 |

|-----|------------------------------------------------------------------------------------------------------------------------|----|

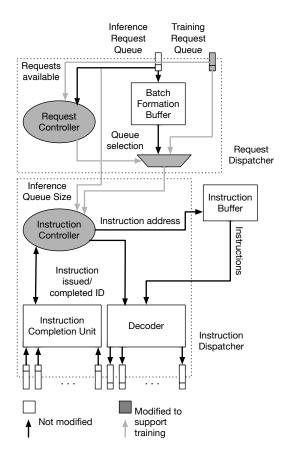

| 5.3 | Equinox two-level controller                                                                                           | 54 |

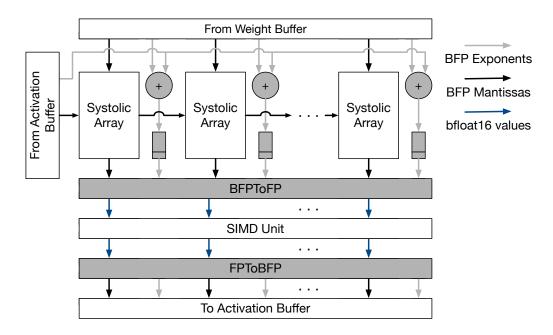

| 5.4 | Datapath modifications for HBFP                                                                                        | 55 |

|     |                                                                                                                        |    |

| 6.1 | Block diagram of Equinox's RTL model                                                                                   | 58 |

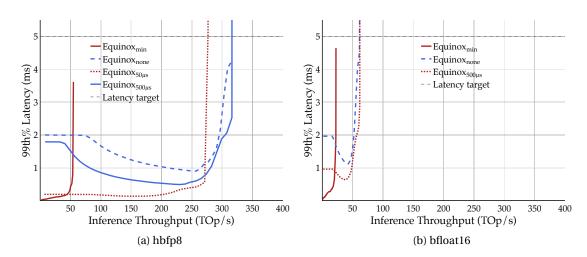

| 6.2 | Equinox inference tail latency as a function of its throughput                                                         | 63 |

| 6.3 | Cycle usage breakdown of $Equinox_{500\mu s}$ at various loads, with and without                                       |    |

|     | hosting training. $\mathit{Inf}$ indicates the accelerator hosts inference only, and $\mathit{Inf}$ + $\mathit{Train}$ |    |

|     | indicates that the accelerator hosts inference and training                                                            | 63 |

| 6.4 | Equinox training throughput as a function of the inference load                                                        | 64 |

| 6.5 | Equinox inference tail latency against its throughput. <i>Inf</i> indicates a configu-                                 |    |

|     | ration without training, Inf+Train+Fair sched. indicates a configuration with                                          |    |

|     | inference, training, and a fair-share scheduler, and Inf+Train+Priority sched.                                         |    |

|     | indicates inference, training, and a priority scheduler                                                                | 68 |

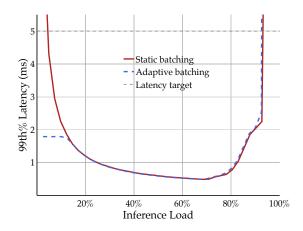

| 6.6 | Equinox's tail latency at various loads with static and adaptive batching policies.                                    | 69 |

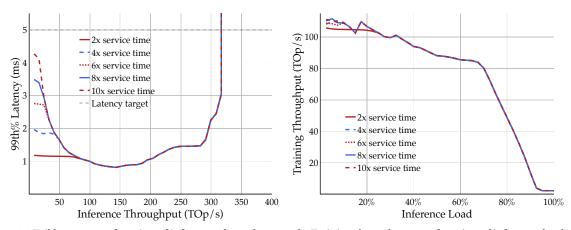

| 6.7 | Equinox's sensitivity to the adaptive batching threshold. " $X \times$ service time"                                   |    |

|     | indicates that the adaptive batching mechanism waits for $X \times$ the workload                                       |    |

|     | service time before issuing an incomplete batch.                                                                       | 69 |

## **List of Tables**

| 3.1 | Validation test error of ResNet-20 on CIFAR-10 as a function of the mantissa bit |    |

|-----|----------------------------------------------------------------------------------|----|

|     | width                                                                            | 20 |

| 3.2 | Validation test error of ResNet-20 on CIFAR-10 as a function of the exponent bit |    |

|     | width                                                                            | 20 |

| 3.3 | Test error of image classification models. RN, WRN and DN indicate ResNet,       |    |

|     | WideResNet and DenseNet, respectively. hbfpX_Y indicates an experiment           |    |

|     | with X-bit mantissas and Y-bit weight storage. All dot product operations are    |    |

|     | performed in X-bit arithmetic                                                    | 31 |

| 3.4 | Perplexity of language modeling models. <i>hbfpX_Y</i> indicates an experiment   |    |

|     | with X-bit mantissas and Y-bit weight storage. All dot product operations are    |    |

|     | performed in X-bit arithmetic                                                    | 31 |

| 4.1 | Maximum throughput for bfloat16 designs under various latency constraints        | 43 |

| 4.2 | Maximum throughput for HBFP designs under various latency constraints            | 46 |

| 5.1 | Accelerator ISA                                                                  | 51 |

| 6.1 | bfloat16 Equinox accelerators evaluated                                          | 61 |

| 6.2 | HBFP Equinox accelerators evaluated                                              | 61 |

| 6.3 | Training and inference performance for various DNN models. Training through-     |    |

|     | put is measured with an inference load of 60%. Inference throughput refers to    |    |

|     | the maximum throughput achieved while maintaining the service latency target.    | 66 |

| 6.4 | $Equinox_{500\mu s}$ area and power                                              | 67 |

## 1 Introduction

Deep neural network (DNN) infrastructure has observed an explosion in investment due to the large popularity of DNNs in online services [18, 27, 32]. Unfortunately, a significant fraction of this investment goes to waste, as custom inference accelerators face an average request load of around 30% because of service demand variability [3]. In general-purpose platforms, idle cycles are reclaimed by co-locating best-effort workloads with latency-critical ones [15]. As no other workload can execute on custom inference accelerators, those idle cycles stay unclaimed, leading to a considerable waste of resources.

Most attempts to reclaim inference accelerators' idle cycles involve using general-purpose platforms. Facebook uses CPUs for DNN inference, consolidating inference services with other best-effort workloads to improve utilization [27]. Microsoft employs FPGAs in their datacenters and leverages reconfiguration to reclaim FPGA idle cycles when load is low [5, 18]. Unfortunately, general-purpose platforms like CPUs and FPGAs are at least an order of magnitude less efficient than ASICs. As such, even when well utilized, general-purpose platforms still exhibit lower overall area and power efficiency for DNN services.

While DNN training workloads can be used as best-effort tasks to reclaim ASIC accelerators idle cycles, the divergence in inference and training workload requirements poses a significant challenge. On the one hand, inference accelerators execute algorithms that can tolerate

narrow fixed-point arithmetic and have small memory footprints. As such, these algorithms are served directly out of on-chip memory to achieve high throughput [18, 24]. Because of tight latency constraints, these accelerators avoid techniques that may delay individual requests, such as batching [18, 51]. On the other hand, training accelerators require floating-point arithmetic, exhibit memory footprints in the range of a few GBs [74], which cannot be easily accommodated on chip, and have no online latency constraints. As a result, training accelerators employ arithmetic logic units (ALUs) with reduced power efficiency, operate on DRAM-resident data, and use batching to minimize data movement and maximize throughput.

In this thesis, we design an inference accelerator that enables training services to piggyback on inference idle cycles without affecting inference latency and energy efficiency.

#### 1.1 Challenges in Piggybacking Training

There are several challenges related to designing an accelerator that piggybacks training services while maintaining inference's energy efficiency and arithmetic density. First, training algorithms require floating point arithmetic, which leads to accelerators with less dense and less efficient ALUs. Without a novel arithmetic representation for training, inference accelerators do not provide many opportunities for training services to achieve significant throughput when the load is low.

DNN accelerators also use batching to reduce data movement and improve energy efficiency. Unfortunately, batching also harms individual inference requests latency, with latency scaling as batch sizes increase. Although batch sizes are selected at compile time, the batch size that achieves the maximum energy efficiency is a property of the ALU array dimensions. As such, the ALU array dimensions define both the accelerator latency and throughput. If latency constraints are too tight, inference accelerators present low throughput, minimizing the opportunities for exposing idle cycles to training.

The final challenge is to maintain the inference service latency guarantees despite the resource sharing that occurs in inference accelerators, which also execute training services. This

challenge requires in-accelerator scheduling support to prioritize inference requests when load surges occur.

#### 1.2 Thesis Goals

This thesis aims to improve the energy efficiency of DNN accelerators by enabling the colocation of inference and training services. We do so by addressing the three showstoppers for piggybacking training on inference accelerators. First, we address the divergence between inference and training arithmetic. We aim to develop an arithmetic representation for DNN training that does not hurt accuracy or convergence rate, with ALU density and energy efficiency similar to representations used in inference accelerators. Second, we aim to find the ALU array dimensions that lead to efficient inference at low latency. Doing so enables us to find optimal designs that maximize the opportunities to expose idle cycles for training. Third, we aim to develop an in-accelerator scheduler that prioritizes latency-sensitive inference over best-effort training requests when needed. The scheduler must quickly identify and react to load surges. Finally, we aim to design an accelerator to show that piggybacking training on inference accelerators is feasible and more energy-efficient than using separate fabrics for DNN inference and training.

#### Thesis statement:

Exposing DNN inference accelerators' idle cycles to training uncovers vast computational resources for training at negligible overhead for inference services.

#### 1.3 Thesis Contributions

This thesis introduces the basic features of an inference accelerator that exposes idle cycles for training. We will refer to such an architecture as ColTraIn (Co-located DNN TRAining and Inference). We then introduce Equinox, a family of ColTraIn accelerators. Finally, we evaluate a few instances of Equinox.

First, we introduce the hybrid block floating point (HBFP) [16] DNN training framework, which maximizes the use of narrow fixed-point arithmetic while preserving convergence. We also introduce wide weight storage to HBFP, to improve HBFP's precision with modest area and memory bandwidth overhead. We explore the HBFP design space to show that DNNs trained on HBFP with 12- and 8-bit mantissas match FP32 accuracy, serving as a drop-in replacement for this representation.

Second, we study the design space of inference accelerator ALU arrays. We quantify the non-linear relationship between throughput and latency that appears in inference accelerators when batching is involved. We find out that latency-optimized designs exhibit low throughput while throughput-optimized designs exhibit high latency. We conclude that optimizing for one metric alone is not an effective approach. We show that designing ALU arrays with a specific latency goal leads to superior throughput and energy efficiency, maximizing the opportunities for training services to execute on inference accelerators.

Finally, we introduce the Equinox family of accelerators and evaluate a few instances of it. Equinox introduces multiple contexts to DNN accelerators to enable inference and training services to share resources and uses the same numeric representation for training and inference. Our evaluation shows that HBFP is an efficient numeric representation, with area and power consumption similar to fixed-point representations. We also show that the combination of HBFP, latency-constrained design, and in-accelerator scheduling leads to efficient ColTraIn accelerators, with throughput and latency similar to inference accelerators.

#### 1.4 Thesis Scope

In this thesis, we focus on systolic-array-based, single-node ColTraIn accelerators. This class of accelerators represents a significant fraction of the DNN accelerators' design space, including Brainwave [18] and TPU [32]. However, the DNN accelerator design space is much broader, featuring a wide variety of ALU arrays and distributed accelerator fabrics. While we do not evaluate the entire design space, the contributions of ColTraIn generally apply, with a few

caveats. In this section, we describe how each contribution of this thesis applies to the design space of ColTraIn accelerators.

First, the numeric representation we introduce, HBFP, is independent of ALU array organization, and it applies to both single node and distributed training. The only constraint imposed by HBFP is the physical separation between dot-products and other computations. Fortunately, most accelerators separate dot products from other operations [18, 32, 51] to improve energy efficiency.

HBFP is applicable to a wide variety of image and text processing models, as shown in the evaluation, with convergence rates similar to floating-point representations. While we cannot guarantee the same convergence rates on models that were not evaluated, we believe that it is applicable in general. As we show, all individual operations performed using HBFP have accuracy similar to single-precision floating point.

Our second contribution, the design space exploration of systolic-array-based accelerators, is not directly applicable to accelerators with other ALU array organizations. The conclusions of our study, however, are general. We show how batching affects throughput and latency in all models that employ vector-matrix multiplications. Our analysis also shows that batching effects are much stronger in accelerators with ALUs that are data movement bound. Even in accelerators like GPUs, which are fundamentally different from systolic arrays, larger batches mitigate data movement bottlenecks but negatively affect latency. Finally, models based on matrix-matrix multiplications, which are not the focus of this thesis, naturally exhibit weight reuse and are not affected as much by batching.

Our third contribution, Equinox, introduces a systolic-array-based inference accelerator capable of piggybacking training services. We introduce mechanisms and policies to share accelerator resources between inference and training services and to schedule operations for both services. The mechanisms introduced are specific to systolic-array-based accelerators, but the policies apply to a wide variety of accelerators. For instance, in NVIDIA GPUs, the policies introduced by Equinox can be implemented in the CTA and warp schedulers.

We evaluate Equinox on a single node setting for both inference and training, showing that it exposes variable throughput to training services, depending on the inference load. As such, in distributed training settings — where higher-level load balancers manage the nodes — Equinox introduces significant scheduling challenges. If load balancers cannot guarantee uniform load across all nodes, then training services observe irregular performance. For training services that employ synchronous distributed algorithms, the overall throughput is capped by the slowest node (i.e., the node in which inference load is highest). Training services can issue hedged or tied requests [13], collecting gradients from whichever nodes finish batch processing first to mitigate load imbalance issues while still providing synchronous guarantees to training services.

We observe that Equinox guarantees synchronous execution in multiple nodes, albeit at reduced throughput. Additionally, if training services tolerate asynchrony, then Equinox clusters are much more effective, as nodes make progress at their own pace. Our goal is not to match the throughput of optimized training accelerators but to exploit the idle cycles already present in inference services to perform training for free.

Finally, we argue that ColTraIn accelerators introduce an efficient way of exploiting inference services' idle cycles. The alternative approach — piggybacking inference on optimized training accelerators — complicates resource provisioning for several reasons. First, training accelerators aim to provide maximum throughput, employing ALU arrays that require large batches to achieve high utilization, negatively affecting latency. Second, training accelerators maximize DRAM and network bandwidth provisioning in detriment of ALU arrays. The introduction of inference services on training accelerators leads to DRAM and network resources' underutilization and introduces contention for ALU arrays. Finally, training services are best-effort, long-running services, without as much load variance as inference accelerators and without as many idle cycles. Without idle cycles, the introduction of inference services on training accelerators would force designers to increase accelerator fabric sizes to accommodate more services.

Nevertheless, the contributions of this thesis still apply to DNN training accelerators. The HBFP encoding improves training throughput by reducing data movement, power, and area of ALU arrays. The scheduling mechanisms introduced by Equinox also apply to training accelerators that piggyback inference services, as they too must prioritize inference services when load is high.

#### 1.5 Thesis Organization

This thesis is organized as follows. Chapter 2 provides background on DNN accelerator design, describing the design space and providing an in-depth explanation for the diversion between inference and training accelerators. Chapters 3, 4, 5, and 6 present the contributions of this thesis.

- Chapter 3 introduces the HBFP arithmetic encoding.

- Chapter 4 introduces our methodology to size ALU arrays for latency-constrained DNN accelerators, mapping the latency-throughput trade-off for inference accelerators.

- Chapters 5 and 6 introduce the design and implementation of Equinox, a family of ColTraIn accelerators.

Finally, we present related work in Chapter 7 and conclude the thesis in Chapter 8.

## 2 Background

DNN workloads are fundamentally different from traditional datacenter services for various reasons. First, DNNs must be trained before they are deployed for inference. Second, both DNN inference and training require algorithms that are computationally and data intensive. Third, DNNs have broad applicability, being used in services ranging from image analysis to text and speech processing. These requirements have forced datacenter operators to adopt accelerators for both inference and training. This chapter provides an overview of DNN workloads and the accelerators that execute them.

#### 2.1 DNN Workloads

DNN workloads are fundamentally different from traditional workloads due to their high computational demands and data intensity. For instance, a single Resnet50 [28] request requires around 4 billion instructions that process a model of around 100MB, requiring several orders of magnitude more data and computation than a single 128-byte memcached [40] request, which requires 175 thousand instructions. Additionally, DNNs can be applied to solve more problems than most other algorithms, both in datacenters and at the edge [27, 32], finding application in image processing, web search, text processing, speech processing, and more.

The broad applicability of DNNs leads to their application in a wide variety of computing systems. In the cloud, online services combine DNNs with traditional datacenter workloads to provide a customized experience for users [18, 27, 32]. The high volume of DNNs services has lead datacenter operators to adopt specialized accelerators that are designed to fit under traditional servers' power budgets [18, 27, 32]. These accelerators are part of traditional datacenter servers, usually not optimized to host DNN services, and are accessed through PCIe or network interfaces. As such, datacenter DNN services are subject to the same constraints of online services, often facing contention for resources [73]. In this thesis, we focus on datacenter accelerators due to their large scale and many opportunities for exposing inference idle cycles to training workloads.

DNNs are also executed on dedicated clusters designed with high per-server power budgets, often featuring several accelerator instances per server board [23, 22, 52]. These clusters often feature servers specialized for DNN services using high-performance networks. These clusters execute both latency-constrained and best-effort DNN services.

Finally, DNNs are also used at the edge [66], where they face tight power constraints, which lead to the use of efficient numeric representations, even if it affects accuracy. The biggest challenges of edge DNN services are the diversity of both the compute fabrics, where some nodes are equipped with DNN accelerators and others are not, and the workloads they execute. Additionally, the requirements of edge DNN services vary widely [44], from real-time (i.e., self-driving cars) to best-effort (i.e., training of face recognition models).

DNNs also differ from traditional workloads because they have to be trained before they are deployed for inference. While the development of traditional workloads requires relatively low computational resources, compared to their actual execution, DNN training is a computational and data-intensive process. DNNs' training algorithms often require millions of iterations [61, 74], which process large datasets. Additionally, DNN training involves exploring the design space, requiring the training of a large number of different variations of a particular model to reach optimized results. Although the training process has different requirements from DNN

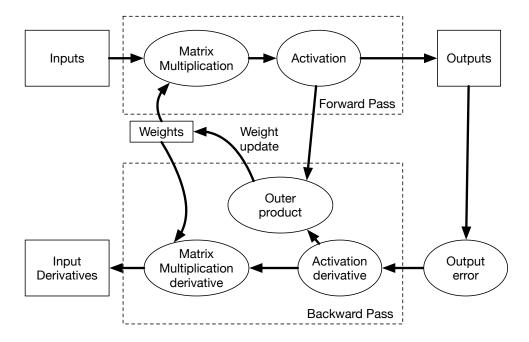

Figure 2.1 – DNN operations.

inference, it is composed of similar operations.

DNN workloads are composed of chains of large matrix operations, which dominate execution time, followed by large vectorial operations. Figure 2.1 shows the operations of a single layer DNN. Squares indicate inputs, outputs, and weights, while ellipses indicate operations. The arrows indicate the operands that flow between operations, also known as tensors. The top part of the figure shows a forward pass. First, groups of inputs are organized into tensors that are then multiplied by the weight matrix. The results then go through a non-linear activation function. For DNNs with multiple layers, this process is done multiple times. The bottom part of the figure shows the backward pass. It starts by computing the output error, which is then processed by derivatives of the activation functions to compute the activation derivatives. The activation derivatives are then fed to the matrix multiplication derivatives, which are sent to previous layers. Activation derivatives are also used to compute the weight updates.

One critical issue in performing the matrix operations present in DNNs is the high relative power consumption of moving data, compared to the power consumed by ALU operations. Accelerators have to exploit reuse in DNN processing to mitigate this issue. DNN services

are diverse, with different models leading to various matrix operations dimensions, with varying levels of reuse. Traditional multi-level perceptrons (MLP) models and recurrent neural networks like long short-term memory networks (LSTM) and gated recurrent unit networks (GRU) are based on vector-matrix multiplications. These models have a lot of inherent activation reuse, with each activation value reused up to a few thousand times [47], but no weight reuse. As such, datacenter operators are forced to batch requests together to increase reuse. Other models, like convolutional neural networks (CNN) [28] and Transformer-based [63] models, are based on matrix-matrix multiplications, offering a lot of activation and weight reuse, leading to more efficient accelerators. Additionally, the relative sizes of activation and weight matrices affect efficiency. In MLPs, RNNs, and Transformer-based models, most of the memory accesses are to model weights [74] while in CNNs, memory accesses are more equally divided between weights and activations [74].

#### 2.2 Physical Constraints in DNN Accelerators

The DNN workloads' high computational density leads to increased pressure on the accelerators' power and area envelopes. In this section, we describe how these constraints affect accelerator design. We first explain how the power constraints lead to data movement bound accelerators, and then we explain how the area constraints affect accelerator design.

The end of Dennard's Scaling led to power-constrained silicon devices [17], also affecting DNN accelerators. Accelerator ALUs, the high-throughput buffers that feed them, and off-chip memory interfaces consume most of the accelerator power [6, 24], limiting the maximum accelerator throughput. Additionally, ALUs and buffers interfaces are power dense [11, 24] and cannot be used to fully occupy dies. To cope with the power density, accelerator designers reduce the operating frequency and increase the number of ALUs, to exploit the parallelism inherent to DNN workloads.

The numeric representations used in accelerators' ALUs also affects their power efficiency. Compared to fixed point, floating-point representations cover a vast range of values but incur high area and power for hardware implementations. Floating point numbers are represented by a mantissa and an exponent, in contrast to fixed-point numbers represented only by a mantissa. As such, a number in floating point is represented by the form  $mantissa \times 2^{exponent}$ . The exponent dynamically adjusts the range of values represented by the mantissa. However, compared to fixed point, the addition of an exponent requires hardware implementations to employ complex circuitry to manage the exponents and to normalize mantissas.

Fixed point and narrow representations reduce the power and area spent per operation [11] by similar amounts, keeping the ALU power density constant. However, taking into account data movement power, efficient ALUs mitigate the power density issues. For instance, 8-bit fixed-point ALUs consume up to one order of magnitude less power and area than bfloat 16 ALUs. However, they reduce data movement power by  $2\times$ . Assuming that the buffer area remains the same, the power density of 8-bit ALUs and buffers that feed them is  $2\times$  lower than bfloat 16's.

Using efficient ALUs increases the fraction of power dedicated to data movement in accelerators. Floating-point ALUs consume more energy to perform operations than to access operands. However, as ALUs become more efficient, this trend changes. The energy required to access 8-bit operands from a 32kb SRAM is  $6.3 \times$  larger than the energy needed to perform an 8-bit fixed-point multiply and accumulate operation [11]. If data is accessed from an off-chip buffer, the difference is three orders of magnitude. As such, accelerators that do not exploit reuse spend a significant fraction of their power in data movement, limiting the power dedicated to ALUs and accelerator throughput.

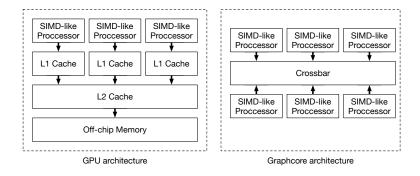

DNN accelerators exploit reuse in various ways. On the one hand, accelerators with many SIMD-like processors offer more flexibility in processing different matrix operations. These processors store data in register files and scratchpad memories for reuse. Unfortunately, this organization also incurs high synchronization and communication overheads. Traditional GPUs [50, 51], (left-hand side of Figure 2.2) are highly threaded, distributing threads across processors, which communicate through the memory system. Inter-thread communication is

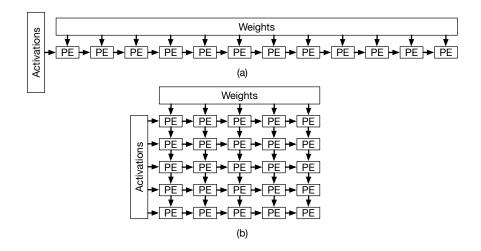

Figure 2.2 – Accelerators employing fine-grained ALU arrays.

often a bottleneck in GPUs [74]. Graphcore [24] (right-hand side of Figure 2.2) uses a similar architecture, but, instead of communicating through the memory system, the processors communicate directly through a large on-chip crossbar. Graphcore divides execution into super steps composed of computation and communication phases, with all processors turned off during the communication phase.

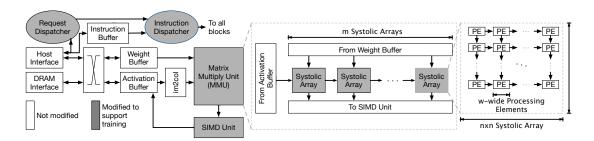

There are also accelerators with large monolithic matrix processing units, featuring ALU arrays connected through a network that is specialized to implement matrix operations. These units access shared on-chip buffers, which are often partitioned to improve their efficiency. Large monolithic units incur fewer communication overheads, because of the specialized network, but are less flexible in the operations they can implement. Microsoft's Brainwave [18] uses large SIMD units specialized for dot products connected through an accumulator tree, like the ones depicted on the left-hand side of Figure 2.3, while Google's TPU [32] uses systolic arrays like the ones pictured on the right-hand side of Figure 2.3. In this thesis, we focus on monolithic processing units due to their high efficiency. We also observe that they exhibit an explicit relationship between the ALU array dimensions and reuse, facilitating the exploration of the accelerator design space.

Area constraints affect DNN accelerators by limiting the number of ALUs and the amount of on-chip buffer available. As such, the slowdown in Moore's Law has reduced the opportunities for accelerators to exploit the vast parallelism in DNNs and to increase on-chip capacity. On-chip capacity is crucial on DNNs because on-chip buffers provide at least an order-of-

Figure 2.3 – Accelerators employing monolithic matrix multiplication units.

magnitude higher bandwidth than off-chip buffers [18, 24]. As such, if on-chip buffers are large enough to accommodate all the DNN service memory footprint, DNN accelerators can achieve superior throughput without relying so much on reuse.

#### 2.3 DNN Inference Accelerator Design

Inference accelerators are conventionally designed to maximize throughput while honoring tight latency requirements for online services. A salient characteristic of inference workloads is their tolerance to narrow fixed-point numeric encoding [18, 32]. Such an encoding results in up to an order of magnitude improvement in ALU silicon density (relative to floating point) [11], in memory capacity [18], and data movement bandwidth and power [61]. For example, Microsoft's Brainwave uses block floating point to process both LSTMs and CNNs [18], and TPUv1 uses 8- and 16-bit fixed point [32]. Using fixed-point-like representations allows both Brainwave and TPUv1 to achieve superior throughput and lower latency than the state of the art when introduced.

Another critical characteristic of inference workloads is their small memory footprint enabling designers to provision a more significant fraction of overall power for ALUs and higher throughput. In inference, the footprint is dominated by model weights, which are often small enough (a few KBs to 100s MBs [74]) to fit entirely on chip [18, 24] with off-chip memory

only present to accommodate the less frequent case of larger models (e.g., Brainwave [18], NVIDIA's T4 [51]). Consequently, data movement in inference accounts for a small fraction of the overall accelerator power budget. On-chip memory accesses consume little power (up to three orders of magnitude less, relative to off-chip accesses [11]). Both Graphcore [24] and Brainwave [18] are designs that exploit large on-chip memories with 10s-100s MBs worth of capacity for inference models.

While inference services lend themselves well to designs with high computational density, they are often online and have tight latency constraints. Inference services are usually part of multi-tiered services where a user query triggers a sequence of sub-query fan-outs, spanning hundreds or thousands of servers [8, 27]. That fan-out effect places tight bounds on the tail response latency of each tier [32, 55]. In DNN services, each tier is comprised of one or more accelerators. DNN accelerators lack all the sources of latency variance present in traditional servers, leaving only service time and queuing delays as sources of latency.

Inference's sensitivity to service-level tail latency creates a non-intuitive relationship between latency and throughput and a dilemma for designers. To increase effective throughput given a fixed power budget, designers rely on batching [18] to increase weight reuse, minimizing data movement bandwidth and power, thereby increasing the power provisioned for ALUs and throughput. At one end of the design space, when latency requirements are tight, lower degrees of batching result in a cap on the accelerator throughput because of the power provisioned to on-chip memory. At the other end, when latency requirements are lax with higher degrees of batching, the on-chip data movement power becomes negligible, freeing up power for ALUs and throughput.

Finally, inference services face low average loads, of around 30% [3], due to service demand variations. Traditional general-purpose servers use best-effort services to improve utilization when the online load is low [15, 39]. In general-purpose servers, the biggest challenge is the complex interactions between the various resources in CPUs, which causes best-effort services to interfere with online services in non-intuitive ways. In the case of DNN accelerators,

partitioning resources is trivial, as compilers can precisely calculate resource utilization. As such, the biggest challenge is that inference accelerators cannot execute other tasks when service load is low, leading to low utilization.

#### 2.4 DNN Training Accelerator Design

A fundamental difference between training and inference stems from the prominent algorithm, stochastic gradient descent (SGD), which poses several limitations on accelerator design. First, SGD requires floating point to converge, leading to ALUs with up to an order of magnitude more area and power consumption than the fixed-point ALUs used in inference services. SGD requires floating point because it operates on values with a wide range. SGD trains neural networks by computing the derivatives of a loss function, which represents how well the DNN performs, with regards to weights and activations. The weights and activation values are much larger than their derivatives, which are based on small differences between the results predicted by the network and the target results. Floating-point represents numbers with a mantissa and an exponent, with the exponent being used to adjust the representation range. Unfortunately, the exponent also introduces high area and power overheads, which affect overall ALU efficiency.

Prior work has attempted to train DNNs with fixed-point arithmetic [36, 64, 71], which represents numbers with a mantissa. While it has been shown that it is possible to achieve training convergence using fixed point, the limited range of fixed-point representations imposes algorithmic restrictions. These restrictions force algorithm designers to impose disruptive modifications to SGD, limiting its applicability and increasing the training process's complexity. The state-of-the-art in DNN training has evolved towards using narrower floating point representations (i.e., bfloat16 [14]), which are more efficient than single-precision floating point, but still less efficient than fixed point.

Second, SGD employs backpropagation, an algorithmic stage with long-term dependencies requiring a memory footprint in the order of up to a few GBs [74]. Such capacity can only be

fulfilled by off-chip DRAM, a memory technology that consumes at least an order of magnitude more energy per access than SRAM. The DRAM's high energy consumption limits the maximum bandwidth, forcing DNN accelerators to exploit more reuse from DNN workloads to achieve high throughput. Unfortunately, SGD also imposes a limitation on the maximum batch size used [38], limiting the maximum weight reuse on DNNs. Batch size limitations, in addition to DRAM's limited bandwidth, leads to accelerators with lower throughput compared to inference accelerators.

Training is often performed in a distributed fashion due to its high computational demands. In distributed training, each the DNN inputs or models are divided across many workers, which compute partial weight updates. Then, the partial weight updates are accumulated across workers, and the full updates are sent back to workers. Distributed training incurs high network bandwidth demands due to the exchange of weight updates.

# 3 Hybrid Block Floating Point

DNN training algorithms require floating point to converge, in contrast to inference, which tolerates fixed-point arithmetic without any accuracy loss [21]. The algorithmic tolerance to fixed-point arithmetic enables inference accelerators to use ALUs with up to an order of magnitude higher silicon density and energy efficiency than the ALUs used by training accelerators. In this chapter, we design an efficient arithmetic representation for training by exploiting dot product operations' properties, which dominate DNN processing.

Numeric representations have two key properties—precision and range—which affect training convergence in different ways. Precise numbers represent values with high resolution within a scale. For instance, an 8-bit fixed-point number can represent 256 values, while a 16-bit fixed-point can represent around 65 thousand values, leading to higher precision. Single-precision floating point numbers have a 24-bit mantissa and an 8-bit exponent, meaning that, for a given exponent, the floating point can represent almost 16 million values. DNNs are sensitive to numeric precision, but only up to a certain point. Table 3.1 shows the validation error obtained when training ResNet-20 [28] models on CIFAR10 [35] using floating point-multipliers with various mantissas and exponent widths. We observe convergence without loss of accuracy with 8-bit mantissas, convergence with a small loss of accuracy with 4-bit mantissas, and divergence only when using 2-bit mantissas. As such, the 24-bit mantissa used in single-precision floating point is overkill. For this reason, machine learning developers

Table 3.1 – Validation test error of ResNet-20 on CIFAR-10 as a function of the mantissa bit width.

Table 3.2 – Validation test error of ResNet-20 on CIFAR-10 as a function of the exponent bit width.

started using bfloat16 [14], which employs an 8-bit mantissa and an 8-bit exponent [23, 22].

DNNs are, however, sensitive to the range of numeric representations. As such, the exponent width cannot be reduced because of its impact over the numeric range. As Table 3.2 shows, validation accuracy decreases as we reduce the exponent width from 8 to 6 bits, and training diverges altogether when using 2-bit exponents. Additionally, the use of half-precision floating points, which use 5-bit exponents, affect training convergence [12]. This reliance on representation range prevents training algorithms from converging using fixed-point representations since they are the equivalent of a floating point with a 0-bit exponent.

While floating-point is a more appropriate representation for training due to its wide range, floating-point ALUs have low silicon density and energy efficiency compared to their fixed-point counterparts. The small silicon density and energy efficiency of single-precision floating point (fp32) has led developers to adopt half-precision floating point (fp16) and bfloat16 as the state-of-the-art in representations for accelerators. However, the logic overhead of lower precision floating-point representations is still high compared to that of fixed point. For instance, although the area of an fp16 multiplier is  $4.7\times$  smaller than that of an fp32 multiplier, it is still  $5.8\times$  larger than its 8-bit fixed-point counterpart [11], with similar trends for energy consumption. This significant overhead is due to the additional hardware necessary to manage the exponent and the mantissa alignment in floating-point representations.

Block floating point (BFP) is a compromise between fixed and floating point. Like floating point, BFP represents numbers with mantissas and exponent and therefore exhibits a wide

dynamic range. Unlike floating point, BFP shares a single exponent across a block of values. As such, within a block, BFP enforces a fixed-point-like range, but different blocks can have different exponents, leading to a wide range of representation. This property enables dot products to be computed with high precision but prevents arbitrary operations from being computed precisely. Additionally, BFP ALUs achieve higher silicon density and energy efficiency because they amortize the exponent management overhead over many values.

In this chapter, we show that using BFP for dot product operations and floating point for other operations leads to a training accelerator with silicon density and energy efficiency comparable to fixed-point accelerators and training convergence rate similar to floating-point accelerators.

## 3.1 Dot Products with BFP Arithmetic

Equation (3.1) computes the real value  $a_i$  of an element i of a BFP tensor a with mantissa  $m_i^a$  and exponent  $e_a$ .

$$a_i = m_i^a \times 2^{e_a} \tag{3.1}$$

In this example, BFP can only represent a accurately if the value distribution of a is not too wide to be captured by  $m^a$ , and the exponent  $e_a$  is representative of said value distribution. If  $e_a$  is too large, then small values are lost, and the most significant bits of the mantissas are wasted. If  $e_a$  is too small, then the larger values in a will be saturated, leading to data loss.

Equation (3.2) calculates the dot product between BFP tensors a and b, each with N elements.

$$a \cdot b = \sum_{i=1}^{N} \left( (m_i^a \times 2^{e_a}) \times (m_i^b \times 2^{e_b}) \right) = 2^{e_a + e_b} \times (m^a \cdot m^b)$$

(3.2)

The dot product  $m^a \cdot m^b$  is computed entirely in fixed-point arithmetic, without the alignment of intermediate values, since all elements  $m^a_i$  and  $m^b_i$  are fixed point. In a matrix multiplication  $A \times B$ , it is enough for A to have one exponent per row, and B to have one exponent per column. In DNNs, activations or activation derivatives would map to the A matrix, and weight

matrices would map to *B*. During training, input matrices are multiplied by both the weight matrix (during forward pass) and their transposed forms (in backpropagation). As such, using one exponent per column in weight matrices would lead to a dot product with a different exponent per weight value, which would degenerate to a floating-point-like dot product. We address this issue by using matrix tiles as BFP blocks. With tiled matrices, tile multiplications are performed using fixed point, and the resulting tiles are accumulated using floating-point arithmetic, requiring mantissa realignment.

## 3.2 Requirements for Numeric Representation

This section describes the challenges and opportunities presented by each operation in DNNs to the arithmetic representations. We start by explaining how different operations present different challenges for numeric representations, making a case for using different representations for different operations in DNN processing.

Dot products — the operations that dominate DNN processing — feature long reductions, which introduce error in hardware that uses floating-point. To calculate dot products, we first compute the element-wise product of the two input tensors, and then reduce the results. In floating-point additions, the mantissa's inputs are first aligned, to normalize their exponents. In this process, the value with the smallest exponent has its mantissas shifted to the right. If the exponent difference is too large, the mantissa of the smallest value can be partially or entirely lost, minimizing that value's contribution to the addition. Over the several additions that compose a reduction, this process is repeated, shifting away the smaller values' mantissa bits, leading to accuracy reduction. The convergence of DNN training with floating-point indicates that the training algorithm is robust enough to tolerate this loss of accuracy.

When narrow floating-point numbers are used, however, the loss of accuracy starts affecting DNN accuracy [42], forcing accelerators to employ mixed-precision arithmetic. These accelerators use narrow representations, like bfloat16 or half-precision floating point, for dot products inputs and single-precision floating point for accumulators. Single-precision floating

point accumulators are useful because of their 24-bit mantissas, which enable values with large differences between exponents to be aligned without loss of precision. However, the single-precision floating point adders used in these accelerators consume significant area and power.

We observe that block floating point (BFP) is a promising numeric representation for dot products because it behaves similarly to floating points. When blocks of values are converted to BFP, the largest value's exponent is used as the exponent of the entire block, and all the other values are aligned. As such, the smallest numbers of the block lose precision, like in floating-point reductions. Additionally, BFPs can implement precise floating-point dot products when accumulators are wide enough. Using wide accumulators in BFP dot products can be done at low overhead when compared to floating-point dot products because fixed-point adders have low area and power compared to fixed-point multipliers.

BFP, however, may negatively affect accuracy when blocks are large. Large blocks force more values to share exponents, requiring a larger number of numbers to fit into the fixed-point range imposed by the mantissa. While this is a problem in arbitrary operations, dot products do not suffer from this issue. When dot products are large, they exhibit an averaging effect, reducing the impact of small individual values over the result.

In activations and batch normalizations, larger input values may not dominate the outputs as they do in dot products. As such, the use of BFP might lead to loss of accuracy. BFP-based accelerators convert dot product results from their wide accumulators back to narrower mantissas by identifying the largest exponents in the block, aligning, and truncating all of the accumulators, reducing the precision of smaller values in the process. Some activation functions, however, may amplify smaller values, amplifying the accuracy reduction. Additionally, in the backward pass, the derivative of some activation functions have their active region around zero, meaning that only values around zero are propagated to the previous layers. Again, if only BFP is used, these values would be lost. Finally, using BFP in activations and batch normalizations have reduced benefits due to the extra logic used to manipulate and

align mantissas.

As such, we show in this chapter that using floating-point ALUs for activations and batch normalizations enables training convergence with minimal impact on energy efficiency. The overhead of using floating-point ALUs for arbitrary operations is small because each floating-point ALU is fed by a dot product unit featuring hundreds of multiply and accumulate (MAC) units. To draw an upper bound on the overhead of the floating-point ALUs, we assume that each floating-point ALU is  $10 \times$  larger than a fixed-point MAC unit and is fed by a dot product unit with 100 MACs, the overhead of the floating-point ALUs is 10%. We expect this number to be smaller, given that the average dot product unit in accelerators is wider than 100 MACs [18, 32].

## 3.2.1 Minimizing BFP Data Loss

To minimize data loss in model weights that last through the training process, we store weights with wider mantissas. All operations are executed using the original mantissa. Only weight updates use the wider mantissa. Therefore, we still reduce the memory bandwidth requirements for forward and backward passes, during which only the most significant bits of the weights are accessed. Weight updates are the only operations that access the least significant bits of the weight values.

# 3.3 BFP Accuracy Analysis

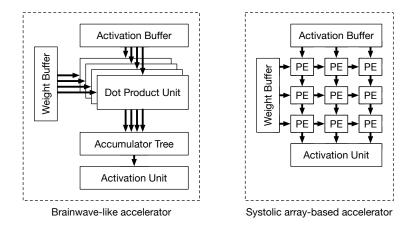

In this section, we show that BFP incurs low accuracy degradation for dot product operations but can incur high accuracy degradation for arbitrary operations. We do so by emulating BFP dot products and BFP sigmoid derivative operations on synthetic data while varying the key parameters of the design space: mantissa bit width, accumulator bit width (for dot products), block size, and range of input values.

We measure the relative root mean square error (RRMSE) between BFP and single-precision floating points. The RRMSE value indicates a ratio between the average error and the total

value of the floating-point baseline. As such, an RRMSE value of zero indicates that BFP and floating point are identical, and an RRMSE of 0.1 indicates that the error incurred by BFP is, on average, 10% of the floating-point value.

### 3.3.1 BFP Dot Product Accuracy

We evaluate the accuracy of BFP dot products by simulating fully connected layers. We compare the result of matrix multiplications of synthetic matrices, generated randomly using the distribution of values observed in original activation and weight matrices.

For each experiment, we varied one of the parameters that affect BFP accuracy. Unless otherwise stated, we use mantissa and accumulator bit widths of 8- and 24-bits, respectively. We multiplied weight and activation matrices with  $100 \times 100$  elements. Weight matrices have a normal distribution with zero average and a range of -4 to 4, while activation matrices have a range of -4 to 4. These value distributions were observed when training LSTMs with floating point.

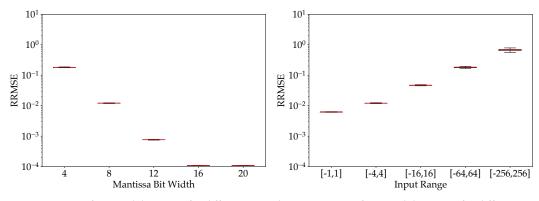

The mantissa bit width is the most important parameter of BFP, as it defines the precision and the range of values that can be represented within a tensor. Figure 3.1a shows the RRMSE incurred by BFP with various mantissa bit widths while keeping the other parameters constant. As expected, the Figure shows that the error exponentially decreases as we increase the bit width, settling down at 0.01%. As DNNs operate on noisy data, the error incurred by 8-bit BFP (around 2%) does not disturb the training process. For models more sensitive to arithmetic precision, 16-bit BFP introduces almost no error. Finally, we execute each experiment a thousand times and report the distribution of the RRMSE values in box plots.

The width of the accumulator used is also an important parameter of BFP dot products, defining accuracy. Figure 3.1b shows the RRMSE of BFP dot products with various accumulator bit widths. As the Figure shows, accumulators with less than 16-bits result in an unacceptable error. Dot product accumulators add values resulting from the multiplication of two mantissas. As such, accumulators store values that require twice the mantissa width to be represented,

incurring high error when accumulators are narrower than that. We observe little benefits as the accumulator width increases over twice the mantissa width.

We also evaluate the influence of input weight matrix range on BFP dot product accuracy, as Figure 3.1c shows. BFP dot products are very robust to input range variations due to the reduction step, which leads to large values dominating the sums. As such, we show that the precision of dot products is virtually the same independent of the range used. We also varied the range of the activations (not shown in the Figure), showing that dot products are insensitive to variations in the range of either operand.

Finally, we evaluate whether the size of the block used in BFP dot products affects the output accuracy. We do so by varying input matrices' sizes, as shown in Figure 3.1d. Precision slightly improves as we increase the matrix size, forcing larger matrices to share exponents. Smaller dot products result in more noisy results, which are amplified by BFP. As we increase the matrix sizes, the long reductions have an averaging effect on the results, reducing the noise.

### 3.3.2 BFP Sigmoid Derivative Accuracy

To show a case when BFP incurs high error, we evaluate the performance of BFP on the sigmoid derivatives, which appear on LSTM training. BFP reduces the accuracy of such operations because they amplify the inputs' small values, which are shifted away during conversions. We compare the result of activations applied to synthetic matrices generated randomly using the distribution of values observed in the original activations. Unless stated otherwise, all results use mantissa bit widths of 8-bits. We used activation matrices with  $100 \times 100$  elements. Activation matrices have a normal distribution with zero average and a range of -4 to 4. These value distributions were observed when training LSTMs using floating point.

We show that the mantissa width of BFP has a similar effect on sigmoid derivatives and matrix multiplications, as shown in Figure 3.2a. As expected, the Figure shows the same trends as in dot products, with error exponentially decreasing as we increase the bit width, settling down at 0.01%.

(c) BFP RRMSE of dot product for different input (d) BFP RRMSE of dot product for different tile sizes. ranges.

Figure 3.1 – Relative root mean square error (RRMSE) incurred by the use of BFP dot products, compared to single-precision floating point results.

(a) BFP RRMSE of sigmoid derivative for different BFP (b) BFP RRMSE of sigmoid derivative for different inmantissa widths. (b) BFP RRMSE of sigmoid derivative for different input ranges.

Figure 3.2 – Relative root mean square error (RRMSE) incurred by the use of BFP sigmoid derivatives, compared to single-precision floating point results.

Finally, we evaluate the effect of input range on BFP sigmoid derivatives. We show that error increases as the input range increases. The error increase is the main reason why BFPs are not suitable to process arbitrary operations. Although value ranges larger than [-4,4] are rare in the input matrices of derivative operations, they affect results significantly when they appear, disrupting the training process.

# 3.4 Methodology

### 3.4.1 HBFP Simulation on GPU

We train DNNs with the proposed HBFP approach, using BFP in the compute-intensive operations (matrix multiplications, convolutions, and their backward passes) and FP32 in the other operations. We simulate BFP dot products in GPUs by modifying PyTorch's [54] linear and convolution layers to reproduce the behavior of BFP matrix multipliers. We redefined PyTorch's convolution and linear modules using its *autograd.function* feature to create new modules that process the inputs and outputs of both the forward and backward passes to simulate BFP. In the forward pass, we convert the activations to BFP, giving the *x* tensor one exponent per training input. Then we execute the target operation in native floating-point arithmetic. In the backward pass, we perform the same pre-/post-processing of the inputs/outputs of the *x* derivative.

We handle the weights in the optimizer. We created a shell optimizer that takes the original optimizer, performs its update function in fp32, and converts the weights to two BFP formats: one with wide and another with narrow mantissas. The former is used in future weight updates while the latter is used in forward and backward passes.

### 3.4.2 Evaluation Setup

**Baseline.** We use models trained with single-precision floating point (fp32) as a baseline. fp32 is the most accurate representation used in DNN training. As such, showing that HBFP

presents accuracy comparable to fp32 also indicates that it is as or more accurate than other floating point alternatives, like half-precision floating point and bfloat16. Additionally, to make the case that HBFP is a drop-in replacement for fp32, we trained both HBFP and fp32 models with the same hyper-parameters.

**Datasets.** We experiment with a set of popular image classification tasks with the CIFAR-100 [35], SVHN [48], and ImageNet [59] datasets. We used standard data augmentation [28, 29] for CIFAR-100 and no augmentation for SVHN. We also evaluate LSTM language modeling tasks with the Penn Tree Bank(PTB) dataset [43]. Finally, we evaluate the BERT [20] language modeling model with the English Wikipedia dataset [65].

**Evaluation metrics.** To evaluate the impact of HBFP and explore the design space of different BFP implementations, we tune the models using fp32 and then train the same models from scratch with the same hyperparameters in HBFP. For the image classification experiments, we report training loss and validation top-1 error. For the language modeling models, we report training loss and validation perplexity.

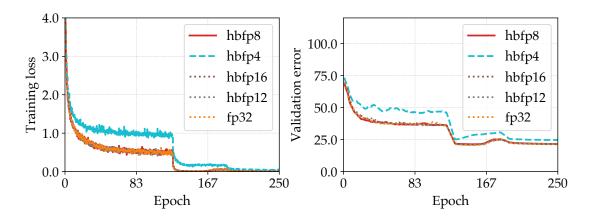

**Training.** We use a WideResNet [69] trained on CIFAR-100 to explore the BFP design space, evaluating models trained with various mantissa widths. To show that HBFP is a viable alternative to FP32, we train a wide range of models using various datasets. We train ResNet [28], WideResNet [69], and DenseNet [30] models on the CIFAR-100 and SVHN datasets; a ResNet model on ImageNet and the LSTM from [41] on PTB. We also trained BERT-Tiny from [20]. We trained all models using the same hyperparameters reported in their respective original papers.

**BFP configuration.** Both the BFP emulation framework and our prototype use accumulators large enough to accommodate the results of the dot products without saturation. For instance, for a 32-wide BFP dot product with 8-bit mantissas, we use 21-bit accumulators. We found out that the overhead of the wide accumulators is small.

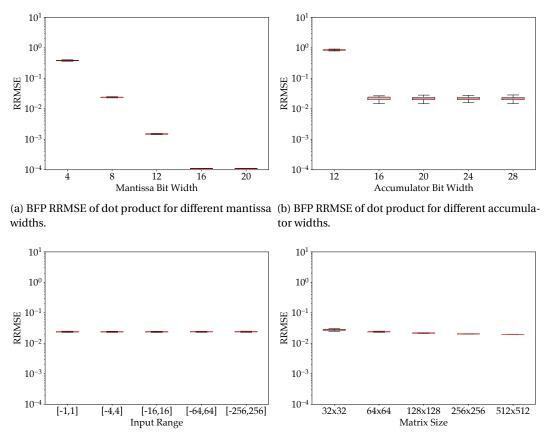

Figure 3.3 – HBFP design space for various mantissa widths. *hbfpX\_Y* indicates an experiment with X-bit mantissas and Y-bit weight storage. All dot product operations are performed with X-bit arithmetic.

## 3.5 Evaluation

We now evaluate DNN training with HBFP. We explore the design space of HBFP, varying the mantissa width to find the best-performing configurations. Then, we move on to evaluate HBFP on various datasets and tasks, to show that HBFP is indeed a drop-in replacement for fp32.

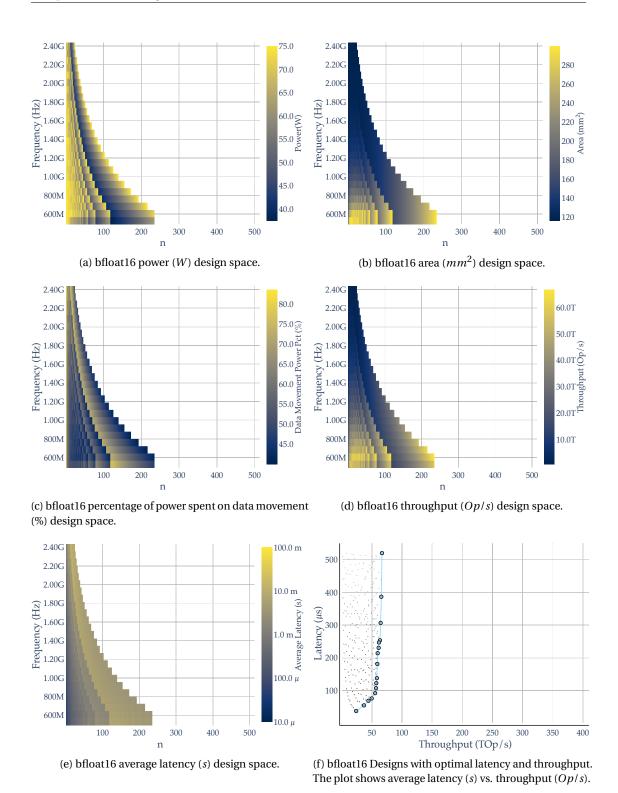

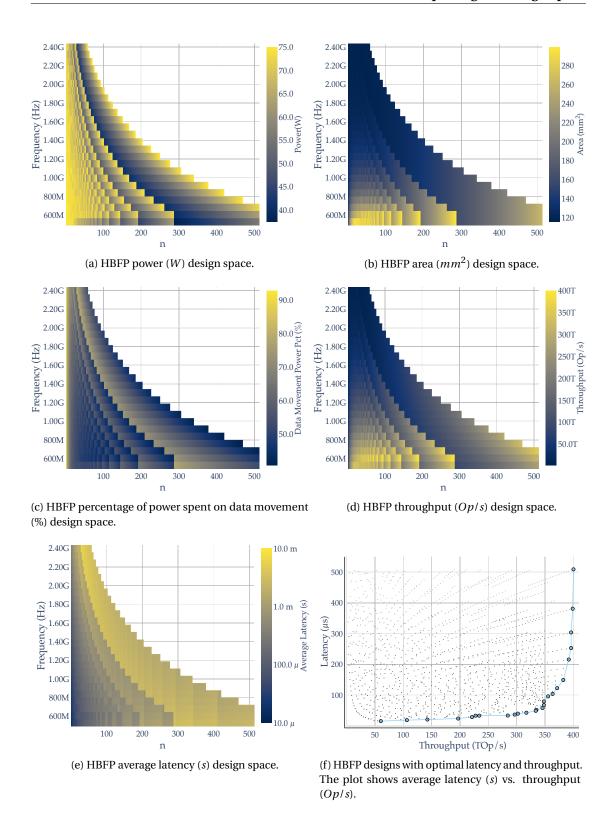

## 3.5.1 HBFP Design Space