# High-Current Low-Voltage Power Supply for Superconducting Magnets

Présentée le 25 septembre 2020

à la Faculté des sciences et techniques de l'ingénieur Laboratoire d'électronique de puissance Programme doctoral en énergie

pour l'obtention du grade de Docteur ès Sciences

par

## Émilien Luc Henri COULINGE

Acceptée sur proposition du jury

Dr S.-R. Cherkaoui, président du jury Prof. D. Dujic, S. Pittet, directeurs de thèse

Dr K. Papastergiou, rapporteur

Prof. P. Grbovic, rapporteur

Prof. A. Rufer, rapporteur

École Polytechnique Fédérale de Lausanne Power Electronics Laboratory Station 11 1015 Lausanne, Switzerland

https://www.epfl.ch/labs/pel

© 2020 by Emilien Coulinge

## **Abstract**

In the wide range of applications for power supplies, the ones dedicated to feeding superconducting magnets occupy a niche. This particular kind of magnets has the intrinsic property of having zero resistance, and is only used in high-end facilities for fundamental research or medical application to produce large magnetic fields. This implies that powering superconducting magnets requires a very high current combined with a low voltage only due to the interface between the power supply and the superconducting circuit.

The case study developed in this thesis is based on European Organization for Nuclear Research (CERN) High Luminosity LHC (HL-LHC) project where an upgrade of the present Large Hadron Collider (LHC) installations needs to be developed. The objective is to increase the overall performances of the collider, targeting to augment the experimental data sets by one order of magnitude compared to the present one. To achieve this goal, a stronger magnetic field is needed to enhance the collision rate of particles by having a thinner particle beam, thus directly impacting the power supply ratings and driving many design choices for the power supply.

This thesis is divided into two parts where at first a global system level approach is adopted, the definition of the operational requirements and the constraints related to high-current low-voltage power supplies in the context of CERN environment are detailed. As the new powering scheme of the dedicated *Inner-Triplet magnets* imposes a 2-quadrant operation of the supply, there is a need to locally integrate an energy storage solution in the supply to recover the magnetic energy when de-energizing the magnet. The integration of such storage element impacts the complete power flow of the power supply, as well as the sizing of the various stages of power conversion. To this extent a study of the best location of the storage within the supply is conducted and gives the basis for the power converters sizing. Additionally, a complete overview of the selected storage technologies is conducted, where supercapacitors and batteries are compared. The overall layout and suitable storage technologies are highlighted regarding the design of this new 2-quadrant high-current low-voltage power supply for superconducting magnets.

The second part focuses on the power stage which processes the high current, the DC/DC output stage. By nature, because of the high level of current, the strict precision and the extended lifetime required for the power supply are such that a modular design is mandatory. Considering the case of a 18 kA nominal current output rating, an in-depth study of an optimized novel 2-quadrant high-current low-voltage DC/DC building block is presented. It is achieved through a multi-objective optimization that includes the core elements of the topology as well as the defined optimal modulation pattern. Volume and efficiency are considered as the main criteria during this process, the best compromise between those two is considered as the optimal solution. An elementary building block rated for  $250 \, \text{A}$ ,  $\pm 10 \, \text{V}$  is selected, where eight paralleled blocks are composing a *sub-converter*, and nine of those *sub-converters* in parallel allow to reach the nominal current requirement. The overall control strategy and experimental performances are demonstrated at a small scale, paving the way to a viable full-scale demonstrator that could effectively be used in a new generation of power supplies for superconducting magnet at CERN.

Keywords high-current, low-voltage, DC/DC power supply, energy storage, multi-objectives optimization, prototype, experimental results

### Résumé

Dans la large gamme d'applications des alimentations électriques, celles dédiées à l'alimentation des aimants supraconducteurs occupent un marché de niche. Ce type particulier d'aimant a la propriété intrinsèque d'avoir une résistance nulle, et n'est utilisé que dans des installations de pointe pour la recherche fondamentale ou dans le domaine médical afin de produire des champs magnétiques imporants. Cela implique que l'alimentation des aimants supraconducteurs doit fournir un courant très élevé combiné à une tension très basse uniquement due à l'interface entre l'alimentation et le circuit supraconducteur.

L'étude développée dans cette thèse est basée sur le projet HL-LHC de l'Organisation Européenne pour la Recherche Nucléaire (CERN) où une mise à niveau des installations actuelles du Grand collisionneur de hadrons (LHC) doit être étudiée. L'objectif est d'améliorer les performances globales du collisionneur, en visant à augmenter d'un ordre de grandeur les données récoltées par les expériences. Pour atteindre cet objectif, un champ magnétique plus puissant est nécessaire afin d'améliorer le nombre de collision des particules, en ayant un faisceau de particules plus fin, ce qui a un impact direct sur la puissance nominale de l'alimentation électrique et détermine de nombreux choix de conception de l'alimentation électrique.

Cette thèse est divisée en deux parties où, dans un premier temps, une approche globale au niveau système est adoptée, la définition des besoins opérationnels et les contraintes liées aux alimentations électriques à courant élevé et basse tension dans le contexte de l'environnement CERN sont détaillées. Comme la nouvelle stratégie d'alimentation des aimants *Inner-Triplet* impose un fonctionnement à 2-quadrants de l'alimentation, il est nécessaire d'intégrer une solution de stockage d'énergie local dans l'alimentation pour récupérer l'énergie magnétique lors de la désexcitation de l'aliment. L'intégration d'un tel élément de stockage a une incidence sur le flux de puissance complet de l'alimentation, ainsi que sur le dimensionnement des différents étages de la conversion de puissance. Dans cette mesure, une étude de l'emplacement le plus approprié pour l'élément de stockage est menée et donne la base du dimensionnement des convertisseurs de puissance. En outre, une vue d'ensemble complète des technologies de stockage sélectionnées est réalisée, où les supercondensateurs et les batteries sont comparés. L'agencement global et les technologies de stockage appropriées sont mis en évidence en ce qui concerne la conception de cette nouvelle alimentation électrique à courant élevé et basse tension fonctionnant en 2-quadrants pour les aimants supraconducteurs.

La deuxième partie se concentre sur l'étage de puissance qui traite le courant élevé, l'étage de sortie DC/DC. Par sa nature, en raison du niveau élevé de courant, la précision stricte et la durée de vie prolongée requises pour l'alimentation électrique sont telles qu'une conception modulaire est obligatoire. Dans le cas d'un courant nominal de sortie de 18 kA, une étude approfondie d'un nouveau bloc élémentaire d'électronique de puissance optimisé pour le fonctionnement 2-quadrants à courant élevé et basse tension est présentée. Elle est réalisée grâce à une optimisation multi-objectifs qui comprend les éléments fondamentaux de la topologie ainsi qu'un modèle de modulation optimal. Le volume et l'efficacité sont considérés comme les principaux critères au cours de ce processus, le meilleur compromis entre ces deux facteurs étant considéré comme la solution optimale. Un bloc de construction élémentaire conçu pour 250 A, ±10 V est sélectionné, où huit blocs en parallèle composent un sous-convertisseur, et neuf de ces sous-convertisseurs en parallèle permettent d'atteindre le courant nominal requis. La stratégie de contrôle globale et les performances expérimentales sont démontrées à échelle réduite, ouvrant la voie à un démonstrateur grandeur nature viable qui pourrait être utilisé efficacement dans une nouvelle génération d'alimentations pour aimant supraconducteur au CERN.

**Mots-clés** courant élevé, basse tension, alimentation électrique DC/DC, stockage d'énergie, optimisation multi-objectifs, prototype, résultats expérimentaux

# Zusammenfassung

Netzgeräte werden heutzutage überall gebraucht und eingesetzt, wenn es jedoch um die Versorgung von supraleitenden Magneten geht, so besetzen Diese nur eine Nische. Eine Besonderheit solcher Magneten ist, dass sie keinen elektrischen Wiederstand aufweisen, und werden nur in Spitzeneinrichtungen für fundamentale Forschung und in medizinischen Anwendungen eingesetzt um ein starkes Magnetfeld zu erzeugen. Dies bedeutet, dass das verbundene Netzgerät in der Lage sein muss sehr hohe Ströme bei sehr niedriger Spannung zu erzeugen wegen der Schnittstelle zwischen dem Netzgerät und dem supraleitenden Stromkreis.

Die Fallstudie, welche in dieser Doktorarbeit entwickelt wurde, basiert auf dem CERN HL-LHC Projekt wo eine Verbesserung von der aktuellen LHC Einrichtung entwickelt werden sollte. Das Ziel ist die insgesamte Leistung des Teilchenbeschleunigers zu erhöhen und dabei gezielt die experimentellen Datensätze um eine Größenordnung im Vergleich zu den bestehenden Datensätzen zu erweitern. Um das gesetzte Ziel zu erreichen wird ein stärkeres Magnetfeld, welches die Kollisionsrate der Teilchen durch einen dünneren Teilchenstrahl verbessert, benötigt. Dies beeinflusst die Nennwerte der Netzgeräte als auch viele andere dies bezogene Designwahlen.

Die Doktorarbeit ist in zwei Teile aufgeteilt. Im ersten Teil wurde eine globale Herangehensweise auf der Systemebene angenommen, zusätzlich wurden die Betriebsanforderungen und die Beschränkungen bezüglich Hochstrom- und Niederspannungsnetzteil im Rahmen von der CERN Umgebung näher definiert. Da das neue Antriebsschema für die zugehörigen *Inner-Triplet Magneten* Zwei-Quadranten-Operation des Speisegeräts verlangt, ist es notwendig einen Energiespeicher lokal in das Netzgerät einzufügen. Dadurch kann die magnetische Energie, die durch Entmagnetisierung der Magnete entsteht, zurückzugewonnen werden. Die Integration eines solchen Speicherelements beeinflusst nicht nur den ganzen Leistungsfluss des Netzgerätes, sondern auch die Dimensionierung von bestimmten Stufen der Energieumwandlung. Diesbezüglich wurde eine Studie durchgeführt, um die beste Plazierung des Energiespeichers innerhalb vom Netzgerät zu bestimmen, womit eine Grundlage für die Dimensionierung des Leistungswandlers gewonnen wird. Darüber hinaus wurde eine umfassende Übersicht über die ausgewählten Speichertechnologien geschaffen, in der die Superkondensatoren und die Batterien miteinander verglichen wurden. Schließlich wurden das Gesamt-Layout und die passenden Speichertechnologien für das Designs des neuen Zwei-Quadranten-Hochstromund Niederspannungsnetzteil für supraleitenden Magneten hervorgehoben.

Der zweite Teil beschäftigt sich mit der Leistungsendstufe, d.h. mit der Ausgangsstufe vom DC/DC Netzgerät, die den Hochstrom verarbeitet. Da von Natur aus, wegen des hohen Stromwertes, strikte Genauigkeit und verlängerte Laufzeit des Netzgerätes erforderlich sind, ist ein modulares Design Pflicht. Unter Berücksichtigung von 18 kA Ausgansstromnennwert wurde eine gründliche Studie über den optimierten und neuartigen Zwei-Quadranten-DC/DC Baustein mit Hochstrom und Niederspannung dargestellt. Mithilfe mehrkriterieller Optimierung, wurden die Hauptelemente der Topologie sowie das optimale Modulationsmuster bestimmt. Dabei wurden Volumen und Effizienz im Optimierungsprozess als Hauptkriterien berücksichtigt und der Kompromiss zwischen den beiden wurde als die optimale Lösung beachtet. Der grundlegende Baustein mit Nennwerten von 250 A und  $\pm 10 \, \mathrm{V}$  wurde ausgewählt und dabei setzten acht parallele Bausteine den sogenannten Sub-Wandler zusammen. Zusätzlich ermöglichen neun parallel geschaltete Sub-Wandler den Stromnennwert zu erreichen. Die gesamte Regelungsstrategie und die experimentellen Ergebnisse wurden im Kleinformat demonstriert, was im Endeffekt die Errichtung eines umsetzbaren maßstäblichen Prototyps ermöglicht, der bei CERN als neue Generation von Netzgeräten für supraleitenden Magneten verwendet werden könnte.

$\textbf{Schl\"{u}sselw\"{o}rter:} \ Hochstrom, Niederspannung, DC/DC\ Netzger\"{a}t, Energiespeicher, Pareto-Optimierung, Prototyp, Versuchsergebnisse$

# Acknowledgements

Electricity is power

John Roderick <sup>1</sup>

First and foremost, I would like to express my deepest gratitude to Prof. Drazen Dujic, for giving me the opportunity to start this project four years ago and guiding me through the years to its successful completion. I am grateful for openness and transparency in his approach, and leadership that has inspired me not only through the PhD work but also with cycling. He shared his passion and taught me to pace myself through this ride and reach the end with no cramps.

I am also delighted to have been able to grow with the Power Electronics Laboratory (PEL) from the very early days, and I am very proud of what it became and where it is heading to. On this journey, I have met exceptional individuals whom I would like to acknowledge - Alex, Anja, Chengmin, Cristina, Dragan, Felix, Fran, Gabriele, Ignacio, Jakub, Maria, Marko, Marko, Milan, Min, Miodrag, Nicolai, Nikolina, Pedro, Philippe, Seongil, Stefan, Uzair, Xiatong, Yan-Kim, all the trainees, students and academic visitors who were part of the lab for shorter time - it has been an honour sharing our academic and research journeys and you have each in your own way made the lab a superb environment to work in. I would like to especially acknowledge Roland Wetter and our super-efficient secretary Nathalie whose hard work every day meant that the lab run as smoothly as possible.

I would like to express my gratitude to the HL-LHC project who supported the thesis research.

This project meant that the CERN Electrical Power Converters (EPC) group was my other *home* and lab. Special thanks to Jean-Paul Burnet for getting me on board and supervising the first years with tact, before handing over the supervision to Dr. Serge Pittet whose precise guidance was always there when I needed it. My days there were shared with the brilliant minds and I would like to acknowledge and thank here: Andy, Charles, Fran, Gerry, Ivan, Jonathan, Lorenz, Louis, Luis, Lukas, Markus, Mathieu, Panos, Sebastian, Stefano, Tom, Zoi.

I am very thankful to the examination committee whose flexibility during the times of the lock-down meant that I could still defend my thesis. Prof. Petar Grbovic, Dr. Kostantinos Papastergiou and Prof. Alfred Rufer who took on the evaluation of the work and whose valuable feedback and guidance helped me improve the quality and clarity of my thesis. I would like to offer special thanks to the committee president, Dr. Rachid Cherkaoui. The meticulous proofreading award goes to Philippe.

I would like to acknowledge those that have helped me balance the work of the past four years with some fun: Annie, Irina, John, Julien, Nik, Pascal, Romain, Sabina, Silvia, Tatiana, Tony, Tere, Valentin and the Photomotivated group. Thank you all for the priceless laughter and unforgettable moments.

Last but not least, I would like to thank my family for their unconditional love and support without which this work would not have been possible. My brother, Jérémy, who has always been there for me, my mom Nathalie and dad Philippe – there are no words to express my love and gratitude for them. As for the rest of my supportive family, I'd like to thank you all for your ongoing encouragement despite the fact that for most of you the specifics of my job remained a mystery. This thesis is for you.

To the colleagues who have become friends, to the friends who have become family - Merci à vous.

Coppet, April 2020 *Emilien*

<sup>&</sup>lt;sup>1</sup>Roderick on the Line, Ep. 340: Scared and Stupid

# **List of Abbreviations**

B2B Board-to-Board

CCM Continuous Conduction Mode

CERN European Organization for Nuclear Research

DCCT DC Current Transformer

EMC Electromagnetic Compatibility ESR Equivalent Series Resistance

HL-LHC High Luminosity LHC

IEC International Electrotechnical Commission

IMS Insulated Metal Substrate

IPOP Input Parallel Output Parallel

LFP Lithium Ferrophosphate

LHC Large Hadron Collider

LTO Lithium-Titanate

MEG Multi-port Energy Gateway MRI Magnetic Resonance Imaging

PCB Printed Circuit Board PSU Power Supply Unit

PWM Pulse-Width Modulation

RMS Root Mean Square

SCL SuperConducting Link

SoC State-of-Charge

SR Synchronous Rectification

# **Contents**

| A۱ | bstra | ct       |                                  | i   |

|----|-------|----------|----------------------------------|-----|

| R  | ésum  | é        |                                  | iii |

| Zι | ısam  | menfa    | assung                           | v   |

| A  | cknov | wledge   | ements                           | vii |

| Li | st of | Abbre    | viations                         | ix  |

| 1  | Intr  | oducti   | ion                              | 1   |

|    | 1.1   | Back     | ground and Motivation            | 2   |

|    | 1.2   | Scope    | e and Objectives of the Thesis   | 5   |

|    | 1.3   | Struc    | ture of the Thesis               | 6   |

|    | 1.4   | List o   | of Publications                  | 6   |

| 2  | Stat  | e of th  | ne Art                           | 9   |

|    | 2.1   | State    | of the Art                       | 9   |

|    |       | 2.1.1    | Welding                          | 10  |

|    |       | 2.1.2    | Aluminum Smelter                 | 10  |

|    |       | 2.1.3    | •                                | 11  |

|    |       | 2.1.4    | •                                | 11  |

|    | 2.2   | Existi   | ing Technologies at CERN         | 12  |

|    |       | 2.2.1    | 1-Quadrant Power Supply Family   | 14  |

|    |       | 2.2.2    |                                  | 15  |

|    |       | 2.2.3    |                                  | 16  |

|    |       | 2.2.4    |                                  | 16  |

|    |       | 2.2.5    | 11 /                             | 17  |

|    |       | 2.2.6    |                                  | 17  |

|    | 2.3   | Sumn     | nary                             | 18  |

| 3  | Ene   | ergy Sto | orage Integration                | 19  |

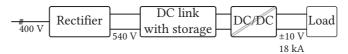

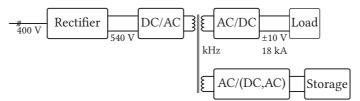

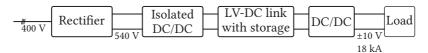

|    | 3.1   | Powe     | er Supply Concept                | 19  |

|    |       | 3.1.1    | Operational Cycle                | 19  |

|    |       | 3.1.2    | Requirements                     | 21  |

|    |       | 3.1.3    | Power Flow Strategy              | 22  |

|    | 3.2   | Energ    | gy Recovery                      | 22  |

|    |       | 3.2.1    | Feeding Energy Back to the Grid  | 22  |

|    |       | 3.2.2    | Storing and Reusing Energy       | 23  |

|    |       | 3.2.3    | Connection of the Energy Storage | 24  |

|    |       | 3.2.4    | Adopted Structure                | 26  |

|    | 3.3   | •        | gy Storage Technology            | 26  |

|    |       | 3.3.1    | Supercapacitors                  | 27  |

|    |       | 222      | Batteries                        | 21  |

|   | 3.4 | Conclusions                                                    | 36 |

|---|-----|----------------------------------------------------------------|----|

| 4 | DC/ | DC Stage Design Optimization                                   | 39 |

|   | 4.1 | DC/DC Output Stage                                             | 39 |

|   |     | 4.1.1 Modularity                                               | 40 |

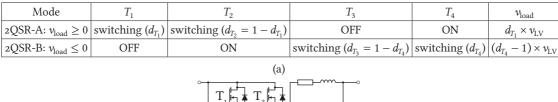

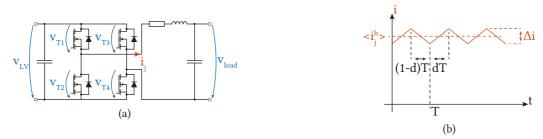

|   |     | 4.1.2 Branch Topology                                          | 41 |

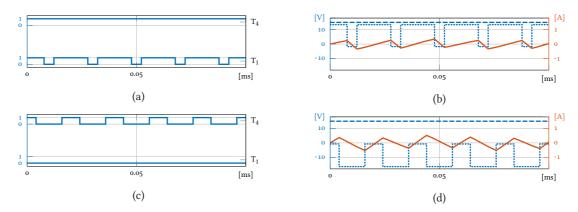

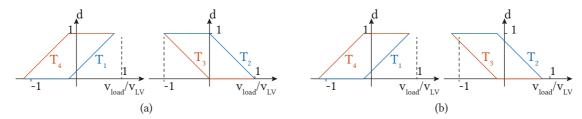

|   | 4.2 | 2-Quadrant Operation                                           | 42 |

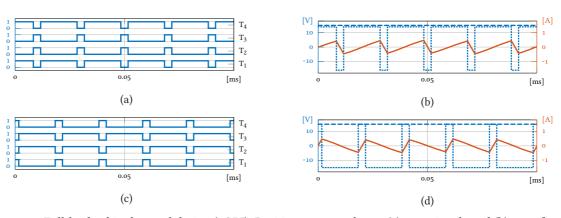

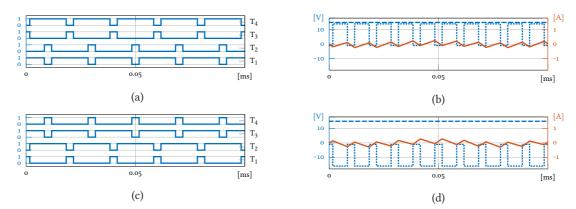

|   |     | 4.2.1 Modes of Operation                                       | 42 |

|   |     | 4.2.2 Mathematical Model                                       | 43 |

|   |     | 4.2.3 Summary 2-Quadrant                                       | 45 |

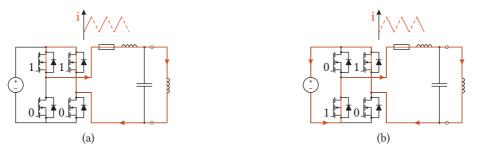

|   | 4.3 | 2-Quadrant Operation with Synchronous Rectification            | 46 |

|   |     | 4.3.1 Negative Output Voltage - Alternative Mode               | 47 |

|   |     | 4.3.2 Summary 2-Quadrant with Synchronous Rectification (SR)   | 48 |

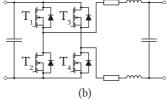

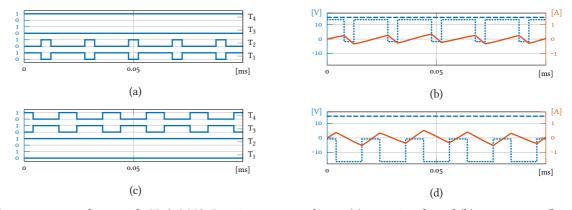

|   | 4.4 | 4-Quadrant Full-Bridge                                         | 48 |

|   |     | 4.4.1 Summary 4-Quadrant                                       | 50 |

|   | 4.5 | Operating Modes Comparison                                     | 50 |

|   |     | 4.5.1 Voltage and Current Stresses                             | 50 |

|   | 4.6 | Power Losses                                                   | 51 |

|   |     | 4.6.1 Conduction Losses                                        | 52 |

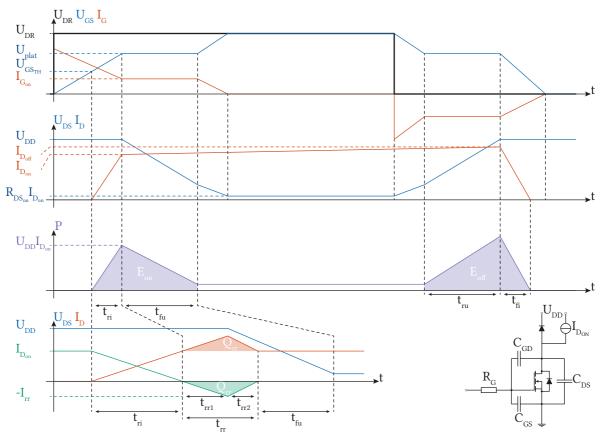

|   |     | 4.6.2 Switching Losses                                         | 53 |

|   |     | 4.6.3 Semiconductors Parameters Extraction from the Data-Sheet | 56 |

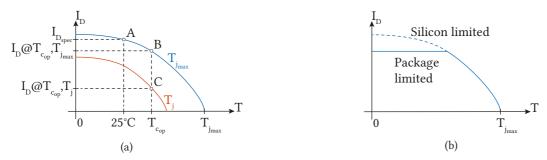

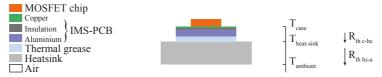

|   |     | 4.6.4 Junction Temperature                                     | 59 |

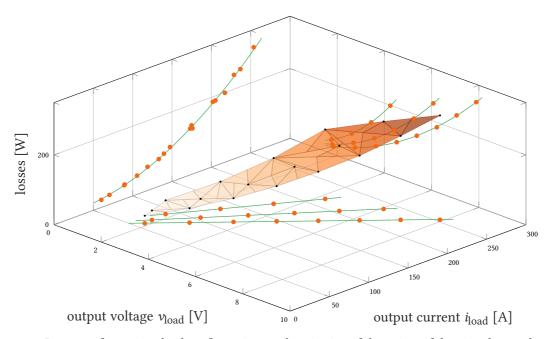

|   | 4.7 | Losses Comparison                                              | 59 |

|   | 4.8 | Conclusions                                                    | 62 |

| 5 | Bra | nch Optimization                                               | 63 |

|   | 5.1 | Sub-Converter Characteristics                                  | 63 |

|   |     | 5.1.1 Requirements                                             | 63 |

|   |     | 5.1.2 Modularity                                               | 64 |

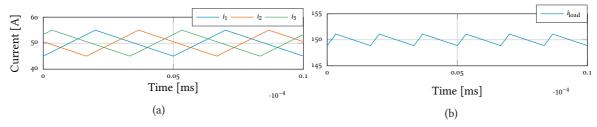

|   |     | 5.1.3 Interleaving                                             | 65 |

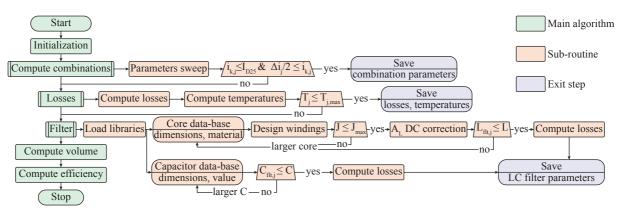

|   | 5.2 | Design Process                                                 | 66 |

|   |     | 5.2.1 Inputs                                                   | 67 |

|   |     | 5.2.2 Compute Combinations                                     | 69 |

|   |     | 5.2.3 Losses                                                   | 70 |

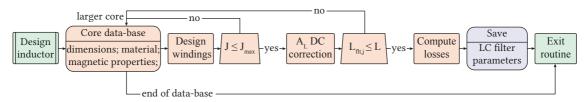

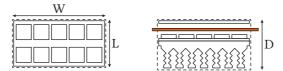

|   |     | 5.2.4 Filter Design                                            | 72 |

|   |     | 5.2.5 Mechanical Considerations                                | 76 |

|   |     | 5.2.6 Valid Designs                                            | 77 |

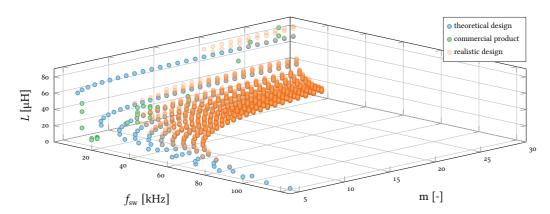

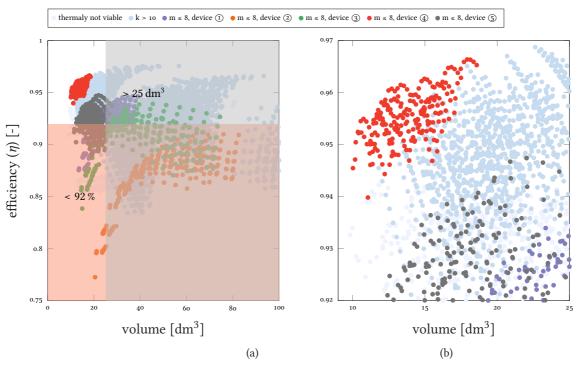

|   | 5.3 | Optimization Results                                           | 78 |

|   |     | 5.3.1 Operating Mode                                           | 78 |

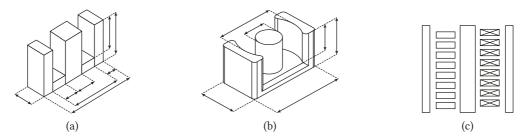

|   |     | 5.3.2 Powder EQ Cores                                          | 78 |

|   |     | 5.3.3 Powder EE Cores                                          | 78 |

|   |     | 5.3.4 Design Trends                                            | 79 |

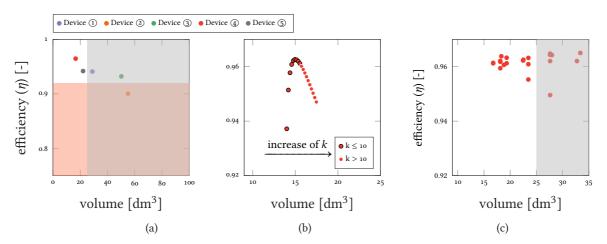

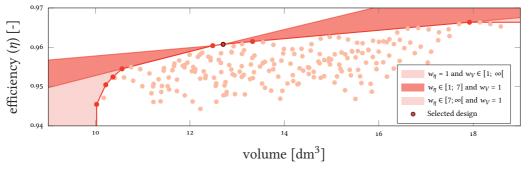

|   | 5.4 | Selected Design                                                | 81 |

|   |     | 5.4.1 Figure of Merit                                          | 81 |

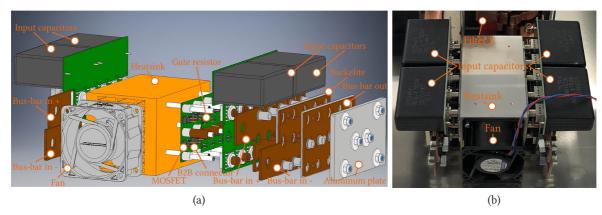

|   |     | 5.4.2 Branch Design                                            | 82 |

|   |     | 5 4 2 Full-Bridge Switching Cell                               | 82 |

|    |      | 5.4.4 Filter Characteristics                             | 82  |

|----|------|----------------------------------------------------------|-----|

|    |      | 5.4.5 Overall Losses and Volume                          | 84  |

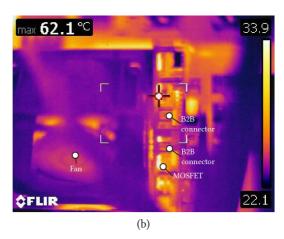

|    |      | 5.4.6 Branch Driver                                      | 84  |

|    | 5.5  | Experimental Results                                     | 86  |

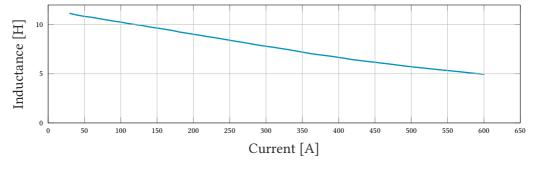

|    |      | 5.5.1 Filter Inductor                                    | 86  |

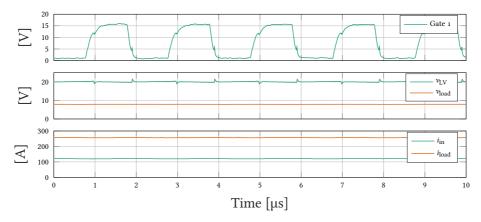

|    |      | 5.5.2 Static Tests in Open-Loop                          | 86  |

|    |      | 5.5.3 Dynamic Tests in Open-Loop                         | 89  |

|    | 5.6  | Conclusions                                              | 89  |

| 6  | Sub  | -Converter Interleaving and Control                      | 91  |

|    | 6.1  | Control Objectives                                       | 91  |

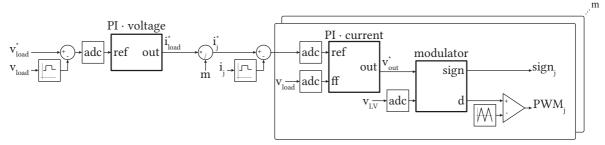

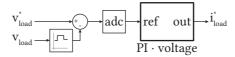

|    |      | 6.1.1 Control Scheme                                     | 91  |

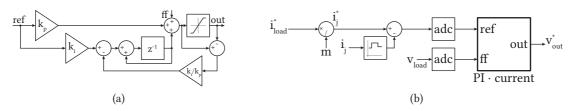

|    |      | 6.1.2 Inner Control Loop                                 | 93  |

|    |      | 6.1.3 Outer Control Loop                                 | 93  |

|    | 6.2  | Implementation in Simulation                             | 94  |

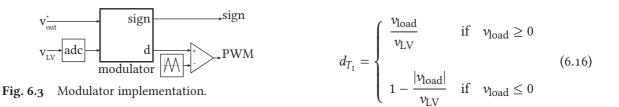

|    |      | 6.2.1 Modulator                                          | 94  |

|    |      | 6.2.2 PI Current Controller                              | 95  |

|    |      | 6.2.3 PI Voltage Controller                              | 96  |

|    | 6.3  | Sensitivity Analysis of the Parasitics on the Duty-Cycle | 98  |

|    |      | 6.3.1 Positive Output Mode                               | 98  |

|    |      | 6.3.2 Negative Output Mode                               | 99  |

|    | 6.4  | Interleaving of Branches                                 | 101 |

|    | 6.5  | Closed-Loop Operation                                    | 102 |

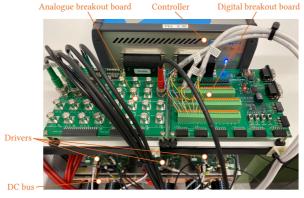

|    |      | 6.5.1 Control Platform                                   | 102 |

|    |      | 6.5.2 Regulation Loop                                    | 103 |

|    | 6.6  | Experimental Results                                     | 103 |

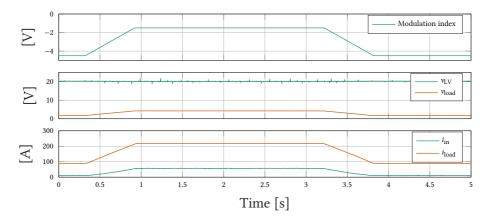

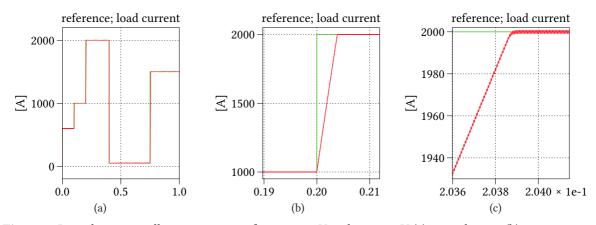

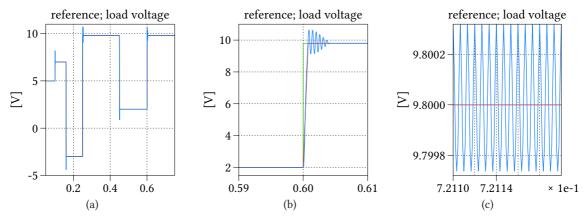

|    |      | 6.6.1 Reference Tracking                                 | 103 |

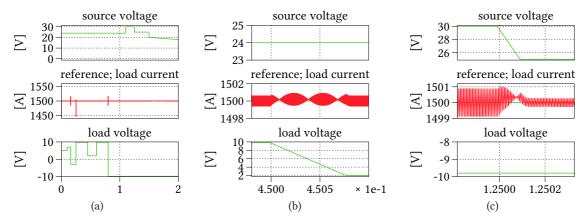

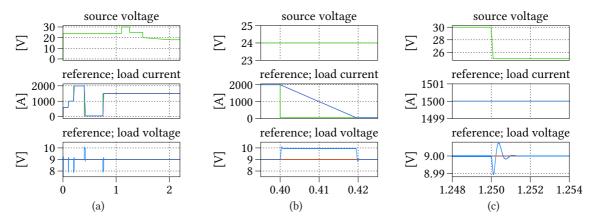

|    |      | 6.6.2 DC Link Disturbance                                | 105 |

|    | 6.7  | Conclusions                                              | 105 |

| 7  | Con  | nclusions and Future Works                               | 107 |

|    | 7.1  | Summary and Contributions                                | 107 |

|    | 7.2  | Overall Conclusion                                       | 108 |

|    | 7.3  | Future Work                                              | 109 |

| Aı | pend | dices                                                    | 111 |

| A  | App  | pendix                                                   | 113 |

|    | A.1  | Inductive Power of <b>Chap. 3</b>                        | 113 |

|    | A.2  | Branch Optimization of <b>Chap. 5</b>                    | 115 |

|    |      | A.2.1 Devices List                                       | 115 |

|    |      | A.2.2 Devices Package                                    | 116 |

|    |      | A.2.3 Early Prototype                                    | 116 |

|    |      |                                                          |     |

# 1 Introduction

A magnet is an object or material that produces a magnetic field. From its early discovery, several centuries before Christ, the lodestone (naturally magnetized piece of the mineral magnetite) were find to attract iron, and started fascinating people. It took a few millennium to learn and understand what was first thought to be magical power, in making a practical use of it in navigation systems with the compass. It is not before Hans Christian Ørsted (1777-1851) that the link between electric current and magnetic field was discovered [1], [2]. Eventually James Clerk Maxwell (1831-1879) was the one to formulate the equations governing electromagnetism in 'A Dynamical Theory of the Electromagnetic Field' [3], bringing together the concepts of electricity, magnetism and light.

History retains William Sturgeon to be the person who built the first electromagnet in 1824 [4]. His prototype consisted of an iron core wrapped in 18 turns of bare copper wire supplied by a single-cell battery, a scheme of his assembly is depicted in Fig. 1.1(a). The concept of electromagnet evolved from this time forth until reaching the ferromagnetic limit of 1.6 T. This limit has been overpassed with the development of superconducting magnets (c.f. Fig. 1.1(b)) [5]–[7], where the current can flow in the conductors with no resistance. Their main use is for Magnetic Resonance Imaging (MRI) [8] or particle accelerators [9]. The improvement of such magnets goes together with the development of adequate power supplies [10], which is the topic of this thesis. The power supply allows to regulate, very precisely, the current flowing through the magnet, thus enables to control the generated magnetic field. In the specific case of particle accelerator facilities, dedicated power supplies [11]–[13] are nowadays the interface between the power grid and all the different electromagnets.

**Fig. 1.1** Evolution of electromagnets: (a) first electromagnet prototype by Sturgeon (1824)¹ and (b) model of a particle accelerator (LHC) superconducting dipole magnet (1994)².

<sup>&</sup>lt;sup>1</sup> 'Improved Electro Magnetic Apparatus' Transaction of the Royal Society of Arts Manufactures and Commerce, Volume 43, Plate 3, Figure 13.

<sup>&</sup>lt;sup>2</sup>CERN image library: CERN-AC-9402027.

#### 1.1 Background and Motivation

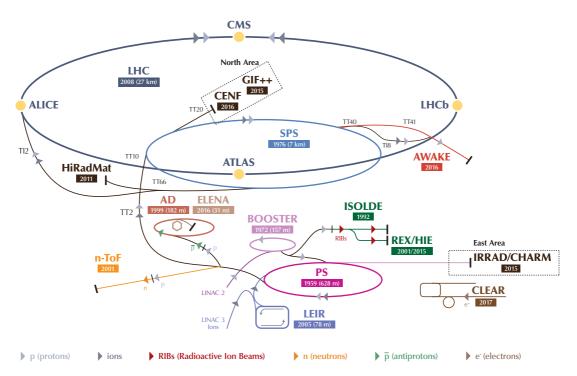

European Organization for Nuclear Research (CERN) is a European research organization whose focus is particle physics. In order to do so, it operates a complex of particle accelerators as depicted in **Fig. 1.2**. In these installations, the magnets are to the particles beams what lenses are to the optical beams. In other words, the beam of particles can be shaped by the magnetic field in its trajectory, its configuration (focus, defocus, polarization) and other properties depending on the nature of its particles, thanks to various configurations of electromagnets. The Large Hadron Collider (LHC) [14], [15] is the largest and the most powerful particle accelerator, not only in CERN, but in the world. The level of energy at which operates the LHC requires the use of superconducting magnets to produce a field over 8 T, when powered by a current of 11 kA [14, Chapter 10].

To power those superconducting magnets, a variety of specialized power supplies have been developed. Their main characteristics is to provide a large current under a reduced voltage thanks to the zero resistance of the superconducting magnets themselves, usually several kilo amperes with a voltage below 200 V [16]. At CERN, the installed base for LHC has a total of 1700 different power supplies which deliver a total of  $1.7 \times 10^6$  A [17] for a proper operation of the system.

LHC - Large Hadron Collider // SPS - Super Proton Synchrotron // PS - Proton Synchrotron // AD - Antiproton Decelerator // CLEAR - CERN Linear Electron Accelerator for Research // AWAKE - Advanced WAKefield Experiment // ISOLDE - Isotope Separator OnLine // REX/HIE - Radioactive EXperiment/High Intensity and Energy ISOLDE // LEIR - Low Energy Ion Ring // LINAC - LINear ACcelerator // n-ToF - Neutrons Time Of Flight // HiRadMat - High-Radiation to Materials // CHARM - Cern High energy AcceleRator Mixed field facility // IRRAD - proton IRRADiation facility // GIF++ - Gamma Irradiation Facility // CENF - CErn Neutrino platForm

**Fig. 1.2** The CERN accelerator complex as of August 2018<sup>3</sup>. Nature of the particles and name of the experiment are also given, where LHC is the particle accelerator of interest for the thesis project.

<sup>&</sup>lt;sup>3</sup>CERN image library: OPEN-PHO-ACCEL-2018-005.

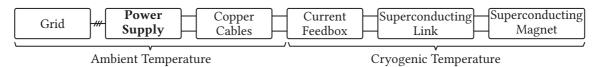

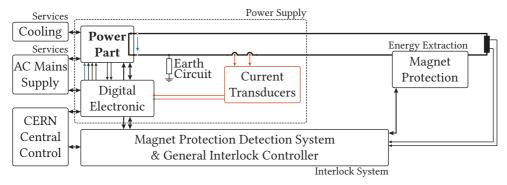

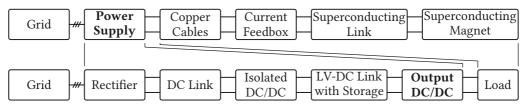

Fig. 1.3 Overall structure of the interface between the electrical grid and a superconducting magnet.

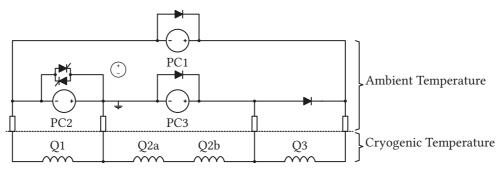

As the connection to superconducting materials cannot be made at the power supply level, there is a need for copper cables to transmit the power to the current feedbox [18], [19], which is the interface from the normal to the superconducting world. The overall structure of this interface between a superconducting magnet and the electrical grid is given in **Fig. 1.3**. On the scheme, ambient temperature is the one of the environment in which the power supply is installed, the cryogenic temperature is 1.9 K. The position of the current feedbox influences the ratings of the power supply: its voltage is imposed by the length and properties of the copper cables to the feedbox, whereas the current ratings are governed by the superconducting magnets needs.

As of 2013, the High Luminosity LHC (HL-LHC) project [20]—[22] was launched as an upgrade of the actual LHC in order to increase its performances by a factor of five at the horizon of the year 2026. One of the main change in this upgrade is the powering structure of several magnets, including the specific ones called *Inner-Triplet magnets*, which are the ones of interest for the work presented in this thesis. Those *Inner-Triplet magnets* are a series of superconducting magnets, consisting of three quadrupole optical elements and four magnets. They provide the final focusing of the particle beam right before the four interaction points (CMS, LHCb, ATLAS and ALICE in **Fig. 1.2**) along the LHC ring. In total, it is eight of such magnets that are present in the collider, each of them being powered by a dedicated power supply.

The HL-LHC upgrade focuses particularly on ATLAS and CMS interaction regions *Inner-Triplet magnets* because of their critical role in the performance of the collider. They are improved to produce a stronger magnetic field, integrating a novel superconducting material, and fed with a state of the art SuperConducting Link (SCL), also using the superconducting technology. The improved physical layout of the elements, even if in the same structure as the one depicted in **Fig. 1.3**, will greatly affect the ratings of the power supply as the energy dissipation in the transmission line between the power supply and the magnet becomes negligible [23].

To be more concrete, some numbers are gathered in this paragraph regarding the CERN energy consumption for the year 2018 [24]. During that year, the CERN overall consumption was 1 251 GWh, where LHC represents 53 % of the total. In the LHC share (664 GWh), 42 % are dedicated to the cryogenics, required to provided the low temperature of the system (1.9 K) that is necessary to obtain the superconducting behavior of the magnets. Only a reduced share of the LHC consumption (5 %) is due to magnets and their power supplies. Nevertheless, it still represents 31 GWh over one year. In the actual trend of making good use of the resources at our disposal, it is legitimate to use the energy wisely in taking advantage of the cycling operation of the particle accelerator: recovering the energy of an ending cycle to reuse it for the upcoming one. The energy integration options are analyzed in order to keep a low footprint of the power supply on the electrical utility grid.

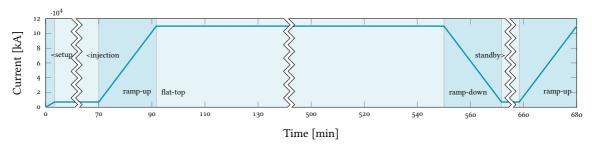

As the LHC is a circular collider relying on superconducting magnets, its operation is based on a cycle of several hours, being repeated once or twice per day depending on the operational conditions. An overview of a typical LHC cycle is given in **Fig. 1.4** [25]–[27], representing the current feeding the main dipoles through time, this is the typical reference profile that all the other magnets follow.

**Fig. 1.4** Typical cycling profile of the LHC (simplified). The y-axis is the current feeding the main dipole magnets, reference of the whole facility.

In the simplified profile presented in Fig. 1.4, typical phases can be identified as follow.

- *Setup* is when no beam in is present the accelerator ring.

- *Injection* is a constant reduced current phase, a few hundred amperes, the beam of particle is established in the LHC. The length of this operation depends on the filling scheme of the particle accelerator [28], it usually lasts for 70 min.

- *Ramp-up* start once the initialization phase is completed. It is verified that a stable circulating beam is ready to be taken to higher intensities needed for physics. All the systems are then ramping gradually towards their nominal point of operation. This phase is 20 min long.

- *Flat-top* is when physics is happening and systems are running at their nominal operation point, this phase can be up to 15 h long if no problem occurs.

- *Ramp-down* happens once the system is decided to be ramped down or a fault occurs, it consists in de-energizing all the systems in order to return to a the setup or injection mode of operation. There are no more particles in the accelerator during this phase which lasts 22 min.

- *Standby* is the phase between two runs. During regular operation, it is desired to be as short as possible in order to maximize operational time for physics, which is the flat-top phase.

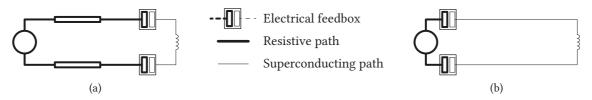

The HL-LHC will rely on the heritage passed by LHC and adopt the same modes of operation, as the upgrade is mostly focused on hardware. Nevertheless, a new requirement on the ramp-down time is adopted, in order to reduce it to 20 min. The addition of this operational constraint and the modification in the powering layout makes the actual *Inner-Triplet magnets* power supplies obsolete. A simplified depiction of the powering layout is given in **Fig. 1.5**. Commissioned in the early 2000's, the actual power supplies are relying on the resistivity of the copper cables (cf. **Fig. 1.5(a)**) to dissipate the energy stored in the magnets, limiting their operation to 1-quadrant only.

**Fig. 1.5** Simplified powering scheme of the *Inner-Triplet magnets*: (a) current one in the LHC with long copper cables and (b) future one in the HL-LHC with feedbox next to the converter and superconducting link.

The upgraded version is drastically reducing the length of the copper cables (cf. Fig. 1.5(b)), lowering the output voltage rating of the power supply and forcing the need for the application of a negative voltage across the load in order to ramp-down the current.

Taking those requirements into consideration makes the development of modern high-current low-voltage power supplies necessary. Thanks to the new powering layout jointly with the cycling operation of the system, some attention can be focus on the energy recovery of the system in order to optimize the use of the energy at the power supply level. Additionally, switched mode based power supply approach is considered as research track of the thesis.

#### 1.2 Scope and Objectives of the Thesis

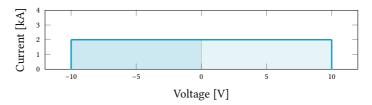

This work focuses on the design optimization and verification of a high-current low-voltage power supply dedicated to the powering of superconducting magnets. Ratings and characteristics of such power supply are gathered hereafter, it should also respect the HL-LHC requirements for unprecedented precision [22]. In order to reach the ramp-down time constraint, it should be able to operate in 2-quadrant by applying a negative voltage across the magnet. During the ramp-down, the energy stored in the magnet could be recovered and stored for the next cycle in a dedicated energy storage unit, thus the use of energy storage technologies is also analyzed at the system level. The design of a DC/DC power supply stage that fits those requirements is the core of the thesis.

- Maximum output current: 18 kA.

- Output voltage range:  $\pm 10 \,\text{V}$ .

- Lifetime expectancy: 20 years; 20 000 cycles expected.

The main contributions of the thesis are:

- A careful definition of the need and constraints regarding power supply for superconducting magnet, where a state of the art about high-current low-voltage power supply is conducted.

- A study about the use of energy storage system in such power supply is conducted, taking advantage of the cycling operation of the particle accelerator; integration possibilities and overview of the storage technologies are presented.

- A multi-objectives design optimization of the power supply is detailed, supported by mathematical tools and components integration, with the goals to obtain a highly efficiency and compact solution.

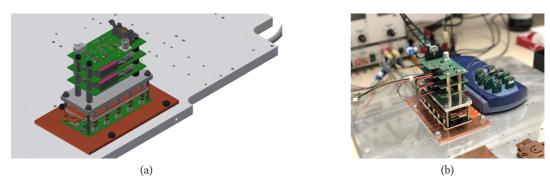

- The implementation of the selected optimal design for a reduced scale power supply prototype, able to provide 750 kA,  $\pm 10$  V is realized, including advanced integration of the components. This constitutes a proof of concept for a full size converter.

#### 1.3 Structure of the Thesis

The thesis is organized as follow.

Chapter 1 contains the introduction, background, objectives and structure of the thesis.

Chapter 2 presents the state of the art in the high-current low-voltage power supplies, for various applications with a particular focus on the superconducting magnets where the specific challenges related to the particle accelerator applications are assessed. The specific case of CERN is detailed where a larger picture at the system level is introduced in order to get a good understanding of the environment surrounding the power supply.

**Chapter 3** details the power supply structure and explore the possibilities to integrate an energy storage system in the specific case of the *Inner-Triplet magnets* powering for HL-LHC. The definition of the storage requirements is established and a brief overview of the energy storage technologies is performed. Findings of the study reveal that the battery based solutions are the most suited for the dedicated application.

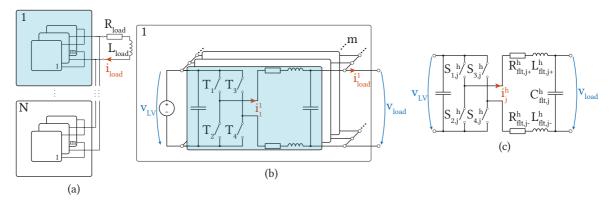

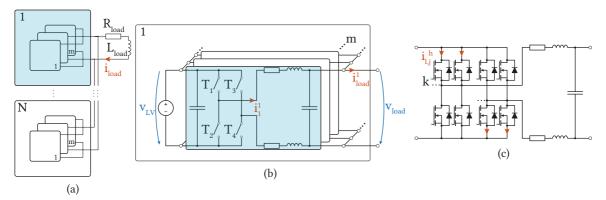

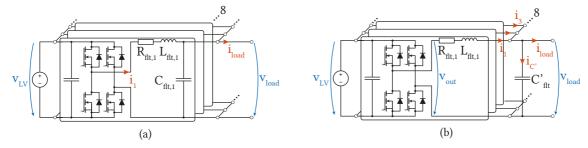

**Chapter 4** focuses on the DC/DC output stage of the power supply: this is the converter that processes the full load current. As the modularity is a key concept of such power supplies, and paralleling is necessary in order to achieve the desired ratings, the modularity structure and terminology is introduced in this chapter. The scope is then narrowed down to an individual *sub-converter* able to deliver 2 kA. Moreover, the definition of the topology and the way to achieve the 2-quadrant operation is defined.

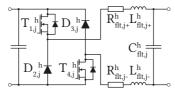

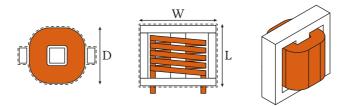

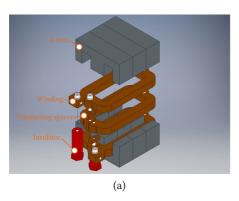

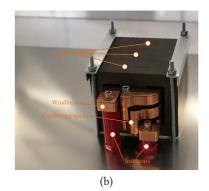

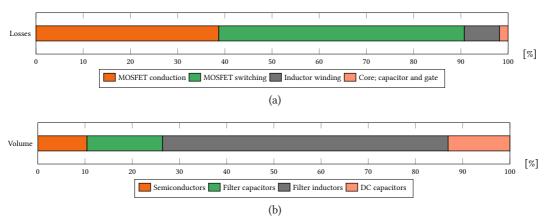

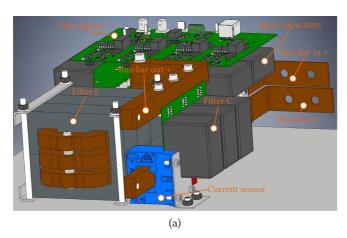

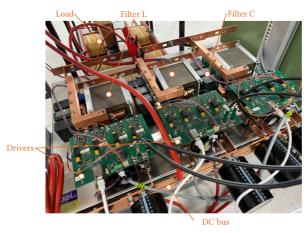

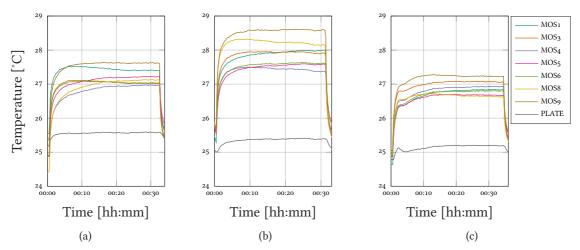

**Chapter 5** presents the hardware selection and optimization for the critical part of the converter: semiconductors and passives constituting the output filter of the stage. A structure and mathematical tools are established in order to compare and optimize the designs according to the defined requirements. As the topology heavily relies on parallelization, the interleaving between stages is considered to relax constraints on individual stages. An optimization tool is implemented and used to sweep the parameters in order to obtain the most efficient of the realistic designs. The results of the design optimization imply that the optimal solution is to divide the *sub-converter* in eight branches, where each switch is composed by six parallel MOSFETs. The implementation of such optimal building block of the system is detailed and verified through testing.

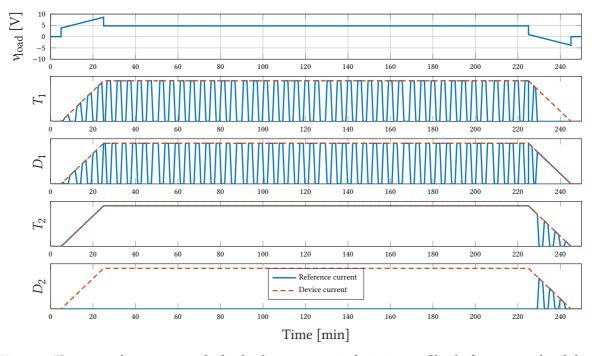

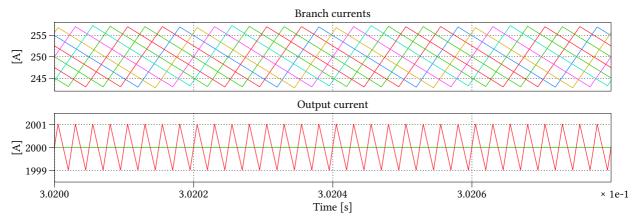

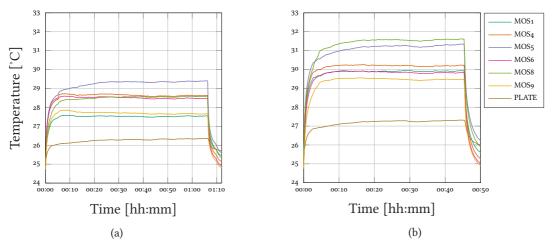

**Chapter 6** presents the control of multiple modules in parallel, taking the optimal *sub-converter* design previously determined, with eight *branches* in parallel. The control system design is carried out, implementing adequate controllers and tunning them to achieve required performances. The experimental results are collected from three realized *branches* operated in parallel, both in steady-state and dynamic operation.

**Chapter 7** concludes the work and highlights the learnings taken from the thesis, laying down the path for future development in what could be even larger particle accelerators.

#### 1.4 List of Publications

Journal papers:

- J1. E. Coulinge, S. Pittet, and D. Dujic, "Design optimization of two-quadrant high-current low-voltage power supply," *IEEE Transactions on Power Electronics*, 2020

- J2. E. Coulinge, S. Pittet, and D. Dujic, "High-current low-voltage interleaved power supply for superconducting magnets," *IET Power Electronics*, (under review)

#### Conference papers:

- C1. E. Coulinge, J. Burnet, and D. Dujic, "High-current low-voltage power supplies for superconducting magnets," in 2017 International Symposium on Power Electronics (Ee), Oct. 2017

- C2. E. Coulinge, J. Burnet, S. Pittet, and D. Dujic, "Comparative study of two-quadrant dc/dc stage in power supply for superconducting magnets," in *2018 IEEE International Conference on Industrial Technology (ICIT)*, Feb. 2018, pp. 652–657

- C3. M. Papamichali, E. Coulinge, F. Freijedo, and D. Dujic, "Power supply system with integrated energy storage for supeconducting magnets," in *PCIM Europe 2018; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management*, Jun. 2018, pp. 1–6

Other publications, not directly related to the scope of the thesis:

O1. E. Coulinge, A. Christe, and D. Dujic, "Electro-thermal design of a modular multilevel converter prototype," in *PCIM Europe 2016; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management*, May 2016, pp. 1–8

# 2 State of the Art

This chapter presents the state of the art in the high-current low-voltage power supplies, for various applications with a particular focus on the superconducting magnets where the specific challenges related to the particle accelerator applications are assessed. The specific case of CERN is detailed where a larger picture at the system level is introduced in order to get a good understanding of the environment surrounding the power supply.

#### 2.1 State of the Art

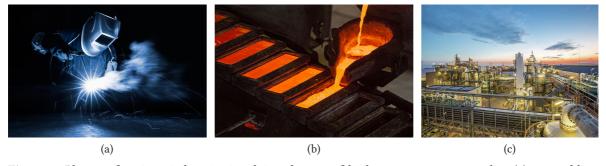

High-current low-voltage power supplies are a niche in the power supply domain. The output range of the power supply is a constraint given by the nature of the load, and only a few specific applications are demanding a high-current with a very low voltage. This implies a load with a very low resistance, such as the one for welding systems, the more advanced inductive loads that use superconductivity or the process of electrolysis which force a non-spontaneous chemical reaction by applying a DC current. The classical topologies and challenges for those specific applications are detailed in the next paragraphs, an illustration of their practical use is depicted in **Fig. 2.1**.

The voltage class of an generic electricity supply is defined by the international standard International Electrotechnical Commission (IEC) *60038:1983*, where in the DC voltage range, the low voltage is between 120 V and 1500 V and extra-low voltage is everything below 120 V. In the following review, this voltage range is considered jointly with a current rating above 100 A.

**Fig. 2.1** Photos of various industries involving the use of high-current power supplies (a) arc welding technique, welder in action, (b) primary casting of the aluminum, last step of the *Hall-Héroult* smelting process and (c) production line of chlorine through *chlor-alkali* process in Rotterdam.

Fig. 2.2 Conventional structure for an arc welding inverter.

#### 2.1.1 Welding

The welding process consists in joining materials by meting the parts together using a process generating a high heat. One particular technique of welding is the arc welding as depicted in **Fig. 2.1(a)**, which is used to join metal to metal where the source of heat is based on an electrical pulse [31].

As the name suggests, an electrical arc is created between an electrode and the base material, that is melted at the point of contact. This technique can then be divided into several specific methods depending on the gas used and the properties of the arc, such as metal/inert-gas (MIG), tungsten/inert-gas, flux-cored, submerged or plasma arc welding. The common characteristic between all of them is their reliance on a high current, which is produced by a power supply usually in the range of tens of kilo-watt, with a current rating above 100 A. A typical mobile MIG welding station for domestic use, is around 1.5 kW with an output regulated range between 32 A and 120 A depending on the set duty-cycle for a voltage rating around 30 V and a weight of 20 kg [32].

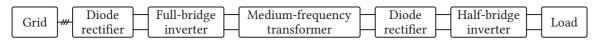

The classical structure of the power supply is given in Fig. 2.2, based on [33]–[35]. Even for industrial use the connection is made on the standard low-voltage AC grid, with standards rated sockets depending on the power of the supply as it is meant to be portable and used in various environments. The input stage allows to create the desired voltage level on medium frequency transformer, where the switching frequency is in the range of several tenth of kilo-Hertz. This transformer also provides galvanic isolation. A passive rectifier stage and a low frequency half-bridge inverter are the last stages before the resistive load. The output current can either be DC or AC with a low frequency, depending on the material to be welded.

#### 2.1.2 Aluminum Smelter

The primary aluminum is the one directly produced from mined ore, opposed to secondary or recycled aluminum that is manufactured from various forms of aluminum scrap. In order to transform the raw ores into pure aluminum metal, a critical step is to force a chemical reaction at a temperature around  $950\,^{\circ}$ C, this is the most energy consuming step of the process.

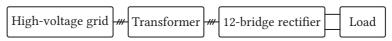

In order to provide the sufficient current, the power structure depicted in **Fig. 2.3** is classically implemented. Multiple of those elementary structure can even be paralleled to obtain larger ratings, and to do so phase shifted transformers are used in order to reduce the stress and harmonics on the grid [36], [37]. The rating for the industrial facility that is named the *potline* is the one that defines the power of the supply, being usually several hundreds of kilo-amperes. The electricity both helps the chemical reaction to happen and maintains the temperature of the cell around 950 °C. A rule of thumb gives a production of 7.5 kg of aluminum per day and per cell for a thousand amperes.

Fig. 2.3 Conventional elementary structure for an industrial aluminum smelter.

This *Hall-Héroult* process is now being used for many years, and even if its efficiency has been improved mostly by advancing the auxiliaries that treat the by-products of the reaction, the main process is intrinsically very energy demanding. This makes the process very heavy and a large consumer, so much so that in some countries, exemptions on the renewable energy targets are given. To meet those requirements, the installation relies on a higher voltage grid for its supply and can even be used to regulate the electrical network demand, that is why they are located in areas with reliable and low cost energy.

#### 2.1.3 Electrolysis

The previously presented aluminum smelting process is actually a particular case of electrolysis named electro-metallurgy. Electrolysis which consists in the passing of a direct electric current through an ionic substance that is either molten or dissolved in a suitable solvent, produces chemical reactions at the electrodes and decomposition of the materials.

According to Faraday's first law of electrolysis, as summarized by its mathematical form in (2.1), the amount of produced material at an electrode during an electrochemical reaction is directly proportional to the average current multiplied by the total time.

$$m = \frac{Q \times M}{F \times z} \tag{2.1}$$

Where m is the mass of substance interacting at the electrode, Q is the total electric charge that passes through the substance, M is the substance molar mass, F the Faraday constant and z the valence of the substance ions. This process is used at large industrial scale, as depicted in **Fig. 2.1(c)**, to produce chlorine, sodium hydroxide, oxygen, hydrogen, and many mores.

The role of the current is at the very heart of this process, making it very demanding when rated up to the industrial level. At this scale, the reliability of the power supply must be guaranteed, and simplicity is again key. The structure is classically very similar to the one presented in **Fig. 2.3**, and even though DC current should be regulated, the precision is not imposed, because of the inertia and the time constants involved. That is also a reason why those facilities can be used to mitigate the grid consumption.

The high-current rectifier is the power supply of choice for those industrial class applications, such as any furnace linked industry or chemistry processing. Typical products from ABB, as the medium current rectifiers or the high current rectifiers families, satisfy this electrochemical and electrometallurgy industries demand. Their rating can go up to  $220 \, \text{kA}$  with a wide range of voltages, up to  $2 \, \text{kV}$  [38], [39]. There is the possibility to parallel connect the units in order to reach even higher current level, as for this case example of  $500 \, \text{kA}$  [40].

#### 2.1.4 Particle Physics

Another very specific but different activity compared to the previous applications is the use of highcurrent low-voltage power supplies in the particle physics domain, where a strong magnetic field that interacts with the charged particles needs to be generated. Once again, the range of applications in this field is wide, from particle detectors [41], to specific magnets or superconducting magnets [42], [43] or even fusion applications [44], [45]. In that area, as every application is very unique, the topology is adapted and there are no global standards on the design of such power supplies. As most of the industrial application already presented, the reliability of the system is the highest on the priorities list. Additionally, the high current precision is a particular goal that any particle physics related power supply needs to achieve. As the current is the quantity that defines the magnetic field, which directly affects the trajectory of the particle, this should be finely controlled at all time. To this extent, some elements are always present in one form or another: a transformer for galvanic isolation, usually in the medium frequency range, a high precision current measurement device, classically a DC Current Transformer (DCCT) and some kind of redundancy in order to reduce the downtimes.

The case study on which the thesis project focuses is a particular set of superconducting magnets within CERN LHC, the design and the commonalities of their high-current low-voltage power supplies is reviewed here after.

#### 2.2 Existing Technologies at CERN

CERN LHC experiment relies on superconducting magnets to accelerate, bend, focus and keep control over the particle beam. The role of the superconducting magnet power supply is to provide reliably a large amount of current in a controlled way and with high precision, because any variation in the delivered current impacts the magnetic field which in turn affects the particle trajectories, which could lead to a premature stop of the experimental run. Quantitatively, 10 parts-per-million (ppm) is the targeted precision for the power supplies, which means 2 mA on a 2 kA power supply. Consequently, in order to maintain a steady operation, both precision and reliability are important.

To achieve both of those objectives, parallel connection of elementary *sub-converters* is often used to reach the desired ratings and take advantage of the modularity in terms of redundancy and interleaving to improve the electrical characteristics of the output waveforms of the power supply. Additionally, a not limited list of other aspects should be considered during the design phase of any CERN dedicated power supply.

The overall volume of the system should be kept low, because of their specific locations that the power supplies could be installed in, for example a confined space in an underground area or a technical gallery. Such kind of restricted emplacement imposes the need to carefully manage the losses as the heat should be evacuated by the dedicated water cooling system or the ambient air circulation system. For instance, the use of soft switching technique [11], [13], [46] helps to minimize switching losses in semiconductors. Another consequence that follows the limited access positions of the power supply imposes a very high availability of the power systems in order to maximize the operational time of the infrastructure with no human intervention.

In terms of safety, the grounding of the magnets requires a galvanic isolation inside the power supplies and the norm Electromagnetic Compatibility (EMC) *IEC61000* level 4 must be respected because of the proximity with other sensitive systems like cryogenic instrumentation or quench protection systems. Finally, the impact on the CERN power grid should be considered and techniques for peak shaving and perturbation rejection are favored.

**Fig. 2.4** Actual *Inner-Triplet* powering scheme. The *Inner-Triplet magnets* is composed by a series of four magnets named Q1, Q2a, Q2b and Q3, powered by three nested power supplies PC1, PC2 and PC3 and with some additional free-wheeling diodes.

**Tab. 2.1** *Inner-Triplet magnets* power supply specifications.

| Supply name     | Rat         | ings        | Operation  | Cooling           |

|-----------------|-------------|-------------|------------|-------------------|

| Зирргу паше     | Voltage [V] | Current [A] | Ореганоп   | Coomig            |

| PC1             | + 8         | + 8000      | 1-quadrant | Water             |

| PC2             | + 8         | + 6000      | 1-quadrant | Water             |

| PC <sub>3</sub> | ± 10        | ± 600       | 4-quadrant | Water, forced air |

The case study of this thesis is about a set of magnets named *Inner-Triplets magnets* whose role is to perform the last focusing of the particle beam before the interaction points, where the collisions happen. Presently, to power those magnets, two families of switch-mode power supply have been developed: a 1-quadrant type for the main circuit and a 4-quadrant type to locally trim the current across one magnet [47], [48]. Their actual powering scheme is provided in **Fig. 2.4**, and the power supply parameters are gathered in **Tab. 2.1**. They are arranged in a combination of three nested converters to feed the current in the series of four magnets. They operate as current controlled voltage source whose command signal comes from the control center and is processed through a decoupling matrix to give their individual set-point. The overall electrical system can be seen as voltage sources feeding a standard *RL* load, where the *R* comes from the copper cables and the *L* from the superconducting magnets.

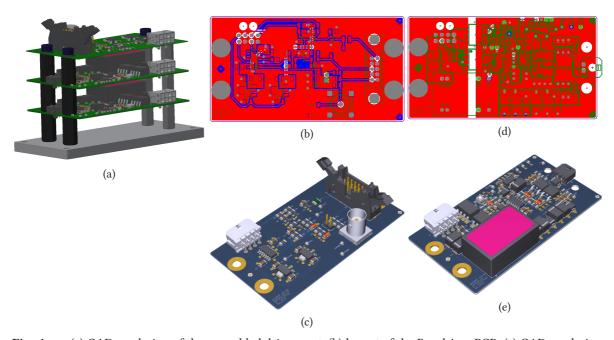

**Fig. 2.5** Simplified integration of power supplies. Thin line represents signals while thick ones represent power exchange between entities.

More generally for the CERN designs, the power part is always integrated as depicted in Fig. 2.5. As the current measurement is a critical part to reach the precision level, it is done internally with redundant DCCTs and is used to feed the Digital Electronic controller. This one is in charge of the regulation, and it takes its reference comes from further up, via the CERN Central Control which defines the operating point of all the systems according to the experimental run to perform. The most important services that surround the power supply are the AC supplies for main power and auxiliaries supplies, as well as the cooling, which can be air or water based depending on the location and the power rating of the supply. Finally a set of protection features are mandatory and implemented to provide safety for both equipment and personal. The earth monitoring circuit measures the current to the ground from the main current loop and the magnet protection systems are present to extract the energy in case of quench (when the superconducting state is lost locally in the magnet).

A selection of the most widely spread high-current low-voltage power supplies used in CERN installations are grouped in **Tab. 2.2** and their topologies are presented in the following paragraphs.

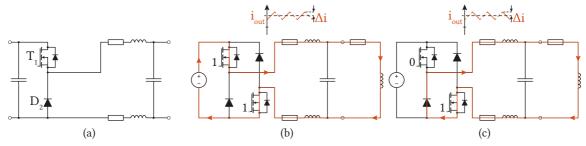

#### 2.2.1 1-Quadrant Power Supply Family

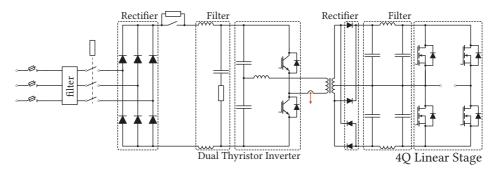

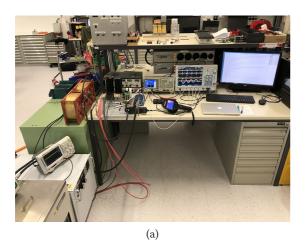

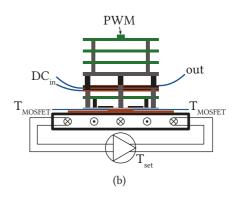

The family of 1-quadrant power supplies is designed in modular fashion, with many *sub-converters* in parallel. Each input module has a simple diode rectifier, providing a DC link voltage to the full-bridge soft-switched inverter of a DC-DC converter. To give a feeling of the size of such converters, picture of their final implementation in racks, including control, auxiliaries and bus-bars is given in **Fig. 2.6**.

**Tab. 2.2** The high-current low-voltage power supplies already existing at CERN.

| Converter         | Type | IN       |       | OUT   |             | Power module |          | Section    |

|-------------------|------|----------|-------|-------|-------------|--------------|----------|------------|

| +4;+6;+8 kA, +8 V | 1Q   | 3∼ 400 V | 100 A | +8 V  | +4;+6;+8 kA | +8 V         | +2 kA    | Sec. 2.2.2 |

| +13 kA, +18 V     | 1Q   | 3∼ 230 V | 420 A | +18 V | +13 kA      | +18 V        | +3.25 kA | Sec. 2.2.3 |

| ±60 A, ±8 V       | 4Q   | 3∼ 230 V | 1.2 A | ±8 V  | ±60 A       | -            |          | Sec. 2.2.6 |

| ±600 A, ±10 V     | 4Q   | 3∼ 230 V | 16 A  | ±10 V | ±600 A      |              | -        | Sec. 2.2.5 |

**Fig. 2.6** Photos of the complete high-current 1-quadrant power supply presented in the following paragraphs (a) 6 kA; 8 V and (b) 13 kA; 18 V.

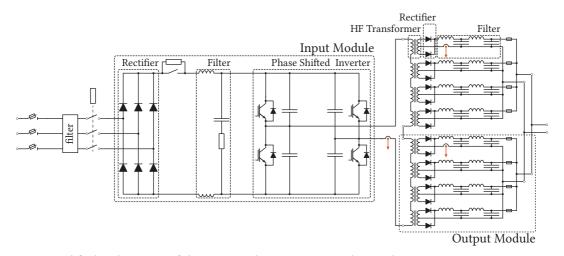

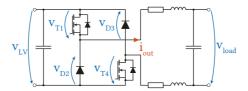

#### 2.2.2 2 kA Based Converters

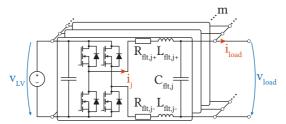

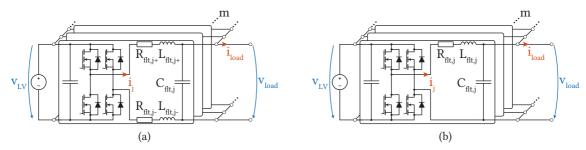

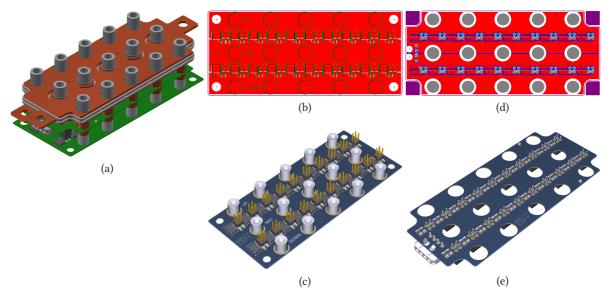

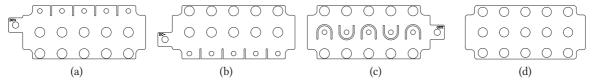

This family is designed as a 1-quadrant, positive voltage, positive current converters. It is constructed on a modular architecture relying on 2 kA sub-converters, which is easily scalable to 4, 6 or 8 kA with an output voltage of 8 V. This design is based on the elementary *sub-converter* depicted in **Fig. 2.7**, where the galvanic isolation is achieved by means of several medium-frequency transformers, connected in series on the primary side, with center-tapped rectifiers connected in parallel on the secondary side. The output of each rectifier features in this case a second order low-pass filter providing attenuation of the voltage ripple.

As it can be seen from the output module, the parallelization is heavily used to obtain the current rating. The current is only measured once per output module (red arrow), and the stage relies on the symmetry for the sharing between the four parallel branches, no active balancing is performed. Having multiple rectifier output stages ease the design of the magnetic parts, allowing to use lower-rated fuse for the protection of the whole system, and bring the high availability required: such a module can be up and running even if a secondary is fused out. Modularity greatly helps for the assembly and maintenance of the complete system, keeping the form factor of basic building block rather compact, and enabling the quick swap of module in case of fault.

Regarding the control and regulation, the *sub-converter* can be considered as a high-frequency current source, which is regulated by a 1 kHz bandwidth voltage loop, and where the phase-shifted PWM operates at 20 kHz. Some additional details about this family of converter is given in **Tab. 2.3**. Then several of those *sub-converters* are parallelized to achieve higher currents, when this is done, an active N+1 redundancy is implemented: e.g. a 6 kA power supply is composed by four elementary 2 kA sub-converters.

**Fig. 2.7** Simplified architecture of the power *sub-converter* 1-quadrant, 2 kA, 8 V.

**Tab. 2.3** Details about the 1-quadrant, 2 kA based family that compose the 4 kA; 6 kA; 8 kA, 8 V converters.

| Cooling |                | Accuracy      | Developer     | Manufacturer |          |

|---------|----------------|---------------|---------------|--------------|----------|

| Water   | 5 ppm @ 30 min | 10 ppm @ 24 h | 70 ppm @ 1 yr | Kempower     | Kempower |

Fig. 2.8 Simplified architecture of the power sub-converter 1-quadrant, 3.25 kA, 18 V.

$\textbf{Tab. 2.4} \quad \text{Details about the 1-quadrant, 3.25 kA based family that compose the 13 kA; 20.5 kA, 18 V converters.}$

| Cooling            |                | Accuracy     | Developer     | Manufacturer |              |

|--------------------|----------------|--------------|---------------|--------------|--------------|

| Water & forced air | 3 ppm @ 30 min | 5 ppm @ 24 h | 50 ppm @ 1 yr | Transtechnik | Transtechnik |

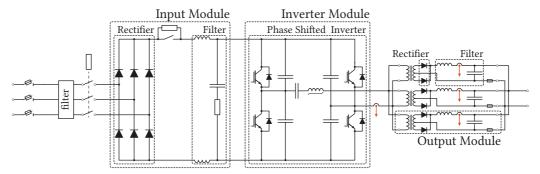

#### 2.2.3 3.25 kA Based Converters

This family of converters is very similar to the one previously presented. A 13 kA 1-quadrant, positive voltage, positive current converters with scaled up ratings for the sub-converter: 3.25 kA, 18 V, depicted in **Fig. 2.8** and which is constructed in the same fashion as the 2 kA one. Additional details about this family of converter is given in **Tab. 2.4**. A unique converter of 20.5 kA has been realized for a specific project, based on the same modules, with a greater number of them in parallel.

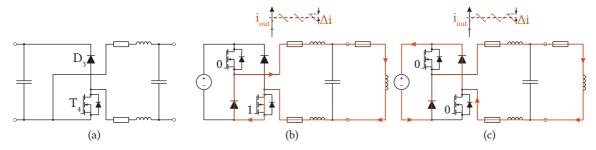

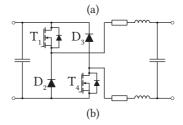

#### 2.2.4 4-Quadrant Power Supply Family

When a power supply is characterized as a 4-quadrant one, it is restricted to the output stage, the power supply has no ability to feed back power to the grid. Nevertheless, locally in the output stage, the current can flow in both direction and the voltage be any polarity. This is a way to have a more flexible control on the load. As the rating of this family of power supply is lower, because they are only used as correctors on the magnet current, they rely less on parallelization and can be integrated in a single module as shown in **Fig. 2.9**.

**Fig. 2.9** Photos of the 4-quadrant power supply presented in the following paragraphs (a)  $\pm 600 \, A$ ;  $\pm 10 \, V$  and (b)  $\pm 60 \, A$ ;  $\pm 8 \, V$ .

Fig. 2.10 Simplified architecture of the 4-quadrant power sub-converter, ±600 A, ±10 V.

**Tab. 2.5** Advanced details about 4-quadrant, ±600 A, ±10 V converter family.

| Cooling            |                 | Accuracy      | Developer      | Manufacturer |            |

|--------------------|-----------------|---------------|----------------|--------------|------------|

| Water & forced air | 10 ppm @ 30 min | 50 ppm @ 24 h | 200 ppm @ 1 yr | EEI-CIRTEM   | EEI-CIRTEM |

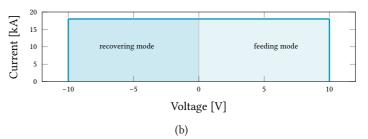

## 2.2.5 600 A Power Supply

The topology of a 4-quadrant power supply is very similar to the previously described 1-quadrant topology, where the output ratings are 600 A, 10 V, and is presented in **Fig. 2.10** with some additional details in **Tab. 2.5**. The input stage is rather identical up to the medium frequency transformer, then the output stage is a combination of a center-tapped passive rectifier and a 4-quadrant linear stage, which uses MOSFET in their linear region of operation to dissipate the recovered energy.

The voltage source is based on a variable switching frequency, between 50 kHz and 200 kHz half-bridge resonant topology followed by a linear stage. This topology gives a very low output EMC noise, at the cost of control complexity.

The output is designed around a linear stage relying on power MOSFET which provide the 4-quadrant operation. They behave as gate voltage controlled current source. In this case, the power supply is not recovering any energy from the load, but it is dissipated as heat inside the power semiconductors. More recently, redundancy feature and tolerance to radiation has been developed by CERN for this type of converter [49]. While the efficiency of this kind of system is not very high, this method guarantees the precision and accuracy in operation.

#### 2.2.6 60 A Power Supply

This converters adopt a similar topology as the 4-quadrant 600 A, with some additional filtering and a crowbar for the dissipation of the energy recovered from the magnet. Its complete topology is illustrated in Fig. 2.11, additional details are given in Tab. 2.6.

**Tab. 2.6** Advanced details about 4-quadrant, ±60 A, ±8 V converter family.

| Cooling    |                 | Developer      | Manufacturer    |      |     |

|------------|-----------------|----------------|-----------------|------|-----|

| Forced air | 50 ppm @ 30 min | 100 ppm @ 24 h | 1000 ppm @ 1 yr | CERN | CEL |

Fig. 2.11 Simplified architecture of the power *sub-converter* 4-quadrant, ±60 A, ±8 V.

# 2.3 Summary

In this chapter a wide variety of power supply is presented, where all of them have a role to feed the dedicated load with high current. Those loads are very specific, mostly part of some industrial complex or advanced research facilities. With a focus narrowed down to the CERN case, the family of high-current supplies for superconducting magnets is detailed, being either 1-quadrant or 4-quadrant and dissipating the recovered magnetic energy. To complete these existing solutions and to follow the operational constraints imposed by the new powering scheme of the *Inner-Triplets magnets*, there is a need for a 2-quadrant operating power supply that integrate energy storage instead of dissipation. Those solutions are presented in the next **Chap. 3**.

# **Energy Storage Integration**

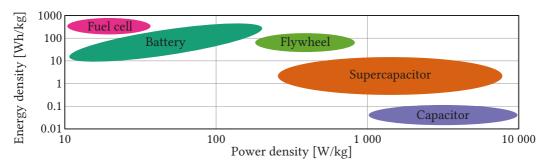

This chapter details the power supply structure and explore the possibilities to integrate an energy storage system in the specific case of the Inner-Triplet magnets powering for HL-LHC. The definition of the storage requirements is established and a brief overview of the energy storage technologies is performed. Findings of the study reveal that the battery based solutions are the most suited for the dedicated application.

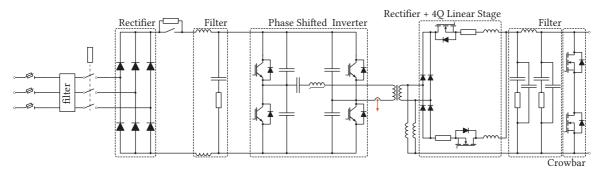

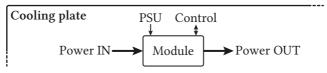

# 3.1 Power Supply Concept

The role of the power supply, from a system level point of view, is to interface the load to the grid providing galvanic isolation and giving the possibility to recover part of the energy stored in the load. This concept is depicted in the block diagram in **Fig. 3.1**. The grid and the load are perfectly known and assumed to be ideal. On one side, the grid is considered to be 400 V three-phase AC lines, outputs of a 18 kV, 2 MVA distribution transformer. On the other side, the load combines the *Inner-Triplet* super-conductive magnets, the super-conductive link, the electrical feed-box that interfaces traditional and superconducting circuits, and the copper cables at the output of the power supply. Thus it can be considered as a simple RL equivalent circuit where R is only defined by DC cables. Quantitatively, L is 255 mH and the considered value of R is 0.13 m $\Omega$ , this value is frozen during the course of the thesis to be independent from the evolutions of the project that is tunning the values according to the work packages inputs and developments.

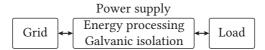

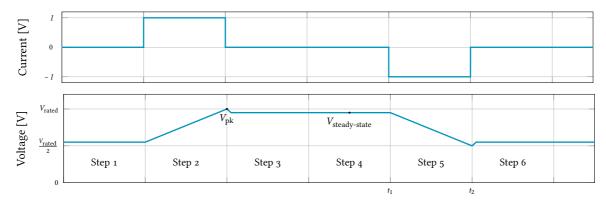

#### 3.1.1 Operational Cycle

Particle accelerators are characterized by a cycling way of operation where the operational cycle is well known and predictable when no unforeseen events occur. For the system of interest, the *Inner-Triplet magnets*, an overview of the defined cycle is given in **Fig. 3.2**. As it can be seen, after an initial ramp-up of the magnets current during approximately 20 min at a given rate of  $16 \, \mathrm{A \, s^{-1}}$ , the steady-state current value is regulated for several hours as collisions are happening for as long as the beam quality is good enough for the experiments to collect data and no problem appears anywhere else in the accelerator. The average duration of this phase is around 12 h.

**Fig. 3.1** Block diagram of the power supply at the system level. The galvanic isolation is necessary because the magnet is grounded for safety reasons.

**Fig. 3.2** Current and voltage profile of a typical cycle for the *Inner-Triplet magnets*, with a cable equivalent resistance of  $0.13 \text{ m}\Omega$ , corresponding to 20 m of water cooled 2600 mm<sup>2</sup> copper cables.

As particles are present in the experiment the precision must be guaranteed at all time during those previous operational phases. The last phase of the cycle is the ramp-down.

Finally, when the ramp-down procedure is triggered, the magnet current should be lowered to its standby level in a similar time as the ramp-up time of 20 min. As there are no more particles circulating in the experiment, the precision is less critical during this phase. As the future power supplies for HL-LHC upgrade will be located in underground galleries, closer to magnets, the cable resistance is removed from the equation. Thus there is a need to apply a negative voltage across the magnet to force the ramp-down of the current.

Thanks to this cycling operation, there is the possibility to reuse the recovered energy during the ramp-down phase of the cycle for the next ramp-up, or even injected it (this energy) back to the grid. It is worth providing a few energetic considerations about the cycle presented in **Fig. 3.2**. While taking into account specifications of the magnet, the calculation presented in (3.1) is performed to get the amount of magnetic energy stored in the load.

$$1/2 \times L \times I^2 = 1/2 \times 0.255 \times (18.10^3)^2 \simeq 40 \text{ MJ}$$

(3.1)

This represents the amount of energy to ideally recover in each cycle, that could be then processed elsewhere in the system or used for the next cycle. Evidently certain amount of energy will be lost in the resistance of the system, and the goal is to have the power supply as efficient as possible to reuse most of that energy. The benefit of having an energy storage inside the power supply leads to a better controllability of the power flow, allowing a peak shaving of the input power which could have a major impact on the infrastructure of the electrical grid side: the power coming from the grid side is rated to cover the losses in the system (resistive power in Fig. 3.2), whereas the inductive power needed during the transition phases is handled by the local energy storage element. This is the opportunity to downsize the input power compared to the peak power of the power supply, which is a feature that CERN highly values.

The goal of this part is to size the storage to handle the inductive part of the power whilst the input stage of the converter is rated for the resistive power during the flat-top. A consideration on the inductive power and its associated energy is given in **Sec. A.1**.

To put this number into perspective, 40 MJ is the energy of 1 L of oil, or 11 kW h of electricity which represents a monetary value of around 2 CHF in the very idealistic case. Over the lifetime of the power supply, the financial value of the recovered energy is not to be considered of great importance. The shift towards the new solution with local energy storage is a decision driven by controllability and scale of the input infrastructure rather than the raw monetary argument.

## 3.1.2 Requirements

Considering the CERN specific requirements, electrical performances, reliability, modularity and availability are the most important key performance indicators, thus representing the priorities when it comes to a new design. The developed 2-quadrant power supply has to comply with the integration scheme previously presented and has to consider the operating cycle of **Fig. 3.2** as nominal. The requirements can be summarized as:

- Peak output power rating: 180 kW.

- Input power rating: minimal; enough to cover the resistive losses.

- Output voltage rating:  $\pm$  10 V.

- Output current rating: +18 kA.

- Class 0 precision (cf. [22]).

- Dynamics:  $\pm 16 \,\mathrm{A \, s^{-1}}$  for a ramp-up/down in around 20 min.

- Lifetime expectancy: 20 years, accounting for 200 days of physics operation a year, and considering 1000 cycles per year; adding up to 20 000 cycles.

- Load resistance:  $0.13 \,\mathrm{m}\Omega$ , which represents around 20 m of copper cables.

- Load inductance: 255 mH.

- From CERN legacy and traditional design rules, based on electrical performances and decoupling arguments, there needs to be at least one input rectifier per magnet, i.e. no DC bus sharing between several loads.

- Any failure of one module composing the power supply should not impact the load, i.e. no change in the load current; the sizing is thus based on the loss of one module, which results in a N + 1 redundancy philosophy.

- Innovation: implementation of energy storage capabilities in the power supply, focused on an energy efficient design.

- Mandatory feature: galvanic isolation and mitigation of the grid perturbations.

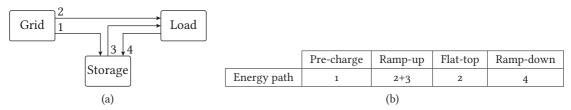

**Fig. 3.3** Energy flow between the grid, the energy storage element and the superconducting magnet (a) conceptual scheme and (b) strategy during the different phases of the cycle.

# 3.1.3 Power Flow Strategy

For any type of retained storage solution, a global strategy can be adopted regarding the power flow. Fig. 3.3(a) shows the possible energy flow paths between the grid, the energy storage element and the magnet, where the arrows indicate the direction of the energy flow. Based on this, Fig. 3.3(b) shows the paths used during each part of the cycle, for a possible energy management strategy. The goal is to take advantage of the storage to support the peak power, which is more than 2.7 times higher than the steady-state power.

During the pre-charge stage, the energy storage element receives energy from the grid in order to be prepared for the beginning of the cycle (path 1). Then, during the ramp-up, the grid supplies the active power (path 2) whilst the energy storage element takes care of the reactive power (path 3). During the steady operation, the energy is mainly provided by the grid (path 2) and, depending on its characteristics, by the energy storage element (path 3). Finally, during the ramp-down, the energy stored in the load is recovered via path 4.

# 3.2 Energy Recovery

There are two main approaches that can be considered for the implementation of the local energy recovery: either a fully reversible power supply that can feed back the energy to the grid, which is not *per se* a dedicated storage, or a local energy storage solution. This section explores those possibilities in detail.

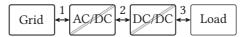

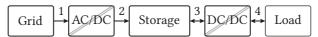

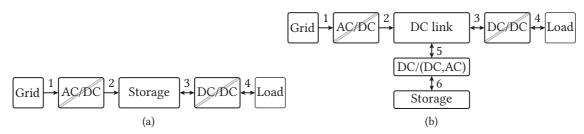

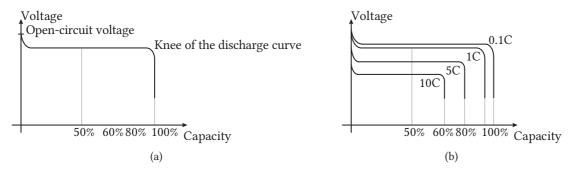

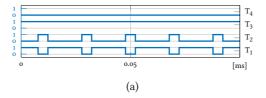

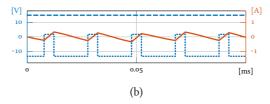

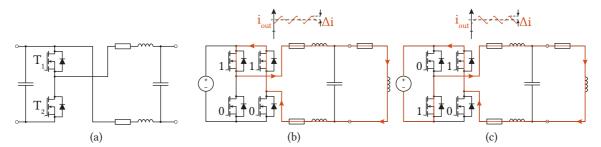

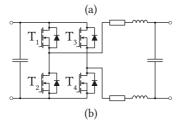

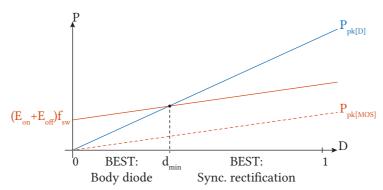

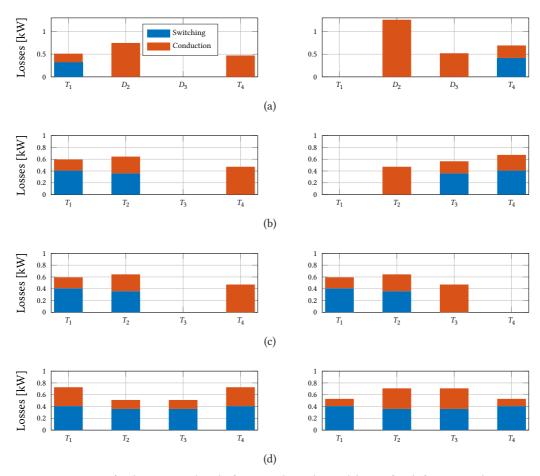

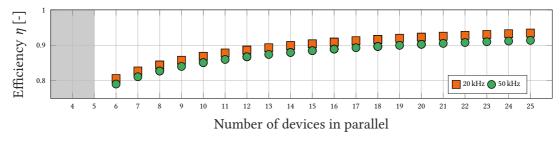

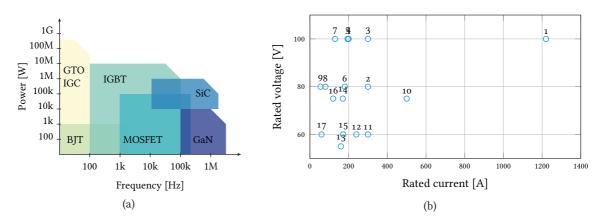

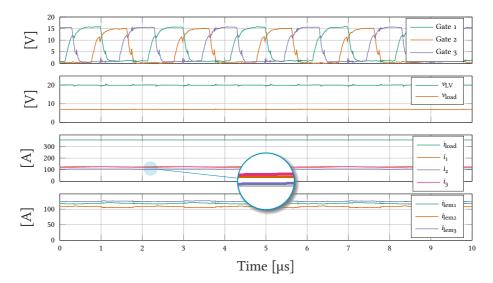

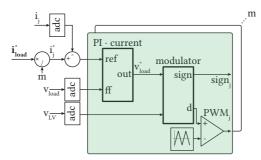

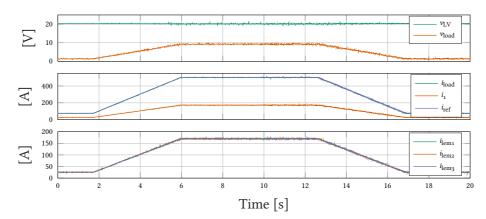

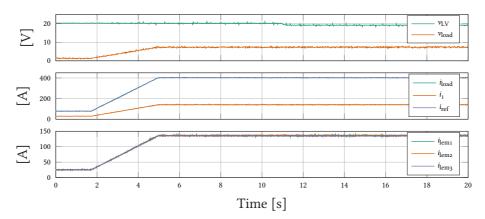

#### 3.2.1 Feeding Energy Back to the Grid