### Thèse n°7661

# EPFL

### Modeling for Ultra Low Noise CMOS Image Sensors

Présentée le 10 septembre 2020

à la Faculté des sciences et techniques de l'ingénieur Laboratoire de circuits intégrés Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

### Raffaele CAPOCCIA

Acceptée sur proposition du jury

Prof. E. Charbon, président du jury Prof. C. Enz, directeur de thèse Prof. A. Theuwissen, rapporteur Prof. E. Fossum, rapporteur Dr J.-M. Sallese, rapporteur

École polytechnique fédérale de Lausanne

2020

Ma Nino non aver paura di sbagliare un calcio di rigore, non è mica da questi particolari che si giudica un giocatore, un giocatore lo vedi dal coraggio, dall'altruismo e dalla fantasia. — Francesco De Gregori

To my family...

# Acknowledgements

I would like to express my deep gratitude to my thesis advisor, Prof. Christian Enz. His guidance and support over the past few years helped me to expand my knowledge in the area of device modeling and sensor design. I am genuinely grateful for having taught me how important is to be methodical and to insist on the detail.

My grateful thanks are also extended to Dr. Assim Boukhayma for his contribution and for having introduced me to the fascinating world of image sensors. His help and encouragement over the entire time of my Ph.D. studies daily motivated me to improve the quality of the research.

I wish to thank Dr. Farzan Jazaeri for everything he taught me during my Ph.D. His passion for physics and device modeling has been a source of inspiration for the research.

I would also like to express my deepest gratitude to Prof. Edoardo Charbon, Prof. Jean-Michel Salles, Prof. Eric Fossum and Prof. Albert Theuwissen for being part of my jury, evaluating my thesis and providing comments and remarks about my work.

My gratitude also goes to Dr. Wei Gao for providing me with the opportunity to conduct an internship in an industrial environment and participate in projects beyond the scope of this thesis. In addition, I must also thank the whole sensor and camera team for giving me the possibility to join their team. I would like to thank Dr. Chiao Liu, Dr. Andrew Berkovich, Dr. Elliott Tsai, Dr. Ziyun Li, Dr. Syed Shakib Sarwar, Reid Pinkham, Tianyi Yang and Seth Hirsh.

I would like to thank Prof. Leblebici and Dr. Akin for their help and encouragement that inspired me during my master thesis to purse a Ph.D. degree. During my PhD, I had the opportunity to work together with two master students, Tijmen Spreij and Alban Morelle. I would like to thank them for the collaboration we had and for their work, which is partially included in this thesis. Thanks also to Dr. Althaus for helping me editing this manuscript.

Particular thanks go to all my colleagues from ICLAB, current and former, for making these past few years a memorable experience. I would like then to express my sincerest thanks to my office mates, Arnout Beckers and Chunmin Zhang, for all the support we always gave each other. I also want to thank all my lab mates: Mattia Cacciotti, Francesco Chicco, Vladimir Kopta,

#### Acknowledgements

Sammy Cerida, Alessandro Pezzotta, Huang Huaiqi, Raghavasimhan Thirunarayanan, Antonio D'Amico, Antonino Caizzone, Vincent Camus, Jérémy Schlachter, Minhao Yang, Daniel Bold, Marta Franceschini and Salvatore Collura for all the fun conversation we had.

I am also thankful to all the friends I met in Switzerland and the fun time we had outside of EPFL. I must acknowledge Mikhail, Navid, Gain, Jonathan, Pamela, Cosimo, Giorgio, Chiara, Michela, Eleonora, Selma e Marta. At the same time I want to acknowledge my friends outside Switzerland for their continuous support, so I thank Beppe, Giulio, Inger, Biagio, Ellis, Ruben, Andrea, Peppe and Fabio.

Finally, my deep gratitude to my family for their continuous love. I am grateful to my sister Marta for always being there for me as a friend, my brothers Francesco e Matteo for their unparalleled support, and my parents Paola and Arcangelo. I am forever indebted to them for giving me the opportunities that have made me who I am.

Neuchâtel, 2020

Raffaele Capoccia

The low-light performance of a CMOS image sensor (CIS) is one of the most important performance metrics in a camera, whether it is used in products for consumer electronics or in an image-acquisition system for machine vision or the Internet-of-Things (IoT). At very low levels of illumination, the image sensors are limited by the noise generated by the readout circuits used to convert the information stored in the photodetector element, the pinned photodiode (PPD). Thanks to the development of efficient noise reduction techniques, modern CISs offer extremely interesting performance with sub-electron input-referred noise values. However, further noise reduction is needed to enable the single photon counting capability, which will allow new opportunities in a large variety of scientific applications.

This thesis focuses on the modeling of ultra-low noise CISs by exploring two main research topics. The first is the modeling of the PPD device together with the transfer gate (TG). The interface between these two structures limits performance in many advanced applications and requires a deep understanding of the charge transfer process. The core of the first compact model for the charge transfer in PPDs is reported here. The second evaluates the impact of different techniques on total noise reduction. In particular, the in-pixel source follower (SF) optimization, the combination of the column-level gain with the correlated multiple sampling (CMS) order and the effect of technology downscaling are analyzed and then verified by software simulations and experimental results.

The core of a physics-based compact model for the charge transfer in PPDs for CIS is presented in this dissertation. A set of analytical expressions is derived for the 2D electrostatic profile, the PPD capacitance, and the charge transfer current. The proposed model relies on the thermionic emission current mechanism, the barrier modulation and the full-depletion approximation to obtain the charge transfer current. The model is fully validated with stationary and opto-electrical technology computer-aided design (TCAD) simulations. The charge transfer model is validated experimentally by the expression of the total amount of the transferred charges derived from the charge transfer current and evaluated for different values of light intensity, TG voltage and transfer time. The result is a proven resource for CIS pixel designers in the analysis, simulation and optimization of PPD-based pixel in CISs.

The main circuit-level technique for noise reduction studied in this thesis is the CMS, which is used to reduce the thermal noise and the residual flicker noise originated in the in-pixel SF. To verify the impact of the combination of the column-level gain and the analog CMS on the readout noise, a readout chain with variable gain and variable CMS order has

been integrated in a standard 180 nm CIS process. The match between the measurement and the noise model results validates experimentally the model itself. Based on transient noise simulation results, the combination of an optimized pMOS source follower (SF), a column-level gain equal to 64 and a CMS of order 8 allows the noise to be reduced to the value of  $0.20 e_{\rm rms}$ , with a readout time of  $43 \,\mu$ s.

Key words: Charge Transfer Current, CMOS Image Sensors (CIS), Compact Device Modeling, Correlated Double Sampling (CDS), Correlated Multiple Sampling (CMS), Flicker noise, Passive Switched Capacitor, Photon Shot Noise, Photon Transfer Curve (PTC), Pinned Photodiode (PPD), Readout Noise, Temporal Noise, Thermal noise, Thermionic Emission Theory.

Le prestazioni a bassa luminosità dei sensori di immagini CMOS sono una delle metriche più importanti per la caratterizzazione di fotocamere utilizzate nell'elettronica di consumo o in sistemi per l'acquisizione di immagini processate da elaboratori o nell'internet delle cose (IdC o IoT). A livelli molto bassi di illuminazione, i sensori di immagini sono limitati dal rumore originato dai circuiti elettronici di lettura, utilizzati a loro volta per convertire l'informazione immagazzinata nel dispositivo fotosensibile, il fotodiodo pinned o pinned photodiode (PPD). Grazie allo sviluppo di efficienti tecniche di riduzione del rumore, i moderni sensori CMOS offrono performance estremamente interessanti con valori di rumore espresso in carica elettrica e riferito all'ingresso del circuito al di sotto del singolo elettrone. Tuttavia, una riduzione addizionale del rumore è necessaria per permettere il conteggio dei singoli elettroni generati durante l'illuminazione, il quale aprirebbe ad una serie di nuove opportunità in diverse applicazioni scientifiche.

Questa tesi si concentra sul modello dei sensori CMOS a bassa luminosità esplorando due ambiti principali di ricerca. Il primo è il modello del dispositivo PPD insieme al gate di trasferimento (o transfer gate (TG)). L'interfaccia tra queste due strutture limita le prestazioni in molte applicazioni avanzate e necessita di una comprensione profonda del processo di trasferimento di carica. Il nucleo del primo modello compatto per il trasferimento di carica nei PPD è presentato in questo dissertazione. Il secondo argomento valuta l'impatto delle diverse tecniche di riduzione del rumore. In particolar modo, l'ottimizzazione dell'inseguitore di tensione (o source follower (SF)) presente in ciascun pixel, la combinazione del guadagno in tensione applicato per ogni colonna dell'array del sensore con il campionamento multiplo correlato (Correlated Multiple Sampling (CMS)) e l'effetto dello scaling tecnologico sono analizzati e verificati con simulazioni software e risultati sperimentali.

Il nucleo del modello compatto qui presentato è basato sulla fisica del dispositivo e descrive il trasferimento di carica nei PPD usati nei CIS. Un insieme di espressioni analitiche è derivato partendo dal profilo elettrostatico in due dimensioni (2D), insieme alla capacità del PPD e alla corrente di trasferimento. Il modello proposto si basa sul meccanismo di corrente per emissione termoionica, la modulazione della barriera di potenziale all'interfaccia con il PPD e l'approssimazione di completo svuotamento. Il modello è interamente validato tramite simulazioni stazionarie e opto-elettriche effettuate con uno strumento software (TCAD) ed è in seguito validato sperimentalmente tramite l'espressione della quantità totale di cariche trasferite. Quest'ultima viene derivata direttamente dalla corrente di trasferimento e valutata

per diversi valori di intensità luminosa, tensione applicata al TG e tempo di trasferimento. Questo modello vuole essere una risorsa per i progettisti durante l'analisi, la simulazione e l'ottimizzazione di pixel basati sui dispositivi PPD.

La principale tecnica circuitale per la riduzione del rumore studiata in questa tesi è il CMS, utilizzato per ridurre il rumore termico e flicker originato nel SF, presente all'interno di ciascun pixel. Per verificare l'impatto della combinazione del guadagno a livello della colonna e del CMS analogico sul rumore, una catena di lettura con un guadagno variabile ed un ordine variabile per il CMS è stata implementata con un processo tecnologico 180 nm specifico per sensori di immagine. Il confronto tra le misure e i risultati del modello rappresentano una validazione sperimentale del modello stesso. Basandosi su delle simulazioni di rumore nel dominio del tempo, la combinazione di un pMOS SF ottimizzato nelle sue dimensioni e di un guadagno a livello della colonna uguale a 64 con un CMS di ordine 8 permette di ridurre il rumore ad un valore pari a  $0.20 e_{\rm rms}$ , con un tempo di lettura di 43 µs.

Parole chiave: Corrente di trasferimento della carica, sensori di immagine CMOS (CIS), modello compatto dispositivo, campionamento doppio correlato (CDS), campionamento multiplo correlato (CMS), rumore flicker, capacità commutate, rumore shot, fotodiodo pinned, rumore del circuito di lettura, rumore temporale, rumore spaziale, rumore termico, teoria ad emissione termoionica.

# Contents

| Ac | knov    | wledgements                                | i   |

|----|---------|--------------------------------------------|-----|

| Ał | ostra   | ct (English/Italiano)                      | iii |

| Ac | crony   | /ms                                        | xi  |

| Li | st of f | figures                                    | xv  |

| Li | stof    | tables xx                                  | iii |

| 1  | Intr    | roduction                                  | 1   |

|    | 1.1     | Brief History of CIS                       | 1   |

|    | 1.2     | CIS Market and Major Trends                | 4   |

|    | 1.3     | Ultra-Low Noise CIS – an Overview          | 6   |

|    | 1.4     | Thesis Motivation and Organization         | 8   |

|    | Refe    | erences for Chapter 1                      | 9   |

| 2  | СМ      | OS Image Sensors                           | 17  |

|    | 2.1     | Silicon-based Photodetectors               | 17  |

|    |         | 2.1.1 Device Physics                       | 17  |

|    |         | 2.1.2 Optical Absorption                   | 18  |

|    |         | 2.1.3 Device Components                    | 19  |

|    | 2.2     | Pixel Architectures                        | 23  |

|    |         | 2.2.1 PPS - 1T                             | 24  |

|    |         | 2.2.2 APS - 3T                             | 24  |

|    |         | 2.2.3 PPD/TG - 4T                          | 25  |

|    | 2.3     | Ultra-Low Noise CIS Architectures          | 26  |

|    |         | 2.3.1 Basic Block Diagram                  | 26  |

|    |         | 2.3.2 Column-level Amplifier Architectures | 28  |

|    |         | 2.3.3 Correlated Sampler Circuits          | 29  |

|    | 2.4     | Summary                                    | 33  |

|    | Refe    | erences for Chapter 2                      | 33  |

|    |         |                                            |     |

### Contents

| 3 | Con  | npact Modeling of Charge Transfer in PPDs for Low Light CIS | 37  |

|---|------|-------------------------------------------------------------|-----|

|   | 3.1  | Device Simulation                                           | 38  |

|   | 3.2  | Pinned Photodiode – Electrostatic Analysis                  | 38  |

|   | 3.3  | Pinned Photodiode Capacitance                               | 43  |

|   | 3.4  | Potential Barrier Modeling                                  | 45  |

|   | 3.5  | Charge Transfer Current                                     | 50  |

|   | 3.6  | Experimental Validation                                     | 53  |

|   |      | 3.6.1 Validation Methodology                                | 53  |

|   |      | 3.6.2 Experimental Setup                                    | 55  |

|   |      | 3.6.3 Measurement Results                                   | 55  |

|   |      | 3.6.4 Model Comparison                                      | 59  |

|   | 3.7  | Summary                                                     | 60  |

|   | Refe | erences for Chapter 3                                       | 61  |

| 4 | Noi  | se Sources in CIS                                           | 65  |

| т | 4.1  | Photon Shot Noise                                           | 65  |

|   | 4.2  | Dark Current Shot Noise                                     | 69  |

|   | 4.3  | Charge Transfer Noise                                       | 70  |

|   | 4.4  | Readout Noise                                               | 72  |

|   | 1.1  | 4.4.1 Thermal Noise                                         | 73  |

|   |      | 4.4.2 Reset or kTC Noise                                    | 74  |

|   |      | 4.4.3 Flicker Noise                                         | 75  |

|   |      | 4.4.4 RTS Noise                                             | 76  |

|   |      | 4.4.5 Leakage Current Shot Noise                            | 78  |

|   | 4.5  | Fixed Pattern Noise                                         | 80  |

|   | 4.6  | Signal-to-Noise Ratio in CIS                                | 82  |

|   | 4.7  | Summary                                                     | 83  |

|   |      | erences for Chapter 4                                       | 83  |

|   |      | -                                                           |     |

| 5 |      | dout Noise Analysis in Ultra-Low Noise CIS                  | 87  |

|   | 5.1  | Ultra-Low Noise Readout Chains                              | 87  |

|   | 5.2  | Noise Analysis                                              | 89  |

|   |      | 5.2.1 Calculation Method                                    | 89  |

|   |      | 5.2.2 Signal Transfer Functions                             | 91  |

|   |      | 5.2.3 Noise Transfer Functions                              | 94  |

|   | - 0  | 5.2.4 Noise Analysis Results                                | 94  |

|   | 5.3  | 5                                                           | 101 |

|   | Refe | erences for Chapter 5                                       | 102 |

| 6 | Noi  | se Reduction Techniques in Ultra-Low Light CIS              | 105 |

|   | 6.1  | Noise Reduction Techniques                                  | 106 |

|   | 6.2  | Combination of SC CMS with Column-level Gain                | 107 |

|   |      | 6.2.1 Readout Design                                        | 109 |

#### Contents

|    |         | 6.2.2   | Measurement Results                               | 117 |

|----|---------|---------|---------------------------------------------------|-----|

|    | 6.3     | Techn   | ology Downscaling Effects on Noise                | 124 |

|    |         | 6.3.1   | Impact of Technology Downscaling on Readout Noise | 124 |

|    |         | 6.3.2   | Simulation setup                                  | 126 |

|    |         | 6.3.3   | Noise Simulation Results                          | 128 |

|    | 6.4     | Comb    | ination of SC CMS with Downscaled Technology      | 132 |

|    |         | 6.4.1   | Simulation Setup                                  |     |

|    |         | 6.4.2   | Noise Simulations Results                         | 133 |

|    |         |         | Photoelectron counting possibility                |     |

|    | 6.5     |         | nary                                              |     |

|    | Refe    | erences | for Chapter 6                                     | 138 |

| 7  | Con     | clusio  | n                                                 | 141 |

|    | 7.1     | Sumn    | nary of Achievements                              | 141 |

|    | 7.2     |         | Findings                                          |     |

|    | 7.3     |         | e Work                                            |     |

|    | Refe    |         | for Chapter 7                                     |     |

| А  | Ann     | endix   |                                                   | 147 |

|    |         |         | ostatics in PPD device                            | 147 |

|    |         |         | ostatics along path A                             |     |

|    |         |         |                                                   |     |

| Li | st of ] | Publica | ations                                            | 149 |

| Сı | ırric   | ulum V  | fitae                                             | 151 |

### Acronyms

- ADC Analog-to-Digital Converter.

- AI Artificial Intelligence.

- APS Active Pixel Sensor.

- **AR** Augmented Reality.

- AZ Auto-Zero.

- BCCD Buried Channel Charge-Coupled Device.

- **BER** Bit error rate.

- BSI Back-Side Illumination.

- **BSIM** Berkeley Short channel IGFET Model.

- **BWI** Bit-Wise Inversion.

- **CCD** Charge-Coupled Device.

- **CDS** Correlated Double Sampling.

- CG Conversion Gain.

- CIS CMOS Image Sensors.

- **CLA** Column-Level Amplifier.

- CMS Correlated Multiple Sampling.

- CS Common Source.

- CTI Charge Transfer Inefficiency.

- CTIA Capacitive Trans-Impedance Amplifier.

- DCSN Dark Current Shot Noise.

#### Acronyms

- **DR** Dynamic Range.

- DSNU Dark Signal Non Uniformity.

- EFWC Equilibrium Full Well Capacity.

- EMW Electromagnetic Wave Solver.

- FPN Fixed Pattern Noise.

- FPS Frames per Second.

- FWC Full Well Capacity.

- HDR High Dynamic Range.

- IC Integrated Circuit.

- LDD Low Doped Drain.

- LTV Linear Time-Variant.

- MI Moderate Inversion.

- MOS Metal-Oxide-Semiconductor.

- **OTA** Operational Transconductance Amplifier.

- PCH Photon Counting Histograms.

- PPD Pinned Photodiode.

- **PPS** Passive Pixel Sensor.

- PRNU Photo Response Non Uniformity.

- **PSD** Power Spectral Density.

- **PSN** Photon Shot Noise.

- PT Photon Transfer.

- PTC Photon Transfer Curve.

- QE Quantum Efficiency.

- QIS Quanta Image Sensor.

- **RMS** Root Mean Square.

- **RS** Row Select.

- **RST** Reset Transistor.

- **RTS** Random Telegraph Signal.

- **SF** Source Follower.

- SI Strong Inversion.

- SN Sense Node.

- **SNR** Signal-to-Noise Ratio.

- **SPAD** Single Photon Avalanche Diode.

- **SRAM** Static Random Access Memory.

- **SS** Single-Slope.

- **STI** Shallow Trench Isolation.

- TCAD Technology Computer-Aided Design.

- TG Transfer Gate.

- **ToF** Time of Flight.

- TRN Temporal Read Noise.

- VCCS Voltage-Controlled Current-Source.

- WI Weak Inversion.

| 1.1 | A summary history of CIS with the crucial events reported in a timeline: from                              |    |

|-----|------------------------------------------------------------------------------------------------------------|----|

|     | the early development stages of technology to modern designs.                                              | 2  |

| 1.2 | CIS market growth in (a) from 2016 to 2019 with forecasts up to 2025. The                                  |    |

|     | positive trend is expected to continue in the upcoming years (source: Yole                                 |    |

|     | Développement). Worldwide number of shipped image sensors in (b) according                                 |    |

|     | to IC Insights.                                                                                            | 4  |

| 1.3 | Modern trends described in [14] that involve image sensors and camera designs:                             |    |

|     | multi-camera systems in (a), high resolution arrays in (b), 3D sensing in (c) and                          |    |

|     | biometric ID based on iris-scanner in (d) (source: Daiwa Capital Markets)                                  | 5  |

| 1.4 | Frames from advertisement in 2020 of the top smartphones of Apple and Sam-                                 |    |

|     | sung, respectively, involving good performances at low-light levels to appeal to                           |    |

|     | consumers                                                                                                  | 6  |

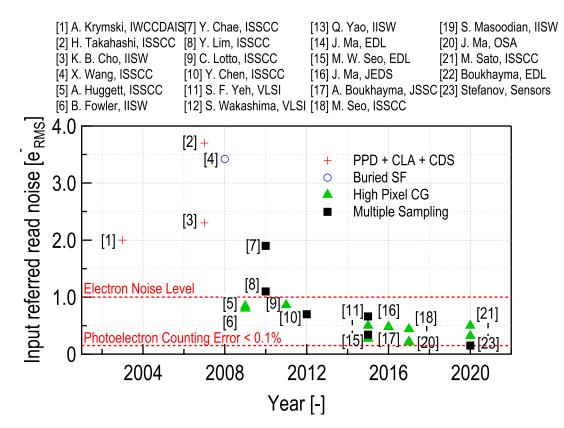

| 1.5 | Values of input-referred read noise in articles published from 2003 to 2020 and                            |    |

|     | reported in the references of this chapter. A large amount of research reached                             |    |

|     | the sub-electron noise value, while the level for a photoelectron counting error                           |    |

|     | lower than 0.1% (0.15 $e_{rms}^{-}$ ) is very close in recent publications                                 | 7  |

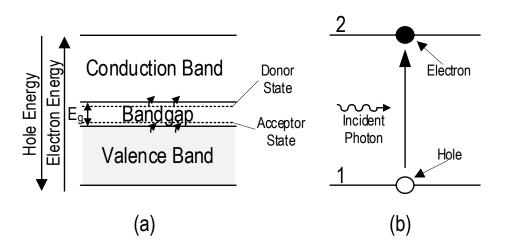

| 2.1 | Energy band diagram of semiconductor in (a). The absorption shown in (b) is                                |    |

|     | one of the possible interactions between the light and the matters                                         | 18 |

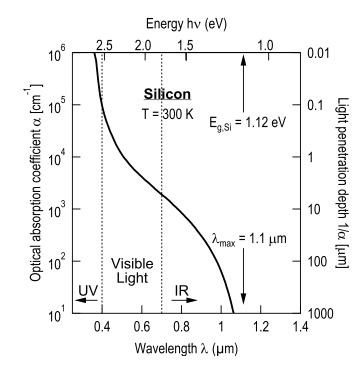

| 2.2 | Absorption coefficient as a function of wavelength for silicon material. Below                             |    |

|     | the cutoff wavelength, absorption increases gradually due to the fact that Si is an                        |    |

|     | indirect gap material                                                                                      | 19 |

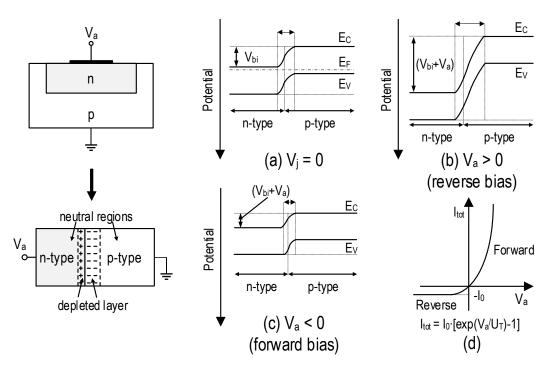

| 2.3 | Cross-section of a $pn$ -junction and its 2D equivalent representation. The elec-                          |    |

|     | trostatic potential profile is depicted at equilibrium in (a), in reverse bias in (b)                      |    |

|     | and in forward bias in (c). The I-V characteristic is shown in (d).                                        | 20 |

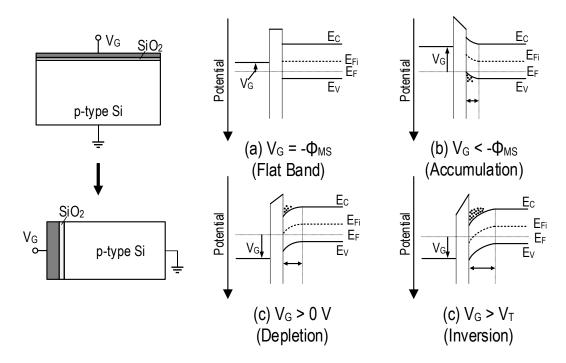

| 2.4 | Cross-section of a MOS structure and its 2D equivalent representation. The                                 |    |

|     | gate electrode is on top of the silicon dioxide layer (SiO <sub>2</sub> ) and a $p$ -type silicon          |    |

|     | structure. The potential distribution of the MOS structure is shown at various                             |    |

|     | gate biases, $V_G$ : for a flat-band condition in (a), for a negative $V_G$ and a surface                  |    |

|     | charge accumulation in (b), for a positive $V_G$ and a shallow depletion in (c) and                        |    |

|     | a surface inversion layer in (d).                                                                          | 21 |

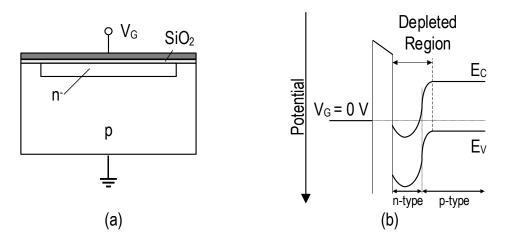

| 2.5 | Cross-sectional view of buried MOS structure in (a) and potential distribution under full depletion in (b) |    |

|     |                                                                                                            | 22 |

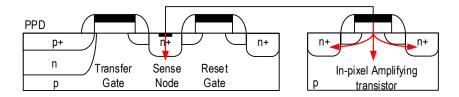

| 2.6  | Cross-sectional view of a buried photodiode or PPD in (a) and potential distribu-<br>tion in (c) under depletion.                                                                                                                                                                                                                                                                                                                                                                                                                               | 23 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

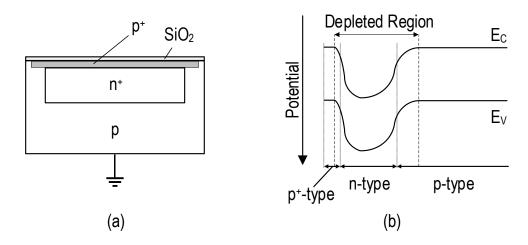

| 2.7  | Four pixel schematics: 1T PPS in (a), 3T in (b), 4T APS in (c) and 4T CTIA in (d).                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24 |

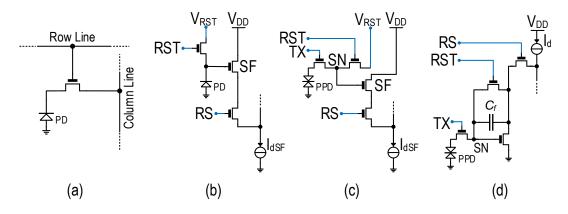

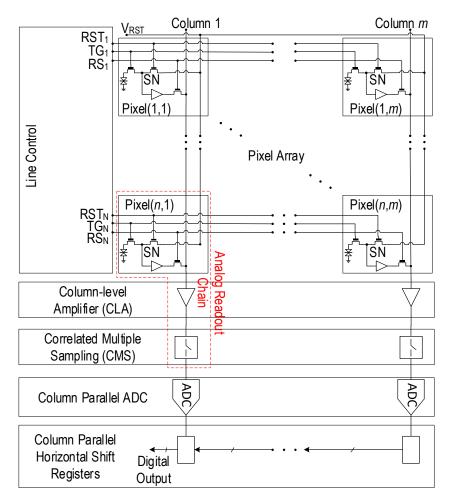

| 2.8  | Block diagram of a conventional low noise CIS composed of an array of 4T pixels.<br>The Line Control enables the control signals for the pixel array according to the<br>readout scheme. At column-level, the CLA, CDS and ADC blocks are generally<br>implemented.                                                                                                                                                                                                                                                                             | 25 |

| 2.9  | Rolling shutter readout mode in (a) with shifted reset, exposures and readout for each line. Global shutter mode in (b) with equal start and stop of the exposure for all lines.                                                                                                                                                                                                                                                                                                                                                                | 26 |

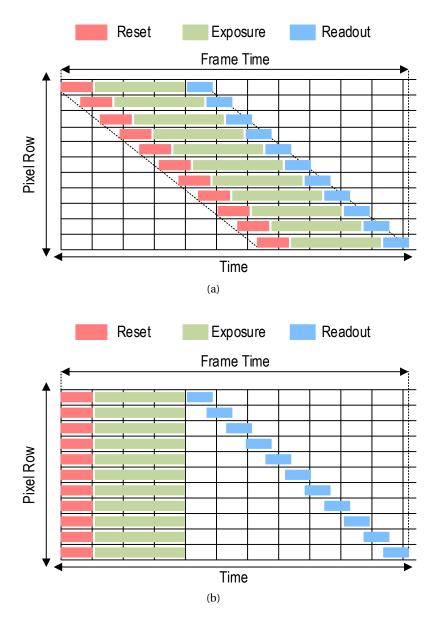

| 2.10 | Column amplifier architectures described in [18]: single-stage capacitive ampli-<br>fier in (a), two-stage capacitive amplifier in (b) and dual single-stage capacitive<br>amplifier in (c).                                                                                                                                                                                                                                                                                                                                                    | 27 |

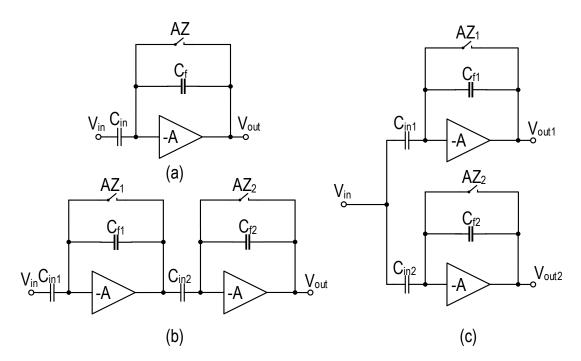

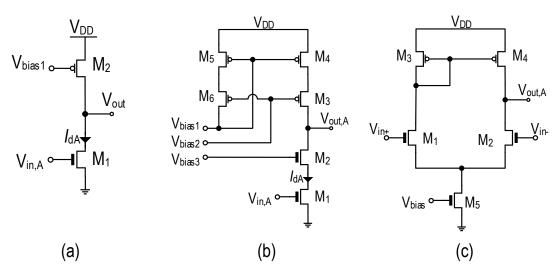

| 2.11 | Column amplifier circuits described in [18]: single-ended MOS amplifier archi-<br>tectures in (a) and (b), differential MOS amplifier in (c).                                                                                                                                                                                                                                                                                                                                                                                                   | 28 |

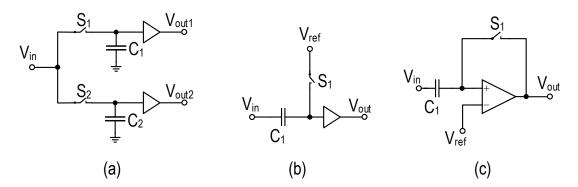

| 2.12 | Three different implementations for the CDS circuit described in [18]: the differ-<br>ential Track and Hold CDS in (a), the single-ended CDS with a voltage buffer in<br>(b) and the single-ended CDS with transconductance amplifier in (c)                                                                                                                                                                                                                                                                                                    | 29 |

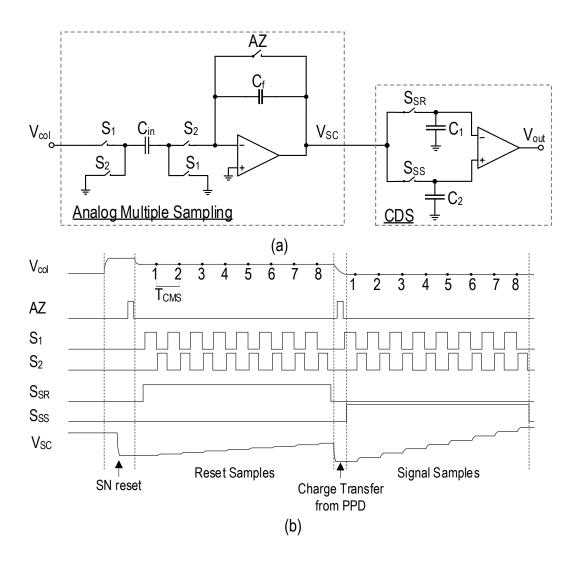

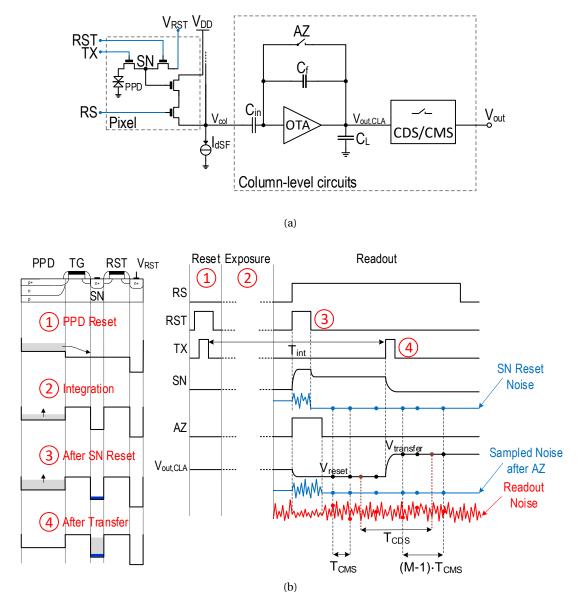

| 2.13 | Analog implementation in (a) of CMS using a switched-capacitor integrator.<br>Timing diagram in (b) of the control signals and voltages at the main internal<br>nodes, during the reset and after the charge transfer from the PPD                                                                                                                                                                                                                                                                                                              | 31 |

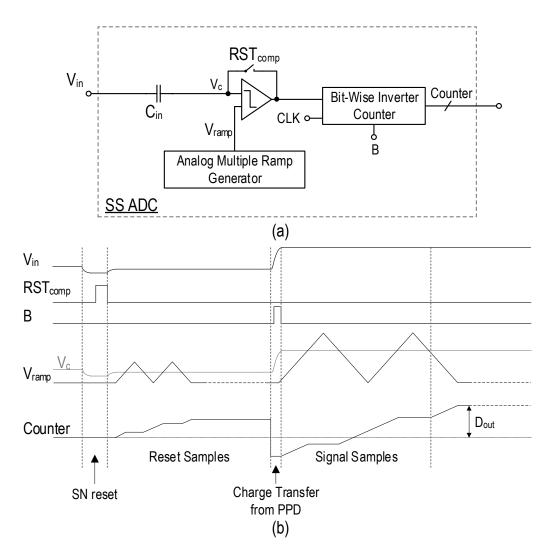

| 2.14 | Digital implementation in (a) of CMS using a multiple-ramp single-slope ADC.<br>Timing diagram in (b) of the control and main node signals during the reset and<br>after the charge transfer from the PPD.                                                                                                                                                                                                                                                                                                                                      | 32 |

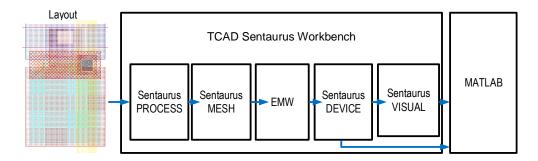

| 3.1  | The suite of tools composing the TCAD Sentaurus Workbench are shown in the order of execution, from the process simulation to the output data visualization.                                                                                                                                                                                                                                                                                                                                                                                    | 38 |

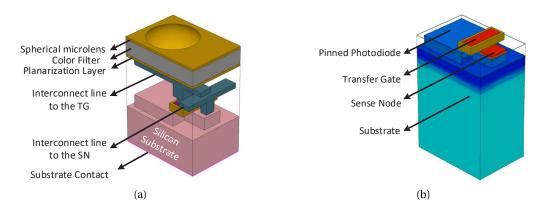

| 3.2  | Pixel back-end in (a): the microlens, the color filter and the interconnections.<br>Pixel front-end in (b): the pinned photodiode, the TG and the SN.                                                                                                                                                                                                                                                                                                                                                                                           | 39 |

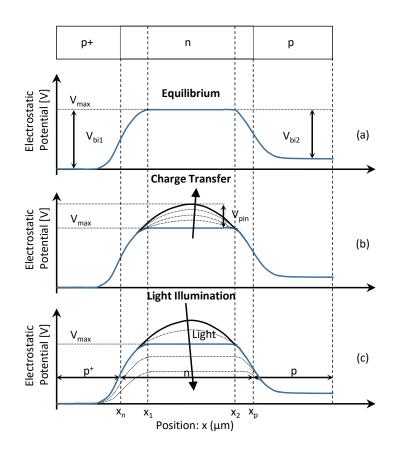

| 3.3  | Sketches of the electrostatic potential of the PPD: (a) at equilibrium condition, showing two built-in potentials, $V_{bi1}$ and $V_{bi2}$ , and maximum potential, $V_{max}$ ; (b) the maximum value of the electrostatic potential increases until the empty condition is reached while transferring the charges from the PPD to the SN. The maximum variation of the electrostatic potential is the pinning voltage, $V_{pin}$ , as defined in [5]; (c) the potential moves towards the flat-band condition due to the applied illumination. | 40 |

|      | **                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

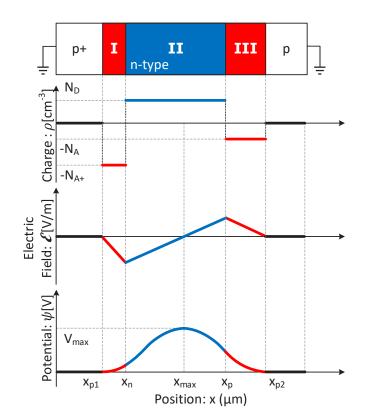

| 3.4  | Simplified cross-section of a PPD under the assumptions of full depletion and abrupt transition: $\rho(x)$ is the charge distribution, $\mathscr{E}(x)$ the electric field and $\psi(x)$ |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | the electrostatic potential along the position x. $x_n$ is the junction boundary                                                                                                         |    |

|      | between the $p^+$ and $n$ layers, $x_p$ the junction boundary between $n$ and the                                                                                                        |    |

|      | substrate, $x_{p1}$ and $x_{p2}$ are the limits of the depletion regions on the $p^+$ and p                                                                                              |    |

|      | regions of the two junctions, respectively. Expressions for the electric field and                                                                                                       |    |

|      | the electrostatic potential are given in Appendix A.1.                                                                                                                                   | 41 |

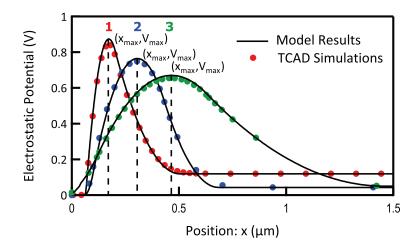

| 3.5  | Electrostatic potential inside the PPD structure for Case 1, 2 and 3 reported in                                                                                                         |    |

| 0.0  | Table 3.1: the profile simulated in TCAD is compared with the expression derived                                                                                                         |    |

|      | in the proposed model. $x_{\text{max}}$ is at 170 nm and $V_{\text{max}}$ is 0.84 V at 300 K in case I,                                                                                  |    |

|      | 305 nm and 0.76 V in case II, and 460 nm and 0.67 V in case III.                                                                                                                         | 42 |

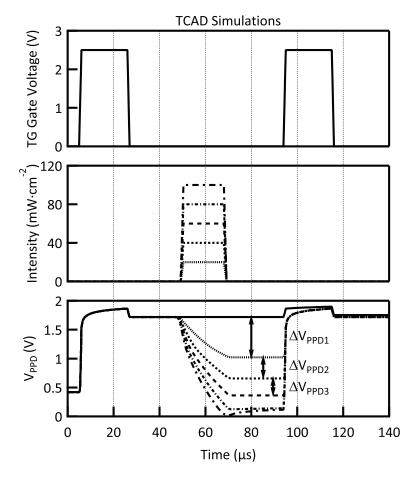

| 26   | Opto-electrical transient simulations: the gate voltage applied to the TG, the                                                                                                           | 12 |

| 3.6  | intensity of the incident wave and the electrostatic potential inside the PPD. The                                                                                                       |    |

|      |                                                                                                                                                                                          |    |

|      | changes in the electrostatic potential are proportional to the incident light and                                                                                                        | 10 |

|      | can be used to derive the PPD capacitance                                                                                                                                                | 43 |

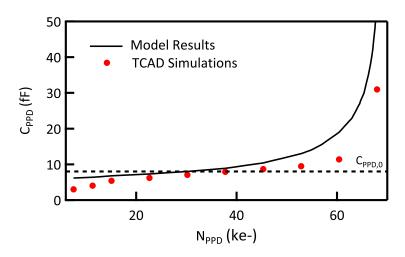

| 3.7  | PPD capacitance as a function of the photogenerated electrons: TCAD simula-                                                                                                              |    |

|      | tions are compared with the proposed model.                                                                                                                                              | 44 |

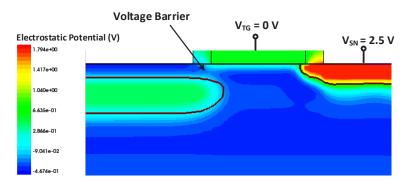

| 3.8  | Electrostatic Potential of the interface between the PPD and the TG when $V_{TG}$ =                                                                                                      |    |

|      | 0V. Evidence of a potential barrier between the <i>n</i> -well and the semiconductor                                                                                                     |    |

|      | beneath the TG.                                                                                                                                                                          | 45 |

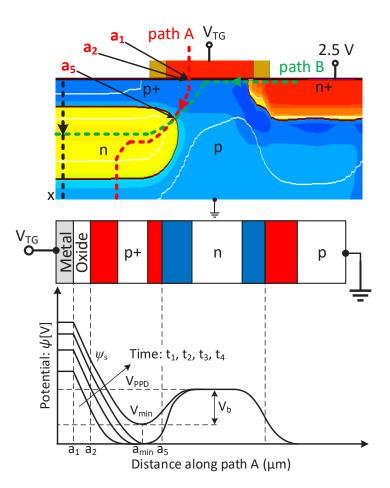

| 3.9  | Section of the interface between the TG and PPD with the 2D equivalent stretched                                                                                                         |    |

|      | version. Electrostatic potential at the interface between the PPD and the TG                                                                                                             |    |

|      | during the sweep of the gate voltage. The barrier voltage is changed by the TG                                                                                                           |    |

|      | and PPD voltage values.                                                                                                                                                                  | 46 |

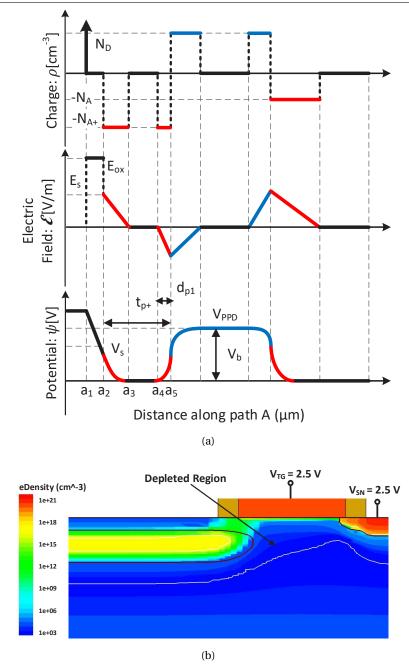

| 3.10 | In (a), the charge distribution, electric field, and electrostatic potential under                                                                                                       |    |

|      | the assumptions of full depletion and abrupt transitions. The interface region in                                                                                                        |    |

|      | (b) is fully depleted along the effective charge transfer path, for a $V_{TG} = 2.5 \text{ V}$ and                                                                                       |    |

|      | $V_{\rm SN} = 2.5  \rm V.$                                                                                                                                                               | 47 |

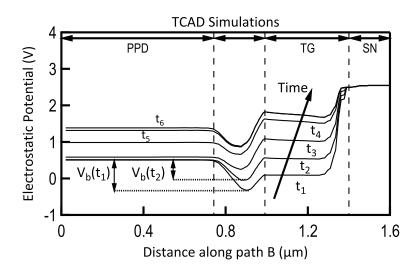

| 3.11 | Electrostatic potential along the path B crossing the PPD well, the interface, the                                                                                                       |    |

|      | area beneath the TG and the SN, for different time instants. $t_1 - t_4$ corresponds                                                                                                     |    |

|      | to the rising edge of $V_{TG}$ , while $t_5 - t_6$ refer to $V_{TG}$ constant.                                                                                                           | 48 |

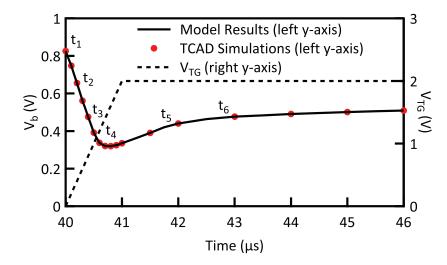

| 3.12 | Value of the potential barrier during time along the charge transfer period. The                                                                                                         |    |

|      | behavior of the barrier is well predicted by the proposed model.                                                                                                                         | 49 |

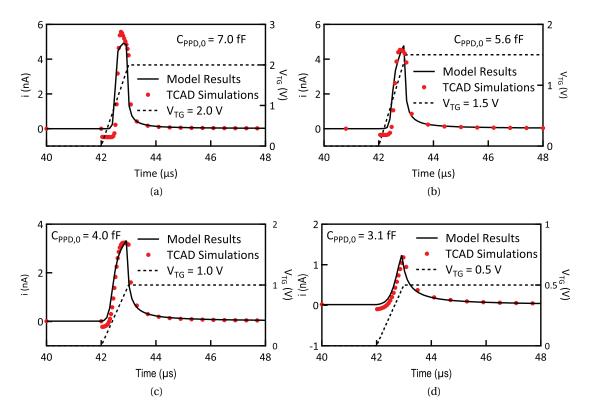

| 3.13 | Current pulses in (a, b, c, d) representing the charge transfer from PPD to SN for                                                                                                       |    |

| 0110 | four different $V_{\text{TG}}$ values: TCAD simulations are compared with the proposed                                                                                                   |    |

|      | model.                                                                                                                                                                                   | 51 |

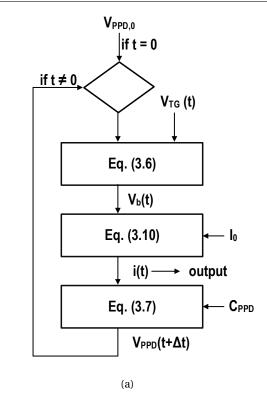

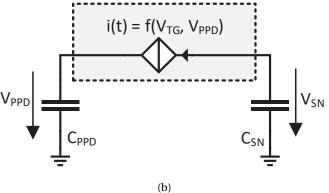

| 3 1/ | Flow in (a) to evaluate the model based on the derived expressions. Proposed                                                                                                             | 01 |

| J.14 | equivalent circuit in (b) for the PPD, TG, and SN, where the function f is given                                                                                                         |    |

|      | in (3.10)                                                                                                                                                                                | 52 |

| 215  |                                                                                                                                                                                          | 52 |

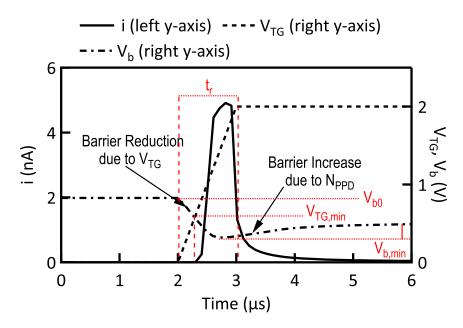

| 3.15 | TCAD transient simulation of the charge transfer current together with the TG                                                                                                            | 50 |

|      | pulse and the potential barrier.                                                                                                                                                         | 53 |

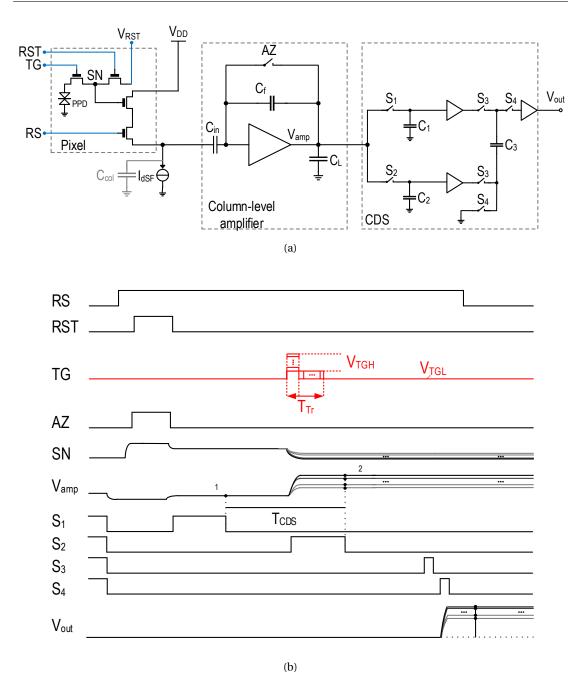

| 3.16 | Schematic in (a) of the implemented readout chain with a 4T pixel, the CLA<br>and the passive CDS circuit. Timing diagram in (b) of the control signals and<br>the main internal nodes: in order to obtain the measurement results, different                |          |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | values for the pulse width and the $V_{TGH}$ are used                                                                                                                                                                                                        | 56       |

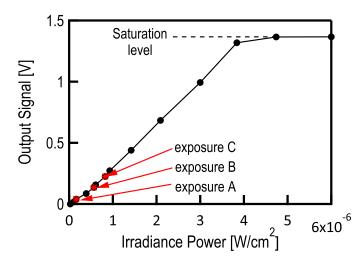

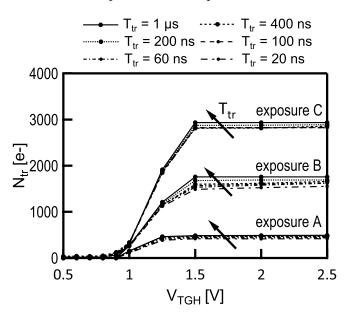

|      | Readout Photon Response with the Exposure A, B and C marked with red asterisks. $N_{\rm tr}$ is plotted for different values of the transfer time versus the TG voltage for three different exposures (exposure A, B and C). This figure shows the values of | 57       |

|      | <i>V</i> <sub>TGH</sub> that allow a complete charge transfer                                                                                                                                                                                                | 57       |

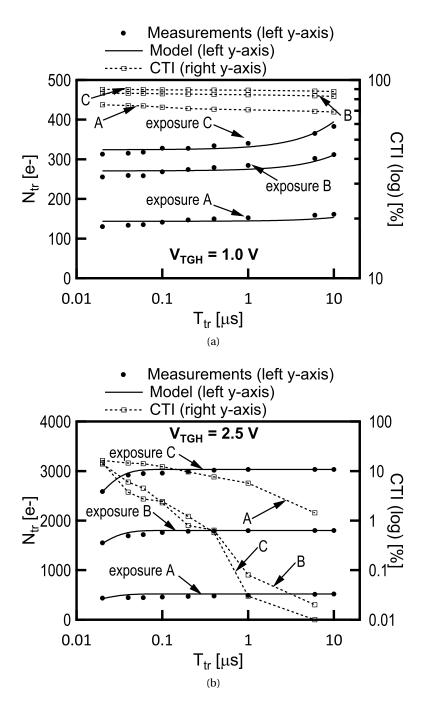

| 3.19 | $N_{\rm tr}$ is plotted for $V_{\rm TGH}$ equal to 1 V in (a) and 2.5 V in (b) versus the $T_{\rm tr}$ , together                                                                                                                                            |          |

|      | with the model results. the CTI for the two cases also is plotted with dashed lines.                                                                                                                                                                         | 58       |

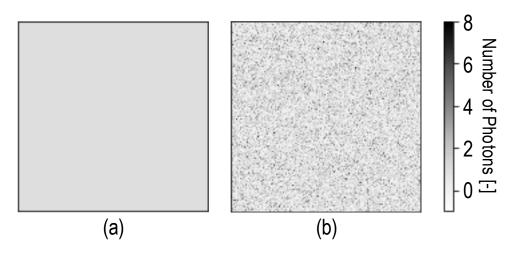

| 4.1  | A noiseless image in (a) and one affected by PSN with average number of photons per pixel equal to 1                                                                                                                                                         | 66       |

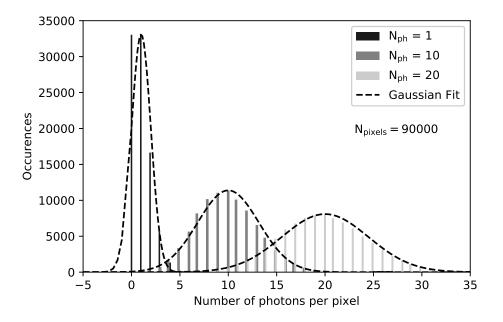

| 4.2  | Histogram of the average number of photons per pixel assuming an average inci-                                                                                                                                                                               | 00       |

| 4.2  | dent photon per pixel equal to 1, 10 and 20, respectively. A Gaussian distribution                                                                                                                                                                           |          |

|      | fits the Poisson distribution well at a large value of incident photons.                                                                                                                                                                                     | 67       |

| 4.0  |                                                                                                                                                                                                                                                              | 67       |

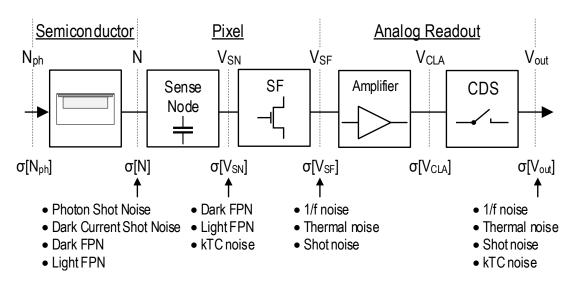

| 4.3  | Block diagram of a CIS digital camera with an average number of photons as                                                                                                                                                                                   |          |

|      | input and an analog output. Each block in between implements the transfer                                                                                                                                                                                    | <u> </u> |

|      | function related to the semiconductor, pixel and readout circuits.                                                                                                                                                                                           | 68       |

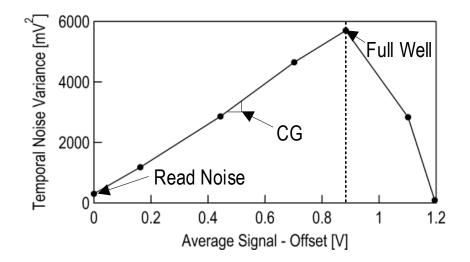

| 4.4  | Measured PTC curve from the readout chain detailed in Chapter 6. The main                                                                                                                                                                                    | <u> </u> |

| 4 5  | information that can be extracted from a PTC curve is indicated in the figure.                                                                                                                                                                               | 69       |

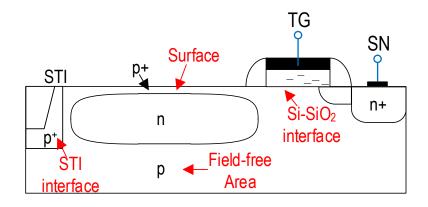

| 4.5  | Cross-section of the PPD together with the TG and the SN. The main sources of                                                                                                                                                                                |          |

|      | dark current are shown: the STI interface, the field-free area, the surface states                                                                                                                                                                           | 70       |

|      | and the interface between the semiconductor and the oxide                                                                                                                                                                                                    | 70       |

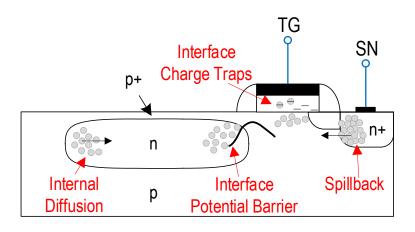

| 4.6  | Cross-section of the PPD together with the TG and the SN. The main sources                                                                                                                                                                                   |          |

|      | of CTI are numbered as follows: (1) the diffusion inside PPD, (2) the potential                                                                                                                                                                              |          |

|      | barrier at the interface, (3) the charge trapping at interface states and (4) the                                                                                                                                                                            |          |

|      | spillback.                                                                                                                                                                                                                                                   | 71       |

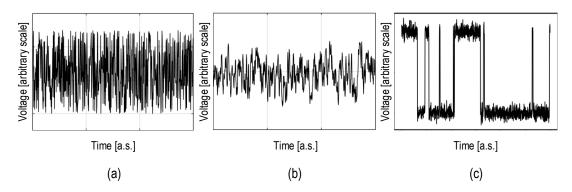

| 4.7  | Simulated waveforms with a dominant thermal noise in (a), only 1/f and thermal                                                                                                                                                                               |          |

|      | noise in (b) and a dominant RTS noise in addition to thermal noise in (c).                                                                                                                                                                                   | 72       |

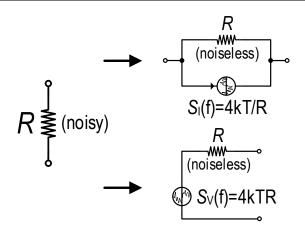

| 4.8  | Equivalent circuit for thermal noise in a resistor: noise current generator in                                                                                                                                                                               |          |

|      | parallel to the resistor and noise voltage in series.                                                                                                                                                                                                        | 73       |

| 4.9  | Equivalent circuit for noise of a MOS transistor: noise current generator between                                                                                                                                                                            |          |

|      | drain and source of the transistor and noise voltage referred to the gate                                                                                                                                                                                    | 74       |

| 4.10 | RC circuit in (a) and equivalent circuit for noise calculation in (b)                                                                                                                                                                                        | 75       |

| 4.11 | RTS noise PSD with Lorentzian shape and corresponding drain current fluctua-                                                                                                                                                                                 |          |

|      | tions in the time domain for a small-area MOSFET (reprinted from [15])                                                                                                                                                                                       | 77       |

| 4.12 | Impact in (a) on a steady current of the shot noise and evolution in time of the                                                                                                                                                                             |          |

|      | number of cumulated charge carriers crossing the barrier (reprinted from [6]).                                                                                                                                                                               |          |

|      | In (b), noise spectrum and as a function of measured gate current of a MOSFET                                                                                                                                                                                |          |

|      | in 100 nm (reprinted from [22])                                                                                                                                                                                                                              | 78       |

| 4.13 | Gate leakage current components flowing between the SF terminals.                                                                                                                                                                                            | 79       |

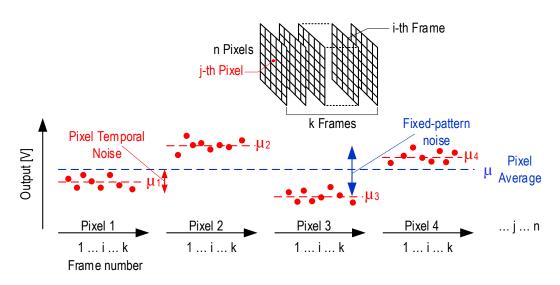

| 4.14       | Measurement methodology for Temporal and Fixed Pattern Noise (adapted from [24]).                                                                                                                                                                     | 81        |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

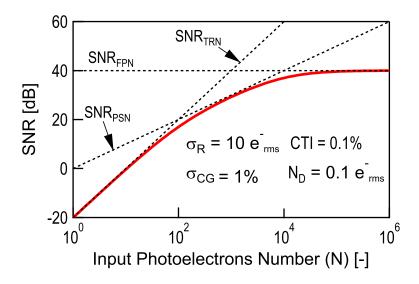

| 4.15       | Plotted in red, the total SNR as a function of the input photoelectrons number, <i>N</i> . In dashed lines, the SNRs which take into account only the TRN, the PSN and                                                                                |           |

|            | the FPN. These lines show the range of photoelectrons where each noise source is dominant.                                                                                                                                                            | 82        |

| 5.1        | Conventional CIS readout chain based on a intra-pixel source-follower amplifier<br>in (a). Timing diagram of a low noise CIS readout chain in (b) with the noise<br>contributions added to the signal. On the left, hydraulic model of a PPD with TG, | 02        |

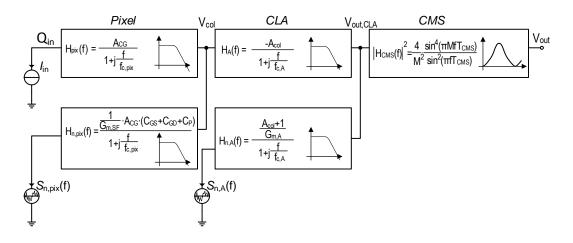

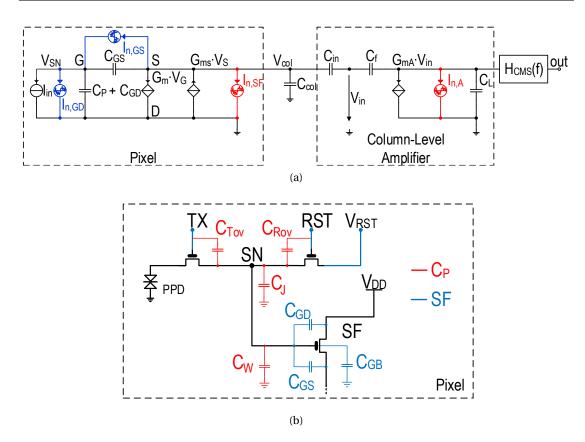

| 5.2        | SN and RST showing different readout steps                                                                                                                                                                                                            | 88        |

| 5.3        | each block                                                                                                                                                                                                                                            | 90        |

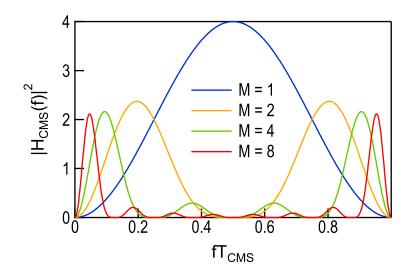

| 5.4        | the SN node term $C_p$<br>The term $ H_{CMS}(f) ^2$ as a function of the frequency normalized to the CMS sampling period $T_{CMS}$ , for four different values of the CMS order.                                                                      | 91<br>93  |

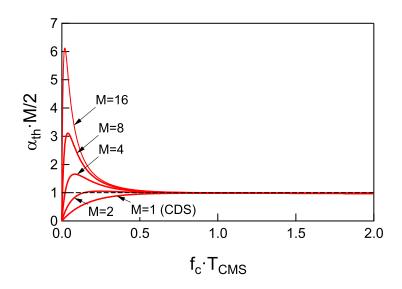

| 5.5        | The parameter $\alpha_{\text{th}}$ is multiplied by $M/2$ and plotted as a function of $f_{\text{c}} \cdot T_{\text{CMS}}$ for different values of $M$ .                                                                                              |           |

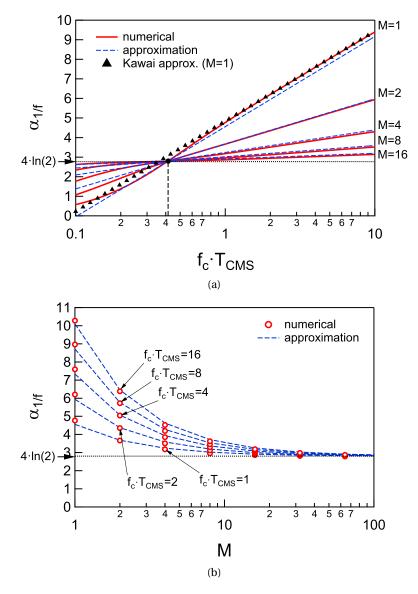

| 5.6        | $\alpha_{1/f}$ in (a) as a function of $f_c \cdot T_{\text{CMS}}$ for different values of $M$ . The same parameter is plotted in (b) as a function of $M$ to emphasize the plateau of the residual flicker                                            | 95        |

| F 7        | noise reduction with <i>M</i> .                                                                                                                                                                                                                       | 97        |

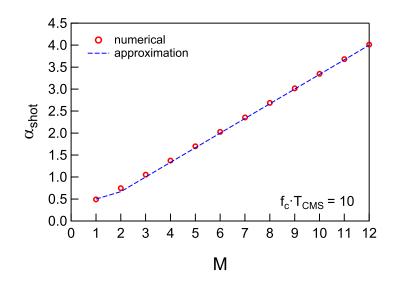

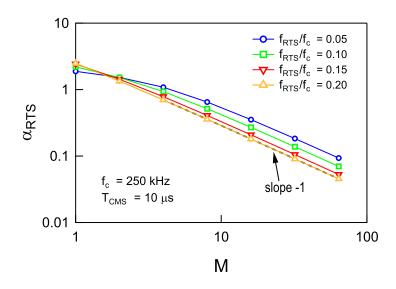

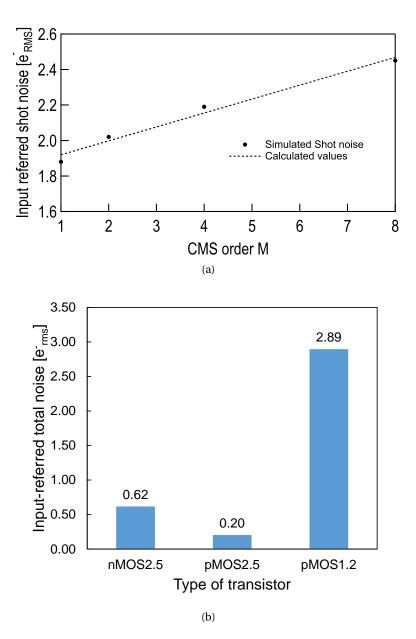

| 5.7<br>5.8 | The parameter $\alpha_{shot}$ is plotted as a function of $M$                                                                                                                                                                                         | 99<br>101 |

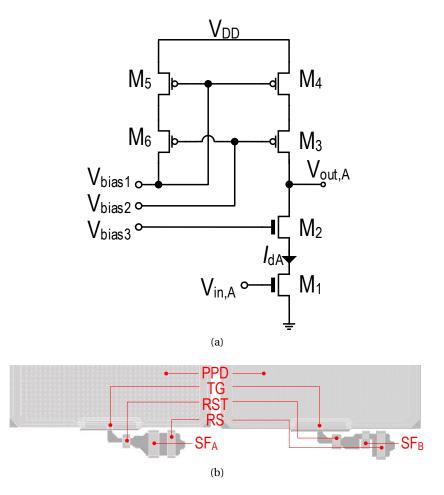

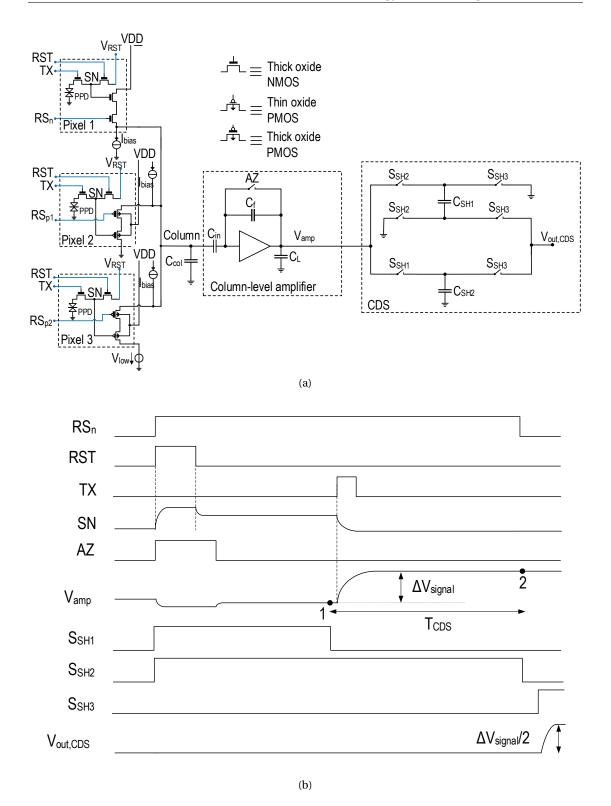

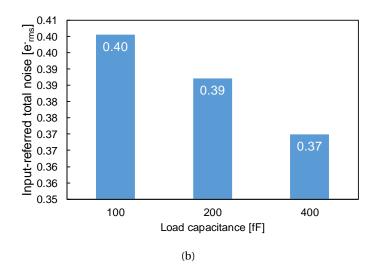

| 6.1        | Schematic in (a) of the implemented CIS readout chain with a 4T pixel, the capacitive amplifier and SC CMS. Timing diagram in (b) of the readout chain                                                                                                |           |

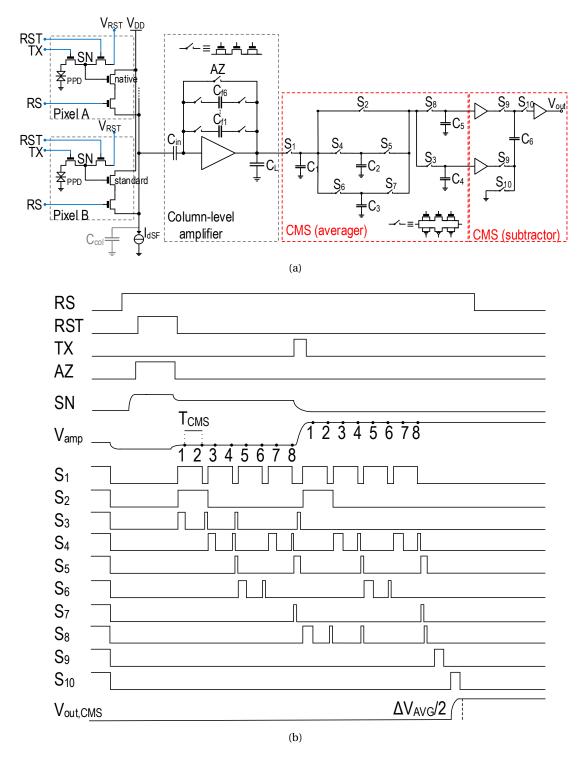

| <b>C D</b> | with all the control signals for the SC CMS for M equal to 8                                                                                                                                                                                          | 108       |

| 6.2<br>6.3 | SC CDS circuit implementation                                                                                                                                                                                                                         | 111       |

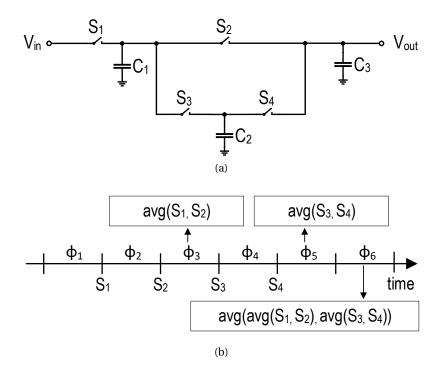

|            | operations for each phase.                                                                                                                                                                                                                            | 112       |

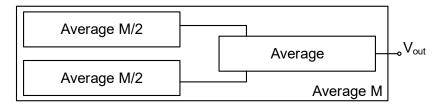

| 6.4        | Generic CMS order $M$ splitted into two blocks of order M/2 and a simple average                                                                                                                                                                      | :113      |

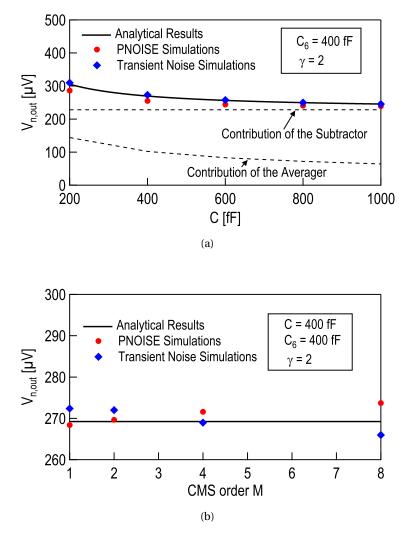

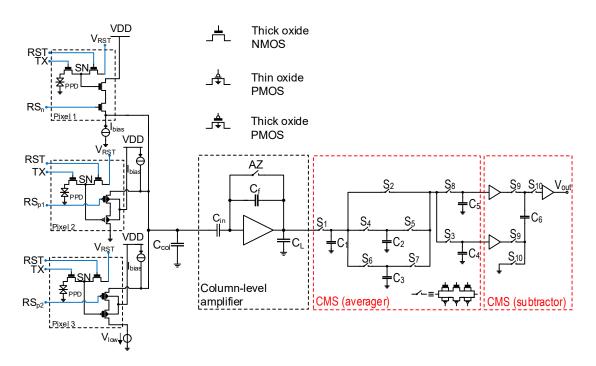

| 6.5        | Comparison between calculated results and PNOISE and transient noise simu-<br>lation results for different values of the averager capacitor (a) and various CMS                                                                                       |           |

| 6.6        | orders (b)                                                                                                                                                                                                                                            | 114       |

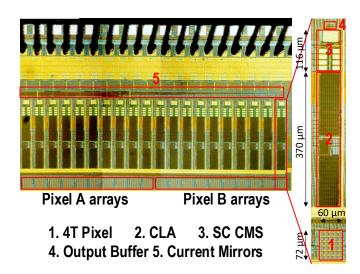

|            | pixels A and B with the PPD and the TG, RST, RS and SF transistors.                                                                                                                                                                                   | 115       |

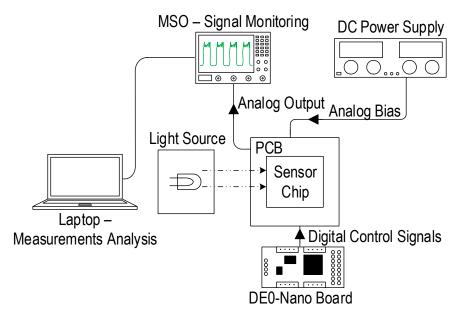

| 6.7        | Chip micrograph showing the main blocks of the readout chains with biasing circuits and buffers                                                                                                                                                       | 116       |

| 6.8  | Setup for the characterization and the noise measurements of the readout chains implemented on the chip.                                                                                                                                                                                                                                           | 117        |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

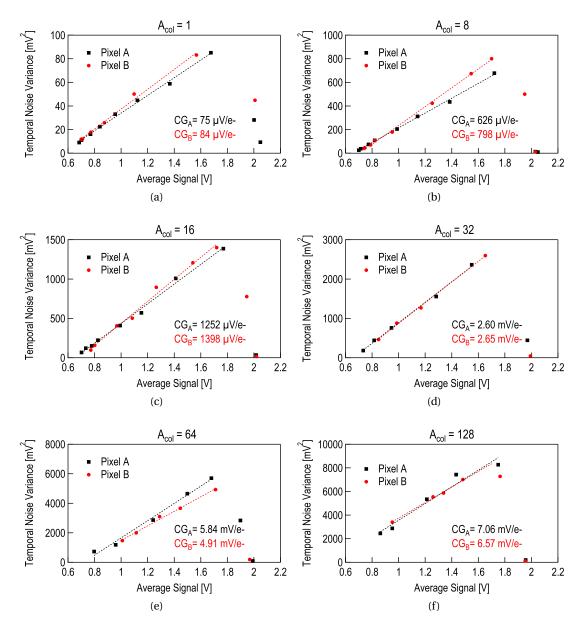

| 6.9  | PTCs of the readout chain for different values of the CLA gain (from 1 to 128), in order from (a) to (f). The overall <i>CG</i> is reported in each figure for both pixels.                                                                                                                                                                        | 118        |

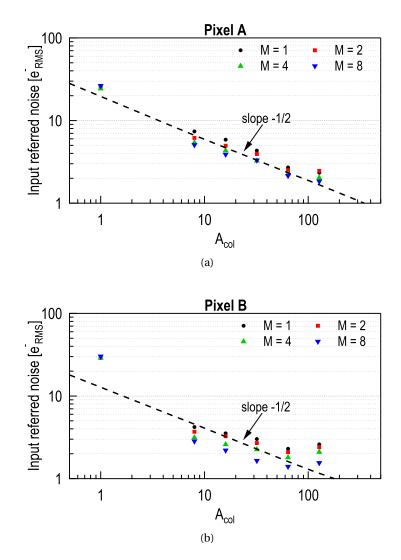

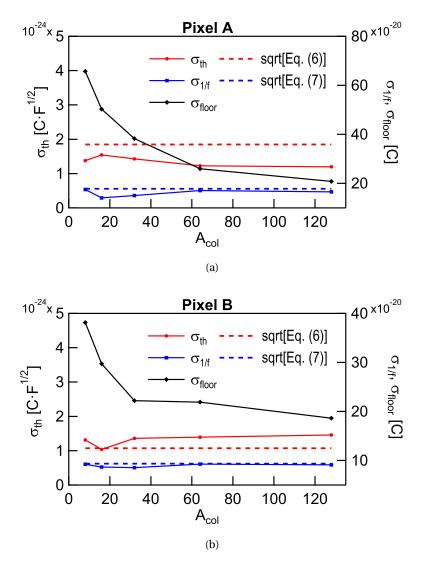

| 6.10 | Input-referred noise for both pixels as a function of the CLA gain value. The expected trend for thermal noise reduction is plotted with a dashed line                                                                                                                                                                                             |            |

| 6.11 | Input-referred total noise for Pixel A (a) and Pixel B (b) as a function of the CMS order M. The measurements are compared with the total noise expression                                                                                                                                                                                         | 115        |

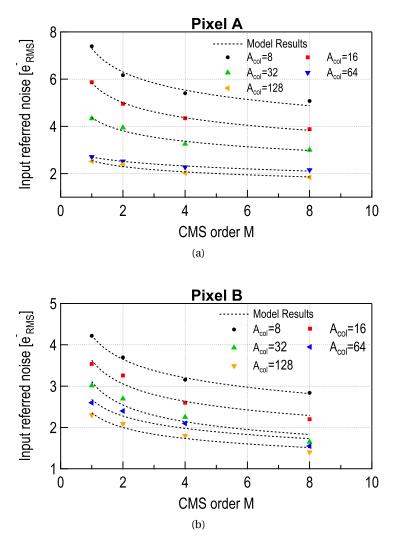

| 6.12 | proposed in (6.9)                                                                                                                                                                                                                                                                                                                                  | 120        |

|      | the right axis) is plotted for each value of the column-level gain for Pixel A (a) and Pixel B (b).                                                                                                                                                                                                                                                | 121        |

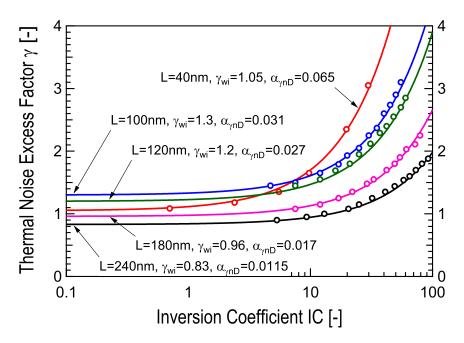

| 6.13 | Measured values of the thermal noise excess factor against IC for $L$ equal to 240 nm, 180 nm, 120 nm, 100 nm and 40 nm (reprinted from [21]).                                                                                                                                                                                                     | 123        |

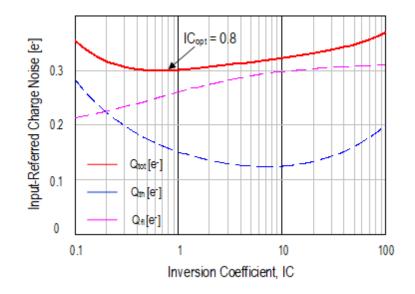

| 6.14 | Total, thermal and flicker RMS charge noise as a function of the SF IC coefficient.<br>In order to generate these curves, the following values are used for the main                                                                                                                                                                               | 120        |

|      | parameters: $C_{ox} = 4.5 \text{fF}\mu\text{m}^{-2}$ , $I_{spec\Box} = 500 \text{nA}$ , $C_{ex} = 0.45 \text{fF}\mu\text{m}^{-1}$ , $n = 1.2$ , $C_P = 0.75 \text{fF}$ , $\gamma_A = 1$ and $G_{mA} = 30 \mu\text{AV}^{-1}$                                                                                                                        | 124        |

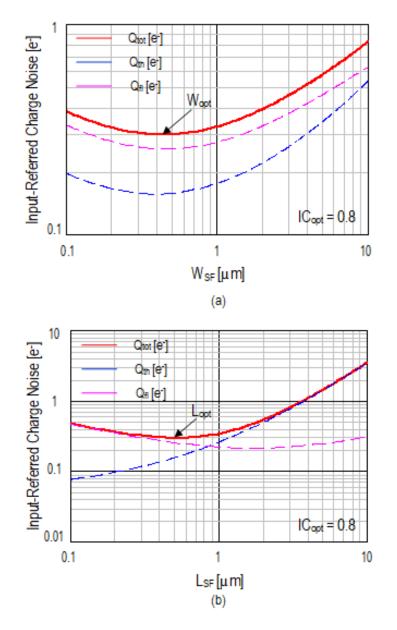

| 6.15 | Total, thermal and flicker RMS charge noise as a function of the SF width in (a) and length in (b). The following values are used for the main parameters: $C_{ox} = 4.5 \text{ fF} \mu \text{m}^{-2}$ , $I_{spec\Box} = 500 \text{ nA}$ , $C_{ex} = 0.45 \text{ fF} \mu \text{m}^{-1}$ , $n = 1.2$ , $C_P = 0.75 \text{ fF}$ , $\gamma_A = 1$ and |            |

| 6.16 | $G_{mA} = 30 \mu A V^{-1}$                                                                                                                                                                                                                                                                                                                         | 125        |

|      | in (b) of the simulated CIS readout chain                                                                                                                                                                                                                                                                                                          | 127        |

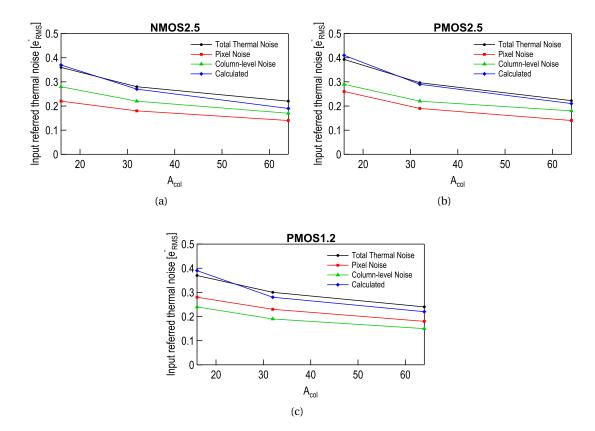

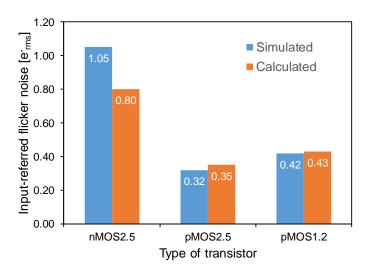

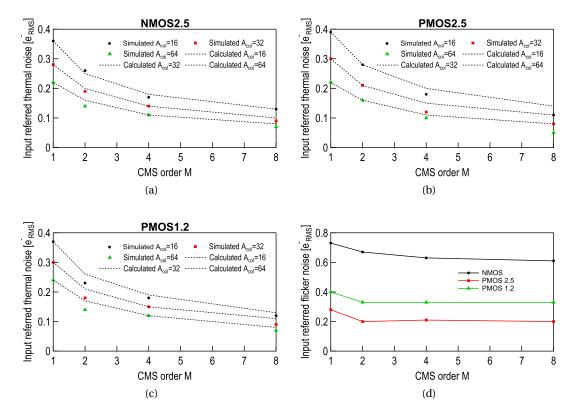

| 6 18 | pMOS2.5 in (b) and pMOS1.2 SF in (c), respectively, as function of the column-<br>level gain                                                                                                                                                                                                                                                       | 129        |

|      | with different type of in-pixel SFs.                                                                                                                                                                                                                                                                                                               | 130        |

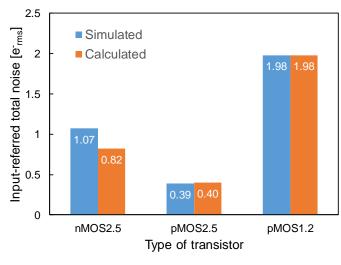

| 6.19 | Input-referred total noise in (a) of the readout chain with nMOS2.5, pMOS1.2<br>and pMOS2.5 SF, respectively. Input-referred total noise of the readout chain                                                                                                                                                                                      | 101        |

| 6.20 | with pMOS2.5 SF as a function of the load capacitance in (b)                                                                                                                                                                                                                                                                                       | 131<br>132 |

| 6.21 | Input-referred thermal noise of the CIS readout chain with nMOS2.5 (a), pMOS2.5 (b) and pMOS1.2 (c) SF, respectively, as function of the column-level gain and                                                                                                                                                                                     |            |

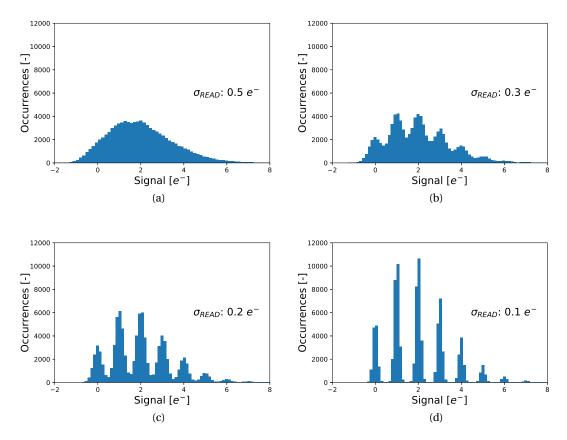

| 6.23 Simulated histogram from (a) to (d) showing the influence of different readout  |     |

|--------------------------------------------------------------------------------------|-----|

| noise levels on the output of an image sensor for an average number of 2 photons     |     |

| per pixel                                                                            | 136 |

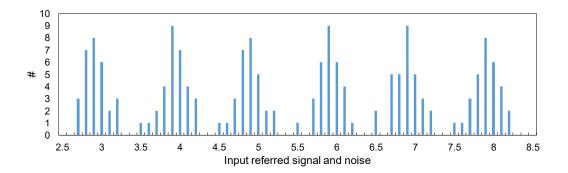

| 6.24 Histogram of the output signal voltage for 6 different inputs: results from the |     |

| transient noise simulations of the readout chain in 65 nm with pMOS2.5 SF. $$ .      | 136 |

# List of Tables

| 3.1 | Main Parameters for Three Cases of Pinned Photodiodes                          | 42  |

|-----|--------------------------------------------------------------------------------|-----|

| 3.2 | Summary of Values for Model Parameters                                         | 59  |

|     |                                                                                |     |

| 6.1 | Summary Table for Noise Reduction Techniques                                   | 107 |

| 6.2 | Values of the Process and Design Parameters                                    | 122 |

| 6.3 | Relevant parameters for noise estimation and calculated input-referred flicker |     |

|     | noise                                                                          | 126 |

## **1** Introduction

This chapter begins with a brief history of CMOS Image Sensors (CIS), starting from the first work in the 1960s to modern achievements. The major trends in camera and camera systems are then presented and followed by an overview of the state-of-the-art in Ultra-Low Light CIS. Finally, the motivation for the work is provided and the organization of the manuscript outlined.

### 1.1 Brief History of CIS

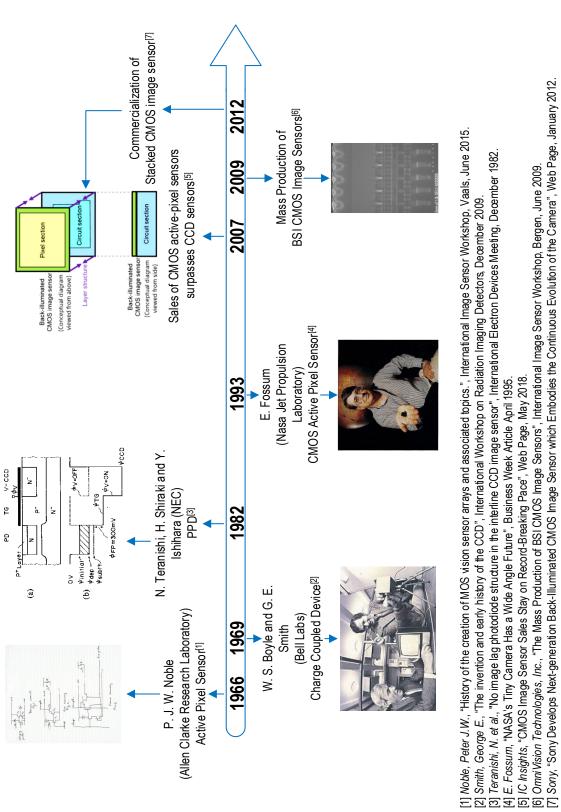

The history of CIS is full of brilliant work and contributions from engineers and scientists all over the world [1]. This section aims to give a brief historical overview by mentioning some of the most important contributions to the development of modern sensors. A timeline with some ground breaking research is shown in Fig. 1.1.

Modern image sensors are based on metal-oxide-semiconductor (MOS) technology, a result of the MOS field-effect transistor (MOSFET) invented at Bell Labs in 1959 [2]. In the developed fabrication processes, two different type of MOS were available: the PMOS (p-type MOS) and the NMOS (n-type MOS).

In 1966, the first generation of optical sensor arrays was reported in the UK by Peter Noble of the Allen Clarke Research laboratory (Plessey), where the first self-scanned  $10 \times 10$  sensor was implemented and the concept of an intra-pixel amplifier (active pixel) introduced [3]. At the new company set up by Noble, Integrated Photomatrix Ltd., a  $64 \times 64$  array (4096 pixels) was implemented to be used in a monochrome camera for moving objects.

The development of semiconductor technology led to the invention of a charge-coupled device (CCD) in 1969 by Williard Boyle and George E. Smith at Bell Labs. While researching the use of MOS technology for electronic shift register [4], the basic building block of the CCD was created: the MOS capacitor. The two researchers realized in fact that a charge could be stored on a MOS structure. One of their colleagues, Michael F. Tompsett, noticed the potential of the CCD device for imaging applications [5]. For the imaging semiconductor circuit, Boyle and

Figure 1.1: A summary history of CIS with the crucial events reported in a timeline: from the early development stages of technology to modern designs.

**Chapter 1. Introduction**

Smith were awarded the Nobel Prize Physics in 2009. CCDs had in fact an important impact on astronomy and were mounted on spacecraft to take images during robotic explorations of space [6].

Digital cameras and camcorders in the 1980s and 1990s embedded CCD sensors, which were industrialized and went into mass production in Japan [6]. The storing elements in CCDs are combined with electrodes positioned on top of an insulating material and on the surface of the semiconductor. They are used to apply a sequence of voltages and move the stored charges underneath from one element to the next. This image sensor works as a shift register for the photogenerated charge, until it reaches the corner of the chip where an amplifier is located. Based on their operational principle, CCDs require a nearly perfect charge transfer in order to avoid the so-called image lag. However, this property was difficult to obtain for large array sizes used at high frame rates and the electronics required to drive the sensor meant the final design was large and bulky.

The demand for more compact systems was one source of motivation for looking into new different solutions, and the integration in a CMOS process was the key to miniaturization. In order to achieve this goal, Eric Fossum at JPL built the first camera-on-chip in 1993 by replacing the multiple charge transfers with a single intra-pixel complete transfer and the output amplifier of a CCD with an intra-pixel one [7]. In this system, the output was sampled twice: once during the reset level and the other after the transfer of the photogenerated charge. The final output was the difference between the two measurements and the operation was called correlated double sampling (CDS). The technique was introduced to suppress the variance of transferred charges to a capacitor due to the Brownian motion of charge elements, also referred as kTC noise.

One of the key elements in modern CIS is the pinned photodiode (PPD), invented by Nobukazu Teranishi, Hiromitsu Shiraki and Yasuo Ishihara at the NEC Corporation in 1980 and published in 1982 [8]. The main advantages of this device were the lower lag, noise and dark current compared to conventional photodiodes, together with a higher quantum efficiency. At the beginning, the PPD was incorporated into CCD sensors in all consumer electronic cameras. By the time CMOS technology had surpassed CCD in the market sales [9], PPDs were being used in nearly all CISs.

The continuous growth in the camera industry led to the advent of large arrays in CIS with power consumption levels lower than CCD sensors. In 2009, Sony commercialized the CMOS back-side illumination (BSI) that further optimized the sensor in terms of quantum efficiency [10]. In 2012, the same company introduced the stacked CMOS BSI sensor opening to higher integration with electronic circuits [11]. The design of modern CISs is driven by the smartphone market and combines advanced chip stacking techniques with active pixels arrays embedding the latest 0.8 µm pixel generation into multiple camera systems [12].

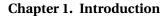

Figure 1.2: CIS market growth in (a) from 2016 to 2019 with forecasts up to 2025. The positive trend is expected to continue in the upcoming years (source: Yole Développement). Worldwide number of shipped image sensors in (b) according to IC Insights.

### 1.2 CIS Market and Major Trends

The considerable spread of CIS had a significant cultural impact: smartphone cameras and digital cameras are now part of our daily life. The rise of social media and selfie culture is linked to the spread of this technology, with social and political effects on people around the world.

In 2017, CMOS sensors accounted for 89% of the global image sensor market [9]. Yole Dévelopment published the results of CIS market dynamics (Fig. 1.2(a)) with annual confirmed revenues from 2016 to 2019, and a forecast from 2020 to 2024 [13]. The continuous growth of

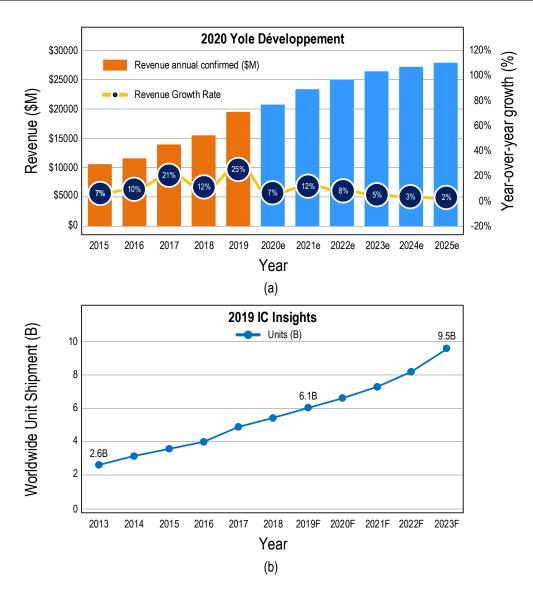

Figure 1.3: Modern trends described in [14] that involve image sensors and camera designs: multicamera systems in (a), high resolution arrays in (b), 3D sensing in (c) and biometric ID based on iris-scanner in (d) (source: Daiwa Capital Markets).

CIS produced an annual revenue of US\$ 19.3b in 2019, exceeding 4.6% of total semiconductor sales. The revenues are expected to continue growing and exceed US\$ 27.5 billion in profits. According to IC Insights and as shown in Fig. 1.2(b), 6.1 billion image sensors are shipped worldwide each year (193 per second) [1, 9].

The smartphone sales (estimated global revenue of US\$ 522 billion in 2018 [15]) is the main driving force of the CIS market. A summary of the main modern trends involving image sensors and camera designs is shown in Fig. 1.3 and extensively described in [14].

The multi-camera era represented in Fig. 1.3(a) started with the adoption of dual-cam smartphones and is now turning into triple and quad-cam systems with enhanced camera functions for image quality. The major benefits of multiple cams include higher optical zoom compared to dual-cams, broader angle, better image quality in low-light environment, enhanced functionality for Artificial Intelligence (AI) (e.g. face, objects and scenes detection and recognition) and auto adjustments of multiple parameters for optimum image output. As predicted in [14], a broader adoption of multiple cams in smartphones is expected during the course of 2020.

Smartphone cameras have also migrated towards higher resolution (from tens to hundreds of mega-pixels) incorporating pixels with a sub-micrometer distance from each other (pixel pitch) [12]. More imaging functions are possible by equipping phones with these state-of-the-art image sensors at the cost of a more complicated design. As shown in Fig. 1.3(b), the

lphone 11

Samsung Galaxy S20 Ultra

Figure 1.4: Frames from advertisement in 2020 of the top smartphones of Apple and Samsung, respectively, involving good performances at low-light levels to appeal to consumers.

reduced pixel size allows in fact less light to be captured and longer focal length and results in a higher thickness for the camera module.

In addition, the leading companies in the market are developing 3D sensing modules to provide 3D features such as gesture or facial recognition [16]. The newly-developed modules consist of a receiver and a transmitter to project and receive light. Fig. 1.3(c) shows the main approaches to 3D sensing: structured light, time of flight (ToF) and stereo systems. Applications for this technology include augmented reality (AR), face and gesture recognition, 3D scanning and mobile payments.

Modern smartphone have adopted biometric ID technology for the iris recognition performed by an extra front camera processing the eye images, as drawn in Fig. 1.3(d) and detailed in [17].

### 1.3 Ultra-Low Noise CIS – an Overview

Ultra low noise CIS are fundamental to reaching high performance in low light imaging for applications such as surveillance, security, night vision and consumer electronics [18, 19, 20], where a good low light performance is crucial. The feature of high sensitivity is also very useful in applications like microscopy, high-precision scientific imaging and 3D vision based on indirect-Time-of-Flight (I-ToF) imagers [21, 22, 23]. As shown in Fig. 1.4, Apple and Samsung (who were reported to capture 56% of all smartphone industry revenues in 2019 [24]) use low-light performance (or night vision) as a key feature of their devices and advertising strategy to appeal to consumers. Hence, both industry and scientific institutions are interested in an image sensor that not only needs to exhibit an incredibly low value of noise, but also offers at the same time a high resolution and speed.

As shown in Fig. 1.5, the current state-of-the-art in low noise CIS exhibits sub-electron inputreferred total noise, which represents a step towards the single photon detection capability for these sensors. The additive readout noise e.g. 1 or 2  $e_{rms}^-$  was in fact responsible for the not

Figure 1.5: Values of input-referred read noise in articles published from 2003 to 2020 and reported in the references of this chapter. A large amount of research reached the sub-electron noise value, while the level for a photoelectron counting error lower than 0.1% ( $0.15 e_{rms}^{-}$ ) is very close in recent publications.

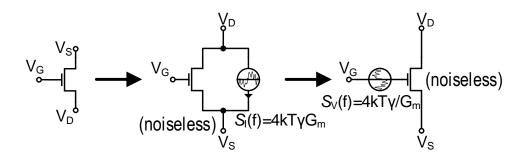

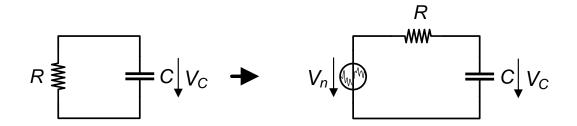

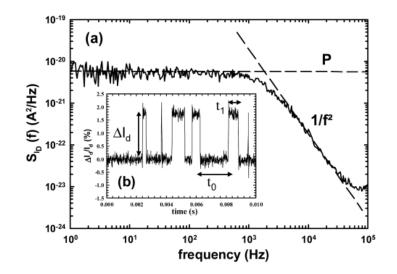

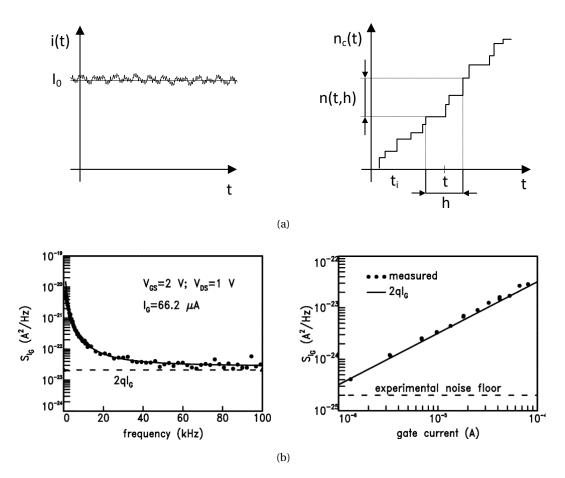

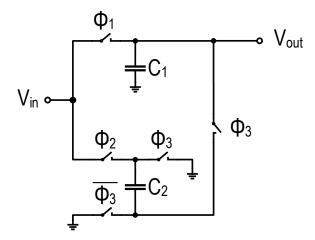

visible quantized nature of the input light in a standard camera output.