Thèse n°7410

# EPFL

### AlGaN/GaN Nanowires: from Electron Transport to RF Applications

Présentée le 15 septembre 2020

à la Faculté des sciences et techniques de l'ingénieur Laboratoire de dispositifs semiconducteurs de puissance Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

### Giovanni SANTORUVO

Acceptée sur proposition du jury

Prof. L. G. Villanueva Torrijo, président du jury Prof. E. D. N. Matioli, directeur de thèse Prof. K. Ensslin, rapporteur Prof. M. Meneghini, rapporteur Prof. N. Grandjean, rapporteur

It is about how hard you can get hit and keep moving forward, how much can you take and keep moving forward. That's how winning is done!

Nessuno può colpire duro quanto può colpire la vita, perciò andando avanti non è importante come colpisci, l'importante è come sai resistere ai colpi, a come incassi e se finisci al tappeto hai la forza di rialzarti! (Doppiaggio italiano)

- Rocky Balboa (Sylvester Stallone)

Alla mia famiglia...

## Acknowledgements

It would take an entire chapter to properly and fairly thank all the people that have helped me in this not easy travel but, I will try to be concise. First of all, I would like to thank my supervisor prof. Elison Matioli for having accepted me in his lab, having placed his trust in me in a crucial moment of his carrier (I was one of his first students) and for all the knowledge and skills he taught me. I also thanks prof. Klaus Ensslin, prof. Nicolas Grandjean and prof. Matteo Meneghini for having revised this work and being present to my doctoral exam.

Though it is not a common acknowledgment, I would like to thanks all the teachers of my life. There is no better time than this, me not be a student anymore, to thanks all the people that have educated me.

A big thanks goes also to my colleagues. In particular, I thank Muriel (the administrative assistant of my lab) for all the help in the paper work (especially for personal issues), Jun for all his answers to my GaN-related questions, and Catherine for all the deep semiconductor-physics discussions and the long collaboration. A big thanks goes to Reza, Luca, George, Riyaz, Remco e Nirmana for both job-related discussions and all the fun time spent together. I also thank all the experts of CMi and IPHYS (the EPFL clean rooms).

I thank a lot my friends in Bitonto (my home town) and especially Giuseppe (one of my biggest supporter!), Francesco and Viviana. Despite the distance and the low frequency at which we see each other, they never forget about me and they always organize cool things when I am back.

A huge thanks goes to my girlfriend Ilaria. She has contagious happiness (which is the meaning of her name) and a beautiful voice (and several funny voices she makes up) that would cheer me up after every bad day (and there were a lot when working in the clean room). She was supportive and she made my living abroad much lighter (I have become more and more homesick).

To conclude, a thanks expanding more than the universe goes to my family: my father Raffaele, my mother Anna and my two younger brothers Donato and Francesco. I think that, independently from how smart you are, without perseverance, sacrifice and patient it is not easy to achieve any good results. For these, and many more, values I thank my parents. This PhD is also yours.

Lausanne, 2 December 2019

Giovanni Santoruvo

## Ringraziamenti

Penso che mi servirebbe un itero capitolo per ringraziare tutti propriamente, tuttavia cercherò di essere conciso. Prima di tutti, vorrei ringraziare il mio relatore di tesi, prof. Elison Matioli, per avermi scelto per il suo laboratorio, per aver riposto in me la sua fiducia in un momento cruciale della sua carriera (sono stato uno dei suoi primi studenti) e per tutto ciò che mi ha insegnato. Ringrazio anche i professori Klaus Ensslin, Nicolas Grandjean e Matteo Meneghini per aver revisionato questo lavoro e per essere stati presenti al mio esame finale di dottorato.

Nonostante non sia un ringraziamento comune, vorrei ringraziare tutti gli insegnanti della mia vita. Non c'è momento migliore di questo, la fine del mio percorso di studi, per ringraziare tutte le persone che mi hanno formato.

Un grande ringraziamento va anche a tutti i miei colleghi. Ringrazio specialmente Muriel (la nostra assistente amministrativa) per tutto l'aiuto nelle faccende burocratiche (spesso anche personali), Jun per tutti i dubbi chiariti riguardo il GaN, e Catherine per la nostra lunga collaborazione e per tutte le profondi discussioni legate al mondo della fisica e dei semiconduttori. Un sentito ringraziamento va a Reza, Luca, George, Riyaz, Remco e Nirmana sia per tutte le nostre conversazioni lavorative che per tutti i momenti divertenti passati insieme fuori dal lavoro. Ringrazio anche tutti gli esperti che operano nelle camere pulite dell'EPFL (CMi e IPHYS).

Ringrazio enormemente i miei amici di Bitonto (la mia città natale), specialmente Giuseppe (che non ha mai perso l'occasione di dimostrare quanto tenesse a me e alla mia carriera!), Francesco e Viviana. Nonostante la distanza e il fatto che non avessimo modo di vederci spesso, non si sono mai dimenticati di me e hanno sempre cercato di passare quanto più tempo possibile con me ogni volta che tornavo a casa.

Un immenso grazie va alla mia ragazza Ilaria. Lei possiede un'allegria contagiosa e una bellissima voce (per non parlare di tutte le sue vocine super divertenti) che mi hanno tirato su di morale in tutti quei giorni non proprio positivi (che non mancavano, specialmente quando lavoravo in camera pulita). Il suo sostegno non è mai mancato e vivere con lei mi ha aiutato a prendere con più leggerezza la mia vita da "espatriato" (sto diventando sempre più nostalgico dell'Italia).

Per finire, un grazie che si espande più dell'universo va alla mia famiglia: a mio padre Raffaele, a mia madre Anna e ai miei due fratelli Donato e Francesco. Io penso che una persona, per quanto intelligente possa essere, senza perseveranza, sacrificio e pazienza difficilmente riuscirà a raggiungere i suoi obiettivi. Per questi valori, e per molti altri, ringrazio i miei genitori. Questo dottorato è anche vostro.

Losanna, 2 dicembre 2019

Giovanni Santoruvo

## Abstract

Gallium Nitride (GaN) and all III-Nitride compounds have revolutionized the world with the development of the blue light emitting diode (LED). In addition, GaN-based epi-structures, such as AlGaN/GaN, enable the fabrication of high electron mobility transistors (HEMTs) for several applications handling high power. In the radio frequency (RF) domain, power amplifiers (PAs) based on GaN HEMTs are currently used for base stations, radars and, in the future, will replace low power amplifiers, currently made with silicon, ensuring much smaller footprint and reduced cost.

Despite the presence of several commercial GaN HEMT-based devices, performances, especially in frequency, are quite far from the predicted theoretical limits. A lot of research focuses in using etched AlGaN/GaN HEMT nanowires (NWs) as channel for ultrascaled metal semiconductor field-effect transistors (MESFETs) to reduce short channel effects, arising when shrinking the gate length to increase the operating frequency, and linearity issues.

In this thesis, we perform a transverse study of AlGaN/GaN NWs starting from the investigation of electron transport and ending with the proposal of new device architectures for improved device performance.

Electron transport is studied in mesoscopic devices based on GaN HEMT NWs. Ballistic transport is observed even at room temperature and at large bias, thanks to the high mobility of electrons and large optical phonon energy. Quenched Hall effect and quantum physics phenomena due to phase coherence are observed at cryogenic temperature under a strong magnetic field. Finally, the sidewall depletion width, an important parameter for designing devices based on NWs, of AlGaN/GaN is extracted, resulting in one of the smallest values (19.5 nm) among all III-V HEMTs.

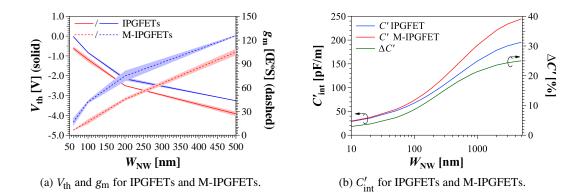

Due to the increased parasitic capacitance in NW-based MESFETs, we also explored more exotic gating techniques consisting of side and in-plane gates (IPGs). IPGFETs and metal IPGFETs (M-IPGFETs) are fabricated, characterized and simulated. A record current density of 1.4 A/mm and transconductance of 665 mS/mm are measured, together with a breakdown voltage larger than 300 V. Simulations of the device capacitance yield values as low as few aF, resulting in possible cut-off frequencies up to 0.89 THz. Such value, together with the large breakdown voltage, push GaN IPGFETs beyond the theoretical limit of GaN for RF applications and paves the way for future device architectures.

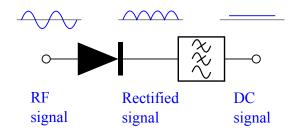

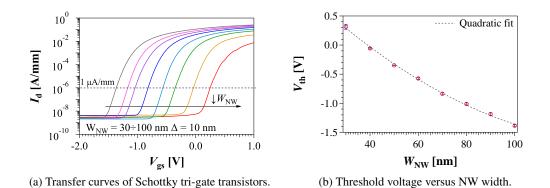

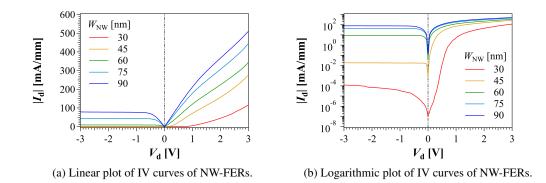

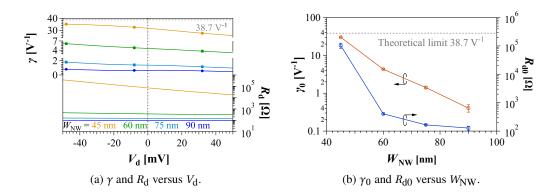

NWs are also used to noticeably improve performance of zero-bias RF detectors. We developed for the first time a field-effect rectifier (FERs) where the channel is constituted by an array of GaN-HEMT etched NWs. The much better gate control over NWs resulted in a current curvature

#### Abstract

$(30.1 V^{-1})$  close to the theoretical limit of Schottky diodes  $(38.7 V^{-1})$ . The cut-off frequency of these devices is up to 140 GHz, which, together with the large measured responsivity (3000 V/W), make NW-FERs very promising for stand-alone applications as well as for integration in GaN Monolithic Microwave Integrated Circuits (MMICs) for improving overall performance and add new applications.

Key words: HEMT, Ballistic transport, III-Nitride, Microwave detection, Nanowires, Quantum effect, RF transistor, Side gate

## Riassunto

Il nitruro di gallio (GaN) e tutti i nitruri basati su elementi appartenenti alla quinta colonna della tavola periodica hanno rivoluzionato il mondo con lo sviluppo dei LED (in inglese light emitting diode) blu. In aggiunta, strutture epitassiali basate sul GaN, hanno permesso la realizzazione di transistor con elettroni ad elevata mobilità (in inglese high electron mobility transistors, HEMT) per diverse applicazioni ad alta potenza. Nel campo delle radio frequenze (RF), gli amplificatori di potenza basati su GaN HEMT sono attualmente utilizzati nelle stazioni radio, radar e, in futuro, sostituiranno anche gli amplificatori a più bassa potenza, attualmente fabbricati in silicio, assicurando dimensioni e costi ridotti.

Nonostante la presenza sul mercato di diversi dispositivi basati su GaN HEMT, le prestazioni, specialmente in frequenza, sono ancora lontane dai valori predetti teoricamente. Molta ricerca è focalizzata sull'uso di nanowire (NW, letteralmente fili di dimensioni nanometriche) incisi partendo da dei wafer di AlGaN/GaN HEMT. Questi NW costituiscono il canale per transistor a effetto di campo basati su giunzioni metallo-semiconduttore, con lo scopo di ridurre gli effetti di canale corto, necessario per aumentare la massima frequenza operativa, e ridurre i problemi di non linearità.

In questa tesi, abbiamo studiato trasversalmente i nanowire basati su AlGaN/GaN iniziando con lo studio di trasporto di elettroni in queste strutture e finendo con delle proposte riguardanti nuove architetture al fine di migliorarne le prestazioni di dispositivi operanti nel campo RF.

Il trasporto degli elettroni è stato studiato in dispositivi mesoscopici basati sui NW di GaN HEMT. Il moto balistico degli elettroni è stato osservato sia a temperature criogeniche (4 K o -269.15 °C) che a temperatura ambiente a elevate tensioni di alimentazione, grazie all'alta mobilità degli elettroni e alla notevole energia richiesta per generare fononi ottici. L'appiattimento dell'effetto Hall (Quenched Hall effect) e fenomeni quantistici legati alla correlazione di fase degli elettroni sono stati osservati a temperature criogeniche e sotto l'effetto di forti campi magnetici. Per concludere, la larghezza di deplezione laterale, un importante parametro per progettare dispositivi basati sui nanowire, è stata estratta ottenendo uno dei valori più piccoli (19.5 nm) ottenibile in qualsiasi HEMT.

Per ridurre le capacità parassite e problemi di trappole nel semiconduttore quando si usano nanowire, abbiamo esplorato la possibilità di controllare il canale lateralmente. Lo studio è iniziato da dispositivi a singolo nanowire con gate complanare (in-plane gate field-effect transistors IPGFETs). Valori record sia di corrente, 1.4 A/mm, che di transconduttanza, 665 mS/mm, sono stati misurati per questi dispositivi. Inoltre, considerando i valori di capacità simulati (pochi aF), delle frequenze di taglio fino 0.89 THz dovrebbero essere raggiungibili. A

#### Riassunto

ciò si aggiunge anche un valore estremamente alto per la tensione di rottura del dispositivo di 300 V. Questi parametri sono stati in seguito migliorati tramite trattamenti chimici e usando gate metallici (metal-IPGFET). Questi ultimi, in particolare, permettono anche di ridurre la resistenza di gate e rendono i M-IPGFET ideali per fabbricare dispositivi con più nanowire in parallelo, al fine di aumentare la potenza in uscita.

I nanowire sono stati anche utilizzati per migliorare le prestazioni di rilevatori di potenza RF non polarizzati (nessuna alimentazione è richiesta per il funzionamento). Abbiamo creato per la prima volta un rettificatore a effetto di campo (field-effect rectifier, FER) che utilizza una stringa di nanowire incisi su un wafer di GaN-HEMT. Grazie al miglior controllo della corrente nei nanowire, abbiamo raggiunto valori di curvatura di corrente ( $30.1 V^{-1}$ ) vicini al limite teorico previsto per i diodi Schottky ( $38.7 V^{-1}$ ). La frequenza di taglio di questi dispositivi arriva fino a 140 GHz insieme a un'elevata responsività misurata di 3000 V/W. Tale combinazione di prestazioni rende questi dispositivi molto promettenti sia per applicazioni semplici che per l'integrazione in circuiti monolitici a microonde (Monolithic Microwave Integrated Circuits, MMICs) basati su GaN per migliorarne le prestazioni e aggiungere nuove funzionalità.

# **Symbols and Acronyms**

### Symbols

| Symbol          | Quantity                         | Measurement unit or value                                  |

|-----------------|----------------------------------|------------------------------------------------------------|

| a               | Lattice constant                 | Å                                                          |

| В               | Magnetic field                   | Т                                                          |

| β               | Responsivity                     | V/W                                                        |

| Bw              | Frequency bandwidth              | Hz                                                         |

| CTE             | Coefficient of thermal expansion | $K^{-1}$                                                   |

| $\Delta a$      | Lattice mismatch                 | %                                                          |

| $\Delta\lambda$ | Thermal mismatch                 | %                                                          |

| DIBL            | Drain induced barrier lowering   | mV/V                                                       |

| EOP             | Optical phonon energy            | eV                                                         |

| $E_F$           | Fermy energy                     | J                                                          |

| $\epsilon$      | Relative dielectric constant     |                                                            |

| $\epsilon_0$    | Vacuum dielectric constant       | $8.85 \times 10^{-12}$ F/m                                 |

| $f_{ m c}$      | Cutoff frequency                 | Hz                                                         |

| $G_0$           | Conductance quantum              | $\sim 80 \ \mu S$                                          |

| γ               | Current curvature                | $V^{-1}$                                                   |

| $\gamma_0$      | Current curvature at 0 V         | $V^{-1}$                                                   |

| $g_{ m m}$      | Transconductance                 | S                                                          |

| h               | Plank constant                   | $6.62 \times 10^{-34} \text{ m}^2 \text{kg/s}$             |

| $\hbar$         | Cut Plank constant               | $2.1 \times 10^{-34} \text{ m}^2 \text{kg/s}$              |

| Ir              | Reverse current                  | А                                                          |

| JFoM            | Johnson figure of merit          | MV/s                                                       |

| J               | Current density                  | A/m                                                        |

| $k_{\rm b}T$    | Boltzmann constant               | 1.38×10 <sup>23</sup> m <sup>2</sup> kg/ s <sup>2</sup> /K |

| λ               | Thermal coefficient              | W/cm/K                                                     |

| $l_{\rm c}$     | Cyclotron radius                 | nm                                                         |

| $L_{\rm G}$     | Gate length                      | nm                                                         |

| $l_{ m m}$      | Mean free path                   | nm                                                         |

| $l_{\phi}$      | Phase coherence length           | nm                                                         |

| M               | Number of modes                  |                                                            |

| $m^*$           | Effective mass                   | kg                                                         |

| $\mu$           | Mobility                         | cm <sup>2</sup> /Vs                                        |

| NEP                    | Noise equivalent power          | $pW\sqrt{Hz}$             |

|------------------------|---------------------------------|---------------------------|

|                        | · ·                             | $cm^{-2}$                 |

| $n_{\rm s}$            | Sheet carrier concentration     | cm -                      |

| $P_{\text{in-RF}}$     | RF input power                  | dBm                       |

| $p_{\rm x}, p_{\rm y}$ | Momentum in x and y             | m <sup>2</sup> /s         |

| q                      | Electronic charge               | 1.602X10 <sup>-19</sup> C |

| $R_0$                  | Resistance quantum              | ~12.5 kΩ                  |

| R <sub>d</sub>         | Differential resistance         | Ω                         |

| $R_{\rm d0}$           | Differential resistance at 0 V  | Ω                         |

| RT                     | Room temperature                | 300 K                     |

| SS                     | Subthrehsold slope              | mV/dec                    |

| τ                      | Mean free time                  | S                         |

| Vbr                    | Breakdown voltage               | V                         |

| $v_{\mathrm{f}}$       | Fermi velocity                  | cm/s                      |

| V <sub>Jn</sub>        | Johnson (thermal) noise voltage | V                         |

| Von                    | Turn-on voltage                 | V                         |

| $v_{\rm sat}$          | Saturation velocity             | cm/s                      |

| $V_{\rm t}$            | Thermal voltage                 | V                         |

| $W_{\rm NW}$           | Nanowire width                  | nm                        |

| $w_{\rm sd}$           | Sidewall depletion width        | nm                        |

|                        |                                 |                           |

#### Acronyms

| Abbreviation | Full name                                         |

|--------------|---------------------------------------------------|

| 2DEG         | 2-Dimensional Electron Gas                        |

| AC           | Alternate Current                                 |

| BOE          | Buffered Oxide Etch                               |

| CMOS         | Complementary Metal Oxide Semiconductor           |

| DC           | Direct Current                                    |

| DI           | Deionezed water                                   |

| DUT          | Device under test                                 |

| EBL          | Electron-Beam Lithography                         |

| GND          | Ground                                            |

| HCl          | Cloridric acid                                    |

| HEMT         | High Electron Mobility Transistor                 |

| HSQ          | Hydrogen Silsesquioxane                           |

| ICP RIE      | Inductive coupled plasma reactive-ion             |

| KOH          | Potassium hydroxide                               |

| MESFET       | Metal-Semiconductor Field-Effect Transistor       |

| MMIC         | Monolithic Microwave Integrated Circuits          |

| MOSFET       | Metal Oxide Semiconductor Field-Effect Transistor |

| NW           | Nanowire                                          |

| PA           | Power Amplifier                                   |

| PMMA         | Polymethyl methacrylate                           |

| RF           | Radio Frequency                                   |

| RT           | Room Temperature                                  |

| RTP          | Rapid thermal process                             |

| SCE          | Short Channel Effect                              |

| TMAH         | Tetramethylammonium hydroxide                     |

| UCF          | Universal Conductance Fluctuations                |

| VNA          | Vector Network Analyzer                           |

| WL           | Weak Localization                                 |

|              |                                                   |

## Contents

| A  | cknow   | vledgements (English/Italian)                                               | i    |  |  |  |  |  |  |

|----|---------|-----------------------------------------------------------------------------|------|--|--|--|--|--|--|

| A  | bstrac  | et (English/Italian)                                                        | v    |  |  |  |  |  |  |

| Sy | mbol    | s and Acronyms                                                              | ix   |  |  |  |  |  |  |

| C  | onten   | ts                                                                          | xiii |  |  |  |  |  |  |

| Li | st of f | igures                                                                      | xvii |  |  |  |  |  |  |

| Li | st of t | ables                                                                       | xix  |  |  |  |  |  |  |

| 1  | Intr    | oduction                                                                    | 1    |  |  |  |  |  |  |

|    | 1.1     | Physical properties of Gallium Nitride for RF applications                  | 2    |  |  |  |  |  |  |

|    | 1.2     | Polarization and 2DEG formation                                             | 5    |  |  |  |  |  |  |

|    | 1.3     | GaN growth and substrates                                                   | 6    |  |  |  |  |  |  |

|    | 1.4     | MESFET based on GaN HEMTs: structure and operation                          | 8    |  |  |  |  |  |  |

|    | 1.5     | State of the art of RF devices based on GaN HEMT                            | 9    |  |  |  |  |  |  |

|    |         | 1.5.1 Commercial GaN HEMT devices                                           | 9    |  |  |  |  |  |  |

|    |         | 1.5.2 GaN HEMT research activity                                            | 10   |  |  |  |  |  |  |

|    |         | 1.5.3 GaN nanowires                                                         | 12   |  |  |  |  |  |  |

|    | 1.6     | Thesis outline                                                              | 13   |  |  |  |  |  |  |

| 2  | Ball    | istic transport in GaN nanowires                                            | 15   |  |  |  |  |  |  |

|    | 2.1     | Introduction                                                                | 15   |  |  |  |  |  |  |

|    | 2.2     | From diffusive to ballistic transport                                       | 15   |  |  |  |  |  |  |

|    | 2.3     | Electrons as waves                                                          | 17   |  |  |  |  |  |  |

|    | 2.4     | 2.4 Mesoscopic devices                                                      |      |  |  |  |  |  |  |

|    | 2.5     | Ballistic transport in mesoscopic GaN devices                               | 18   |  |  |  |  |  |  |

|    |         | 2.5.1 Advantages of GaN-HEMTs for ballistic transport studies and devices . | 18   |  |  |  |  |  |  |

|    |         | 2.5.2 Ballistic transport at room temperatures                              | 21   |  |  |  |  |  |  |

|    |         | 2.5.3 Ballistic transport under magnetic field at 4.2 K                     | 23   |  |  |  |  |  |  |

|    | 2.6     | Quenched Hall effect, UCF and WL                                            | 25   |  |  |  |  |  |  |

|    | 2.7     | 2.7 From physics to applications: frequency multiplication                  |      |  |  |  |  |  |  |

|   | 2.8  | Conclusion                                                                                        | 29 |

|---|------|---------------------------------------------------------------------------------------------------|----|

| 3 | New  | gating techniques                                                                                 | 31 |

|   | 3.1  | Introduction                                                                                      | 31 |

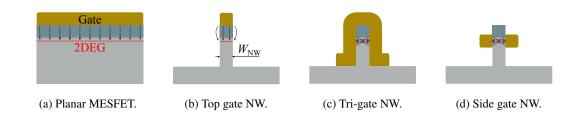

|   | 3.2  | From planar gate to tri-gate                                                                      | 31 |

|   | 3.3  | Gated NWs                                                                                         | 32 |

|   |      | 3.3.1 From planar gate to side gates                                                              | 32 |

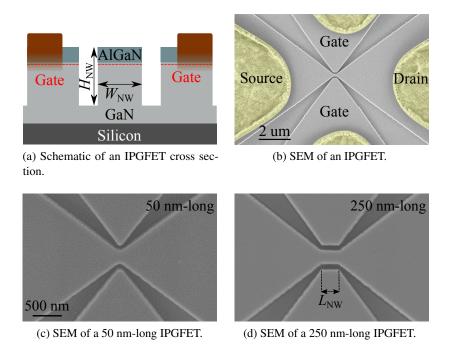

|   |      | 3.3.2 In-plane gate field-effect transistor                                                       | 33 |

|   | 3.4  | AlGaN/GaN IPGFETs                                                                                 | 35 |

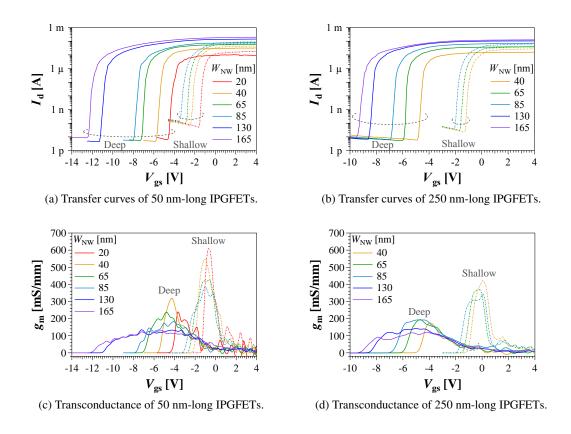

|   |      | 3.4.1 Transfer characteristics and capacitance simulations                                        | 36 |

|   |      | 3.4.2 Output characteristic and breakdown test                                                    | 39 |

|   |      | 3.4.3 Healing of dry-etching damages on the sidewalls                                             | 39 |

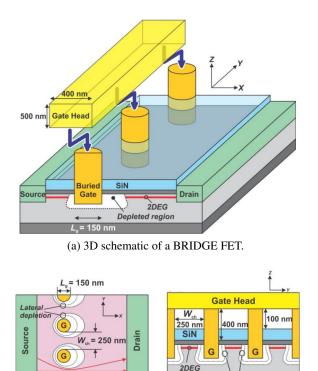

|   | 3.5  | Metal-IPGFETs: a step towards scaled-up devices                                                   | 40 |

|   |      | 3.5.1 Scaled-up side-gate FETs                                                                    | 42 |

|   | 3.6  | Conclusion                                                                                        | 43 |

|   |      |                                                                                                   |    |

| 4 |      | -HEMT zero-bias RF detectors                                                                      | 45 |

|   | 4.1  | Introduction                                                                                      | 45 |

|   | 4.2  | Radio-frequency detectors                                                                         | 45 |

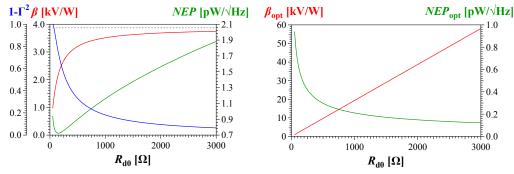

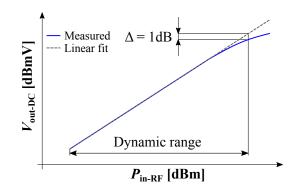

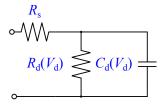

|   | 4.3  | Figures of merit                                                                                  | 46 |

|   | 4.4  | State of the art of solid state zero-bias RF detectors                                            | 51 |

|   | 4.5  | Field-effect rectifiers                                                                           | 52 |

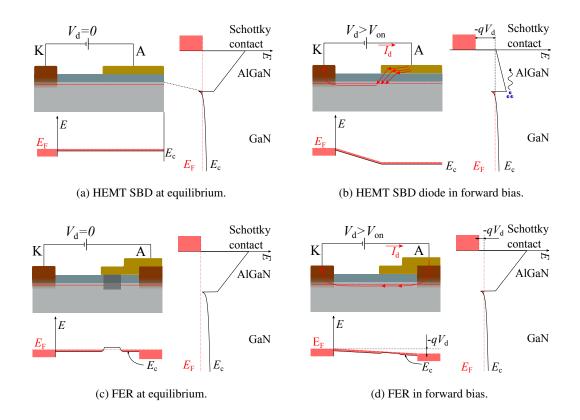

|   |      | 4.5.1 Field-effect rectifiers and Schottky diodes                                                 | 52 |

|   |      | 4.5.2 Effect of $V_{\text{th}}$ on $V_{\text{on}}$ and $I_{\text{r}}$ for field-effect rectifiers | 52 |

|   |      | 4.5.3 Comparison of curvature                                                                     | 54 |

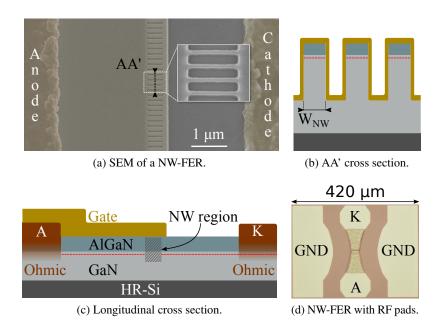

|   | 4.6  | Nanowire Field-Effect Rectifiers (NW-FERs): device concept                                        | 55 |

|   | 4.7  | DC characterization of NW-FERs                                                                    | 56 |

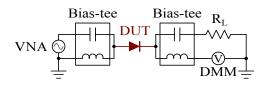

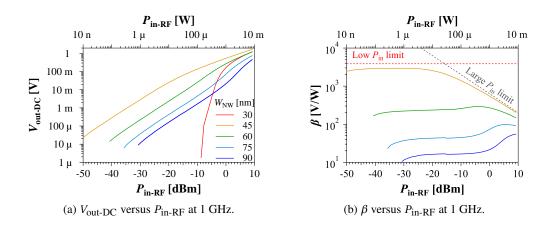

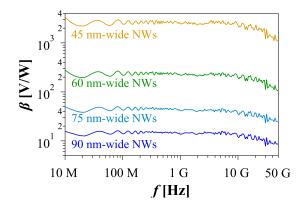

|   | 4.8  | RF characterization of NW-FERs                                                                    | 58 |

|   |      | 4.8.1 Responsivity measurement                                                                    | 59 |

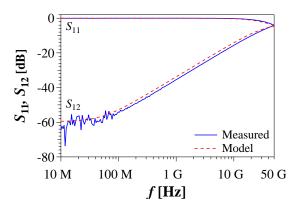

|   |      | 4.8.2 S-parameter measurement                                                                     | 60 |

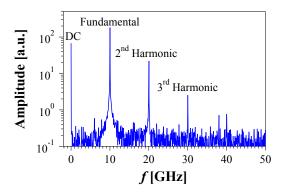

|   | 4.9  | Other applications: frequency multiplication                                                      | 62 |

|   | 4.10 | Chapter conclusion                                                                                | 63 |

| 5 | Con  | clusion and future directions                                                                     | 65 |

| Α | Fabr | rication process                                                                                  | 67 |

|   |      | Process flow                                                                                      | 67 |

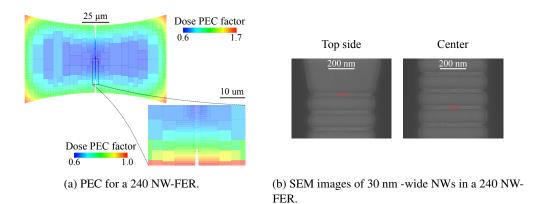

|   |      | A.1.1 Proximity error correction for EBL                                                          | 73 |

|   | A.2  | E-beam writing on transparent and low conductive substrates                                       | 74 |

| В | RF n | neasurements with VNA                                                                             | 77 |

|   | B.1  | Introduction                                                                                      | 77 |

|   | B.2  | On-wafer SOLT calibration                                                                         | 78 |

|   |      |                                                                                                   |    |

| B.3     | Open-short de-embedding | 79 |

|---------|-------------------------|----|

| Referen | ces                     | 94 |

| Curricu | lum Vitae               | 95 |

# List of Figures

| 1.1  | IoT                                                                                                                                        | 1  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | 5G                                                                                                                                         | 2  |

| 1.3  | Band gap versus lattice constant a                                                                                                         | 3  |

| 1.4  | Saturation velocity and electron mobility                                                                                                  | 4  |

| 1.5  | GaN crystal cell                                                                                                                           | 5  |

| 1.6  | AlGaN/GaN HEMT band diagram and charge distribution                                                                                        | 6  |

| 1.7  | Metal Semiconductor Field-Effect Transistor structure based on AlGaN/GaN                                                                   |    |

|      | НЕМТ                                                                                                                                       | 9  |

| 1.8  | Qorvo GaN MMIC                                                                                                                             | 10 |

| 1.9  | Ultrascaled and linear GaN-HEMT based MESFETs                                                                                              | 12 |

| 1.10 | Different types of GaN NWs                                                                                                                 | 13 |

| 2.1  | Transport regimes                                                                                                                          | 16 |

| 2.2  | General resistance representation                                                                                                          | 17 |

| 2.3  | 1D energy-momentum relation                                                                                                                | 19 |

| 2.4  | Sidewall depletion                                                                                                                         | 20 |

| 2.5  | Electron-filter cross                                                                                                                      | 21 |

| 2.6  | Ballistic transport at room temperature                                                                                                    | 22 |

| 2.7  | Ballistic transport at 4.2 K                                                                                                               | 23 |

| 2.8  | Ballistic transport at 4.2 K with magnetic field: 2D map                                                                                   | 24 |

| 2.9  | Ballistic transport at 4.2 K with magnetic field: some values of B                                                                         | 24 |

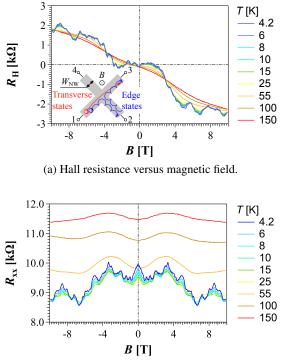

| 2.10 | Hall measurement from 4.2 K to 150 K                                                                                                       | 26 |

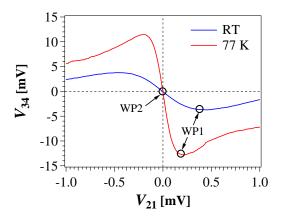

| 2.11 | Working point in $V_{34}$ for harmonic generation                                                                                          | 27 |

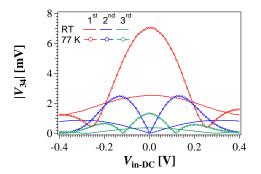

| 2.12 | Electron-filter cross as harmonic generator                                                                                                | 28 |

| 3.1  | Different gate techniques                                                                                                                  | 33 |

| 3.2  | AlGaN/GaN IPGFET SEM images and cross section schematic                                                                                    | 34 |

| 3.3  | AlGaN/GaN IPGFETs transfer characteristics                                                                                                 | 35 |

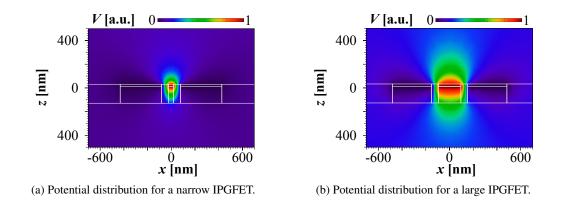

| 3.4  | Potential distribution in IPGFETs                                                                                                          | 37 |

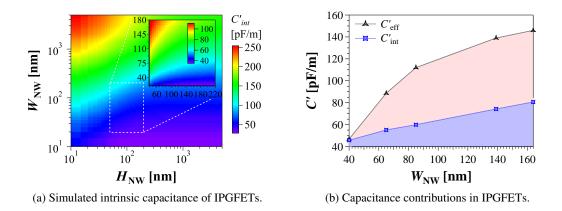

| 3.5  | AlGaN/GaN IPGFETs capacitance                                                                                                              | 38 |

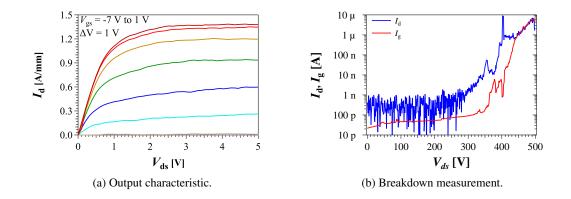

| 3.6  | Output characteristics of an IPGFET                                                                                                        | 39 |

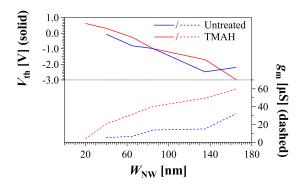

| 3.7  | Effect of TMAH treatment on $V_{\text{th}}$ and $g_{\text{m}}$                                                                             | 40 |

| 3.8  | $V_{\text{th}}$ and $g_{\text{m}}$ in IPGFETs and M-IPGFETs $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 41 |

|      |                                                                                                                                            |    |

| 3.9  | BRIDGE FET                                               | 42 |

|------|----------------------------------------------------------|----|

| 4.1  | Diode detector                                           | 47 |

| 4.2  | Responsivity and <i>NEP</i> versus $R_{d0}$ in detectors | 48 |

| 4.3  | 1-dB compression point                                   | 49 |

| 4.4  | Equivalent circuit of a diode square-law detector        | 50 |

| 4.5  | Schottky diode and field-effect rectifier band diagrams  | 53 |

| 4.6  | NW-FER SEM and schematics                                | 55 |

| 4.7  | Schottky tri-gate and threshold voltage                  | 56 |

| 4.8  | IV curves of NW-FER                                      | 57 |

| 4.9  | Curvature and differential resistance of NW-FERs         | 58 |

| 4.10 | Responsivity setup for dual port devices                 | 59 |

| 4.11 | Responsivity measurement versus input power              | 60 |

| 4.12 | Responsivity versus frequency                            | 60 |

| 4.13 | S-parameters of a 45 nm-wide NW-FER                      | 61 |

| 4.14 | Frequency multiplication with NW-FERs                    | 62 |

| A.1  | Proximity error correction                               | 75 |

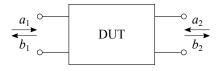

| B.1  | Dual-port DUT                                            | 77 |

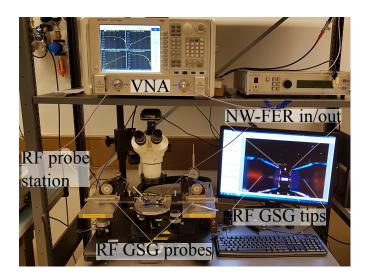

| B.2  | RF measurement setup with VNA                            | 78 |

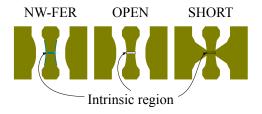

| B.3  | Open short de-embedding for NW-FERs                      | 80 |

## List of Tables

| 1.1 | Material properties for RF applications                    | 4  |

|-----|------------------------------------------------------------|----|

| 1.2 | Properties of substrates for growing GaN                   | 7  |

| 2.1 | Transport properties of semiconductors for RF applications | 20 |

| 2.2 | Frequency multiplication with electron-filter crosses      | 29 |

| 3.1 | Cut-off frequency prediction for IPGFETs                   | 38 |

| A.3 | List of abbreviation and acronyms in the process flow      | 73 |

| A.4 | EBL writing on insulating and transparent substrates       | 76 |

## **1** Introduction

Internet of Things IoT is a network superstructure where different objects ("things"), humans, and computing devices are identified by a UID (unique identifier) and data communication can also happen without any human action [1].

IoT is supposed to revolutionize our lives in the near future leading to autonomous cars, smart homes, improvements in healthcare and in many fields of human activities. The basic idea behind IoT is that every element in the network can communicate with others once an internet access is granted (Fig. 1.1).

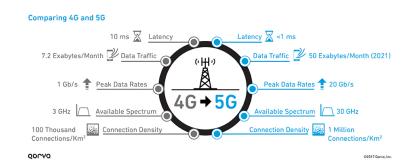

The fifth generation of mobile communication (also known as 5G) will ensure a network access to mobile phones and remote embedded systems with unprecedented data rate (to enable 4K and 8K streaming), extremely small latency (very important for autonomous driving and telesurgery, for example) and high connection density (billions of devices are expected to be connected). Fig. 1.2 quantitatively describes the performance of 5G and the comparison with its predecessor (4G).

The 5G infrastructure is based on a large number of cells with different dimensions, power, and

Figure 1.1 – Schematic (from ScienceSoft) showing the concept of the internet of things. Every object, from home appliances and wearable objects to industrial machines and city facilities, is connected to the cloud, which can be accessed from several devices and allows both monitoring and remote control in real-time.

Figure 1.2 – Illustration (from Qorvo) of the main differences between the fourth and fifth generation of mobile communications. All the improvements are essential for the real development of IoT. For example, the small latency is necessary for autonomous driving and remote control (e.g., telesurgery), while the 10X larger connection density is the basement for connecting several "things".

numbers of user capabilities [2]. For low-power cells (femto and pico cells), the required power can be easily delivered from low-doping metal oxide semiconductor (LDMOS) technology on silicon. For larger cells, the higher power demand (up to tens of watts) makes devices based on Si and GaAs very inefficient and space-consuming.

Gallium Nitride (GaN) and the entire family of III-Nitride semiconductors, thanks to their physical properties (which will be later discussed), are more favorable for high power applications; thus, they do and will play a more and more relevant role. In addition, GaN-based devices will also have an impact on low power applications since they can deliver the same power in a smaller footprint, besides the reduced device resistance also allows an easy matching with the antenna yielding in a strong, and further, reduction of the overall required footprint (thus cheaper and more economical appealing systems) [3].

In the next sections, we will discuss GaN and other III-Nitride compounds, together with the physical properties that make these materials very favorable for 5G applications and several more. Later we will review the state of the art of GaN devices for RF applications and we will highlight some issues in current technologies. Finally, we will talk about the use of nanowires (NWs) to enhance performance for the next generation of GaN electronic devices.

### 1.1 Physical properties of Gallium Nitride for RF applications

Gallium Nitride is the most known binary compound of the family of III-Nitrides, where we can also find Indium Nitride (InN), Aluminum Nitride (AlN) and Boron Nitride (BN, though it is investigated more as 2D material than bulk).

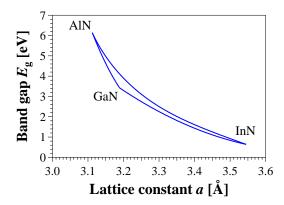

One of the main advantages of III-Nitrides is the property to tune the band gap from 0.6 eV of InN up to 3.39 eV of GaN and 6.1 eV of AlN. Intermediate values are obtained by using ternary

Figure 1.3 – Band gap versus lattice constant for the three main nitride compounds (AlN, GaN, and InN) and their ternary alloys, namely  $Al_xGa_{1-x}N$ ,  $In_xGa_{1-x}N$ , and  $Al_xIn_{1-x}N$ .

or quaternary alloys, mainly based on Ga, Al, and In. In Fig. 1.3, we report the variation of band gap when creating ternary alloys using the three main Nitride compounds (e.g.  $Al_xGa_{1-x}N$ ,  $In_xGa_{1-x}N$  and  $Al_xIn_{1-x}N$  with x varying from 0 to 1). The models used for determining  $E_g$  and a are the bowling model (quadratic) and linear model, respectively [4–6].

The capability of tuning the band gap using almost lattice-matched alloys is crucial for band structure engineering since it enables the growth of different epistructures for specific purposes. For example, the famous blue light-emitting diode (LED) is based on a multi-quantum-well (MQW) formed with layers of GaN and InGaN: carrier recombination for generating light happens in the InGaN layers having band gaps engineered to emit in the blue spectrum.

GaN and AlN (including AlGaN) belong to the family of large band gap semiconductors, which are very desirable for applications related to engine electrification and the high power telecommunications systems. A large band gap translates in higher breakdown voltage ( $V_{br}$ ) for the fabricated devices, that is to say, more considerable power capabilities than narrow gap semiconductor (e.g., Si). Specifically for RF amplification, the breakdown voltage sets the maximum bias voltage for devices, which directly influences the maximum output power.

The saturation velocity ( $v_{sat}$ ) is another crucial property since it determines the speed at which electrons cross the gate or base region (according to the type of transistor). The saturation velocity has a direct influence on the device cut-off frequency ( $f_c$ ), which, for a lateral field-effect transistor (FET) having a gate length  $L_g$ , is equal to:

$$f_{\rm c} = v_{\rm s}/2\pi L_{\rm g} \tag{1.1}$$

Both high saturation velocity and large breakdown are fundamental in defining the device performance, and the Johnson Figure of Merit (*JFoM*) is usually used to describe the trade-off

| Material | $E_{g} [eV]$ | $\epsilon_{\rm r}$ | E <sub>BR</sub> [MV/cm] | $\mu$ [cm <sup>2</sup> /Vs] | $v_{\rm sat}$ [cm/s] | JFoM |

|----------|--------------|--------------------|-------------------------|-----------------------------|----------------------|------|

| Si       | 1.1          | 11.8               | 0.3                     | 1350                        | $1.0 \times 10^{7}$  | 1    |

| SiC      | 3.26         | 10                 | 3.0                     | 700                         | $2.0 \times 10^{7}$  | 20   |

| Diamond  | 5.5          | 5.5                | 5.6                     | 1900                        | $2.7 \times 10^{7}$  | 50   |

| GaN      | 3.39         | 9.0                | 3.3                     | 1200                        | $2.5 \times 10^{7}$  | 27.5 |

| GaAs     | 1.42         | 13.1               | 0.4                     | 8500                        | $1.0 \times 10^{7}$  | 2.7  |

Table 1.1 – Main semiconductors for RF applications and their physical properties together with the Johnson figure of merit (normalized with respect to the Si one). Values comes from Ref. [7]

between the two properties:

$$JFoM = \frac{E_{\rm BR} v_{\rm sat}}{2\pi} = V_{\rm BR} f_{\rm c}$$

(1.2)

In Tab. 1.1, we collect the values of the main physical properties influencing the RF behavior for materials which have or will have a substantial impact on the RF domain. Despite the very high *JFoM* for diamond, this material is still at an embryonic stage in both growth (wafer size, cost, and quality) and fabrication process; in addition, it does not allow the formation of heterostructures which can ensure higher carrier mobility. The second most favorable candidate is then GaN, which has also other significant features: very high quality material thanks to growth developments for the fabrication of blue LEDs, large variety of wafers on which GaN can be grown, better thermal conductivity than GaAs, high mobility and carrier concentration in GaN-based high electron mobility transistors (HEMTs).

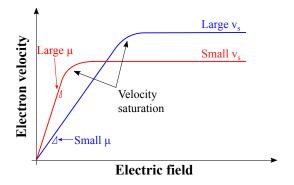

Figure 1.4 – Electron velocity in two different semiconductors: one has low mobility and high saturation velocity (blue line) and the other the opposite (red line). Such independence between electron mobility and velocity can be observed comparing GaAs and SiC (Tab. 1.1).

Despite the common thought, we believe that the role of the mobility for RF devices depends on the application and might be secondary. For example, amplifiers designed in class from A to C work with a drain (or collector) bias causing the saturation of electron velocity, which is uncorrelated from the mobility (e.g. SiC has twice the saturation velocity of GaAs, yet its mobility is more than 10x smaller) and determines the cut-off frequency (Eq. 1.1). In this perspective, high mobility becomes useful only for low power applications since a small drain bias is needed for reaching the saturation velocity (Fig. 1.4); moreover, also noise performances are improved. In the case of RF power amplifiers (PAs), an increase of mobility reduces the voltage at which the saturation happens by a few volts, which is not an impressive improvement considering that operating bias voltage values are in the range of tens of volt.

### **1.2 Polarization and 2DEG formation**

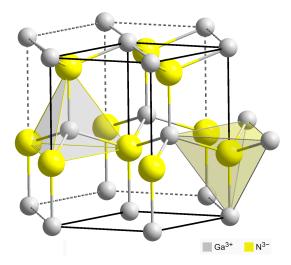

The common property of III-Nitrides is the wurtzite structure of the elementary cell (Fig. 1.5). The asymmetric position of the nitrogen ion with respect to the electrostatic centroid of the pyramid defined by the four gallium ions generates a dipole moment. When forming the crystal structure, dipoles of each cell sum together producing an electric field in between two layers (at the top and the bottom surfaces) of fixed charges (with opposite sign). This phenomenon is called spontaneous polarization (the same name also defines the charge density of the two layers), which generates an electric field in the order of MV/cm. Since III-Nitrides are piezoelectric materials, a polarization field is also generated when growing a binary or ternary compound on top of another with a different lattice constant. The lattice mismatch strains the thinner layer (the strain in the thick layer can be neglected if the ratio of the thicknesses is large) originating a piezoelectric polarization.

Figure 1.5 – Illustration of the combination of some GaN elementary crystal cells. Each cell is constituted by four Ga atoms, defining the four edges of the triangular-base pyramid, and a N atom in the center. The ionic bonds produce the formation of a nitrogen anion and four gallium cations per cell.

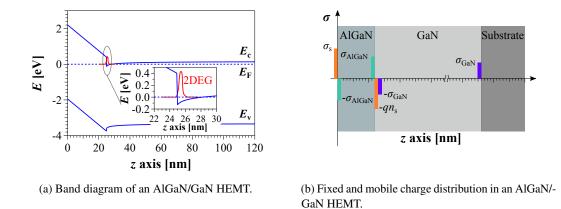

Figure 1.6 - (a) and (b) Simulated band diagram and qualitative charge distribution of an AlGaN/GaN HEMT along its growth direction .

Both the spontaneous and piezoelectric polarization are essential in the formation of a 2dimension electron gas. The most common HEMT structure is formed by using an AlGaN barrier on top of a GaN channel. Fig. 1.6a shows the band structure for an  $Al_xGa_{1-x}N/GaN$ heterostructure while Fig. 1.6b shows the charge distribution. When putting together the channel and the barrier, the total electric field (which is the sum of both the spontaneous and piezoelectric polarization) produces an accumulation of electrons at the interface between the two materials (more precisely in the GaN channel) while a fixed layer of positive charge is left at the interface with the air. Due to the accumulation of electrons, the conduction band bends down forming a triangular-shaped quantum well where electrons are confined, thus forming a 2-dimensional electron gas (2DEG) layer. The carrier concentration  $(n_s)$  of this layer depends on the material used for the barrier and its thickness, since both influences the total electric field due to piezoelectric and spontaneous polarization. Usual values are in the range of  $1 \times 10^{13}$  cm<sup>-2</sup> (higher values, up to  $6 \times 10^{13}$  cm<sup>-2</sup> have been also demonstrated [8]), which are at least one order of magnitude larger than those in other HEMT structures [9, 10]. The mobility of electrons in GaN-HEMT can be as high as 2200 V/cm<sup>2</sup>s [11], exceeding the value reachable in bulk GaN (1200 V/cm<sup>2</sup>s). Such improvement is produced by a screening effect of the high-density 2DEG with respect to charged centers in the barrier, e.g. dislocations, thus actively reducing scattering sources [4].

### **1.3 GaN growth and substrates**

GaN epistructures (e.g. p-i-n, MQW, HEMT, etc.) can be grown with different techniques. Metal oxide chemical vapor deposition (MOCVD) is the most used in the LED and HEMT industry since it ensures relatively good material properties and quality with a large throughput. Molecular beam epitaxy (MBE) is generally employed in the academic field since it gives much better control of the growth parameters, thus enabling the formation of very complex epistructure, yet with a very small growth rate. Hybride phase epitaxy (HVPE), instead, is used to fabricate GaN

| Substrate                                         | GaN                                                                   | Sapphire                                                                      | 6H-SiC                                                          | Si (111)                                                                            |

|---------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------|

| <i>a</i> [Å]                                      | 3.189                                                                 | 4.758                                                                         | 3.08                                                            | 3.84                                                                                |

| $\lambda$ [W/cm/K]                                | 1.3                                                                   | 0.5                                                                           | 3.0-3.8                                                         | 1–1.5                                                                               |

| ρ [Ωcm]                                           | 10 <sup>6</sup>                                                       | $10^{14}$                                                                     | 10 <sup>5</sup>                                                 | $10^3 - 10^4$                                                                       |

| $CTE \text{ in-plane}$ $[10^{-6} \text{ K}^{-1}]$ | 5.59                                                                  | 7.5                                                                           | 4.2                                                             | 2.59                                                                                |

| $\Delta a$ [%]                                    | _                                                                     | 16                                                                            | 3.5                                                             | -16.9                                                                               |

| $\Delta CTE [\%]$                                 | -                                                                     | -34                                                                           | 25                                                              | 54                                                                                  |

| Advantages                                        | <ul> <li>Homoepitaxy</li> <li>Large ρ</li> </ul>                      | <ul> <li>Inexpensive</li> <li>Simple growth</li> <li>Large ρ</li> </ul>       | <ul> <li>High λ</li> <li>Small ΔCTE</li> <li>Large ρ</li> </ul> | <ul><li>Inexpensive</li><li>Very scalable</li><li>Si industry<br/>support</li></ul> |

| Disadvantages                                     | <ul><li>Expensive</li><li>Poor scalability</li><li>Up to 2"</li></ul> | <ul> <li>Large wafer<br/>bowing</li> <li>Large Δa</li> <li>Small λ</li> </ul> | <ul><li>Expensive</li><li>Limited<br/>wafer size</li></ul>      | <ul> <li>Large Δa and bowing</li> <li>Complex growth</li> <li>Small ρ</li> </ul>    |

Table 1.2 – List of the most common substrates on which GaN can be grown. Physical properties such as the lattice constant (*a*), the thermal conductivity ( $\lambda$ ), solid electrical resistance ( $\rho$ ) and the coefficient of thermal expansion (*CTE*) are reported together with the lattice mismatch ( $\Delta a$ ) and thermal mismatch ( $\Delta CTE$ ) with respect to GaN [12].

substrates due to the fast growth rate.

GaN can be grown on different substrates with very noticeable differences in material properties, quality, and costs. In Tab. 1.2 we report the four main substrates usually used for GaN growth. The lattice constant of the substrate determines the presence of strain, either compressive (e.g. GaN on sapphire) or tensile (e.g. GaN on silicon), the density of dislocations and the growth complexity to alleviate such defects (for example, a thick, up to several  $\mu$ m, buffer is usually grown on Si).

Strain also arises when the coefficient of thermal expansions (CTE), particularly the in-plane one, of the substrate is different from that of GaN. Growths usually happen at temperatures higher than 1000 °C, then, when cooling down the growth chamber, both GaN and the used substrate shrink by different amounts, if the CTE is different, and strain or bowing result as effects.

The last aspects to consider in choosing the substrate are its thermal conductivity and solid electrical resistivity. Independently from the application, highly thermal conductive substrates (e.g. SiC) are more desirable since the generated heat can be easily dissipated, allowing higher power operation than in low thermally conductive wafers. A good electrical conductivity is more favorable for high power low frequency (up to few MHz) applications, while high resistive substrates are preferred for RF ones.

The highest material quality for any epistructure is obtained using GaN substrates; however,

they are costly (especially high resistive wafers) and strongly limited in size. Foreign substrates, presenting small lattice and thermal mismatch with respect to GaN are generally used and they include 6H-SiC, Si (111), and sapphire. The growth of GaN on foreign substrates can yield to the formation of cracks, high dislocation density, and large wafer bowing.

For RF applications, the two most suitable candidates are SiC and Si, since sapphire wafers are not ideal for dissipating considerable power due to the poor thermal properties. GaN on SiC is, so far, the best choice for RF devices where high-frequency operation and large power (i.e. large dissipated power) are needed. SiC ensures good thermal conductivity together with extremely good electrical insulation (which results in reduced RF losses with respect to more conductive substrates), though at the expense of higher material cost and size limitations.

High resistive (HR) silicon wafers can be used for applications where the handled power is not high (otherwise, there would be several thermal issues) and the operating frequency is below 10 GHz. The latter is caused by poor insulation capability of HR silicon which generates significant RF losses at high frequency. The advantages of using Si instead of SiC are the lower price and the larger wafer size (GaN can be grown on up-to-8" Si wafers) as well as the possibility to convert old Si manufacturing chains to produce GaN devices. All these factors contribute to actively reduce the cost (of course at the expense of the performance); thus, they target more mass commercial applications. Another advantage, which is still under research, is the monolith integration of logic circuits (for which 100 Si is needed) and RF circuits [13]. A similar trend is followed for GaN-based power devices using the silicon on insulator (SOI) technology [14].

### **1.4 MESFET based on GaN HEMTs: structure and operation**

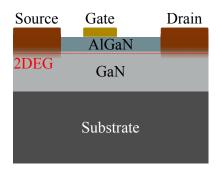

The most known device structure for a transistor based on a GaN HEMT is the MEtal-Semiconductor field-effect transistor (MESFET). Fig. 1.7 shows a device based on an AlGaN/GaN HEMT, where the source and drain are formed by fabricating ohmic contacts while a Shottky contact is used as gate to control the channel underneath. The device is usually isolated either by mesa etching or by ion implantation.

Ohmic contacts are usually realized by depositing and annealing, by a rapid thermal process (RTP), a stack of metals, which can varies from a simple Au-free Ti/Al stack [15] to 6-layer stacks using more exotic metals and also semiconductors (generally Si or Ge with the intent to perform a n-doping of the barrier)[16]. The used metal stack and RTP conditions (temperature, annealing time, chamber gas) strongly influence the morphology of the contacts (generally annealed ohmic contacts are quite rough), the contact resistance with the 2DEG (down to 0.21  $\Omega$ mm [16]) and lateral diffusion of the metals (very important for MESFET with short source-drain distance). Much better contacts can be achieved by partially etching the epistructure underneath the desired contact regions and regrowing heavily n-doped (up to 10<sup>19</sup> cm<sup>-3</sup>) GaN. The growth is usually performed by MBE and allows achieving ohmic contact resistance in the order 0.085  $\Omega$ mm [17]. In this case, the metal is deposited on top of the regrown regions and no annealing is required,

Figure 1.7 - Schematic of a MESFET based on an AlGaN/GaN HEMT structure.

thus this technology, despite being more complex, is the best choice for ultra scaled devices.

The Schottky gate is realized by using a metal with a high working function, since such value determines, in the case of a thick barrier where the tunneling current can be neglected, the gate leakage current. Nickel is the most common choice and it is generally followed by a thick gold layer that ensures very low gate contact resistance (not to be confused with the gate conductance, which takes into account the leakage current through the gate).

The working principle of a MESFET is based on the modulation of the 2DEG carrier density by applying a negative voltage to the Schottky gate. Further accumulation of electrons in the 2DEG is strongly limited by the reduction of the Schottky barrier height for positive gate voltage, which results in a considerable gate leakage. This problem can be solved by using a MOS-HEMT structures, which also allow the fabrication of normally-off devices (no 2DEG at equilibrium under the gate).

### 1.5 State of the art of RF devices based on GaN HEMT

### 1.5.1 Commercial GaN HEMT devices

The main RF application for GaN-based HEMT is for PAs, thanks to the large breakdown voltage which allows increasing the supplied bias, so the maximum output power. Commercial GaN PAs are already available and they can reach power up to 100 W in a single stage (e.g. the Qorvo's TGA2813-CP PA).

The large band gap makes GaN also less susceptible to noise and capable of working at high temperatures (some hundreds of Celsius), thus very appealing for low noise amplifiers (LNAs). A further advantage in using GaN for LNAs is strong robustness to excess of input power, indeed commercial devices can resist to up 10 W exceeding power (e.g. Qorvo's TGA2227-SM) and such capability is not present in any other competing technology.

Figure 1.8 – Qorvo GaN MMIC unveiled by System Plus Consulting [18]. The MMIC targets 5G base stations and includes a high linearity LNA, a low insertion-loss TR switch and a high gain PA.

Another, less mainstream, commercial application involves the fabrication of RF switches (e.g. the United Monolithic Semiconductors CHS8618-99F GaN reflective single pole double trows). The large breakdown voltage allows operations with high power signals while the high current capabilities, due to the large saturation velocity and high carrier concentration, ensures very small insertion losses (1.3 dB).

Thanks to the lateral structure of devices based on GaN-HEMTs, the fabrication of microwave monolithic integrated circuits (MMICs) is feasible and very promising. MMICs, in general, allow reducing parasitic components due to the proximity of the devices which coexists on the same die, hence losses are reduced and the frequency operation is increased; furthermore, the total cost of the system is strongly diminished. Fig. 1.8 shows a front end module for 5G base stations wholly built on a GaN on SiC chip. The MMIC contains a high linearity LNA, a low insertion-loss Transmit Receive (TR) switch and a high gain PA.

### 1.5.2 GaN HEMT research activity

Despite the availability of excellent and competitive commercial devices, there is a lot of research activities which aim to improve some device properties, expand the fields of application of GaN-HEMT devices and mitigate some issues.

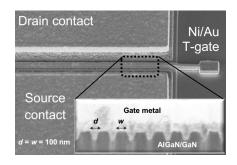

While commercial devices can work up to several tens of GHz, researchers are developing scaling technologies to approach the theoretical limit predicted for GaN. This process involves the reduction of the gate length (down to a few tens of nm) and the reduction of parasitic capacitance and resistance contributions. Ultrascaled GaN HEMTs require the fabrication of the T-shaped gate, which helps to reduce both the gate length and resistance, regrown contacts to reduce the

overall device resistance and optimization of the passivation layer. Tang et al. [19] demonstrated the best ever reported frequency performance in a 20 nm-long gate device (Fig. 1.9a) with a cut-off frequency ( $f_c$ ) of 454 GHz.

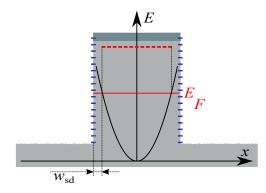

Ultra-short gate devices, though, present two main disadvantages: reduction of break down voltage and increase of short channel effects (SCE). The latter includes poor channel control which translates in very high subthreshold slope (SS), far from the ideal 60 mV/dec, and large drain induced barrier lowering (DIBL). Previous works have shown that short channel effects start to be dominant when the ratio between the gate length and the gate-to-DEG distance (e.g. the barrier thickness in case of a Schottky gate) is smaller than 7.5 (average values between two different papers investigating short channel effects [20, 21]). For example, a GaN HEMT with a gate length of 20 nm would require a barrier thickness of about 3 nm.

The reduction of the barrier thickness under the gate is achievable either by growing HEMT wafers with thinner barriers or by using the gate recess technique. The former usually requires to use different materials than AlGaN for the barrier to ensure the formation of the 2DEG (the average AlGaN barrier thickness is around 25 nm and smaller values would strongly reduce the carrier concentration, yielding an increase of resistance). For example, the barrier thickness can be reduced down to 6 nm using InAlN [22] or to 4 nm using AlN [19] while still maintaining an average carrier density around  $1 \times 10^{13}$  cm<sup>-2</sup>.

Gate recess, instead, requires a very precise etching of a portion of the barrier under the gate region. In this case, the research is mainly focused on improving the etch speed control and reduce etch damages. For this purpose, digital etching is one of the most common techniques and involves cycles of oxidation of the barrier by  $O_2$  plasma and removal by acid (usually hydrochloric acid). For each cycle, a constant number of atomic layers are removed ensuring very good control; however, such technique, widespread in the academic field, would be challenging to use in the industry. Atomic layer etching (ALE), already developed for narrow-gap III-V semiconductors and just released for III-Nitrides, can be a good substitute for digital etching since it still works by oxidation-removal cycles but everything happens inside the reacting chamber of the tool, hence it is very promising for mass production.

Despite the used techniques and material to achieve thin barriers, electron tunneling cannot be neglected and this strongly deteriorates the operating power range [23].

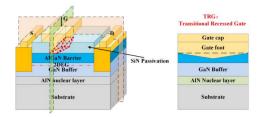

Linearity over input voltage is another important feature of PAs. The modulation scheme implemented for 5G communications produces signals with a high peak-to-average power ratio, thus the amplitude of the signal to be amplified has a wide dynamic range. A linear modulation can be ensured either by using pre-distortion techniques, which use complex algorithms and require further hardware, or by using high-linearity PAs. A flat transconductance of transistors over the gate voltage ensures good linear behavior and this can be achieved by properly tuning the transistor threshold voltage along the device width [25]. This solution can be implemented by using different techniques; for example, by a transitional-recess gate technology (Fig. 1.9b) [24].

(a) 20 nm T-gate MESFET with an AlN/GaN HEMT.

(b) Schematic of MESFET with a transitional-recessed gate.

Figure 1.9 – (a) Cross section of a MESFET with a 20 nm long T-gate and regrown ohmic contact [19]. The reported frequency performance ( $f_c \sim 450$  GHz) is the best realized with any III-Nitride HEMT. (b) Schematics of a MESFET with transitional-recess along the gate width for improving the device linearity thanks to a smooth variation of the threshold voltage [24, 25].

### 1.5.3 GaN nanowires

GaN nanowires (NWs) might be a solution to both linearity problems and short channel effects. Growth and etching of GaN nanowires are the two possible fabrication techniques.

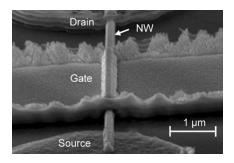

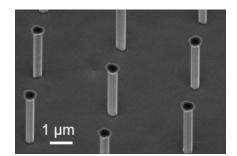

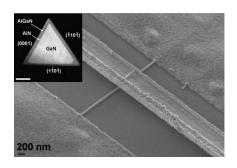

NWs can be grown on different substrates using catalysts or the selective area growth technique inside either MOCVD or MBE chambers. Fig.1.10a shows a MESFET based on an n-type NW which was grown on Si (111) and then transferred on SiO<sub>2</sub> over Si wafer, while Fig. 1.10b illustrate a metal insulator semiconductor FET (MISFET) relying on a radially grown AlGaN/GaN epistructure [26].

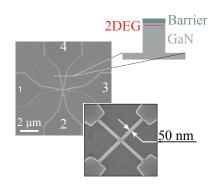

The second approach starts using a wafer with the desired epi-structure, which can be n-p-n for vertically devices (Fig. 1.10c [28]) or HEMT for lateral ones (Fig. 1.10d [29]), and perform a dry-etching with an hard mask or metals defining the NW diameter or width for vertical or lateral NWs, respectively. In this case, ad especially for vertical NWs, which are used to create gate all around (GAA) MOSFETs, the interface is very important and a wet etching process, based either on hot potassium hydroxide (KOH) or hot tetramethylammonium hydroxide (TMAH), is performed to heal dry-etching damages on the sidewalls.

Top-down NW HEMTs are very promising because they help to solve the previously listed issues, such as linearity and short channel effects, without a strong degradation of the material and 2DEG properties. For example, Joglekar et al. [25] have demonstrated that by using an array of GaN HEMT NWs with different widths, it is possible to obtain a more flat transconductance, indicating a more linear behavior of the device. Short channel effects can also be sharply reduced as shown by Ture et al., indeed the subthreshold slope improved from 200 mV/dec in the planar MESFET to 75 mV/dec in the NW-based one [29].

(a) MESFET based on a grown GaN NW.

(c) Vertically etched GaN NWs.

(b) MISFET based on a grown AlGaN/GaN NW.

(d) MESFET with T-gate based on NWs etched from a GaN HEMT wafer.

Figure 1.10 - (a) MESFET based on a MBE grown n-type *c*-axis GaN NW [27]. (b) MISFET based on a MOCVD grown *c*-axis AlGaN/GaN NW [26]. In the inset, a cross section of a NW with a scale bar of 50 nm. (c) Vertical NWs etched from a n-p-n GaN wafer [28]. (d) MESFET with a T-gate which wraps the three sides of NWs etched from an AlGaN/GaN HEMT on SiC [29].

## 1.6 Thesis outline

The use of GaN HEMT NWs is becoming more common and favorable for several applications, from high power [30,31] to RF [32–34], and a lot of research is still going on.

In this thesis, we deeply investigate GaN HEMT NWs under different aspects to have more physics insights about these structures and offer new applications and architectures.

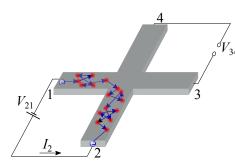

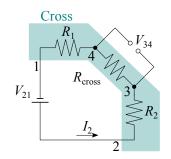

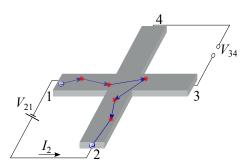

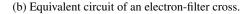

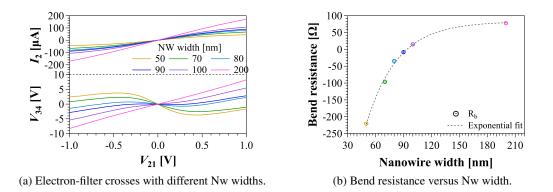

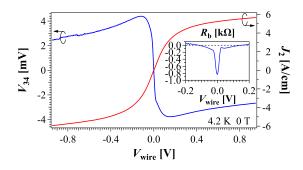

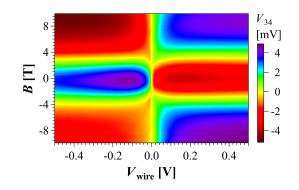

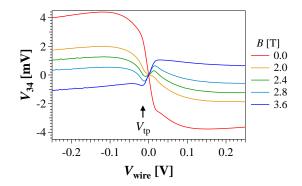

In chapter 2, we report electron transport studies performed in a mesoscopic device, called electron filter cross, which is based on two crossing NWs. This study reveals fascinating phenomena, such as ballistic transport at RT, quenched Hall effect, and quantum phase coherence, as well as it gives some practical information about NWs, e.g. a very accurate measurement of the sidewall depletion width. The reported results mainly come from Ref. [35].

In chapter 3, we discuss unconventional gating techniques for GaN HEMT NWs which should

alleviate the increase of parasitic capacitance, a drawback present for any NW-based transistors. This chapter is based on results published in Ref. [36] and other unpublished results of our group.

In chapter 4, we investigate a new architecture for RF power detectors working at zero bias, which is based on field-effect rectifiers having a channel constituted by an array of etched GaN HEMT NWs. This chapter is based on results published in Ref. [37].

Chapter 5 concludes the thesis and ends with some future work projects.

# **2** Ballistic transport in GaN nanowires

### 2.1 Introduction

In this chapter, we will discuss about electron transport studies performed by fabricating and measuring mesoscopic devices using III-Nitride HEMTs. The chapter first gives a theoretical overview of ballistic transport and quantum phenomena associated with the wave nature of electrons. Most of the material for this section comes from the book of S. Datta [38] and the review article about mesoscopic devices of T. J. Thornton [39]. Then we report about the measurements performed in our lab using GaN-based mesoscopic devices by varying several parameters (device dimensions, bias, temperature, magnetic field, etc.). Finally, we conclude with a small summary of the chapter. The shown results are from Ref. [35].

## 2.2 From diffusive to ballistic transport

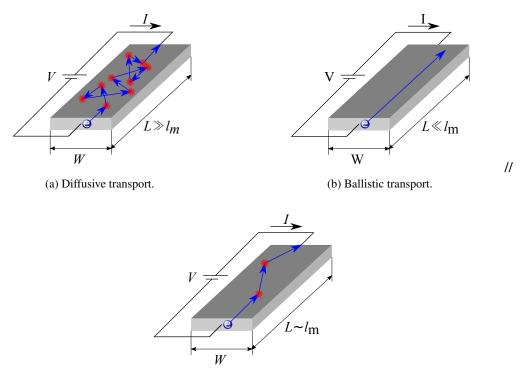

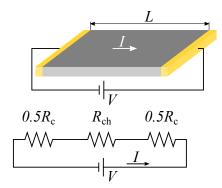

Considering a 2D conducting layer with a length L and a width W, if we apply a voltage (V), as shown in Fig. 2.1a, then the measured current I is equal to  $\frac{V}{R} = V \frac{L}{\sigma_0 W}$ , where  $\sigma_0 = n_s q^2 \tau / m^*$ is the Drude conductivity (with q and  $m^*$  being the elementary charge and the effective mass of the carrier, respectively) [38].  $n_s$  represents the number of available carriers (electrons or holes) per unit of area while  $\tau$  is the mean free time, which is the average time between two consecutive collisions of a carrier. The sources of these collisions are numerous and depend on both the material and the applied electric field [40]. The product between  $\tau$  and the average speed of electron ( $v_F$ ) defines the mean free path ( $l_m$ ), that is to say the average distance between two consecutive collisions.

For  $L \gg l_{\rm m}$  electrons scatter multiple times before reaching the other terminal and this transport regime is called diffusive (Fig. 2.1a). On the other hand, ballistic transport is achieved for  $L \ll l_{\rm m}$ , in which case electrons do not suffer any collision over the length L (Fig. 2.1b). In these conditions, the overall resistance does not reach 0  $\Omega$  but  $h/2q^2 \sim 12.5k\Omega$  (*h* is the Plank constant), known as resistance quantum ( $R_0$ , or conductance quantum  $G_0 = 1/R_0$ ) which is

(c) Quasi-ballistic transport.

Figure 2.1 - (a) Diffusive transport of an electron between two terminals, which is characterized by several collisions along the path. (b) Ballistic transport of an electron with a transmission probability equal to 1. (c) Quasi-ballistic transport in which case electrons suffer scattering with a probability to directly reach the other terminal between 0 and 1.

defined as the resistance of a 1D semiconductor where only one energy level (mode) is available. The number of modes (*M*) can be increased by enlarging the semiconductor width, for instance, and this was experimentally observed in 1988 [41,42]. The result of the experiments was the quantization of conductance by *quanta* equal to  $G_0$ , though the width of the channel was smoothly increased by the applied electric field. In the case of ballistic transport, the resistance associated with each mode is 0  $\Omega$ , since there is no scattering, and the voltage drops only at contacts and equally by  $IR_0/2$  for each mode; thus the total measurable resistance is  $R_0/M$ .

In the case of  $L \sim l_{\rm m}$  (Fig. 2.1c), there are two resistance contributions, namely the contact resistance  $R_{\rm c}$  and the channel resistance  $R_{\rm ch}$  (Fig. 2.1c), with the latter caused by a few collisions along the path *L*. This situation is used to define a common expression for the resistance in a semiconductor (Fig. 2.2), independently from the size and the transport regime [38]:

$$R = R_{\rm ch} + R_{\rm c} = \frac{L}{\sigma_0 W} + \frac{l_{\rm m}}{\sigma_0 W}$$

(2.1)

Figure 2.2 – General resistance representation, which is independent of the transport nature, of a semiconductor sample with two ohmic contacts.

For  $L \gg l_{\rm m}$ ,  $R_{\rm c}$  is negligible, the transport is diffusive and the Eq.2.1 becomes simply  $\frac{L}{\sigma W}$ , whereas, in the opposite case, the transport is ballistic and the only resistance contribution is from contacts and Eq. 2.1 reduces to  $\frac{l_{\rm m}}{\sigma W} = R_0/M$ . Eq. 2.1 can also be written as a function of the number of modes and the transmission coefficient  $T = l_{\rm m}/(L + l_{\rm m})$ , which indicates the probability for an electron to reach the other terminal without collisions, obtaining the Landauer formula:

$$R = \frac{h}{2q^2} \frac{1}{MT}$$

(2.2)

### 2.3 Electrons as waves

At the beginning of the XX century, De Broglie suggested the idea, which was later demonstrated by the Davisson-Germer experiment in 1927, that electrons, as light, have a dual nature; in particular, they can behave either as a wave or as a particle in according to the surround conditions. The study the wave nature of electrons in semiconductors is possible if the applied bias is lower than  $E_{\rm F}/q$  ( $E_{\rm F}$  is the Fermi energy) and one or more dimensions are smaller than the phase coherence (or phase-relaxation) length ( $l_{\phi}$ ), which is referred as the average distance over which the phase associated to the wavelength of an electron is maintained. In these conditions, quantum interference phenomena can happen and the value of  $l_{\phi}$  can be extracted, which depends on temperature and material properties. The main difference between  $l_{\rm m}$  and  $l_{\phi}$  comes from the nature of electron collisions, which can be elastic (no loss in energy and phase) or inelastic. Both scattering mechanism influences the mean free path since both produce a change of momentum (direction of electrons), thus the transition from ballistic to diffusive transport. On the other hand, the phase-coherent length will be sensitive only to the inelastic collisions, which can be neglected at cryogenic temperatures leading to the manifestation of interference effects.

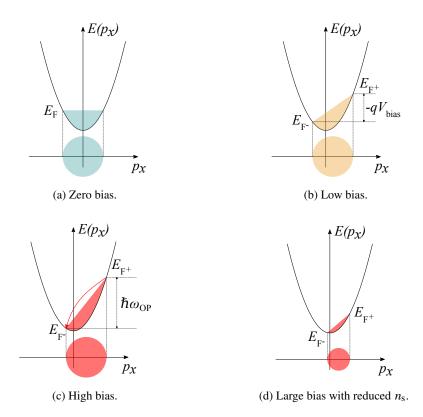

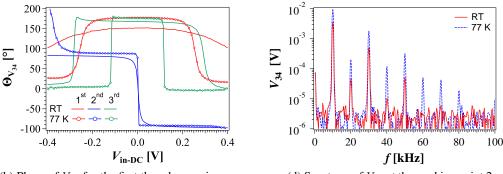

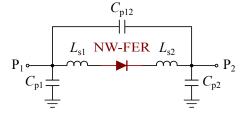

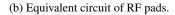

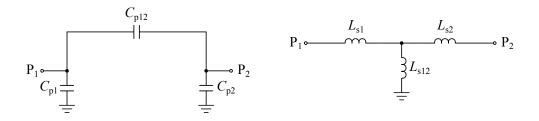

Weak localization (WL) is one of the most important consequences of the wave nature of electrons