Thèse n° 8164

# EPFL

# Data Structures and Algorithms for Logic Synthesis in Advanced Technologies

Présentée le 7 septembre 2020

à la Faculté informatique et communications Laboratoire des systèmes intégrés (IC/STI) Programme doctoral en informatique et communications

pour l'obtention du grade de Docteur ès Sciences

par

### **Eleonora TESTA**

Acceptée sur proposition du jury

Prof. P. lenne, président du jury Prof. G. De Micheli, Dr M. Soeken, directeurs de thèse Prof. P.-E. Gaillardon, rapporteur Prof. J.-H. R. Jiang, rapporteur Prof. A. P. Burg, rapporteur

École polytechnique fédérale de Lausanne

2020

"Brilliant," said Hermione. "This isn't magic – it's logic – a puzzle. A lot of the greatest wizards haven't got an ounce of logic, they'd be stuck in here forever." — Harry Potter and the Philosopher's Stone

To my beloved family

## Acknowledgements

PhD is universally recognized as a very stressful and demanding period, but, for me, it has also been rewarding and full of good memories. I am grateful to many people for help and assistance in these five years.

First, I would like to express my sincere gratitude to my advisor Prof. Giovanni De Micheli (Nanni), for his constant motivation, guidance, and immense knowledge of logic synthesis. During these last years, Nanni demanded a lot, but he was also fair and understanding towards me and my colleagues. I could not have hoped for a better advisor and laboratory environment. I wish to extend my deepest appreciation to my PhD co-advisor Dr. Mathias Soeken for his bits of advice and support throughout my PhD. Thank you, Mathias. This thesis would not have been possible without your valued help and limitless patience.

Besides my advisors, I would like to recognize the invaluable assistance of Dr. Luca Amarù for allowing me to be as Synopsys Inc. and for his guidance and constant motivation. Thanks for sharing your bright ideas with me and for your trust in my abilities. I wish to extend my special thanks to Prof. Pierre-Emmanuel Gaillardon, for giving me the opportunity to start my PhD within the LSI and for all our collaborations. I would also like to express my deepest appreciation to Dr. Alan Mishchenko, Dr. Heinz Riener, and Dr. Patrick Vuillod for the great research collaborations we had. My special thanks go to Prof. Francky Catthoor, Dr. Odysseas Zografos and Dr. Julien Ryckaert for their assistance of my PhD at IMEC. I also would like to extend my gratitude to the members of my oral committee Prof. P. Ienne and Prof. A. P. Burg from EPFL, and Prof. J.-H. R. Jiang from the National Taiwan University.

My sincere thanks also go to my colleagues at the LSI. Not only you provided me with a stimulating research environment, but you have also made these five years more cheerful and carefree. I would like to recognize the invaluable assistance that you all provided during my study. A special thanks also to Francesca, Giulia, Ivan, and Simone for being not only great colleagues but dear friends. In particular, thanks to Winston, Bruno, and Giulia for putting up with me during long months of TA. I recognize that it is not always easy. I wish to show my gratitude also to Aya, Fereshte, Nadja, and Tugba, and to all the people that stopped at LSI, even for a little while: Eleonora, Lucia, and Sofia. I would like to express my deepest gratitude to Dewmini, for all her invaluable work, and in general to all my students for teaching me more than I thought them. I wish also to acknowledge the help provided by the technical IT staff, and the invaluable assistance of Carole, Chantal, and Christina. I would like to thank all my other friends in Lausanne, Leuven, and Sunnyvale; in particular, Elisa, Enrico, Martina,

#### Acknowledgements

Mattia, Michela, and Mish. Finally, I would like to extend my deepest and sincere gratitude to Francesca and Giovanni. You have made my PhD life easier and happier since the first day. Thank you for your priceless friendship.

Special grazie to my italian friends. For your visits to Lausanne, the holidays together, and for distracting me from my PhD life. Thanks to Carlo, Chiara, Eleonora, Luca, Marco, and Mattia. My sincere thanks also go to my lifelong friends Allegra, Elisa, Marta, and Serena. "Grazie per esserci sempre".

I would like to thank my family, in particular, Beatrice, Enrico, Milda, and Silvia. "Grazie a tutti per il costante supporto e affetto. Grazie mamma per il coraggio". Thanks also to Fabio, who makes my sister Silvia much happier and nicer. Last, but not least, my biggest thanks to the person who most of all helped, comforted, and supported me in the past five years. Thanks, Enrico, for being close to me even at 9000 km and 9 hours away.

April 3, 2020

## Abstract

Logic synthesis is a key component of digital design and modern *electronic design automation* (EDA) tools; it is thus an essential instrument for the design of leading-edge chips, and to push the limits of performance (upwards) and power consumption (downwards). In the last two decades, the electronic circuits and digital systems community has evolved dramatically, facing many architectural and technological changes. Consequently, EDA and logic synthesis have adapted and changed to be able to accurately design the new generation of digital systems. In the present day, logic synthesis is an important area of research for two main reasons: (i) Many and diverse ways of computation, alternative to *complementary* metal-oxide-semiconductor (CMOS), have been presented in the last years. Post-silicon technologies (called emerging technologies) have been shown to be feasible and may provide us with better - more efficient - electronic devices. In a similar way, novel areas of applications of logic synthesis are emerging, ranging from deep learning to cryptography and security applications. (ii) The current computing and storage means make it possible to solve exactly problems that were only approximated before. Moreover, new reasoning engines, covering from deep learning to new SAT-solvers, can be used as a mean of computation, thus possibly unlocking novel optimization opportunities and enabling hardware of higher-quality.

The objective of this thesis is to advance state-of-the-art logic synthesis and present a variety of novel data structures and algorithms, addressing diverse types of applications in modern logic synthesis flows, considering standard CMOS design as well as emerging technology and cryptography.

Motivated by the many emerging technologies that implement majority gates, we first focus on majority-based logic synthesis. We present novel algorithms over the recently introduced *majority-inverter graphs* (MIGs). First, a novel optimization flow based on Boolean transformations is proposed. Then, we demonstrate how technology-dependent logic synthesis is an essential step for the abstraction and manipulation of novel and diverse majoritybased emerging technologies and, more important, their technological constraints. Moreover, we advance state-of-the-art theoretical results on majority logic. In particular, we mainly focus on the problem of "how best can the *n*-argument majority function (majority-*n*) be realized with a network of 3-input majority gates?". For this purpose, we present novel general upper bounds and decompositions, together with optimum results for majority-5 and -7 and best-known results for the majority-9 function. In the second part, we shift into more pragmatic results and show practical aspects of logic synthesis, designed to be successful in modern logic synthesis flows. We focus here on XOR-based logic synthesis. Motivated by the

#### Abstract

novel computing capabilities, we propose a novel optimization flow based on the Boolean difference for area optimization of standard CMOS technologies (for *application specific integrated circuits* (ASICs) design). Moreover, we establish a novel application of logic synthesis to cryptography and security applications. It has been demonstrated that the number of AND gates in a *xor-and graph* (XAG) correlates with the degree of vulnerability (security) of cryptography benchmarks and plays an important role in high-level cryptography protocols such as *multi-party computation* (MPC) and *fully homomorphic encryption* (FHE). We introduce a complete and automatic synthesis flow which consists of the main transformations involved in logic synthesis but aims instead at minimization of the number of AND gates over XAGs. Our tool and methods obtain significant results over both EPFL and cryptography and security benchmarks.

We argue that given the progress and novel opportunities of technology, logic synthesis has to be revisited while considering the plurality of primitives and novel engines that can be of interest, and, consequently, the corresponding objective functions and optimization problems.

**Keywords** Electronic design automation, logic synthesis, majority logic, emerging technologies

### Sommario

La sintesi logica è una componente chiave del design di circuiti elettronici digitali e dei moderni strumenti per *electronic design automation* (EDA); è quindi uno strumento essenziale per la progettazione di chip all'avanguardia e per spingere i limiti delle prestazioni (verso l'alto) e del consumo di energia (verso il basso). Negli ultimi due decenni, i circuiti elettronici e i sistemi digitali si sono evoluti notevolmente, affrontando molti cambiamenti architettonici e tecnologici. Di conseguenza, l'EDA e la sintesi logica si sono adattate e modificate per poter progettare con precisione questa nuova generazione di circuiti digitali. Al giorno d'oggi, la sintesi logica è un'importante area di ricerca per due motivi principali: (i) Negli ultimi anni sono state presentate molte e diverse technologie alternative al complementary metal-oxide-semiconductor (CMOS). Le tecnologie post-silicio (chiamate emerging technologies) hanno dimostrato di essere non solo realizzabili, ma potrebbero fornire dispositivi elettronici migliori e più efficienti. Allo stesso modo, stanno emergendo nuove aree di applicazione della sintesi logica, che vanno dal deep learning alla crittografia e alla sicurezza. (ii) Gli attuali mezzi di computazione e memorizzazione consentono di risolvere in maniera esatta problemi che sono stati finora risolti solo euristicamente. Inoltre, nuovi approcci come deep learning e SAT-solvers, possono essere utilizzati come mezzo di calcolo, potenzialmente sbloccando nuove opportunità di ottimizzazione e consentendo hardware di qualità superiore.

L'obiettivo di questa tesi è far avanzare la sintesi logica e presentare una varietà di nuove strutture dati e algoritmi, dedicandosi a diversi tipi di applicazioni nella sintesi logica moderna. Consideriamo quindi sia il design di circuiti elettronici basati su CMOS, nonché emerging technologies e applicazioni per la crittografia.

Motivati dalle molte emerging technologies che implementano la funzione logica del majority (funzione logica di maggioranza), ci concentriamo in primo luogo sulla sintesi logica basata sul majority e presentiamo nuovi algoritmi per *majority-inverter graphs* (MIGs). Innanzitutto, viene proposto un nuovo metodo di ottimizzazione dell'area degli MIG basato su trasformazioni Booleane. Quindi, dimostriamo come la sintesi logica debba dipendere dalla tecnologia e come questa sia un passo essenziale per l'astrazione e la manipolazione di nuove e diversificate emerging technologies e, più importante, dei loro limiti e vincoli tecnologici. Inoltre, avanziamo i risultati teorici sulle proprietá della logica a majority. In particolare, ci concentriamo principalmente sul problema di "come può essere realizzata al meglio la funzione majority con *n* ingressi (majority- *n*) con un grafo di porte a majority-3?". A tale scopo, presentiamo nuovi limiti superiori sulla loro realizzazione e nuove scomposizioni, insieme a risultati ottimi per il majority-5 e -7 e risultati migliori (conosciuti finora) per la

#### Sommario

funzione del majority-9. Nella seconda parte, passiamo a risultati più pragmatici e mostriamo aspetti pratici della sintesi logica, progettati per avere successo nei sistemi di sintesi logica industriali e moderni. Ci concentriamo qui sulla sintesi logica basata su OR esclusivo (XOR). Motivati dalle moderne capacità di computazione ed elaborazione, proponiamo un nuovo flusso di sintesi basato sulla differenza Booleana per l'ottimizzazione dell'area di circuiti basati su tecnologia CMOS (circuiti *application specific integrated circuits* (ASICs)). Inoltre, stabiliamo una nuova applicazione della sintesi logica nel campo della crittografia e della sicurezza. È stato dimostrato che il numero di porte AND in *xor-and graph* (XAG) è correlato al grado di vulnerabilità (sicurezza) dei circuiti e protocolli di crittografia e ha un ruolo centrale in applicazioni come *multi-party computation* (MPC) e *fully homomorphic encryption* (FHE). Introduciamo un nuovo metodo di sintesi logica, ma mira invece a minimizzare il numero di porte AND su XAGs. Il nostro tool e i nostri metodi ottengono risultati significativi sia sui circuiti proposti dall'EPFL che su quelli per la crittografia e la sicurezza.

Sosteniamo che alla luce dei progressi e delle nuove opportunità date dalla tecnologia, la sintesi logica debba essere rivisitata tenendo conto della pluralità di primitive Booleane e nuovi metodi di computazione, e di conseguenza, dei corrispondenti e diversi problemi di ottimizzazione.

**Parole Chiave** Electronic design automation, sintesi logica, funzione di maggioranza, nuove nanotecnologie

# Contents

| 111 | AIIU  | nicuge  | ements                          | v    |

|-----|-------|---------|---------------------------------|------|

| Ał  | ostra | ct (Eng | lish/Italian)                   | vii  |

| Li  | st of | Figure  | s                               | XV   |

| Li  | st of | Tables  |                                 | xvii |

| Li  | st of | Acrony  | yms                             | xix  |

| 1   | Intr  | oducti  | ion                             | 1    |

|     | 1.1   | Electi  | ronic Design Automation         | . 3  |

|     | 1.2   | Resea   | rch Motivation                  | . 5  |

|     |       | 1.2.1   | Modern CMOS Technologies        | . 5  |

|     |       | 1.2.2   | Alternative Applications        | . 6  |

|     | 1.3   | Thesi   | s Contributions                 | . 6  |

|     |       | 1.3.1   | Majority-based Logic Syntesis   | . 7  |

|     |       | 1.3.2   | XOR-based Logic Synthesis       | . 9  |

|     | 1.4   | Thesi   | s Organization                  | . 10 |

| 2   | Bac   | kgrou   | nd                              | 13   |

|     | 2.1   | Data    | Structures                      | . 13 |

|     |       | 2.1.1   | Truth Tables                    | . 13 |

|     |       | 2.1.2   | 2-level Representations         | . 14 |

|     |       | 2.1.3   | Binary Decision Diagrams        | . 15 |

|     |       | 2.1.4   | Multi-level Logic Networks      | . 16 |

|     | 2.2   | Algor   | ithms                           | . 18 |

|     |       | 2.2.1   | Algebraic Methods               | . 19 |

|     |       | 2.2.2   | Boolean Methods                 | . 22 |

|     |       | 2.2.3   | Exact Methods                   | . 27 |

|     | 2.3   | Effici  | ent Circuit Partitioning        | . 28 |

|     |       | 2.3.1   | Small Scale: Cut Enumeration    | . 29 |

|     |       | 2.3.2   | Detecting All Reconvergent MFFC | . 30 |

|     |       | 2.3.3   | Windowing                       | . 31 |

|     | 2.4   | Sumr    | nary                            | . 32 |

#### Contents

| 3 | Maj | ority-based Logic Synthesis                                       | 33  |

|---|-----|-------------------------------------------------------------------|-----|

|   | 3.1 | Motivation                                                        | 33  |

|   | 3.2 | Majority-based Emerging Technologies                              | 35  |

|   | 3.3 | Boolean Resynthesis for MIGs                                      | 39  |

|   |     | 3.3.1 Functional Reduction                                        | 39  |

|   |     | 3.3.2 Boolean Resubstitution                                      | 40  |

|   |     | 3.3.3 Replacement Optimization                                    | 41  |

|   |     | 3.3.4 Experimental Results                                        | 42  |

|   | 3.4 | Inverter Propagation and Fan-out Constraint                       | 43  |

|   |     | 3.4.1 Inversion Propagation                                       | 44  |

|   |     | 3.4.2 Fan-Out Restriction                                         | 46  |

|   |     | 3.4.3 Experimental Results                                        | 48  |

|   | 3.5 | Exact Synthesis with Constraints                                  | 49  |

|   |     | 3.5.1 Preliminaries                                               | 49  |

|   |     | 3.5.2 Constraints Encoding                                        | 52  |

|   |     | 3.5.3 Exact Algorithms                                            | 54  |

|   |     | 3.5.4 Experimental Results                                        | 57  |

|   | 3.6 | Area-Delay-Energy Product for QCA and STMG                        | 60  |

|   | 3.7 | Summary                                                           | 63  |

| 4 | Mai | ority-n Logic                                                     | 65  |

|   | 4.1 |                                                                   | 66  |

|   | 4.2 |                                                                   | 68  |

|   |     |                                                                   | 69  |

|   |     |                                                                   | 70  |

|   | 4.3 |                                                                   | 71  |

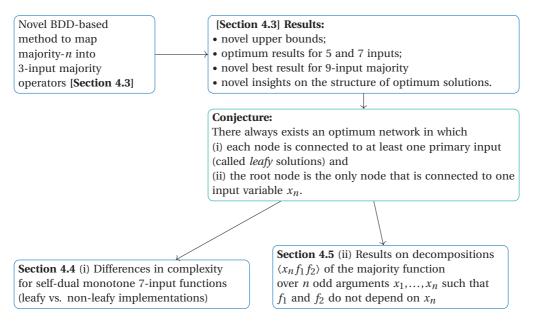

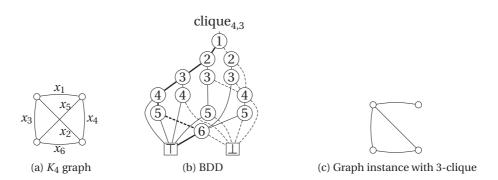

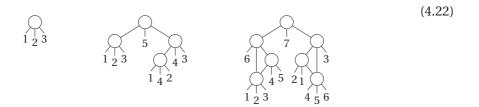

|   |     | 4.3.1 Transforming BDDs into Majority Graphs                      | 71  |

|   |     |                                                                   | 74  |

|   | 4.4 |                                                                   | 81  |

|   |     | 4.4.1 Preliminaries                                               | 82  |

|   |     | 4.4.2 Length and Combinational Complexity                         | 84  |

|   |     | 4.4.3 Experimental Results                                        | 87  |

|   | 4.5 | -                                                                 | 92  |

|   |     |                                                                   | 94  |

|   |     | 4.5.2 Majority- <i>n</i> Decompositions                           | 94  |

|   |     | 4.5.3 Application to Find Optimum Majority Networks               | 97  |

|   | 4.6 | Summary                                                           | 97  |

| 5 | XOF | R-based Logic Synthesis                                           | 99  |

| J | 5.1 |                                                                   | .00 |

|   | 5.2 |                                                                   | .00 |

|   | 5.2 |                                                                   | .02 |

|   |     | 5.2.1 Ineory    1      5.2.2 Boolean Difference Optimization    1 |     |

|   |     |                                                                   | 00  |

|    |       | 5.2.3  | Experimental Results                               | 106 |

|----|-------|--------|----------------------------------------------------|-----|

|    | 5.3   | Multi  | plicative Complexity and Cryptography Applications | 110 |

|    |       | 5.3.1  | Preliminaries                                      | 110 |

|    |       | 5.3.2  | General XOR-based Resynthesis Framework            | 112 |

|    |       | 5.3.3  | Experimental Results                               | 118 |

|    | 5.4   | Sumn   | nary                                               | 125 |

|    |       |        |                                                    |     |

| 6  | Con   | clusio | ns                                                 | 127 |

|    | 6.1   | Sumn   | nary of Thesis Contributions                       | 127 |

|    | 6.2   | Open   | Problems                                           | 129 |

|    |       | _      |                                                    |     |

| Bi | bliog | graphy |                                                    | 131 |

| Cı | arric | ulum V | /itae                                              | 147 |

|    |       |        |                                                    |     |

# List of Figures

| 1.1 | Novel and standard applications for logic synthesis           | 2   |

|-----|---------------------------------------------------------------|-----|

| 1.2 | Simplified EDA flow                                           | 3   |

| 1.3 | Typical logic synthesis flow                                  | 4   |

| 1.4 | Explanation of the majority function                          | 8   |

| 2.1 | Example of BDD                                                | 15  |

| 2.2 | Different logic networks for a 4-bit adder                    | 17  |

| 2.3 | Example of various MIG structures                             | 18  |

| 2.4 | Example of AIG rewriting                                      | 19  |

| 2.5 | Example of MIG optimization using the algebraic rewriting     | 21  |

| 2.6 | Boolean rewriting in MIGs                                     | 27  |

| 2.7 | Example of 3-cut over AIG                                     | 29  |

| 3.1 | Chapter organization                                          | 34  |

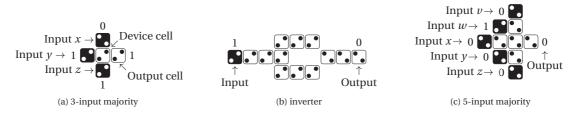

| 3.2 | QCA layout for various gates                                  | 37  |

| 3.3 | 0 1 0                                                         | 37  |

| 3.4 | 1                                                             | 40  |

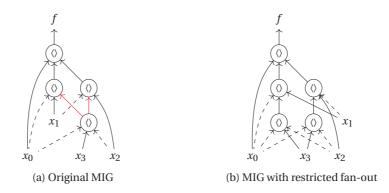

| 3.5 | Example of inverter propagation on MIG                        | 45  |

| 3.6 | Example of inverter propagation with size increase            | 45  |

| 3.7 | Example of fan-out restriction on MIG                         | 47  |

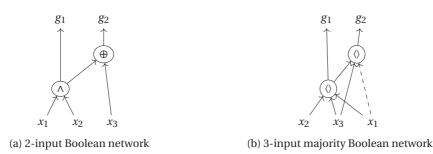

| 3.8 | Exact synthesis: 2-input and 3-input Boolean networks example | 50  |

| 4.1 | Chapter organization                                          | 66  |

| 4.2 | Example of BDD for function $clique_{4,3}$                    | 69  |

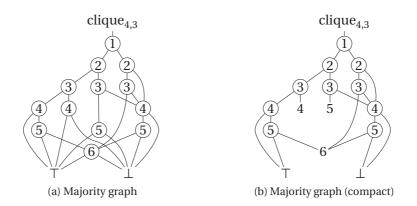

| 4.3 | Example of majority-graph                                     | 71  |

| 4.4 | Example of leafy majority graph                               | 73  |

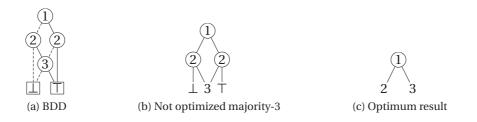

| 4.5 | Mapping the majority-3 from its optimal BDD                   | 74  |

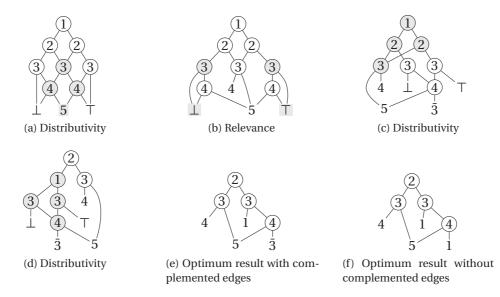

| 4.6 |                                                               | 76  |

| 4.7 | Decomposing majority-7 into majority-3                        | 77  |

| 4.8 | Optimum majority-7                                            | 78  |

| 4.9 | Decomposing majority-9 into majority-3                        | 79  |

| 5.1 | 1 0                                                           | 00  |

| 5.2 | Boolean difference example                                    | .03 |

#### List of Figures

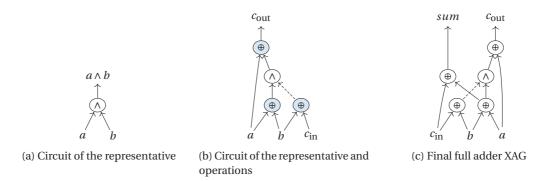

| 5.3 | Example of XAG                                  | 110 |

|-----|-------------------------------------------------|-----|

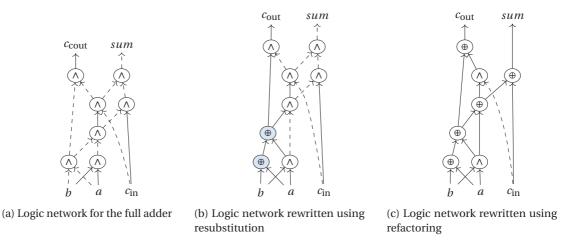

| 5.4 | Rewriting example over XAG                      | 113 |

| 5.5 | Resubstitution and refactoring example over XAG | 117 |

# List of Tables

| 1.1  | Correspondance between chapters, contents, and publications                      | 7   |

|------|----------------------------------------------------------------------------------|-----|

| 3.1  | Results for size optimization over MIGs                                          | 43  |

| 3.2  | Results of inversion propagation and fan-out restriction over MIGs               | 48  |

| 3.3  | Comparison of the proposed exact synthesis to state-of-the-art methods           | 58  |

| 3.4  | Comparison of quality of results of the proposed exact synthesis algorithms      | 59  |

| 3.5  | Results of exact synthesis with constraints on LUTs of larger benchmarks         | 59  |

| 3.6  | Technology parameters for QCA                                                    | 60  |

| 3.7  | Inversion-free and fan-out restriction on QCA                                    | 61  |

| 3.8  | Technology parameters for STMG                                                   | 62  |

| 3.9  | Inversion-free and fan-out restriction on STMG                                   | 63  |

| 3.10 | Results for size optimization after QCA and STMG mapping                         | 64  |

| 4.1  | Upper bounds on the number of majority-3 operations to realize majority- $n$ .   | 81  |

| 4.2  | L(f) and $C(f)$ for self-dual monotone 7-input classes                           | 88  |

| 4.3  | L(f) and $C(f)$ for self-dual monotone 7-input functions from state-of-the-art . | 91  |

| 4.4  | C(f) for self-dual monotone 7-input functions with inverters                     | 91  |

|      |                                                                                  |     |

| 5.1  | Best 6-LUT area results for the EPFL benchmarks                                  | 108 |

| 5.2  | Smallest AIG results for the EPFL benchmarks                                     | 109 |

| 5.3  | Post Place&Route results on 36 industrial design for ASICs                       | 109 |

| 5.4  | Experimental results for EPFL benchmarks using rewriting                         | 120 |

| 5.5  | Experimental results for EPFL benchmarks with complete flow                      | 122 |

| 5.6  | Experimental results for MPC and FHE benchmarks using the rewriting algorithm    | 123 |

| 5.7  | Experimental results for MPC and FHE benchmarks using the complete flow .        | 123 |

| 5.8  | Experimental results for MPC benchmarks                                          | 125 |

# List of Acronyms

| ADEP area-delay-energy product                     |

|----------------------------------------------------|

| AIG and-inverter graph                             |

| AOI and-or-inverter                                |

| AOIG                                               |

| ASICs Asplication specific integrated circuits     |

| BDD binary decision diagram                        |

| CEGAR counter-example-guided abstraction refinemen |

| CMOS complementary metal-oxide-semiconductor       |

| CNF                                                |

| EDA electronic design automation                   |

| FHE fully homomorphic encryption                   |

| FPGAs field-programmable gate arrays               |

| ICs integrated circuits                            |

| MFFC free cone                                     |

| MIG graph                                          |

| MPC multi-party computation                        |

| MSPF Maximum set of permissible functions          |

| MTJ magnetic tunnel junctions                      |

| PI primary input                                   |

| PO primary output                                  |

#### List of Acronyms

| QCAduantum-dot cellular automata |

|----------------------------------|

| QoR quality of results           |

| ReRAMs resistive RAMs            |

| RTL register-tranfer level       |

| SAT satisfiability               |

| SET single-electron transistor   |

| SOP sum-of-product               |

| SPP                              |

| STMG spin torque majority gate   |

| STT                              |

| TFO transitive fan-out           |

| XAG xor-and graph                |

| XMG graph                        |

## **1** Introduction

Electronic circuits are omnipresent and considered an essential part of our everyday life. In the last decades, they have experienced tremendous growth that has been enabled by a wide range of tools to abstract, represent, and manipulate digital circuits as well as to optimize their realization. Such tools are called, all together, *electronic design automation* (EDA) tools and are responsible for the fast evolution of electronic circuits. This progress of electronic circuits was also due to the continuous downscaling of *complementary metal–oxide–semiconductor* (CMOS) transistors dimensions that enabled the semiconductor industry to decrease the cost and area of digital designs while increasing their performance [129]. Nowadays, transistor scaling is reaching the limit of what is physically achievable; EDA tools are thus left with the important challenge of further pushing the performances and *quality of results* (QoR) of digital circuits.

*Logic synthesis* is a key component of digital design and modern EDA tools [2, 3, 4]; it is thus an essential instrument for the design of leading-edge chips, and to push the limits of performance (upwards) and power consumption (downwards). In the last two decades, the electronic circuits and digital systems community has evolved dramatically, facing many architectural and technological changes. Consequently, EDA and logic synthesis have adapted and changed to be able to accurately design the new generation of digital systems. In the present days, logic synthesis is an important area of research for two main reasons:

(*i*) Many and diverse ways of computation, alternative to CMOS, have been presented in the last years. Post-silicon technologies (also called emerging nanotechnologies) have been shown to be feasible and may provide us with better – more efficient – electronic devices. In a similar way, new architectures such as neuromorphic [68] and quantum computing [57] are becoming more and more practical. Finally, novel areas of applications of logic synthesis are emerging, ranging from deep learning [53] to cryptography and security applications [149].

(*ii*) The current computing and storage means make it possible to solve exactly problems that were only approximated before. Moreover, new reasoning engines, covering from deep learning to new SAT-solvers, can be used as a means of computation, thus possibly unlocking novel optimization opportunities and enabling hardware of higher-quality [82, 193].

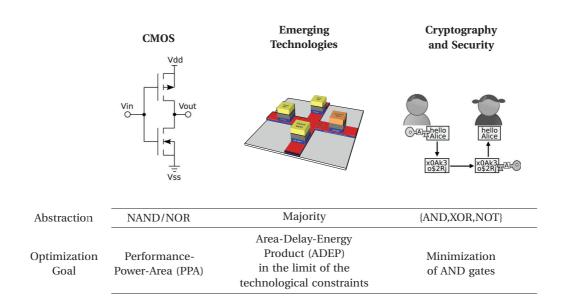

Figure 1.1 – Some examples of novel and standard paradigms of computations and applications for logic synthesis. Standard CMOS-based design uses NAND/NOR, and aims at optimizing the PPA, while emerging technologies are often based on the majority function. Cryptography applications are modeled using the basis {AND,XOR,NOT}. In this case, the minimization of the number of AND gates is desirable for applications such as *fully homomorphic encryption* (FHE) and *multi-party computation* (MPC)

As a result of the novel paradigms of computation, applications, and resources, the circuit primitives for logic design have increased and changed over the years [174]. Some examples – relevant to the rest of the thesis – are presented in Figure 1.1. CMOS technology has always favored circuits based on NORs, NANDs, and their extensions. Thus, today the majority of state-of-the-art tools handle these primitives and their extensions (e.g., AND-OR-Inverter gates) to represent and optimize logic circuits. On the other hand, new emerging technologies, such as some optical technologies [72] and *quantum-dot cellular automata* (QCA) [106], leverage majority (MAJ) and inverter (INV) gates as primitives. Neuromorphic architectures exploit threshold gates, which can be seen as majority gates with weighted inputs, and the basis {AND, XOR, NOT} [36] is often used in the modeling of cryptography circuits. In a similar way, novel cost functions and optimization goals have arisen. As an example, logic synthesis for cryptography considers as optimization goal the number of AND gates, which correlates to the degree of vulnerability of a function. Emerging technologies such as *spin torque majority gate* (STMG) [135], which can efficiently realize the majority operator, are on the contrary unable to implement an inverter. It follows that inverter-free circuits are desirable.

In view of the progress and novel opportunities of technology, logic synthesis has to be revisited while considering the plurality of primitives and novel engines that can be of interest, and, consequently, the corresponding objective functions and optimization problems. The

Figure 1.2 - Simplified EDA flow

goal of this thesis is to present a variety of novel data structures and algorithms, addressing diverse types of applications in modern logic synthesis. We thus present several logic synthesis methods and we show their applicability to standard and emerging technology applications.

#### **1.1 Electronic Design Automation**

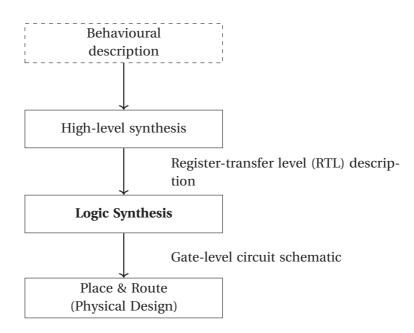

The term EDA refers to the tools, algorithms, and methods used to automatically design *integrated circuits* (ICs) and general electronic systems. A typical EDA flow starts from a high-level description of such electronic system and generates a final implementation in terms of technology components. This is achieved thanks to several steps of logic abstractions and algorithms, usually called: *high-level synthesis, logic synthesis,* and *physical design* [69].

For the sake of this thesis, we present an oversimplified EDA flow as depicted in Figure 1.2. In particular, high-level synthesis converts a programming language description (behavioural description) into a *register-tranfer level* (RTL) netlist [49]. This step determines the macroscopic structure of the circuits, and it is thus also called *structural synthesis*. On the contrary, *logic synthesis* produces the microscopic (in terms of logic gates) structure of the circuit [37, 84]. It optimizes and manipulates RTL netlists into logic models that are interconnections of logic primitives. The last step of a standard EDA flow (see Figure 1.2) is *physical design*, which consists of *placement* and *routing* (P&R) [141]. This step is responsible for generating the final layout of the chip and provides the link with the fabrication process. Placement refers to the assignment of positions to the cells while routing deals with their interconnections. Note that, modern EDA flows do not clearly separate between these three steps, but aim at more integration between them [5, 94].

In conjunction with synthesis, *optimization* is usually considered. It means, all the three presented steps are usually constrained to consider a given optimization metric, that could be for instance area, power, and or delay of the digital circuit. Nowadays, most synthesis and optimization algorithms are tuned to work on CMOS technology. CMOS technology provides an efficient realization of NORs, NANDs and *and-or-inverters* (AOIs) which can be abstracted as negative unate functions. Consequently, most EDA tools use these primitives to abstract and optimize circuits. In a similar way, placement and routing algorithms changed consequently to the technological evolution of CMOS down to the nano-scale.

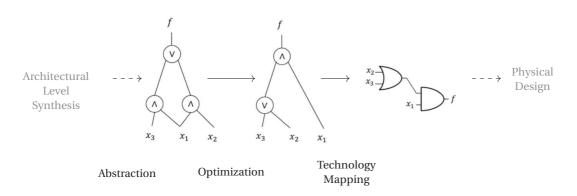

In this thesis, we focus on *logic synthesis*. Recall that logic synthesis is the process by which an abstract form of desired circuit behavior, typically at RTL, is turned into an optimized design implementation in terms of logic gates (depicted in detail in Figure 1.3). Common examples of this process include synthesis of hardware description languages (including VHDL and Verilog), which are specialized computer languages used to program the structure, design, and operation of digital logic circuits. Broadly speaking, the overall problem of logic synthesis is one of finding "the best implementation" of a logic function, where the term "best" may depend on goals and computational methods and it may not be unique. Thus, synthesis encompasses also logic optimization.

In logic synthesis, the logic circuit is abstracted as a logic network, which is usually defined over a set of primitive logic gates. The first approaches to logic synthesis addressed two-level *sum-of-product* (SOP) representations and attempted to reduce the cardinality of logic covers (i.e., the number of product-terms also called implicants). For example, the first logic synthesis algorithm (dated back to 1956) is the Quine-McCluskey algorithm [112], which solves the minimization of logic covers exactly. Several approaches to heuristic minimization of two-level forms [69] ended up instead in the program ESPRESSO [37, 154] that had a large impact on the design automation community of the time. Contemporary logic synthesis and its successes have risen in the 80s with the establishment of CMOS technology. In modern industrial flow, efficient multi-level logic representations are involved. Being based on CMOS,

modern logic synthesis flow mainly use AND/OR primitives to abstract and optimize logic (see Figure 1.3). Note that most approaches divide synthesis into a *technology-independent* phase, where the interconnection of logic blocks is minimized independently of the library, followed by a *technology mapping* step where the instances of library elements are chosen. As an example of technology mapping, in the case of *application specific integrated circuits* (ASICs), the logic model is mapped into standard cells, while it is transformed into look-up-tables for *field-programmable gate arrays* (FPGAs) [45].

#### 1.2 Research Motivation

In recent years, EDA tools and researches have been facing new and difficult challenges. On one side, as transistor scaling slows down at advanced technology nodes, e.g., 10nm, 8nm, 7nm, EDA solutions are becoming essential to keeping up with the (expected) QoR. This motivates EDA researchers (and logic synthesis) to push further the optimization tools and revisit high-quality and high-computational-complexity optimization methods in light of modern computing capabilities. On the other hand, novel synthesis tools need to adjust and reshape to take into account the novel paradigm of computation given by modern and emerging nanotechnologies, as well as, new fields of application such as quantum computers and security.

This thesis investigates novel logic synthesis data structures and algorithms that find application in both these tasks, being thus responsible for designing competitive CMOS circuits (Section 1.2.1), but also addressing alternative applications (Section 1.2.2) as emerging technologies and cryptography and security applications.

#### 1.2.1 Modern CMOS Technologies

Modern logic synthesis, together with the EDA community, is challenged every day. Novel logic synthesis methods and data structures need to be examined, together with a reinvestigation of already existing methods in light of the modern (and more powerful) computing potential.

As a matter of fact, standard CMOS-based logic synthesis is constrained in using mainly AND/OR primitives. For this reason, in recent years, the logic synthesis community has mainly investigated alternative and more expressive data structure and logic functions. This has resulted for instance in the *majority-inverter graphs* (MIGs) [14] or *xor-majority graphs* (XMGs) [81], which use majority and XOR as the main Boolean function for representing and optimizing logic. Even though remarkable results have been already demonstrated, much work is still needed in this regard, to build *complete* synthesis flows based on these alternative functions and to investigate theoretical properties and optimization potential. Furthermore, expensive Boolean methods (that involve expensive runtime tasks) are usually used cautiously in modern EDA flows, where faster algebraic methods are instead preferred. Boolean methods usually achieve better results as compared to algebraic methods, as they consider the Boolean

nature of the functions. This leaves many possible optimization opportunities still unexplored.

#### **1.2.2** Alternative Applications

In the last years, many and diverse emerging technologies have been presented, based on new paradigms and ways of computation. Moreover, recently, logic synthesis has been employed for the optimization of circuits in various domains, ranging from quantum computers to cryptography circuits.

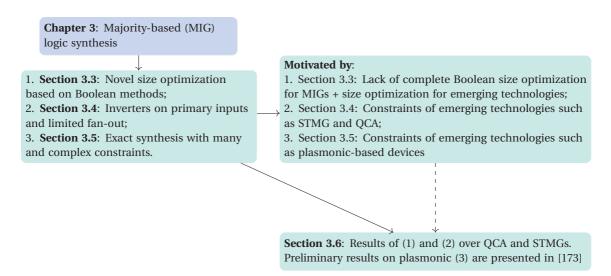

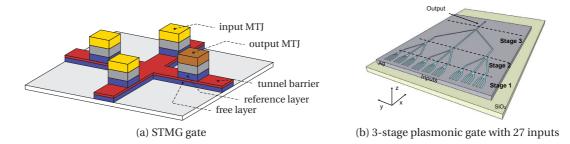

Even though CMOS technology will be the core of modern digital systems for at least another decade, logic synthesis and EDA tools need to start revisiting their optimization methods in order to be able to efficiently abstract and optimize future technologies. Examples of majority-based nanotechnologies include QCA [106], superconducting electronic devices (RSFQ [107] and AQFP [169]), STMG [135] and plasmonic-based devices [72]. For example, the recently proposed plasmonic technology [72] is a promising alternative to CMOS-based design thanks to the waveguide's low power consumption and high speed of computation. Besides these qualities, this novel technology also implements different functionalities uncommon to traditional CMOS. First, plasmonic devices are intrinsically based on the majority-voter operation; moreover, they can efficiently implement threshold functions up to 27-input. On the other hand, this expressive power comes at some costs. Indeed, the 27-input block is the largest building block that can be implemented today using the mentioned plasmonic technology. This is due to the fact that the propagation losses put a limitation on the maximum number of cascaded stages (i.e., the number of levels of the circuits). Currently, it is not efficient to have more than three stages, which means that, after the third stage, either an amplifier or a converter to the voltage domain is necessary [72]. Other technologies, as for example STMG, suffer instead the lack of inverter implementation, thus inverters-free circuits are needed. QCA technology has unefficient implementation of inverters, thus benefit from their minimization [176].

Consequently, logic synthesis and EDA tools are even more important. Not only they need to be able to abstract efficiently such novel functionalities but also to investigate their design capabilities. They are left with the important task of studying and examining the design limits of such technologies in circuit implementation, in order to help in deciding for the next generation of technologies.

#### **1.3 Thesis Contributions**

This thesis is centered around logic synthesis, in particular, on novel data structures and algorithms addressing standard CMOS technologies as well as novel applications (i.e., emerging technologies and cryptography). In the following, our contributions are classified according the Boolean function involved in the optimization and abstraction. Our contributions are thus divided into two main categories: *majority-logic* and *XOR-logic*. To ease the reading of

|                      | Торіс                                        | Chapter                | Reference                          |

|----------------------|----------------------------------------------|------------------------|------------------------------------|

| Majority-based Logic |                                              |                        |                                    |

|                      | Emerging Technologies<br>Theoretical Results | Chapter 3<br>Chapter 4 | [151, 180, 181]<br>[166, 172, 177] |

| YOP based Logic      |                                              | enup ter 1             | [100, 11-, 111]                    |

| XOR-based Logic      | Standard Synthesis Flow                      | Chapter 5              | [170, 171]                         |

|                      | Cryptography and Security                    | Chapter 5              | [175, 178]                         |

Table 1.1 - Correspondance between chapters, contents, and publications

the thesis, our achievements are here presented in the same order they will appear in the chapters of the thesis. Table 1.1 summarizes the topics and their corresponding publications and chapters.

#### 1.3.1 Majority-based Logic Syntesis

The methods and abstractions presented here are based on the majority function, denoted by  $\langle x_1, x_2, ..., x_n \rangle$ , where *n* is the (odd) number of inputs. The achievements and their position concerning previous works are organized and summarized according to (i) logic synthesis for emerging technologies, and (ii) theoretical results.

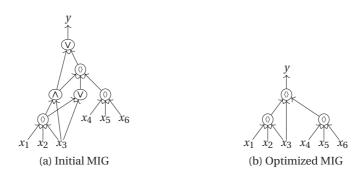

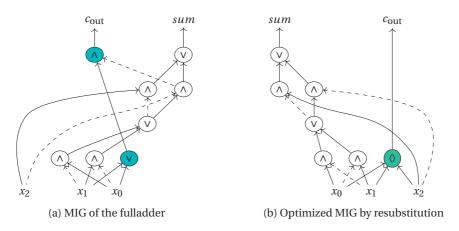

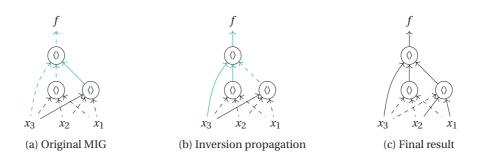

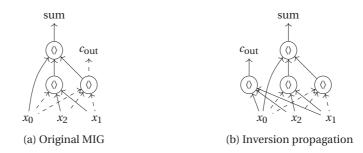

• Emerging Technologies: Motivated by the many emerging technologies that easily implement majority gates, this first part of the thesis presents novel algorithms over MIGs. First, a novel optimization flow based on Boolean transformations is proposed. The flow aims at size optimization over MIGs, next mapped into QCA and STMG. Second, novel techniques to consider constraints of emerging technologies inside MIGs state-of-the-art synthesis flows are evaluated. First, we deal with inversion and fan-out limitations of majority-based technologies such as QCA and STMG. Second, we propose an *exact synthesis* method for circuits with limited fan-out and constrained depth. Our results in logic synthesis for emerging technologies are in Chapter 3 and have been published in the following publications [151, 180, 181]. This section is the result of our fruitful collaboration with the IMEC research center in Leuven, Belgium.

#### **Relation to Previous Works**

Majority logic owes its renewed interest to many emerging nanotechnologies that naturally implement majority as their primitive building block [18]. Indeed, because Moore's law [129] will reach its end in the next decade [195], alternative devices need to be implemented and designed.

MIGs allow remarkable logic representation and optimization. A logic optimization flow that employs algebraic and Boolean methods for MIG depth reduction has been recently

Figure 1.4 – Explanation of the majority function: the majority function of three inputs evaluates to true if and only if at least two of the three inputs are true. Source *http://redpanels.com/36/*

presented in [16]. However, these optimization methods are not able to obtain the same results when considering MIG size. Work on size reduction of MIGs is quite sparse [81, 101, 161] and suffers from scalability issues when exact synthesis is involved [81, 161]. Our goal is to present a flow for the size optimization of MIGs. Being Boolean, our flow has a positive effect on the quality but it is challenging in the implementation. We overcome these limits by using windowing techniques, truth tables, and Boolean filtering rules.

Many recent works have instead specifically considered logic synthesis for emerging technologies [18]. As an example, the works in [127, 194] addresses majority-based nanotechnologies by mapping the resulting networks into majority based devices such as QCA and *single-electron transistor* (SET). The work in [28] considers instead logic synthesis for emerging memories, as *resistive RAMs* (ReRAMs), and the one in [32] demonstrates how to implement the *implication* function with memristors. Finally, Zografos et al. [198] presented an MIG-based method for the synthesis of circuits based on spin-wave devices. In our work, we map majority networks into QCA and STMG by using area, delay, and power estimations obtained at IMEC research institute. Moreover, we also demonstrate how to integrate the constraints of such technologies into the synthesis flow. This is achieved by proposing novel algorithms or by adjusting already existing ones.

• **Theoretical Results:** This part of the thesis continues our investigation of majoritybased logic synthesis and MIGs, but shifts to theoretical results and new identities. We present a novel *binary decision diagram* (BDD)-based method to map monotone majority functions over *n* inputs (majority-*n*) into MIGs. In particular, their optimum-size representations are discussed and novel upper bounds and decompositions are investigated. Moreover, *complexity* studies over self-dual monotone functions in terms of majority gates are studied. The results for these theoretical results are presented in Chapter 4 and published in [166, 172, 177].

#### **Relation to Previous Works**

Majority logic was intensively studied in the 1960s [8, 12, 115]. In 1964, Amarel et al. [12] proposed algorithms to rewrite majority-*n* into majority-3. At that time, many majority-based

algorithms were proposed but, due to the limited available computational resources, they were not followed by implementations. Recently, a generalization to the majority operation of n inputs has been presented in [13, 55]. In [17], the authors consider majority logic decomposition based on BDDs. In [17], majority dominator nodes are used to guide the decomposition process; these nodes allow the identification of candidate functions that can be used to build the majority decomposition. Although BDDs are used in the implementation of their algorithm, it has a very different nature compared to our work, in which we equate BDDs to majority graphs in the case of monotone Boolean functions. Moreover, our method finds upper bounds and decompositions rules that put the basis for novel theoretical investigation on majority-n logic.

Concerning self-dual monotone functions, we make use of exact synthesis to study their complexity, which is defined as the minimum number of gates to realize a Boolean function over majority operators or as its shortest formula. Generally, the study of the complexity of Boolean functions deals with finding some upper bounds [78, 88] or lower bounds [139] over a set of primitives. In our case, we are instead concerned with finding exact numbers for the complexity of functions over majority operators. In [97], the complexity for all 4- and 5-input Boolean functions in terms of 2-input Boolean operators have been studied, while 3-input Boolean operators have been used in [83]. We deal instead with 7-input functions over 3-input majority operators, in particular, we investigate the positive effect of the inverters in reducing the complexity of this class of functions, and the negative impact of some constraints.

#### 1.3.2 XOR-based Logic Synthesis

The methods and abstractions presented are based on the XOR function, denoted in the thesis with the symbol  $\oplus$ . The achievements and their position with respect to previous works are organized and summarized according to (i) standard logic synthesis, and (ii) logic synthesis for cryptography and security.

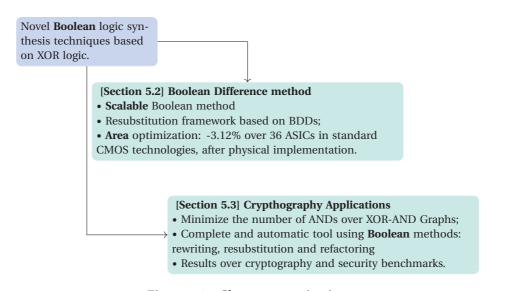

• **Standard Logic Synthesis:** This part presents a novel optimization flow based on the Boolean difference. Note that the Boolean difference operation is the XOR of two Boolean functions. Motivated by the novel computing capabilities, and in contrast to the previous sections, this part of the thesis shows more practical aspects of logic synthesis, designed to be successful in modern logic synthesis flows. The flow aims at area optimization addressing standard CMOS technologies (ASICs design). The results are evaluated after place & route, maintaining a reasonable runtime budget for the optimization flow. The results are computed on 36 commercial benchmarks. This section is the result of a 3-months internship at Synopsys Inc., California, US. This achievement is fully described in Chapter 5 and has resulted in the publication [171] and submission [170].

#### **Relation to Previous Works**

The interest in Boolean methods is due to the continuous need for improvement in QoR faced

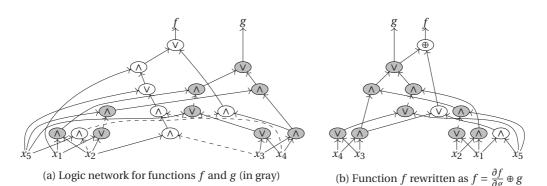

by the EDA community (as already stressed in the previous sections). Among all Boolean methods, a central role is played by Boolean resubstitution, which, in practice, is considered the most powerful method in terms of QoR. It takes advantage of don't cares [66] and *permissible functions* [131] to express the function of a node using other nodes already present in the logic network to achieve a more compact implementation. The recent work in [19] has demonstrated novel resubstitution techniques based on truth tables, and their efficient scalability in industrial flows. Our work continues this research study, by presenting a novel Boolean resubstitution method that uses an XOR-based technique together with BDDs to further decrease the area, but without increasing the runtime.

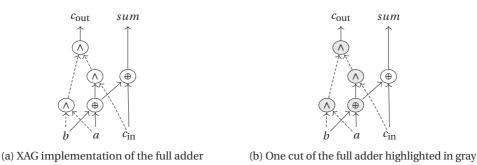

• **Cryptography and Security:** The last part of the thesis continues XOR-based logic synthesis, but investigates a novel application of logic synthesis for crythography and security applications. We introduce a novel complete and automatic synthesis flow which consists of the main transformations involved in logic synthesis, being rewriting, resubstitution, and refactoring. The goal is the minimization of the number of AND gates over *xor-and graphs* (XAGs), which correlates with the degree of vulnerability (security) of a cryptography benchmark. In this scenario, the XOR operation is "for free". This achievement is fully described in Chapter 5 and in the publications [175, 178].

#### **Relations to Previous Works**

Logic synthesis for cryptography has recently become subject of growing interest. In this scenario, logic synthesis uses XAGs as data structure to represent and optimize logic. Further, it aims at the minimization of the number of AND gates. Novel optimization techniques are thus needed since state-of-the-art tools [40, 190] automatically address size optimization, without precisely minimizing the number of ANDs. Recently, the works in [33, 60, 149] have started this new domain of application for logic synthesis. Unfortunately, the methods from the cryptography community rely heavily on manual decomposition and optimization strategies [33], while the method in [149] implements few changes to a commercial CMOS-based tool without explicitly designing specific algorithms. Our methods and tool focus on implementing a complete and automatic flow, to address these novel applications. Our algorithms are instead specifically designed to consider a different abstraction based on AND and XOR, and to minimize the number of ANDs, which has been demonstrated beneficial for diverse cryptography applications [64, 100, 183].

#### 1.4 Thesis Organization

This thesis is organized as follows:

• **Chapter 2 – Background:** This chapter introduces the background needed to understand the rest of the thesis. It provides an overview of the most important data structures and algorithms involved in classical logic synthesis. It also considers recent advances in exact synthesis methods.

- Chapter 3 Majority-based Logic Synthesis: In this chapter, we present novel algorithms and techniques that work over MIGs. Specifically, we propose novel Boolean methods for size optimization, demonstrating an 18% average size reduction. Particular focus is also given to the synthesis and design of majority-based logic for emerging technologies, as QCA and STMG. Such emerging technologies use the majority function as their main building block but suffer from diverse technological constraints that need to be considered in the synthesis flow. For this purpose, the chapter presents (i) techniques to limit the fan-out of the majority gates and move inverters on primary inputs; and (ii) exact synthesis methods to limit both depth and fan-out of MIGs. As already pointed out, these constraints are due to the physical limitations of the considered emerging technologies.

- **Chapter 4 Majority-n Logic:** This chapter continues the study of majority logic, but moves to more theoretical aspects. In particular, the chapter mainly addresses the problem of "how best can the n-argument majority function (majority-*n*) be realized with a network of 3-input majority gates?". For this purpose, we present a novel method that directly maps BDDs of monotone functions into majority graphs. The proposed methods allow us to obtain the optimum network for the majority-5 and majority-7, and the best-known circuit for the majority-9. Novel general upper bounds and novel decompositions are also presented. The majority function is both self-dual and monotone; thus, the chapter also focuses on the study of self-dual monotone functions and their complexity. As an example, it demonstrates how the inverter can help in reducing the complexity of 7-input functions over majority graphs.

- **Chapter 5 XOR-based Logic Synthesis:** In this chapter, we move from the majority logic to the XOR-based logic synthesis. We present two different applications: (i) CMOS-based logic synthesis and (ii) logic synthesis addressing cryptography and security applications. For the CMOS-based design, we developed a novel XOR-based resubstitution method for the size optimization of digital circuits. Our flow results in a remarkable area and power reduction after place & route. The latter considers logic synthesis for an alternative application in cryptography. For this purpose, we developed a novel framework to minimize the number od AND gates (called *multiplicative complexity*) of XAGs, which is a metric that directly correlates to the vulnerability of the circuits. The new framework is successfully tested on two sets of cryptography benchmarks.

- **Chapter 6 Conclusions:** Finally, this chapter concludes the thesis. A summary of research accomplishments is presented, together with future perspectives.

To summarize, this thesis presents novel logic synthesis algorithms for the optimization of standard CMOS-based applications. It takes advantage of modern – more advanced – computing capabilities to push further the optimization results of existing flows. It also introduces technology-dependent logic synthesis as an essential step for the abstraction

#### **Chapter 1. Introduction**

and manipulation of novel and diverse majority-based emerging technologies. Moreover, it advances state-of-the-art theoretical results on majority logic. Finally, this thesis establishes a novel field of application for logic synthesis, in the cryptography and security field.

## 2 Background

This thesis targets the development of novel data structures and algorithms within logic synthesis for standard and emerging technologies. This chapter is dedicated to the background and preliminaries needed through the whole thesis and aims at giving a broad overview of this field [174]. First, we introduce the data structures involved in logic synthesis to represent logic. These include *truth tables, binary decision diagrams* (BDDs), 2-level and multi-level logic forms. Then, we describe the algorithms for logic function optimization. Both heuristic algebraic and Boolean methods are described, followed by exact methods and synthesis. Finally, we overview methods to partition circuits into smaller sub-units for the application of runtime-expensive methods (e.g., Boolean resubstitution) in a controlled manner.

In the following, we assume that the reader is familiar with the basic concepts of Boolean algebra and Boolean functions; we refer the reader to [44, 69, 97] for further background.

#### 2.1 Data Structures

We present various data structures that are commonly used by logic synthesis algorithms. The subsections are ordered according to the scalability of the data structures, starting from truth tables, which are suitable for functions with a small *support* (i.e., number of variables), to multi-level logic networks, which are the data structure (in various forms and shapes) to represent Boolean functions in almost all modern research and commercial tools.

#### 2.1.1 Truth Tables

A truth table is an explicit representation where the function values are listed for all possible input combinations. Formally, a truth table for a Boolean function  $f(x_1,...,x_n)$  is a bitstring  $b_{2^n-1}b_{2^n-2}...b_1b_0$  of  $2^n$  bits, where  $f(x_1,...,x_n) = b_x$  such that  $x = (x_n...x_1)_2$  is the integer representation of the input assignment. Consequently, we may also consider a truth table as a number in the half-open interval  $[0,2^{2^n})$ , for which the truth table representation is the binary expansion of that number.

**Example 2.1** The truth table for a majority-of-three (majority-3) function  $\langle x_1 x_2 x_3 \rangle = (x_1 \lor x_2) \land (x_1 \lor x_3) \land (x_2 \lor x_3)$  is 11101000, where  $\land$  and  $\lor$  are the AND and OR, respectively. Since the binary notation can quickly become very large, it is customary to use a hexadecimal notation, in which each block of 4 bits is represented by the corresponding hexadecimal digit. For the majority-of-three function, the hexadecimal truth table is e8.

A truth table is a *canonical* (i.e., unique) representation of a function. Consequently, for small functions, truth tables can be used for a simple equivalence check of two functions, if a truth table can be efficiently derived from them.

#### 2.1.2 2-level Representations

Logic functions can be represented in *disjunctive normal form*, also referred to as *sum-of-product* (SOP),

$$f = p_1 \vee p_2 \vee \dots \vee p_k \tag{2.1}$$

where each

$$p_{i} = x_{1}^{q_{i,1}} \wedge x_{2}^{q_{i,2}} \wedge \dots \wedge x_{n}^{q_{i,n}}$$

(2.2)

is a *product* of literals with  $0 \le q_{i,j} \le 2^R - 1$  for  $1 \le i \le k$  and  $1 \le j \le n$  and where *R* is a radix. We have R = 2 for binary Boolean logic, R = 3 for ternary logic, etc. This represents the so called *positional cube* notation [69] where usually the  $q_{i,j}$  are represented in binary form. Therefore, for binary-valued logic the negative and positive literals are  $x^1 = x^{\{01\}} = \bar{x}$  and  $x^2 = x^{\{10\}} = x$ , respectively,  $x^3 = x^{\{11\}}$  is a *don't care* term (i.e., both values of a variable are possible) and  $x^0 = x^{\{00\}} = \phi$  is the empty set (i.e., no value).

**Example 2.2** Let  $f(x_1, x_2, x_3) = x_1 ? x_2 : x_3$ , which is also called the if-then-else operator. A disjunctive normal form is  $f = x_1 x_2 \bar{x}_3 \lor x_1 x_2 x_3 \lor \bar{x}_1 x_2 x_3 \lor \bar{x}_1 \bar{x}_2 x_3$ . An alternative, shorter form is  $f = x_1 x_2 \lor \bar{x}_1 x_3$ . In general, one is interested in finding a disjunctive normal form that minimizes the number of product terms k.

Many algorithms have been presented to find disjunctive normal forms with some minimality properties (see, e.g., [156]). Also, other 2-level representations have been investigated. Examples are *conjunctive normal form* (CNF), or *product-of-sums* (that interchange ' $\lor$ ' and ' $\land$ ' in (2.1) and (2.2)) or *exclusive sum-of-products* (which use ' $\oplus$ ' instead of ' $\lor$ ' in (2.1)). Conjunctive normal forms play a central role in *Boolean satisfiability* solving (see, e.g., [29, 98]) and can be seen as the dual representation of disjunctive normal forms [44]. Exclusive sum-of-product representations find extensive use in cryptography applications (see, e.g., [35, 36, 50]) and quantum computing (see, e.g., [75, 124]).

Figure 2.1 – BDD for the function  $(x_1 \oplus x_2) \lor (x_3 \oplus x_4)$

#### 2.1.3 Binary Decision Diagrams

Logic functions can be expressed by *decision diagrams* in many ways. The most common representation is the BDD [46, 97] which is a directed acyclic graph where internal nodes are associated with the Shannon expansion of the function, i.e.,  $f = x_i f_{x_i} \oplus \bar{x}_i f_{\bar{x}_i}$ , where  $f_{x_i}$  and  $f_{\bar{x}_i}$  are the *cofactors* obtained from f when the variable  $x_i$  is assigned 1 or 0, respectively. When referring to BDDs, it is usually implicitly understood that the variables are ordered and the diagram reduced (i.e., BDD refers to ROBDDs [46]). Moreover BDDs are constructed and manipulated so that redundancy is avoided, and thus they are canonical representations of logic functions.

**Example 2.3** Figure 2.1 shows the BDD for the function  $(x_1 \oplus x_2) \lor (x_3 \oplus x_4)$ . Solid and dashed lines represent here positive and negative cofactors respectively. Two terminal nodes labeled ' $\bot$ ' and ' $\top$ ' represent the constant functions 0 and 1.

BDDs exploit the fact that for many functions of practical interest, smaller subfunctions occur repeatedly and need to be represented only once. Combined with an efficient recursive algorithm that makes use of caching techniques and hash tables to implement elementary operations, BDDs are a powerful data structure for Boolean function representation and manipulation. Indeed, algorithms for BDD manipulation have polynomial-time complexity (usually quadratic or cubic) in the number of nodes, and such a number grows mildly with the problem size (i.e., variables) in many—but not all—cases, e.g., multipliers are an exception.

The variable order in BDDs affects their size. Improving the variable ordering for BDDs (i.e., minimizing the BDD graph size) is NP-complete [31]. An exact algorithm [71] and many heuristics [76] have been presented that aim at finding a good ordering. It is easy to fit a single BDD node, which contains the variable index and pointers to its two children, into a single 64-bit unsigned integer [97]. Thus, BDDs can represent a good scalable representation for logic functions. They can cope with larger functions as compared to truth tables. When their storage becomes excessive, functions are usually decomposed into blocks forming logic networks.

#### 2.1.4 Multi-level Logic Networks

A multi-level *logic network* is an interconnection of blocks, each implementing a logic function and whose representation style may vary. The interconnection is modeled by a directed acyclic graph where nodes represent primary inputs and outputs, as well as local functions. In most cases such functions are restricted to have a single output, by similarity to CMOS logic gates. For internal nodes, the indegree and outdegree are referred to as *fan-in* and *fan-out* respectively. Note that logic networks can be extended to deal with sequential cyclic circuits [69], but such cases are not considered here.

We use a formal notation for logic networks, that is also referred to as *Boolean chains* in the literature [97]. Given primary inputs  $x_1, \ldots, x_n$ , a logic network consisting of r local functions is a sequence

$$x_i = f_i(x_{i_1}, x_{i_2}, \dots, x_{i_{ar(f_i)}}) \quad \text{for } n < i \le n + r,$$

(2.3)

where  $f_i$  is a gate function with  $ar(f_i)$  inputs and  $0 \le i_j < i$  for  $1 \le j \le ar(f_i)$  are indexes to primary inputs or previous gates in the sequence. For convenience, we define  $x_0 = 0$ . Also, we define a sequence of primary outputs  $y_1 = x_{o_1}, \dots, y_m = x_{o_m}$ .

**Example 2.4** A full adder with inputs  $x_1, x_2, x_3$  can be realized by the network

$$x_4 = x_1 \oplus x_2 \oplus x_3, \qquad x_5 = \langle x_1 x_2 x_3 \rangle$$

with outputs  $y_1 = x_4$  for the sum and  $y_2 = x_5$  for the carry. The network uses the parity function  $f_4$  and the majority function  $f_5$ .

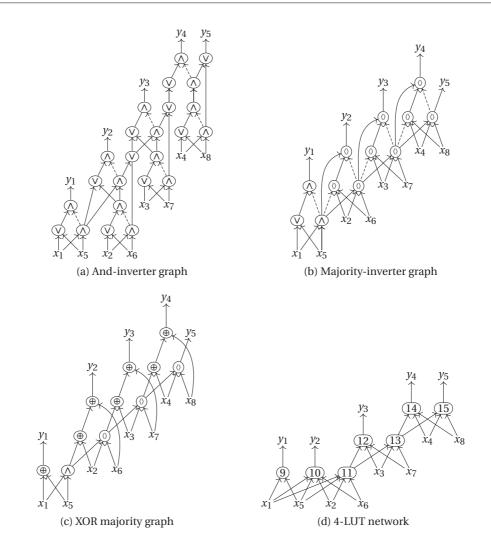

Logic networks can be specialized by placing restrictions on the internal nodes. A *homogeneous* logic network is one where the fan-in of each internal node is fixed. Restrictions can be applied to local functions as well (e.g., networks consisting of NANDs and/or NORs). For example, *and-inverter graphs* (AIGs), [87, 102] employ AND and Inverters (or equivalently apply AND functions to positive/negative literals). The *majority-inverter graphs* (MIGs), [14] use majority and inverter gates and *xor-majority graphs* (XMGs) [81] use majority and XOR gates. For FPGA design, bounded input look-up tables *k*-LUT networks are used, where  $ar(f) \le k$ .

**Example 2.5** Figure 2.2 shows logic networks for a 4-bit full adder, which computes  $(x_4x_3x_2x_1)_2 + (x_8x_7x_6x_5)_2 = (y_5y_4y_3y_2y_1)_2$ . Figures 2.2(a), (b), and (c) show an AIG, and MIG, and an XMG, respectively. Inverted inputs are drawn using dashed edges. Figure 2.2(d) shows a 4-LUT network. The gate functions are  $f_9 = 6$ ,  $f_{10} = 936c$ ,  $f_{11} = 137f$ ,  $f_{12} = 69$ ,  $f_{13} = 2b$ ,  $f_{14} = 69$ , and  $f_{15} = a4$ .

Combinational logic functions can be represented by many different logic networks. A central task in logic synthesis is to optimize some figure of merit that relates to area, performance, and/or power consumption of the final implementation. Commonly-used cost functions are the *size* r of the logic network, measured in the number of nodes, the *depth d* of the logic

Figure 2.2 - Different logic networks for a 4-bit adder: (a) AIG, (b) MIG, (c) XMG, (d) LUT

network, which is the longest path from any primary input to any primary output, and the *switching activity*.

In the thesis, we make use of MIGs as main data structure for Chapters 3 and 4. The central function in MIGs is the *majority-of-three* function. The majority function of three Boolean variables *x*, *y*, and *z*, denoted  $\langle xyz \rangle$ , evaluates to true if and only if at least two of the three inputs are true. The majority function is monotone and self-dual [97] and can be expressed in disjunctive and conjunctive normal form as

$$\langle xyz \rangle = xy \lor xz \lor yz = (x \lor y)(x \lor z)(y \lor z).$$

(2.4)

Setting any variable to 0 gives the conjunction of the other two variables, and analogously one obtains the disjunction by setting any variable to 1, i.e.,

$$\langle x0y \rangle = x \land y \text{ and } \langle x1y \rangle = x \lor y.$$

(2.5)

17

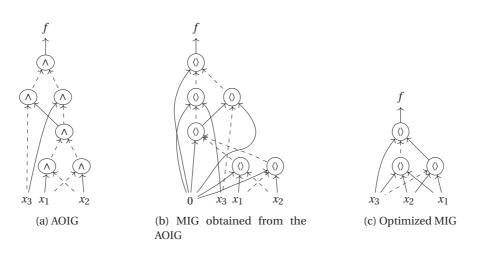

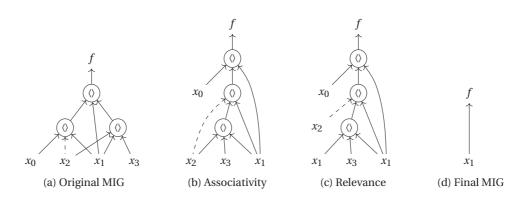

Figure 2.3 – Example (a) of *and-or-inverter graph* (AOIG) representation for  $f = x \oplus y \oplus z$ , and the MIG derived from its AOIG (b), complement attributes are represented by dashed lines. 3-input nodes are majority operators. Example (c) of optimized (more compact) MIG for f

MIGs are thus universal representation forms and can efficiently represent any Boolean function thanks to the expressiveness of the majority operator. As a consequence of the AND/OR inclusion by MAJ, traditional AOIGs are a special case of MIGs, and MIGs  $\supset$  AOIGs. It follows that MIGs can be easily derived from AOIGs. In the worst case, AND/OR operators can be replaced node-wise by majority-3 (MAJ-3) operators with a constant input, however, even smaller MIG representations arise when fully exploiting the majority functionality, i.e., with non-constant inputs. An example of MIG representation derived from its optimal AOIG is shown in Figure 2.3(b), while the optimized MIG is depicted in Figure 2.3(c). Since MIGs  $\supset$  AOIGs, and AOIGs  $\supset$  AIGs, by transitivity MIGs  $\supset$  AIGs.

Note that the majority function can be generalized for an odd number of *n* variables to  $\langle x_1 \dots x_n \rangle = [x_1 + \dots + x_n > \frac{n}{2}].$

# 2.2 Algorithms

We present here the underlying techniques for logic optimization algorithms. In particular, we concentrate on multi-level networks as they will be used in the rest of the thesis, and we present both algebraic and Boolean methods. We conclude with an overview on exact synthesis. We preserve here the historical names of approaches for logic network optimization, namely (i) *algebraic methods* (based on polynomial algebra) and *algebraic rewriting* (based on algebraic axioms, possibly of Boolean algebra) and (ii) *Boolean methods* (based on Boolean algebra). Heuristics are employed in these approaches to select the type and sequence of transformations.

Figure 2.4 – Example of AIG rewriting from [121]

## 2.2.1 Algebraic Methods

Traditional algebraic methods represent each logic network node in SOP form and treat them as polynomials [39, 41]. This simplifying abstraction enables fast manipulation of very large logic networks. Algorithms are designed as operators that iterate one type of transformation until the logic network reaches a local minimum (w.r.t. the transformation itself). Examples of transformations are *extraction, substitution, decomposition,* and *algebraic rewriting* [39, 69]. We refer the reader to [39, 41, 69] for the details of the first three methods, that will not be discussed here; while we focus instead on algebraic rewriting as it will be important for future chapters of the thesis.

# **Algebraic Rewriting**

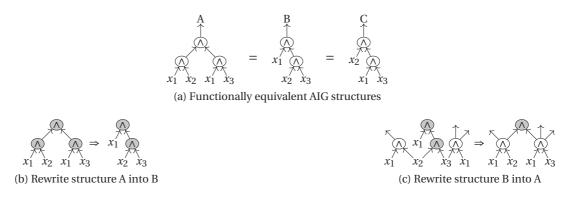

The purpose of algebraic rewriting is to change and rewrite portions of a logic network in order to improve, for instance, the number of nodes and/or levels [121]. The general idea consists of applying transformation rules (based on algebraic axioms) with the objectives of improving some figure of merit. Rewriting is more effective when logic networks are homogeneous (e.g., AIGs, MIGs, and XMGs), because logic transformations can be made specific.

Algebraic rewriting has been used extensively in ABC [121]. For example, a database of pre-computed circuit structures for a function can be included, and for any subcircuit one can compute its function and check whether replacing the subcircuit by a pre-computed structure leads to an improvement. If other nodes in the circuit are reused in the rewriting, it may be beneficial to replace a smaller structure by a larger one.

**Example 2.6** An example for AIG rewriting as implemented in ABC is shown in Figure 2.4. Figure 2.4(a) shows three functionally equivalent AIGs structures. These equivalences are employed in Figure 2.4(b) and (c) to reshape the structure of AIGs into functionally equivalent ones.

Refactoring is a variant of rewriting, in which large cones of logic feeding a node are iteratively selected with the aim to replace them by a factored form of the function. It resynthesizes

large subnetworks in a logic network from scratch and without using existing nodes in the logic network. The change is accepted if there is an improvement in the selected cost metric (usually number of nodes) [119, 121].

Algebraic rewriting is very effective for MIGs. The related majority algebra and axiomatic system  $\Omega$  have been described in [14], where it is shown that  $\Omega$  is sound and complete, providing reachability in the solution space. This means that for MIGs there exists a sequence of steps – possibly with polynomial bound – leading to the optimum solution. Such a path may not exist in other representation frameworks. Indeed, experimental evidence has shown that the MIGhty program [14] implementing algebraic rewriting has outperformed other tools on several benchmarks [14].

Regarding algebraic optimization for MIGs, a dedicated Boolean algebra has been introduced in [14, 16]. The MIG Boolean algebra is defined as the axiomatic system ( $\mathbb{B}$ ,  $\langle \rangle$ ,  $^{-}$ , 0, 1), where  $\langle \rangle$  is the majority operator and  $^{-}$  is the complementation. An axiomatic system for the MIG Boolean algebra, referred to as  $\Omega$ , is introduced and defined over five primitive transformation rules. Some other additional rules can be derived from  $\Omega$ ; three of them, referred to as  $\Psi$ , are presented in [16]:

$$\Omega \begin{cases}

Commutativity - \Omega.C \\

\langle xyz \rangle = \langle yxz \rangle = \langle zyx \rangle \\

Majority - \Omega.M \\

\langle xxy \rangle = x \quad \langle x\bar{x}y \rangle = y \\

Associativity - \Omega.A \\

\langle xu \langle yuz \rangle \rangle = \langle zu \langle yux \rangle \rangle \\

Distributivity - \Omega.D \\

\langle xy \langle uvz \rangle \rangle = \langle xyu \rangle \langle xyv \rangle z \rangle \\

Inverter Propagation - \Omega.I \\

\overline{\langle xyz \rangle} = \langle \bar{x}\bar{y}\bar{z} \rangle

\end{cases}$$

Relevance - Ψ.R

\langle xyz \rangle = \langle xyz\_{x/\bar{y}} \rangle

Complementary Associativity - Ψ.C

\langle xu \langle y\bar{u}z \rangle \rangle = \langle xu \langle yxz \rangle \rangle \\

Substitution - Ψ.S

\langle xyz \rangle = \langle v \langle \bar{v} \langle v\_{U}uxyz \rangle u \rangle \langle \bar{v} \langle v\_{U}\bar{u}xyz \rangle \bar{u} \rangle \rangle

(2.7)

where the symbol  $z_{x/y}$  is a replacement operation; that means, it replaces x with y in all its appearances in z. Some of these axioms are inspired by median algebra and others from the properties of the median operator in a distributive lattice. We like to emphasize these identities of the majority function, as they are essential for the forthcoming chapters. First, all three arguments to the majority function are *commutative*, i.e.,

$$\langle xyz \rangle = \langle yxz \rangle = \langle zxy \rangle. \tag{2.8}$$

Also, the majority function evaluates to a single argument if two arguments are equal or complement to each other, i.e.,

$$\langle xxy \rangle = x \qquad \langle x\bar{x}y \rangle = y.$$

(2.9)

The associativity rule on the majority function allows us to exchange variables if two operations

Figure 2.5 – Example of MIG optimization using the algebraic rewriting. (a) is the initial MIG; (b) MIG after associativity rule; (c) relevance transformation; (d) final result after rule  $\Omega$ .*M*

are nested and share a common variable, i.e.,

$$\langle xu\langle yuz\rangle\rangle = \langle\langle xuy\rangle uz\rangle. \tag{2.10}$$

The associativity rule becomes obvious, when replacing *u* by some operator symbol 'o' and the angular brackets by parentheses:  $(x \circ (y \circ z)) = ((x \circ y) \circ z)$ ; as pointed out by Schensted [158]. An alternative way to think about its validity, is by setting *u* to 0 and 1, and noting that  $\land$  and  $\lor$  are associative [97]. Due to these properties, the set  $M = \mathbb{B} = \{0, 1\}$  and the ternary operation  $\langle xyz \rangle$  defined according to (2.4) are a *median algebra* [30]. A median algebra is defined as a set and a majority operator satisfying commutativity, associativity, and the first identity in (2.9).

Also a *distributivity rule* can be derived from these three rules [160]:

$$\langle xu\langle yvz\rangle\rangle = \langle\langle xuy\rangle v\langle xuz\rangle\rangle \tag{2.11}$$

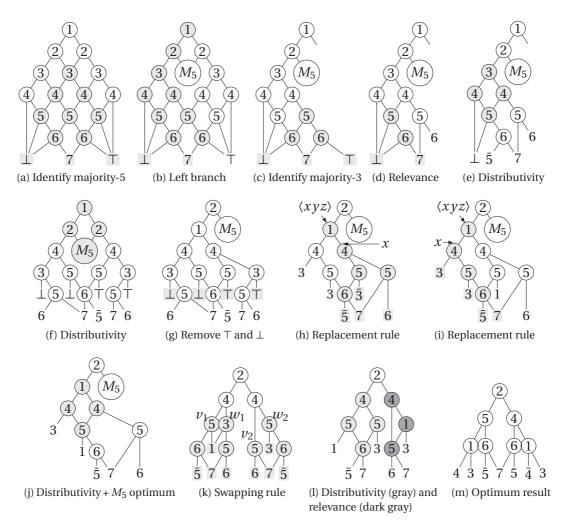

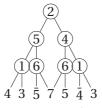

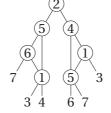

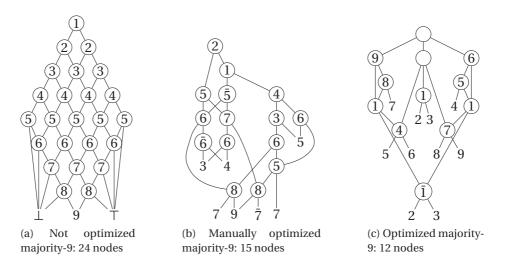

To easily memorize this rule, it's handy to replace u by a symbol ' $\circ$ ' and v by a symbol ' $\times$ '.