# InAs-on-Insulator Fin Nanostructures for Integrated Computation and Sensing Functions

Présentée le 21 juillet 2020

à la Faculté des sciences et techniques de l'ingénieur Laboratoire des dispositifs nanoélectroniques Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

#### Maneesha RUPAKULA

Acceptée sur proposition du jury

Dr J.-M. Sallese, président du jury Prof. M. A. Ionescu, directeur de thèse

Prof. J. Schmitz, rapporteur

Prof. F. Udrea, rapporteur

Dr R. Butté, rapporteur

### Acknowledgements

First, set of my gratitude goes to the wonderful jury who agreed to be on my thesis defence committee. They read, corrected and gave me feedback for my thesis and for my career journey as well. Next, my utmost thank you goes to my supervisor, Prof. Adrian lonescu. He gave me a wonderful chance to work in his laboratory, to fail time and again but get up only stronger and do only better. He supported my journey with him for 6 years not only as a supervisor but as a wonderuful human being, standing up for me wherever it was necessary. Thank you dear Lucie, Isabelle, Karin, Raymond for being the background magic wizards that you are. You solve issues I bring to you like I never had them in the first place. Then, my next thanks goes to my collaborators at IBM Zurich- Kirsten, Heinz and Clarissa. Kirsten has been a great scientific critic of my work and always only improving the quality of work. Heinz has helped me not only for sample growth but imporants ideas and discussions. Clarissa, you defined a new standard of friendship. You cared for me as a collaborator and as a friend too. I am grateful to this trio for the exchanges we have had. Further, I must thank Veeresh and Eamon at IBM Zurich for the insights they gave me at the beginning of my project work.

Special thanks to Dr.Jean-Michel Sallese for being so welcoming to students, always. I could just walk into your office anytime I wanted to discuss and walk out feeling full of ideas and motivated to work. Farzan, you have also welcomed me the same way, thank you.

Next, I need to acknowledge the staff and co-workers of CMi at EPFL. Over the years we shared fun moments, current affairs, controversial affairs, anything under the sun in corridors, near machines and while dressing in and out of the cleanroom. The interactions with you all energized me positively always. Specially mentioning Rémy, Zdenek, Joffrey, Cyrille, Giovanni, Patrick, Kaspar, Giancarlo, Ryan, Micheal, Stefano, Daniel, Minghua, Riyaz, Mohammed and many, many others.

ELB seniors- Arnab, Sara, Cem, Wolfgang and Antonios. You guys have been great mentors and a rock solid support system when I first came to the lab. Thank you for not only teaching me what you know in experiments but our countless interactions that infused in me happiness and aspiration to do better. Your friendship means the most to me. Also, thinking of all the fun times, meals and coffees I shared with Pankaj, Elizabeth, Höel, Livio, Emanuele and Mariazel.

Xsensio big brothers have always watched over me (in all the right sense) - Fabien and Johan. You were always around and available to support me whenever you could. I could as easily walk into your office as I did into your whatsapp chats. Thank you for being a glue for fun. Ali, if there is even one thing in your life I can help with please ask me. Then, I would

be atleast 'n-1' favours away from the ones I should return to you.

Now my ELB 321 family. I mean we are family and what a modern, diverse family at that, incredible. In the last 5 years of my everyday life, I interacted the most with you guys and I am not ready to believe there has been an officemate luckier than me in ELB 321. Among many, many things, I will treasure these qualities from you guys. Erick, forever the cool dude/bro for me, thank you for teaching me the delicate balance of attachment and abandon one should have towards one's vocation to remain sane. Francesco (my gentleman friend), I admire your LASER sharp focus at work, you may have had multiple tabs running in your smart 'little grey cells' but whenever I stop by your desk, I could not help but notice that you are perfecting one task a time. Also, you have given me pep talks, shared philosophies, narrated stories that I really needed to cheer me up. Thank you Brutus for helping this Pixie out always. Junrui, my first chinese friend. What can I say man, but just have to ask, how do you manage to make all the hardwork look so easy and doable? Also, not sure I will find another Zhang friendship more wonderful than ours. Sadegh, the late entrant but the one destined to be in our office, thank you for being there every single day of 2019 so I never felt alone when I came to our office.

'Nanolunch'ers - a lot can happen over food and coffee they say. Thank you for all the cheerful camaraderie we shared over the years Nicolo, Matteo, Teo, Chiara (extra special hugs to this cuddle bear for everything she does), Carlotta, Fatameh (How much do I owe you for all your food I have eaten?), Andrei, Bakul, Maria and Amin. People told me that the best lunches with co-workers will be during the PhD phase and I am sure to miss it a lot.

Who runs the world? Girls. These EPFL warrior girls who I so, so adore - Banafseh, Zahra, Mahsa, Soumya, Kaitlin, Elmira, Dory, Yasaman, Bernarda and many others. You girls rock.

My special thanks goes to all in my Suisse family. How lucky am I that our paths crossed and grateful that the bonds we formed are multiplying with the new additions in your families - The Blanc famille (Seb + Aurélie+ Justine et Violaine), FraS + Enrico, Monique + Ivan, the darling Buttets (JJ- my fav gal, Estella, Val), the ever supportive Hacks (Simon, Gab, Kath, Isabelle, Michel), Alessandra + Francesco, Negar + Alessandro, Mish + Gio, Annalisa + Alessandro, Namrata + Chetan, Martand + Cécile and Sam (Lochmater et al.). I love you guys so very much.

My EPFL desi family with whom we made a home away from home. Rishabh (my bestie), Ashish, Bob (first Indian friend in Europe), Uzair (druzzi), Sanket, Sai, Tintin, Chethana, Sangram (grammy), Mohito (most eligible bachelor), Pranito, Shravan (desiboy), Harshit, Harshal, Preethi and so many more of whose names I cannot take here for obvious reasons of taking too much space.

My in laws, especially my second supervisor Prof. Rajneesh Kumar (papa), my most loyal supporter mummyjee and the awesome cheerleader, saurav- your support at every step meant the world to me. Nanna, thank you for kindling the scientific curiousity in both me and akka from a young age and also for letting us explore the world as free birds. Amma, you built the most comfortable nest that these free birds always wish to come back to. And my love to all the Rupakula family members.

Akka, bava and vedulu (my liliputian)- I dedicated my thesis to your little boy, Vedulu. I think that should sum up what you three mean to me, the universe. Akka, the first Dr.Rupakula in the house and my pillar of strength and favourite punch bag. Thinking of it, we did not turn out so bad after all, hope you are proud of your little doctors, Nanna and Amma.

Finally, my jaan, there are only a handful of your kind left in this world, you know. Together, we are yin and yang. Everyday, you make me a better version of myself. You inspire and motivate me not only as my life partner but also as a fellow scientist. You are my biggest inspiration and favourite critique. Thank you for coming into my life and building with me a life better than the one I built in my dreams.

Lausanne, 16 March 2020

${\sf Manee}$

### Abstract

Field-effect transistors (FETs) have established themselves as a leading platform for electrical detection of chemical and biological species. Their advantages over other optical, mechanical sensing platforms are attributed to being miniaturizable, mechanically durable, label-free, responsive in real-time, compatible with scalable CMOS technology and their cheap manufacturing cost. 3D nanostructures such as nanowires (NWs) show great promise for improving sensitivity and limit of detection due to their high surface-to-volume ratio and non-planar geometry. However, when seen in literature the material of choice has predominantly been silicon because of its mastery over economies of scale in the electronic industry. Few and far in between, alternative materials are being explored and quite noticeable among them is indium arsenide (InAs). InAs is interesting not only for its superior electronic properties but also its integration capabilities. Firstly, with its higher electron mobility, the supply voltage can be scaled down in line with transistor miniaturization trends. Secondly, its small, direct bandgap enables novel heterojunction devices such as tunnel FETs. Finally, InAs integration on silicon has seen major advances over other materials giving it an edge for highly scalable platforms. Indeed, the properties mentioned are interesting from a computation point of view but are also highly favourable for sensing functions.

Rather than the typical InAs NW geometry for sensing explored in literature, in this thesis we focus on 3D fin geometry. From a computation standpoint, a tall fin geometry is interesting for better electrostatic gate control to have a high signal-to-noise ratio as well as enabling higher ON currents in future implementations of tunneling FETs. From a sensing standpoint, the 3D dimensionality favours detection at ultra-low concentrations. We demonstrate n-type, InAs-on-insulator fin nanostructures with a unique vertical aspect ratio as single and multiple-fin arrays. Using nanofabrication and characterization tools, highly crystalline InAs fins of 130 nm fin height and fin width down to 30 nm are built (i.e. an aspect ratio of nearly 4:1). For a tight pitch layout of multiple fin array, where the effective device width exceeds the actual device width and for even tens of millivolts applied voltage, high current levels in microamperes range are read-out. The ion sensitive functioning is validated for hydrogen ions. A sensivity of 41.2 mV/pH is extracted at 6 microampere drain current. What differentiates this work from other InAs sensor devices in literature is not only the unique 3D fin geometry but also integration method of InAs module on silicon that is catalyst-free, monolithically integrated on silicon, highly scalable and CMOS compatible.

Finally, further study of the devices built for sensing is carried out using metal gating

from focussed ion beam (FIB) deposition and ionic liquid (IL) gating. To benchmark the performance of Ionic liquid gating technique, it has been applied to another set of devices SOI Ribbon FETs and compared with its pH response.

**Keywords:** InAsOI, InAs, Field-Effect Transistor (FET) sensors, FinFET sensor, aspect ratio, Ion-Sensitive FET, nanostructure, pH sensor, ion sensing, SOI, high-k dielectric, III-V integration

### Résumé

Les transistors à effet de champ (field-effect transistors, FET) se sont imposés comme une plate-forme de pointe pour la détection électrique d'espèces chimiques et biologiques. Leurs avantages par rapport aux autres plateformes de détection optique et mécanique sont attribués à leur propension à la miniaturisation, leur durabilité mécanique, leur réponse sans marquage (label-free) et en temps réel, leur compatibilité avec la technologie extensible CMOS ainsi que leur coût de fabrication peu élevé. Les nanostructures 3D telles que les nano-fils (Nanowires, NW) sont très prometteuses pour améliorer la sensibilité et la limite de détection en raison de leur facteur d'aspect élevé et de leur géométrie non plane. Cependant, le silicium reste le matériau décrit de manière prépondérante dans la littérature en raison de l'économie d'échelle qu'il permet dans l'industrie électronique, éclipsant de fait l'étude de matériaux alternatifs, tel que notablement l'arséniure d'indium (InAs). L'InAs possède un haut potentiel d'utilisation non seulement grâce à ses propriétés électroniques supérieures, mais aussi pour ses capacités d'intégration. En effet, sa grande mobilité électronique permet une réduction de la tension d'alimentation en parfait accord avec la tendance actuelle de miniaturisation des transistors. De plus, son intervalle de bande interdite faible et direct permet le développement de nouveaux dispositifs à hétérojonction tels que les FETs à effet tunnel. Enfin, l'intégration de l'InAs sur le silicium a connu des avancées majeures par rapport à d'autres matériaux, ce qui lui confère un avantage important pour les plates-formes hautement industrialisables. En effet, les propriétés mentionnées sont intéressantes d'un point de vue performance de calcul mais sont également très favorables pour les fonctions de détection.

Plutôt que de se fonder sur la géométrie de NW d'InAs typique pour la détection qui a été extensivement décrite dans la littérature, nous nous concentrons dans cette thèse sur une géométrie 3D en aileron. D'une part, du point de vue des performances de calcul, une géométrie à aileron haut est intéressante pour un meilleur contrôle de la grille électrostatique afin d'obtenir un rapport signal/bruit élevé, ainsi que pour permettre des courants ON plus élevés dans les futures implémentations de FETs à effet tunnel. D'autre part, du point de vue des performances de détection, la dimensionnalité 3D favorise la détection de molécules d'intérêt à des concentrations ultra-basses. Nous démontrons des nanostructures à aileron de type n, InAs-sur-isolant, avec un rapport d'aspect vertical unique, sous forme de réseaux d'ailerons simples et multiples. En utilisant des outils de nanofabrication et de caractérisation, des ailerons de InAs hautement cristallin de 130 nm de hauteur et de 30 nm de largeur sont produits (i.e. avec un rapport d'aspect proche de 4 :1). Pour une disposition dense de réseaux à ailerons multiples, où la largeur effective du dispositif dépasse la largeur réelle du

dispositif, et pour une tension appliquée de seulement quelques dizaines de millivolts, des niveaux de courant élevés dans la gamme des microampères sont lus. La sensibilité ionique des dispositifs a été validée pour les ions hydrogène. Une sensibilité de 41,2 mV/pH est extraite à un courant de drain de 6 microampères. L'innovation de ce projet réside non seulement dans le développement d'une géométrie 3D en aileron unique, mais aussi dans l'utilisation d'une méthode d'intégration du module InAs sur silicium sans catalyseur, d'une façon monolithique, hautement industrialisable, et compatible CMOS.

Enfin, une étude plus approfondie des dispositifs élaborés pour la détection est réalisée avec une grille métallique déposée par faisceau d'ions focalisés (FIB) ainsi que par une grille consistant d'un liquide ionique (IL). Afin d'évaluer les performances du contrôle de la grille par liquide ionique, celle technique a été appliquée à un autre type de dispositifs FET à ruban de Silicium-Sur-Isolant (Silicon-On-Insulator, SOI), et leurs réponses respectives au pH comparées.

## Acronyms

ALD Atomic Layer Deposition

BHF Buffered Hydrofluoric acid

CMOS Complementary Metal-Oxide Semiconductor

DC Direct Current

DHF Dilute Hydrofluoric acid

EBL Electron Beam Lithography

FET Field-Effect Transistor

FIB Focussed Ion Beam

MOSFET Metal Oxide Semiconductor Field-Effect Transistor

GND Ground

IC Integrated Circuit

LTO Low Thermal Oxide

MBE Molecular Beam Epitaxy

MEMS Micro Electro Mechanical System

MIS Metal Insulator Semiconductor

RT Room Temperature

SEM Scanning Electron Microscopy

SOI Silicon On Insulator

TEOS Tetra Ethyl Ortho Silicate Oxide

TCAD Technology Computer-Aided Design

TFET Tunneling Field-Effect Transistor

TEM Transmission Electron Microscopy

VLSI Very Large Scale Integration

## Units of measurements

- $^{o}\mathrm{C}$  Celsius degree

- A Ampere

- C Coulomb

- eV electron Volt

- J Joule

- <sup>o</sup>K Kelvin degree

- kg Kilogram

- m Meter

- s Second

- h Hour

- V Volt

- W Watt

- $\Omega$  Ohm

# SI decimal prefixes

```

\mathbf{10}^{12}

Tera

{f T}

\mathbf{G}

\mathbf{10}^{9}

Giga

10^6

Mega

\mathbf{M}

10^{3}

kilo

\mathbf{10}^2

hecto

\mathbf{h}

\mathbf{10}^{1}

Deca

da

1

10^{-1}

\mathbf{deci}

10^{-2}

centi

milli

10^{-3}

\mathbf{m}

10^{-6}

micro

10^{-9}

nano

10^{-12}

pico

10^{-15}

\mathbf{f}

femto

```

## Physical constants

```

e \text{ (or } q) = 1.60206 \times 10^{-19} \text{ C}

Elementary Charge

= 6.62606896 \times 10^{-34} \text{ J.s}

Planck Constant

h

= 8.617343 \times 10^{-5} \text{ eV.K}^{-1}

Boltzmann Constant

k_B

= 8.85418782 \times 10^{-12} \text{ F.m}^{-1}

Free Space Permittivity

Air Relative Permittivity \epsilon_r

= 2.99792458 \times 10^{8} \text{ m.s}^{-1}

Speed of Light

c

= 8.314 \text{ J/(mol.K)}

Gas Constant

R

```

# Contents

| Αc  | cknow  | /ledgen | nents                                                | iii           |

|-----|--------|---------|------------------------------------------------------|---------------|

| Αŀ  | ostrac | t (Eng  | lish/Français)                                       | vii           |

| Αc  | crony  | ms      |                                                      | xi            |

| Uı  | nits o | f meas  | urements                                             | xiii          |

| SI  | decii  | mal pre | fixes                                                | χV            |

| Pł  | ıysica | l const | ants                                                 | xvii          |

| Lis | st of  | figures |                                                      | xxi           |

| Lis | st of  | tables  | xx                                                   | <b>xvii</b> i |

| 1   | The    | sis Ove | erview                                               | 1             |

| 2   | Intro  | oductio | on                                                   | 3             |

|     | 2.1    | Motiva  | ation                                                | 3             |

|     | 2.2    | Comp    | utation Unit: MOSFET                                 | 4             |

|     |        | 2.2.1   | Conduction Mechanisms                                | 8             |

|     |        | 2.2.2   | Multiple Gate Architecture                           | 11            |

|     |        | 2.2.3   | Novel Gating Architecture: Ionic Liquid Gating       | 12            |

|     | 2.3    | Sensin  | g Platform : Electrochemical transducer              | 15            |

|     |        | 2.3.1   | lon selective electrodes                             | 16            |

|     |        | 2.3.2   | FET based sensing                                    | 21            |

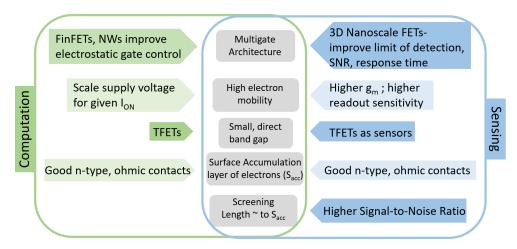

|     | 2.4    |         | ation of InAs architecture for computing and sensing | 23            |

|     | 2.5    |         | anostructures for sensing                            | 23            |

|     | 2.6    |         | es in our System                                     | 31            |

|     |        | 2.6.1   | Indium Arsenide                                      | 31            |

|     |        | 2.6.2   | Geometry: High-Aspect-Ratio (HAR) fin                | 37            |

|     |        | 2.6.3   | Sensing area                                         | 37            |

|     |        | 2.6.4   | Sensing High-k Oxide                                 | 38            |

|     |        | 2.6.5   | Junctionless Transistor                              | 38            |

|   | 2.7  | Summa    | ary                                                              | 41  |

|---|------|----------|------------------------------------------------------------------|-----|

| 3 | Tecl | nnology  | Development of InAs-On-Insulator (InAsOI) FinFET Nanostruc-      |     |

|   | ture | S        |                                                                  | 43  |

|   | 3.1  | Process  | S Overview                                                       | 43  |

|   | 3.2  | Pre-gro  | owth steps                                                       | 44  |

|   |      | 3.2.1    | Alignment Marks                                                  | 45  |

|   |      | 3.2.2    | Ebeam lithography                                                | 47  |

|   |      | 3.2.3    | Silicon reactive ion etching                                     | 48  |

|   |      | 3.2.4    | Oxide deposition                                                 | 50  |

|   |      | 3.2.5    | Template opening ebeam lithography                               | 51  |

|   |      | 3.2.6    | Wafer dicing                                                     | 52  |

|   |      | 3.2.7    | Silicon anisotropic wet etching                                  | 52  |

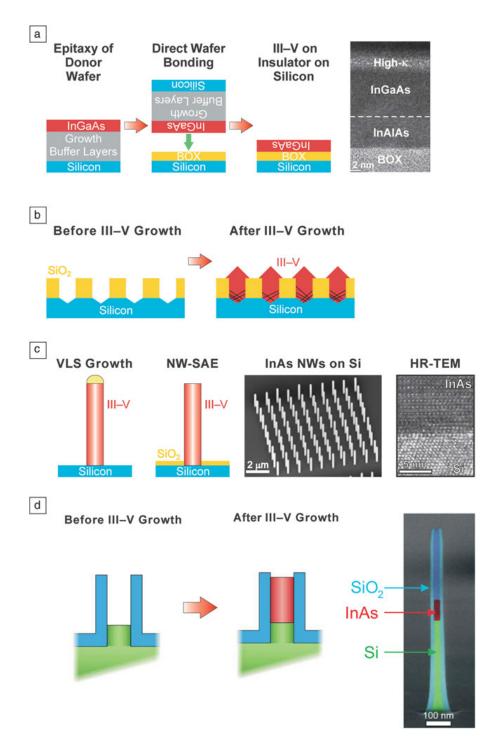

|   | 3.3  | Templa   | ate Assisted Selective Epitaxy Mechanism                         | 54  |

|   | 3.4  | MOVP     | E Growth characterization                                        | 57  |

|   |      | 3.4.1    | Non-idealities in growth                                         | 63  |

|   | 3.5  | Post gi  | rowth processing                                                 | 65  |

|   |      | 3.5.1    | Parasitic removal                                                | 65  |

|   |      | 3.5.2    | Source & drain lithography                                       | 68  |

|   |      | 3.5.3    | Source & drain metallization                                     | 69  |

|   |      | 3.5.4    | ALD isolation & pad opening                                      | 70  |

|   | 3.6  | Summa    | ary                                                              | 73  |

| 4 | Mea  | sureme   | nts & Discussion                                                 | 75  |

|   | 4.1  | InAsOI   | FinFETs as pH Sensor                                             | 76  |

|   |      | 4.1.1    | ISFET Characterization Setup                                     | 76  |

|   |      | 4.1.2    | ISFET Measurements                                               | 78  |

|   |      | 4.1.3    | Discussion                                                       | 83  |

|   | 4.2  | Ad-hoc   | Characterization                                                 | 83  |

|   | 4.3  | Ionic li | quid gating measurements                                         | 85  |

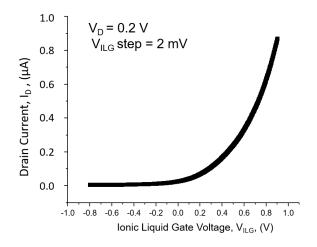

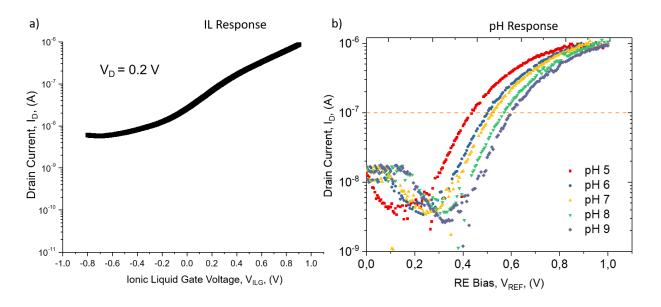

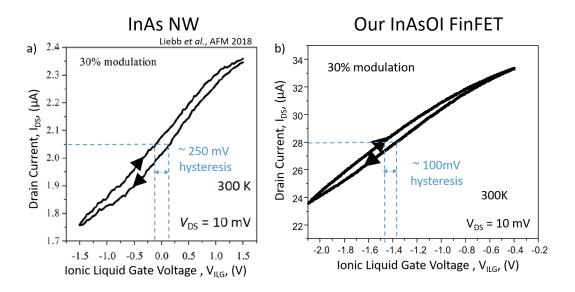

|   |      | 4.3.1    | IL Measurements on SOI Ribbon FETs                               | 85  |

|   |      | 4.3.2    | IL Measurements on InAsOI FinFETs                                | 91  |

|   | 4.4  | Metal    | Gate Patterning                                                  | 93  |

|   | 4.5  | Summa    | ary                                                              | 96  |

| 5 | Con  | clusions | and Perspectives                                                 | 97  |

|   | 5.1  | Conclu   | sions                                                            | 97  |

|   |      | 5.1.1    | Scalable III-V Integration platform for sensing: TASE            | 97  |

|   |      | 5.1.2    | High Aspect Ratio Fin fabrication                                | 98  |

|   |      | 5.1.3    | Experimental characterization - pH sensing, Metal gate and Ionic |     |

|   |      |          | Liquid gate                                                      | 98  |

|   | 5.2  | Perspe   | ctives                                                           | 99  |

|   |      | 5.2.1    | Design & Fabrication                                             | 100 |

|               |                                | ontents |

|---------------|--------------------------------|---------|

|               | Case for biosensing            |         |

| 5.2.3         | TFET as a sensitive bio-sensor | . 102   |

| Bibliography  |                                | 103     |

| Curriculum Vi | itae                           | 113     |

# List of Figures

| 2.1  | n-type MOSFET schematic with 4 terminals.                                        | Э  |

|------|----------------------------------------------------------------------------------|----|

| 2.2  | Visualization of Moore's Law                                                     | 6  |

| 2.3  | Performance of CPU with time in terms of cost, functionality and high            |    |

|      | performance                                                                      | 7  |

| 2.4  | Dennard scaling law visualized in a MOSFET structure: scaling doping con-        |    |

|      | centration (in orange), physical parameters (in blue), supply voltage (in green) | 7  |

| 2.5  | MOS capacitor behaviour                                                          | 9  |

| 2.6  | Drain current (log scale) vs gate voltage - transfer characteristics are shown   |    |

|      | for three different MOSFET modes a) Inversion b) Accumulation c) Depletion.      | 10 |

| 2.7  | Diagram summarizing ionic liquid properties and applications                     | 12 |

| 2.8  | liquid specifications                                                            | 14 |

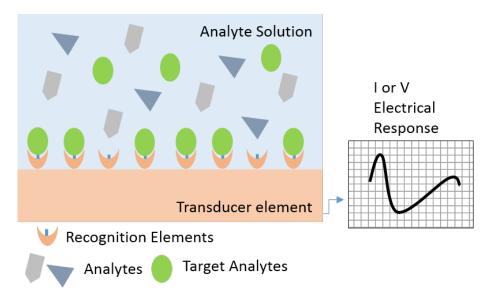

| 2.9  | Principle of electrochemical sensing                                             | 15 |

| 2.10 | Main components of a potentiometer cell measurement setup with a reference       |    |

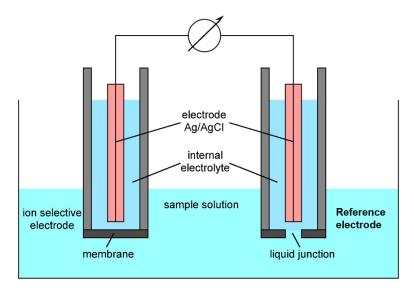

|      | electrode and ion selective electrode                                            | 16 |

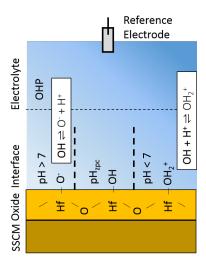

| 2.11 | Solid state ISE with a oxide layer behaving as ISM for $H^+$ ions                | 18 |

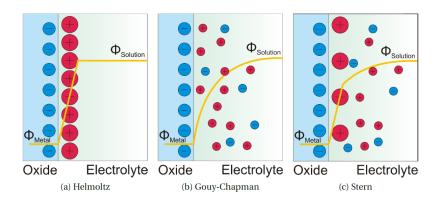

| 2.12 | EIS models a) Helmholtz, b) Gouy-Chapman, c) Stern                               | 20 |

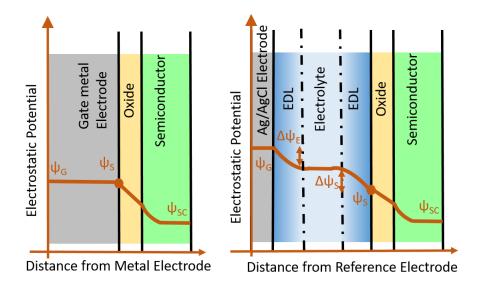

| 2.13 | Interface and potential drop with distance in (left) metal gate electrode and    |    |

|      | (right) reference electrode in liquid gating                                     | 22 |

| 2.14 | Motivation for InAs architure from a computation and sensing perspective.        | 23 |

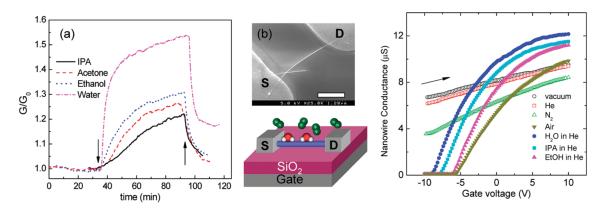

| 2.15 | Left to Right: Change in conductance with different gas molecules, SEM           |    |

|      | image of NW structure and change in NW conductance as a function of back         |    |

|      | gate voltage                                                                     | 24 |

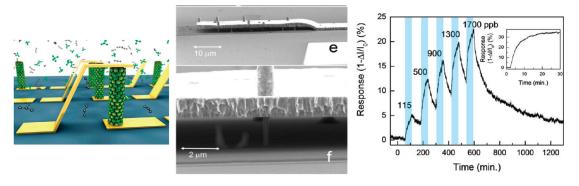

| 2.16 | Left to Right: Concept of air bridge InAs NW sensor, in e) SEM images of the     |    |

|      | contact over many vertical InAs NWs, f) a zoom of the NW, metal contact          |    |

|      | and response of NW array to different concentrations of $NO_2$ down to 9 ppb     |    |

|      | of $NO_2/N_2$ in inset                                                           | 24 |

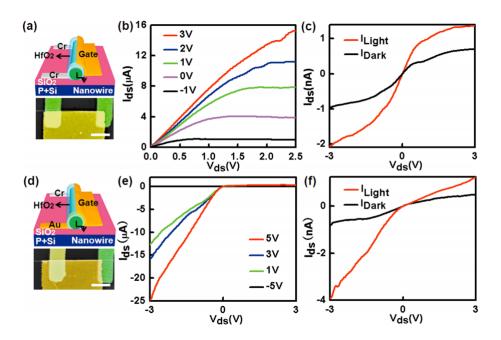

| 2.17 | (a)-(c) Show schematic, SEM image of Ohmic-Ohmic contacted devices and           |    |

|      | their photo response behaviour at different gate voltages in light and in dark   |    |

|      | conditions, (d)-(f)show schematic, SEM image of Ohmic-Schottky contacted         |    |

|      | devices and their photo response behaviour at different gate voltages in light   |    |

|      | and dark conditions                                                              | 25 |

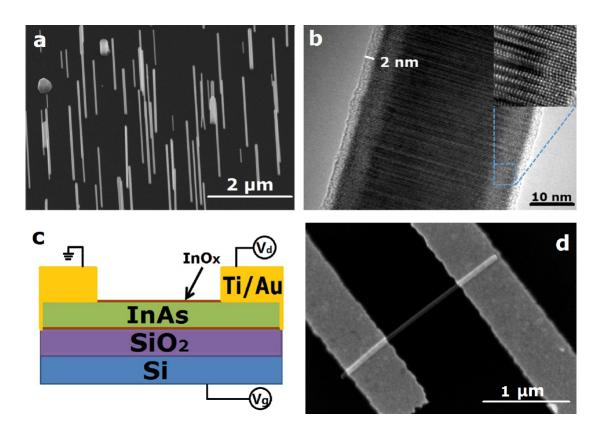

| 2.18 | , , , , , , , , , , , , , , , , , , , ,                                          |    |

|      | schematic of complete structure. d) SEM image of a typical measured device.      | 26 |

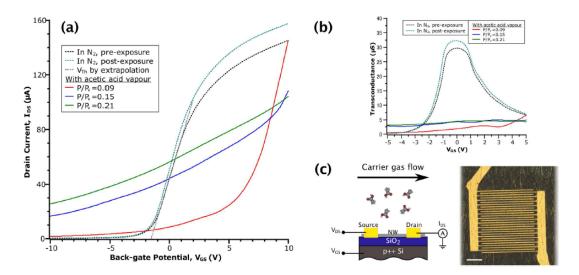

| 2.19 | (a) Transfer characteristics of InAs NW FET in different vapor environments.                                         |    |

|------|----------------------------------------------------------------------------------------------------------------------|----|

|      | b) Transconductance curve obtained from differentiation of data in (a). (c)                                          |    |

|      | Schematic of NWFET structure (left) and optical image of a complete device                                           |    |

|      | (right).Scale bar 20 $\mu$ m                                                                                         | 27 |

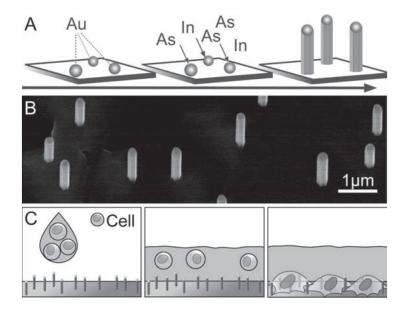

| 2.20 | Use of vertical InAs NW array to culture mammalian cells and study their cell                                        |    |

|      | function                                                                                                             | 27 |

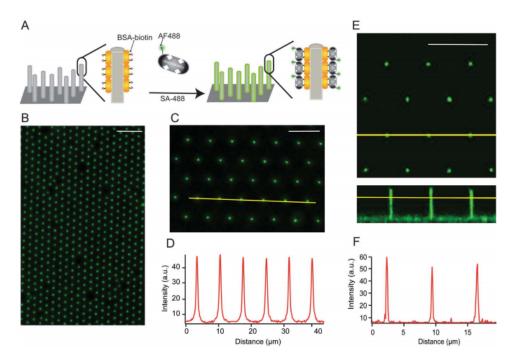

| 2.21 | Flourescence detection of protein immoblized on NW arrays. A) Scheme of                                              |    |

|      | functionalization of NW arrays with BSA-biotin and SA-488. B) wide field                                             |    |

|      | image showing the spacing of NWs is $2\mu m$ . C) wide field image showing                                           |    |

|      | spacing of NWs is $7\mu m$ . D)- F) shows intensity of corresponding yellow lines                                    |    |

|      | marked in the figure.                                                                                                | 28 |

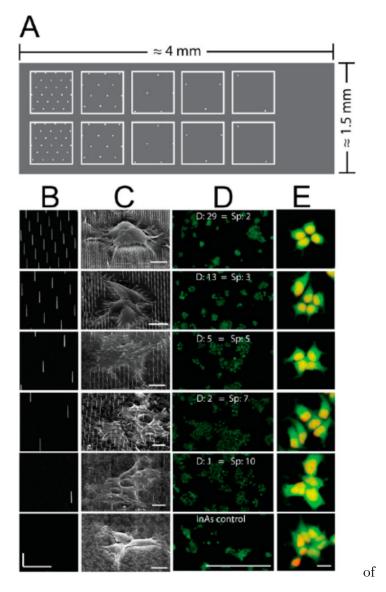

| 2.22 | A. A schematic image showing the various NW density areas of vertical InAs                                           |    |

|      | NWs. White squares are of 500×500 $\mu m^2$ with 2,3,5,7,10 $\mu$ m spacing between                                  |    |

|      | NWs. B. Tilted SEM images of the density of nanowires. C. Morphology                                                 |    |

|      | differences on the different NW densities where small, rounded forms seen                                            |    |

|      | on the high density wires and flat, spread out form on lower densities. D. &                                         |    |

|      | E. Living cells signature is seen through maintaining esterase activity (green                                       |    |

|      | = calcein-AM) and cell morphology qualitatively similar in red i.e DRAQ5 nuclear label staining                      | 29 |

| 2 22 | -                                                                                                                    | 29 |

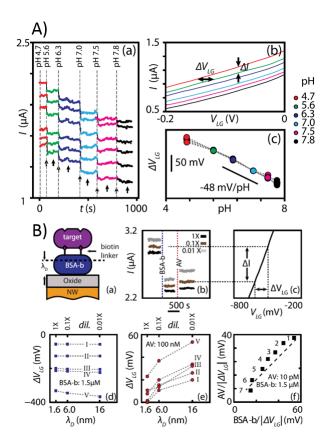

| 2.23 | A. Sensitivity of InAs sensor towards pH 4.7 to 7.8. B)Sensitivity of functionalized InAs NW towards avidin protein. | 30 |

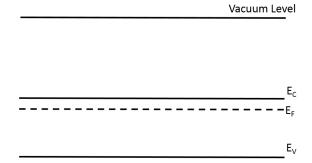

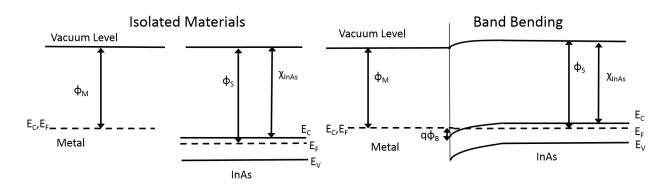

| 2.24 | Energy Band Diagram of intrinsic InAs.                                                                               | 32 |

| 2.25 | Energy Band Diagram of intrinsic InAs.                                                                               | 32 |

| 2.26 | Energy Band Diagram of intrinsic InAs                                                                                | 33 |

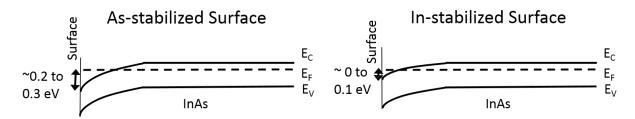

| 2.27 | Principle showing energy harvesting from fluidic flow by InAs NW wires                                               | 34 |

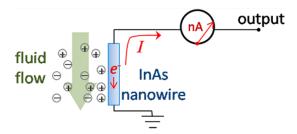

| 2.28 | Techniques for III-V Integration on silicon                                                                          | 36 |

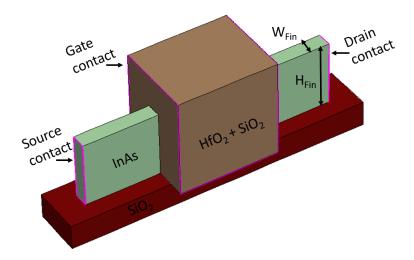

| 2.29 | Simulated InAs-on-insulator FinFET structure                                                                         | 39 |

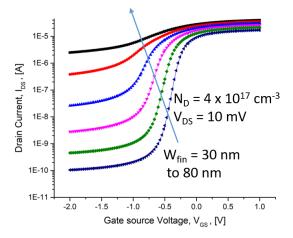

| 2.30 | Transfer characteristics I                                                                                           | 40 |

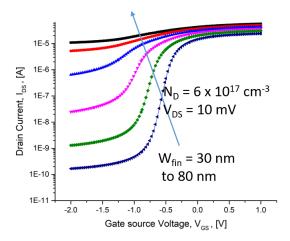

| 2.31 | Transfer characteristics II                                                                                          | 40 |

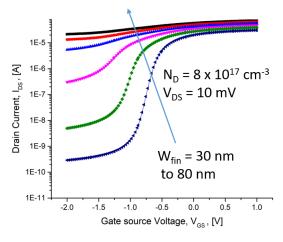

| 2.32 | Transfer characteristics III                                                                                         | 40 |

|      |                                                                                                                      |    |

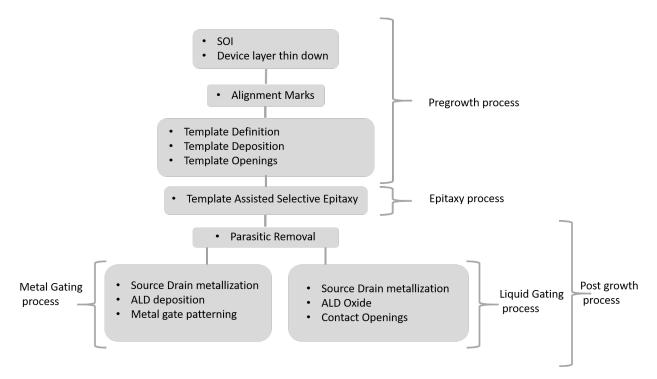

| 3.1  | Classification of process steps for clarity is shown                                                                 | 44 |

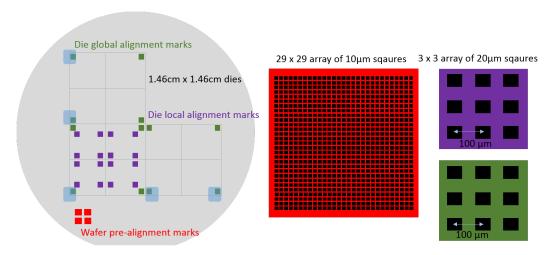

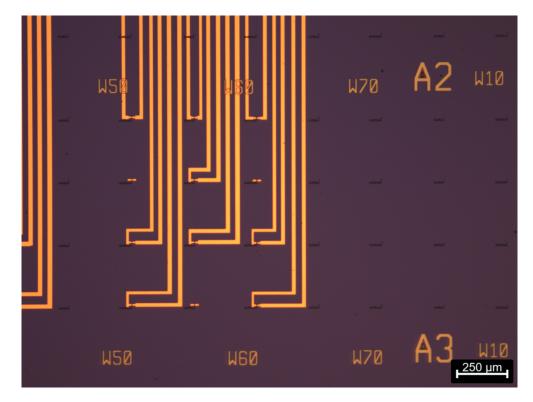

| 3.2  | Alignment marks are visualized on the wafer- prealignment marks, global wafer                                        |    |

|      | alignment procedure, die global alignment marks, die local alignment marks                                           | 45 |

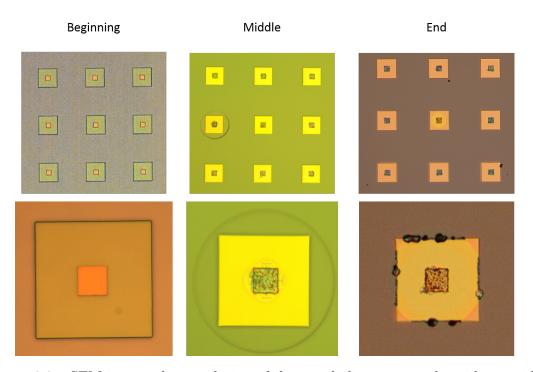

| 3.3  | SEM images show evolution of the metal alignment marks with an oxide                                                 |    |

|      | protection layer. Small square is the metal marks, larger square is the protection                                   |    |

|      |                                                                                                                      | 46 |

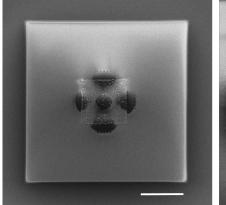

| 3.4  | High resolution SEM image of a used Pt alignment mark - seen is the edge                                             |    |

|      | , , , ,                                                                                                              | 47 |

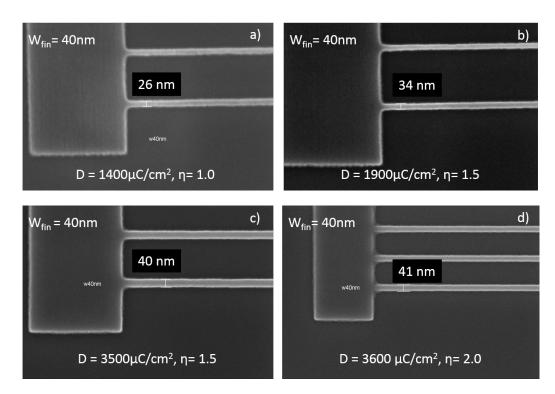

| 3.5  | From under exposed to over exposed HSQ structures for different range of                                             |    |

|      | Dose, $\eta$ values depicted in SEM images                                                                           | 49 |

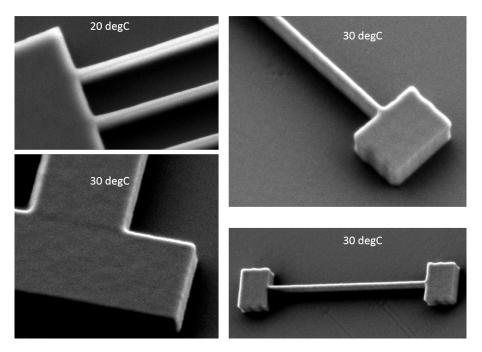

| 3.6  | Tilted SEM images of different test structures on buried oxide showing vertical sidewall etches                                                             | 50 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

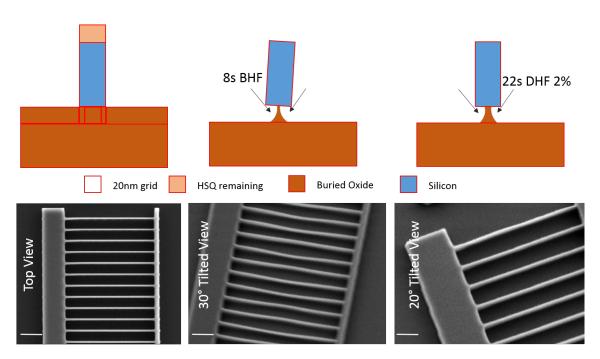

| 3.7  | The top and tilted SEM views of an array of 30 nm wide fins where BHF over etch results in a collapse and is resolved with DHF 2% etch. Scale bar left to   |    |

|      | right - 300 nm, 200 nm, 150 nm                                                                                                                              | 51 |

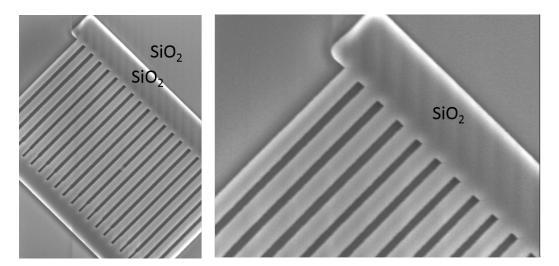

| 3.8  | Template oxide enclosing entire Si structure seen in the top view SEM images                                                                                | 52 |

| 3.9  | SEM images showing openings in PMMA resist of the template oxide in various test structures                                                                 | 53 |

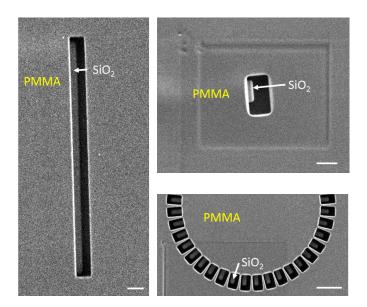

| 2 10 |                                                                                                                                                             | 99 |

| 3.10 | a) Schematic of TMAH etch setup with heating and stirring functionality. b) SEM Image of a Si partial etch inside the $SiO_2$ template is seen. Scale bar = |    |

|      | 200 nm                                                                                                                                                      | 53 |

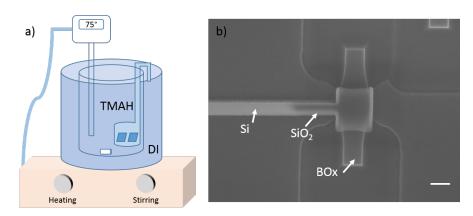

| 2 11 | (a) to (d) Topview SEM images of various structures back etched to different                                                                                | 99 |

| J.11 | legnths. The bright areas where template oxide is filled with Silicon and dark                                                                              |    |

|      | regions where template oxide is hollow are clearly distinguishable. Scale bar                                                                               |    |

|      | $= 1~\mu$ m, 1 $\mu$ m, 200 nm, 200 nm                                                                                                                      | 54 |

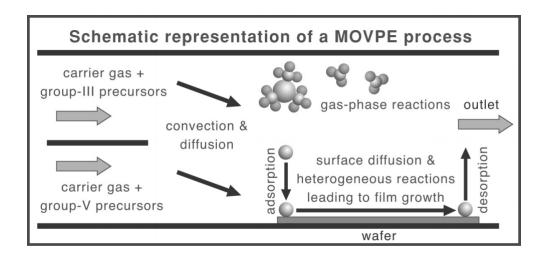

| 3.12 | MOVPE deposition mechanism                                                                                                                                  | 55 |

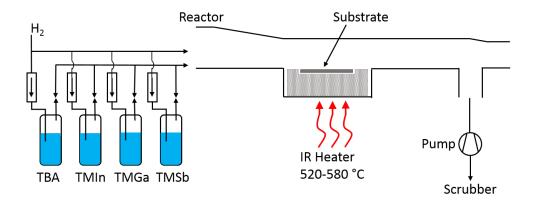

|      | MOCVD Reactor Furnace                                                                                                                                       | 55 |

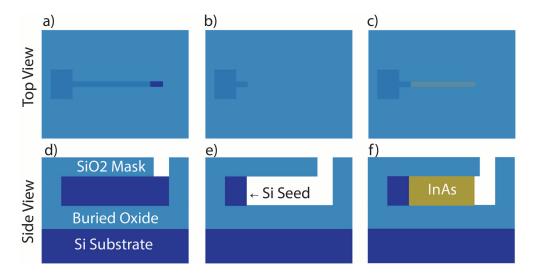

|      | a) to c) Top view and d) to f) side view schematic of steps of main steps in                                                                                |    |

|      | order to realize templates for epitaxy                                                                                                                      | 56 |

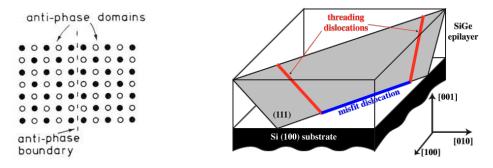

| 3.15 | Antiphase boundary                                                                                                                                          | 56 |

| 3.16 | Threading dislocations                                                                                                                                      | 56 |

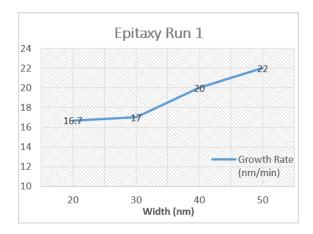

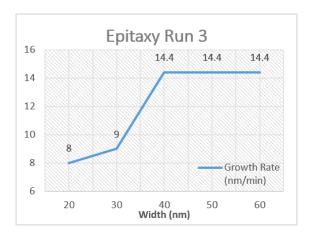

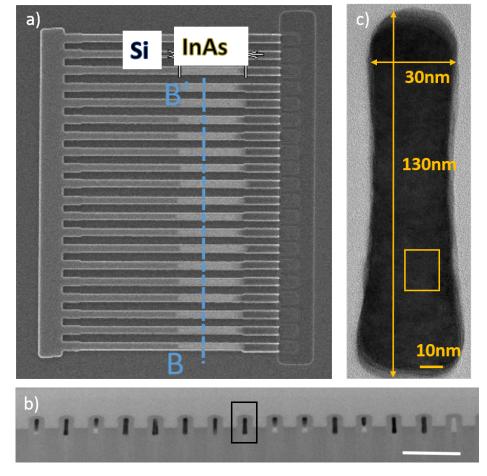

|      | Plot of growth rate versus fin width for InAs epitaxy run at 550°C for 10 mins                                                                              | 57 |

| 3.18 | Plot of growth rate versus fin width for InAs epitaxy run at 550°C for 50 mins                                                                              | 57 |

| 3.19 | Plot of growth rate versus fin width for InAs epitaxy run at 550°C for 50 mins                                                                              | 58 |

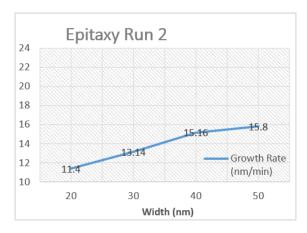

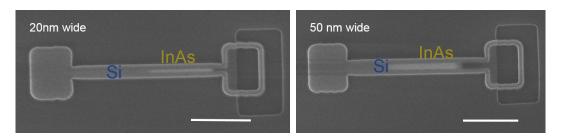

| 3.20 | Top view SEM image of fins with design width of 20 nm and 50 nm with a                                                                                      |    |

|      | difference in the back etch length and the grown InAs length for a growth                                                                                   |    |

|      | time of 50 mins. Scale bar $=$ 600 nm                                                                                                                       | 58 |

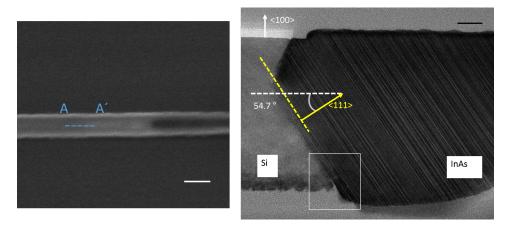

| 3.21 | The TEM image is taken across the line AA'. High resolution TEM shows a                                                                                     |    |

|      | directional etch stop in $(111)$ plane when using TMAH silicon etching. Scale                                                                               |    |

|      | $bar = 100 \; nm, \; 20 \; nm.  \dots $               | 59 |

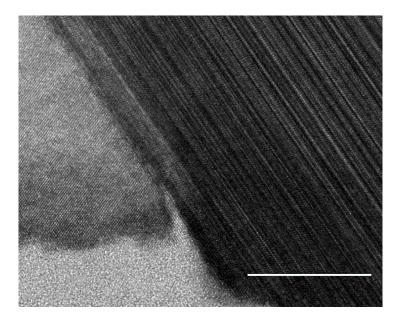

| 3.22 | A zoom of the previous HR TEM image at the hetero interface is shown here.                                                                                  |    |

|      | Scale bar $= 20 \text{ nm}.$                                                                                                                                | 59 |

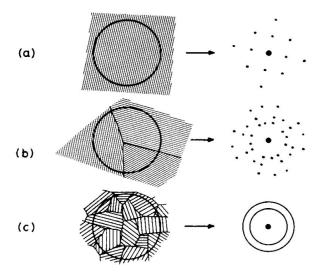

| 3.23 | Diffraction Patterns - a) Single crystalline pattern showing discrete spots. b)                                                                             |    |

|      | when few grains are present the spots begin to form circles. c) large randomly                                                                              |    |

|      | oriented grains show no spots but rings                                                                                                                     | 60 |

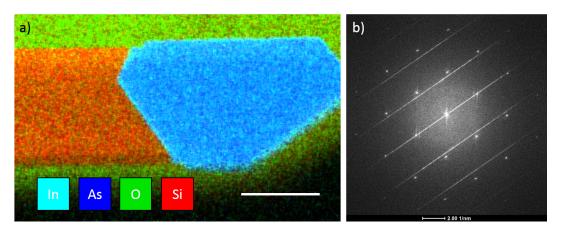

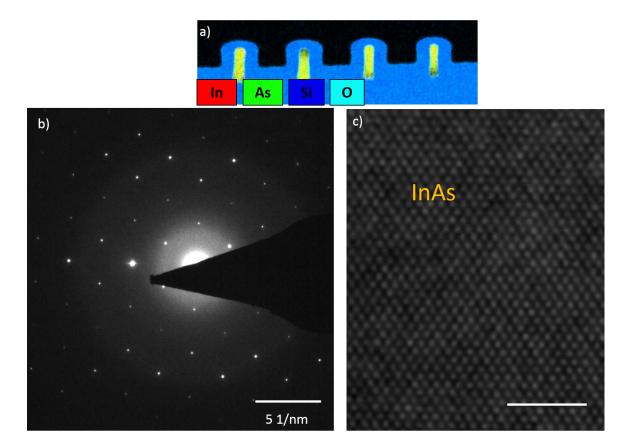

| 3.24 | a) An energy dispersive x-ray analysis (EDX) gives the elemental map indicating                                                                             |    |

|      | the material composition b) Single crystalline pattern showing discrete spots                                                                               | 00 |

| 2.05 | in the SAED image                                                                                                                                           | 60 |

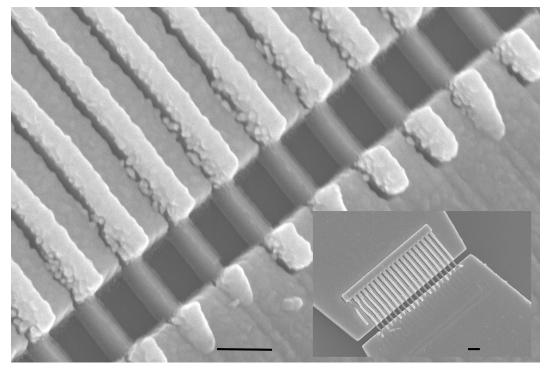

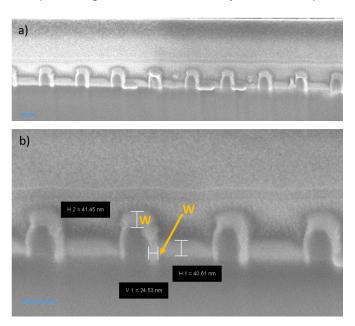

| 3.25 | The TEM image is taken across the line BB'.b) Focussed ion beam cross                                                                                       |    |

|      | section of multiple fin array is shown. c) High Resolution image depicts the                                                                                | 61 |

|      | unique tall aspect ratio. Scale bar $= 500 \text{ nm}$                                                                                                      | 61 |

| 3.26  | a) An energy dispersive x-ray analysis gives the elemental analysis map indicating the material composition b) Single crystalline pattern showing                  |    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|       | discrete spots in the SAED image                                                                                                                                   | 62 |

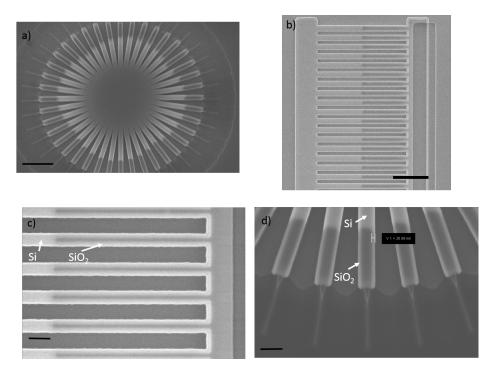

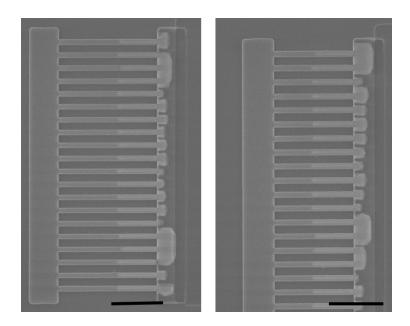

| 3.27  | SEM images show examples of good clean growths of multi-fin array with                                                                                             |    |

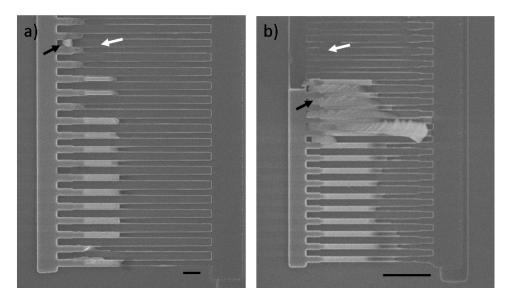

|       | growth length larger than 1 $\mu$ m. Scale bar is 1 $\mu$ m and 1 $\mu$ m                                                                                          | 63 |

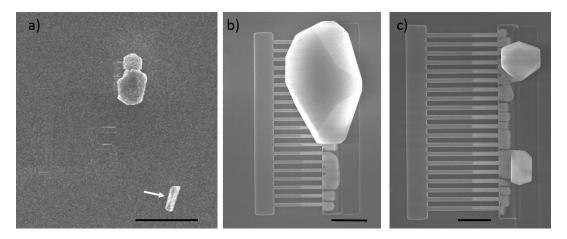

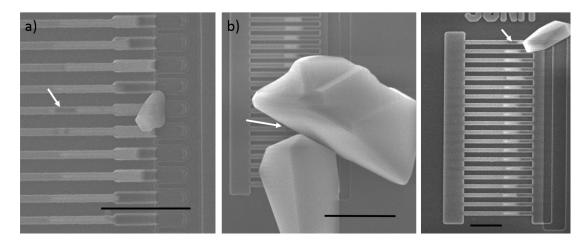

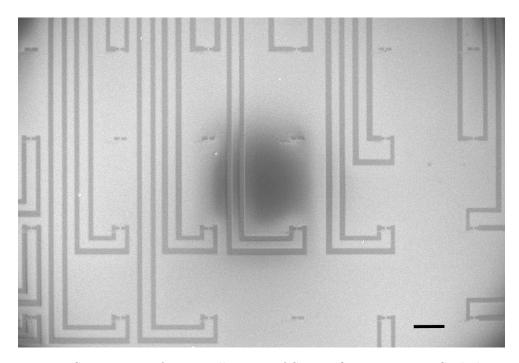

| 3.28  | SEM images showing a) overgrowth on the device and a parasitic growth on $SiO_2$ b) overgrown multiple fin structure. c) overgrowth from a clean device            |    |

| 3.29  | growth. Scale bar 10 $\mu$ m, 1 $\mu$ m and 1 $\mu$ m                                                                                                              | 64 |

|       | indicating the gap and c) another bad seeding that results in a fast over growth. Scale bar 1 $\mu$ m, 2 $\mu$ m and 1 $\mu$ m                                     | 64 |

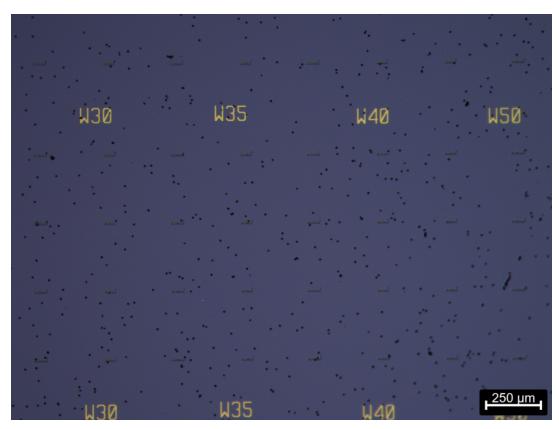

| 3.30  | Optical microscope image showing unwanted InAs growths all over the chip                                                                                           |    |

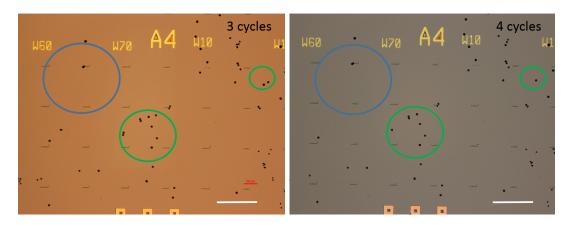

| 3.31  | Seen as the black dots                                                                                                                                             | 65 |

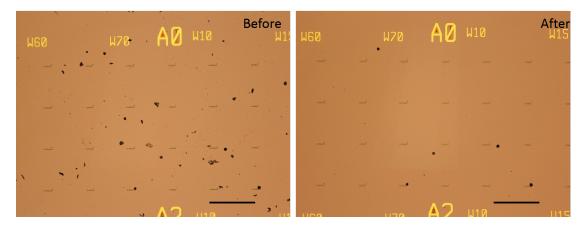

|       | and heat to clean unwanted InAs growths. Scale bar 300 $\mu$ m and 300 $\mu$ m.                                                                                    | 66 |

| 3.32  | Optical microscope image shows before and after case of using ultrasound and heat does not result to much variation except minor changes marked in                 |    |

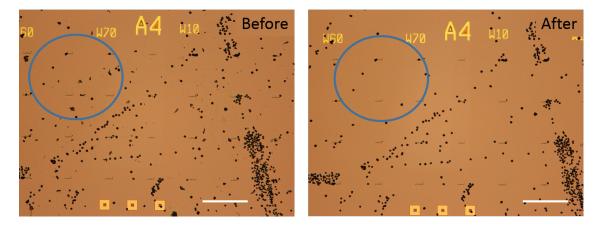

| 0.00  | blue circle areas. Scale bar 300 $\mu$ m and 300 $\mu$ m.                                                                                                          | 66 |

| 3.33  | Optical images same section as pictured in previous figure 3.32, before and                                                                                        |    |

|       | after case of applying 3 and 4 cycles of UV-sensitive stick and peel tape steps. Differences are marked in blue and green circled areas. Scale bar 300 $\mu$ m and |    |

|       | 300 $\mu$ m                                                                                                                                                        | 67 |

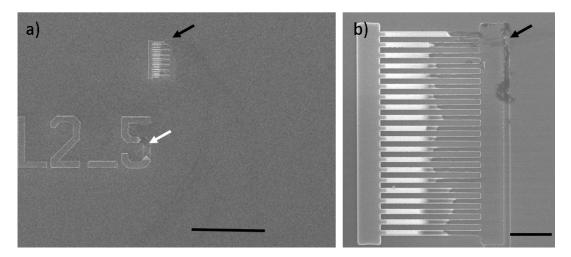

| 3 3/1 | SEM images showing damages showing same region a) zoomed out where                                                                                                 | 07 |

| 3.34  | black arrow indicate history of a removed unwawted particle, white arrow indicated unwanted damage b) zoomed in where black arrow indicates history                |    |

|       | of removed unwanted particle .Scale bar 10 $\mu$ m and 1 $\mu$ m                                                                                                   | 67 |

| 3.35  | SEM images of two different devices in a) and b) where white arrows indicate damage to grown structures whereas black arrows indicate the partially                |    |

|       | removed parasitic particles. showing Scale bar 300 nm and 1 $\mu$ m                                                                                                | 68 |

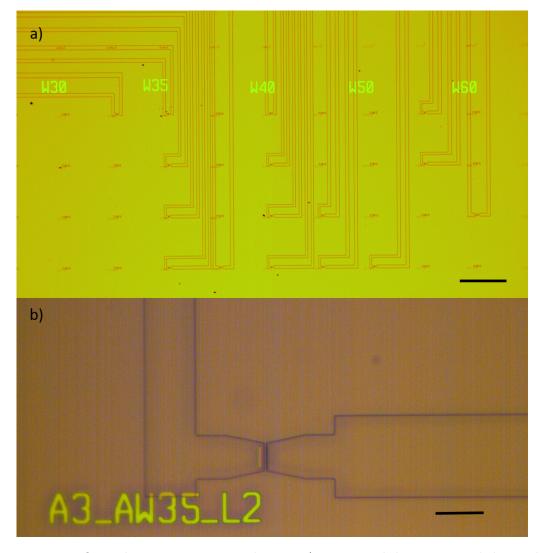

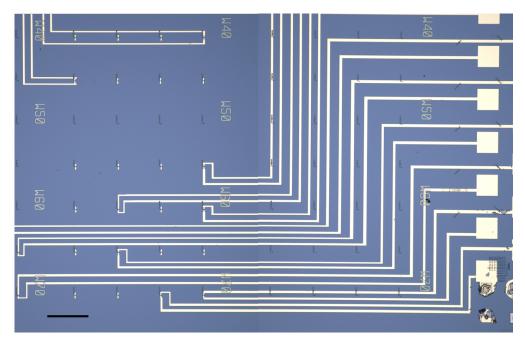

|       | Optical microscope image showing a) source and drain contact lithography in PMMA resist and b) zoom in on one device. Scale bar 300 $\mu$ m and 15 $\mu$ m.        | 69 |

| 3.37  | Optical microscope image after metallization of source & drain areas. Scale                                                                                        |    |

|       | bar is $100~\mu m$                                                                                                                                                 | 70 |

|       | SEM image after metallization of Source & Drain areas. Scale bar is 100 $\mu \mathrm{m}$                                                                           | 71 |

| 3.39  | SEM image of a zoom in of source and drain metallization on a single device,                                                                                       |    |

|       | in the inset a zoom out of the entire device with pads is seen. Scale bar is                                                                                       | _  |

| 0.10  | 200 nm and 300 nm for inset                                                                                                                                        | 71 |

| 3.40  | Optical microscope image shows source and drain metallization on many                                                                                              |    |

|       | devices leading to the large 150 $\mu$ m X 150 $\mu$ m contact pads. Scale bar is 300                                                                              | 70 |

|       | $\mu$ m                                                                                                                                                            | 72 |

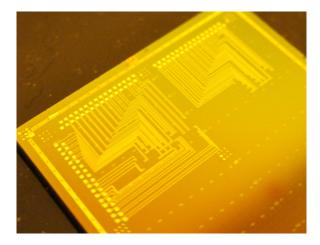

| 3.41 | Photograph of a chip after complete fabrication                                    |

|------|------------------------------------------------------------------------------------|

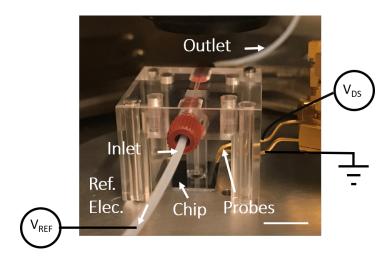

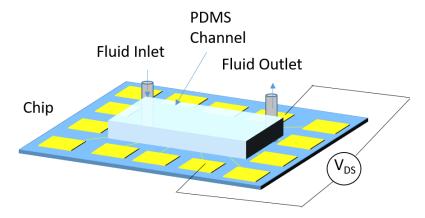

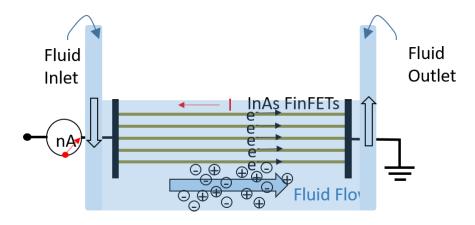

| 4.1  | Fluidic measurement setup. Scale bar is 1 cm                                       |

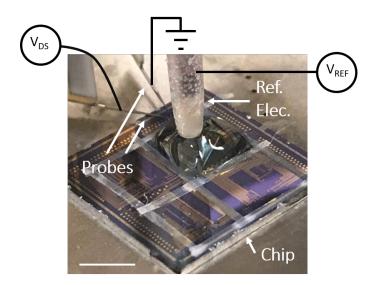

| 4.2  | Droplet setup for ISFET measurement                                                |

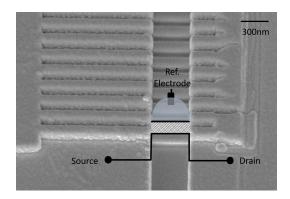

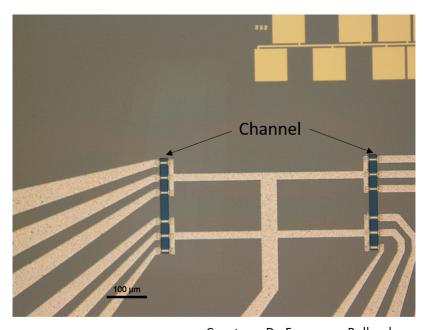

| 4.3  | SEM image show s source and drain metallization on complete device and             |

|      | also how the measurement is carried out on the device                              |

| 4.4  | a) pH response of the device and b) voltage sensitivity extraction for the same    |

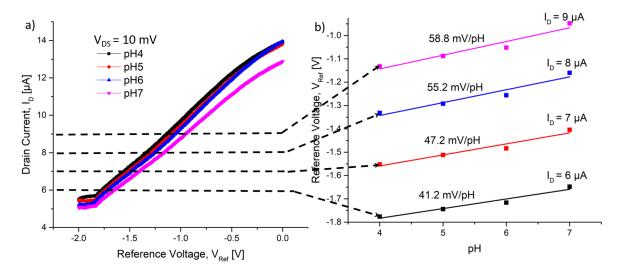

|      | 40 nm wide fin                                                                     |

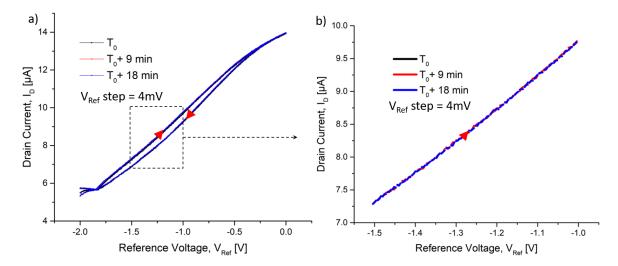

| 4.5  | a) At pH 4 repeatability of pH response for different time points in a voltage     |

|      | interva and b) pH response curves repeatability for the entire voltage sweep       |

|      | also showing hysteresis                                                            |

| 4.6  | a) At pH 4 repeatability of pH response for the entire voltage sweep also          |

|      | showing forward to backward sweeps and b) pH response repeatability at pH          |

|      | 4 for different time points in a select voltage interval                           |

| 4.7  | Cross section illustration of device pointing to likey interface defects resulting |

|      | in hysteresis in transfer characteristics                                          |

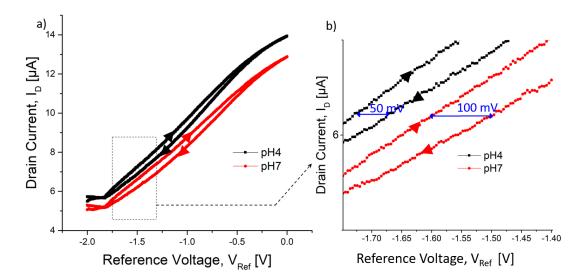

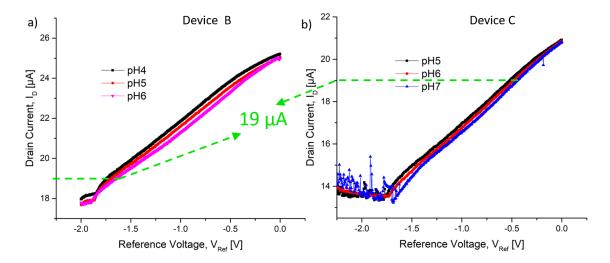

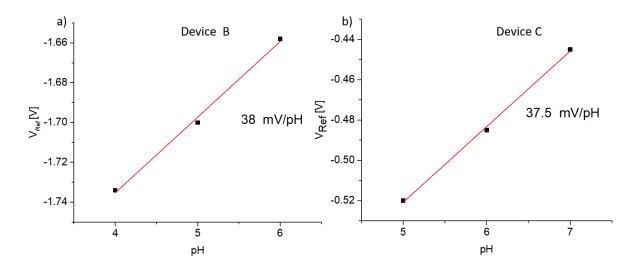

| 4.8  | pH response curves for a) device B and b) device C                                 |

| 4.9  | Sensitivity extracted at 19 $\mu$ A for a) device B and for b) device C            |

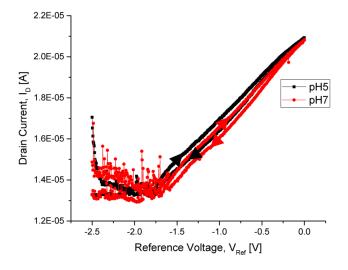

| 4.10 | Hysteresis in device C for pH 5 and pH 7                                           |

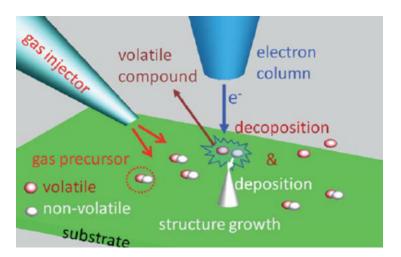

| 4.11 | Schematic of FIB Deposition Principle                                              |

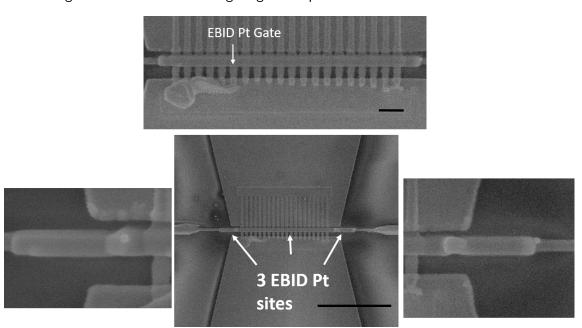

| 4.12 | SEM right after EBID Pt deposition process. Scale bar 500 nm and 4 $\mu$ m         |

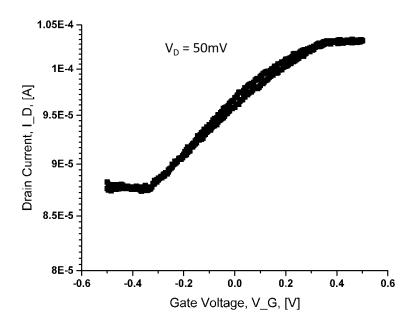

| 4.13 | $I_{D^{-}}V_{G}$ characteristics from a EBID Pt gate modulated device $\dots\dots$ |

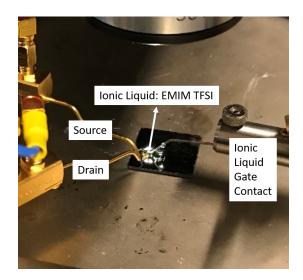

| 4.14 | IL Measurement Setup                                                               |

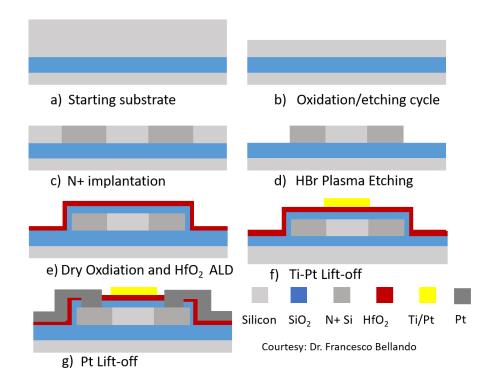

| 4.15 | Main steps in fabrication process of SOI Ribbon FET                                |

| 4.16 | Main steps in fabrication process of SOI Ribbon FET                                |

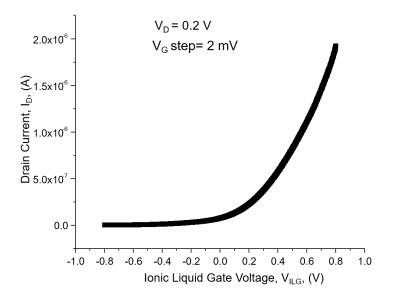

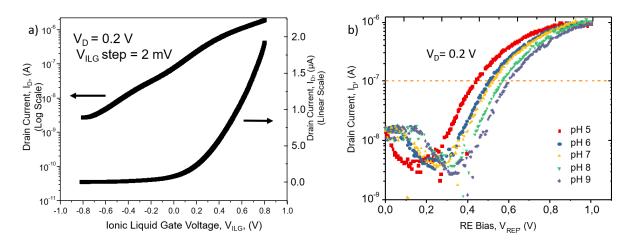

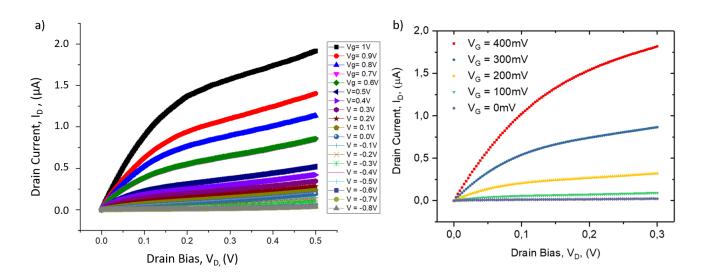

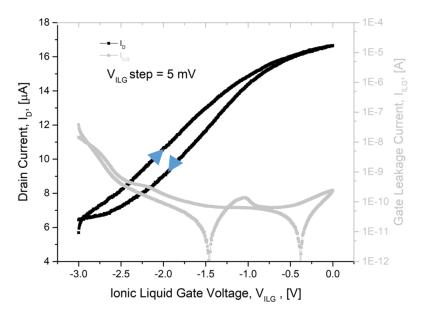

| 4.17 | SOI Ribbon FET transfer curve response to IL gating                                |

| 4.18 | SOI Ribbon FET1 IL response versus pH Response                                     |

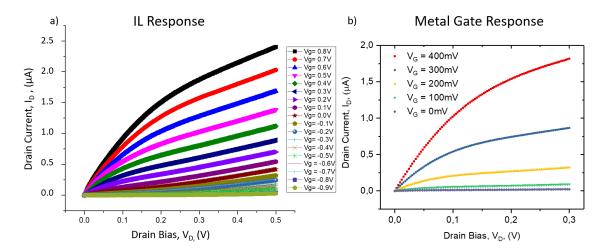

| 4.19 | Comparison of SOI Ribbon FET1 output characteristics for IL gating and             |

|      | metal gating                                                                       |

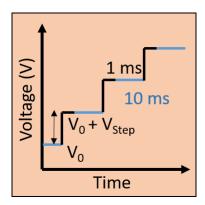

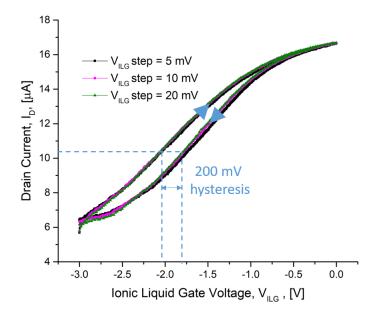

| 4.20 | Type of voltage signal applied to the gate in order to control sweep rate          |

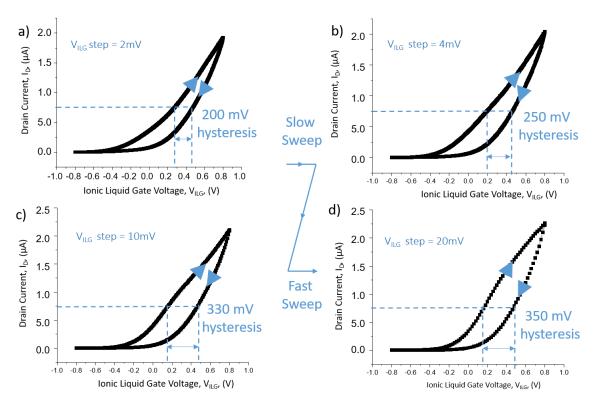

| 4.21 | SOI Ribbon FET 1 effect of changing sweep rate on hysteretic loops                 |

| 4.22 | SOI Ribbon FET 2 transfer curve response to IL gating                              |

| 4.23 | SOI Ribbon FET 2 IL response versus pH Response                                    |

| 4.24 | Comparison of SOI Ribbon FET 2 output characteristics for IL gating and            |

|      | metal gating                                                                       |

| 4.25 | InAsOI FinFET device response with IL gating drain current to the left axis        |

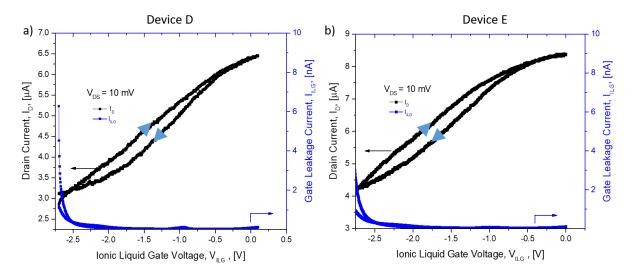

|      | and gate leakage current to the right of the axis.                                 |

| 4.26 | Investigation of hysteresis effect in InAsOI FinFET by varying the sweep rate.     |

| 4.27 | InAsOI FinFET IL Reproducibility                                                   |

| 4.28 | InAsOI FinFET vs InAs NW IL gating transfer response                               |

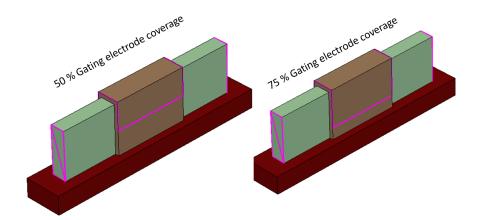

| 4.29 | Device schematic for simulation of partial gating electrode (left) 50 % gating     |

|      | and (right) 75 % gating.                                                           |

|      |                                                                                    |

#### List of Figures

| 4.30 | Device simulation showing transfer characteristics of partial gating electrode                                          |     |

|------|-------------------------------------------------------------------------------------------------------------------------|-----|

|      | (left) 50 % gating and (right) 75 % gating                                                                              | 94  |

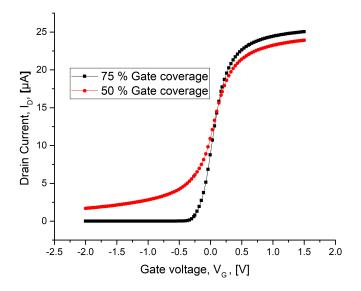

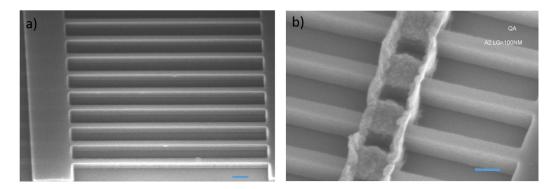

| 4.31 | Tilted (30 $^{\circ}$ ) SEM image of a) device before patterning and b) after EBL                                       |     |

|      | patterning, tungsten sputtering without any tilt and lift-off of resist. Scale                                          |     |

|      | bar is 200 nm and 100 nm                                                                                                | 95  |

| 4.32 | Tilted (30 $^{\circ}$ ) SEM image of a FIB cross section showing continuous metal                                       |     |

|      | $\label{eq:film-on-a-multiple} \ \ \text{film-on-a-multiple-fins-with-tilted-sputtering-of-W-but-without-an-EBL-step.}$ |     |

|      | Scale bar is 100 nm and 100 nm                                                                                          | 95  |

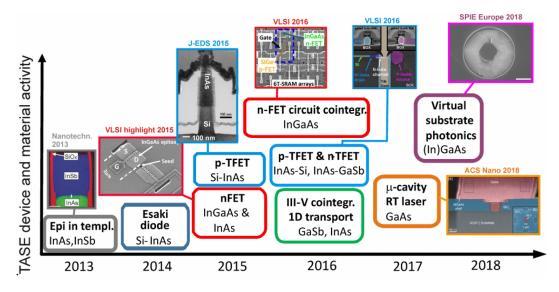

| 5.1  | TASE device and material activity                                                                                       | 97  |

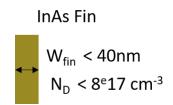

| 5.2  | InAs fin cross section                                                                                                  | 100 |

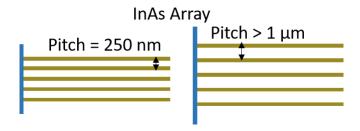

| 5.3  | InAs fin array design                                                                                                   | 100 |

| 5.4  | InAs FinFET with on chip reference electrode and supporting microfluidics .                                             | 101 |

| 5.5  | InAs fin arrays usef for energy harvesting                                                                              | 101 |

## List of Tables

| 2.1        | Table of scaled parameters for dennards law and generalized scaling law         | 8  |

|------------|---------------------------------------------------------------------------------|----|

| 2.2        | Table of ionic liquid specifications                                            | 13 |

| 2.3        | Electrochemical windows calculated for various ILs at a cut-off current density |    |

|            | of 0.5 mA/cm $^2$ using GC electrode at 25 °C                                   | 14 |

| 2.4        | A comparison of silicon & InAs electronic properties                            | 31 |

| 2.5        | A comparison of Si & InAs crystal properties                                    | 35 |

| 3.1        | Summary of the technology development achievements from this chapter            | 73 |

| 4.1        | Summary of sensor response                                                      | 96 |

| 5.1<br>5.2 | III-V Fin geometry comparison                                                   | 98 |

|            | terization                                                                      | 99 |

## 1 Thesis Overview

An overall outline of the thesis structure is given here.

Chapter 2- At the start, a broad context for the work of ion sensing in healthcare and environmental monitoring is provided. Then the reader is refreshed with main concepts to bear in mind while reading the thesis. A). Basics of computing technology are presented: Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) principle, how MOSFET miniaturization benefits the electronic industry, different conduction mechanisms in MOSFET with a focus on junctionless transistor (used in this thesis) and how multiple gate architectures, emphasizing Fin Field-effect transistor (FinFETs) are relevant. Further, a brief discussion for iontronics is given since ionic liquid (IL) gating is also employed to characterize device functioning. B). Field of electrochemical sensing is introduced: principle of conventional ion selective electrodes (ISEs) is given, concepts of Nernst limit, electrical double layer, reference electrode are elucidated. The gradual progression towards solid-state ISEs is explained. Next, we rationalize field-effect transistor (FET) based electrochemical sensing and speak about its figures of merit such as sensitivity, responsivity, detection limit and specificity. The case for importance of a nanoscale FET sensor to improve the various figures of merit is given. C). Through a review of scientific literature for InAs nanoscale sensors the interest of the scientific community in using InAs nanostructures especially NWs for electrochemical and biological sensing is iterated. D). Finally, we systematize the choices in our system in terms of material, integration platform, sensing geometry, sensing area, sensing oxide and summarize these reasons towards an InAsOI FinFET sensor and computing module.

Chapter 3- The entire technology development process steps to realize working devices are detailed here. The fabrication is classified under 3 main divisions- pre-growth steps, epitaxy growth process and post growth processing. Fabrication issues and how they were tackled are extensively presented. All process steps were carried out entirely by the author at the cleanroom of Center for micronanotechnology institute (EPFL) except for the step of metal organic chemican vapor deposition growth that was done by collaborators at IBM Research

#### Thesis Overview

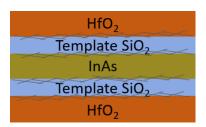

Zurich and the transmission electron microscope images taken in collaboration with staff at the Interdisciplinary Center for Electron Microscopy (EPFL). The fabricated devices are referred to as InAs-On-Insulator (InAsOI) FinFETs

**Chapter** 4- The first measurement results of built devices as ion-sensitive field effect transistor are presented. To further characterize the devices other gating techniques are explored - metal gating and ionic liquid gating are used. Another fabrication batch is necessary in order to carry out more detailed statistical analysis. With changes in design, growth process the limitations of current results can be resolved and steps taken towards this end are also addressed.

**Chapter 5**- The main contributions of this work are highlighted to conclude the thesis work. For future perspectives a case for sensing based on different electronic principles such as tunneling field effect transistors is made. The chosen technology module of this thesis is highly versatile and suitable for such a future tunneling transistor implementation.

## 2 Introduction

#### 2.1 Motivation

Internet of Things (IoT) is a concept where a swarm of sensors and devices are deployed ubiquitously, collect data continuously and are connected to the internet to communicate with each other. The concept isn't new as there existed IoT objects such as automatic teller machines (ATMs) and cold drink vending machines as early as 1970s and 1980s that were connected to the internet and monitored remotely. However the context in which IoT is relevant today is all-pervasive from healthcare to environmental monitoring, automotive industry, to agriculture, manufacturing industry and energy management in every day home and office spaces. These IoT devices enable generation and collection of vast amounts of data that can be processed at the edge or the cloud in order to respond in real-time to various scenarios.

loT is taking the world by storm as the number of smartphones are surging, technology costs are going down, more devices with internet capabilities and sensors are built and the cost of connecting to the internet is decreasing. As of late 2000s, the number of devices connected to the internet were declared to have surpassed the number of people connected to it. And it is further predicted that by 2030 a 100 trillion connected devices will be present in the world [1].

The demand for ion-sensors and biosensors has also risen due to their offering of continuous real-time and parallel detection of multiple species along with being low cost and portable. These features are very attractive for point-of-care applications for healthcare as well as remote environmental monitoring. Rising and aging populations in many parts of the world lead to increased healthcare burden on governments and societies. An increasing concern is reducing these medical costs. Medicine is progressing towards a personalized era thanks to its clinical relevance. In personalized medicine, two key aspects can be differentiated as personalization in the prediction of illness and the treatment of illness are both important. Patient monitoring systems enable early diagnosis of diseases or illness condition. During

illness treatment, tailoring drug therapeutics to individual's unique needs enables maximum drug efficacy. Molecular diagnostics based on patient's DNA allow clinicians to identify the possible outcome of a patient to a particular treatment in advance of administering. Conventional laboratory diagnostic platforms are struggling to cope with these demands of personalized medicine.

On the bright side with developments in semiconductor technology, there has been an emergence of FET based solutions for clinical diagnostics [2, 3, 4, 5, 6, 7]. Advances in electronics, biotechnology, microfluidics and micro-nano technology have paved way for these analytical systems at the micron scale. The FET, a workhorse of the electronics industry is a mature component which can be configured to measure responses to biological or chemical reactions. Ion torrent and DNA electronics are companies which develop next generation sequencing (NGS) techniques where the system directly translates chemical sequences (A, C, G, T) into digital information (0,1) on a semiconductor chip. In other words the system marries chemistry to proven semiconductor technology or is when Watson meets Moore. DNA electronics are examples of companies exploiting diagnostic technology using ion sensitive FETs. The advantages of these technologies are obvious low power consumption, miniaturization, high-throughput, rapid sequencing at an economic scale using semiconductors. NGS is currently driving discovery and enabling the future of personalized medicine.

This FET ion sensing technology has implications not only in the healthcare industry but other industries too. Measurement of ions such as  $CN^-$ ,  $F^-$ ,  $S^-$ ,  $CI^-$  - in the context of water pollution monitoring,  $Pb^{2+}$ ,  $Hg^+$ ,  $Cd^+$ ,  $As^+$  - in air pollution monitoring,  $NO_3^-$ ,  $NO_2^-$  -in food processing industry,  $Ca^{2+}$  in dairy industry,  $K^+$  in fruit juice industry or  $H^+$ ,  $Na^+$ ,  $K^+$ ,  $Ca^{2+}$  in the healthcare industry [8, 9, 10, 11, 12]. It is towards such an FET based ion sensing application that this thesis is also directed.

#### 2.2 Computation Unit: MOSFET

A transistor can be described as the most basic computation component of nearly all modern electronic equipment. In this section, we will see how the evolution of transistor led to great improvements in computating power. And in the next section 2.3.2 how the same technology is also advantageous to a sensing configuration. Any electronic device is made up of millions and possibly billions of transistors working together. This is why efforts in making them smaller, more efficient and cheaper are eternal. The transistor was first patented by Julius E.Lilienfeld in 1925 [13]. However, Walter Brattain, John Bardeen and William Shockley are historically credited with the first successful demonstration of a field-effect transistor in 1948 [14]. A transistor is simply a portmanteau of the words transfer and resistor as it transfers a signal at the input with a particular resistance to the output at a different value. Today, MOSFETs are the most widely used type of transistors in the integrated circuit (IC) industry. They have four terminals: source, drain, gate and bulk. In a lot of times, the source and body terminals are connected to each other making the device three terminal in

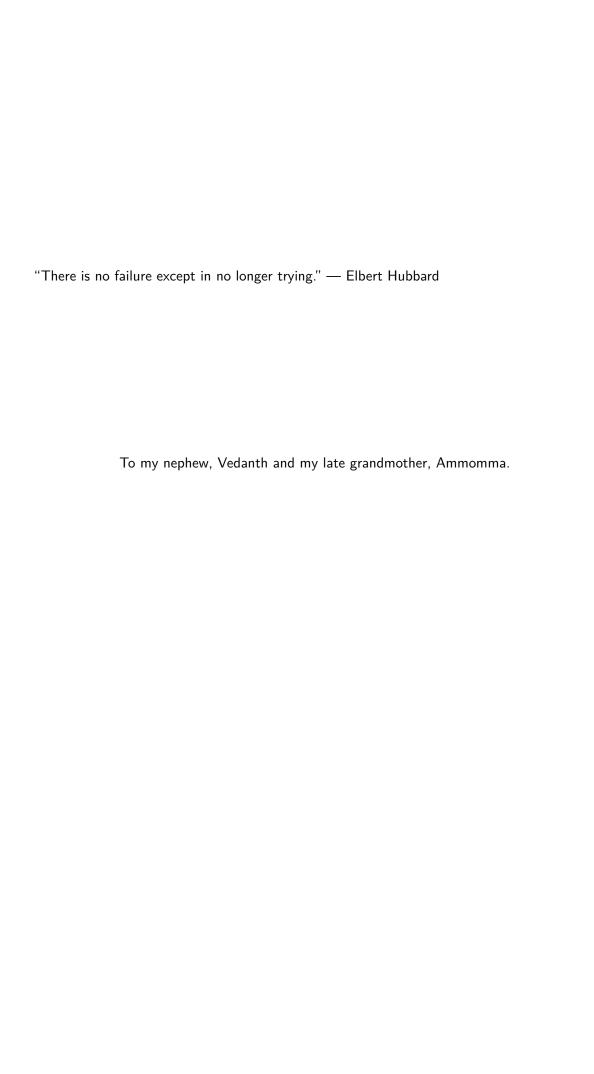

operation. Essentially the current flow between the drain and source is controlled by the gate terminal through a gate oxide hence the name field-effect as shown in the schematic of figure 2.1(a). The source and bulk terminals are grounded together. In the device, the gate source voltage (or in short, gate voltage) is  $V_{GS}$ , the drain source voltage is  $V_{DS}$  are applied and the drain current,  $I_{DS}$  is read out. The transfer characteristics of a n-type MOSFET is shown in figure 2.1(b). One can distinguish a region where current grows exponentially called the sub-threshold region. After a certain gate voltage called the threshold voltage  $(V_{Th})$  the transistor is considered to be turned ON. Here on, the current grows gradually and eventually enters a linear region of operation.

Figure 2.1 – n-type MOSFET schematic with 4 terminals.

When using a MOSFET in digital applications, it is operated as a switch. The transistor switches between two distinct, stable states: OFF and ON, making them binary logic state devices. While the transition from OFF to ON state is relevant in terms of charge needed to change states and for speed of the final operation. Whereas, for MOSFET as an analog block, the transition region between OFF and ON states is very important. In this transition region, the subthreshold region, incremental changes in  $V_{GS}$  modulate the output  $I_D$  over a wider range. The MOSFET device is at the heart of the electronic industry revolution. Two important figures of merit for MOSFETs are the inverse substhreshold slope, also known as the substhreshold swing (SS) and the transconductance efficiency that are described as follows. Shown in equation 2.1 and equation 2.2 are SS and the units are mV/dec.

$$SS = \frac{dV_{GS}}{d(log(I_{DS}))} = \left(\frac{dV_{GS}}{d\phi_S}\right) \cdot \left(\frac{d\phi_S}{d(log(I_{DS}))}\right) = m \cdot n \tag{2.1}$$

where m =  $\frac{dV_{GS}}{d\phi_S}$  is known as the body factor and n =  $\frac{d\phi_S}{d(log(I_{DS}))}$  is a factor related to injection mechanism in particular the distribution of electrons according to Fermi-Dirac

statistics and depends only on temperature. Therefore, SS can be re-writen as follows:

$$SS = m \cdot n = \left(1 + \frac{C_D + C_{it}}{C_{ox}}\right) \frac{kT}{q} \ln(10) = 59\left(1 + \frac{C_D + C_{it}}{C_{ox}}\right) mV/dec$$

(2.2)

In equation 2.3 is the transconductance efficiency or transconductance-to-current ratio which is an important parameter for analog design.

$$\frac{g_m}{I_{DS}} = \frac{1}{I_{DS}} \frac{\delta I_{DS}}{\delta V_{GS}} = \frac{\delta (ln I_{DS})}{\delta V_{GS}} = \frac{ln(10)}{SS}$$

(2.3)

MOSFETs implemented in a particular style of circuit design called complementary metal-oxide semiconductor (CMOS) are the norm for the IC industry now. Complementary means logic functions are performed in pairs of devices nMOSFET and pMOSFET. In the pair only one transistor is ON at a time and the combination allows to consume power only momentarily while switching between ON & OFF state. Hence, the main highlights of CMOS technology are good noise immunity and low static power dissipation.

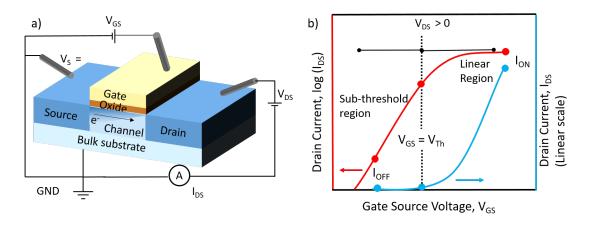

Figure 2.2 – a) Visualization of Moore's Law with the number of transistors in a commercial processor by INTEL with year of introduction, b) Graph prepared by Gordon Moore on the number of components per function growing over the years. Graphs taken from [15, 16].

The microelectronics industry has gained immensely from MOSFET miniaturization. Gordon Moore, co-founder of Fairchild Semiconductor in 1965 published a seminal paper which predicted that the components (transistors, capacitors, resistors and diodes) in an IC doubles roughly every two years [15]. This is visualized in two graphs that alternately

represent the same idea in figure 2.2. In figure 2.2 (a) an increase in number of transistors per processor and in figure 2.2 (b) the increase in number of components both with respect to time in years. Infact this observation he made became so popular that it went on to dictate the economics of the electronic industry for decades and is popularly known as Moore's law.

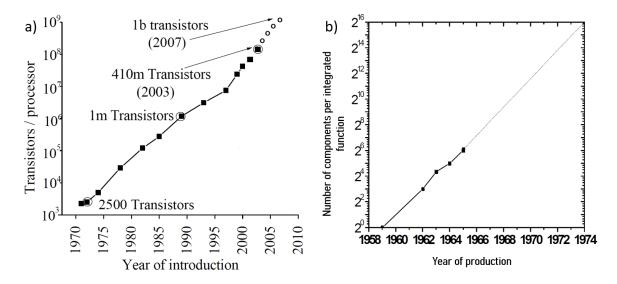

Figure 2.3 – Performance of CPU with time in terms of cost, functionality and high performance.

In the 1960s an IC chip had few transistors, within three orders of magnitude. Whereas today millions and possibly billions of transistors exist on a central processing unit (CPU) chip or a micro-processor unit (MPU) chip as we see in figure 2.3. The advantages of miniaturization and implications of Moore's law can be seen in figure 2.3 which include increasing functionality per chip, reducing manufacturing cost of processor units and building higher preformance systems.

Figure 2.4 – Dennard scaling law visualized in a MOSFET structure: scaling doping concentration (in orange), physical parameters (in blue), supply voltage (in green) Modified from [16].

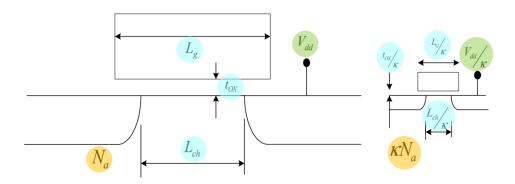

In 1974, Robert Dennard  $et\ al.$  and others published a paper that delved into the how the physics of MOS scaling enables performance enhancement from which constant field scaling theory emerged[17]. A linear transformation by a scaling factor, k is applied to three parameters: supply voltage,  $V_{dd}$ , doping concentration,  $N_a$ , and to physical dimensions of gate length,  $L_G$ , channel length,  $L_{ch}$  and gate oxide thickness,  $t_{OX}$  in a way that the device electric field scaling remains constant. Pictured in figure 2.4 modified from [16] is a sketch on left (right) is the device before (after) scaling. Despite changes in the above mentioned parameters, the electric field intensity written as Voltage/Length cancels out the scaling factor and remains unchanged.

| Scaled Parameters                        | Constant field Scaling | Generalised scaling    |

|------------------------------------------|------------------------|------------------------|

| $t_{OX}$ , $L$ , $W$ , $X_{j}$ , $W_{d}$ | 1/κ                    | 1/κ                    |

| $N_a, N_d  (ions/cm^3)$                  | K                      | $\alpha\kappa$         |

| Power supply: $(V_{dd})$                 | $1/\kappa$             | $lpha/_{\kappa}$       |

| Electric field in device: ( $E$ )        | 1                      | $\alpha$               |

| Capacitance: (C)                         | 1/ <sub>K</sub>        | 1/κ                    |

| Inversion charge density (Q)             | 1                      | $\alpha$               |

| Circuit delay time: $	au^{CV}/I$         | $1/\kappa$             | 1/κ                    |

| Power dissipation: (P)                   | $\frac{1}{\kappa^2}$   | $\alpha^2/_{\kappa^2}$ |

| Power density $(\sim P/A)$               | 1                      | $lpha^2$               |

| Circuit density                          | $\kappa^2$             | $\kappa^2$             |

| Chip Area (A)                            | $\frac{1}{\kappa^2}$   | $\frac{1}{\kappa^2}$   |

| Current, Drift: (I)                      | 1/κ                    | 1/κ                    |

Table 2.1 – Scaled parameters for Dennard's law and generalized scaling law. Taken from [16].

However as the MOSFET scaling continued and the channel length started becoming comparable to the depletion layer width of the source and drain junction negative effects called short channel effects (SCE) started coming into play [18]. The effects of SCEs among others are drain incuded barrier lowering (DIBL) and surface scattering of carriers. Therefore when the device dimensions entered sub-micron dimensions, two-dimensional effects in SCE and DIBL became important. Hence, the gradual field approximation became invalid and the field increased and resulted in slower reduction in supply voltage than predicted by constant field scaling [19, 20]. Brews *et al.*, Baccarani *et al.* introduced a more generalized scaling rule taking into account an additional parameter scaling constant  $'\alpha'$  and generalized scaling

took the form shown in equation 2.4 [19, 20].

$$V'_{dd} = -\frac{\alpha}{\kappa} V_{dd} \Rightarrow \alpha = \kappa \frac{V'_{dd}}{V_{dd}}$$

(2.4)

where  $V_{dd}=$  Supply voltage of previous generation,  $V'_{dd}=$  New supply voltage,  $\alpha=$  scaling constant,  $\kappa=$  scaling factor. A summary of the Dennard scaling and generalized scaling parameters is shown in the table 2.1.

#### 2.2.1 Conduction Mechanisms

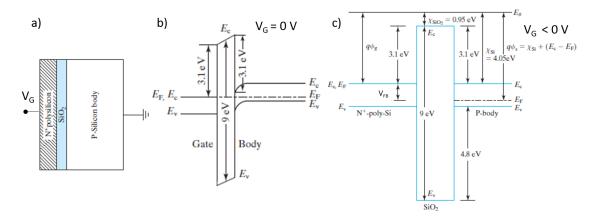

MOSFETs can be classified as normally OFF and normally ON devices when no gate source voltage is applied i.e  $V_{GS}=0$  V. In normally OFF devices, drain current is blocked due to a reverse biased drain-channel junction. On the other hand for normally ON devices, drain current conducts because there is a channel between source and drain and a voltage needs to be applied to turn OFF the device. The work function difference between the gate electrode and the semiconductor helps to tune this normally ON and normally OFF behaviour. An important constituent of a MOSFET is the presence of semiconductor junctions at the source and drain regions and the presence of a MOS capacitor (MOSCAP) block. The MOSCAP under consideration is shown in figure 2.5(a) [21]. Where the body is p-type silicon, the gate oxide is  $SiO_2$  and the gate electrode in this case is  $N^+$  doped polysilicon. The gate voltage is  $V_G$  and all potentials are referenced with respect to the body or bulk terminal which is grounded.

Figure 2.5 – MOS capacitor behaviour. Schematic modified from [21].

In figure 2.5(b) - (c) are energy band diagrams drawn across the three sections of the device when no gate voltage has been applied and when a negative gate voltage is applied respectively. In figure 2.5(c) one can see that the energy bands ( $E_C$  and  $E_V$ ) of the substrate are flat at the gate-oxide-silicon substrate interface and this condition is known as the flat band condition and occurs when a negative voltage is applied at the gate terminal. The

notations of the symbols used in the figure are as follows:  $\mathsf{E}_C=$  conduction band energy,  $\mathsf{E}_V=$  valence band energy,  $\mathsf{E}_F=$  fermi energy level,  $\mathsf{E}_G=$  band gap,  $\chi_{Si}=$  electron affinity in silicon,  $\chi_{SiO_2}=$  electron affinity in silicon dioxide,  $\psi_g=$  gate material work function,  $\psi_S=$  semiconductor work function and  $\mathsf{V}_{FB}=$  flat band voltage.

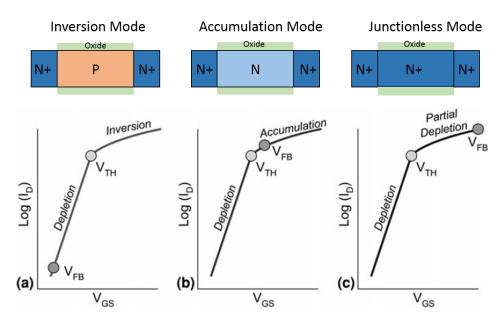

For a n-type MOSFET, the doping configurations and the transfer characteristics for three different operation modes are illustrated in figure 2.6(a)-(c) and are inversion mode, accumulation mode and junctionless mode. Where  $V_{TH}$  is the threshold voltage after which the device is considered to be turned ON. The  $V_{FB}$  is flatband voltage as described in the earlier paragraph. The transfer characteristics of the three modes resemble eachother however it must be kept in mind that the underlying conduction mechanism is still different.

Figure 2.6 – Drain current (log scale) vs gate voltage - transfer characteristics are shown for three different MOSFET modes a) Inversion b)Accumulation c) Depletion. Image taken from [22].

- In inversion mode, below  $V_{TH}$ , the device is either partially depleted or fully depleted. And  $V_{FB}$  is at a voltage lower than  $V_{TH}$ , in the OFF region of the device. Below  $V_{FB}$ , the body of the substrate is neutral p-type. Above  $V_{TH}$ , when turned ON, the channel region is depleted, forms a weak *inversion* layer and then a stronger inversion layer.

- In accumulation mode, below  $V_{TH}$  the channel is fully depleted. When a section of the channel is no longer depleted then one reaches  $V_{TH}$ . When  $V_{GS}$  is increased further, the channel becomes neutral, with no depletion, reaching  $V_{FB}$ . For higher  $V_{GS}$  than  $V_{FB}$  an accumulation layer forms in the ON state of the device.

- In junctionless mode, the entire semiconductor is highly and uniformly doped from source to channel to drain region. Below  $V_{TH}$  is partially or fully depleted and turend

OFF. At  $V_{TH}$  the peak electron concentration in the channel reaches that of the background doping level,  $N_D$ . When  $V_{GS}$  is increased further, the entire channel cross section reaches  $N_D$  concentration and hence  $V_{FB}$  is reached.

Particulary junctionless transistors have gained interest as they do not have semiconductor junctions. In inversion mode devices, formation of ultra-shallow junctions with high doping concentrations beccame a big challenge because of diffusion laws and statistical nature of doping of atoms [22]. A junctionless architecture is a highly doped semiconductor block in the form of a thin layer as used in double gate planar MOSFET (DG MOSFET) or nanowire (NW FET) or a fin (FinFET). The cross section of the device is important as it has to be narrow enough to enable turn OFF.

# 2.2.2 Multiple Gate Architecture

When MOSFETs were scaled into sub-micron range the performance starts to degrade significantly and this does not favour the miniaturization trend. For a planar MOSFET, the electrostatic control of the channel is essentially one dimensional. This led to problems such as short channel effects - sub-threshold slope degradation and Drain induced barrier lowering (DIBL) when scaled down. Multiple-gate architectures started to emerge in response to enhancing such performance limitations [23]. The electrostatic control over channel can be regained by changing the shape of MOSFET to more two (2D) dimensional or three dimensional (3D) architectures. A multiple-gate is when the gate metal wraps around the channel of nanowire or fin in 3D FET structures. In section 2.6.5 using TCAD simulations the performance of the multi-gate FinFET structure of this thesis work is presented.

# 2.2.3 Novel Gating Architecture: Ionic Liquid Gating

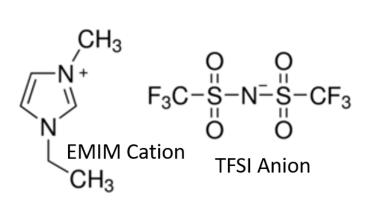

lontronics is an emerging field that seeks to control electronic devices with materials such as ionic liquids (IL) in which charge carriers are ions [24]. Iontronics as a technology is overarches the fields of solid-state electronics and biological systems. An IL is a substance, purely ionic, described as a salt and are present in liquid state at unsually low temperatures. They are often compared to the boiling point of water (100  $^{\circ}$ C) as a reference i.e an IL is a liquid below 100  $^{\circ}$ C. A diagram in figure 2.7 summarizes the interesting properties of ILs and their applications in a wide range of fields.

Figure 2.7 – Diagram summarizing ionic liquid properties and applications. Taken from [25].

A key aspect of ILs is the formation of an electric double layer (EDL) at the interface of an electronic conductor that is known to induce very high electric fields and results in efficient carrier modulation [26, 27]. The accumulaiton of charge carriers can be used to demonstrate various phenomena such as phase transition, magnetic ordering and superconductivity [27]. The EDL between ionic conductors (i.e also behaving as electronic insulators) and electronic conductors are exploited to build novel electronic concepts [24, 28]. At the nanoscale with high performance solid-state devices hitting a road block, researchers are pursuing unconventional ways of processing not based on solid-state electronics e.g molecular logic gates [29, 30], chemical logic gates [31], microelectrochemical logic circuits [32] and DNA computing [33]. In the review paper by Chun et al., it is explained how iontronics is close to nature than solid-state electronics in the following ways: 1) since information in biological systems is

transmitted by a variety of ions Na<sup>+</sup>, K<sup>+</sup>, Cl<sup>-</sup>, Ca<sup>2+</sup> and 2) biological processors have highly dynamic structures that operate non-linearly. For example, ion transport in cell membranes polarizes and depolarizes neurons in the brain. Charge selectivity towards specific ions or molecules can be tailored indicating the application of iontronics for analytical chemistry. Moreover iontronic devices are made of hydrogels that function in aqueous environments therefore have less restrictions for biocompatible, biodegradable logic circuits for sensing [24].

| Ionic liquids specific |

|------------------------|

|------------------------|