# $C_{\rm oss}$ Loss Tangent of Field-Effect Transistors: Generalizing High-Frequency Soft-Switching Losses

Nirmana Perera, Student Member, IEEE, Mohammad Samizadeh Nikoo Member, IEEE, Armin Jafari, Luca Nela, Student Member, IEEE, and Elison Matioli, Member, IEEE

Abstract—The dissipated energy  $(E_{\rm diss})$  related to the resonant charging/discharging of a transistor output capacitance, becomes a dominant loss factor for power converters operating in the MHz range. A recent work has introduced a small-signal measurement method to quantify  $E_{\text{diss}}$  with a frequency-dependent small-signal resistance,  $R_s$ , and an effective small-signal output capacitance,  $C_{

m oss}^{

m eff}$ . This work provides further insights on the effect of  $R_{

m s}$  and  $C_{\rm oss}$  upon the device losses in a broader sense. In particular, the  $C_{oss}$  loss tangent,  $tan(\delta)$ , is introduced as a normalized  $E_{\rm diss}$  to combine the roles of  $R_{\rm s}$  and  $C_{\rm oss}$  together with the operating frequency into a single loss parameter. By evaluating commercial device families, it is demonstrated that  $\tan{(\delta)}$  is constant for a given family, independent of the device on-state resistance,  $R_{DS(on)}$ . It is shown that a minimum  $E_{diss}$  is achieved by having the lowest  $tan(\delta)$  for a given stored energy  $(E_{oss})$  in  $C_{oss}$ . With accompanying guidelines, this work identifies  $tan(\delta)$  as a powerful figure of merit to classify field-effect transistors for softswitching applications, regardless of  $R_{DS(on)}$  variations in devices within a family. The proposed concept provides a comprehensive method to characterize and benchmark power transistors for high-frequency applications.

Index Terms— $C_{\rm oss}$ ,  $C_{\rm oss}$  losses,  $E_{\rm diss}$ , output capacitance, modeling of losses, soft-switching loss, loss tangent, WBG devices.

### I. INTRODUCTION

IDE-Band-Gap (WBG) devices have paved the way to push the boundaries of power conversion in the MHz range, especially for soft-switching and resonant power converters [1]–[3]. One of the major factors that hinders this trend is the non-recoverable power losses associated with device output capacitance,  $C_0$  (where the corresponding small-signal quantity is defined as  $C_{\rm oss}$  in device data sheets [4]). The topic has gained heightened attention since the observation of large-signal hysteresis losses in charging/discharging  $C_0$  of Si Super-Junction (SJ) MOSFETs [5]–[7], followed by similar observations in WBG devices [8]–[11].

Based on impedance measurements, a recent work on the topic reported the existence of a small-signal series resistance  $(R_{\rm s})$  related to  $C_{\rm oss}$  [12]. The work further presented a small-signal measurement model (see Fig. 1(a)) to quantify the frequency-dependent large-signal energy losses related to the output capacitance of WBG devices. The model consists of two elements in series [12]: a nonlinear (voltage-dependent) effective small-signal capacitance  $C_{\rm oss}^{\rm eff} = \sqrt{\frac{1}{V_{\rm p}}} \int_{0}^{V_{\rm p}} C_{\rm oss}^2 dv_{\rm DS}$  that encompasses the total variation of  $C_{\rm oss}$  for a given voltage

This work was supported in part by the Swiss Office of Energy (SFOE) Grant Number SI501887-01 (MEPCO) and in part by the Swiss National Science Foundation under Assistant Professor (AP) Energy Grant PYAPP2\_166901. The authors are with the Power and Wide-BandGap Electronics Research Laboratory, École Polytechnique Fédérale de Lausanne, 1015 Lausanne, Switzerland (e-mail: nirmana.perera@epfl.ch, mohammad.samizadeh@epfl.ch, armin.jafari@epfl.ch, luca.nela@epfl.ch, elison.matioli@epfl.ch).

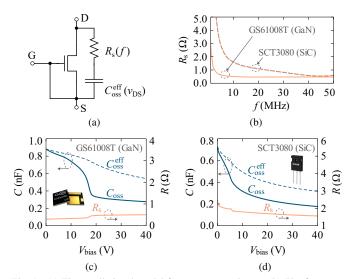

Fig. 1. (a) The small-signal model for output capacitance. (b) The frequency dependence of  $R_{\rm s}$  for a 100-V GaN device and a 650-V SiC device, where (c) and (d) show the variation of  $C_{\rm oss}$ ,  $C_{\rm oss}^{\rm eff}$  and  $R_{\rm s}$  with bias voltage for the same devices. A Keysight E4990A impedance analyzer with a 16047E test fixture (50 MHz) was used with an excitation signal of f=10 MHz at a peak of 100 mV. The gate and source terminals of the transistors were shorted, i.e.  $v_{\rm GS}=0$  V ( $C_{\rm oss}=C_{\rm GD}+C_{\rm DS}$ ).

excitation on the device's drain-source voltage,  $v_{\rm DS}$ , with a peak value of  $V_{\rm p}$ ; and  $R_{\rm s}$ , whose value is frequency-dependent. The dissipated energy  $(E_{\rm diss})$  in charging/discharging the  $C_{\rm oss}$  branch, in a full cycle, is attributed to  $R_{\rm s}$ .

This letter reports important findings on  $R_s$  related to commercial normally-off device families, and investigates its implications in a broader sense to generalize high-frequency soft-switching losses. To encompass the  $C_{oss}$  and the  $R_{s}$ information of a device, the concept of  $C_{oss}$  loss tangent,  $tan(\delta)$ , is introduced as a unified selection and benchmarking criterion; where  $R_s$  and the capacitive reactance,  $X_c$  =  $1/j\omega C_{\rm oss}^{\rm eff}$ , respectively, represent the real and imaginary parts of a complex impedance with an angle  $\delta$ . The loss tangent normalizes  $E_{\text{diss}}$  with respect to  $E_{\text{oss}}$  (stored energy in  $C_{\text{oss}}$  for a given drain-source voltage), enabling comparison of device families solely based on their loss tangent values, regardless of on-state resistance  $(R_{DS(on)})$  variations in devices within a family. Benchmarking of devices based on the proposed concept provides important information for the circuit designer to choose the best device that minimizes the overall losses. Moreover, the presented results can be insightful for the device designer to improve the high-frequency behaviour of their devices.

## II. $R_{\rm S}$ and the $C_{ m OSS}$ Loss Tangent

The output capacitance model in Fig. 1(a) is valid for any type of excitation on the device's drain-source voltage. The

2

| Family | Voltage | Technology    | Manufacturer |

|--------|---------|---------------|--------------|

| A      | 500     | Si (planar)   | Vishay       |

| В      | 650     | GaN           | GaN Systems  |

| C      | 700     | SiC           | Microsemi    |

| D      | 650     | SiC           | Rohm         |

| E      | 650     | SiC (Cascode) | United SiC   |

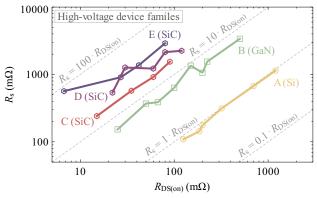

Fig. 2. Variation of  $R_s$  (at  $v_{DS}=40$  V and  $v_{GS}=0$  V) with  $R_{DS(on)}$  for 500-700 V normally-off device families. The excitation signal has fMHz and a peak of 100 mV.

resulting  $E_{diss}$  value depends on the type and magnitude of the excitation signal. Fig. 1(b) shows the dependence of  $R_{\rm s}$ with the frequency of excitation, f, for two WBG devices. Fig. 1(c) and Fig. 1(d) highlight the nonlinear variation of  $C_{\rm oss}$ and  $C_{\mathrm{oss}}^{\mathrm{eff}}$  with  $v_{\mathrm{DS}}$  for the same two devices. They also show that  $R_s$  is not a strong function of voltage, and therefore, can be approximated as a constant for a given f [12]. A Keysight E4990A impedance analyzer with a 16047E test fixture (50 MHz) was used in this work for all impedance measurements.

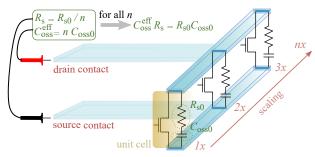

To study the behaviour of  $R_s$  within commercial devices, Fig. 2 plots  $R_s$  vs  $R_{DS(on)}$ , for five high-voltage device families A to E (tabulated in Table I) at 10 MHz. All families generally show a linear relation between  $R_s$  and  $R_{DS(on)}$ . SiC families show a higher  $R_{\rm s}/R_{\rm DS(on)}$  ratio (> 10), while the Si family A shows the lowest ratio ( $\approx 1$ ). These results suggest that  $R_{\rm s}$ is fundamentally related to the sizing of a device in a linear manner: i.e.  $R_{\rm s} \propto R_{\rm DS(on)} \propto 1/I_{\rm D(rated)}$ , where  $I_{\rm D(rated)}$  is the device current rating. To investigate the implications further, the sizing<sup>1</sup> of a device family is modeled by a distribution of unit cells as depicted in Fig. 3. Each cell has a current rating of  $I_{\rm D0}$  and an output capacitance with the parameters  $R_{\rm s0}$  and effective capacitance  $C_{\mbox{\scriptsize oss0}}.$  A device sized with n number of cells has  $I_{\text{D(rated)}} = n \cdot I_{\text{D0}}$ . This entails that the product  $C_{\text{oss}}^{\text{eff}} \cdot R_{\text{s}}$ is independent of the sizing of the device (illustrated in Fig. 3):

$$C_{\text{oss}}^{\text{eff}} \cdot R_{\text{s}} = C_{\text{oss}0} \cdot R_{\text{s}0}. \tag{1}$$

Using the result

$$R_{\rm s} \propto R_{\rm DS(on)}$$

and (1),

$$R_{\rm s} \propto R_{\rm DS(on)} \propto \frac{1}{C_{\rm oss}^{\rm eff}} \propto \frac{1}{I_{\rm D(rated)}}. \tag{2}$$

The product  $C_{\text{oss0}} \cdot R_{\text{s0}}$  is a unique feature of a device structure/family that is independent of its current rating. To infer its relation to  $E_{diss}$ ,  $R_{s}$  is considered as a perturbation element,

<sup>1</sup>Sizing is also commonly referred to as the scaling-up of a device in deviceengineer terminology. Increasing the device width (e.g. scaling it up) increases the current rating, and equivalently, decreases its on-state resistance.

Fig. 3. Sizing of a large device of a current rating  $I_{D(rated)}$  can be imagined by a distribution of n unit cells, where each has a current rating of  $I_{D0}$ .

which is valid as long as the inequality  $\omega C_{\text{oss}}^{\text{eff}} R_{\text{s}} \ll 1$  is satisfied. Therefore, the voltage across  $R_s$  can be neglected and the current through it can be approximated as  $C_{\text{oss}} \cdot dv_{\text{DS}}/dt$ . Then,  $E_{\rm diss}$  for a large-signal excitation on  $v_{\rm DS}$  (from 0 to  $V_{\rm p}$ ) is given by (3), where k = 4 for triangular voltages [12].

$$E_{\rm diss} = k f V_{\rm p}^2 C_{\rm oss}^{\rm eff}^2 R_{\rm s} \tag{3}$$

To develop a unified loss-parameter that includes frequency dependence, a  $C_{oss}$  loss tangent is defined in (4).

$$\tan(\delta) = \frac{R_{\rm s}}{|X_{\rm c}|} = \frac{R_{\rm s}}{1/(\omega C_{\rm oss}^{\rm eff})} = \omega C_{\rm oss}^{\rm eff} R_{\rm s} \tag{4}$$

By using (3) and (4), a normalized  $E_{\rm diss}$  is defined with respect

to an effective stored energy

$$(\frac{1}{2}C_{\text{oss}}^{\text{eff}} \cdot V_{\text{p}}^2)$$

of device  $C_{\text{oss}}$ :

$$\overline{E_{\text{diss}}} = \frac{E_{\text{diss}}}{\frac{1}{2}C_{\text{oss}}^{\text{eff}} \cdot V_{\text{p}}^2} = \frac{k}{\pi} \tan(\delta). \tag{5}$$

We arrive at the following important conclusions:

- 1)  $\tan(\delta)$  normalizes  $E_{\rm diss}$  and encompasses  $C_{\rm oss}^{\rm eff},\,R_{\rm s}$  and fin a single parameter for loss evaluation. In other words,  $tan(\delta)$  is a measure of  $E_{diss}$  for a unit stored energy.

- 2) Equations (1) and (4) show that  $tan(\delta)$  is constant for a given family and is independent of current rating. Also, (5) shows that scaling up increases (as  $C_{oss}^{eff}$  increases) the absolute  $E_{\rm diss}$  within a device family.

- 3) For different device families, the family with the lowest  $tan(\delta)$  offers the lowest  $E_{diss}$  for a given stored energy (or equivalently for a given current capability).

It should be noted that the parameter k is a factor that depends upon the large-signal excitation and is independent of the device structure.<sup>2</sup> On the other hand,  $tan(\delta)$  is a device specific parameter independent of k. Thus  $tan(\delta)$  allows to compare the soft-switching performance of different device families, independently of the excitation signal.

## III. RESULTS

In this section, the proposed concepts are experimentally evaluated on commercial devices, providing further insights on the implications of  $R_s$  and  $tan(\delta)$ . The loss tangents and the related percentage losses (with respect to an effective stored energy  $\frac{1}{2}C_{\text{oss}}^{\text{eff}} \cdot V_{\text{p}}^2$ ) with the excitation frequency (up to 50 MHz) are plotted in Fig. 4(a) for different device structures: Si, SiC, and GaN power devices with similar current ratings on the high-voltage range (500-900 V) are considered. Note

<sup>2</sup>Since  $v_{GS} = 0$  V, the large-signal excitation on the device, and hence the voltage-transient times of  $v_{DS}$ , is determined by the external load and  $C_o$ .

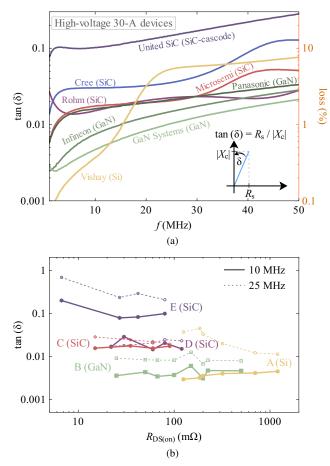

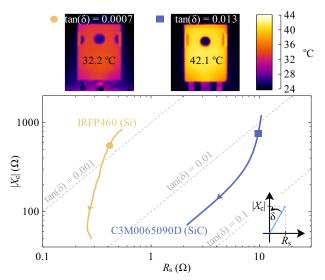

Fig. 4. (a) The variation of  $\tan(\delta)$  vs f for 30-A high-voltage (500-900 V) devices from different manufacturers. The percentage losses are also given with respect to their effective stored energies, where the factor k/pi from (5) is not considered. A sinusoidal excitation signal with a peak of 100 mV was employed. (b) The variation of  $\tan(\delta)$  with  $R_{\rm DS(on)}$  for the device families A-E (tabulated in Table I), measured at f=10 MHz (solid lines) and f=25 MHz (dotted lines), with  $C_{\rm oss}^{\rm eff}$  values estimated at  $v_{\rm DS}=400$  V.

that, since  $R_s$  is a frequency-dependent parameter [12], as illustrated in the example-cases shown in Fig. 1(b), the value of  $tan(\delta)$  changes non-linearly with f. For frequencies below 15 MHz, the Si device (planar MOSFET) and the GaN devices from GaN Systems and Infineon show  $tan(\delta)$  values well below 0.01, with less than 1 % of losses. However, above 15 MHz, GaN devices show the lowest  $tan(\delta)$  values, keeping around 3 % of losses. The lower rate of increase of  $tan(\delta)$  towards the large frequencies of the GaN devices is attributed to the general decrease of  $R_s$  with frequency [12]. The significant increase of  $tan(\delta)$  in the Si device up to 25 MHz, which leads up to  $\approx 8$  % of losses, is due to the large increase of its  $R_s$  in this frequency region. The SiC devices show negligible variation in their  $tan(\delta)$  values between 5 to 30 MHz. This agrees well with the observations in [2], where the measured  $E_{\rm diss}$  for the tested SiC devices show little change within the considered frequency range. All the SiC devices generally show higher losses for the whole frequency range.

Fig. 4(b) plots  $\tan(\delta)$  value with  $R_{\rm DS(on)}$  for different devices within a family at 10 MHz (solid lines) and at 25 MHz (dotted lines): five different families from A to E were considered (see Table I). For all the device families it is clearly observed that  $\tan(\delta)$  stays fairly constant for 10 MHz, irrespective of the

Fig. 5. Temperature rise of two devices that have approximately equal  $E_{\rm oss}$  values ( $\approx 10~\mu{\rm J}$ ) at 400 V, but different  $\tan(\delta)$  values. The devices were excited using the Sawyer-Tower circuit with a  $v_{\rm DS}$  swing of 400 V and  $f=900~{\rm kHz}$ . Note: the arrows in  $|X_{\rm c}|$  curves show the direction of increasing frequency.

value of  $R_{\rm DS(on)}$ , hence with the device current rating. This is in agreement with (2), and is expected based on the linear behaviour observed between  $R_{\rm s}$  and  $R_{\rm DS(on)}$  at 10 MHz in Fig. 2. A similar trend can be seen at 25 MHz, except for the Si family that shows a deviated behaviour with much higher  $\tan(\delta)$  values at lower  $R_{\rm DS(on)}$  values. The families A (Si) and B (GaN) offer best performance at 10 MHz, with  $\tan(\delta) \approx 0.005$ ; however, the GaN family B offers much lower  $R_{\rm DS(on)}$ , allowing same level of soft-switching performance at much higher current ratings. The GaN device family outperforms all the families at 25 MHz with the lowest  $\tan(\delta)$ .

Since it can be assumed that  $E_{\rm oss} \propto C_{\rm oss}^{\rm eff},$  and based on (5), the device family with lowest  $tan(\delta)$  should be selected as the preferred choice to minimize  $E_{\rm diss}$  for a given  $E_{\rm oss}$ . To corroborate this experimentally, two high-voltage Si and SiC devices were excited with the Sawyer-Tower circuit at a peak voltage of 400 V and a frequency of 900 kHz. The devices have similar  $E_{oss}$  values (around 10  $\mu J$ ) and the same hardware-package (TO-247); also similar environmental conditions were maintained during the test. Fig. 5 shows the impedance-plane measurements of the two devices whose  $|X_c|$ values lie in the same range, indicating that  $E_{oss}$  values are in close range. The steady-sate thermal images of the two devices are also shown in Fig. 5. The SiC device exhibits much higher power dissipation compared to the Si device. This is due to its much larger  $tan(\delta)$  value ( $\approx 0.013$ ) which is more than an order of magnitude larger compared to the Si device.

The loss-tangent method is valid for frequency-dependent energy losses related to  $C_{\rm o}$ , which can be characterized by the small-signal  $R_{\rm s}$ . This is the case observed in most WBG devices [12]. For such devices, the large-signal  $C_{\rm o}$  loss is solely determined by  $\tan(\delta)$ . On the other hand, the frequency-independent energy losses [12], which can be observed mostly in Si-SJ devices, should be estimated using large-signal measurement methods, like the Sawyer-Tower method [8]. Since these losses are observed at much lower frequencies, such as

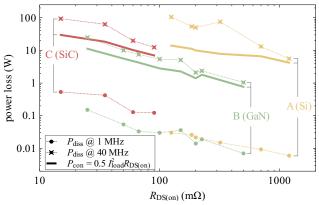

Fig. 6. Comparison of power loss levels with  $R_{\rm DS(on)}$  for three device families, where yellow, green and red colors correspond to the device families A-C (tabulated in Table I), respectively. The solid lines show the maximum possible conduction loss ( $P_{\rm con}$ ) for a given family for 50 % of rated current. Soft-switching power loss ( $P_{\rm diss}$ ) values of each considered device (for a  $V_{\rm p}$  of 400 V) are shown at 1 MHz (dot symbol) and 40 MHz (star symbol).

10-50 kHz [7], at which the value of  $\tan(\delta)$  is negligible, the extracted frequency-independent loss is a good measure of the  $C_0$  losses. If such a device has a frequency-dependent energy loss component, then one can simply add the frequency-independent component to the losses predicted by  $\tan(\delta)$ , to calculate the total loss. However, the frequency-dependent component becomes dominant, and surpasses the frequency-independent portion at larger frequencies.

### IV. DISCUSSION

In this subsection the applicability of the proposed concepts in the selection of devices for high-frequency soft-switching applications is discussed. The conduction power loss ( $P_{\rm con}$ ) and soft-switching power loss ( $P_{\rm diss}$ ) of a device can be expressed as given in (6) and (7), respectively.  $P_{\rm con}$  is evaluated for a 50% duty cycle, where  $I_{\rm load}$  is defined as a sinusoidal RMS current that is equal to 50% of device's rated current.

$$P_{\text{con}} = 0.5 \, \overline{I}_{\text{load}}^2 R_{\text{DS(on)}} \tag{6}$$

$$P_{\rm diss} = f \cdot E_{\rm diss} = f \cdot \frac{k}{\pi} \tan(\delta) \cdot \frac{1}{2} C_{\rm oss}^{\rm eff} V_{\rm p}^2 \tag{7}$$

To minimize the total losses in a soft-switching device, the total loss  $P_{\rm con}$  +  $P_{\rm diss}$  should be minimized. In order to provide a perspective to this requirement, the relative distributions of  $P_{\rm con}$  and  $P_{\rm diss}$  of the commercial device families A-C are plotted in Fig. 6. The solid lines show the maximum possible  $P_{\rm con}$  for a given family. The  $P_{\rm diss}$  values (at  $V_{\rm p}=400~{\rm V}$ ) for all the considered devices are shown at two frequencies, 1 MHz (dots) and 40 MHz (stars). A general guide for the selection of devices for soft-switching applications is given below.

At lower frequencies (typically below 1 MHz),  $P_{\rm con}$  dominates the losses, thus one needs to minimize the losses by selecting the device with lowest  $R_{\rm DS(on)}$ . At high frequencies, which generally occurs above 5-10 MHz,  $P_{\rm diss}$  dominates the losses, and therefore, should be minimized. This can be achieved in two ways based on the design problem.

1) On the one hand, if the selection is within a given family, the device with lowest  $E_{\rm oss}$  (or  $C_{\rm oss}^{\rm eff}$ ) should be selected. This is because  $\tan(\delta)$  is fixed for a family and losses scale with  $C_{\rm oss}^{\rm eff}$ . Based on (2), this means selecting the

- device with the highest  $R_{\rm DS(on)}$ , that is in fact, contrary to the conventional belief. This is clearly observed in Fig. 6, where all families tend to show lower  $P_{\rm diss}$  with higher  $R_{\rm DS(on)}$ .

- 2) On the other hand, if the  $E_{\rm oss}$  value is given, similar to the case study in Fig. 5, the device with the lowest  $\tan(\delta)$  value should be selected.

Fig. 6 also highlights some important aspects of the selected commercial device families. The Si and the GaN family offer lower  $P_{\text{diss}}$  values (< 100 mW) at 1 MHz, while at 40 MHz, the GaN family (B) offers the lowest losses (< 10 W). At veryhigh frequencies, such as 40 MHz, the soft-switching losses dominate in comparison to conduction losses and results in significant power losses. It should be emphasized that, as the conduction losses could be well below their maximum possible value for a certain application (i.e. much below the solid lines in Fig. 6), optimization of  $P_{\text{diss}}$  in the range of tens of MHz is extremely important. The proposed concepts in this work provide the essential insights on the subject. We recommend that device manufacturers consider the loss tangent of the output capacitance as an important figure of merit and provide the related characteristic curves with the excitation frequency in the device data sheets. Provision of a comparison of the loss tangents for complete families would further facilitate the device selection process for the power electronic designer.

#### V. CONCLUSIONS

The concept of  $C_{\rm oss}$  loss tangent was introduced as a powerful measure of output-capacitance-related soft-switching losses. It was shown, that for a given device family, the loss tangent is a fixed value independent of current rating. This allows comparison of device families solely based on their loss tangent values, regardless of their on-state resistance values. Based on the developed concept, commercially available high-voltage wide-band-gap and planar-Si device structures were benchmarked for their loss tangent over a wide frequency range. The results show that for frequencies above 10 MHz, the GaN devices show significant performance benefits compared to Si and SiC devices. Based on the proposed concept, important guidelines for the selection of devices for highfrequency applications were presented. This work provides a method to properly select transistors for high-frequency softswitching converter designs.

# REFERENCES

- [1] X. Li, X. Li, P. Liu, S. Guo, L. Zhang, A. Q. Huang, X. Deng, and B. Zhang, "Achieving Zero Switching Loss in Silicon Carbide MOSFET," *IEEE Transactions on Power Electronics*, vol. 34, no. 12, pp. 12193–12199, Dec. 2019.

- [2] G. Zulauf, Z. Tong, J. D. Plummer, and J. M. Rivas-Davila, "Active Power Device Selection in High- and Very-High-Frequency Power Converters," *IEEE Transactions on Power Electronics*, vol. 34, no. 7, pp. 6818–6833, Jul. 2019.

- [3] M. D. Seeman, "GaN Devices in Resonant LLC Converters: System-level considerations," *IEEE Power Electronics Magazine*, vol. 2, no. 1, pp. 36–41, Mar. 2015.

- [4] M. H. Rashid, Ed., *Power Electronics Handbook: Devices, Circuits, and Applications Handbook*, 3rd ed. Burlington, MA: Elsevier, 2011.

- [5] J. B. Fedison, M. Fornage, M. J. Harrison, and D. R. Zimmanck, "Coss related energy loss in power MOSFETs used in zero-voltage-switched applications," in 2014 IEEE Applied Power Electronics Conference and Exposition - APEC 2014, Mar. 2014, pp. 150–156.

- [6] J. Roig and F. Bauwens, "Origin of Anomalous Coss Hysteresis in Resonant Converters With Superjunction FETs," *IEEE Transactions on Electron Devices*, vol. 62, no. 9, pp. 3092–3094, Sep. 2015.

- [7] J. B. Fedison and M. J. Harrison, "COSS hysteresis in advanced superjunction MOSFETs," in 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Mar. 2016, pp. 247–252.

- [8] G. Zulauf, S. Park, W. Liang, K. Surakitbovorn, and J. M. R. Davila, "Coss Losses in 600 V GaN Power Semiconductors in Soft-Switched, High- and Very-High-Frequency Power Converters," *IEEE Transactions on Power Electronics*, pp. 1–1, 2018.

- [9] M. S. Nikoo, A. Jafari, N. Perera, and E. Matioli, "Measurement of Large-Signal Coss and Coss Losses of Transistors Based on Nonlinear Resonance," *IEEE Transactions on Power Electronics*, pp. 1–1, 2019.

- [10] D. Bura, T. Plum, J. Baringhaus, and R. W. D. Doncker, "Hysteresis Losses in the Output Capacitance of Wide Bandgap and Superjunction Transistors," in 2018 20th European Conference on Power Electronics and Applications (EPE'18 ECCE Europe), Sep. 2018, pp. P.1–P.9.

- [11] M. Guacci, M. Heller, D. Neumayr, D. Bortis, J. W. Kolar, G. Deboy, C. Ostermaier, and O. Häberlen, "On the Origin of the Coss -Losses in Soft-Switching GaN-on-Si Power HEMTs," *IEEE Journal of Emerging* and Selected Topics in Power Electronics, vol. 7, no. 2, pp. 679–694, Jun. 2019.

- [12] M. Samizadeh Nikoo, A. Jafari, N. Perera, and E. Matioli, "New Insights on Output Capacitance Losses in Wide-Band-Gap Transistors," *IEEE Transactions on Power Electronics*, pp. 1–1, 2019.