# Material and Electrical study of HfO2-Based Resistive Random Access Memories (ReRAMs)

Thèse Nº 7412

Présentée le 22 novembre 2019

à la Faculté des sciences et techniques de l'ingénieur Laboratoire de systèmes microélectroniques Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

## Behnoush ATTARIMASHALKOUBEH

Acceptée sur proposition du jury

Prof. G. De Micheli, président du jury Prof. Y. Leblebici, Prof. P. Muralt, directeurs de thèse Dr M. Shayganpoor, rapporteur Dr N. Raeishosseini, rapporteuse Prof. C. Dehollain, rapporteuse

As you start to walk out on the way, the way appears. — Rumi

# Acknowledgements

In the beginning, I would like to express my gratitude to my thesis advisor, *Prof. Yusuf Leblebici* for giving me the opportunity of working in his laboratory, his continuous support, and positive attitude. He always encouraged me to pursue and implement new ideas despite the high cost of fabrication. I am also grateful to my co-advisor *Prof. Paul Muralt* for all his support, useful and inspiring discussions we had during my Ph.D., especially the last few months. Besides my advisors, I would like to thank the rest of my thesis committee: *Prof. Giovanni De Micheli* and *Prof. Catherine Dehollain* from EPFL; *Dr. Mehrdad Shayganpoor* from TDK electronics Austria, and *Dr. Niloufar Raeishosseini* from Imperial College London, for their insightful comments and encouragement.

My sincere thanks also go to *Dr. Mounir Mensi* for his patience, immense knowledge of materials and all scientific discussions we had.

Moreover, I wish to thank *Igor Krawczuk* for developing the pulse measurement system and *Yigit Demirag* for his work on the modeling of the devices.

As the fabrication parts of my work have been done in CMI cleanroom of EPFL, I would like to thanks all CMI staffs and *Philippe Fluckiger* for their continuous support. I would like to particularly thank *Julien Dorsaz, Guy Clerc, Rémy Juttin, Cyrille Hibert, Joffrey Pernollet* and *Zdnek Benes* for their valuable training sessions, and positive attitudes.

I have been lucky to be lab members with wonderful LSM members. Special thanks to *Ayça Akkaya, Firat çelik, Dr. Şeniz Esra Küçük*, and *Bilal Demir* for all those funny, interesting scientific, historical, and cultural discussions we had over the past years. Many thanks to *Mustafa Kiliç, Duygu Kostak, Dr. Can Baltaci*, and *Jonathan Narinx* for their friendship and support during my assistantship duties. I would like to expand my gratitude to the LSM staff, *Prof. Alain Vachoux, Prof. Alexandre Schmid* for their professional support, *Melinda Mischler* and *Patricia Volanthen* for administrative help.

After all, leaving far from family was not easy without having great friends by my side to lift my spirits when felt overwhelmed during my Ph.D. time. I would like to thank my friend *Halima Najibi* for the bonding we share from my very first day in LSM, for all those real laughs, funny moments in the gym and the girl nights we have had. Many thanks to *Saeid Rad, Saleh Salimi* and *Azade Yazdanyar* for all the talks, coffee breaks, lunches, and true moments of friendship we shared in the last four and half years together. Their true friendship made every single lunch, day, and weekend fun; and their support never lessens by time.

Many thanks to my second family, *Dominique*, *Jean-Pierre*, and *Audrey*, for their support and giving me a taste of home thousands of kilometers away from my homeland.

#### Acknowledgements

My deepest gratitude goes to my lovely parents, *Forouzandeh* and *Abbas*, for what they have done for their children. My father inspired me in the first place to enter an engineering school and managed to constantly remind me of the importance of education in empowering young women. I truly appreciate his dedication in our education, through literature and science from our early ages. And my mother, who is always there to protect and cherish our lives with her endless love, patience, and support.

My siblings, who are the best one can ask for. My brother *Babak* who from his childhood always looked out for me, motivated and even pushed me when motivating was not enough, even if it means setting a password on the TV during my high school exam time to force me to study! My sister, *Bahareh* and her calming, loving character; our daily long phone calls made me feel like still living together and sharing sister talks till 3 am together. Thank you Bahareh, for being my best friend and for all those nights you slept with the lights on in our bedroom when I studied late at night. And my thanks to my amazing brother-in-law *Farshid*, who joined later to our family and became my second brother, bonded not by blood but with love.

My siblings, who are the best one can ask for. My brother *Babak* who from his childhood always looked out for me, motivated and when it was needed pushed me even if it means setting a password on the TV during my exam time in the high school to force me to study! My sister, *Bahareh* and her calming, loving character, made me feel not far from home, thank you Bahareh for being my best friend and all those nights you slept with the lights on in our bedroom when I studied late at night. My amazing brother-in-law *Farshid*, who joined later to our family and became my second brother, not by blood but by love.

Last but not least, my dear *Jérémy*, my best friend, love, and husband. Your endless love, kindness, support, and understanding helped me to get through the hard days of my PhD life. Thank you for your magical super-power in bringing peace and disappearing the problems, for all those long hours you spent in my office over the weekends while I was working. you have truly proved "L'amour n'est pas seulement un sentiment, il est un art aussi. –Honoré de Balzac". *Thank you Jérémy joon*.

Lausanne, 20 September 2019

Behnoush Attari

# Abstract

Resistive Random Access Memories (ReRAMs) have been researched intensively in the last past decades as a promising alternatives technology for the next generation non-volatile memory (NVM) devices. ReRAM's excellent performance with high switching speed, excellent scalability, and low power consumption, together with accessible fabrication techniques have raised increasing interests and encourages further studies.

A ReRAM device in its most basic structure consists of a thin layer of a transition metal oxide (TMO) sandwiched between two metal layers (Top and Bottom Electrodes). ReRAMs could be categorized into different groups regarding the implemented materials and their performance. The concept of switching mechanism is straightforward; the as-fabricated devices appeared to be highly resistive (HRS); when the top electrode (TE) is biased, the resistance state of the devices switched to the lower resistance level (LRS) in an operation called SET. This process is commonly reversible through the application of proper negative external stimuli, which can change back to the high resistance state of the device from LRS to HRS.

Oxygen vacancies are recognized as the main elements controlling the device performance. During the set process, the oxygen vacancies rearrange to form conductive bridges between the TE and bottom electrode (BE). Further application of negative biases can partially/ fully dissolve the conductive filaments and led to HRS by disconnecting the two metallic electrodes from one the other.

The switching mechanism is due to relocation and movement of oxygen vacancies, but the stochastic nature of the formation of filament also makes it hard to control this phenomenon precisely. As a result, the reported variation issue in the key switching parameters of ReRAMs, lessens the reliability of this technology and hinders its commercialization.

To suppress the variability hurdle in ReRAMs, it is crucial to have a better understanding of the switching mechanism. Hence, the interaction between deposited materials in the as-fabricated devices and during electrical measurements under external stimuli needs to be intensely studied to obtain an in-depth knowledge of the behavior of the oxygen vacancies.

The first purpose of this research is to overcome the variation in the key switching parameters of stand-alone ReRAMs to be used in cross-point structures. Among various TMO materials, Hafnium oxide (HfO<sub>2</sub>) is considered as a promising oxide due to its excellent performance results (i.e. : high switching speed, endurance, on/off ratio) and accessibility of deposition tools.

In this work, we implemented two main approaches to improve the reliability and uniformity of HfO<sub>2</sub>-based ReRAMs; the structural engineering, and post-fabrication thermal treatment

#### Acknowledgements

and studied the effect of each method on the performance of  $HfO_2$ -based fabricated ReRAMs. ReRAMs due to their simple structure can be implemented to the cross-point Configuration. The simple but yet effective cross-point design, allows an effective cell area of  $4F^2$  in 2D, while the feasibility of achieving 3D configuration by stacking multiple 2D layers, brings down the cell area to  $4F^2/n$  and leads to the remarkably high integration density. However, the sneak current through unwanted neighbor cells significantly decreases the system efficiency, deteriorates the read margin, and limits the maximum size of a cross-point array. To overcome the sneak path issue, different strategies could be implemented; among all, serially connecting each memory element to an additional selection device in a 1S1R con

figuration is an active way to introduce selectivity to the cross-point arrays.

In the second part of this work, we introduced a novel one-selector one-resistor (1S1R) configuration, which eliminates the need for the physical wiring and provides valuable information on isolated selector/resistor and the integrated 1S1R.

# Résumé

Les Resistive Random Access Memories (ReRAM) ont fait l'objet de nombreuses recherches au cours des dernières décennies en tant qu'alternative technologique prometteuse pour la prochaine génération de dispositifs à mémoire non-volatile. Les excellentes propriétés des ReRAMs telles que la vitesse de commutation élevée, la scalabilité, la faible consommation énergétique ainsi que les techniques de fabrication accessibles ont suscité un intérêt croissant et encourage à de nouvelles recherches.

Un dispositif ReRAM dans sa structure la plus simple consiste en une fine couche d'oxyde de métal de transition (TMO) intercalée entre deux couches métalliques (électrodes du haut et du bas). Les ReRAMs peuvent être catégorisées en différents groupes en fonction des matériaux mis en œuvre et de leur performance. Le concept du mécanisme de commutation est simple; les dispositifs tels que fabriqués apparaissent comme étant hautement résistifs (HRS); lorsque l'électrode supérieure (TE) est polarisée, l'état de résistance des dispositifs passe au niveau de résistance inférieur (LRS) dans une opération appelée SET. Ce processus est généralement réversible par l'application de stimuli externes négatifs appropriés, qui peuvent changer l'état de résistance du dispositif de LRS à HRS.

Les vides d'oxygène sont reconnus comme les principaux éléments contrôlant les performances du dispositif. Pendant le processus de réglage, les vides d'oxygène se réorganisent pour former des ponts conducteurs entre les électrodes supérieure et inférieure qui, en appliquant des tensions négatives supplémentaires, peuvent les dissoudre partiellement ou totalement et conduire à un état hautement résistif (HRS) en séparant les deux électrodes métalliques l'une de l'autre.

L'excellente performance des ReRAMs est rendue possible grâce à leur mécanisme de commutation qui est basé sur le déplacement et le mouvement des vides d'oxygène à l'échelle nanométrique. Cependant, la nature stochastique de la formation du filament rend difficile le contrôle précis de ce phénomène. Par conséquent, les problèmes de variations signalés dans les principaux paramètres de commutation des ReRAMs réduisent la fiabilité de cette technologie et entravent sa commercialisation. Pour faire face à cet obstacle, il est crucial de mieux comprendre le mécanisme de commutation. Ainsi, les interactions entre les matériaux déposés dans les dispositifs fabriqués et pendant les mesures électriques sous stimuli externes doivent être intensément étudiées pour obtenir une connaissance approfondie du comportement des vides d'oxygène. Le premier objectif de cette thèse est d'éliminer la variation des principaux paramètres de commutation des ReRAMs autonomes à utiliser dans les structures à points de croisement. Parmi les différents oxydes de métal de transition (TMO), l'oxyde

#### Acknowledgements

d'hafnium (HfO<sub>2</sub>) est considéré comme un oxyde prometteur en raison de ses excellentes performances et de l'accessibilité des outils de déposition.

Dans cette thèse, nous avons mis en œuvre deux approches principales pour améliorer la fiabilité et l'uniformité des ReRAMs à base de HfO<sub>2</sub> : l'ingénierie structurale et le traitement thermique post-fabrication.

Grâce à leur structure simple, les ReRAMs peuvent être implémentés dans les structures à points de croisement. La conception simple mais efficace de cette structure permet d'obtenir une surface efficace de  $4F^2$  en 2D, tandis que la possibilité d'obtenir une configuration 3D en empilant plusieurs couches 2D, ramène la surface à  $4F^2/n$  et conduit à une densité d'intégration remarquablement élevée. Cependant, le courant de fuite à travers les cellules indésirables voisines diminue considérablement l'efficacité du système, détériore la marge de lecture et limite la taille maximale d'un réseau de points de croisement. Pour surmonter le problème du courant de fuite, différentes stratégies pourraient être mises en œuvre. Parmi toutes celles envisagées, relier en série chaque élément de mémoire à un dispositif de sélection supplémentaire dans une configuration 1S1R est un moyen actif d'introduire la sélectivité dans les tableaux à points de croisement.

Dans la deuxième partie de cette thèse, nous avons introduit une nouvelle configuration avec un seul sélecteur et une seule résistance (1S1R), qui élimine le besoin de câblage physique et fournit des informations précieuses pour le sélecteur/résistance isolé et le 1S1R intégré.

# Contents

| Ac | knov    | wledgements                                                                              | v    |

|----|---------|------------------------------------------------------------------------------------------|------|

| Ał | ostra   | ct (English/Français)                                                                    | vii  |

| Li | st of : | figures                                                                                  | xiii |

| Li | st of   | tables x                                                                                 | viii |

| In | trod    | uction                                                                                   | 1    |

| 1  | Intr    | oduction                                                                                 | 1    |

|    | 1.1     | Semiconductor Timeline                                                                   | 1    |

|    | 1.2     | Classification of Semiconductor Transistor-based Memory Technologies                     | 9    |

|    |         | 1.2.1 Volatile Memory                                                                    | 9    |

|    |         | 1.2.2 Non Volatile Memory                                                                | 10   |

|    | 1.3     | Emerging Memory Technologies                                                             | 10   |

| 2  | Res     | istive Random Access Memory (ReRAM)                                                      | 13   |

|    | 2.1     | The structure                                                                            | 14   |

|    | 2.2     | Classification of ReRAMs                                                                 | 14   |

|    |         | 2.2.1 Classification based on the Type of Resistive Switching                            | 14   |

|    |         | 2.2.2 Classification based on the Mechanism of Resistive Switching                       | 15   |

|    | 2.3     | Mechanism of Resistive Switching in ReRAMs                                               | 16   |

|    | 2.4     | The Choice of Material and the Device Properties                                         | 17   |

| 3  | Cro     | ss-Point Array                                                                           | 19   |

|    | 3.1     | Introduction                                                                             | 19   |

|    | 3.2     | Sneak Path Current Issue                                                                 | 19   |

|    | 3.3     | One selector-One resistor (1S1R)                                                         | 22   |

| 4  |         | ect of Hf Metal Layer on the switching characteristics of HfO $_x$ -based resistive Ran- | -    |

|    |         | n Access Memory                                                                          | 25   |

|    | 4.1     | Introduction                                                                             | 26   |

|    | 4.2     | Materials and Methods                                                                    | 27   |

|    |         | 4.2.1 Fabrication Process 3low                                                           | 27   |

### Contents

|   |                                            | 4.2.2 Electrical Measurement                                                                   | 28     |

|---|--------------------------------------------|------------------------------------------------------------------------------------------------|--------|

|   | 4.3                                        | Results and Discussion                                                                         | 28     |

|   | 4.4                                        | Conclusion                                                                                     | 30     |

| 5 | Effe                                       | ect of metal buffer layer and thermal annealing on $HfO_x$ -based ReRAMs                       | 33     |

|   | 5.1                                        | Introduction                                                                                   | 34     |

|   | 5.2                                        | ReRAM Fabrication Process                                                                      | 35     |

|   | 5.3                                        | Fabrication Process Optimization                                                               | 36     |

|   |                                            | 5.3.1 Metal Buffer Effect                                                                      | 36     |

|   |                                            | 5.3.2 Post Metallization                                                                       | 37     |

|   | 5.4                                        | Device Characterization                                                                        | 38     |

|   | 5.5                                        | Conclusion                                                                                     | 42     |

| 6 | Evo                                        | lution of oxygen vacancies under electrical characterization for $HfO_x$ -based ReR            | AMs 43 |

|   | 6.1                                        | Introduction                                                                                   | 44     |

|   | 6.2                                        | Materials and Methods                                                                          | 45     |

|   |                                            | 6.2.1 Fabrication Process Flow                                                                 | 45     |

|   |                                            | 6.2.2 Electrical Setup and Measurement                                                         | 46     |

|   | 6.3                                        | Results and Discussions                                                                        | 47     |

|   |                                            | 6.3.1 Electrical Setup Engineering                                                             | 49     |

|   | 6.4                                        | Conclusion                                                                                     | 52     |

| 7 |                                            | ationship between the Gibbs free energy of oxidation with the resistive switching              | 5      |

|   | pro                                        | perties of bi-oxides memristors                                                                | 53     |

|   | 7.1                                        | Introduction                                                                                   | 54     |

|   | 7.2 Fabrication and electrical measurement |                                                                                                | 55     |

|   | 7.3                                        | Result and Discussion                                                                          | 56     |

|   | 7.4                                        | Conclusion                                                                                     | 58     |

| 8 | In-c                                       | lepth Structural and Electrical Characteristics Study of HfO <sub>X</sub> -based resistive Rar | 1-     |

|   | don                                        | n Access Memories (ReRAMs)                                                                     | 61     |

|   | 8.1                                        | Introduction                                                                                   | 62     |

|   | 8.2                                        | Method and materials                                                                           | 63     |

|   |                                            | 8.2.1 Process Flow and Fabrication                                                             | 63     |

|   |                                            | 8.2.2 Electrical Setup and Measurement                                                         | 65     |

|   | 8.3                                        | Result and discussion                                                                          | 65     |

|   |                                            | 8.3.1 HfO <sub>2</sub> -alone ReRAMs                                                           | 65     |

|   |                                            | 8.3.2 Bi-Oxide $HfO_2$ -based ReRAMs                                                           | 65     |

|   |                                            | 8.3.3 Role of Buffer Layer                                                                     | 67     |

|   | 8.4                                        | Conclusion                                                                                     | 71     |

#### Contents

| 9  | Nov   | el 3D architecture of 1S1R                                                                 | 73 |

|----|-------|--------------------------------------------------------------------------------------------|----|

|    | 9.1   | Introduction                                                                               | 74 |

|    | 9.2   | The 3D configuration of 1S1R                                                               | 75 |

|    |       | 9.2.1 The Concept                                                                          | 75 |

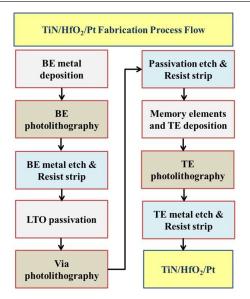

|    |       | 9.2.2 Process Flow and Fabrication                                                         | 77 |

| 10 | Imp   | roving reliability issue of HfO <sub>2</sub> -based memristors by protecting the switching |    |

|    | mat   | erials against buffer layer deposition                                                     | 79 |

|    | 10.1  | Introduction                                                                               | 80 |

|    | 10.2  | Materials and Methods                                                                      | 83 |

|    |       | 10.2.1 Device Fabrication                                                                  | 83 |

|    |       | 10.2.2 Electrical Measurement                                                              | 83 |

|    | 10.3  | Result and Discussion                                                                      | 83 |

|    | 10.4  | Conclusion                                                                                 | 86 |

| A  | Fut   | ıre Work                                                                                   | 87 |

| Bi | bliog | raphy                                                                                      | 96 |

| Cu | ırric | lum Vitae                                                                                  | 97 |

# List of Figures

| 1.1  | An Image of Faraday's experimental researches in electricity                         | 4  |

|------|--------------------------------------------------------------------------------------|----|

| 1.2  | A commercialized crystal detector                                                    | 4  |

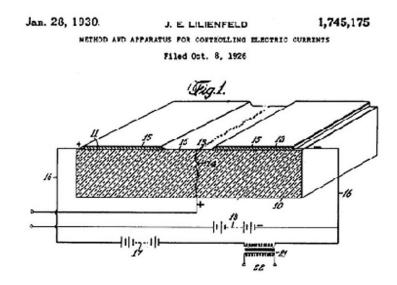

| 1.3  | Lilienfeld's patent illustrating field-effect transistor                             | 5  |

| 1.4  | The first band gap demonstration proposed by Wilson                                  | 5  |

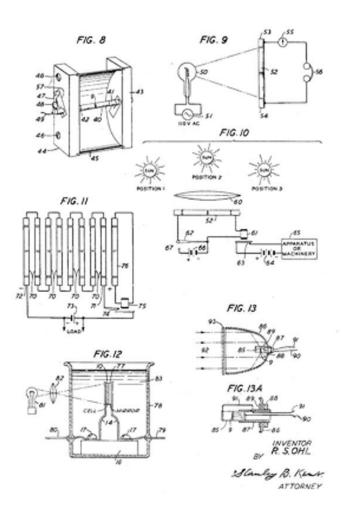

| 1.5  | A page of Ohl's patent field in 1941                                                 | 6  |

| 1.6  | A 1948 image which shows Shockley describing his junction transistor based           |    |

|      | theory                                                                               | 6  |

| 1.7  | The Sonotone hearing aid, the device contains one germanium transistor and           |    |

|      | two tubes                                                                            | 7  |

| 1.8  | RCA 16-transistor MOSFET circuit                                                     | 7  |

| 1.9  | Dr. Moore's Law                                                                      | 8  |

| 1.10 | Dr. Moore's Law, the first and second edition                                        | 8  |

| 1.11 | Schematic demonstration of DRAM and SRAM technologies                                | 9  |

| 1.12 | The emerging memory technology must provide a proper trade-off between               |    |

|      | required properties of industries                                                    | 11 |

| 2.1  | Number of publications per year between 2004 to 2013                                 | 14 |

| 2.2  | Schematic demonstration of a) I-V switching of a unipolar ReRAM, b) MIM              |    |

|      | structure, and c) I-V switching of a bipolar ReRAM                                   | 15 |

| 2.3  | Schematic demonstration for a) A Filamentary ReRAM, and b) An interface-type         |    |

|      | ReRAM                                                                                | 16 |

| 2.4  | Schematic demonstration of the resistive switching process, including the electro-   |    |

|      | forming, set, and resets steps for a simple binary metal-oxide ReRAM device          | 17 |

| 3.1  | a) Illustration of sneak current in a cross-point array with nearly linear RS during |    |

| 5.1  | the read operation, b) circuit schematic of cross-point array                        | 20 |

| 3.2  | Schematic of the cross-point array circuit. V1 and V2 represent the applied          | _0 |

| 0.2  | voltage on the un-selected word and bit lines                                        | 20 |

| 3.3  | Different cell structure, device and circuit characteristics and their impacts on    |    |

|      | system performance                                                                   | 21 |

| 3.4  | Schematic demonstration of 1S1R on different substrate                               | 22 |

| 3.5  | Schematic demonstration of a 1S1R cross-point array                                  | 23 |

|      |                                                                                      |    |

### List of Figures

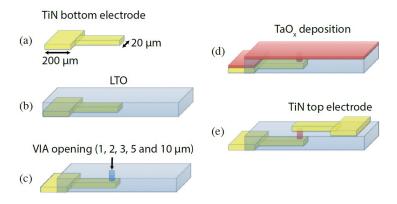

| 4.1 | Schematic demonstration of the process flow used for fabrication of $HfO_x$ -based ReRAMs               | 28 |

|-----|---------------------------------------------------------------------------------------------------------|----|

| 4.2 | A schematic demonstration of a single cell fabrication with the dimension of its                        |    |

|     | parts                                                                                                   | 28 |

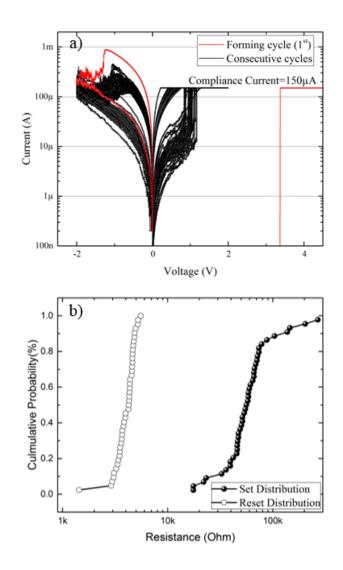

| 4.3 | I-V characteristic for Device 1, b) the HRS and LRS distribution                                        | 3  |

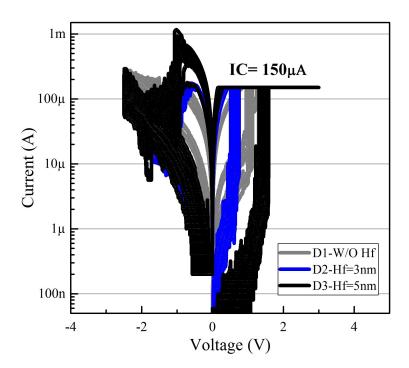

| 4.4 | I-V characteristics the devices D1, D2, and D3 (HfO <sub>x</sub> -alone and HfO <sub>x</sub> with Hf    |    |

|     | buffer layer, after their forming cycles                                                                | 32 |

| 4.5 | Schematic switching mechanism demonstrating the role of Hf as reactive metal                            |    |

|     | in creation of oxygen vacancies.                                                                        | 32 |

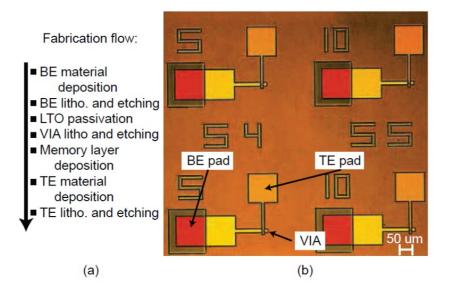

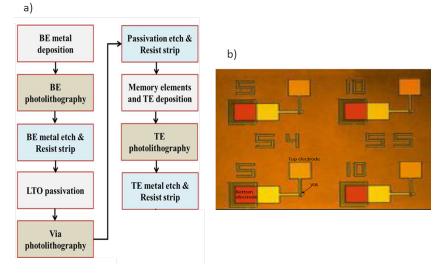

| 5.1 | (a) Schematization of the ReRAM fabrication process flow and (b) device micro-                          |    |

| 0.1 | graph. The device diameters range from 800 nm to 10 $\mu$ m                                             | 3  |

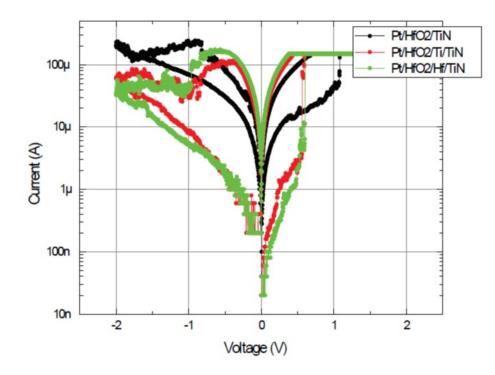

| 5.2 | Influence of different metal buffer layers on the ReRAM electrical character-                           | -  |

|     | istics. The figure shows the test result for $Pt/HfO_x/TiN$ , $Pt/HfO_x/Ti/TiN$ and                     |    |

|     | $Pt/HfO_x/Hf/TiN$ devices                                                                               | 3  |

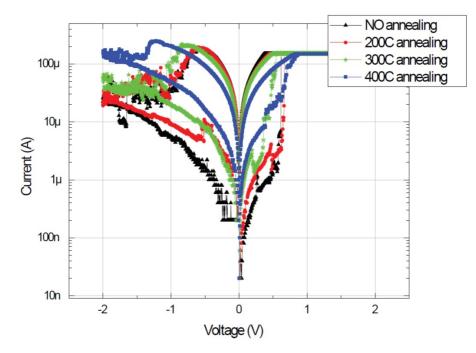

| 5.3 | Effects of thermal annealing at 200° C, 300° C and 400° C on Pt/HfO <sub>x</sub> /Hf/TiN                |    |

|     | ReRAMs                                                                                                  | 3  |

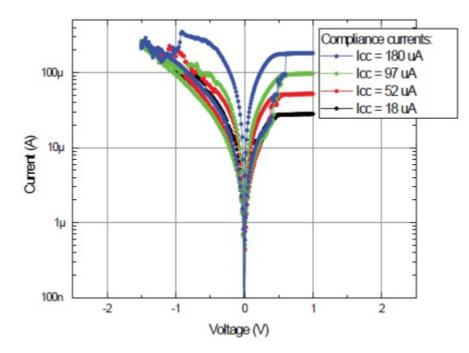

| 5.4 | Different LRS stated obtained by modulating the current compliance for the                              |    |

|     | HfO <sub>x</sub> /Hf/TiN devices at 18 $\mu$ A, 52 $\mu$ A, 97 $\mu$ A and 180 $\mu$ A                  | 3  |

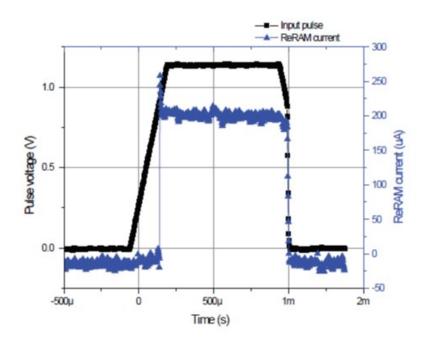

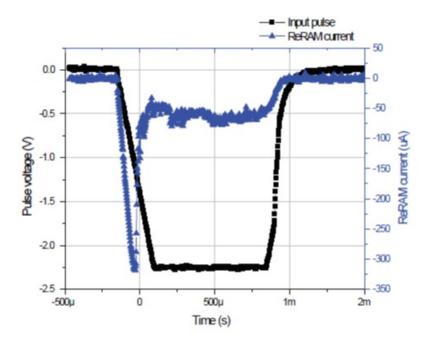

| 5.5 | Electrical behavior $Pt/HfO_x/Hf/TiN$ devices. The input voltage pulses are at 2.25                     |    |

|     | V and 1.15 V with a length of 1 ms. The set current is limited to 210 $\mu$ A                           | 4  |

| 5.6 | Current transient behaviour for $Pt/HfO_x/Hf/TiN$ ReRAM devices. The current                            |    |

|     | is measured from the voltage drop of a series 1 $k\Omega$ resistor. The device set and                  |    |

|     | reset time are 400 ns and a 10 $\mu$ s, respectively. The test conditions are the same                  |    |

|     | as the one used for the voltage pulse test (-2.25V and 1.15V, 1ms, 210 $\mu \rm A)$                     | 4  |

| 6.1 | a)Schamatic summary of the process flow steps, b) Optical picture of the ReRAMs                         |    |

|     | cells before measurement, demonstrating the TEs, BEs and the vias                                       | 45 |

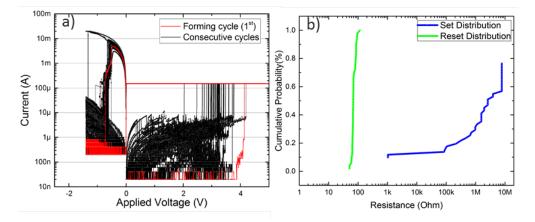

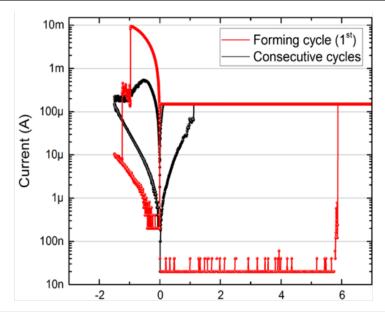

| 6.2 | Device No.1 with Pt(BE)/ HfO <sub>2</sub> (5 nm)/ Pt(TE) structure: a) I-V characteristic for           |    |

|     | first 100 cycles, b)Set and reset distribution                                                          | 4  |

| 6.3 | I-V characteristic for the first 100 cycles of the device No.5 with $Pt(BE) / HfO_2(5)$                 |    |

|     | nm)/TiO <sub>2</sub> (3 nm)/Ti(5 nm)/Pt(TE) structure                                                   | 48 |

| 6.4 | I-V characteristic for the first 100 cycles of the device No.6 with Pt(BE)/ $HfO_2(5)$                  |    |

|     | nm)/TiO <sub>2</sub> (5 nm)/Ti(5 nm)/Pt(TE) structure                                                   | 48 |

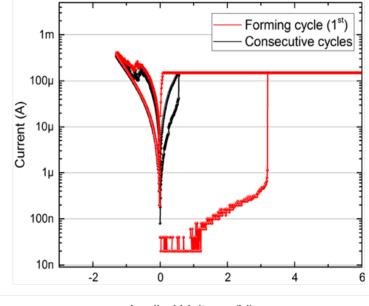

| 6.5 | a) Device No.1 with $Pt(BE)/HfO_2(5 \text{ nm})/Pt(TE)$ , b) Switching mechanism for the                |    |

|     | devices No.5 and 6 with $Pt(BE)/HfO_2(5 \text{ nm})/TiO_2(3 \text{ and } 5 \text{ nm})/Pt(TE)$ (accord- |    |

|     | ingly) during: 1- set and 2- reset processes                                                            | 49 |

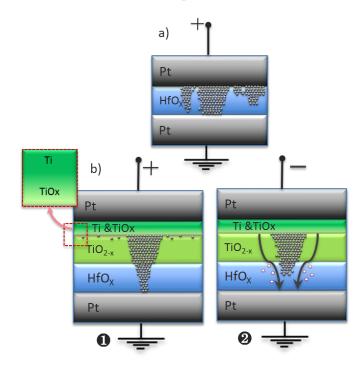

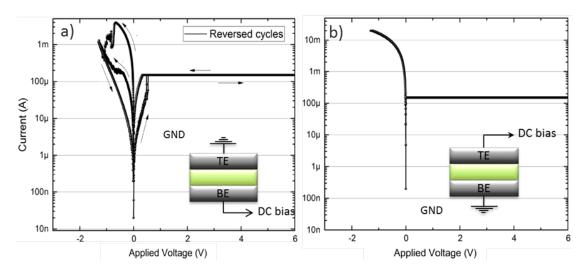

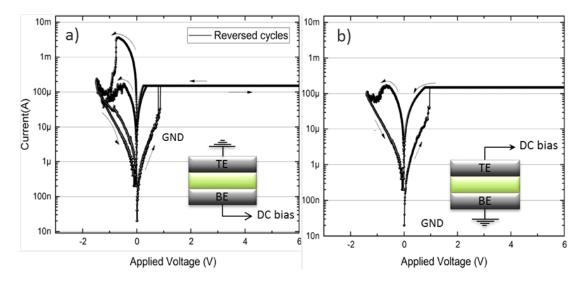

| 6.6 | a) Device No.5 Pt(BE)/HfO <sub>2</sub> (5 nm)/TiO <sub>2</sub> (3 nm)/Ti(5 nm)/Pt(TE) for: a)Reversed   |    |

|     | measurement setup (BE biased, TE grounded), b) back to original (TE biased,                             |    |

|     | BE grounded)                                                                                            | 5  |

| 6.7 | a) Device No.6 Pt(BE)/HfO <sub>2</sub> (5 nm)/TiO <sub>2</sub> (3 nm)/Ti(5 nm)/Pt(TE) for: a) Reversed  |    |

|     | measurement setup (BE biased, TE grounded), b) back to original (TE biased,                             |    |

|     | BE grounded)                                                                                            | 5  |

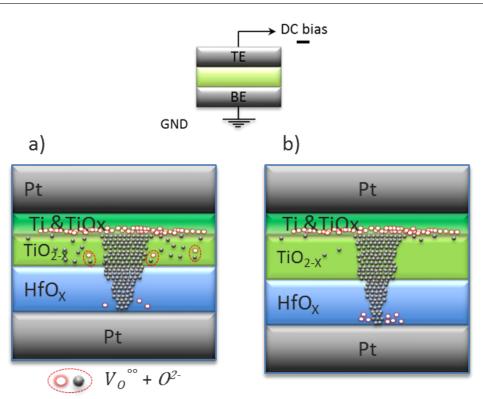

| 6.8  | Schematic demonstration of reset process after switching back to original mea-<br>surement setup for (Te biased, BE grounded) for: a) Device No.5, b) Device<br>No.6                                                                                                                                                                                              | 52        |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

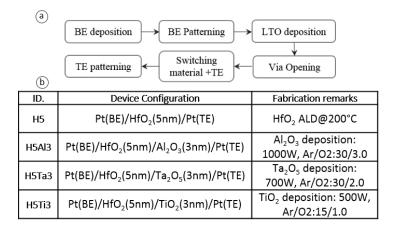

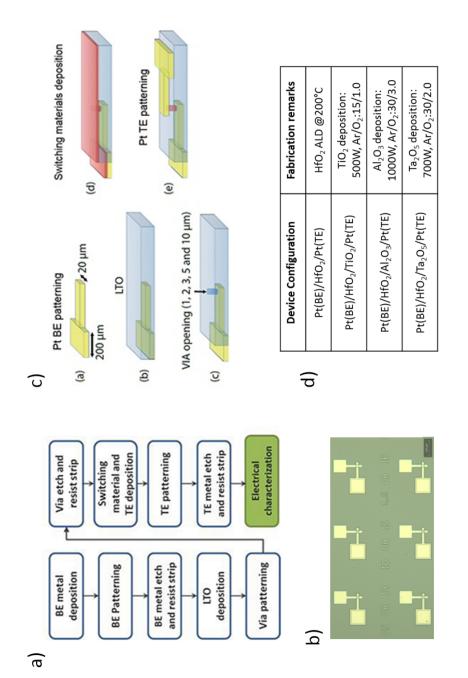

| 7.1  | a) Brief schematic demonstration of process flow, b) Device name, their material configurations and fabrication details                                                                                                                                                                                                                                           | 56        |

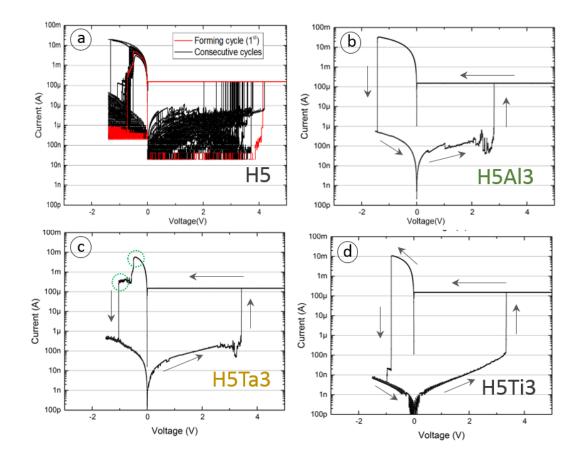

| 7.2  | The I-V characteristics of a) Pt(BE)/HfO <sub>2</sub> (5 nm)/Pt(TE), b)Pt(BE)/HfO <sub>2</sub> (5 nm)/Al <sub>2</sub> O <sub>5</sub> (nm)/Pt(TE), c)Pt(BE)/HfO <sub>2</sub> (5 nm)/Ta <sub>2</sub> O <sub>5</sub> (3 nm)/Pt(TE), and d)Pt(BE)/HfO <sub>2</sub> (5 nm)/TiO <sub>2</sub> (3 nm)/Pt(TE)                                                              | ₃(3<br>57 |

| 7.3  | Summary of switching parameters values for fabricated devices                                                                                                                                                                                                                                                                                                     | 58        |

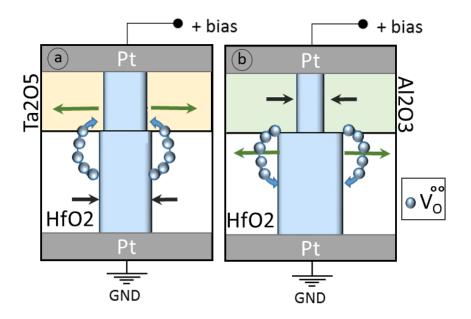

| 7.4  | Schematic demonstration of switching mechanism for H5Al3 and H5Ta3                                                                                                                                                                                                                                                                                                | 58        |

| 8.1  | a) Flow chart of fabrication steps, b) Schematic demonstration of process flow including the material deposition and the patterning steps, c)optical microscope image of a device after fabrication and d)Device configuration and fabrication details. The relatively larger pads (in yellow) are designed to provide sufficient space for the measurement steps | 64        |

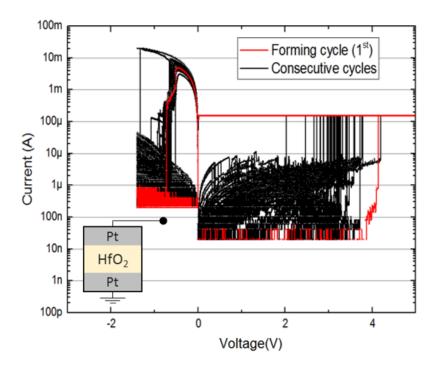

| 8.2  | The I-V characteristics of the $Pt/HfO_2(5 \text{ nm})/Pt$ , the forming voltage is plotted in red while the next consecutive sweeps are plotted in black. The inset schematically demonstrates the biasing of the device                                                                                                                                         | 66        |

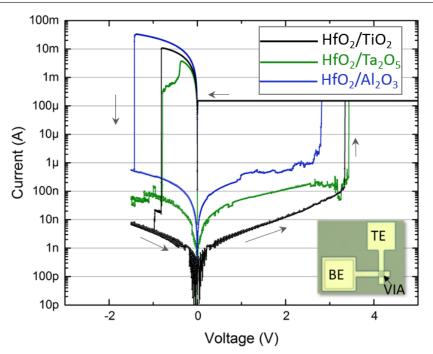

| 8.3  | I-V characterisation of bi-oxide devices with $Pt/HfO_2(5 nm)/Al_2O_3(3 nm)/Pt$<br>(plotted in blue), $Pt/HfO_2(5 nm)/Ta_2O_5(3 nm)/Pt$ (plotted in green), and $Pt/HfO_2(5 nm)/TiO_2(3 nm)/Pt$ (plotted in black). The inset demonstrates a optical microscopic image of the devices, with BE and TE and the vias vertically between them                        | 68        |

| 8.4  | The summary over forming voltages of bi-oxide ReRAMs HfO <sub>2</sub> =5 nm, with sec-<br>ondary oxides for varied thicknesses                                                                                                                                                                                                                                    | 68        |

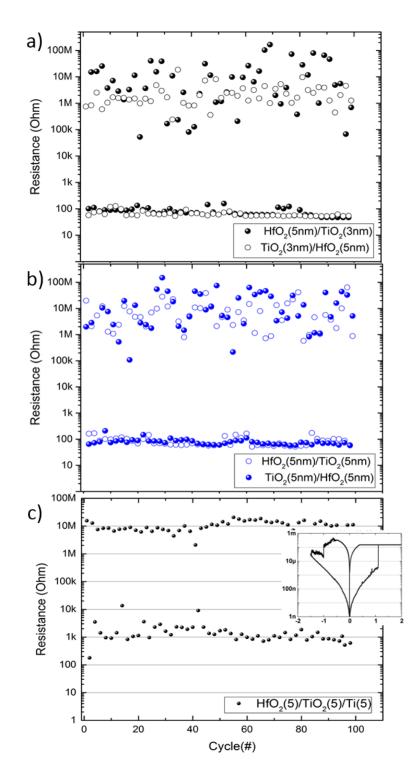

| 8.5  | Cycle to Cycle HRS/LRS distributions for devices with a) $TiO_2(3)/HfO_2(5)$ and $HfO_2(5)/TiO_2(3)$ , and b) $TiO_2(5)/HfO_2(5)$ and $HfO_2(5)/TiO_2(5)$ , and c) $HfO_2(5)/TiO_2(5)$ configurations                                                                                                                                                             | 5)<br>69  |

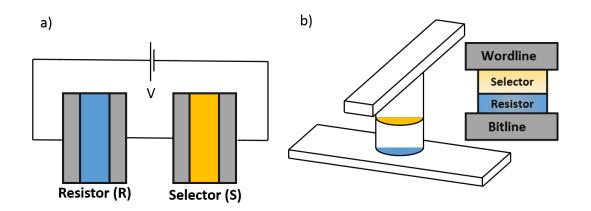

| 9.1  | a) Schematic demonstration of conventional 1S1R architecture a) physically wired , b) in contact together                                                                                                                                                                                                                                                         | 76        |

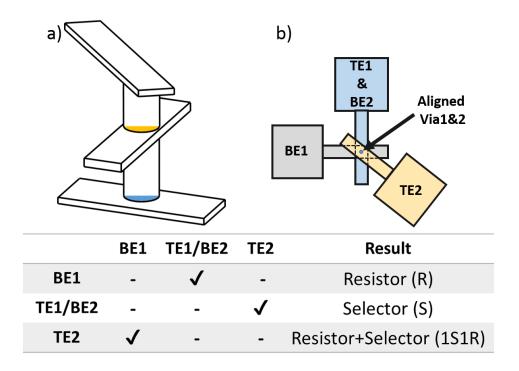

| 9.2  | a) Schematic demonstration of proposed 1S1R, b) different possible configura-<br>tions of device measurement (BE: bottom electrode, TE: top electrode)                                                                                                                                                                                                            | 76        |

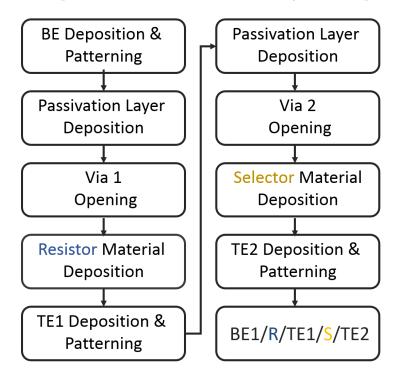

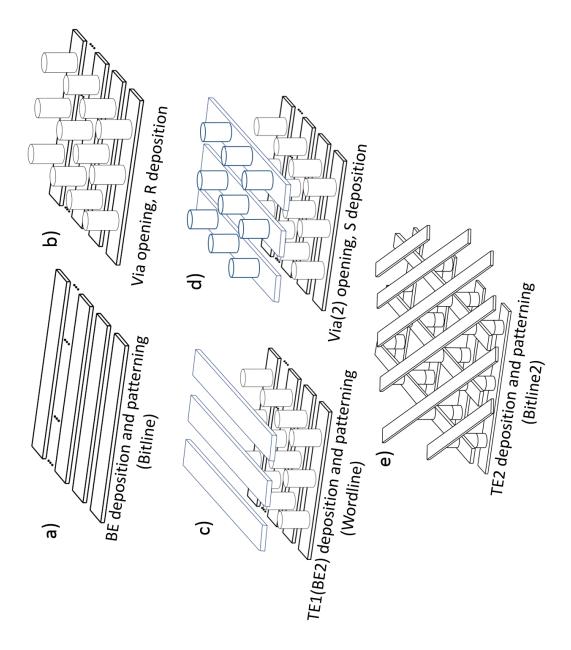

| 9.3  | The general process flow of fabrication of the 1S1R devices                                                                                                                                                                                                                                                                                                       | 77        |

| 9.4  | Fabrication steps of 3D 1S1R cross-point array flow                                                                                                                                                                                                                                                                                                               | 78        |

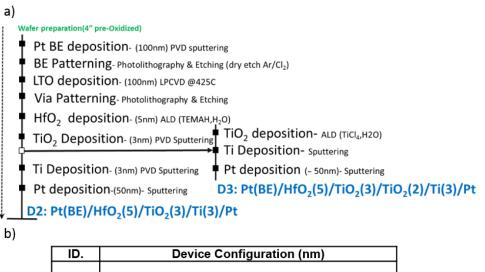

| 10.1 | a) Brief schematic demonstration of process flow, b) device name and configura-<br>tion                                                                                                                                                                                                                                                                           | 81        |

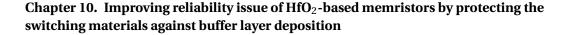

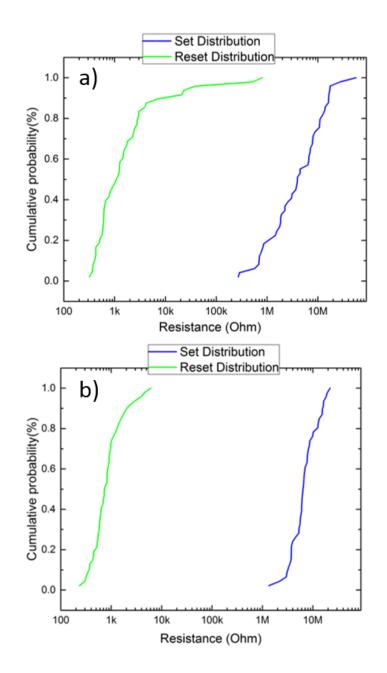

| 10.2 I-V characteristics for a) $D_1$ , b) $D_2$ . Inset shows the distribution for sets and |    |

|----------------------------------------------------------------------------------------------|----|

| resets, c) $D_3$ , and d) summary of key switching parameters for $D_2$ and $D_3$ . The      |    |

| bottom left insets in the parts b, and c shows the microscopic image of the final            |    |

| fabricated device with TE and BE pads and the vias formed between them. The                  |    |

| insets in the bottom right for part b and c schematically demonstrate the biasing            |    |

| methods for the fabricated devices                                                           | 82 |

| 10.3 Cumulative distributions of resistance (set and reset) for a) $D_2$ , b) $D_2$          | 85 |

# List of Tables

| 1.1 | A comparison between conventional memory technologies including SRAM,                  |    |

|-----|----------------------------------------------------------------------------------------|----|

|     | DRAM, Flash (NOR-NAND)                                                                 | 10 |

| 1.2 | A comparison between emerging memory technologies including: SRR-RAM,                  |    |

|     | PCRAM, ReRAM or memristor                                                              | 11 |

| 2.1 | A short list of studied materials for the storage media in ReRAMs                      | 18 |

| 3.1 | A summary of required properties for selector device for suppression of the            |    |

|     | sneak path                                                                             | 21 |

| 3.2 | A comparison between different structural solution of the sneak-path issue $\ . \ .$   | 22 |

| 4.1 | The fabricated devices and their structures. D1 representing a $hfO_x$ -alone device,  |    |

|     | D2 and D3 the HfO <sub>x</sub> -based devices with Hf=5 and 3 nm, accordingly $\ldots$ | 30 |

| 6.1 | A summary of the fabricated devices with their stack structures                        | 46 |

# **1** Introduction

### **1.1 Semiconductor Timeline**

In 1833, English scientist Michael Faraday's discovery of benzene resulted in the first observation of semiconductor materials. He noticed the electro-conductivity of "silver sulfide" increased with increasing temperature. He wrote: "I have lately met with an extraordinary case ... which is in direct contrast with the influence of heat upon metallic bodies ... On applying a lamp ... the conducting power rose rapidly with the heat ... On removing the lamp and allowing the heat to fall, the effects were reversed."

In 1874 German physicist Ferdinand Braun probed a lead sulfide using thin metal wire; he noticed the current flowed freely in just one direction which today is recognized as the rectification effect in diodes. The Braun's semiconductor didn't have any useful application until early 1900 when it was used in radio as a signal detector.

In the early 1900s, electrical engineer Greenleaf W. Pickard working in American Telephone and Telegraph tested thousands of mineral samples to study their rectification properties and discovered Silicon crystals to demonstrate the best results. Later in 1906, he founded the first company to produce and sell silicon-based semiconductor devices, which was "cats's-Whisker" a crystal radio detector (Figure 1.2). The German word "halbleiter" translated in English as "semiconductor" was first used in 1911 to describe materials with electro-negativity in middle of metals and insulators.

In 1926, Polish-American physicist and inventor Julius Lilienfeld introduced a field-effect transistor using copper-sulfide semiconductor (Figure 1.3). In 1931, Alan Wilson, a British physicist working in Leipzig Germany, created a model semiconductor behavior. In his paper, he proposed the semiconductor behavior was due to the presence of impurities in pure crystals of the materials. Later he tried to explain the diode effect using quantum-mechanical tunneling between metal and semiconductor materials, but it was not till 1938, which a proper explanation of rectification phenomenon finally emerged. Several scientists from different countries independently attributed the rectification phenomenon to a correlation between the concentration of electrons and setting up an asymmetric barrier to current flow.

In 1926, Polish-American physicist and inventor Julius Lilienfeld introduced a field-effect

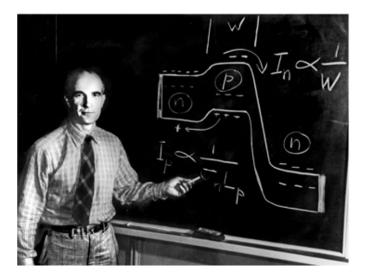

transistor using copper-sulfide semiconductor. In 1931, Alan Wilson, a British physicist working in Leipzig Germany, created a model semiconductor behavior. In his paper, he proposed the semiconductor behavior was due to the presence of impurities in pure crystals of the materials. Later he tried to explain the diode effect using quantum-mechanical tunneling between metal and semiconductor materials (see Figure 1.4, but it was not till 1938, which a proper explanation of rectification phenomenon finally emerged. Several scientists from different countries independently attributed the rectification phenomenon to a correlation between the concentration of electrons and setting up an asymmetric barrier to current flow. In 1940, Russell Ohl in Bell Telephone Labs in NJ introduced the concept of n-type (for negative) and p-type (positive) semiconductor. He exposed a small piece of silicon to bright light and noticed different parts of the pieces of silicon responded differently regarding the type of impurities it is containing. The part with phosphorus yielded more electrons comparing to the part with boron, led to to the deficiency of electrons and introduced the interface of those two parts as a p-n junction. In 1947, in BELL labs, the use of various impurities in providing the n-type or p-type of semiconductor through the implementing the elements of the fifth column of the periodic table (n-type: phosphorus) and third column (p-type: boron) had been investigated. Finally, in 1948, William Shockley introduced the junction transistor based on Ohl's discovery. On June 30, 1948, the first "transistor" implementing gold and germanium has been introduced by Shockley at a press conference in New York.

In 1957, Fairchild semiconductor started its work in Palo Alto followed by many other hightech companies such as Intel and AMD as the first silicon-based company in Silicon-Valley. In 1960 the first concept of MOSFET (Metal Insulator Semiconductor Field Effect Transistor), which is widely used by now in all manufactured microchips, has been introduced (Figure 1.8. By 1952, after a few intensive years of research on semiconductors, the "Sonotone" a hearing aid including a germanium transistor has been introduced to the market with the value of 229.50 USD (Figure 1.7).

Eventually, the semiconductor transistors replaced vacuum tubes in digital computers, in 1956 Bell Labs introduced a computer using 700 point-contact transistors and more than 10,000 diodes. On April 1954, the silicon transistors dominated the markets over the germanium transistors. The accidentally discovered silicon dioxide ( $SiO_2$ ) layer, soon became essential to protect the silicon wafers during manufacturing. Since 1955 and the first attempts in employing photolithography tools to define small designs on a silicon wafer (200 micrometers was achieved by 1957), up to now (below 0.1micrometer), the photolithography process has been considered as an essential step in semiconductor industries.

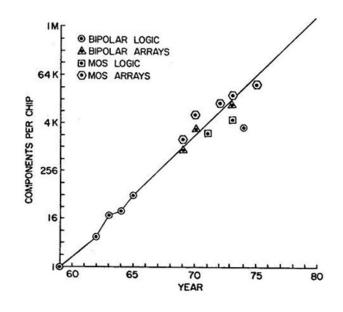

In 1973, the Fairchild Lab. introduced the first CMOS design, using p and n-channel MOS-FET with almost zero power in standby mode, what is known as CMOS nowadays. By 1964, achieving a higher density of MOSFETs with low cost of production, due to complicated manufacturing and reliability appeared more difficult than predicted earlier. Finally, in 1965, Gordon Moore, the R D head of Fairchild and later the co-founder of Intel, published an internal paper and predicted that the number of integrated components on a chip would double every year[56].

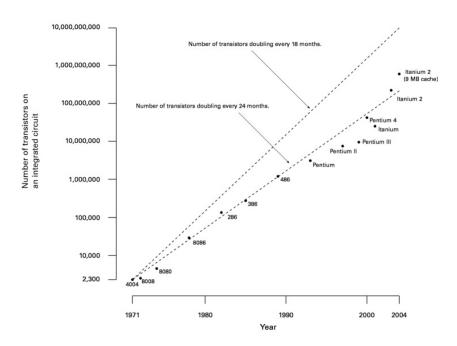

In 1975, at the IEEE Electron Device Meeting, Moore announced a modification in his previous

prediction, he slowed the predicted rate of increase in complexity to be " doubling every two years" taking into account the new data. In 1995, Moore announced that "The current prediction is that this is not going to stop soon."

Moore's prediction known as "Moore's Law" is considered as the standard principles of the semiconductor industries have attempted to achieve ever since.

Despite, the achievement of the industry staying faithful (and predicted to be for few more years to come) to Moore's law, but several limiting factors have appeared and are believed to prevent the industries in following the predicted growing pace, the economical [64] and physical limitation[57].

In spite of lower end-consumer prices for higher density components, the production costs have increased significantly. The costs of research, development, manufacturing, fabrication, and tests have increased continuously by introducing each new generation, known as Rock's law[63].

The Moore's law from 1965 when there were less than 100 transistors in an integrated circuit, has stayed valid till now with millions of transistors on a single chip. In an interview in 2007 at Intel's twice-annual technical conference, Moore stated: "another decade, a decade and a half I think we'll hit something fairly fundamental," he quoted Stephen Hawking says: "When Stephen Hawking was asked what the fundamental limits to microelectronics are, he said the speed of light and the atomic nature of matter" [51]. Therefore, considering an ultimate physical limitation to Moore's law would set a future boundary to electronics miniaturization[61]. By continuous miniaturization, the quantum mechanical effects start to show significant effects as quantum tunneling is considered to be as one of those phenomena. In quantum tunneling, when barriers reach a thickness of below 1-3nm, the electrons can pass through the electric field[44] with higher probability, this effect has been already seen for a while and has gotten worse by lower scaling. The quantum tunneling is an origin of leakage current that disturbs the scaling down the transistors, which causes significant power waste and the heating issues for semiconductor industries. Besides, the memory technologies which uses capacitors for bit-storage suffer from non-quantum based leakage current troubles. Notably, the dielectric leakage current caused by manufacturing material imperfections in the dialectic material insulator is considered to be a major problem. As the density of defects increases with the miniaturization of transistors, the problem gets more severe[81] [52].

In 2015, the CEO of Intel, Brian Krzanich, has noted that: "Brian would say that the difference between seven and five nm technologies is that it's only going to get harder, and there will be fewer and fewer people able to do it." He predicted which we can expect the 5 nm technology to arrive around 2020, then continued with two years of the product cycle, and be produced by 2022; but after that, Moore's law will reach its logical end. Recently, in April 2019, the Taiwanese Semiconductor Manufacturing Co. (TSMC) and Samsung announced their achievement in reaching to 5 nm technology. The new 5nm technologies are claimed to offer a 15 percent higher speed and a 30 percent gain in power efficiency. Interestingly, as Brian predicted, among all semiconductor manufacturer just TSMC and Samsung are offering the 5nm technology, they can afford the immense investment and are expecting reasonable profits.

Figure 1.1 – A 1914 reprint of Faraday's 1839 publication of "Experimental Researches in Electricity", adapted from [1].

Figure 1.2 – A commercialized crystal detector introduced in early 1900s, picture courtesy of : John D. Jenkins, www.sparksmuseum.com.

Figure 1.3 – An illustration from the original Lilienfeld's patent depicting a field-effect transistor.

Figure 1.4 – Wilson's sketch depicting energy band gap with impurity level, Courtesy of Siemens Corporate Archive, Munich.

Figure 1.5 – A page of Ohl's patent field in 1941.

Figure 1.6 – A 1948 image which shows Shockley describing his junction transistor based theory, © 2006-2007 Alcatel-Lucent. All rights reserved.

Figure 1.7 – The Sonotone hearing aid, the device contains one germanium transistor and two tubes, Courtesy of Bob McGarrah.

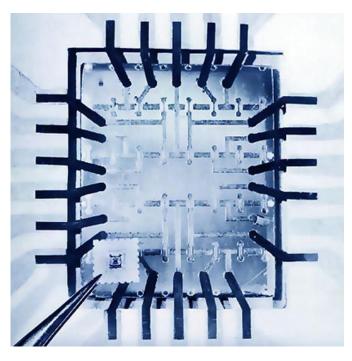

Figure 1.8 – RCA 16-transistor MOSFET circuit demonstrated in front of an enlarged image of it, credits:RCA Incorporated.

Figure 1.9 – Dr. Moore's prediction of number of integrated components on a chip.

Moore's Law

Figure 1.10 – Dr. Moore's Law, the first and second edition.

## 1.2 Classification of Semiconductor Transistor-based Memory Technologies

Semiconductor memories can be classified based on many functional criteria. As one of the major classification, silicon-based semiconductor memories can be categorized according to the number of times they can be re-written to random access memories (RAMs) and read-only memories (ROMs); unlike ROMs, in RAMs there is no limitation in the number of reading or writing cycles to any cell, in almost identical time.

The memory technologies could also be categorized to volatile and non-volatile[10]. In volatile memories, the stored information/data will be erased when the power supply turned off [52], while the non-volatile memories (NVM) retain the data even in the absence of power supply.

#### 1.2.1 Volatile Memory

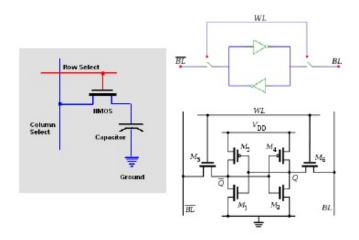

Dynamic RAMs (DRAM) and Static RAMs(SRAM) are considered as the two main technologies of volatile memories, whose need voltage supply to retain their information, while Flash technology is nonvolatile and hold their information without one. SRAMs are very fast (write/erase time : approximately 0.3ns) while the speed is more than 10ns for DRAM, also each SRAM cell includes 4 to 6 transistors, with 140F<sup>2</sup> feature size ("F" is the minimum feature size), while DRAM has a smaller configuration of one-transistor and one-capacitor (1T1C) with 6F<sup>2</sup> minimum cell size (Figure 1.11. Therefore, SRAMS are used as cache (the access time is the main criteria), where the main memories benefit from high-density DRAM technologies.

Figure 1.11 - DRAM (left) and SRAM (right) cells, adapted from[75].

By scaling down the transistors, the electric field barrier becomes smaller, and the electrons can cross it with higher probability. The resulted leakage current becomes more noticeable for the thickness below 3 nm[44]. As mentioned earlier, both DRAM and SRAM consist of

transistors in their structure; therefore scaling down is considered as a significant problem in these technologies.

#### 1.2.2 Non Volatile Memory

Today, the nonvolatile memories, especially hard disk drives, are generally used for the long term storage. The reliable hard disk technology offers high endurance but is considered to be quite slow with the access latencies around few milliseconds [60], hence is being gradually replaced with flash-based technology.

Flash memory is a nonvolatile MOSFET, using a floating gate and tunneling current to write/erase the information. Flash technology comes in NAND or NOR technologies, offering high capacities, small size  $(2-10F^2)$  and relatively low cost of production, however, suffers from the low speed much slower than DRAM (microsecond) and low endurance. The average endurance of high-density flash memories are generally around  $10^4-10^5$  (few specific researches reported  $10^6$  for NAND and  $10^7$  for NOR)[60][11], which is not able to fulfill the industry demanded endurance.

Table 1.1 adapted from [47], provide a comparison between the leader of conventional memory technologies.

| Factors                       | SRAM            | DRAM                 | Flash (NOR-NAND)                        |

|-------------------------------|-----------------|----------------------|-----------------------------------------|

| Feature size                  | 50-120          | 6-10                 | 10, 2-5                                 |

| Read time(ns)                 | 1-2             | 10-60                | 10,50                                   |

| Write/erase Time(ns)          | 1-2             | 10-60                | $10^5 	ext{-}10^7$ , $10^4 	ext{-}10^6$ |

| Endurance                     | $10^{16}$       | $10^{16}$            | 10 <sup>5</sup> ,10 <sup>5</sup>        |

| Power Consumption(read/write) | Low             | Low                  | High,High                               |

| Power Consumption(Other)      | Leakage Current | <b>Refresh</b> Power | No,No                                   |

| Data Retention                | No              | No                   | Yes,Yes                                 |

Table 1.1 - A comparison between conventional memory technologies

### 1.3 Emerging Memory Technologies

Recently, the memory industries have an increasing demand for scaling down the feature size in microelectronic products, but the conventional charge-based memory technology have limitation of 8 nm tunnel oxide layer thickness to make 10 years data retention and prevent the charge loss, therefore new technologies have been introduced as intensively studied to overcome the scaling hurdle. The emerging NVM technology includes resistive RAM (i.e., PCRAM and ReRAM) and magnetoresistive RAM (i.e., STT-RAM) are yet in their early stages and require further studies. The tables 1.2 adapted from [47], provides an overview over comparison of all emerging memory technologies.

Comparing Table1.1 and 1.2, it can be concluded which the emerging NVM are relatively better

| Factors                        | STT-RAM              | PCRAM                 | ReRAM     |

|--------------------------------|----------------------|-----------------------|-----------|

| Feature size $(F^2)$           | 4-20                 | 6-12                  | <4        |

| Read time (ns)                 | 2-20                 | 20-60                 | 10-50     |

| Write/erase Time (ns)          | 2-20                 | 50-120                | 10-100    |

| Endurance                      | $10^{15}$            | $10^{10}$ - $10^{12}$ | $10^{15}$ |

| Power Consumption (read/write) | Read Low, Write High | Med                   | Low       |

| Power Consumption (Other)      | No                   | No                    | No        |

| Data Retention                 | Yes                  | Yes                   | Yes       |

|                                |                      |                       |           |

Table 1.2 - A comparison between emerging memory technologies

than conventional memory technologies with lower cell size and power consumption. To gradually replace the conventional memory technologies, the emerging technologies must have low power consumption, high read/write speed, small feature size, and high density[47].

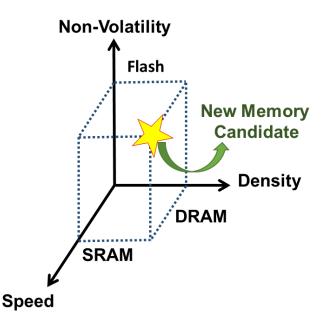

Figure 1.12 – The emerging memory technology must provide a proper trade-off between required properties of industries

Figure 1.12 schematically demonstrates how the emerging memory technology should provide a proper trade-off between three main criteria of 1-Non-volatility, 2-density, and 3-Speed.

Among all candidates, the Resistive Random Access Memory (ReRAM) are considered as a promising candidate with low memory size feature (4 F<sup>2</sup>), low power consumption and high endurance and retention time. In following the ReRAM technology, working mechanism, the

material selection will be explained in more details.

# 2 Resistive Random Access Memory (ReRAM)

As the conventional charge-based memory technologies have failed to fulfill the constantly increasing demand of industries for further miniaturization, the researches are intensively focused on the emerging memory technologies including ferroelectric RAMs (FRAMs), magnetic RAMs (MRAMs), phase-change RAMs (PRAMs) and resistive RAMs (RRAMs). FRAMs and MRAMs have faced limitation in miniaturization regarding their large memory cells, while PRAM has faced a hurdle in its commercialization due to the large power needed to switch between amorphous and crystalline phases[32].

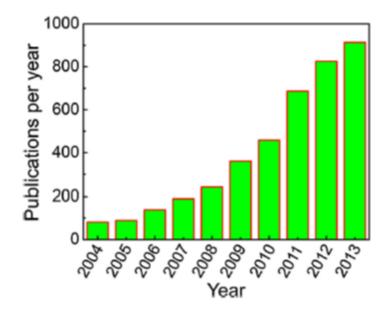

The discovery of resistive switching (RS) is dated back to 1962 when Hickmott[31] first observed large negative differential resistance in thin oxide films such as SiO<sub>x</sub>, Al2O<sub>3</sub>, ZrO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub> and TiO<sub>2</sub>, followed with the same observation for more materials in a capacitor-like structure[29][22]. The strong interests in RS had declined over time in competition with Sibased memories but have raised again in the late 1990s when Zhuang et al.[90] introduced a 64-bit Pr<sub>0.7</sub>Ca<sub>0.3</sub>MnO<sub>3</sub> ReRAMs array using a 0.5CMOS process for NVM application. The Zhuang et al.'s research demonstrated relatively low operation voltage (<5 V), on/off ratio of more than 10<sup>3</sup> and fast switching speed (10 ns). Introducing the first organic-based ReRAM in 2002 [50] followed by exciting demonstration[8] of the first transition-metal-oxide based ReRAM with improved switching properties (operating voltage<3 V, set/reset operation of 10<sup>6</sup>, and 10<sup>12</sup> reading endurance) have boosted the research on ReRAMs and opened up new perspectives to explore different materials and structures to improve the ReRAM device performance.

Today, ReRAMs are considered as the fourth fundamental passive circuit elements also known as memristors (predicted in the early 1970s by L. Chua [20]) and are proposed to be implemented for a wide range of applications including neuromorphic and stochastic computing circuit for unconventional computing (used for multi-parallel computing[37][27]) and FPGA (as re-configurable switches[72]).

Figure 2.1 shows the number of publications per year (2004-2013) adopted from [58]

Figure 2.1 – the increasing number of publications per year between 2004 to 2013 highlights the role of ReRAM as a promising NVM.

## 2.1 The structure

ReRAMs, with their low-cost fabrication and compatibility with conventional semiconductor processes, are believed to have the potential to be used as a universal memory technology. ReRAM is a two terminal device that consists of a metal oxide layer sandwiched between two metal electrodes(top and bottom electrodes), also known as metal-insulator-metal (MIM). The resistance of ReRAMs can be precisely modulated via the application of external stimuli between at least two different levels.

## 2.2 Classification of ReRAMs

The conductivity can be electrically switched between high resistance state (HRS, "0") and Low resistance state (LRS, "1") through "Set" and "Reset" operations. The specific resistance state of the device could be maintained after the electric stimulus is canceled, which is the indication of non-volatility of the ReRAMs.

#### 2.2.1 Classification based on the Type of Resistive Switching

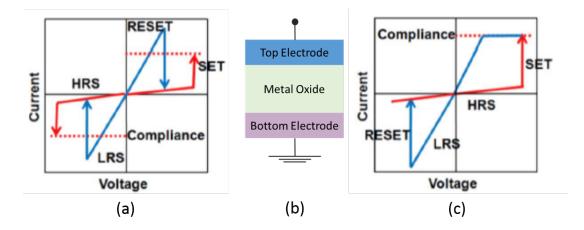

According to the device performance under electrical characterization, the ReRAMs can be classified into two groups: unipolar and bipolar. In unipolar devices, the set and reset operations happen regardless of the polarity of the applied voltage. In contrast, in bipolar ReRAMs, the switching property depends on the polarity of the applied voltage with set and reset operations happening in different polarities. Figure 2.2 shows b) MIM structure working with a) unipolar, and c) bipolar operation modes.

Figure 2.2 – Schematic demonstration of a) I-V switching of a unipolar ReRAM, b) MIM structure, and c) I-V switching of a bipolar ReRAM.

#### 2.2.2 Classification based on the Mechanism of Resistive Switching

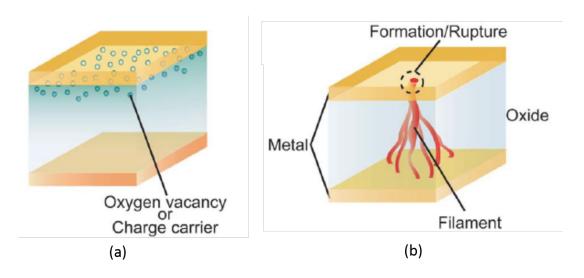

The ReRAMs can be categorized into two groups of filamentary and interface switching by the conduction mode in their LRS[25].

#### Interface switching-Type ReRAMs

In this category, the filaments can not form between the two electrodes; therefore, the contact resistance of the interface controls the switching performance of the device. This type of switching is normally observed in structures with one ohmic and one Schottky-like interface[25] (considering a three-layer structure).

#### Filamentary-Type ReRAMs

In this category, formation and annihilation of conductive local filaments (CF) determine the resistance state of the device. The CFs are composed of metallic nano-bridges[86] or oxygen ions[84] depending on the choice of materials for ReRAMs. Formation of CFs can bridge between two metal electrodes and the current in LRS can flow through these confined path within the insulator layer. In this category, Zhang et al has reported[89] that the LRS resistance is independent of the device size while the resistance in HRS is depending on its size and increases when the size decreased. Figure 2.3 schematically demonstrate the filamentary and interface-type mechanism of resistive switching.

Further mentioning of ReRAMs refers to the filamentary type oxide- based ReRAMs (OxRAMs).

Figure 2.3 – Schematic demonstration for a) A Filamentary ReRAM, and b) An interface-type ReRAM, adopted from [65].

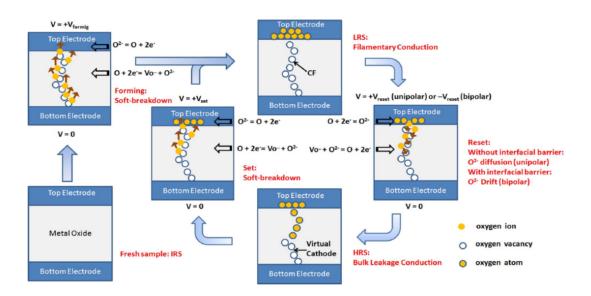

## 2.3 Mechanism of Resistive Switching in ReRAMs

The switching mechanism in ReRAM is depicted schematically in Figure 2.4 in the following. In general, the as-fabricated ReRAM device (pristine state) are considered to be highly resistive. The device undergoes electrical characterization as the TE is biased while the BE is grounded. During the first sweep of positive voltage (also known as electro-forming and forming voltage), the dielectric goes through a soft breakdown and oxygen ions drift to TE by the applied electric field. If the TE is a noble material, the migrated oxygen vacancies remain there as neutral non-lattice oxygen, while they react with oxidable TE and form an interfacial oxide layer. Noble metals form very robust and dense chemisorption bonding with oxygen atoms instead of forming metal-oxide oxides[46]. However, if an oxygen-reactive metal such as Al is used as TE, a very thin layer of highly insulating oxide will be formed at the interface which can hinder the forming process[21].

In ReRAMs in the LRS state, the current flows through CF within the insulator layer. As the formation of CFs is reversible via application of negative polarity biases, the oxygen ions drift back from the TE to the insulator layer and recombine with the oxygen vacancies and return the ReRAM device to the HRS. Lower set voltage ( $V_{set}$ ) can be expected to be seen for following cycles as the reset might not dissolve all formed CFs.

Figure 2.4 – Schematic demonstration of the resistive switching process, including electroforming, set, and reset steps for a simple binary metal-oxide ReRAM device, adopted from[88].

#### 2.4 The Choice of Material and the Device Properties

As mentioned earlier, ReRAM devices are usually composed of a metal-oxide or dielectric layer sandwiched between two metal-electrodes.

#### Metal-Oxide or Storage Media

Over the last decades, numerous oxide materials have been studied as dielectric/storage media for ReRAMs. Generally, the organic materials show a highlighted better stability in switching properties over inorganic materials [65].

Among all introduced materials, HfO<sub>2</sub> appeared as a superior candidate for the storage media of ReRAMs. As it is depicted in Table 2.1, HfO<sub>2</sub>-based ReRAMs show a proper trade-off between different parameters of resistive switching.

Recently, *Atomic Layer Deposition tool* (ALD) is considered as a promising tool for deposition of the storage media of ReRAMs as this technique provides reproducible and precise control over thickness, uniformity and stoichiometric of deposited materials[70][14].

| Dielectric layer                             | On/Off ratio     | Operation Speed | Endurance          |

|----------------------------------------------|------------------|-----------------|--------------------|

| Binary Oxide                                 |                  |                 |                    |

| $MgO_x$                                      | >10 <sup>5</sup> | -               | $>4*10^{2}$        |

| $AlO_x$                                      | >10 <sup>6</sup> | <10 ns;<10 ns   | >10 <sup>4</sup>   |

| $\mathrm{TiO}_{x}$                           | >10 <sup>5</sup> | <5 ns;<5 ns     | $>2*10^{6}$        |

| $MnO_x$                                      | >10 <sup>4</sup> | <100 ns;<200 ns | >10 <sup>5</sup>   |

| $NiO_x$                                      | >10 <sup>6</sup> | <10 ns;<20 ns   | >10 <sup>6</sup>   |

| $GaO_x$                                      | >10 <sup>2</sup> | <400 ns;<600 ns | >10 <sup>4</sup>   |

| $GeO_x$                                      | >10 <sup>9</sup> | <20 ns;<20 ns   | >10 <sup>6</sup>   |

| $HfO_x$                                      | >10 <sup>5</sup> | <300 ps;<300 ps | >10 <sup>10</sup>  |

| $GdO_x$                                      | $>5 * 10^5$      | <1 ns;<1 ns     | >10 <sup>7</sup>   |

| Complicated and Ternary oxides               |                  |                 |                    |

| BaTiO <sub>3</sub>                           | >10 <sup>4</sup> | <10 ns;<10 ns   | >10 <sup>5</sup>   |

| PCMO                                         | >10 <sup>3</sup> | <8 ns;<8 ns     | >10 <sup>1</sup> 0 |

| Chalcogenides                                |                  |                 |                    |

| $Cu_2S$                                      | >10 <sup>6</sup> | <100 µs; < µs   | >10 <sup>5</sup>   |

| $\operatorname{Ge}_{x}\operatorname{Se}_{y}$ | >10 <sup>6</sup> | <100 ns;<100 ns | >10 <sup>10</sup>  |

| Nitrides                                     |                  |                 |                    |

| AlN                                          | >10 <sup>3</sup> | <10 ns;<10 ns   | >10 <sup>8</sup>   |

| SiN                                          | >10 <sup>7</sup> | <100 ns;<100 ns | >10 <sup>9</sup>   |

Table 2.1 – A short list of studied materials for the storage media in ReRAMs, adopted from [58].

## **3** Cross-Point Array

#### 3.1 Introduction

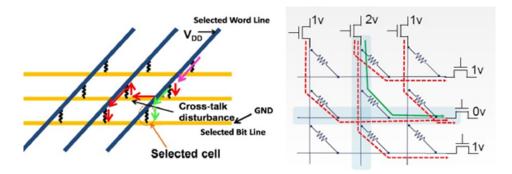

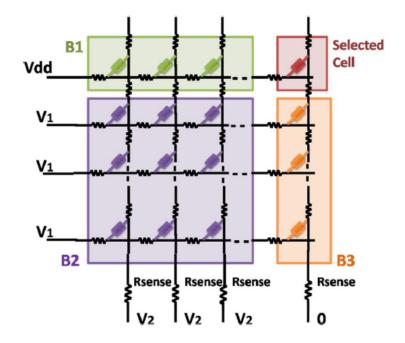

Cross-point array architectures based on resistive switching elements, because of their ultimate scalability have been considered for the next generation non-volatile memory devices and re-configurable logic circuit[80]. A cross-point array consists of parallel interconnects (word and bit lines) perpendicular to each other at two different planes. The simple yet effective cross-point array architecture, allows an effective cell area being  $4F^2$  in 2D design. The feasibility of achieving 3D configuration by stacking multiple 2D layers reduces the minimal feature size further to  $4F^2/n$  and leads to very high integration density (>1Tb as it is required for high-density NVM applications)[4]. However, the sneak current through unwanted neighbor cells, significantly *decreases* the system efficiency, deteriorates the read margin, and limits the maximum size of a cross-point array[26].

#### 3.2 Sneak Path Current Issue

Considering the line resistance, the IR voltage drop on the interconnecting lines are significant, it decreases the accessibility to the target cell, especially during the write operation where high currents are involved (higher IR drop). This leakage currents also raise the total power consumption. Now considering the needs for a bigger array, the array performance degradation is getting even worse due to the higher available paths for the leakage. As it is demonstrated in the Figure 3.1, three different zones (R1, R2 and R3) will be defined in a cross-point system depending on the selected word line(WL) and Bit Line(BL).

Figure 3.1 – a) Illustration of sneak current in a cross-point array with nearly linear RS during the read operation [23], b) circuit schematic of cross-point array[4]. Red dashed lines: sneak current, solid green line: actual readout signal.

Figure 3.2 – Schematic of the cross-point array circuit. V1 and V2 represent the applied voltage on the un-selected word and bit lines[23]

To overcome the sneak path issue, a separate non-linear RS device could be connected with each resistive memory element in series.

An ideal non-linear element candidate to optimally operate with ReRAM should fulfill requirements such as high on-off ratio, scalability, switching speed, endurance compatibility with RS element, low variability and current density, these properties are summarized in 3.1. Several

Table 3.1 – A summary of required properties for selector device for suppression of the sneak path, adopted from [4]

| Parameters                   | Required Value                 |

|------------------------------|--------------------------------|

| ON current $(I_O N)$         | >10 MA/cm <sup>2</sup>         |

| On/Off Ratio                 | >10 <sup>6</sup>               |

| Processing Temperature       | <400° C                        |

| <b>Operation</b> Temperature | 85° C                          |

| Switching Speed              | <50 ns                         |

| <b>Operation Polarity</b>    | Compatible with memory element |

| Scalability                  | Compatible with memory element |

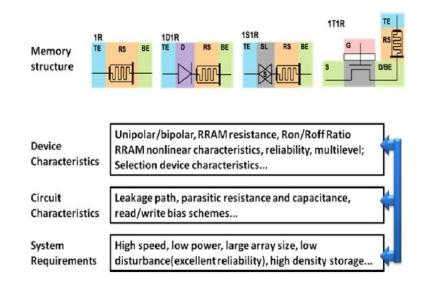

device structures compatible with the cross-point array have been studied, such as: One-diode One-Resistor(1D1R), Complementary RS (CRS), One-MOSFET transistor One-Resistor (1T1R), One-Bipolar junction transistor One-Resistor (1BJT1R), and One-Bipolar selector and One-Bipolar resistor (1S1R); all structures are shown schematically in Figure 3.3 and their properties are compared in the Table 3.2

Figure 3.3 – Different cell structure, device and circuit characteristics and their impacts on system performance[23]

| Device Structure | Cell Size         | Destructive Read | Process Temperature |

|------------------|-------------------|------------------|---------------------|

| 1T1R             | >8 F <sup>2</sup> | No               | High                |

| 1BJT1R           | $4 \mathrm{F}^2$  | No               | High                |

| CRS              | $4 \mathrm{F}^2$  | Yes              | Low                 |

| 1D1R             | $4 \mathrm{F}^2$  | No               | High                |

| 1S1R             | $4 \mathrm{F}^2$  | No               | Low                 |

Table 3.2 – A comparison between different structural solution of the sneak-path issue, adopted from [33].

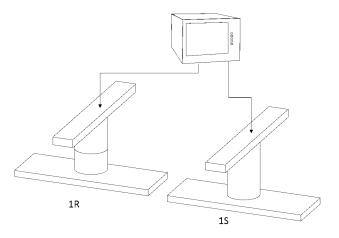

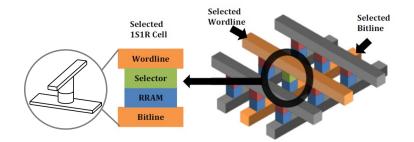

#### 3.3 One selector-One resistor (1S1R)

Serially connecting each memory element to an additional selection device in a 1S1R configuration is an effective way to introduce selectivity to the cross-point arrays. This method permits optimizing of every individual component separately to reach the device performance requirements. Therefore, it is believed that the 1S1R RRAM cross-point array is suitable for the potential storage class memory (SCM) applications.

When both selector and resistor elements are wired together and are biased, the resulted behavior of the system is different from of each single components.

Figure 3.5 schematically demonstrates a conventional 1S1R cross-point array with selector and resistor elements integrated between word and bit lines.

Figure 3.4 - Schematic demonstration of 1S1R on different substrate.

For the ultra-high density non-volatile memory applications (>1Tb), 3D-stackable structures are needed; therefore, more studies over the 1S1R structure are encouraged.

Figure 3.5 – Schematic demonstration of a 1S1R cross-point array[34].

# **4** Effect of Hf Metal Layer on the switching characteristics of HfO<sub>x</sub>-based resistive Random Access Memory

Authors: Behnoush Attarimashalkoubeh<sup>1</sup>, Jury Sandrini<sup>1</sup>, Elmira Shahrabi<sup>1</sup>, Mario Barlas<sup>2</sup>, Yusuf Leblebici<sup>1</sup>

<sup>1</sup> Microelectronic Systems Laboratory, EPFL, Lausanne, Switzerland.

<sup>2</sup> Advanced Memory Group CEA-LETI Grenoble, France.

**Authors contribution:** B.A. Performed the research, including the fabrication process, electrical characterization, data analysis, and wrote the manuscript. J.S. has contributed to the development of the process flow and was involved in the fabrication steps. E.S. revised the manuscript. M.B. has helped in the development of a few steps of the fabrication process, and Y.L supervised the research and revised the manuscript.

Chapter 4. Effect of Hf Metal Layer on the switching characteristics of  $HfO_x$ -based resistive Random Access Memory

### Effect of Hf Metal Layer on the switching characteristics of HfO<sub>x</sub>-based resistive Random Access Memory

**Authors**: Behnoush Attarimashalkoubeh<sup>1</sup>, Jury Sandrini<sup>1</sup>, Elmira Shahrabi<sup>1</sup>, Mario Barlas<sup>2</sup>, Yusuf Leblebici<sup>1</sup>

<sup>1</sup> Microelectronic Systems Laboratory, EPFL, Lausanne, Switzerland

<sup>2</sup> Advanced Memory Group CEA-LETI Grenoble, France

#### Abstract

In this study, we propose the insertion of an ultra-thin Hf layer at the interface between TiN (top electrode) and  $HfO_x$  (electrolyte), and the study of its effect on the device electrical properties. In order to obtain the desired switching characteristics, the Hf layer thickness must be precisely engineered. The device with optimized Hf layer thickness exhibits better uniformity and lower forming voltage. This improvement could be explained by the role of the Hf layer in the creation of permanent oxygen vacancies in the oxide layer, which facilitates the switching phenomena.

Keywords: Resistive Random Access Memory (ReRAM), Oxygen reservoir, Oxygen vacancy.

#### 4.1 Introduction