# Computational characteristics and hardware implications of brain tissue simulations

Thèse N°9767

Présentée le 5 novembre 2019 à la Faculté des sciences de la vie Groupe Schürmann Programme doctoral en neurosciences

pour l'obtention du grade de Docteur ès Sciences

par

#### Francesco CREMONESI

Acceptée sur proposition du jury

Prof. F. C. Hummel, président du jury Prof. F. Schürmann, directeur de thèse

Prof. U. Bhalla, rapporteur Prof. M. Diesmann, rapporteur Prof. B. Falsafi, rapporteur

I wish I did not think about it so much, he thought.

— Ernest Hemingway, For Whom the Bell Tolls

To Ale, Leo, Mati, and the rest of the next generation yet to come.

## Acknowledgements

In the last five years I have grown professionally and personally more than I could ever anticipate. For this, I owe thanks to countless people around me.

Felix Schürmann, you have guided my efforts and managed to remind me of the big picture every time I got lost in my own overthinking. Thank you for your scientific inputs and for your timely words of encouragement. Georg Hager, you've not only taught me everything I know about microprocessor architecture, you've succeeded in showing me the fun and challenging side of it. Michael Hines, thank you for teaching me all the subtleties in the methods for simulating neurons. Your patience and explanations have helped me navigate the world of neuron modelling, and your work in the NEURON simulator is an inspiration to me. Fabien Delalondre, even though you missed out on the last part of this wild ride, you laid its foundations. Without your confidence in me I wouldn't be here today.

My work has also significantly benefited from the practical help of several people. Pramod, thank you for your hard work in making the software tools usable, and for the uncountable discussions about computer performance. Jim, thank you for the whole simulation toolchain that you built and manage, and for teaching me about ancient scripting languages such as hoc. Judit, you've taught me the value of being organised and prepared and you've provided scientific help at moments when I really needed it. Omar, thank you for all the discussion about performance and for your help in NMODL development. Karin, you did your best in turning my stream of consciousness into acceptable scientific writing. Georg, Gerhard, Julian and the rest of the people at RRZE, thank you for your support in understanding the ECM model and your development efforts in Kerncraft. Dries and the rest of the core-services team, thank you for maintaining a running system, exploring bios options and fixing prefetcher configuration on the fly. Dace, Alina, Raquel, Julien, Hashini, Aleksandra and the rest of the administrative services team, I cannot thank you enough for your help in organising various aspects of my work and defence especially.

The one giant stroke of luck that defines my experience at Blue Brain is the unexpectedly high correlation of talent and niceness in the people around me. Taylor, we built our friendship revising cellular neuroscience facts together and developed it side by side in the trenches. You've shown me how to be a good scientist and how to make proper figures, but most of all you've taught me to be a skeptic and an intellectual. Francesco, when I had to interview you I immediately knew that your technical skills were a span above my own, but I never imagined you would be so effective at sharing your knowledge with me. Thank you for teaching me that when you want to understand something, you study night and day until you get it. Bruno,

#### Acknowledgements

we've been through this together and we supported each other when things got tough. You've taught me that a bit of asynchrony and chaos can lead to great improvements. Antonio, you've liberated a part of me that was locked in my childhood memories, and taught me that I can embrace it and still be cool. Tim, you've been my first friend in Switzerland and an unstoppable publishing machine. Giuseppe, your ironic view of PhD life got me through several sleepless nights. Nando, without your python lessons I'd still be stuck debugging triple-nested for loops in my analysis scripts. Berat, thank you for our discussions between jumps and hoops. Sam, thank you for reminding me that math is beautiful.

I've also made friends with some truly amazing people outside the office during these five years. Isa and Till, thank you for all the energy and happiness you've given me to make the days feel lighter. You managed to give me the support and relief I needed, even when I didn't realise I wanted it. #GoPhd! Mari and Fra, you've had the unique ability of providing me with technical discussions and comfort food simultaneously. Thank you for taking care of me when I needed it. Pierre and Nicolas, you've helped me maintain sanity by showing me another world made of notes and counterpoint. Dillenn, Nils, Josephine, John, Nico and the rest of the basketball team, thank you for making me feel welcome in a new city.

Finally, my thoughts go to people from my previous life before BBP. Mom and dad, thank you for teaching me to follow my passions, to use my imagination, to always do my best and to remain humble. To the rest of my family, thank you for your unwavering support. Ludo, you're the brother that I grew up with. Ale, your ambition and freedom in life are an inspiration to me. Also, *sono figo!* Nico and Jacopo, we've been through thick and thin, yet you still haven't stopped listening to my endless stories about my research, thank you. Miro, you are my oldest friend, and you've known the best and worst of me, thank you for always being there.

Silvia, there is no space here to describe the details of why and how much I'm grateful to you. I feel it with a clarity that I hadn't known before. Your determined, lovely smile is what inspired me in approaching this research every day. Let us go and build the next step together.

Genève, 3 Septembre 2019

F. C.

## **Abstract**

Understanding the link between the brain's anatomy and its function through computer simulations of neural tissue models is a widely used approach in computational neuroscience. This technique enables rapid prototyping and testing of hypotheses, allowing researchers to bridge the scales of biological phenomena. Until recently, the constant trend of improvement in computational power has supported an exponential growth in the scale and level of detail of *in silico* experiments. However, a systematic characterization of the performance landscape has not yet been carried out.

In this work we intend to capture intrinsic computational properties of the existing modelling abstractions and answer questions about the intricate relationship between simulation algorithms and modern hardware architecture. Our first contribution is a novel set of hardwareagnostic metrics that enables us to bring focus to the heterogeneous landscape of brain tissue models. We develop a methodology able to capture subtle differences between cell-based models and quantify their impact on performance based on hardware features. We show that lumping simulation experiments together by referring to numbers of neurons and synapses without further detail hides fundamental differences in computational and hardware requirements across models. In addition to analysing different neuron representations, we investigate the impact of biological heterogeneity on the performance of a cortical microcircuit model. Our analysis indicates that while general-purpose computers have until now sustained highperformance simulations of all brain tissue models, the next generation of in silico models will require hardware tailored to the underlying abstraction. We find that all formalisms saturate the memory bandwidth with a fairly small number of shared memory threads, but the reasons behind this are quite different: conductance-based models are dominated by the large memory traffic of clock-driven kernels, while current-based models are most affected by event-driven execution and memory latency. In distributed simulations the latency of the interconnect fabric is the root cause for a significant degradation in performance.

We argue that performance analyses such as ours are required to enable the next generation of brain tissue simulations – or else scientific progress risks being hindered by the presence of severe hardware bottlenecks. Our methodology provides a common tool to facilitate the communication between modellers, developers and hardware designers in order to sustain the larger memory and performance requirements of future brain tissue simulations.

**Keywords** Computational neuroscience, High-performance computing, Performance modelling, Blue Brain Project, Hardware modelling, Neuronal modelling, *in silico* neuroscience

### Sommario

Comprendere il collegamento tra l'anatomia del cervello e il suo funzionamento attraverso l'utilizzo di simulazioni al computer è ormai una tecnica ampiamente utilizzata nell'ambito delle neuroscience computazionali. Questo metodo permette di formulare e testare rapidamente ipotesi scientifiche, dando ai ricercatori la possibilità di formare un collegamento tra le diverse scale fisiche del fenomeno biologico. Il trend costante di crescita delle capacità computazionali dei computer ha fino ad ora supportato una crescita esponenziale nel livello di dettaglio degli esperimenti *in silico*. Tuttavia una caratterizzazione sistematica del panorama delle prestazioni di queste simulazioni non è ancora stata condotta.

In questa tesi ci proponiamo di identificare le proprietà computazionali intrinseche ai modelli di neuroni e rispondere a domande sulla relazione tra algoritmi di simulazione e architettura dell'hardware. Il nostro primo contributo è un nuovo insieme di metriche agnostiche dell'hardware per analizzare il panorama eterogeneo di modelli del tessuto cerebrale. Sviluppiamo poi una metodologia capace di catturare sottili differenze tra modelli a livello cellulare e quantificare il loro impatto sulla prestazione a partire da proprietà dell'hardware. Dimostriamo che raggruppare esperimenti di simulazione riferendosi solamente al numero di neuroni e sinapsi senza fornire ulteriori dettagli nasconde differenze fondamentali tra i requisiti computazionali di modelli differenti. In aggiunta all'analisi di diversi formalismi investighiamo l'impatto della variabilità biologica sulle prestazioni di un modello di microcircuito corticale.

La nostra analisi indica che, mentre i computer d'uso generale hanno potuto sostenere fino ad ora simulazioni ad alta prestazione di tutti i modelli di tessuto cerebrale, la prossima generazione di modelli *in silico* richiederà hardware concepito su misura. Dimostriamo che tutti i formalismi per rappresentare un neurone saturano la larghezza di banda della memoria utilizzando un numero di thread a memoria condivisa relativamente basso, ma le ragioni alla base di ciò sono diverse: i modelli a base di conduttanza sono dominati da un grande traffico di dati, mentre nei modelli a base di corrente i fattori chiave di prestazione sono la latenza della memoria e l'esecuzione event-driven. Nelle simulazioni distribuite la latenza della rete di connessione è la causa principale di una perdita di prestazioni.

Sosteniamo che analisi delle prestazioni come la nostra siano necessarie per consentire lo sviluppo della prossima generazione di simulazioni del tessuto cerebrale, altrimenti il progresso scientifico rischia di essere impedito da gravi limitazioni dell'hardware. La nostra metodologia fornisce uno strumento comune per facilitare la comunicazione tra modellatori, sviluppatori e disegnatori di hardware per poter sostenere i requisiti maggiori di memoria e prestazioni delle simulazioni future di tessuto cerebrale.

# **Contents**

| A  | cknov | wledge  | ments                                                                     | 7    |

|----|-------|---------|---------------------------------------------------------------------------|------|

| Al | ostra | ct (Eng | glish/Italiano)                                                           | vii  |

| Li | st of | figures | <b>i</b>                                                                  | xiii |

| Li | st of | tables  |                                                                           | xv   |

| 1  | Intr  | oducti  | ion                                                                       | 1    |

|    | 1.1   | Perfo   | rmance in brain tissue simulations                                        | 1    |

| 2  | Ove   | rview   | of brain tissue simulations and performance                               | 7    |

|    | 2.1   | State   | of the art in brain tissue models and abstractions                        | 7    |

|    |       | 2.1.1   | Cellular-level modelling abstractions                                     | 8    |

|    |       | 2.1.2   | Strategies for solving the temporal dimension                             | 10   |

|    |       | 2.1.3   | Simulation algorithm and core properties                                  | 11   |

|    |       | 2.1.4   | Notable examples of high performance brain tissue simulations             | 15   |

|    | 2.2   | A stru  | actured view of the modelling landscape                                   | 16   |

|    |       | 2.2.1   | A representative collection of <i>in silico</i> models and experiments    | 16   |

|    |       | 2.2.2   | Hardware-agnostic performance metrics                                     | 21   |

|    |       | 2.2.3   | Characterization of modelling approaches                                  | 24   |

|    | 2.3   | State   | of the art in analytic performance modelling                              | 26   |

|    |       | 2.3.1   | Performance modelling of single-node shared-memory applications           | 26   |

|    |       | 2.3.2   | Performance modelling of distributed applications                         | 28   |

|    | 2.4   | State   | of the art in empirical performance analysis of brain simulations         | 29   |

| 3  | Ana   | lytic p | erformance modelling of neuron simulations                                | 33   |

|    | 3.1   | Analy   | tic performance modelling of shared-memory brain tissue simulation kernel | s 34 |

|    |       | 3.1.1   | G-based kernels in a detailed neuron                                      | 37   |

|    |       | 3.1.2   | Hines solver                                                              | 43   |

|    |       | 3.1.3   | Clock-driven point neuron kernels                                         | 45   |

|    |       | 3.1.4   | Validation of clock-driven kernels                                        | 49   |

|    |       | 3.1.5   | Spike delivery kernels                                                    | 51   |

|    |       | 3.1.6   | Discussion                                                                | 56   |

|    | 3.2   | Perfor  | rmance modelling of interprocess communication                            | 57   |

#### **Contents**

|   |      | 3.2.1   | Modelling the interprocess communication in brain tissue models $\ \ . \ \ .$ | 57   |

|---|------|---------|-------------------------------------------------------------------------------|------|

| 4 | Peri | formar  | nce landscape of brain tissue simulations                                     | 67   |

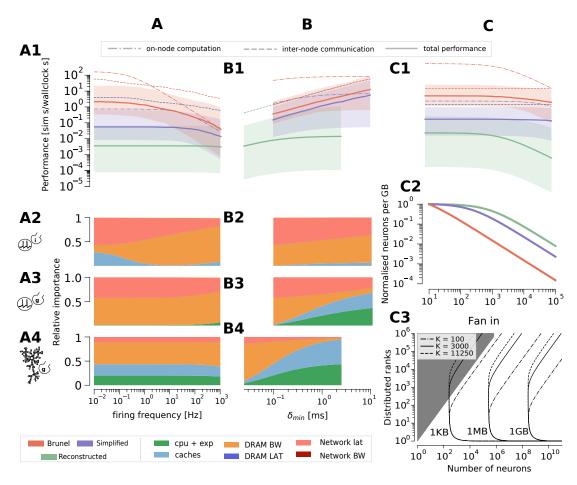

|   | 4.1  | Analy   | sis of the performance landscape                                              | 68   |

|   |      | 4.1.1   | Serial regime                                                                 | 69   |

|   |      | 4.1.2   | Shared memory max-filling                                                     | 70   |

|   |      | 4.1.3   | Distributed max-filling                                                       | 74   |

|   |      | 4.1.4   | Shared memory constant problem size                                           | 76   |

|   |      | 4.1.5   | Distributed constant problem size                                             | 78   |

|   |      | 4.1.6   | Dependence of performance on model parameters                                 | 80   |

|   | 4.2  | Discu   | ssion of Performance Landscape and Future Projections                         | 85   |

| 5 | A ca | ise-stu | dy in the heterogeneous performance of a cortical microcircuit                | 91   |

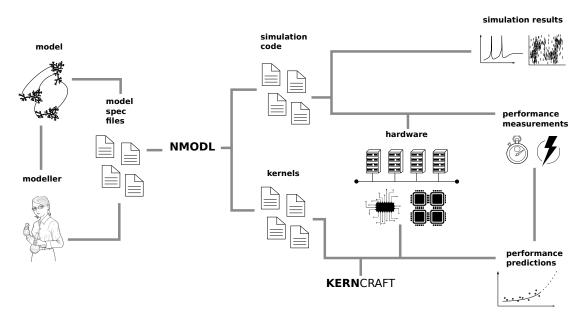

|   | 5.1  | Auton   | natic performance modelling of ion channel and synapse simulation kernels     | s 92 |

|   |      | 5.1.1   | NMODL                                                                         | 94   |

|   |      | 5.1.2   | Kerncraft                                                                     | 94   |

|   |      | 5.1.3   | Extensions of NMODL's code generation backend for Kerncraft automatic         |      |

|   |      |         | performance analysis                                                          | 95   |

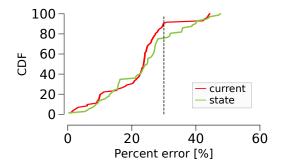

|   |      |         | Automatically obtained ECM models of ion channel and synapse kernels          | 97   |

|   |      |         | Validation                                                                    | 98   |

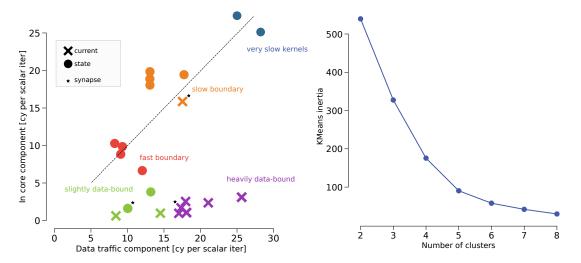

|   | 5.2  |         | ogeneity in ion channel and synapse computational properties                  | 100  |

|   |      | 5.2.1   | Overlap of kernels having complementary performance properties                | 101  |

|   | 5.3  |         | ogeneity in the performance properties of neurons                             | 104  |

|   |      | 5.3.1   | Serial performance                                                            |      |

|   |      | 5.3.2   | Shared memory parallel performance                                            |      |

|   | 5.4  |         | imbalance at the network level                                                |      |

|   |      | 5.4.1   | Static load balance                                                           |      |

|   |      |         | Dynamic load balance                                                          |      |

|   | 5.5  |         | ssion                                                                         |      |

|   |      | 5.5.1   | Limitations and future work                                                   | 122  |

| 6 | Disc | cussior |                                                                               | 123  |

|   | 6.1  |         |                                                                               | 124  |

|   | 6.2  |         | ware implications                                                             | 126  |

|   | 6.3  |         |                                                                               | 128  |

|   | 6.4  | Closir  | ng remarks                                                                    | 129  |

| A |      |         | n algorithms and fundamental concepts                                         | 131  |

|   | A.1  | Suppl   | ementary material for Chapter 2                                               | 135  |

| В |      |         | the ECM and LogGP model                                                       | 137  |

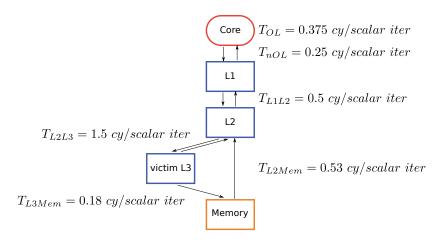

|   | B.1  |         | CM model                                                                      | 137  |

|   |      | B.1.1   | The roofline model                                                            | 137  |

|   |      | B 1.2   | Fundamentals of The ECM model                                                 | 139  |

| LogGP model                                           | 157                                                   |

|-------------------------------------------------------|-------------------------------------------------------|

| LogGP model                                           | 157                                                   |

|                                                       |                                                       |

|                                                       |                                                       |

| el code listings                                      | 151                                                   |

| on Intel Skylake                                      | 146                                                   |

| Inference based on the ECM model                      | 144                                                   |

| Runtime ECM predictions for shared memory parallelism | 142                                                   |

| 4<br>⁄I                                               | Runtime ECM predictions for shared memory parallelism |

**E** Scientific papers

**Curriculum Vitae**

**Bibliography**

**Contents**

167

194

195

# **List of Figures**

| 1.1 | State of the art cellular-level simulations                                            | 2  |

|-----|----------------------------------------------------------------------------------------|----|

| 1.2 | Schematic view of a performance model applied to neuroscientific simulations           | 5  |

| 2.1 | Multiple scales of modelling                                                           | 9  |

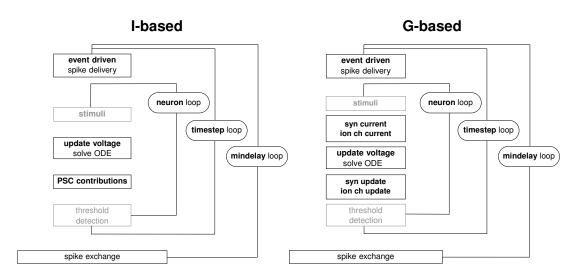

| 2.2 | Algorithmic skeletons for I-based and G-based formalisms                               | 12 |

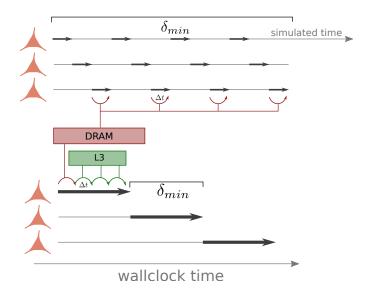

| 2.3 | Loop ordering optimisation                                                             | 14 |

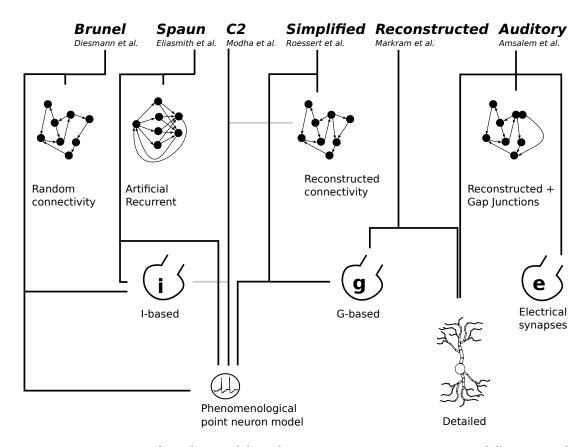

| 2.4 | Summary of <i>in silico</i> models and experiments                                     | 17 |

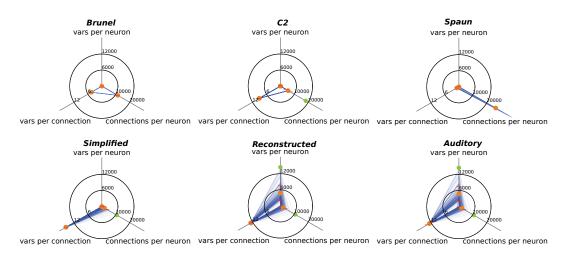

| 2.5 | Breakdown of the unit size metric                                                      | 22 |

| 2.6 | Information sharing metrics                                                            | 23 |

| 2.7 | Serial iterations metrics                                                              | 24 |

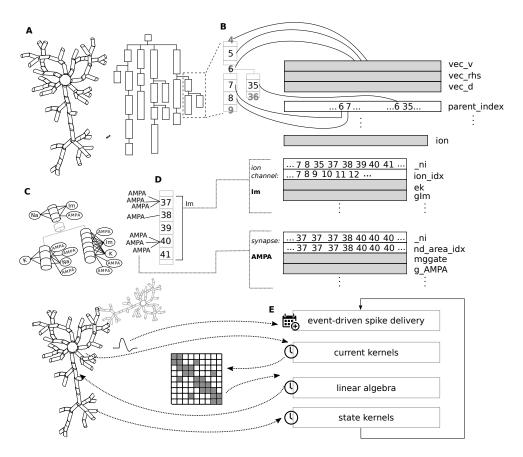

| 3.1 | Neuron representation and data layout in a morphologically detailed G-based            |    |

|     | model                                                                                  | 38 |

| 3.2 | Validation of ECM model for linear algebra kernel                                      | 44 |

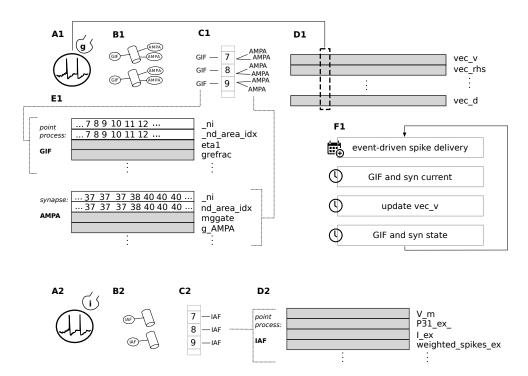

| 3.3 | Neuron representation and data layout in point neuron models                           | 46 |

| 3.4 | Validation of performance model applied to clock-driven kernels of <i>in silico</i>    |    |

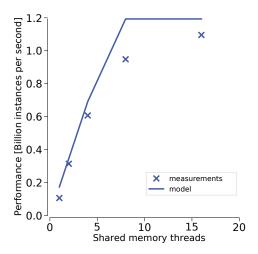

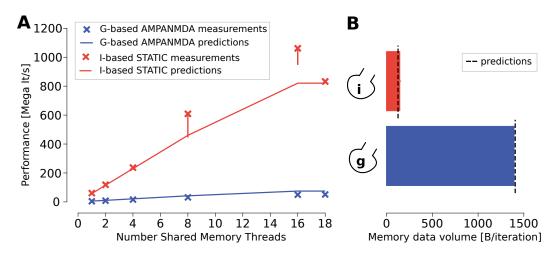

|     | models                                                                                 | 49 |

| 3.5 | Empirical assessment of factorization patterns for the evaluation of the exp           |    |

|     | function                                                                               | 51 |

| 3.6 | Validation of the spike delivery kernel                                                | 55 |

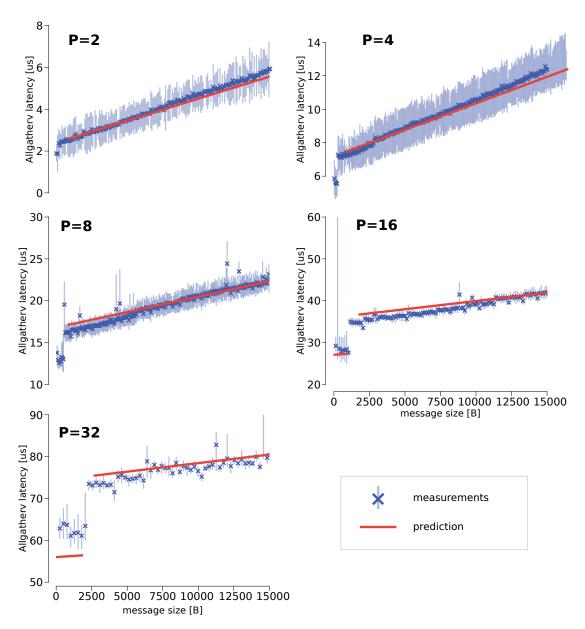

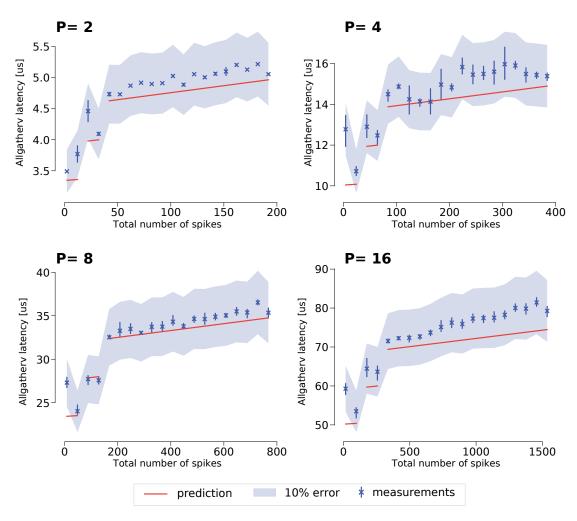

| 3.7 | Validation of LogGP model for interprocess communication using a synthetic             |    |

|     | benchmark                                                                              | 62 |

| 3.8 | Validation of LogGP model for interprocess spike exchange in the simulation            |    |

|     | environment                                                                            | 63 |

| 4.1 | Serial performance characteristics of computational kernels in brain tissue sim-       |    |

|     | ulations                                                                               | 69 |

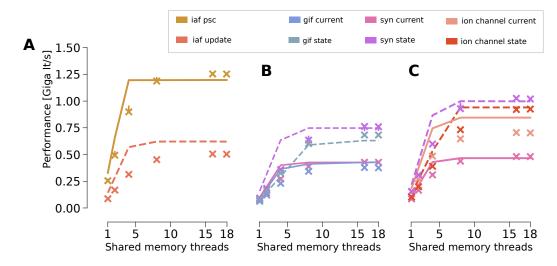

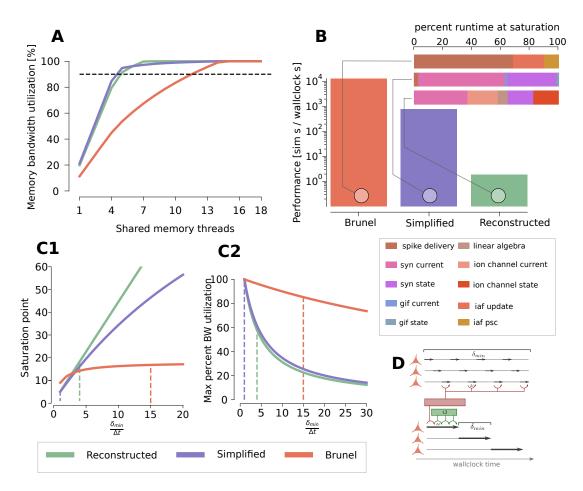

| 4.2 | Shared-memory performance characteristics in the max-filling regime                    | 71 |

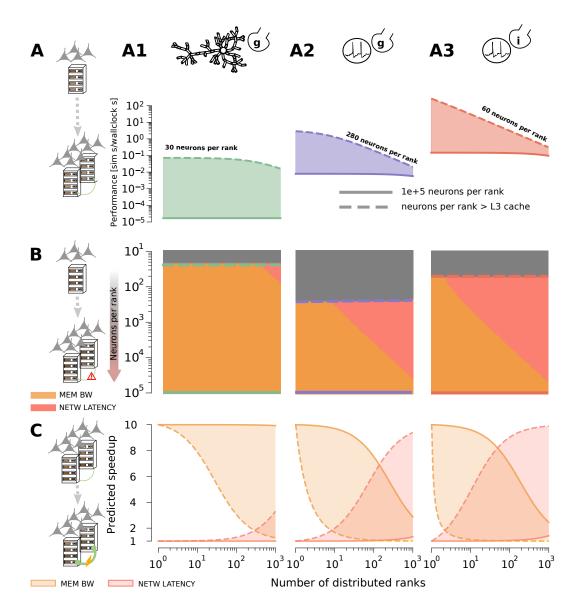

| 4.3 | Predicted performance characteristics of the distributed max-filling regime. $$ . $$ . | 75 |

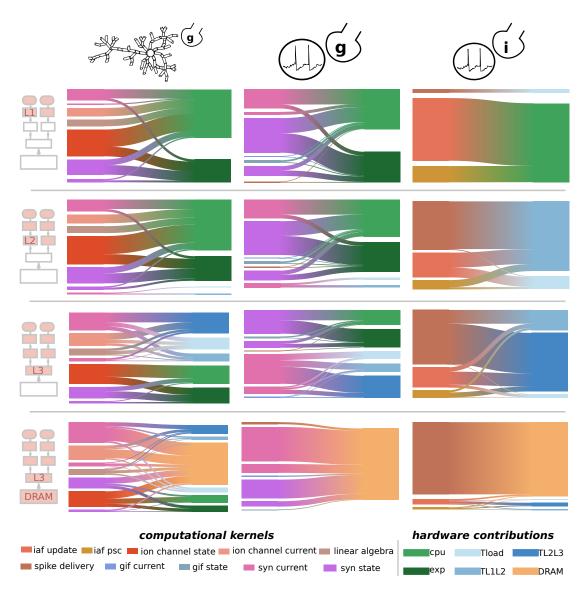

| 4.4 | Predicted shared-memory runtime contributions from computational kernels               |    |

|     | and hardware features                                                                  | 79 |

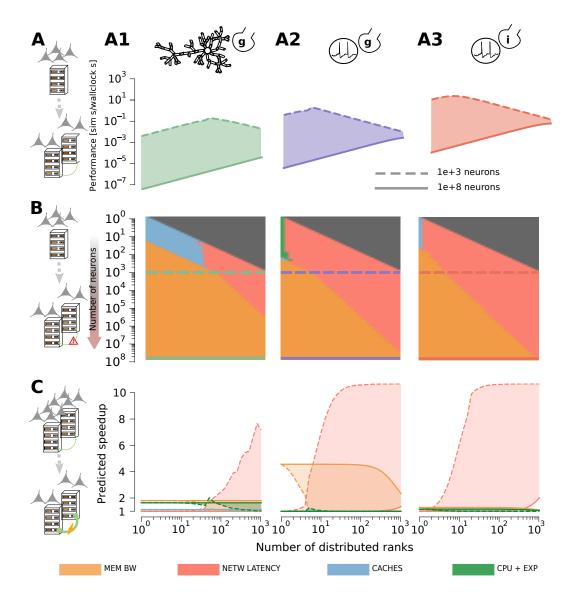

| 4.5 | Performance characteristics of the distributed constant problem size regime. $$ .      | 81 |

| 4.6 | Effect of model parameters on performance                                              | 82 |

#### **List of Figures**

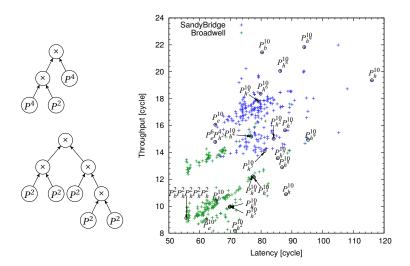

| 5.1        | Automatic performance modelling workflow                                         | 93  |

|------------|----------------------------------------------------------------------------------|-----|

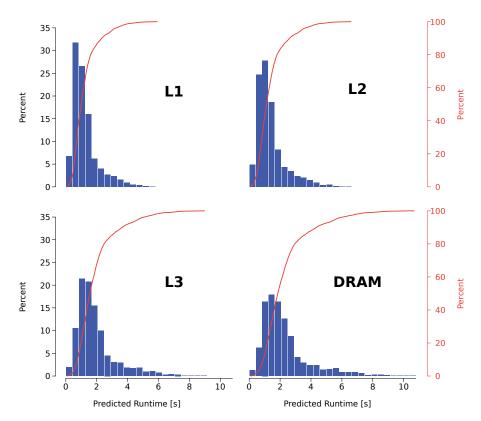

| 5.2        | Cumulative distribution function of the automatic prediction error               | 99  |

| 5.3        | Serial performance profile of individual instances of ion channel and synapse    |     |

|            | kernels                                                                          | 100 |

| 5.4        | Potential performance improvement from overlapping of different kernels. $\;\;$  | 103 |

| 5.5        | Distribution of predicted serial runtime of whole neurons as a function of the   |     |

|            | memory hierarchy level where data resides                                        | 104 |

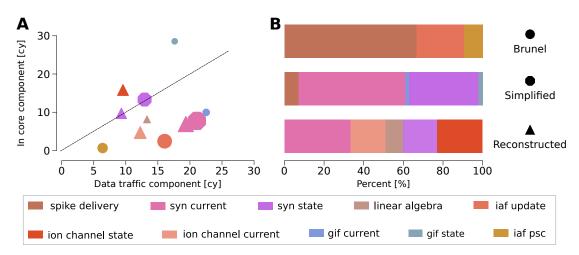

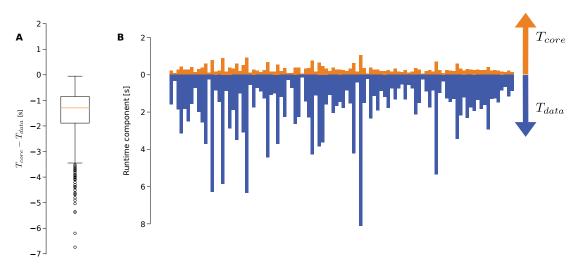

| 5.6        | Single-thread $T_{core}$ and $T_{data}$ contributions by neuron                  | 106 |

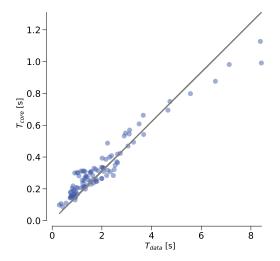

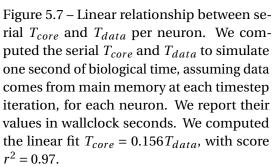

| 5.7        | Linear relationship between $T_{core}$ and $T_{data}$                            | 107 |

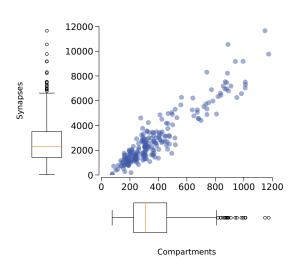

| 5.8        | Number of compartments and synapses co-vary                                      | 107 |

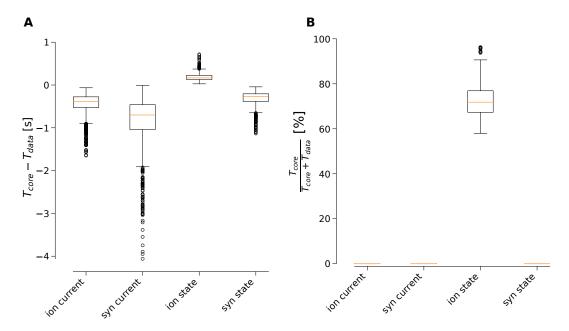

| 5.9        | Distribution of serial runtime properties of kernel families per neuron          | 109 |

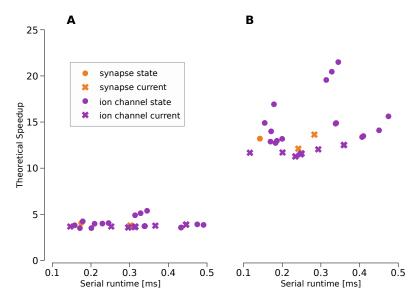

| 5.10       | Parallel speedup of individual ion channel and synapse instances                 | 110 |

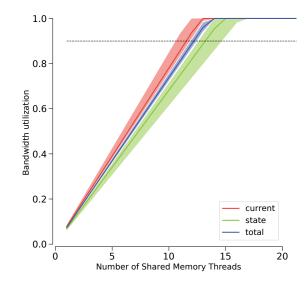

| 5.11       | Average bandwidth utilization per neuron                                         | 112 |

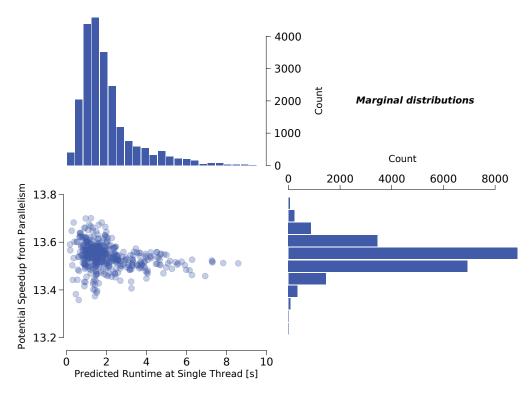

| 5.12       | Distribution over neurons of predicted serial runtime and theoretical maximum    |     |

|            | speedup from shared memory parallelism.                                          | 113 |

| 5.13       | Static load imbalance in a distributed simulation of a detailed microcircuit. $$ | 116 |

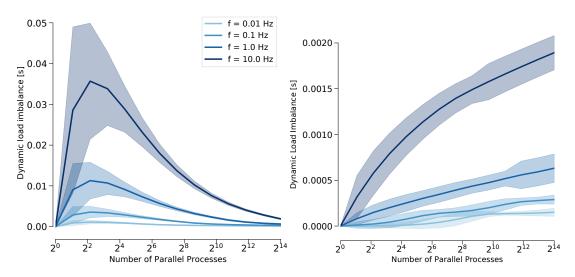

| 5.14       | Dynamic load imbalance arising from spike delivery                               | 118 |

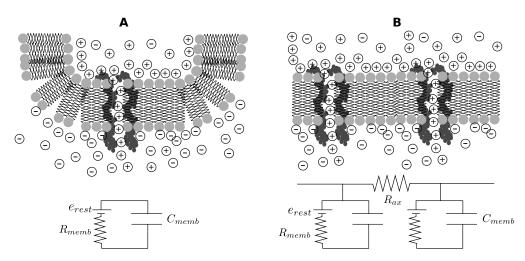

| A.1        | Equivalent RC circuit for neuron representations                                 | 133 |

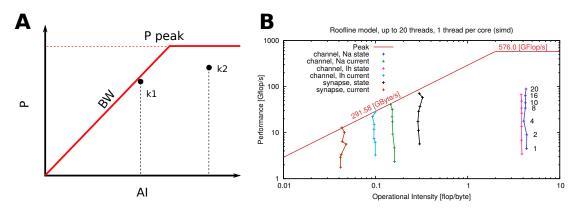

| B.1        | Roofline model                                                                   | 138 |

| B.2        | Schematic view of estimating the data component in the ECM model                 | 141 |

| B.3        | Diagram of modelled parallel execution in the ECM model                          | 143 |

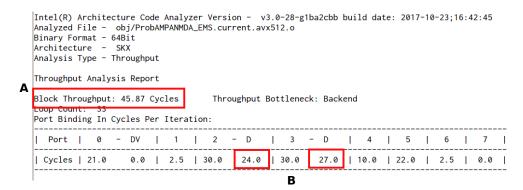

| <b>B.4</b> | Example of IACA output                                                           | 147 |

| B.5        | Diagram of ECM contributions                                                     | 150 |

| B.6        | Ping-ping-pong illustrative example of the LogGP model                           | 158 |

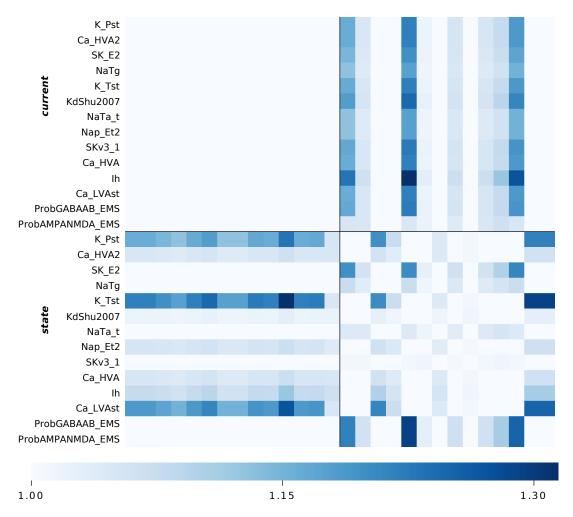

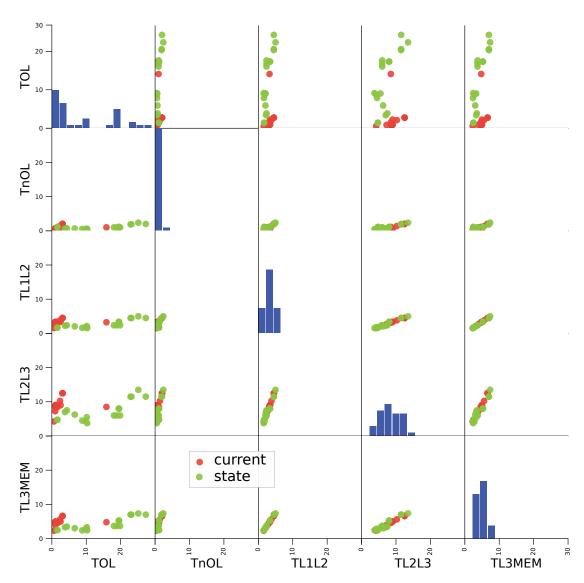

| C.1        | Scatter plot matrix of ECM model description of state and current kernels in     |     |

|            | morphologically detailed neurons                                                 | 162 |

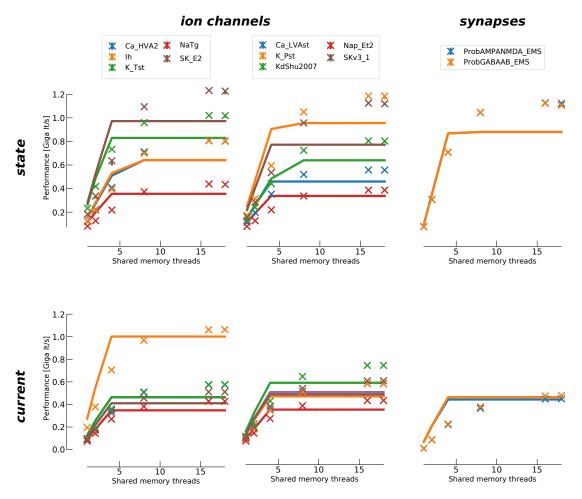

| C.2        | Validation of automatic ECM model of all ion channel and synapse kernels in a    |     |

|            | shared-memory scaling scenario                                                   | 164 |

## **List of Tables**

| 2.1  | Summary of main algorithmic features                                | 20 |

|------|---------------------------------------------------------------------|----|

| 3.1  | Hardware characteristics of reference architecture SKX              | 36 |

| 3.2  | ECM and validation for Im current kernel                            | 39 |

| 3.3  | ECM and validation for synapse current                              | 41 |

| 3.4  | ECM and validation for Im state                                     | 12 |

| 3.5  | ECM and validation for synapse state                                | 13 |

| 3.6  | ECM for linear algebra                                              | 15 |

| 3.7  | ECM model of clock-driven kernels                                   | 18 |

| 3.8  | Validation of ECM model for clock-driven kernels                    | 50 |

| 3.9  | Best-case ECM model of spike delivery                               | 53 |

| 3.10 | LogGP parameters for Infiniband EDR with HPE-MPI                    | 58 |

| 4.1  | Classical performance metrics for <i>in silico</i> models           | 38 |

| 4.2  |                                                                     | 77 |

| 4.2  | Tun-emp predicted performance, relaxing the saturation assumption   | •  |

| 5.1  | Automatic ECM performance model for all kernels                     | 97 |

| 5.2  | Validation of automatic ECM models                                  | 99 |

| 5.3  | Summary of predicted performance improvement from kernel overlap 10 | 03 |

| 5.4  | Summary of distribution of predicted serial runtime                 | 05 |

| 5.5  | Summary of test-set metrics for submodels and full model            | 80 |

| 5.6  | Statistics on the predicted runtime of individual neurons           | 14 |

| 5.7  | Distribution of load imbalance under several configurations         | 17 |

| A.1  | Parameters of <i>in silico</i> models and experiments               | 35 |

|      |                                                                     |    |

| B.1  | Synthetic benchmark mimicking the spike delivery access pattern     | 56 |

| C.1  | ECM runtime predictions for all cortical microcircuit kernels       | 63 |

## 1 Introduction

#### 1.1 Performance in brain tissue simulations

Cellular-level digital reconstructions and simulations of brain tissue electrophysiology have become a widespread tool for neuroscientific discovery. Even though in silico experiments cannot fully replace traditional in vitro or in vivo ones, it has been argued that they represent an indispensable contribution to the future of neuroscience (Einevoll et al., 2019; Fan and Markram, 2019). However, the memory footprint and performance requirements for simulating a brain represents an unprecedented challenge in the computational sciences. For example, it has been projected that simulating a human-scale whole-cortex model could require an exascale computer (Markram, 2012), while real-time simulations of such a system could even be impossible with the current hardware solutions (Zenke and Gerstner, 2014). Even a volume of cortical tissue as small as a cubic millimetre can contain several tens of thousands of neurons and glia cells, orders of magnitude more synaptic connections and several orders of magnitude more of proteins, neurotransmitters and signalling molecules. Therefore it is perhaps not surprising that computer performance has been one of the major limiting factors in the computational modelling and exploration of biological neural networks (Einevoll et al., 2019; Kotaleski and Blackwell, 2010; Markram, 2012). To overcome this challenge computational neuroscientists have routinely employed high-performance computing (HPC) techniques (Helias et al., 2012; Markram et al., 2015). These optimised approaches have enabled researchers to probe the electrochemical properties of the brain at an unprecedented scale (see e.g. Ananthanarayanan et al., 2009; Izhikevich and Edelman, 2008; Jordan et al., 2018; Nolte et al., 2018; Reimann et al., 2013). Several large-scale brain tissue models leveraging HPC hardware have been published (see Chapter 2 for a review), but achieving efficient, high-performance simulations still remains an open problem.

Much of the early increase in computational requirements of models and simulations have been supported by Dennard scaling (Dennard et al., 1974) and Moore's law (Moore, 1995), but with chip-manufacturing technology reaching its limit and the consequent rise of multi-core and heterogeneous architectures (Hardavellas et al., 2011; Simonite, 2016), computational

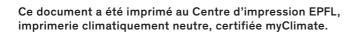

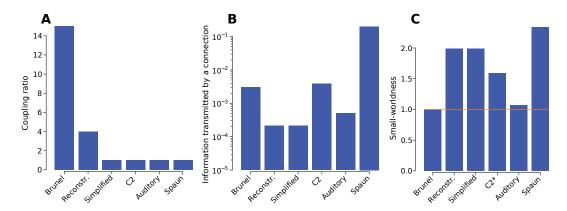

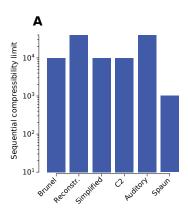

Figure 1.1 – State of the art cellular-level simulations and performance. Supercomputers and HPC architectures are begin used to conduct *in silico* experiments based on mathematical models of neurons. **A**: examples of state-of-the-art brain tissue simulations based on different underlying neuronal abstractions. Researchers typically report the number of neurons and synapses in their simulations as a proxy for complexity of the problem. **B**: cluster size and reported performance of published brain tissue simulations. Cluster size is measured in number of parallel distributed ranks. Performance is measured in simulated seconds per wallclock second to simulate the whole network. The marker size is proportional to the number of neurons in the simulated network.

neuroscientists have been forced to develop more efficient algorithms and software to be able to keep up with the increasing demands of modellers. Research efforts in the context of simulation neuroscience have investigated the efficient utilization of modern multicore processors (see e.g. Brette and Goodman, 2011; Eichner et al., 2009; Kumbhar et al., 2016, 2018), parallel computing (see e.g. Helias et al., 2012; Morrison et al., 2005; Ovcharenko et al., 2015), accelerators (see e.g. Brette and Goodman, 2012; Fidjeland et al., 2009; Knight and Nowotny, 2018) and brain-inspired hardware (see e.g. Benjamin et al., 2014; Indiveri et al., 2011; Painkras et al., 2013).

Typically researchers report the number of neurons and synapses as a proxy for the complexity of their model and compare it against the performance and amount of parallelism in the simulation experiment as shown in Figure 1.1. However this does not paint the whole picture. The wide variety of modelling scales and abstractions has led to a heterogeneous landscape of brain tissue models, making it difficult to compare brain tissue simulations. Moreover, the differences in hardware characteristics can lead to different interpretations of performance results. Finally, the underlying mechanisms and reasons supporting a certain performance are often overlooked or left unexplored.

It becomes clear that a detailed understanding of the performance properties of brain tissue simulations and models represents a fundamental milestone in achieving a better comprehension of the brain's electrophysiology and function. Some performance studies have been conducted, but the large variability between modelling abstractions that is observed in the neuroscientific literature is matched by an equally large variability in the simulation performance. Researchers have investigated memory efficiency (Knight and Nowotny, 2018; Kunkel et al., 2014), automatic generation of efficient kernel code (Kumbhar et al., 2019a; Yavuz et al., 2016), vectorisation (Brette and Goodman, 2011), efficient communication of spikes (see e.g. Ananthanarayanan and Modha, 2007; Hines et al., 2011; Navaridas et al., 2012), splitting of complex neurons (Hines et al., 2008; Kozloski and Wagner, 2011), asynchronous execution (Magalhães and Schürmann, 2019), and other optimisations. Simple performance models have also been proposed for distributed point neuron networks (Peyser and Schenck, 2015; Schenck et al., 2014) or for relevant sub portions of the simulation algorithm (Ewart et al., 2015).

Such work demonstrates the growing interest of the community in simulation performance, but suffers from a few important drawbacks: it is hardware platform and use case specific, and requires new benchmarks for every change in model or simulation configuration; it does not immediately explain differences in performance across *in silico* models and experiments; it provides very limited insight into which hardware features are the most relevant for simulation performance; it does not generalize to new architectures and does not allow exploration of new hardware solutions.

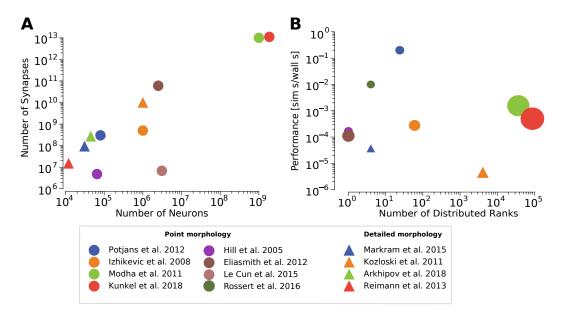

We have highlighted significant differences in the performance profiles of *in silico* models falling within the same category of cellular level representations, but such differences have not yet been thoroughly analysed and discussed. We believe that the situation calls for a better, deeper understanding of how hardware capabilities intersect with brain tissue simulation algorithms to determine their timely and efficient execution. This would empower computational neuroscientists to design more efficient *in silico* experiments and answer fundamental questions about the future of computing architectures by fostering a stronger collaboration between *in silico* modellers, developers and hardware specialists. We seek to fill the gap in our understanding of the performance and computational properties of *in silico* brain tissue simulations by developing an understanding of how neuronal abstractions, simulation algorithms and hardware interact to determine performance. We take inspiration from the field of performance modelling, which combines the representation of a simulation algorithm and a hardware platform to produce insight and predictions on the runtime performance and efficient utilization of resources (see e.g. Balsamo et al., 2004; Calotoiu et al., 2013; Pllana et al., 2007; Williams et al., 2009), as shown in Figure 1.2.

The goal of this thesis is to lay the foundations for a constructive discussion on the computational properties and hardware features that determine the performance of brain tissue simulations. Our first contribution is a structured review of the literature on brain tissue simulations by means of a set of novel hardware-agnostic metrics that capture the most salient

#### Chapter 1. Introduction

performance properties of a representative collection of *in silico* models and experiments. Our second contribution is the development of an analytic performance modelling framework able to combine a description of the simulation algorithm with hardware feature specifications to obtain a runtime prediction based on a concrete understanding of the execution of the simulation workflow on modern hardware. Finally, our third contribution is an analysis of three modelling strategies that encompass most of the state-of-the-art brain tissue simulation models based on the performance modelling method described before. Our analysis is conducted along two axes: a wide-angle view of differences between modelling strategies and their implications for simulation performance and a zoomed-in view of the effects of heterogeneity within a single model of a cortical microcircuit on the performance profile. Ultimately, our work represents an effort to enable and foster cooperation between the communities of neuroscientific modellers, software developers and hardware designers.

This thesis is structured as follows: Chapter 2 presents an extensive review of brain tissue simulations and their performance, and introduces a hardware-agnostic metrics framework to structure our understanding of the heterogeneous landscape of modelling and simulation strategies. Chapter 3 establishes the connection with hardware properties through performance modelling and explains the methods and challenges in understanding the performance of *in silico* brain models; Chapter 4 develops a detailed analysis of the performance characteristics and relevant hardware features of brain tissue simulations, with a focus on understanding the commonalities and differences across models; Chapter 5 investigates the heterogeneity in model parameters and computational properties within an *in silico* cortical microcircuit model, analysing its impact on the computational characteristics of the simulation; and finally, Chapter 6 summarises our main findings, discusses some limitations of our analysis and suggests future strategies to overcome them.

Figure 1.2 – A schematic view of a performance model applied to neuroscientific simulations. A performance model takes as input a parametrized representation of the neuron model, the connectivity, the simulation parameters, as well as a representation of the hardware platform and the interconnect fabric, and combines this information into an analytic expression to obtain insight on the performance bottlenecks and projections.

# 2 Overview of brain tissue simulations and performance

This chapter presents the state of the art in brain tissue simulations and performance modelling. The purpose of this chapter is to highlight fundamental concepts that will be useful in understanding and framing our work. To this end, we compile a list of representative simulation use cases and introduce a novel set of hardware-agnostic metrics that capture the most salient performance properties of brain tissue models. We use our framework to give a structured review of the literature of brain tissue simulations from the point of view of computational characteristics and performance implications on modern hardware. We conclude with an overview of performance modelling techniques and a detailed review of empirical performance studies applied to brain tissue simulations. While we do not provide an exhaustive review, our main contribution is the distillation of the heterogeneous literature in a structured form.

#### 2.1 State of the art in brain tissue models and abstractions

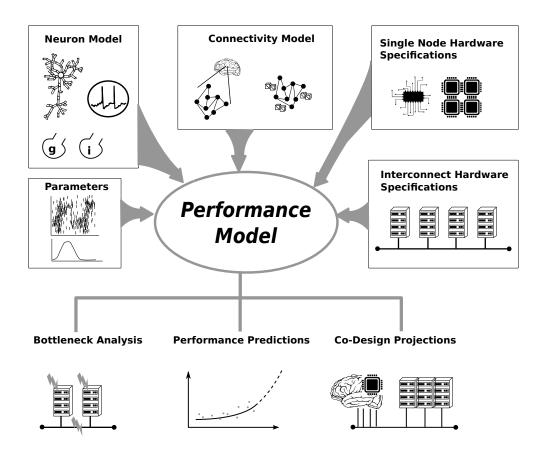

Due to the multiscale nature of the brain, there exists an extremely large body of literature on models that can qualitatively and quantitatively reproduce different aspects of the brain. Modellers have addressed multiscale interactions in the brain by examining how molecular mechanisms and pathways affect cell-level behaviours such as vesicle fusion (Shillcock, 2013), synaptic plasticity (Kotaleski and Blackwell, 2010), and input sequence discrimination (Bhalla, 2017), how membrane potential and synaptic activity affect macro-scale behaviours such as voltage sensitive dye fluorescence (Newton et al., 2016), and finally how neural activity translates to cognitive function and complex behaviour (Falotico et al., 2017; Feldmeyer et al., 2013; Stewart et al., 2012). In addition to explicitly taking into account interactions between phenomena from multiple scales, there exists a multitude of modelling approaches focused on a unique level of abstraction. We distinguish here five different levels: molecular, sub-cellular, cellular, population and cognitive level. At the molecular level (Bhalla, 2014a), scientists use molecular dynamics simulation to understand how nanoscale forces affect the way in which proteins and other important molecules interact, for example in the process of vesicle fusion (Shillcock, 2013). At the sub-cellular level, researchers frequently use a simplification

process based on the well-mixed assumption to circumvent the explicit representation of individual molecules or ions and model instead their concentration. This level of abstraction was used to study the effect of inhomogeneous ion channel distribution on the neuronal membrane (Poirazi et al., 2003) and to understand how signalling pathways within synapses underlie long-lasting conservation of changes in synaptic efficacy at the heart of memory formation (Hayer and Bhalla, 2005). At the cellular level, the computational unit is the individual neuron and researchers study how synaptic connectivity and the membrane's bioelectrical properties affect the membrane potential of the cell. Within this formalism neurons can be modelled either as points (Gerstner et al., 2014) or with full morphological detail (Rall, 1962) and can be assembled in cortical microcircuits that represent a unitary portion of brain tissue (Calabrese and Woolley, 2015; Földy et al., 2005; Markram et al., 2015; Potjans and Diesmann, 2012). At the population level, assemblies of multiple neurons that share certain properties represent the modelling unit and only connectivity between populations is considered, grouping and simplifying synaptic connections between individual neurons. The population abstraction has been used to model cognitive functions and learning (Eliasmith et al., 2012), as well as in clinically relevant applications such as modelling brain tumour (Aerts et al., 2018), while its coarse level of detail makes it an ideal candidate for coupling with signalaveraging measurement methods such as EEG (Jansen and Rit, 1995; Wendling et al., 2003) and voltage sensitive dyes (Markounikau et al., 2010). Finally, at the cognitive level scientists are interested in modelling the causal relationship between observed stimuli and behaviour, often employing statistical tools that have no direct relationship with their biological substrate. Classical examples include Bayesian models (Penny, 2012), Markov models (Hintze et al., 2017) and artificial neural networks (LeCun et al., 2015; Schmidhuber, 2015). Figure 2.1 summarises the main scales of modelling.

This thesis was inspired by the work of Markram et al. (2015) and embedded in the Blue Brain Project, therefore it is framed in the context of cellular-level approaches. This level of abstraction allows for a faithful matching to a wide range of anatomical and electrophysiological data (see e.g. Hagen et al., 2016, 2018; Markram et al., 2015; Potjans and Diesmann, 2012; Pozzorini et al., 2015) and presents an important challenge in terms of understanding its computational properties, as the relationship between neuron models and performance has not yet been fully understood. Therefore the cellular-level approach represents an ideal ground to conduct our analysis. As a first step, we review in the following sections several strategies for modelling individual neurons as well as for integrating their evolution in time.

#### 2.1.1 Cellular-level modelling abstractions

Point neuron models that can qualitatively and quantitatively reproduce the phenomenology of membrane potential fluctuations have been known for decades. One of the earliest representations to be formalized and mathematically analysed is the Lapicque – or leaky integrate and fire (LIF) – model (Lapicque, 1907), which treated the membrane as a resistor-capacitor circuit with a spike generation mechanism every time the potential reaches a certain

Figure 2.1 – Multiple scales of modelling and main abstractions for cellular models. At the molecular scale scientists study the effects of nano-interactions between molecules on neuronal activity. At the sub-cellular scale individual molecules are aggregated and the focus is on chemical reactions and diffusion of ions in the cellular and extracellular mediums. At the cellular scale synaptic connectivity and neurons' electrophysiology are investigated. At the population scale the main object of study are the firing dynamics of neuronal assemblies. At the behavioural scale the main objective is to reproduce and understand the brain's cognitive functions. In this thesis we focus on the cellular level of abstraction. Within it, multiple formalisms to represent neurons and synapses exist. Morphologically detailed models include information about a neuron's dendritic arborization, while point models focus on connectivity between neurons. G-based models use the electrical conductance of synaptic receptors as the most representative abstraction of a synapse, while I-based models directly use the synaptic current, and electrical synapses represent direct connections between the membrane locations of two neurons.

threshold. The LIF model has an extremely simple mathematical representation with a single linear ordinary differential equation (ODE), but has nevertheless enjoyed widespread use and applications (Gerstner et al., 2014; Tuckwell, 1988). The Hodgkin-Huxley model (Hodgkin and Huxley, 1952) takes a more complex approach. It uses a system of nonlinear ODEs with four unknowns to reproduce the phenomenon of rapid depolarisation and hyperpolarisation of neuronal membranes – known as action potential –, by modelling contributions from fast, depolarising sodium currents and slower, hyperpolarising potassium currents. A two-variable simplification was conceived a few years later, at the price of a cubic nonlinearity and the loss of interpretability of the individual current contributions (FitzHugh, 1961). More recently a simple two-variable system of ODEs with only quadratic nonlinearity was sufficient to replicate a wide range of spiking behaviours by careful tuning of its parameters (Izhikevich, 2003). Taking a similar approach, a study introduced the two variable adaptive exponential integrate and fire (AdEx) model (Brette and Gerstner, 2005) and another introduced the generalized integrate and fire (GIF) model (Pozzorini et al., 2013), which is a LIF model with a spike-triggered current and a moving threshold, both capable of reproducing an extremely wide range of observed spiking behaviours and amenable to automatic parameter fitting (Pozzorini et al., 2015).

Compartmental models allow computational neuroscientists to include the morphological details of dendritic arborization in their models (Bhalla, 2012). This field was pioneered by the seminal work of Rall (1962) who, inspired by the beauty and complexity of the drawings by Ramón y Cajal (1909), developed the mathematical formalism necessary to allow spatial discretisation of neurons along the axial dimension. Based on this work, models of individual fibres (Cooley and Dodge Jr, 1966), branched dendrites (Parnas and Segey, 1979) and whole neurons (Traub et al., 1991) have been proposed. Compartmental models represent a discretisation of the cable equation (Thompson and Kelvin, 1855) and the use of this equation in neuroscience has recently been revisited as an approximation of the Maxwell equations (Lindsay et al., 2004). As a consequence of the reliability of axonal transmission, especially in the cortex (Cox et al., 2000), a simplification is often made to simulate only the generation of an action potential (AP) in the axonal initial segment and avoid computing the actual transmission to downstream synapses by assuming a reliable transmission at a constant speed. This simplification allows reducing the computational burden by treating axonal transmission as a simple time delay, without the need to store and update the states of the axonal compartments. Citing scalability reasons, other groups have instead adopted the opposite strategy to simulate axonal compartments (Kozloski and Wagner, 2011).

#### 2.1.2 Strategies for solving the temporal dimension

A review by Brette et al. (2007) presented a comprehensive analysis of the algorithmic and software simulation tools available to computational neuroscientists. They introduce several key concepts useful for characterising and classifying *in silico* models, namely in terms of the drivers for time-advancing, i.e. clock-driven or event-driven, and the current-based (I-based)

or conductance-based (G-based) formalisms for the integration of synaptic events. In clock-driven algorithms, operational kernels are performed regularly at fixed intervals of biological time; while in event-driven algorithms kernels are performed only if and every time a specific event occurs, typically in the form of receiving a spike. Differences in synaptic formalisms will be explained in Section 2.1.3. Figure 2.1 summarises the main modelling formalisms at the cellular level of abstraction.

Usually the analytical solution of the equations describing neuronal dynamics cannot be obtained analytically and numerical methods must instead be employed (Mascagni et al., 1989). For time-dependent ODEs comprising only of a linear and a constant term, the Exponential Euler method exploits the fact that an analytical solution can be obtained to design a first-order accurate time-stepping scheme (Bower and Beeman, 2012; MacGregor, 1987). Rotter and Diesmann (1999) introduced an extension of this scheme that enables exact integration of the temporal dynamics of a wide range of neuron models over a fixed timestep grid. For more general ODEs, the Runge-Kutta method has often been applied (see e.g. Gewaltig, 2015; Naud et al., 2008), but first order Euler schemes, both implicit and explicit, have also been used (Carnevale and Hines, 2006) as well as more modern and complex numerical schemes (see e.g. Hahne et al., 2015, 2017; Rempe and Chopp, 2006; Stewart and Bair, 2009). When using an implicit time-stepping scheme in solving the partial differential equations (PDE) associated with compartmental models, the resolution of a linear system is required because of the coupling between neighbouring compartments. The work of Hines introduced a scheme allowing to exploit linear-complexity methods to invert the corresponding matrix, enabling a generation of fast and numerically stable morphologically detailed models (Hines, 1984). To overcome accuracy and performance limitations of the fixed timestep schemes, adaptive timestep frameworks (Lytton and Hines, 2005) and hybrid explicit-implicit time stepping schemes have also been proposed (Rempe and Chopp, 2006).

#### 2.1.3 Simulation algorithm and core properties

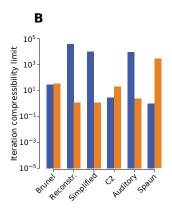

In the following paragraphs, we give a brief overview of the fundamental concepts related to the simulation algorithm underlying all *in silico* models and experiments. A detailed account of the algorithmic steps is given in Appendix A. While presenting a full account of the simulation workflows for all *in silico* models is out of the scope of this work, we focus on the similarities and differences that are instrumental to grasping the challenges and results in the remainder of this thesis, and refer the interested reader to (Brette et al., 2007; Carnevale and Hines, 2006; Gerstner et al., 2014) for more details. We present the algorithmic skeletons in Figure 2.2.

All the brain tissue simulations considered here fall under the category of cellular-level spiking neural network models. Within this modelling scale, the main biophysical phenomena of interest are the Action Potential (AP) and the transmission of individual spikes. An AP is a fast-dynamics event that is elicited when the membrane potential measured at the neuron's Axon Initial Segment (AIS) reaches a certain threshold. In modelling terms, the crossing of the

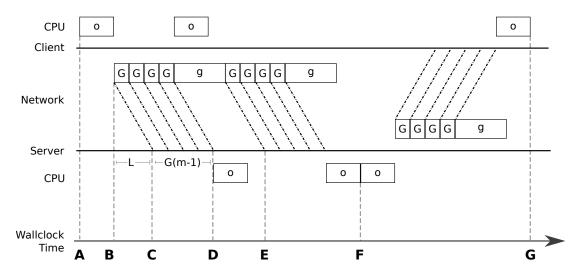

Figure 2.2 – Algorithmic skeletons for I-based (*left*) and G-based formalisms(*right*). The figure highlights the three main loops in both formalisms: an innermost loop in which every single neuron is advanced by one timestep, a middle loop where time is stepped until a minimum delay boundary is reached, and an outermost loop that usually corresponds to a global synchronization timestep and interprocess spike exchange. Boxes in light grey are part of the simulation algorithm and are shown for completeness, but are not considered in our performance analysis as they do not constitute fundamental computational or communication kernels.

threshold is denoted as a **spike**. The AP is often conceptualized as a travelling standing wave moving along the axon, whose path crosses several synaptic locations. When the AP reaches a synaptic location in the presynaptic neuron, neurotransmitter is released in the adjacent extracellular volume. The neurotransmitter molecule binds to receptors in the postsynaptic neuron, determining the opening of specific channels that allow the influx or outflux of charged ions, ultimately causing a small variation in membrane potential at the postsynaptic neuron. Given the all-or-none nature of AP, spikes are often modelled using an event-driven formalism (Hines and Carnevale, 2004) mediated by a **synaptic delay**, although exceptions have been explored in the literature (Kozloski and Wagner, 2011). An important optimisation has been introduced by Morrison et al. (2005) when neurons communicate only via spikes: the global synchronization phase to exchange spiking information across neurons need only be performed every multiple of the **minimum network delay** period, denoted  $\delta_{\min}$ , while within this period the temporal dynamics of neurons may effectively be considered independent.

All the network models in our analysis can be interpreted as a graph, where nodes represent neurons, and edges represent weighted connections or synapses. We use *K* to denote the **fan-in** of neurons, i.e. the average number of incoming connections. For synapses there exist two main strategies for mathematical representation: current-based synapses (denoted hereinafter I-based) and conductance-based synapses (G-based). These correspond to the CUBA and COBA synapse formalisms (Brette et al., 2007). In current-based synapses, the

consequence of receiving a synaptic event is that a constant amount of current is injected in the postsynaptic neuron. In modelling terms this amount is called the **post-synaptic current** (PSC). In conductance-based synapses, on the other hand, the amount of current injected in the postsynaptic neuron is variable for different spikes and depends on the synaptic conductance through Ohm's law. Thus, when a synaptic event is received by a G-based synapse, the conductance – or a state variable from which the conductance can be computed – of that synapse is updated by a fixed quantity. In addition to the chemical synapses described above, neurons can also establish a direct connection between membranes known as an electrical synapse or a gap junction.

While there are significant differences across models in the way in which the membrane potential is modelled and integrated over time, all of the formalisms considered here have some sort of nonlinear dynamics that is able to, under the right conditions, reproduce the behaviour of the AP. However, different representations of neurons based on the level of morphological detail exist: point neurons do not include any information from the dendritic arborization of the neuron, while morphologically detailed neurons typically do. In terms of data representation, point neuron models typically require a few state variables to represent the membrane potential, while detailed models usually need at least one variable per compartment for the membrane potential, plus a few more for every ion channel type associated to that compartment – i.e. the spatial discretisation unit – making the total number of variables that represent a neuron quite large. There is also heterogeneity in the data representation of synapses depending on the underlying formalism: I-based synapses are represented by the total post-synaptic current  $I_{\rm syn}$ , while G-based synapses by their conductance  $g_{\rm syn}$ .

The heterogeneity in morphological representations and synaptic formalisms leads to some fundamental differences as well as some similarities across simulation strategies. Our analysis is focused on fixed timestep integration methods based on the bulk synchronous-parallel (BSP) formalism (Valiant, 1990). Figure 2.2 presents the main simulation algorithm for I-based and G-based formalisms. A detailed account of all the phases in the simulation workflow is provided in Appendix A. In the I-based simulation workflow, the effect of spikes is integrated at the beginning of each timestep, then the state of all neurons is advanced by one timestep by first numerically integrating the membrane equation and then updating the post synaptic current (PSC). When all neurons have been advanced to a time that is a multiple of the  $\delta_{\min}$ , a global synchronization point occurs and neurons exchange spiking information. In the G-based algorithm the integration and the communication of spikes happens in the same way, but the algorithm to update neuron states is different (Hines, 1984). First, a loop through all ion channel and synaptic types computes the current contributed by individual instances to the neuron's membrane equation. Then the membrane equation is solved numerically, and finally the state variables of all the ion channel and synapse instances can be advanced in time, once again through numerical integration. In the case of morphologically detailed neurons, solving the membrane equation usually requires the inversion of a matrix, for which Hines (1984) provided a linear-complexity algorithm.

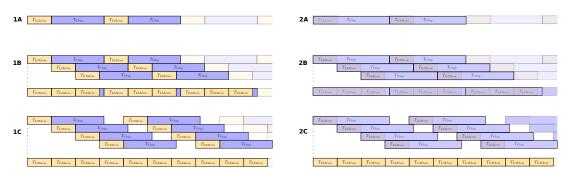

Figure 2.3 – Loop ordering optimisation. In the naïve implementation *(top)* the state of each neuron is advanced by one timestep, then the next neuron is processed and also advanced by one timestep, until all neurons have reached the same instant in time. In this implementation there is no possibility for cache reuse, and data is always fetched from main memory at every time iteration. In the loop ordering optimisation *(bottom)*, the state of a neuron is advanced by a whole minimum delay interval before the next neuron is processed. In this implementation, data must only be fetched from main memory at the first time iteration, and we assume data to be in the L3 cache during all subsequent iterations.

We conclude this section with the description of an important optimisation that promotes data reuse. It is possible to swap the timestep and neuron loops, by having a single neuron advance multiple timesteps until it reaches a minimum delay boundary, before the next neuron's evolution is integrated in time. By updating a neuron's state for multiple timesteps sequentially it should be possible to temporarily store data in caches instead of main memory, as long as a neuron's memory traffic requirements and the number of spikes to be integrated by that neuron are sufficiently low. We denote hereinafter this optimisation as the loop ordering optimisation. Figure 2.3 presents a visual representation of this technique, highlighting the source of data for each neuron's update step. In the naïve implementation each neuron is advanced only by a single timestep each time, therefore no reuse is possible because each neuron will overwrite the caches with its own data. In the optimised implementation a neuron is advanced by multiple timesteps, thus the relevant state data for that neuron is not overwritten from one timestep to the next, and can be stored in the cache. This optimisation was first introduced in Plesser et al. (2007) and is built-in in modern simulators such as NEST (Gewaltig and Diesmann, 2007) and Arbor (Akar et al., 2019b), while it can also be enabled through proper configuration in CoreNEURON (Kumbhar et al., 2019b). In terms of implementation effort, the loop ordering optimisation does not come for free. In particular, separate spike event queues must be maintained for each neuron to enable efficient integration of synaptic events.

#### 2.1.4 Notable examples of high performance brain tissue simulations

Coupling modelling efforts with high-performance computing (HPC) has allowed to overcome limitations in the scale at which experiments are being conducted, such as measuring individual ionic currents and local field potentials from thousands of cells simultaneously (Reimann et al., 2013), isolating different sources of noise (Nolte et al., 2018), or perturbing individual spikes (Izhikevich and Edelman, 2008). As a consequence, HPC has enabled computational neuroscientists to test hypotheses and study protocols with a faster turnaround than ever (Jordan et al., 2018; Knight and Nowotny, 2018; Ovcharenko et al., 2015). Moreover, the process of identifying strategic data and principles governing the brain's organisation and function lies at the heart of the modelling effort. Such an endeavour represents a very effective way to understand the brain as a complex system, by inspecting the model when it fails to reproduce a certain behaviour of interest (Fan and Markram, 2019; Reimann, 2014). Finally, the existence of a validated computational model of the brain could allow, in the future, to reduce our reliance on animal experiments as well as develop and validate disease treatments *in silico* (D'Angelo, 2014; Frackowiak and Markram, 2015).

The underlying complexity of the brain entails that the best simulation attempts to date are the outcome of many years of collaborative efforts. Historically, one of the first simulations of the mammalian thalamocortical system was presented by Izhikevich and Edelman (2008). Despite being the first large-scale endeavour, this model was by no means simplistic and featured stylized neuronal morphologies, short and long term synaptic plasticity, and data-constrained random connectivity. Given the complexity of simulating brain systems, especially at the scale of brain regions, big science initiatives have been developed that have the capability to leverage unprecedented amounts of data made available by new technologies (De Garis et al., 2010; Kandel et al., 2013). The Blue Brain Project (BBP) is a research initiative aimed at building and simulating a biologically detailed digital reconstruction of the rodent brain (Markram, 2006; Markram et al., 2015). This endeavour is based on a data integration strategy consisting of collecting fragmented neuroscientific data. Specifications for this reconstruction are obtained by combining experimental data such as neuron morphologies and patch-clamp recordings with digital reconstruction heuristics for single-cell parameter fitting (Van Geit et al., 2008, 2016), cell connectivity (Iavarone et al., 2019; Reimann et al., 2015, 2019) and reconstructed thalamic inputs (Iavarone et al., 2019) to obtain a cortical microcircuit (Markram et al., 2015). The Human Brain Project is a European-wide initiative aimed at building the research infrastructure necessary to advance neuroscience, medicine and computing in the next decade (Markram, 2012). One of the main deliverables of this project is the Brain Simulation Platform, a collaborative platform for the reconstruction and simulation of brain models. The Allen Institute for Brain Science has recently developed BioNet (Gratiy et al., 2018), a python framework for describing large-scale neural network experiments using the NEURON simulator as backend that has been used in a model of layer 4 of mouse visual cortex (Arkhipov et al., 2018).

Computer simulations are also being used as a primary tool for neuroscientific discovery. The

transition from sleep to wakefulness (and vice versa) has been analysed using simulations of computational models (Hill and Tononi, 2005), and more recently by explicitly modelling neuromodulator release (Bazhenov et al., 2002). Simulations of neuromodulators have also been used to investigate the relationship between persistent spiking and cognitive tasks in a computational model of entorhinal cortex (Fransén et al., 2002). The microcircuit described by Potjans and Diesmann (2012) has been extensively used to study the computational properties of a cortical column with a focus on learning and neuroplasticity, both in its original version and as a basis for population models (Cain et al., 2016; Schwalger et al., 2017). Computer models of chemical reaction pathways have been used to investigate the role of specific signalling molecules in synaptic plasticity (Graupner and Brunel, 2007; Hayer and Bhalla, 2005), while multiscale models have been used to analyse the interactions of different levels of signalling (Bhalla, 2014b). In addition to publicly funded research institutions, private companies such as IBM have invested in developing functioning models of brain subsystems, both to study how synaptic plasticity regulates neuronal responses (Kozloski, 2016; Kozloski and Cecchi, 2010) and to develop the field of cognitive computing (Modha et al., 2011).

#### 2.2 A structured view of the modelling landscape

#### 2.2.1 A representative collection of *in silico* models and experiments

Several modelling abstractions and formalisms have been proposed in the literature of brain tissue simulations, and for each one there can be different algorithms and implementations, which have in turn been concretised in simulations on different hardware platforms. Upon close inspection we have identified a collection of representative use cases that captures the wide variety of cellular-level models in the literature. The identification and codification of recurring algorithmic patterns was demonstrated successfully in the HPC domain with Berkeley's dwarves of computing (see Asanovic et al., 2006, 2009). Their analysis identified and described twelve recurring computational patterns that can be considered the building blocks of almost all HPC applications in the literature. This methodology was extended to other computational fields such as big data (Fox et al., 2014), cloud computing (Phillips et al., 2011), accelerator-based computing (Krommydas et al., 2016) and automatic symbolic computation (Kaltofen, 2012), while a list of computational motifs in biological neural networks' architectures was also compiled (Marcus et al., 2014). The review by Brette et al. (2007) applied a similar approach to neuroscientific use cases, although their focus was on simulator software and target applications, while ours is a general analysis of the most representative and widely used models. We introduce below the in silico models and experiments at the basis of our characterisation of the performance landscape. We focus on short to medium length simulations of brain tissue, excluding long-term plasticity from our analysis. While long duration learning experiments have a significant interest in the computational neuroscience community, we narrow our analysis to simulations of the inference dynamics of neuronal circuits comparable to the work of Markram et al. (2015). This choice still allows us to investigate meaningful properties of neural network dynamics (see e.g. Brunel, 2000; del Mar Quiroga et al., 2016;

Figure 2.4 – Summary of *in silico* models and experiments. Lines connect a model's name with its underlying neuron model, synaptic formalism and network topology. Grey lines stemming from the C2 model were used to avoid intersecting lines that would have hindered the clarity of the figure.

Markram et al., 2015; Reimann et al., 2013) and circumvents the large degree of complexity added by the wide variety of long-term plasticity models and simulation experiments (see e.g. Citri and Malenka, 2008; Frémaux and Gerstner, 2016; Markram et al., 2012; Rennó-Costa et al., 2019). For each use case we highlight important modelling differences and similarities, and summarise their main features in Figure 2.4. More information about the numerical values of model parameters can be found in Table A.1 in Appendix A.

**The Brunel model** This *in silico* model is based on a randomly connected network exhibiting the balanced excitation-inhibition property that can be observed *in vivo* in the mammalian cortex (Brunel, 2000). While other connectivity strategies considered here also use randomness, the peculiarity of the Brunel model is that it is not constrained by experimental data nor locality considerations, such that a neuron has equal chance of forming a connection with any other neuron within the network. It uses the leaky integrate-and-fire model, a phenomenological point neuron model able to reproduce many types of electric neuronal behaviour,

coupled with static (and possibly plastic) current-based synapses. We consider here a very large-scale implementation that served as a proof of concept for the feasibility of human brain-scale simulations (Helias et al., 2012; Kunkel et al., 2014), although we exclude synaptic plasticity from their model. This large-scale *in silico* experiment contained  $1.86 \times 10^9$  neurons and  $11.1 \times 10^{12}$  synapses, and was made possible by calculated software design decisions and optimisations, and a parallel cluster comprising 82944 nodes. It is characterised by a homogeneous set of parameters across neurons and synapses, large synaptic delays and a very large number of incoming connections per neuron.

The Spaun model The Spaun *in silico* model is able to replicate human-like cognitive functions using a spiking neural network (Eliasmith et al., 2012). It is based on the Semantic Pointer Architecture (MacNeil and Eliasmith, 2011) and the Neural Engineering Framework (Eliasmith and Anderson, 2004). A recent implementation on the neuromorphic substrate SpiNNaker was also demonstrated (Mundy, 2016; Mundy et al., 2015). The architecture of Spaun was inspired by the brain regions observed in the mammalian neocortex, but is ultimately engineered to achieve its cognitive goal. It uses  $2.5 \times 10^6$  IAF neurons and  $60 \times 10^9$  synapses and has been shown to learn tasks that require memory, classification and motor control. In terms of modelling choices, Spaun uses a large time integration step, very lightweight neuron and synapse models consisting of only a few parameters each and a few readout neurons with extremely large numbers of incoming connections.

**The C2 model** This *in silico* model has been developed as part of the private industry's effort to establish itself in the domain of cognitive computing. It achieved a very large scale simulation of  $1.6 \times 10^9$  neurons and  $8.87 \times 10^{12}$  synapses over 147,456 CPUs in Lawrence Livermore's National Laboratory's Dawn Blue Gene/P in 2009 (Ananthanarayanan et al., 2009). It uses Izhikevic point neuron models (Izhikevich et al., 2004) and synapses with short-term plasticity, and its connectivity was obtained from the CoCoMac dataset (Bakker et al., 2012) by extracting connection probabilities. This model is characterised by the elimination of synchronous, blocking collective communications in favour of asynchronous sending and receiving of messages (Ananthanarayanan and Modha, 2007).

**The Reconstructed model** This *in silico* models is obtained by a detailed reconstruction of a neocortical microcircuit, i.e. a functional unit of cortical tissue (Markram et al., 2015). This model uses digitally reconstructed morphologically detailed neurons, with individual models for ion channels and synapses whose distribution is obtained via a parameter fitting process to reproduce electrophysiological data. Connectivity is implemented with G-based synapses with short-term plasticity following the Tsodyks and Markram (1997) formalism, while the connection probability is given by detecting touches between neurons and filtering them according to biologically inspired rules (Reimann et al., 2015). This model requires a small time integration step to properly account for the dynamics of fast ion channel currents. Moreover,

the distributions of synaptic delays and number of incoming connections are quite dispersed and exhibit low minimums and large maximums. A large-scale simulation of this model was achieved using 28,672 CPUs on the Blue Gene/Q system at Jülich in 2015 (Ovcharenko et al., 2015).

The Simplified model To tame the complexity of the Reconstructed model, a simplified version was developed with similar connectivity patterns but different neuron and synapse models (Rössert et al., 2016). In this *in silico* model, morphologically detailed neurons are replaced with point generalized integrate-and-fire (GIF) neurons (Pozzorini et al., 2015). While the G-based formalism for synapses is retained, the number of incoming connections per neuron is restricted to a fixed number, where different connections are lumped together according to their synaptic delay and distance from the soma. Thanks to the simplification process, the timestep of this model can be increased compared to the original Reconstructed one, and significantly less parameters are required to represent a neuron.

**The Auditory model** An extension of the Reconstructed model where some dendro-dendritic connections between cells of the same type – Layer 2/3 Basket Cells – of the neocortex have been instantiated using electrical synapses (gap junctions) (Amsalem et al., 2016). This study replicated experimental findings in the auditory cortex that gap junctions affect the selectivity of interneurons. This *in silico* model is based on complex morphologically detailed neurons, and even though an explicit scheme can be used for the propagation of gap junction voltages without introducing numerical instability, it requires a synchronization barrier at every timestep.

We identify three main modelling families which contain all the *in silico* models cited above. The Brunel, Spaun and C2 all fall under the category of I-based point neuron models. They distinguish themselves based on the strategy for determining connectivity, but in terms of overall algorithm structure they can be considered equivalent. For reference, the microcircuit proposed by Potjans and Diesmann (2012) also belongs to this category. The Simplified model is, to our knowledge, the only large-scale example of G-based point neuron *in silico* experiment. Finally, the third category comprising the Reconstructed and Auditory models is the family of G-based morphologically detailed abstractions. In this case, the difference between the two models is simply the presence of electrical synapses, which determines a slight modification in the interprocess communication patterns. These modelling families will constitute the backbone of our performance analysis, and we summarise in Table 2.1 the main features of each one.

Chapter 2. Overview of brain tissue simulations and performance

| Table 2.1 – Summary of main algorithmic features. |                                                                    |                                                                    |                                                                       |

|---------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------|

|                                                   | point I-based                                                      | point G-based                                                      | detailed G-based                                                      |

| spike delivery                                    | update neuron $I_{ m syn}$                                         | update synapse<br>g <sub>syn</sub>                                 | update synapse<br>g <sub>syn</sub>                                    |

| current contribu-<br>tions                        | precomputed $I_{\rm syn}$                                          | update $I_{\rm syn}$ , $I_{\rm ion}$ using Ohm's law A.5           | update $I_{\text{syn}}$ , $I_{\text{ion}}$ of relevant matrix element |

| voltage update                                    | solve small sys-<br>tem of ODE with<br>at most four equa-<br>tions | solve small sys-<br>tem of ODE with<br>at most four equa-<br>tions | invert linear system matrix in $O(n)$ time using Hines algorithm      |