## Research and development of an intelligent particle tracker detector electronic system

Thèse N°9702

Présentée le 27 septembre 2019

à la Faculté des sciences et techniques de l'ingénieur Laboratoire de systèmes microélectroniques Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

#### Alessandro CARATELLI

Acceptée sur proposition du jury

Dr J.-M. Sallese, président du jury

Prof. Y. Leblebici, Dr K. Kloukinas, directeurs de thèse

Dr L. Caponetto, rapporteur

Dr P. Valerio, rapporteur

Prof. D. Atienza, rapporteur

#### **Abstract**

In high energy physics, silicon particles detectors are widely used in tracking applications. They feature high-resolution measurements of the traversing particle positioning and frequently its energy. With the new possibilities introduced by technology scaling, the next generation of silicon detectors will be capable of real-time computing higher level information.

Within the scope of this thesis is discussed a novel silicon particle detection system, for the CMS experiment, capable of providing information regarding the particle direction and transverse momentum, in addition to simple geometrical positioning and energy measurements. This feature allows the event reconstruction and even the offline physics analysis to handle more advanced measurements. Introducing in the sensor readout ASICs the ability to perform a simple real-time analysis of the particle signatures, allows to locally reject information unnecessary for the event reconstruction, with a significant gain in terms of bandwidth and power consumption.

Studies have been carried out to identify the optimal architecture. At system-level, a simulation framework was developed to study and optimize the data processing algorithm and evaluate the more appropriate solution. A silicon prototype of the micro-strip readout ASIC incorporating all required functionalities for operating in the CMS experiment has been designed in a 65 nm technology. One of the major challenges of the design is introduced by the very harsh environment, characterized by a high ionizing radiation dose up to 100 Mrad and a low temperature around  $-40^{\circ}$ C. Low-power and radiation tolerance design techniques have been employed to fulfill the very tight power requirement and to mitigate total ionizing dose and single-event effects. The ASIC performance has been characterized by different working temperatures, operating conditions, and radiation levels. For this purpose, a custom test bench and software was developed. The ASIC measurements show results in agreement with the simulations, proving to fulfill the requirements.

#### Résumé

En physique des hautes énergies, les détecteurs de particules de silicium sont largement utilisés dans les applications de tracking. Ils offrent des mesures à haute résolution du positionnement de la particule en traversée et souvent de son énergie. Grâce aux nouvelles possibilités offertes par la mise à l'échelle technologique, la prochaine génération de détecteurs au silicium sera capable de calculer en temps réel des informations de niveau supérieur.

Dans le cadre de cette thèse sera discuté un nouveau système de détection de particules de silicium, pour l'expérience CMS, capable de fournir des informations sur la direction des particules et la dynamique transversale, en plus de simples mesures géométriques de positionnement et d'énergie. Cette fonctionnalité permettra la reconstruction d'événements et même l'analyse physique hors ligne pour traiter des mesures plus avancées. L'introduction dans les ASICs de lecture des capteurs de la possibilité d'effectuer une simple analyse en temps réel de la signature des particules, permet de rejeter localement les informations inutiles à la reconstruction de l'événement, avec un gain significatif en termes de bande passante et de consommation électrique. Des études ont été menées pour identifier l'architecture optimale. Au niveau du système, un cadre de simulation a été développé pour étudier et optimiser l'algorithme de traitement des données et évaluer la solution la plus appropriée. Un prototype en silicium de l'ASIC de lecture des micro-stripes intégrant toutes les fonctionnalités nécessaires au fonctionnement de l'expérience CMS a été conçu dans une technologie 65 nm. L'un des principaux défis de la conception est introduit par l'environnement très dur, caractérisé par une forte dose de rayonnement ionisant jusqu'à 100 Mrad et une température basse autour de −40°C. Des techniques de design à faible puissance et à tolérance aux rayonnements ont été employées pour répondre aux exigences très strictes en matière de puissance et pour atténuer les effets de la dose ionisante totale et des événements uniques. Les performances de l'ASIC ont

#### **Abstract**

été caractérisées par des températures de travail, des conditions de fonctionnement et des niveaux de rayonnement différents. Pour ce faire, un banc d'essai et un logiciel sur mesure ont été développés. Les résultats des mesures effectuées à l'aide de l'ASIC concordent avec les simulations, ce qui prouve que les exigences sont satisfaites.

## **Contents**

| Ał | ostra   | ct / Rés | sumé                                                            | ii |

|----|---------|----------|-----------------------------------------------------------------|----|

| Li | st of ] | Figure   | s                                                               | хi |

| Gl | ossaı   | ry and   | acronyms                                                        | xv |

| 1  | Intr    | oducti   | on                                                              | 1  |

| 2  | HEI     | P detec  | tor electronics, challenges and state of the art                | 7  |

|    | 2.1     | The C    | MS experiment and the high luminosity upgrade                   | 8  |

|    | 2.2     | The C    | MS silicon tracker                                              | 10 |

|    |         | 2.2.1    | Requirements for the silicon tracker upgrade                    | 11 |

|    |         | 2.2.2    | Material budget and power constraints for the outer tracker     | 13 |

|    |         | 2.2.3    | Radiation levels                                                | 14 |

|    | 2.3     | Silico   | n particle detectors and technologies                           | 16 |

|    |         | 2.3.1    | Silicon detector principles                                     | 16 |

|    |         | 2.3.2    | Micro-strip and pixel detectors                                 | 18 |

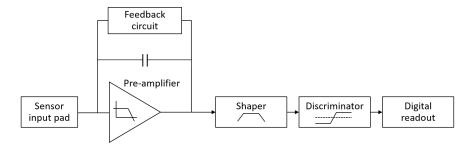

|    |         | 2.3.3    | Front-end electronics                                           | 19 |

|    |         | 2.3.4    | Readout systems                                                 | 21 |

|    | 2.4     | Radia    | tion effects on CMOS electronics                                | 23 |

|    |         | 2.4.1    | Cumulative effects: total ionizing dose and displacement damage | 24 |

|    |         | 2.4.2    | Single event effects                                            | 25 |

| 3  | Fro     | nt-End   | electronics for a novel particle tracker architecture           | 29 |

|    | 3.1     | Partic   | le tracking based on an intelligent pixel detector              | 31 |

|    | 3.2     | A new    | approach: The $p_T$ module concept                              | 32 |

|    | 3.3     | Requi    | rements and choice of the silicon sensor                        | 35 |

|    | 3.4     | The p    | $_{ m T}$ modules in the CMS outer tracker $$                   | 36 |

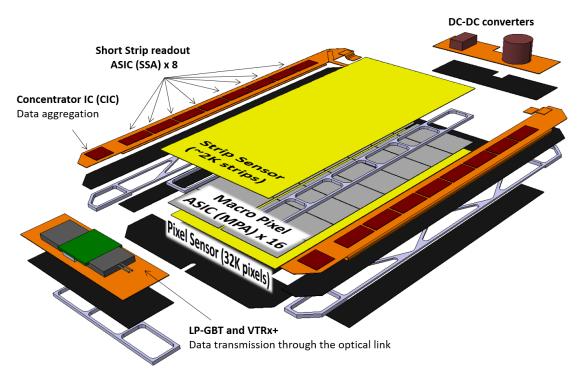

|    | 3.5     | The P    | ixel-Strip (PS) module design                                   | 39 |

#### **Contents**

|   | 3.6 | System | tem-level modeling                                                                     |           |  |

|---|-----|--------|----------------------------------------------------------------------------------------|-----------|--|

|   |     | 3.6.1  | Multi-chip system level simulation framework for architecture studies and verification |           |  |

|   |     |        | studies and verification                                                               |           |  |

|   |     | 3.6.2  | The framework implementation                                                           | 45        |  |

|   |     | 3.6.3  | Stimuli generation                                                                     | 47        |  |

|   |     |        | 3.6.3.1 Random particle event generation                                               | 48        |  |

|   |     |        | 3.6.3.2 The combinatorial stimuli generation                                           | 51        |  |

|   |     |        | 3.6.3.3 The Monte Carlo stimuli generation                                             | 52        |  |

|   |     |        | 3.6.3.4 Communication protocols and configuration                                      | 52        |  |

|   |     | 3.6.4  | Reference model                                                                        | 53        |  |

|   |     | 3.6.5  | Monitors, scoreboards and efficiency evaluation                                        | 54        |  |

|   |     | 3.6.6  | A test-cases library for functional verification                                       | 55        |  |

|   | 3.7 | Trigge | ered transmission of full sensor data                                                  | 56        |  |

|   |     | 3.7.1  | L1 data path architecture studies                                                      | 56        |  |

|   | 3.8 | Stub   | data path                                                                              | 60        |  |

|   |     | 3.8.1  | Stub-data bandwidth and efficiency studies across the detector                         | 62        |  |

|   |     | 3.8.2  | Clustering across neighbouring ASICs                                                   | 66        |  |

|   |     | 3.8.3  | Particle cluster filtering and coincidence window                                      |           |  |

|   | 3.9 | Descr  | ription of the final PS module architecture                                            | 70        |  |

|   | Б   | .1     |                                                                                        |           |  |

| 4 |     |        | studies to the design of the SSA ASIC                                                  | <b>75</b> |  |

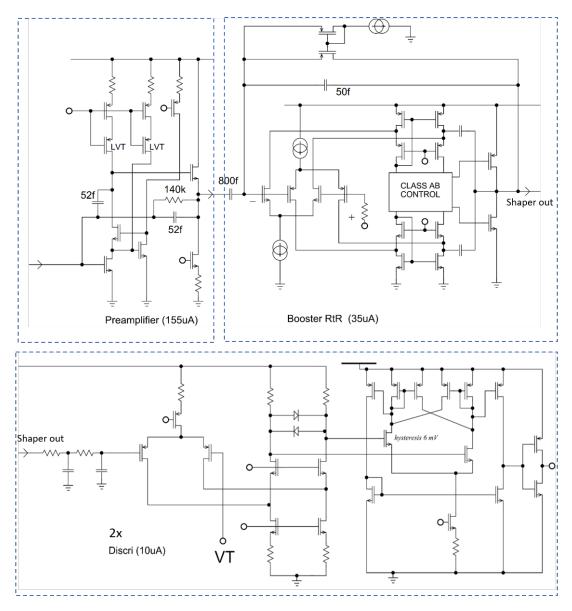

|   |     |        | nel analog front-end                                                                   | 77        |  |

|   | 4.2 |        | eles hit digitization                                                                  | 81        |  |

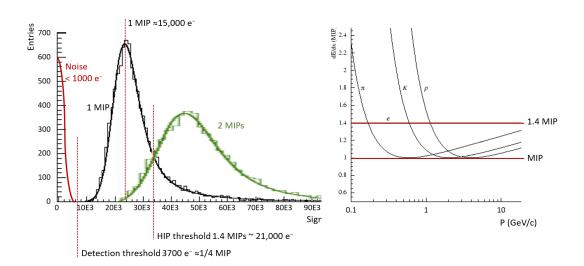

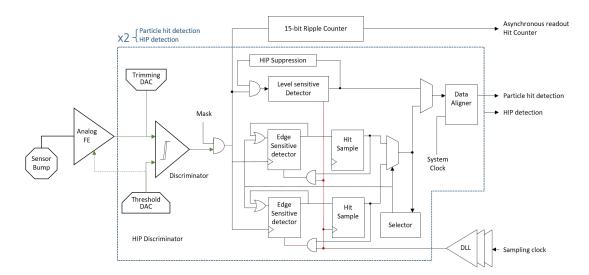

|   |     | 4.2.1  | A double discrimination for high energy particles detection                            | 81        |  |

|   |     | 4.2.2  | Digital channel front-end                                                              | 84        |  |

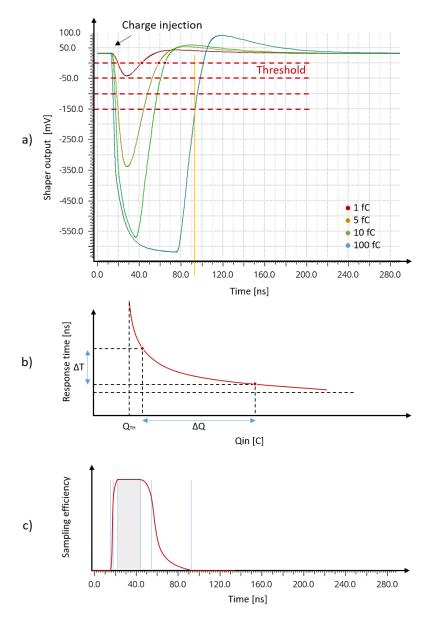

|   |     | 4.2.3  | Timewalk and clock de-skewing                                                          | 86        |  |

|   |     | 4.2.4  | Asynchronous readout and channel equalization                                          | 89        |  |

|   | 4.3 |        | nuous transmission of high- $p_T$ particle primitives                                  | 92        |  |

|   | 4.4 | Trigge | ered data readout                                                                      | 95        |  |

|   |     | 4.4.1  | Power optimization                                                                     | 95        |  |

|   |     | 4.4.2  | High ionizing particles flags                                                          | 99        |  |

| Αŀ | oout 1 | the aut | thor                                                       | 187 |

|----|--------|---------|------------------------------------------------------------|-----|

| Bi | bliog  | graphy  |                                                            | 165 |

| 6  | Sun    | nmary   | and conclusions                                            | 161 |

|    |        | 5.6.3   | Error rates evaluation                                     | 155 |

|    |        | 5.6.2   | Cross-section measurements                                 |     |

|    |        | 5.6.1   | SEU induced errors in control logic                        |     |

|    | 5.6    |         | e-event radiation effects studies                          |     |

|    |        |         | Effects on bias, analog front-end and noise performances   |     |

|    |        |         | Effects on digital circuits                                |     |

|    | 5.5    | Total   | ionizing dose results                                      | 144 |

|    | 5.4    |         | probing results and production yield                       |     |

|    | 5.3    | SSA-N   | MPA and SSA-SSA communication                              | 140 |

|    |        | 5.2.5   | Bias variations and threshold-DACs linearity               | 139 |

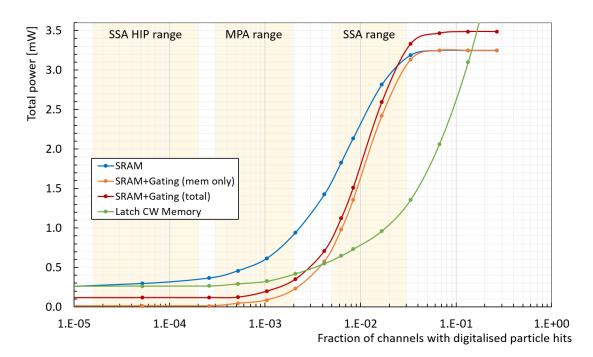

|    |        |         | tectable charge                                            | 137 |

|    |        | 5.2.4   | Threshold mismatch, channels equalization, and minimum de- |     |

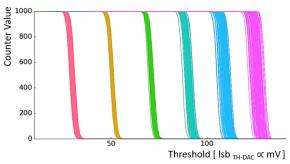

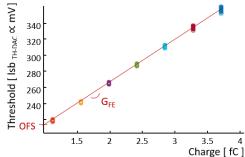

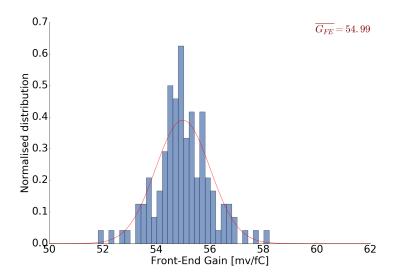

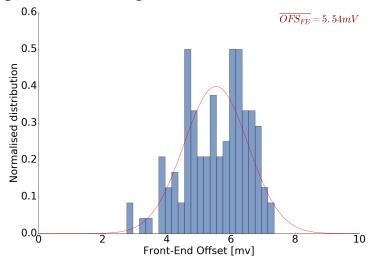

|    |        | 5.2.3   | Front-end gain indirect measurements and distribution      | 136 |

|    |        | 5.2.2   | Front-end noise studies                                    |     |

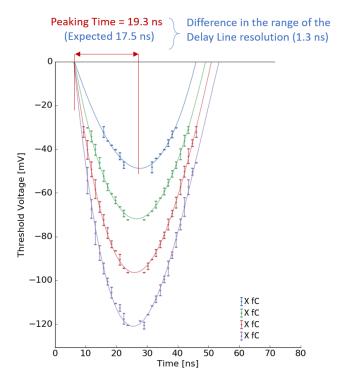

|    |        | 5.2.1   | Shaper pulse reconstruction                                | 133 |

|    | 5.2    |         | -end characterization                                      |     |

|    | 5.1    | A cust  | tom setup for prototype characterization                   | 129 |

| 5  | Exp    | erime   | ntal result on the silicon prototype                       | 127 |

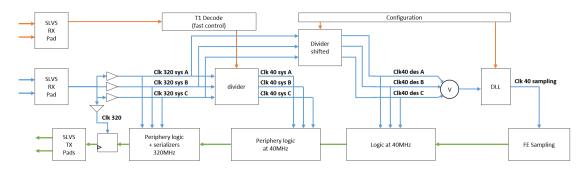

|    |        | 4.6.7   | Clock distribution and implementation flow                 | 124 |

|    |        | 4.6.6   | The flip-chip floorplan and the power distribution         |     |

|    |        | 4.6.5   | Single Event effect hardening                              |     |

|    |        | 4.6.4   | Timing corners for low-temperature and high-radiation      |     |

|    |        | 4.6.3   | Total Ionizing Dose tolerance                              |     |

|    |        | 4.6.2   | Supply voltage scaling and temperature inversion effect    |     |

|    |        | 4.6.1   | Choice of the technology                                   |     |

|    | 4.6    | ASIC    | implementation                                             |     |

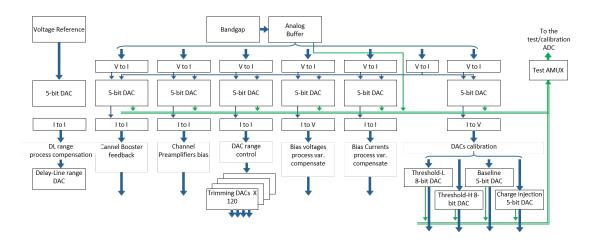

|    |        | 4.5.2   | Bias calibration                                           | 102 |

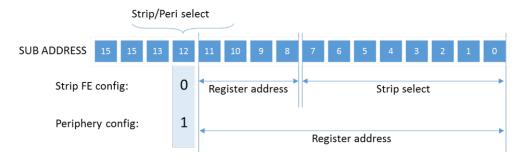

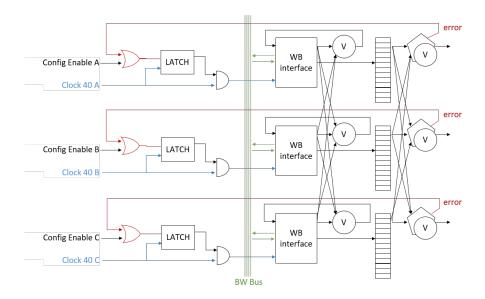

|    |        | 4.5.1   | Synchronous command and slow-control                       | 100 |

|    | 4.5    | Contr   | ol and calibration                                         | 100 |

|    |        |         |                                                            |     |

## **List of Figures**

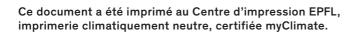

| 1.1  | The complex of the LHC accelerators                                              | 4  |

|------|----------------------------------------------------------------------------------|----|

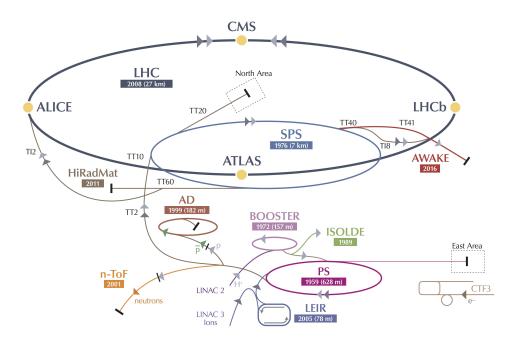

| 2.1  | CMS detector visualization                                                       | 8  |

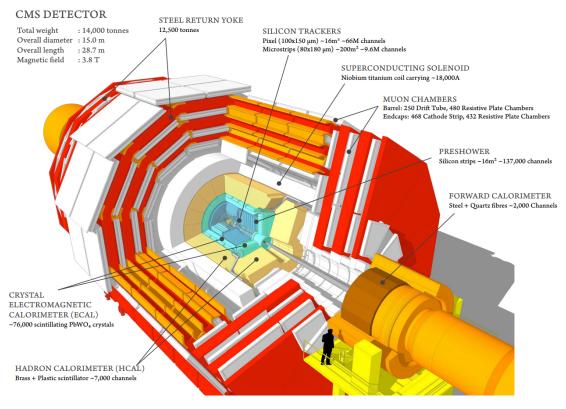

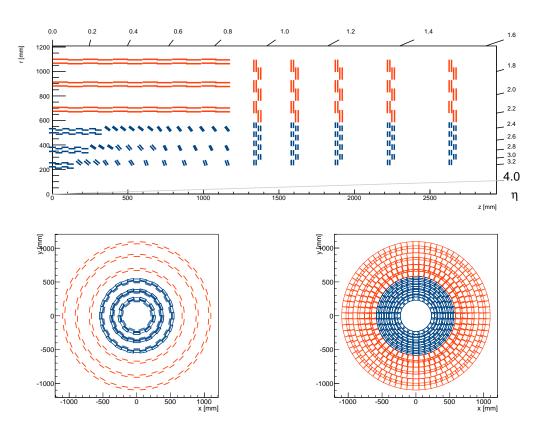

| 2.2  | Visualization of the CMS silicon tracker upgrade                                 | 11 |

| 2.3  | Material budget in the CMS detector                                              | 14 |

| 2.4  | Integrated 1 MeV neutron equivalent particle fluence                             | 15 |

| 2.5  | Total Ionizing Dose expected in the CMS tracker Phase-2 upgrade                  | 15 |

| 2.6  | Most probable energy loss in silicon, normalized to the mean loss of a MIP       | 17 |

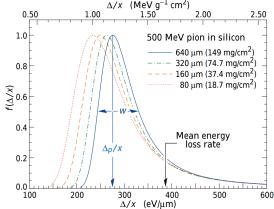

| 2.7  | Straggling functions in silicon for 500 MeV pions                                | 17 |

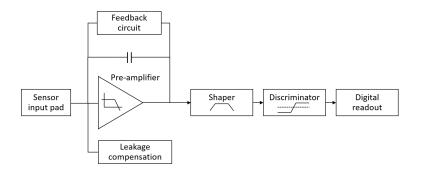

| 2.8  | Block diagram of a typical front-end circuit                                     | 20 |

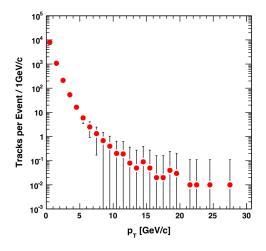

| 3.1  | $p_T$ spectrum of the average number of tracks per event                         | 34 |

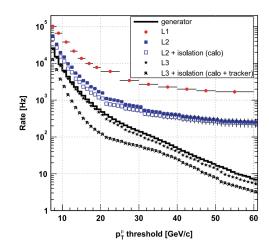

| 3.2  |                                                                                  | 34 |

| 3.3  |                                                                                  | 37 |

| 3.4  |                                                                                  | 40 |

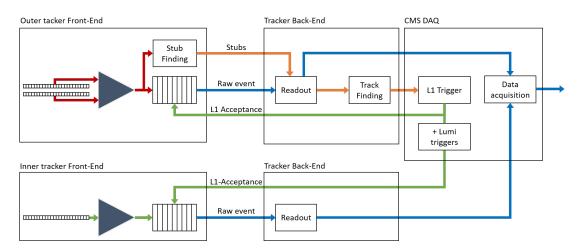

| 3.5  | Block diagram of the tracker readout chain                                       | 41 |

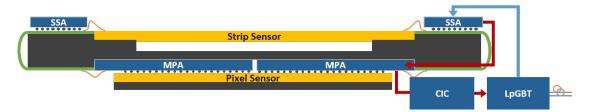

| 3.6  | Section of the PS module and chip-set data flow                                  | 41 |

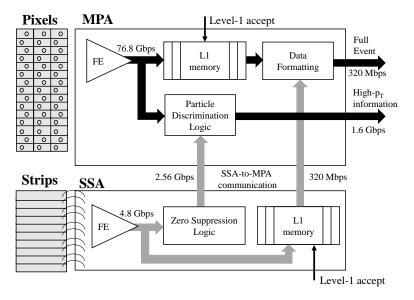

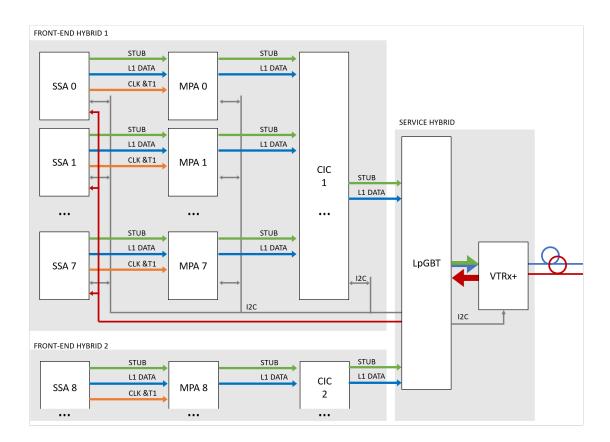

| 3.7  | Block diagram of the SSA and MPA communication                                   | 43 |

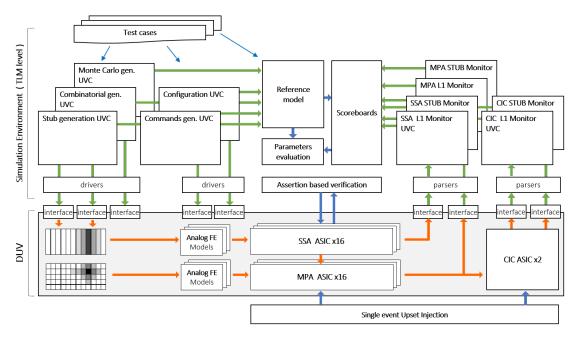

| 3.8  | Simulation framework for the CMS outer-tracker detector chain                    | 46 |

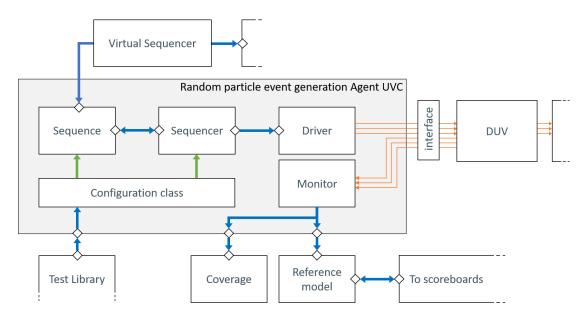

| 3.9  | Agent UVM Verification Component block diagram                                   | 48 |

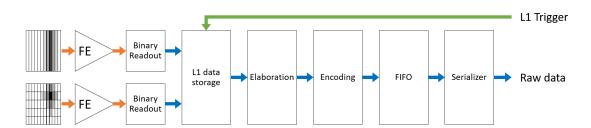

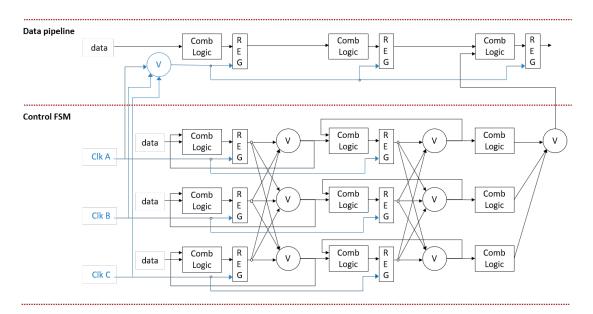

| 3.10 | Block diagram of the main steps for the triggered data path                      | 56 |

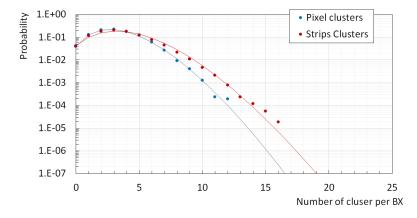

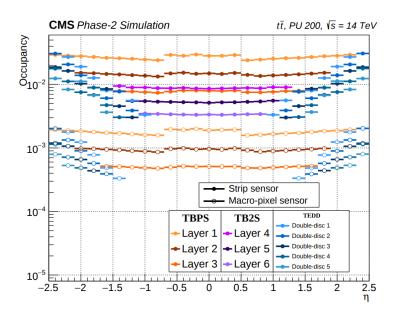

| 3.11 | Number of clusters probability for 200 PU Monte Carlo events                     | 57 |

| 3.12 | Hit occupancy as a function of $\eta$                                            | 58 |

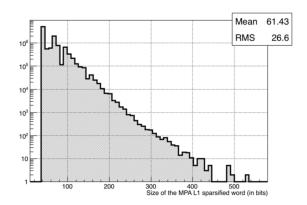

| 3.13 | Size of the MPA L1 sparsified words, for pileup 200 events                       | 59 |

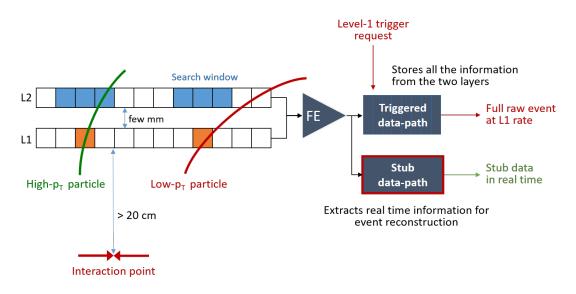

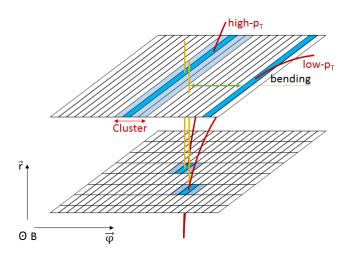

| 3.14 | Example of the PS module track bending discrimination                            | 61 |

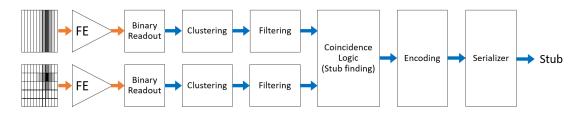

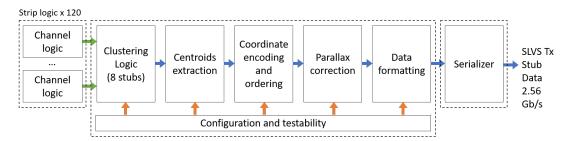

| 3.15 | Block diagram of the necessary steps for the Stub data path                      | 61 |

| 3.16 | Probability of $> n$ stubs in 1 BX, probability of $> n$ stubs in 2 BX at PU 200 | 63 |

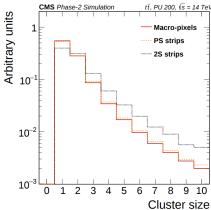

| 3.17 | Charge deposition cluster size distribution for the pixel and strip sensors      | 63 |

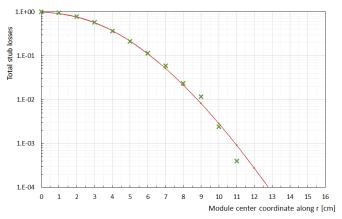

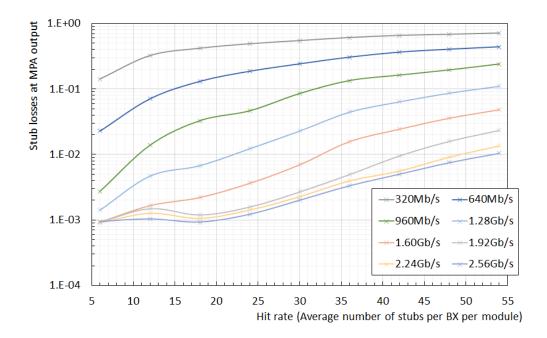

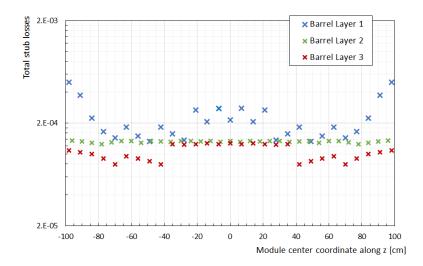

| 3.18 | Average stub losses at the MPA output                                            | 64 |

| 3.19 | Expected stub losses as a function of the modules' $z$ positions                 | 65 |

#### **List of Figures**

| 3.20 | D Expected stub losses as a function of the modules' $r$ positions $\ldots$                   | 65  |

|------|-----------------------------------------------------------------------------------------------|-----|

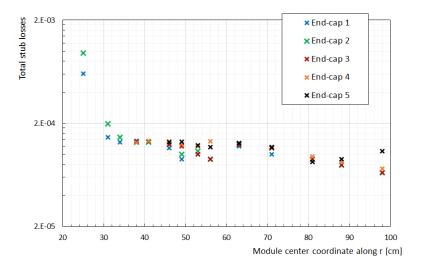

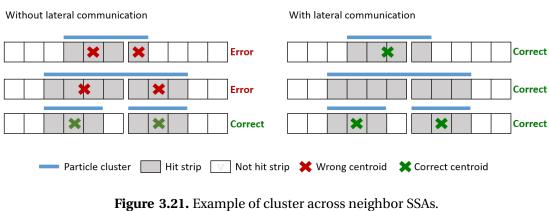

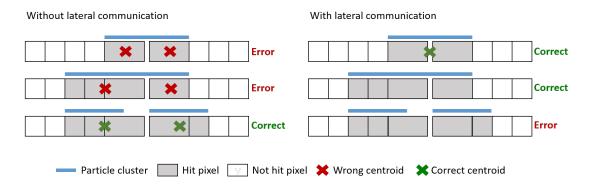

| 3.2  | 1 Example of cluster across neighbor SSAs                                                     | 67  |

| 3.22 | 2 Example of cluster across neighbor MPAs                                                     | 67  |

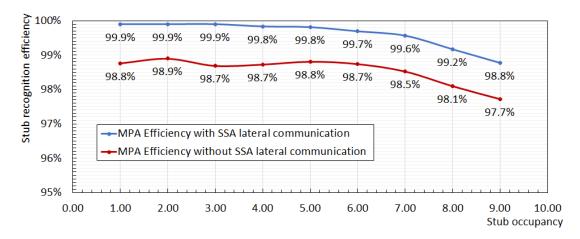

| 3.23 | 3 SSA lateral communication effect on stub recognition efficiency                             | 68  |

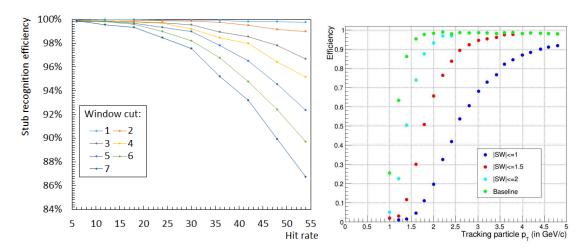

| 3.24 | 4 Stub recognition efficiency for different stub window cuts                                  | 69  |

| 3.25 | 5 Stub efficiency for multiple SW cuts in TIB1                                                | 69  |

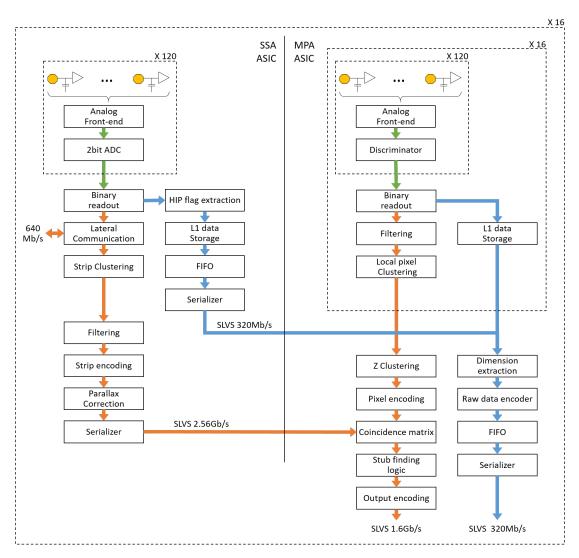

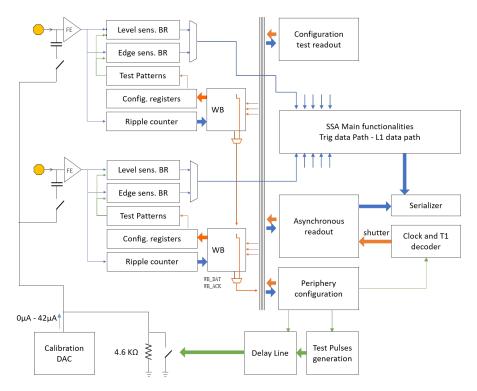

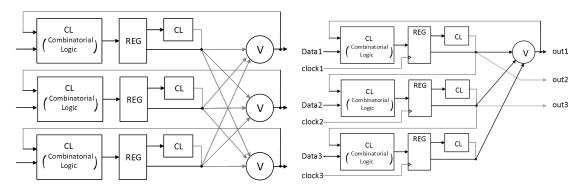

| 3.26 | 6 Block diagram of the PS module final architecture                                           | 71  |

| 3.27 | 7 PS module final implementation diagram                                                      | 72  |

| 3.28 | 3 3D rendering of the PS module                                                               | 73  |

| 4.1  | SSA analog front-end block diagram                                                            | 77  |

| 4.2  | SSA analog front-end schematic                                                                | 78  |

| 4.3  | Signal distribution in $e^-$ for 1 MIP $p_T$ and 2 MIP $p_T. \ \ldots \ \ldots \ \ldots$      | 82  |

| 4.4  | Most probable energy loss as a function of the particle energy                                | 82  |

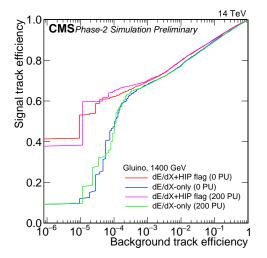

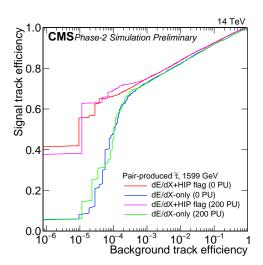

| 4.5  | Performance of the dE/dx discrimination for $\tilde{g}$ and $\tilde{\tau}$ with SSA HIP flags | 83  |

| 4.6  | Block diagram of the SSA channel digital front-end                                            | 85  |

| 4.7  | Shaper pulse simulation and hit sampling efficiency                                           | 88  |

| 4.8  | Block diagram of the calibration and asynchronous readout path                                | 90  |

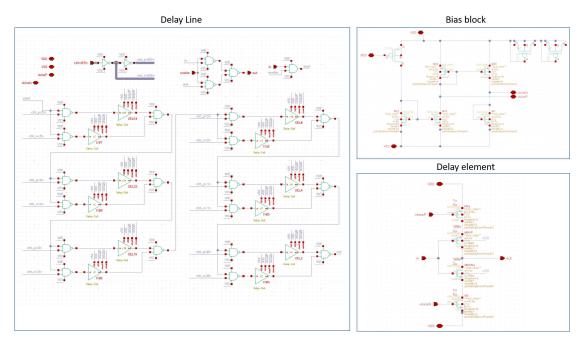

| 4.9  | Calibration pulse injection control Delay Line                                                | 91  |

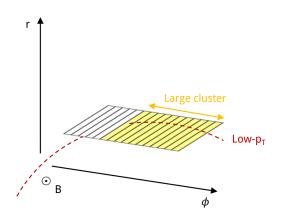

| 4.10 | D Example of a large cluster caused by low- $p_T$ particles                                   | 92  |

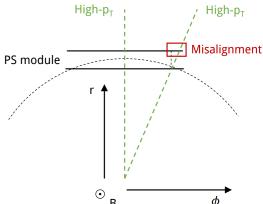

| 4.1  | 1 Parallax error for SSA sensor                                                               | 92  |

| 4.12 | 2 Block diagram of the SSA Stub data path                                                     | 94  |

| 4.13 | 3 Memory power consumption as a function of the occupancy                                     | 98  |

| 4.14 | 4 List of the event-synchronous control commands                                              | 101 |

| 4.15 | 5 Slow-control interface sub-addressing scheme                                                | 102 |

| 4.16 | Block diagram of the biasing and calibration block                                            | 103 |

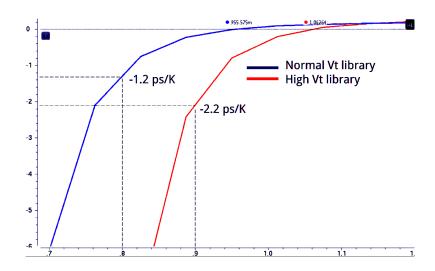

| 4.17 | 7 Temperature coefficient and inversion effect                                                | 106 |

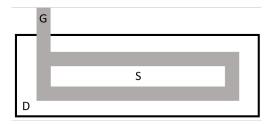

| 4.18 | B Example of Enclosed Layout Transistor (ELT)                                                 | 108 |

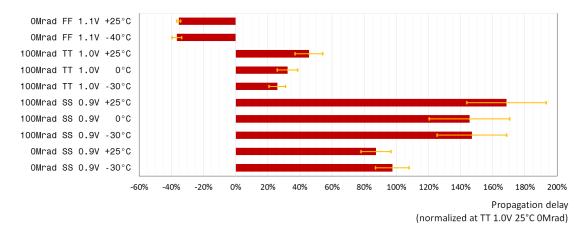

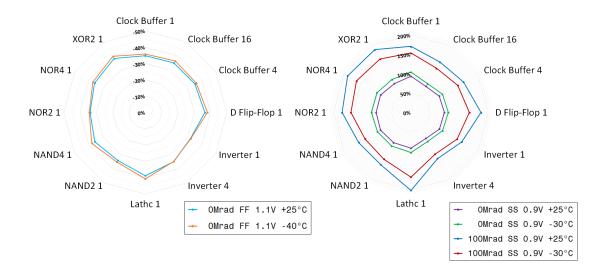

| 4.19 | Propagation delay comparison between multiple corners                                         | 110 |

| 4.20 | O Propagation delay comparison between different corners                                      | 110 |

| 4.2  | 1 Summary of the PVT+Rad timing corners                                                       | 111 |

| 4.22 | 2 Triple module redundancy implementation in the SSA                                          | 114 |

| 4.23 | 3 Comparison between triple module redundancy implementations                                 | 115 |

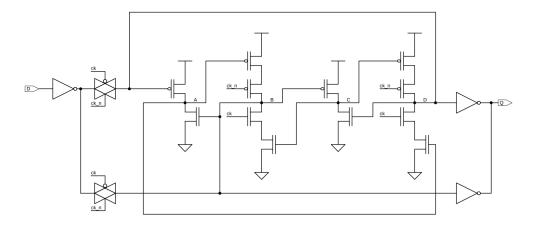

| 4.24 | 4 Dual-interlocked (DICE) latch                                                               | 117 |

| 4.25 | 5 Triple module redundancy with self-refresh feedback                                         | 118 |

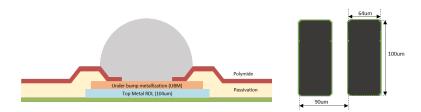

| 4.26 | 6 Implementation of the C4 Bump and wire-bond metallizations                                  | 121 |

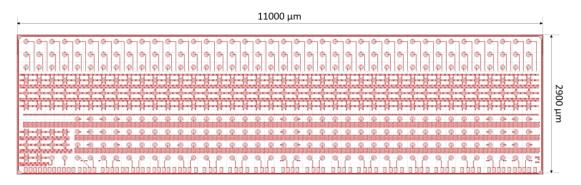

| 4.27 | 7 View of the final SSA ASIC top-metal layer                                                  | 122 |

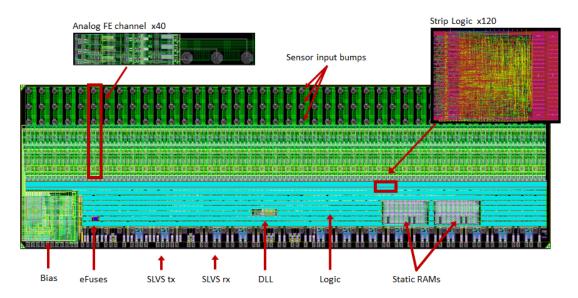

| 4.28 | B Final layout of the SSA ASIC                                                                | 122 |

| 4.29 SSA clock distribution                                                            | <br>124 |

|----------------------------------------------------------------------------------------|---------|

| 4.30 Dynamic IR drop analysis                                                          | <br>125 |

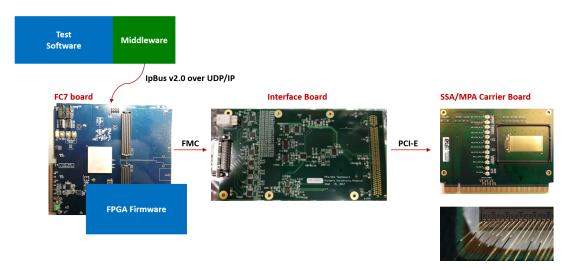

| 5.1 Hardware diagram of the SSA test system                                            | 129     |

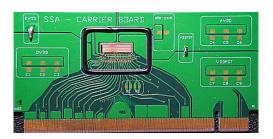

| 5.2 Custom carrier board designed for SSA characterization                             | 130     |

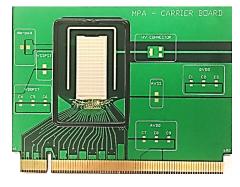

| 5.3 Custom carrier board designed for MPA characterization                             | 130     |

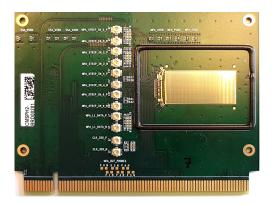

| 5.4 Custom carrier board for SSA-MPA communication studies .                           | 130     |

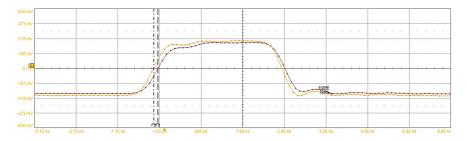

| 5.5 Shaper output signal reconstruction for different input charge                     | 134     |

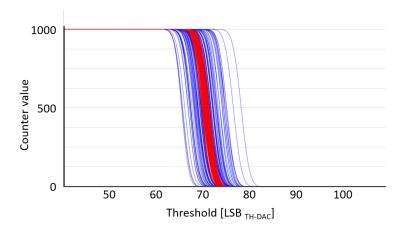

| 5.6 Complementary error function fitting the measures S-Curves                         | 135     |

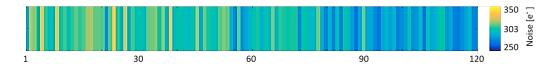

| 5.7 Front-End noise map across the SSA                                                 | 136     |

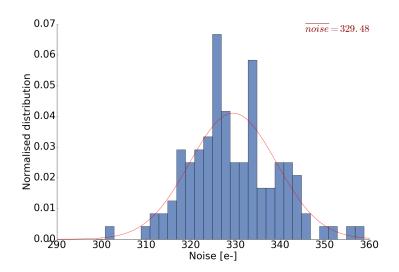

| 5.8 On-Chip distribution of the FE channel noise                                       | 136     |

| 5.9 S-curves measured for different values of input charges                            | 137     |

| 5.10 Front-End Gain and Offset measurement                                             | 137     |

| 5.11 Front-end gain distribution for a non-trimmed SSA                                 | 138     |

| 5.12 Front-end Offset distribution for a non-trimmed SSA                               | 138     |

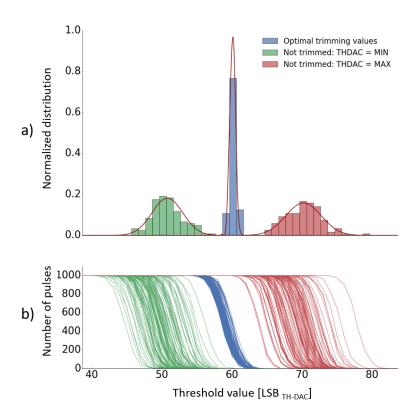

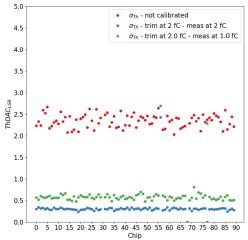

| 5.13 On-chip distribution and trimming of the channel effective the                    | 139     |

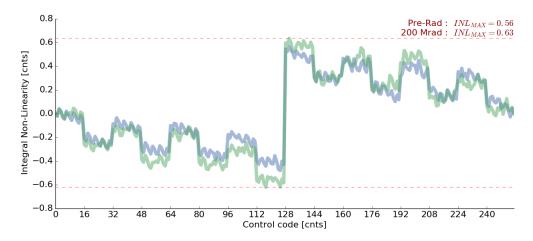

| 5.14 Threshold DAC integral non-linearity                                              | 140     |

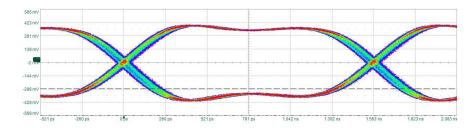

| 5.15 Eye diagram of the stub data-line                                                 | 141     |

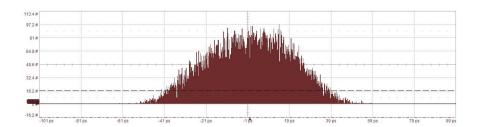

| 5.16 Jitter histogram measured on the stub data-line                                   | 141     |

| 5.17 Phase difference measured between the stub-data lines                             | 141     |

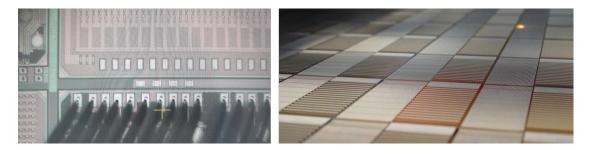

| 5.18 Microscope photo of the SSA wafer probing                                         | 142     |

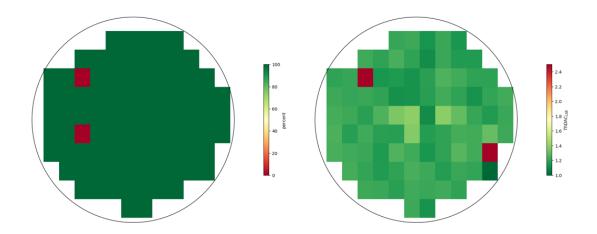

| 5.19 Digital functionalities test-results wafer map                                    | 143     |

| 5.20 Average analog front-end noise wafer map                                          | 143     |

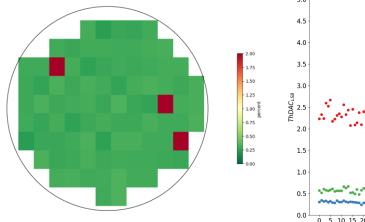

| 5.21 Wafer map of the achievable threshold standard deviation                          | 143     |

| 5.22 Average value of the particle-hit detection threshold                             | 143     |

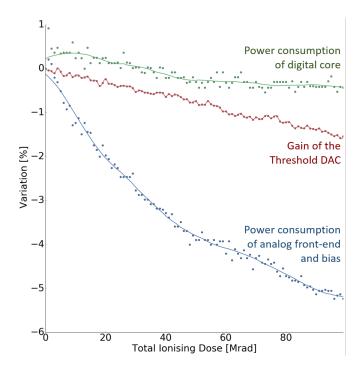

| 5.23 Variation of power consumption and Th-DAC Gain respect to                         | 145     |

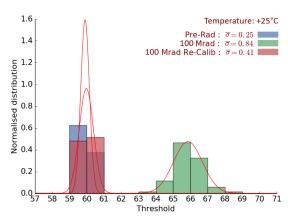

| 5.24 Distribution of the channel threshold after irradiating at +25°C                  | 146     |

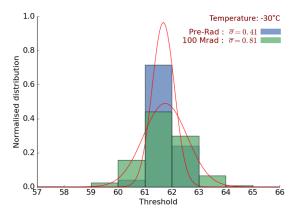

| 5.25 Distribution of the channel threshold after irradiating at -30°C                  | 146     |

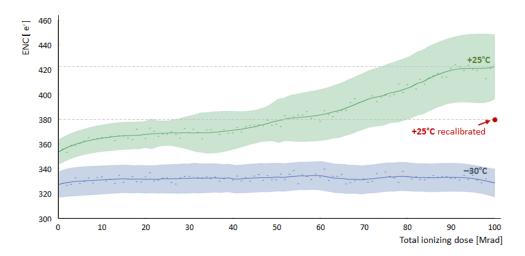

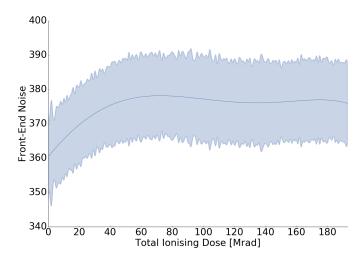

| 5.26 Front-End ENC respect to the total dose at $+25^{\circ}$ C and at $-30^{\circ}$ C | 147     |

| 5.27 Front-End ENC distributions pre-rad and at 100 Mrad (+25°C)                       | 147     |

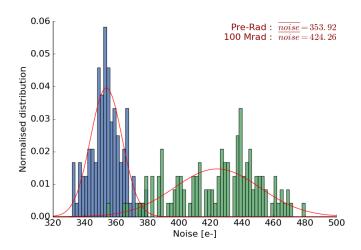

| 5.28 ENC degradation with TID at +25°C 200 Mrad calibrated SSA                         | 148     |

| 5.29 Properties of the heavy ions for SSA test                                         | <br>149 |

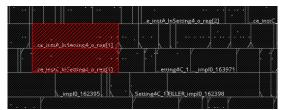

| 5.30 SEU-weak configuration register placement                                         | <br>151 |

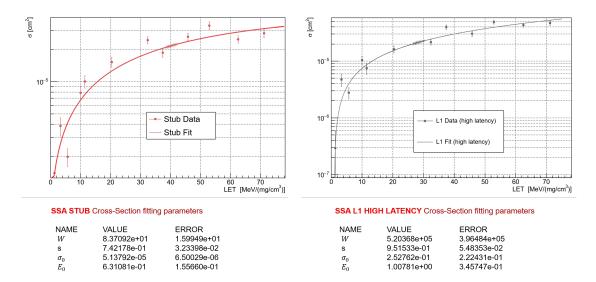

| 5.31 Cross-section as function of LET for the SSA stub data                            | <br>153 |

| 5.32 Cross-section as function of LET for SSA L1 data                                  | <br>153 |

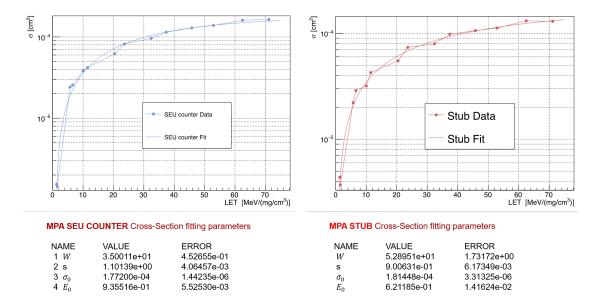

| 5.33 Cross-section as function of LET for the MPA stub data                            | 154     |

| 5.34 Cross-section as function of the LET for MPA SEU counter                          | <br>154 |

| 5.35 Cross-section as function of LET for the MPA L1 1.0µs latency                     | <br>154 |

#### **List of Figures**

| 5.36 | Cross-section as function of LET for the MPA L1 12.6 $\mu$ s latency         | 154 |

|------|------------------------------------------------------------------------------|-----|

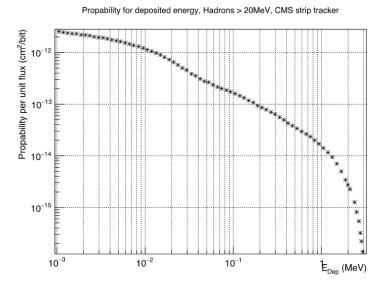

| 5.37 | Hadrons>20 MeV energy deposition prob. distr. for CMS spectrum               | 157 |

| 5.38 | MPA and SSA SEU cross-section                                                | 157 |

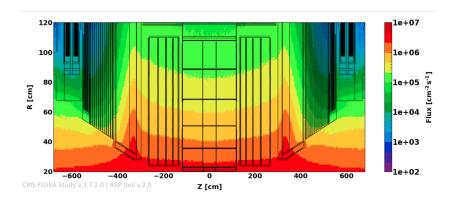

| 5.39 | r- $z$ flux map for Hadrons E>20 MeV in the CMS tracker 7 TeV p-p event      | 158 |

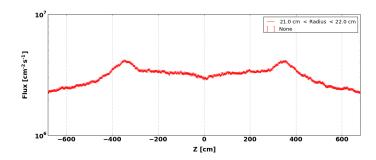

| 5.40 | Flux for hadrons with E>20 MeV in the CMS tracker as function of Z $$ . $$ . | 158 |

| 5.41 | PS module expected error rates for the tracker spectrum                      | 159 |

| 5.42 | Maximum SEU error rates expected at the PS-module output                     | 160 |

## Glossary and acronyms

**2S module** p<sub>T</sub>-module composed by two sensor readout ASIC of the CMS outer silicon-strip detectors, 3.4

5.2

5.5-5.6, 6.0

barrel Concentric cylindrical layers cen- CML Current Mode Logic tered in the in the nominal interaction **CMOS** Complementary Metal Oxide Semipoint and located in the CMS tracker at conductor, 1.0, 2.3, 4.6  $20 \,\mathrm{cm} < r < 120 \,\mathrm{cm}$ , 2.2, 3.4, 3.8, 4.4

LHC, the BX rate is 40 MHz., 1.0, 2.1, 2.3, 3.2, 3.6, 4.2–4.3, 4.6, 5.0–5.1, 5.5–5.6 3.2, 3.8

**BX-ID** Data

method for interconnecting semiconduc- 5.6 tor devices with solder bumps deposited CSA Charge Sensitive Amplifier in the die area, 2.3, 3.5, 4.5-4.6

**CAD** Computer-aided design. It reprephysical implementation flow, 4.6 sents software that aim to aid in the cre- **D19C** Firmware project that aimed to proation, modification, analysis, or optimiza- vide DAQ system for the CMS Phase 2 tion of a design

tracker 2S-module

**ADC** Analog to Digital Converter, 4.5, 5.1- **CIC** Concentrator Integrated Circuit. It is the data concentrator ASIC of the CMS ASIC Application Specific Integrated Cir- Outer Tracker PS and 2S modules for the cuit, 2.0, 2.2–2.4, 3.0–3.9, 4.0–4.6, 5.0–5.3, phase-2 upgrade, 3.5–3.6, 3.8–3.9, 4.2, 4.5, 5.6

CMS Compact Muon Solenoid detector. It **BX** The instant at which the particles is a general-purpose detector at the Large bunch are brought into collision. In the Hadron Collider (LHC) 0.0, 1.0, 2.1–2.2,

**CMSSW** CMS Software components, 3.7 Bunch Crossing Identification **cross-section** The section normal to the beam direction outside of that the particle C4 Controlled Collapse Chip Connection, is not deflected. It can be considered as also known as Flip-Chip technology, is a a measure of the interaction probability,

**CTS** Clock Tree Synthesis, it is a step of the

tracker upgrade, 5.1

**CBC** CMS Binary Chip (CIC). Is the strip **DAC** Digital to Analog Converter, 4.1–4.2,

4.5, 5.1–5.2, 5.5 FIFO First In First Out circuit element **DAQ** Data AcQuisition system, 2.2–2.3, **FPGA** Field Programmable Gate Array, 4.2 3.2, 4.2, 5.1 DD Displacement Damage, 2.4 **HCAL** Hadron Calorimeter of the CMS experiment, 2.1 DL Delay Line, 4.2 **DLL** Delay-Locked Loop. Similar to a PLL **HEP** High Energy Physics, 1.0, 2.3–2.4, 3.6, where the internal voltage-controlled os- 4.6 cillator is replaced by a delay line, 4.2 **high-p**<sub>T</sub> high transverse momentum (p<sub>T</sub>) DRV Design Rule Violation, 4.6 particle. In this context it refers to particles with  $p_T > 2 \text{ GeV}/c$ , 3.2, 3.5–3.6, 3.8–3.9, **DTC** Data Trigger and Control system of the CMS detector, 5.1 4.3 **HIP** High Ionizing Particle. In this context **DUT** Device under Test **DUV** Design Under Verification, 3.6 it refers to particles with an energy deposition in silicon greater than 1.4 times the **ECAL** Electromagnetic Calorimeter of the average energy deposited by a MIP, 3.6-CMS experiment, 2.1 3.7, 3.9, 4.2, 4.4 **ECC** Error Correction Code EDA Electronic Design Automation, also **HL-LHC** High Luminosity Large Hadron referred to as electronic computer-aided Collider, 1.0, 2.1–2.2, 3.3, 3.6, 4.2, 5.0 design (ECAD), 3.6 **HLT** High Level Trigger system **E**<sub>**DEP**</sub> Deposited ionizing energy **HPD** Hybrid Pixel Detector, 2.3 ELT Enclosed Layout Transistor. It is a lay- HV High Voltage biasing out technique to reduce the leakage cur- **Infinite loop** i.e. link to page xvi. rent increase due to the charge trapped in **INL** Integral Non-Linearity, 4.2, 5.2 the STIs for devices exposed to ionizing integrated luminosity The integrated luradiation, 4.6, 5.5 minosity over the operation time  $\mathcal{L}$  de-**ENC** Equivalent Noise Charge , 5.2, 5.5 fines the total amount of data recorded by **end-cap** Parallel disks centered in the in an experiment, 1.0 the z located in the CMS tracker at z >IP Interaction Point or Intellectual propri-130 cm, 2.2, 3.4, 3.8, 4.4 ety (according to the context) **ESD** Electro-Static Discharge **IPbus** A flexible Ethernet-based control FC7 flexible, µTCA compatible Advanced system for xTCA hardware, 5.1 Mezzanine Card (AMC) for generic data L1 Level-1 trigger system (hardware trigacquisition/control applications, 5.1 ger) of the CMS detector, 2.2, 3.1-3.2, 3.5-**FE** Front-End, 3.5–3.6, 3.9, 5.2 3.6.3.9 **FEA** Finite Element Analysis L1 data Raw sensor image transmitted only when required by a L1 trigger

data processing, 2.2, 3.7

L1 rate Average occurrence frequency of expected to recognize, 2.2 the CMS Level-1 trigger request

**LDD** Light Doped Drain

of energy that an ionizing particle transfers to the material traversed per unit dis- Monte Carlo A broad class of computatance, 4.4, 4.6, 5.6, 6.0

Level-1 trigger system (hardware trigger) of the CMS detector, 4.4, 4.6

**LHC** Large Hadron Collider, 1.0, 2.2, 3.5– 3.6, 4.5, 5.6, 6.0

**low-p**<sub>T</sub> Low transverse momentum  $(p_T)$ cles with  $p_T < 2 \text{ GeV}/c$ , 3.2, 3.5–3.6, 3.8–3.9, 4.6, 5.1, 5.3, 5.5–5.6, 6.0 4.3

LS3 Third long shutdown of the CMS detector to allow the upgrade operations

LSB Least Significant Bit

**luminosity** The events rate occurrence in a particle interaction is defined as  $\frac{dN}{dt}$  =  $\sigma\ell$ , where  $\ell$  represents the instantaneous number of interactions per second, called luminosity while  $\sigma$  represents the cross- 5.5–5.6, 6.0 section of the interaction, 1.0

**LV** Low Voltage powering

macro-pixel pixel with high aspect ratio Phase-2 Upgrade CMS detector upgrade (i.e in the PS module is  $100 \times 1467 \,\mu\text{m}$ ), 3.4 MaPSA Macro Pixel Sub-Assembly, it represents the C4 assembly of 16 MPA ASICs

over a single pixel sensor, 3.5

L1 latency latency between the transmis- material budget the quantity of matesion of a trigger request and the cor- rial in the tracker volume, that introresponding event occurrence. It correduces a limiting factor for the detection sponds to the time available for the L1 ratios of particles that may interact with it and compromise what the detector is

> MIP Minimum Ionizing Particle, 2.3, 4.2, 4.4

**LET** Linear Energy Transfer. The amount **MMMC** Multi-Mode Multi-Corner analysis, 4.6

> tional algorithms that rely on repeated random sampling to obtain numerical results, 3.6–3.8, 4.3–4.4

MOS Metal Oxide Semiconductor, 2.4 MPA Macro Pixel ASIC (MPA. Is the pixelsensor readout ASIC of the CMS outer particle. In this context it refers to partitracker PS-module 0.0, 3.0, 3.5–3.9, 4.0–

> MPA-Light Small scale, limited functionality prototype of the MPA ASIC, 5.5

MPW Multi Project Wafer, 4.6

nMOS n-channel Metal Oxide Semiconductor (MOS) device, 4.1, 4.4, 4.6

outer-tracker CMS tracker barrel layers and end-cap disk located at  $r > 200 \,\mathrm{mm}$ , 2.0, 2.2, 2.4, 3.2–3.6, 4.0, 4.2–4.4, 4.6, 5.1,

**PCB** Printed Circuit Board, 3.5, 4.6, 5.1, 5.3

during HL-LHC LS3, 2.1

**pileup** in HEP experiments it represents the average amount of overlapped signals in the event reconstruction 0.0, 2.1–2.2, interpretation of timing data for use at any 3.0-3.1, 3.6-3.8, 4.2

tem that generates an output signal whose phase is related to the phase of an input signal, 5.1

ductor (MOS) device, 4.1, 4.4, 4.6

p-p Proton-proton collision, 5.6

pseudorapidity Kinematical variable of node in a micro-electronic device, 4.6 a relativistic particle defined as  $\eta =$  $-\ln \tan \frac{\theta}{2}$ , where  $\theta$  is the particle zenith angle referenced to the direction of the crossing beams, 2.1

**PS module** p<sub>T</sub>-module that combines a silicon micro-strip sensor with a siliconpixel sensor, 3.4–3.9, 4.0, 4.3, 4.6, 5.1, 5.5– 5.6

**PSP** Power Skew Product

3.2, 3.4–3.6, 3.8, 4.2–4.3

pable to provide transverse momentum measurements, 3.2, 3.4–3.5

**Python** An interpreted, high-level, general-purpose programming language RDL Re-Distribution Layer, 4.6

RTL Register Transfer Level. It is a design abstraction which models a synchronous digital circuit in terms of the flow of digital signals (data) between hardware registers, and the logical operations performed on those signals, 3.6, 4.6

IEEE standard for the representation and

stage of an electronic design process, 4.6 PLL Phase-Locked Loop. It is a control sys- SEE Single Event Effect. Effects caused by one single ionizing particle striking a sensitive node in a micro-electronic device, 2.4

pMOS p-channel Metal Oxide Semicon- SET Single Event Transient. Time limited change of logical state caused by one single ionizing particle striking a sensitive

> SEU Single Event Upset. Change of logical state caused by one single ionizing particle striking a sensitive node in a microelectronic device, 2.4, 4.4-4.6, 5.6, 6.0

> **SLVS** Scalable Low Voltage Signaling. It is a differential signal transmission standard , 3.7–3.9, 4.6, 5.1, 5.3

**SM** Standard Model in particle physics is the theory describing three of the four p<sub>T</sub> Particle transverse momentum 0.0, 2.1, known fundamental forces (electromagnetic, weak, and strong interactions, and **p**<sub>T</sub>-module Silicon detectors modules ca- not including the gravitational force) and classifying the known elementary particles, 1.0

> **SNM** Signal to Noise Margin, 4.6 **SOI** Silicon On Insulator technology, 4.6

**SSA** Short Strip ASIC (SSA). Is the microstrip-sensor readout ASIC of the CMS outer tracker PS-module, 1.0, 3.0, 3.5–3.9,

4.0-4.6, 5.0-5.3, 5.5-5.6, 6.0

**SST** Silicon Strip Tracker

**STI** Shallow Trench Isolation. Isolation which prevents electric current leakage **SDF** Standard Delay Format (SDF) is an between adjacent semiconductor devices , 2.4, 4.6

**strip** Detectors obtained by segmenting 4.2 the doped side into strips over the full length of the detector, 1.0, 3.4

stub High-p<sub>T</sub> particles primitives transmitted by p<sub>T</sub>-modules, 3.2, 3.4-3.6, 3.8-3.9, 4.3, 5.3, 5.6

SystemVerilog IEEE 1800 standard hardware description and verification language used to model, design and simulate electronic systems, 3.6

TCL Tool Command Language. It is a high-level, general-purpose, interpreted, dynamic programming language, 4.6

TID Total Ionizing Dose, The cumulative damage of the semiconductor lattice caused by ionizing radiation over the exposition time, 2.2, 4.4, 4.6, 5.5

timewalk The difference in time between charge injection at a FE input and its detection, 3.6, 4.2

time-walk Time dispersion of a discriminated pulse due to the combined effect of the pulse heights spread and the single threshold discrimination

**TLM** Transaction Level Modeling abstraction, 3.6

TMR Triple Modular Redundancy. Circuit technique to increase tolerance to radiation related single-event effects, 4.6

**ToA** Time of Arrival of a particle, 2.3, 3.6, V<sub>T</sub> Threshold voltage, 4.4, 4.6

**ToF** Time of Flight, in this context it refers to the particles time required to reach the silicon detector, 4.2

ToT Time over Threshold method to determine the amplitude of an analog signal. The signal is compared to a threshold and the duration of the output pulse is measured, 2.3, 4.2

tracker CMS sub-detector that allows reconstructing the particle trajectory and transverse momentum p<sub>T</sub> in the 3.8T magnetic field provided by the superconducting solenoid, 2.1-2.3, 3.0-3.6, 3.8-3.9, 4.2-4.4, 4.6, 5.0-5.1, 5.5-5.6

**UBM** Under Bump Metalization

**UVC** Universal Verification Methodology Verification Component, 3.6

**UVM** The Universal Verification Methodology is a standardized methodology for verifying integrated circuit designs, 3.6

**VCD** Value Change Dump

Verilog IEEE 1364 standard hardware description language (HDL) used to model electronic systems

**Verilog-AMS** It is a derivative of Verilog HDL language that includes analog and mixed-signal extensions (AMS), 3.6

### 1 Introduction

High energy physics (HEP) explores the nature of the particles that constitute matter and their mutual interactions. Particles, or related decay products, can be observed by their interactions with detectors capable of producing measurable signals. The history of particle detectors started more than a century ago. In the early days of particle physics, scintillation screens and photographic films allowed for the study of radioactivity. The "detection system" was the physicist eye [23]. Since that time, different technologies have been leading to essential steps in the particle physics field. The advent of the cloud chambers, invented by C. T. Wilson in the 1911 [24], made particle tracks directly visible and led to the discovery of the positron in 1932 [25] and of the K meson in the 1947 [26]. In the cloud chamber, when an energetic charged particle interacts with the supersaturated vapor, it results in a trail of ionized-gas particles that acts as a condensation center. The droplets are visible as "clouds" for several seconds.

A modified version of the cloud chamber, the bubble chamber, was developed by Donald A. Glaser in the 1952 [27]. As particles enter the chamber, a piston suddenly decreases its pressure, and the liquid enters into a superheated, metastable phase. At the passage of charged particles, the liquid vaporizes along with the ionizing track generating visible bubbles which density is proportional to the energy loss. The applied magnetic field imposes charged particles to travel along helical paths allowing for momentum measurements. A set of cameras allows capturing the particle trajectories. While some of the early prototypes were filled with beer [28], the CERN bubble chamber detector Gargamelle (1970-1979), filled with heavy-liquid and operating initially with a muon-neutrino beam produced by the Proton-Synchrotron and lately by the

#### Chapter 1. Introduction

Super Proton Synchrotron (SPS), leaded to the discovery of weak neutral currents in the 1973 [29]. The largest and last bubble chamber build (the BEBC), with its 3000km of developed and analyzed photo-film [30], enabled the discovery of D-mesons [31].

The first electronic detectors appeared much earlier with the Geiger-Müller tube [32] that uses the Townsend avalanche phenomenon to produce a readily detectable electric pulse triggered by a charge particle ionization. Only later, the scintillation counters started to be used together with photo-multiplier tubes (PMT), providing higher sensitivity [33]. After the introduction of Multi-Wire Proportional chambers (MWPC) in the 1968 [34] (proportional counter capable of providing positional information on particle trajectory) and successively of the Drift Chambers in the 1971 [35], electronic detectors started to feature increased *resolution*, finer *granularity*, and faster data read-out [36]. The possibility of reading out *electric signals* from particle detection that allows the usage of *computerized analysis* systems, defined the end of the bubble chamber era.

During the seventies appeared the Time Projection Chamber (TPC), a type of particle detector that utilizes a sensitive volume of gas or liquid to perform a three-dimensional reconstruction of particle trajectories. It found the primary application in the PEP-4 detector at SLAC [37]. More recent developments led to the micro-pattern gas detectors as MicroMegas [38] that utilizes metallic micro-meshes and GEMs (Gas Electron Multipliers) [39]. The latter has been used in many types of particle physics experiments starting from the Compass [40] experiment at CERN, in sub-detectors of today experiments and even in hadron therapy and radiotherapy [41].

Towards the end of the seventies, the possibility of using *semiconductor devices* as high precision tracking detectors started to emerge, representing a third major detector typology [36]. The first *micro-strip* silicon detector was published by the Pisa group [42] involved in charm quark production studies at CERN's SPS [43] accelerator. NA11/NA32 experiment at CERN build the first operational silicon-strip detector in 1983 [44] for tracking and vertex measurements.

The spatial resolution in the  $\mu$ m-range, the introduction of planar technology and the readout speed that allow measuring short-living particles, gave a strong impulse to the research on silicon strip detectors. The final boost to this technology arrived with the possibility to integrate electronic readout circuits and even dedicated readout ASICs

within the detector [45]. Micro-strip and pixel detectors represent today the leading technology for particles tracking. Particle detectors designed for modern accelerators often combine several technologies and complex readout and analysis systems.

The European Organization for Nuclear Research (CERN) was created in 1954 as a unified effort of European countries to provide a scientific facility for advanced research on particle physics [46]. It is today one of the world's largest and most successful scientific laboratories, as well as an outstanding example of international collaboration between its 22 member states and 8 associated members [47].

During the first operational runs, the Large Hadron Collider (LHC) [48] was successful in terms of discoveries. Among of all the achievements, the probably most notorious one was the discovery of a particle at about 125 GeV [49] consistent with the boson theorized by P. Higgs, R. Brout and F. Englert [50], [51], announced by the two general-purpose experiments: Compact Muon Solenoid (CMS) [52] and ATLAS (A Toroidal LHC ApparatuS) [53]. At the time of the LHC commissioning, the Higgs boson was representing the missing particle to be observed for concluding the standard model [54].

In the LHC, superconducting magnets accelerate protons up to a peak value of 7.0 TeV in the 27 km counter-rotating accelerator facility. In four crossing points, the beams are brought into collision with a center of mass energy of more than 14 TeV. A complex of several accelerators (Figure 1.1) allows reaching the target energies. At the four collision point are located the ATLAS, CMS, LHCb [55] and ALICE [56] detectors. More details about CERN and the LHC can be found in article [57].

The **events rate** occurrence in a particle interaction is defined as  $\frac{dN}{dt} = \sigma \ell$ , where  $\ell$  represents the instantaneous number of interactions per second, called **luminosity**, while  $\sigma$  represents the cross-section of the interaction. The luminosity for a Gaussian beam distribution can be expressed in a form of:

$$\ell = F \frac{N_b^2 \gamma n_b f}{4\pi\epsilon \beta^*},$$

where  $N_b$  is the number of particles per bunch in the beam while  $n_b$  the number of bunches per beam and  $\gamma$  is the relativistic gamma factor.  $\beta^*$  represents the focal length at the collision point,  $\epsilon_n$  is the transverse beam emittance and f is the frequency of

**Figure 1.1.** The complex of the LHC accelerators [60].

the revolution. F is a correction factor to represent the luminosity reduction due to the crossing angle at the interaction point [58]. The **integrated luminosity** over the operation time  $\mathcal L$  defines the total amount of data recorded by an experiment. Clearly the luminosity is not constant within a run, it decays due the collisions themselves and due to inelastic interactions. The integrated luminosity is defined as:

$$\mathscr{L} = \int_0^T \frac{\ell_0}{(1+t/\tau)}.$$

The instantaneous luminosity of the LHC reached the  $2.1 \cdot 10^{34} \, \text{cm}^{-2} \text{s}^{-1}$  during the 2018 [59]. The expected integrated luminosity collected by the CMS experiment in its most recent run is  $\sim 300 \, \text{fb}^{-1}$ . The rate at which the particles bunch are brought into collision is 40 MHz and is called **bunch-crossing (BX) rate**.

Several others phenomena beyond the Standard Model (SM) need to be studied. For instance, the observation of neutrino oscillation does not conciliate with the standard model that assumes neutrino as massless. No particle was observed that can be responsible for dark matter cosmological observations. In the same time the matter-antimatter asymmetry needs to be explained. Some theories, for instance, the super-symmetry theory proposes extensions to the SM which might resolve some of these outstanding issues, and predict new particles with masses accessible at the

#### LHC [61].

For these motivations, a substantial upgrade of the LHC will extend its discovery potential by increasing the peak luminosity up to  $5 \cdot 10^3 4 \, \mathrm{cm}^{-2} \mathrm{s}^{-1}$ , and potentially to  $7.5 \cdot 10^3 4 \, \mathrm{cm}^{-2} \mathrm{s}^{-1}$  in the ultimate luminosity scenario [62]. The integrated luminosity expected for the High-Luminosity LHC (HL-LHC or HiLumi) operational time is  $4000 \, \mathrm{fb}^{-1}$ . It will enable the experiments to enlarge their data sample by one order of magnitude comparing to the LHC baseline program [63]. The couplings of the Higgs boson to Standard Model fermions are currently measured with around 20% uncertainty. The large data set provided by the  $4000 \, \mathrm{fb}^{-1}$  integrated luminosity will allow reducing this uncertainty below 1% [61].

The CMS and ATLAS experiments will be able to provide extended studies of Higgs bosons and eventually to perform direct search for new particles that could solve open questions in HEP as the nature of dark matter, the stabilization of the Higgs mass, and the nature of the electroweak symmetry breaking [64]. It will enable the search for exotic processes as states with large missing transverse energy which could indicate the production of weakly interacting massive particles and as the signature of the lightest supersymmetric particles [65]. The LHCb experiment will pursue the observation of rare decays and CP violation in charm and beauty hadrons. Further studies on the quark-gluon plasma will be allowed by high luminosity Pb-Pb collisions in the ALICE experiment. The HL-LHC upgrade was approved in June 2016 and defined as one of the highest strategic priority by the European Strategy for Particle Physics (ESPP) [66].

For these reasons, the CMS detector will face a major upgrade towards the end of 2020 [67] which comprises the complete substitution of the CMS tracking system. The concept of intelligent particle tracking will be introduced in CMS. The frontend ASICs will be required to locally pre-select interesting physics events before the transmission to the back-end system, making possible the event-reconstruction in the high luminosity environment.

This thesis focuses on the studies and design of a micro-strip detector readout system and the ASICs that implement this concept.

This thesis is organized as follow:

- Chapter 1 (this chapter) gives a short historical introduction to particle detection systems, up to the now-days silicon pixel and strip detectors.

- Chapter 2 provides a theoretical background on the silicon detectors for HEP

applications and introduces the requirements for the high luminosity upgrade

of the CMS silicon tracker at CERN. State of the art is presented with emphasis

on the main challenges. Finally, a short overview of the radiation effects on

CMOS electronics is provided.

- Chapter 3 introduces the main goal of this thesis to combine for the first time in a high energy physics detector, particle trajectory and transverse momentum estimation, in addition to geometrical information and energy measurements and to locally pre-select interesting physics event before the transmission to the back-end system, making possible the event reconstruction in the high-luminosity environment. In the first part of the chapter, the advantages and the limitations of this approach are discussed. The second part of the chapter describes in details the studies and the design choices at the system level that lead to the implemented architecture. Besides, a simulation framework was developed to assist the studies and the design process of the whole readout system.

- Chapter 4 illustrates the design and implementation of the SSA, a readout ASIC of the silicon strip detector of the CMS Outer Tracker Pixel-strip (PS) module. The ASIC incorporates all the functionality and performance characteristics for operation in the final readout system.

- Chapter 5 describes the results of the silicon prototype characterization under different operating conditions. It presents the irradiation results and the estimation of the error rates expected by the operation in the target environment.

- In Chapter 6 the conclusions are drown and the possible improvements are discussed.

The definitions and the terminology necessary for the comprehension of the thesis are summarized in the glossary.

# 2 HEP detector electronics, challenges and state of the art

The Compact Muon Solenoid (CMS) experiment at CERN is foreseen to receive a substantial upgrade of the outer-tracker detector and its front-end readout electronics, requiring higher granularity and readout bandwidth to handle the large number of pileup events in the High-Luminosity LHC. For this reason, the entire tracking system will be replaced with new detectors featuring higher radiation tolerance and ability to handle higher data rates and readout bandwidths. The main challenges introduced by the upgrade are presented in this chapter.

Section 2.3 introduces the principles of silicon detector and the related readout electronics. Examples of state of the art tracking systems and their application in energy physics experiments are presented.

Radiation effects on electronics together with the power requirements represents one of the major challenge for the design of the ASICs operating in the innermost regions of the LHC experiments. Section 2.4 provides a short overview of the radiation effects on CMOS electronics.

## 2.1 The CMS experiment and the high luminosity upgrade

The CMS experiment is one of four CERN detectors situated on the LHC beam crossing points. Figure 2.1 shows a visualization of the detector. The particles generated in the collisions propagate radially, traversing the silicon tracker. The latter allows reconstructing the particle trajectory and transverse momentum  $p_T$  in the 3.8T magnetic field provided by the superconducting solenoid surrounding the tracking system. Both the electromagnetic calorimeter (ECAL) composed by scintillating crystals, and the surrounding hadronic calorimeter (HCAL) located within the solenoid volume, allow evaluating the particle energy. The return yoke of the magnet is interleaved with the muon chambers. The detector is 21.6 m and features a diameter of 15 m. The overall weight is approximately  $14 \cdot 10^6$  kg. A detailed description of the detector is reported in the CMS collaboration report [52].

Figure 2.1. CMS detector visualization [68].

A coordinate system with origin in the nominal interaction point is defined as:  $\hat{x}$  points towards the center of the LHC circle,  $\hat{z}$  is tangent to the rotating beam pointing in the anticlockwise direction (longitudinal direction),  $\hat{y}$  points vertical to form a right handed cartesian coordinate system. The  $\hat{x}\hat{y}$  plane is called transverse plane.  $\mathbf{p_T}$  and  $\mathbf{E_T}$  refers respectively to the particles **transverse momentum** and **transverse energy** in the  $\hat{x}\hat{y}$  plane. Due to the CMS detector structure, often a cylindrical coordinate system is adopted. r is defined as the radial distance from the nominal beam line ( $\hat{z}$  axis),  $\varphi$  is azimuthal angle measured in the  $\hat{x}\hat{y}$  plane from the x axis,  $\theta$  is the angle measured in the  $\hat{r}\hat{z}$  plane from the z axis. Additional derived coordinates are defined due to the direct dependency of physical properties: the **pseudorapidity**  $\eta = -\ln{(\tan{(\theta/2)})}$  represents the particle angle relative to the beam axis and the **dip angle** is defined as  $\lambda = \pi - \theta$ .

The CMS detector requires a substantial upgrade in order to exploit the increase in luminosity provided by the HL-LHC [67]. This upgrade is usually referred as the Phase-2 Upgrade. A major update of the CMS detector is foreseen to cope with the  $5 \cdot 10^3 4 \, \text{cm}^{-2} \text{s}^{-1}$  luminosity of the HL-LHC and the cumulative radiation damages to the electronics.

At the same time, we can observe a significant overlap in space and time of signals due to different proton-proton collisions happening in the same BX. Most of this collisions are in the low energy range and not interesting for the physics analysis. They produce detectable signals that can affect the event reconstruction efficiency. In addition, the strong magnetic field, combined with the multitude of primary and secondary low energy particles, creates so-called "loopers". These particles may have a life time of more than one BX. The average amount of overlapped signals is called **pileup**.

Most of sub-detectors will feature increased granularity and resolution to mitigate the higher pileup in the event reconstruction. It makes more complex to associate particle traces to the primary vertex. The particle reconstruction in CMS is based on the particle-flow technique [69] and relies on the capability of correctly separating the charged-particle traces in the tracker, the energy deposition in the calorimeter and the measurements of the momentum in the muon system [70]. An increased granularity and resolution in energy measurement are necessary to maintain the same level of the detector performance in the extreme pileup conditions.

The rates of production data for the HL-LHC CMS detector is more than an order of magnitude higher compared to the current detector. The trigger and the readout system need to be upgraded as well to allow the analysis to make use of it.

#### 2.2 The CMS silicon tracker

The detector located in the innermost region of the CMS detector is the silicon tracker [71]. It is composed of the multiple layers of the thin silicon sensors capable of evaluating the position of a traversing particle. The particle momentum can be evaluated at the back-end by computing the crossing coordinate in the different layers and measuring the curvature of the particle trajectory in the 3.8 T magnetic field provided by the superconducting solenoid. The inner part of the tracker allows for a precise reconstruction of the vertex due to its high spatial resolution.

The current CMS tracker is entirely composed by silicon strip particle detectors [72]. Micro-strips detectors are obtained by segmenting the silicon sensor over the full detector length to achieve spacial resolution along the  $\varphi$  direction. More than twenty different module geometries are currently implemented, with strip length between 80 mm and 200 mm and width ranging between 80 µm to 205 µm [73]. The total silicon detection area is ~ 200 m², divided into the 10 **barrel layers** (concentric cylindrical layers centered in the in the nominal interaction point and located at 20 cm < r < 120 cm) and 12 **end-cap disks** per side [74].

The strip readout ASICs, called APV25 and implemented in a commercial 250 nm technology, operates in a triggered readout mode to drastically reduce the data rates [75]. In other words, the ASICs locally store the information during the time required for the Level-1 trigger computation. If no trigger signal is received within the latency time, the information is discarded. In the other case, the event is transmitted. The trigger decision is computed upon the information from the muon detectors and the calorimeter to select the most interesting events exclusively for the physics analysis, accordingly to the available bandwidth. The maximum average trigger rate is currently  $100\,\mathrm{kHz}$  and the latency is  $3.2\,\mathrm{\mu s}$  [71].

#### 2.2.1 Requirements for the silicon tracker upgrade

In order to maintain or improve the physics performance of the CMS detector in the high pileup conditions of the HL-LHC, the entire tracking system must be replaced with new detectors featuring higher radiation tolerance and enhanced functionality allowing the front-end electronics or even the offline analysis in experiments to handle more complex features and measurements immediately [15].

The previous generation of the CMS tracker detector will be able to cope with the first few years of operation of the High Luminosity LHC. Accumulated radiation damage in the pixel sensors reduces the charge collection efficiency as well as the Lorentz angle, leading initially to decreased charge sharing among neighbouring pixels and hence to deteriorated spatial resolution, and eventually to reduced hit efficiency. Its intrinsic limitations bound the CMS Data Acquisition (DAQ) to a maximum Level-1 (L1) acceptance rate of about 100 kHz, with an available latency of  $4\mu$  for the trigger decision.

**Figure 2.2.** Visualization of the CMS silicon tracker for the high luminosity upgrade [68].

#### Chapter 2. HEP detector electronics, challenges and state of the art

Higher trigger rates will allow transmitting to the experiment back-end a significantly higher amount of event data. A longer L1 latency (up to  $12.5\,\mu s$ ) between the transmission of the trigger request and the corresponding event occurrence, will increase the time available for data processing. With the increased computation power and longer available time, the trigger system can handle more complex real-time calculations for the trigger decision.

In the previous generation of the CMS tracker detector, the highest instantaneous luminosity reached the record of 53 pileup events in a special 2017 high pileup run. In the upgraded CMS detector, an average of about 140 pileup events is expected for an instantaneous luminosity of  $5.0 \cdot 10^{34} \, \mathrm{cm}^{-1} \mathrm{s}^{-1}$ . This value will rise to 200 pileup events in the ultimate luminosity scenario.

The larger pileup and the increase in particle density requires the tracker front-end ASICs to provide:

- Higher granularity higher channel (either pixel or strip) density, will allow keeping the occupancy level at a few percents (< 3%) as in the current detector.

- Reduced material budget the quantity of material in the tracker volume, that

introduces a limiting factor for the detection ratios of particles that may interact with it and compromise what the detector is expected to recognize (see

Section 2.2.2).

- Improved trigger capability the ability to cope with the higher average number of collisions of the HL-LHC. In this case, the trigger rate should be increased from the current 100 kHz. The event reconstruction mostly identifies particles through its decay products. Searching for a specific decay pair has a significant probability of finding a random combination of other products with similar properties. It is generally referred as combinatorial background.

- A possible technique to overcome these limitations in the event reconstruction, enhance the rejection of the combinatorial background and improve the transverse momentum resolution, consists in utilizing information from the tracker itself in the trigger event reconstruction (see Section 3.4).

- Improved two-track separation the present tracker is limited to highly energetic jets track finding performance due to the merging of particle hits in the pixel detector. The ability to identify and distinguish especially close particle tracks is necessary to exploit the large amounts of collision data.

- Resolution in the  $\hat{z}$  direction the higher granularity together with the requirement of having a good estimation of the z-coordinate of the hit, impose the use of pixelated sensors.

- Increased bandwidth a drastically increased bandwidth and the introduction of a data compression procedures to accommodate the higher data rates allows the offline analysis of taking advantage of the  $5 \cdot 10^{34} \, \mathrm{cm}^{-2} \mathrm{s}^{-1}$  luminosity.

- Improved radiation tolerance due to the high increase in radiation levels, the electronics needs to guarantee the correct operation for the experiment within its expected lifetime (see Section 2.2.3).

#### 2.2.2 Material budget and power constraints for the outer tracker

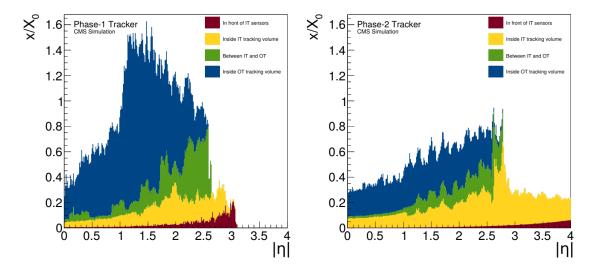

The quantity of material gives a limiting factor for the detection efficiency in the tracker fiducial volume (material budget) that may interact with the particles and compromise what the detector is expected to see. A quantification of the interactions can be expressed in units of radiation length, defined as the characteristic length that describes the energy decay of a beam of electrons. Figure 2.3 shows the material budget as a function of the pseudorapidity  $\eta$  for the current CMS detector and the expected value in the same units for the HL-LHC upgraded detector [9].

The material budget in the current detector reaches the 180% of the radiation length at  $\eta$ =1.5, mostly due to the stacked barrel layers of the outer tracker. It represents a significant limitation to the resolution of the electromagnetic calorimeter due to the energy loss in the layers traversed before to reach it. In addition, the particles scattering in this layers affects their trajectories and the tracking resolution.

Reducing the material budget does not come for free. It introduces a strong limitation in the material allowed for the the power distribution and in particular for the cooling system. The silicon sensors are designed to operate with a temperature below  $-20^{\circ}$ C to avoid breakdown or thermal runaway of the sensor [76], and to limit the degradation due to radiation effects. The material budget requirements implies a strong constraint on the outer tracker modules power consumption and power density. The cooling system will be based on a  $CO_2$  two-phase cooling to reduce the amount of passive material in the tracking volume [77].

As it will be highlighted in Section 3.4, the maximum power consumption and power

**Figure 2.3.** On the left the material budget in the current CMS detector volume expressed in units of radiation length as a function of the pseudorapidty  $\eta$ . On the right the expected material budget for the upgraded detector [9].

density for the ASICs discussed in Chapter 4 are respectively 250 mW and 90 mW/cm<sup>2</sup>. An excess in power consumption would overload the power converters and the cooling structure, increasing the temperature of the module.

#### 2.2.3 Radiation levels

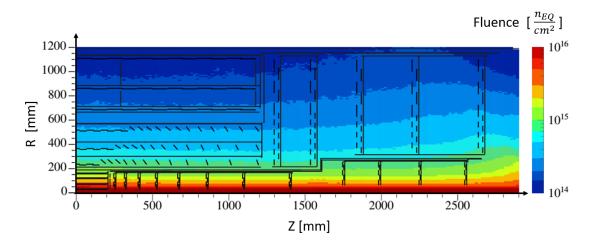

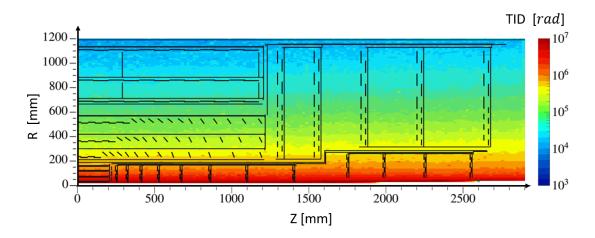

Up to 200 pileup events is expected for an instantaneous luminosity of  $5.0 \cdot 10^{34} \, \mathrm{cm^{-1} s^{-1}}$  for the upgraded CMS detector. The upgraded tracker is required to be fully efficient up to a target integrated luminosity of  $3000 \, \mathrm{fb^{-1}}$  [15], without any maintenance intervention for the outer-tracker. At such integrated luminosity, reached after 10 years of operation, the 1 MeV-neutron-equivalent fluence at the centre of the detector will be  $2.3 \cdot 10^{16} \, \mathrm{n_{EQ}/cm^2}$ . The Total Ionizing Dose (TID) will reach 12 MGy (1200 Mrad) [9], an unprecedented radiation level for advanced electronics, which is orders of magnitude higher of what expected in space applications.

Figure 2.4 and Figure 2.5 show the simulation results respectively of the expected fluence and the consequent collected dose in 10 years of operation and obtained using the Fluka simulation package [78], [79]. The results are expressed as function of the distance from the nominal interaction point in cylindrical coordinates.

**Figure 2.4.** Integrated 1 MeV neutron equivalent particle fluence per cm<sup>2</sup> in the upgraded tracker detector [9].

**Figure 2.5.** Total ionizing dose expected in the upgraded CMS tracker detector for an integrated luminosity of 3000 fb<sup>-1</sup> [9].

It is evident that the particle fluence is strongly depends on the radius. The expected TID in the locations where the outer-tracker electronics will be installed, is in the order of 100 Mrad. Only custom electronics implementing high-radiation hardening techniques can operate in this environment. An additional 50% margin needs to be taken into account due to the Fluka simulations results uncertainties on the radiation exposure [9].

#### 2.3 Silicon particle detectors and technologies

Particle tracking detectors are based on the detection of a signal given by the free charge carriers generated by the passage of a charged particle through a medium as a semiconductor. Silicon detectors, compared to other particle detector types, combine a high precision and resolution, with a readout speed order of magnitude higher than many other systems. Signals generated by the energy deposition are directly available in electric form allowing for local analog and digital processing.

#### 2.3.1 Silicon detector principles

The average energy loss of a charged particle traversing a material (silicon) is described by the Bethe-Bloch formula:

$$-\frac{dE}{dx} = 4\pi N_a r_e^2 m_e c^2 z^2 \frac{Z}{A} \frac{1}{\beta^2} \left[ \frac{1}{2} \ln \frac{2m_e c^2 \beta^2 \gamma^2 T_{max}}{I^2} - \beta^2 - \frac{\delta(\gamma)}{2} \right],$$

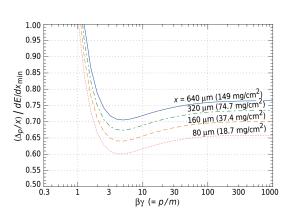

where z represents the the incident particle charge, I - the mean excitation energy,  $T_{max}$  - the maximum kinetic energy,  $m_e$  - the electron mass,  $r_e$  - the classical electron radius,  $\delta$  - the density effect correction,  $\beta = v/c$ ,  $\gamma = 1/\sqrt{1-\beta^2}$ . The interesting particles for the standard physics present a momentum (GeV/c  $\propto \beta \gamma$ ) in the intermediate and higher regions, where the Bethe-Bloch formula well approximates the mean rate of ionization energy loss for charged particles (stopping power) [80]. The  $1/\beta^2$  term is dominant at low energies, leading to a reduction of the stopping power for higher energies. At higher energies, a slow rise is given by the logarithmic term. The minimum of the deposited energy is located at  $\beta \gamma \approx 3$ . A particle detector in the target applications of the CMS tracker needs to be able to detect the minimum ionizing particle (MIP), or in other words to keep an equivalent noise level below this value. The Bethe-Bloch does not describe the low energy range where the particles have velocity on the same order of the orbital electrons leading to a drop of the stopping power.

Besides, the statistical fluctuation of the energy transfer per scattering needs to be considered. The energy loss probability distribution  $f(\Delta; \beta \gamma, x)$  is described by the Landau distribution 2.7. Only a part of the absorbed energy leads to electron-hole pairs generation. The average number of  $e^-h^+$  pairs (J) is related to the deposited energy  $\Delta$ by  $J = \Delta/P$ , where P represents the mean value of the energy needed for

ionization, equal to  $\sim 3.68\,\mathrm{eV}$  for the silicon [81]. The probability function  $f(\Delta)$  are usually called energy loss distribution or straggling function. The most probable number of  $e^-h^+$  pairs generated for a MIP in silicon is 76 per 1 µm. As a result of the high density of the silicon (2.33 g/cm³), the average energy loss for a MIP is about 390 eV/µm resulting in  $108\,e^-h^+$  pairs per 1 µm [82]. When designing a silicon detector, it is important to take in account the landau fluctuation to maximize the detection probability.

The basic principle of a silicon sensor (microstrip or pixel) is based on a highly doped silicon slice on a resistive substrate of the opposite polarity to form a diode structure. When an ionizing particle traverses the sensitive volume, it generates electron-hole pairs along its path. Due to the bias voltage applied to the sensor, for a p-sensor the holes drift to the  $p^+$  doped strips while the electrons drift to the  $n^{++}$  backplane, or vice versa for an n-type sensor [83].

Free charge carriers are also thermally generated leading to unwanted leakage currents. The thermal generation is independent of the concentration. The rate of the recombination is proportional to the np concentration product and limited by the minority carriers. When an excess is induced by a particle passing through or by radiation, if no bias is applied, the thermal equilibrium is reached with an exponential decay which time constant depends on the concentration of the carriers in excess. For a reversely biased structure, the carriers are removed keeping the concentration below  $n^2$  and leading to a current pulse at the contacts. The induced current can

**Figure 2.6.** Most probable energy loss in silicon, normalized to the mean loss of a MIP [80].

**Figure 2.7.** Straggling functions in silicon for 500 MeV pions, normalized respect to the most probable  $\Delta p/x$  [80].

be read out by a charge-sensitive amplifier, to provide a signal proportional to the collected charge. As a result of the small energy band gap of the silicon (1.2 eV) and its material density, the ratio between the number of charge carriers produced and the traversing particle energy loss, is sufficiently high to be able to generate signals with a detectable amplitude.

The applied bias voltage is usually above the value required for full depletion to be able to utilize the whole available volume [84]. Considering the electrons and holes mobility at high temperature, the charge collection time is usually in the order of the ns, allowing adopting this kind of sensor in high event rate applications as the HEP experiments.

# 2.3.2 Micro-strip and pixel detectors

Microstrip detectors are obtained by segmenting the doped side into strips over the full length of the detector and with a pitch usually between few tens to few hundreds of  $\mu$ m. The segmented side is usually covered by a few  $\mu$ m layers of SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub>, which protect the wafer during fabrication but the detector itself as well. The aluminium contacts can be placed directly on the doped strips (DC coupled detectors) or on a thin oxide or nitride layer, in which case the doped strips are capacitively connected to the readout electronics (AC coupled detectors). The latter solution is more expensive, due to the additional steps needed in the production, however capacitive coupling prevents leakage currents to flow through the electronics. The electrical connection between the strips and the readout electronics is usually realized via thin wires (wirebonding).

The planar process allows also the segmentation of one of the detector sides into a two-dimensional array of pixels. In this case an unambiguous 2-dimensional information about the position of the hit is achieved. The lateral size of pixels usually ranges between a few tens of µm and a few mm. The number of pixels and by that the number of readout channels increases linearly with the active area of the detector, while for silicon strip detectors, the number of readout channels increases with the square root of the active detector area. A higher cost of pixel detectors results from the complexity of the readout electronics and of the mounting techniques, especially when the pixel dimensions are small. The use of pixel detectors is nevertheless inevitable in

environments in which the detector occupancy is high, i.e. the sensor is traversed by many close-by particles. The use of strip detectors is in this case impossible due to ambiguities in the determination of the hit positions. Several categories of pixel detector are available and they can be divided according to the technology used for charge collection. Hybrid Pixel Detector (HPD) is the most used technology for HEP application [85]. It uses high resistivity silicon substrates like in the case of microstrip detectors. The sensor is divided in pixels with the same pitch as the readout chip and both are connected using a flipchip technology. This technique, also known as controlled collapse chip connection or its acronym, C4, is a method for interconnecting chips to external circuitry with solder bumps that have been deposited onto the chip pads.

In HPD, since the two parts are produced separately, they can be optimized and designed independently from each other. Also, any standard CMOS (complementary metal-oxide-semiconductor) technology can be used to design the readout electronics, so the scaling in the lithographic process can be exploited to build more advanced systems. The main disadvantage of this architecture is the cost of the flip-chip process, especially for detectors with very small pixels.

#### 2.3.3 Front-end electronics

In the majority of the particle trackers, it is not required a direct measurement of the deposited charge. Such readout systems are comparing the front-end output signal with a single threshold, to identify the particle passage through the pixel sensitive area. In some applications, a amplitude measurements are required in addition to the spacial information. A possible approach consists of using a low-resolution flash ADC to convert the shaper pulse height. The result is directly proportional to the integrated charge deposited on the sensor.

A common solution that allows avoiding additional analog signal processing, consists of the measurements of the width of the digital pulse obtained by comparing the shaper output signal with the threshold. The particle charge information is obtained by measuring the time over threshold (ToT). Utilizing a constant current feedback leads to a linear relation between the charge and the ToT. An example of a readout ASICs that implement this techniques is the RD53A [86].

Figure 2.8. Block diagram of a typical front-end circuit implementation.

If it is not required a high resolution, the ToT can be measured by detecting rising and falling edge of the pulse with the available clock resolution. The limitation of such approach is the dead-time due to long signals and the clock jitter. Sometimes, to decorrelate the primary vertex information, could be convenient to add the time of arrival (ToA) evaluation aside to the ToT measurement, as it is implemented in the work of [87]. Applications like the CMS HGC readout ASIC combines ToT and ToA measurements together with amplitude measurements based on utilizing an ADC per channel.