# **Multiport Energy Gateway**

Thèse N° 9361

Présentée le 26 septembre 2019 à la Faculté des sciences et techniques de l'ingénieur Laboratoire d'électronique de puissance Programme doctoral en energie

pour l'obtention du grade de Docteur ès Sciences par

#### Yan-Kim TRAN

Acceptée sur proposition du jury

Dr S.-R. Cherkaoui, président du jury Prof. D. Dujic, directeur de thèse Prof. Ph. Ladoux, rapporteur Dr A. Nami, rapporteur Prof. A. Rufer, rapporteur

École Polytechnique Fédérale de Lausanne Power Electronics Laboratory Station 11 1015 Lausanne, Switzerland

http://pel.epfl.ch

© 2019 by Yan-Kim Tran

*à ma Famille* Yan-Kim Tran

## **Abstract**

The global problem of energy supply and the reduction of the carbon footprint can only be solved by a massive replacement of fossil fuels and nuclear energy by renewable resources such as solar or wind energy sources. As these latter are mostly weather-dependent, they are uncontrollable and unpredictable in the long term. Their relative volatility can be mitigated with their spreading in terms of number and in terms of geographical location, as well as with the use of storage elements. These being mostly DC, their integration would be considerably eased by the use of DC grids which would allow the synchronization of resources to be avoided and would eliminate line impedance effects, proper to AC systems, and thus allowing the energy to be transferred over longer distances and through meshed networks more complex and requiring new types of interfaces or converters.

Indeed, in the past, voltage step-up and step-down transformations were only possible with the help of low-frequency (50-60Hz) and bulky transformers, which are still used nowadays in most AC grids. But the progresses of the last two decades in the field of power semiconductors now allow the realization of high-performance DC-DC converters with increasingly high voltages. A promising concept is the solid-state-transformer (SST), which uses a multi-modular structure integrating multiple medium-frequency transformers and offers an efficient and compact solution for voltage adaptation. While several researches on this particular subject have been done or are in progress for bi-port converters, the multiport version of it, which would allow the integration of storage elements directly on the additional port(s), has been only very few studied.

Therefore, this thesis proposes a new converter structure which combines on one hand the SST principle, in order to reach medium voltage ratings and on the other hand the multiport resonant conversion principle in order to limit switching losses and achieve higher switching frequencies necessary for an increased power density.

After a brief overview of existing storage technologies and multiport converters topologies, a description of the proposed structure and its operating principle are presented. The structure is composed by multiple identical submodules, connected in series on the MV side, in parallel on the LV side and each able to inteface a storage element on an extra port. This results in a relatively simple operation based on operating modes depending on the direction of the energy flow and allowing the independent use of one or more storage elements. Then, the mathematical models required to describe the converter are developed for each of these operating modes and make it possible to highlight the operating regions benefiting from soft switching and having a higher efficiency. This area is defined by the ratio of the impedances of the split resonant tank distributed between the three ports of each submodule. These models are also used to define sizing criteria which are applied for the design of a prototype converter for the medium-voltage grid and which parameters are used as the basis for the simulation. Finally, a detailed description of the converter dynamics is presented and simplified into models from which a control structure can derived and the controller parameters are calculated. In order to illustrate each of the elements developed in this work, a low-voltage prototype is designed and experimental results support most of the outcomes of this work.

Keywords: multi-port resonant converter, medium-voltage DC grids, power electronics, soft switching

### Résumé

La problématique globale de l'approvisionnement en énergie et la réduction de l'empreinte carbone ne peuvent être résolus que par un remplacement massif des énergies fossiles ou atomiques par des ressources renouvelables. Ces dernières étant pour la majeure partie dépendantes de la météo, elles sont non contrôlables et imprévisibles à long terme. Cette volatilité peut être palliée avec l'intégration d'un nombre élevé de ces ressources, leur répartition géographiquement décentralisée, ainsi que l'utilisation d'éléments de stockage. Ceci serait facilité par l'utilisation de réseaux à courant continu (DC) qui permettraient de s'affranchir de la synchronisation des ressources et supprimeraient les effets d'impédance de ligne, autorisant ainsi le transport de l'énergie sur des distances plus grandes et à travers des réseaux maillés plus complexes nécessitant de nouveau types d'interfaces ou convertisseurs.

En effet, dans le passé, l'élévation et l'abaissement de tension n'étaient possible que via des transformateurs basse-fréquence, utilisé aujourd'hui encore dans la plus part des réseaux à courant alternatif (AC). Mais les progrès faits durant ces deux dernières décennies dans le domaine des semiconducteurs de puissance permettent maintenant la réalisation de convertisseurs DC-DC performants et atteignant des tensions de plus en plus élevées. Un concept prometteur est le solid-state-transformer (SST). Il inclut une structure multi-modulaire intégrant de multiple transformateurs moyenne-fréquence et offre un moyen d'adaptation de tension efficace et compact. Mais si de nombreuses recherches sur le sujet ont été faite ou sont en cours pour des convertisseurs bi-port, la version multiport, qui permettrait l'intégration d'éléments de stockage directement sur les ports additionnels, n'a été que très peu été étudiée.

Cette thèse propose donc une nouvelle structure de convertisseur combinant à la fois le principe de SST destiné à la moyenne-tension et le principe de convertisseur résonant multiport permettant de limiter les pertes par commutation et d'atteindre des fréquences de commutation plus élevées, synonymes d'une densité de puissance accrue. Après un bref aperçu des technologies de stockage et des convertisseurs multiports existants, une description de la structure proposée ainsi que son principe de fonctionnement sont présentés. La structure est constituée de plusieurs sous-modules identiques connectés en série du côté moyenne-tension, en parallèle du côté basse tension et pouvant interfacer chacun un element de stockage sur un port additionel. Il en résulte un fonctionnement simple basé sur des modes d'opération dépendants de la direction du flux d'énergie et qui permet l'utilisation des éléments de stockage de manière indépendante. Ensuite, les modèles mathématiques nécessaires à la description du convertisseur sont élaborés pour chacun de ces modes de fonctionnement et permettent de mettre en évidence les zones d'opération bénéficiant de commutation douce d'un rendement plus élevé. Cette zone est définie par le rapport des impédance des circuits résonants répartis entre les trois port de chaque sous-module. Ces modèles servent aussi à définir des critères de dimensionnement qui sont appliqués pour la conception d'un convertisseur prototype destiné au réseau moyenne-tension et dont les paramètres sont utilisés comme base pour la simulation. Finalement, une description de la dynamique du convertisseur est présentée à l'aide de modèles simplifiés à partir desquels la structure de contrôle est dérivée et les paramètres des régulateurs sont calculés. Dans le but d'illustrer chacun des éléments développés dans ce travail, un prototype basse-tension est conçu et permet d'appuyer la majeure partie des conclusions de ce travail par des résultats expérimentaux.

Mots-clés: convertisseur multiport résonant, réseaux continus moyenne tension, électronique de puissance, commutation douce

# Acknowledgments

The PhD is an adventure that has made me meet, and get to know many people. A good part of them have been of great help or precious support to me and I would like to take this opportunity to acknowledge their efforts and support which played a direct or indirect role in this accomplishment.

First of all, I would like to thank Professor Drazen Dujic from the bottom of my heart, first for giving me the opportunity to do this thesis in his laboratory and for providing me with technical and material support throughout this research. But above all, I would like to thank him for his person, his way of leading the laboratory, his patience, his transparency and his unconditional availability. I was lucky to see the laboratory emerge, somehow, and evolve with all the surprises and challenges it brings, but he has always been able to ensure a healthy and pleasant work atmosphere.

I would also like to thank the SNSF for the funding of this thesis through the NRP70 project.

Thanks a lot to the jury members the Dr. Rachid Cherkaoui, the Dr. Alireza Nami and the Prof. Philippe Ladoux for accepting to give their time to review this document and for their valuable advice which for sure have enhances the quality of this document. I would like to thank especially the Prof. Alfred Rufer, head of the Industrial Electronics Laboratory (LEI) and also member of the jury, first for his helpful comments and advice for this work but particularly for having transmitted to me this passion for power electronics together with the Prof. Philippe Barrade.

I would also like to express my gratitude to Dr Franciso Freijedo, Post-doc at the PEL, for his numerous and valuable advice on control and his immense support in writing the few papers we submitted together. A big thank you to my successive office colleagues, Alex, Uzair and Emilien for supporting me for many long hours in these few common square meters, helping me on various problems while keeping a friendly atmosphere. Thanks to all my colleagues from the PEL: The two Marko, Min, Dragan, Stefan, Seongil, Nicolai, Miodrag, Milan, Ignacio, Gabriele, Prof. Masataka, Anja and Nikolina who have contributed to make life in the laboratory much more funny and pleasant.

I would like to thank Roland Wetter for his availability and efficiency, for all his advice related to infrastructure and tools, and his rigor in the organization of the laboratory. Thank you to Nathalie and Maria, shadow workers, without whom the administrative, organizational or logistical tasks would have left very little room for research.

I would also like to mention the no less than Dr. Nicolas Cherix and Dr. Simon Delalay, the founders of imperix for giving me the opportunity to forge my first concrete experiences in power electronics and, above all, allowed me to be at the right place at the right time and without whom I would never have met Prof. Dujic.

Thanks to my Family for its unconditional support and constant encouragement not only during this thesis, but also during all these years of study. Thanks to Flore for her understanding, her patience and especially for her warm comfort during the last phase of writing. Finally, a big wink to my friends, and especially Odile and Lucie who have always been here for me, both in travels and party and as well in difficult moments.

Thank You

Lausanne, August 2019 *Yan-Kim*

# **List of Abbreviations**

AC alternating current

BESS battery energy storage system

BOM bill of material

CAES compressed air energy storage

DAB dual active bridge DC direct current

DCM discontinuous conduction mode

DISO dual-input-single-output

EDLC electrical double layer capacitor

ES energy storage

FHA first harmonic approximation

HESS hybrid energy storage system

HVDC high voltage DC

IGBT insulated-gate bipolar transistorIPOS input-parallel-output-seriesISOP input-series-output-parallel

LVDC low voltage DC

MAB multiple-active-bridge

MEG Multiport Energy Gateway

MFT medium frequency transformer

MV medium voltage MVDC medium voltage DC NPC neutral point clamped

PV photo-voltaic

QAB quadruple-active-bridge

SFOE Swiss Federal Office of Energy

$SIDO \quad single-input-dual-output$

SISO single-input-single-output

SNSF Swiss National Science Foundation

SOC state-of-charge

SRC series resonant converter SST solid state transformer

TAB triple-active-bridge

UPS uninterruptible power supply

ZCS zero-current-switching ZVS zero-voltage-switching

# **List of Symbols**

$A_{core}$ Cross section of one element of the ferrite core of a MFT Maximum flux density, tesla  $B_{max}$  $C_r$ Resonant capacitance  $C_{DCi}$ Capacitance of the DC-bus on port i  $C_{com}$ Common mode equivalent resonant capacitor Differential mode equivalent resonant capacitor  $C_{dif}$ Output capacitance of the IGBT i Coesi Resonant capacitance located on the primary side of the MFT  $C_{r,p}$ Resonant capacitance located on the secondary side of the MFT  $C_{r,s}$  $C_{r,x}$ Resonant capacitance located the port x of the MFT Conduction losses of a semiconductor  $E_{cond}$ Turn-off losses of a semiconductor  $E_{off}$ Turn-on losses of a semiconductor  $E_{on}$ Reverse recovery losses of a diode  $E_{rr}$ Current normalization base  $I_{base}$  $K_f$ waveform coefficient  $L_{\sigma}$ Leakage inductance Magnetizing inductance  $L_m$  $L_r$ Resonant inductance Common mode equivalent resonant inductor  $L_{com}$ Differential mode equivalent resonant inductor  $L_{dif}$ Resonant inductance located on the primary side of the MFT  $L_{r,p}$ Resonant inductance located on the secondary side of the MFT  $L_{r,s}$  $L_{r,x}$ Resonant inductance located the port x of the MFT  $N_c$ Number of parallel ferrite element in a MFT core Number of cascaded submodule of a MEG converter  $N_{\rm s}$  $P_{max}^{air}$ Maximal losses dissipation of an air-cooled system Maximal losses dissipation of a water-cooled system Power from the energy storage elements  $P_{ES}$ Power from the low-voltage port  $P_{LV}$ Power from the medium-voltage port  $P_{MV}$

Common mode equivalent power

$P_{com}$

$P_{dif}$  Differential mode equivalent power

$P_{kn}$  Power from the port k of submodule n

$Q_a$  Available charges in a soft-switched current

$Q_{oes}$  Stored charges is a semiconductor

Q quality factor of a RLC circuit

$R_{c-f}^{th}$  Thermal resistance between module case and heat-sink fin

$R_{f-a}^{th}$  Thermal resistance between fin and air

$R_{i-c}^{th}$  Thermal resistance between semiconductor junction and module case

$R_{com}$  Common mode equivalent parasitic resistor

$R_{core}$  Reluctance of a ferrite core

$R_{dif}$  Differential mode equivalent parasitic resistor

$R_{gap}$  Reluctance of the air gap

$R_{on}$  On-state resistor of an IGBT

$T_{dti}$  Deadtime of the semiconductor i

$T_{res}$  Resonant period

$T_{sw}$  Switching period

$V_{base}$  Voltage normalization base

$V_{dc,k}$  DC bus voltage on the port k

$V_{dif}$  Differential voltage between the DC bus of two ports

$V_f$  Forward voltage of an IGBT

$\Delta_T$  Temperature elevation

α Damping attenuation of a RLC circuit

$\mu_0$  Permeability of air

$\mu_r$  Relative permeability

$\omega_0$  Resonant angular frequency

$\omega_d$  Damped resonant angular frequency

*ζ* Damping factor of a RLC circuit

$d_i$  Duty-cycle of the DC-DC stage on port i

$f_{Bi}$  Switching frequency of the regulation stage on the port i

$f_r$  Switching frequency

$f_{sw}$  Switching frequency

$i_{ac\,k}^{x}$  Resonant current in the port k during interval x

$i_{com}$  Common mode current

$i_{dif}$  Differential mode current

$i_{k,n}$  Current through the port k of submodule n

$l_{core}$  Magnetic path length in a ferrite core

$l_{gap}$  Air gap length

$v_{ac,k}^X$  AC voltage applied to the port k of the resonant stage during the interval X

$v_{k,n}$  Voltage at the terminals of port k of submodule n

# Contents

| Al | ostra | ct                                                        | i   |

|----|-------|-----------------------------------------------------------|-----|

| Ré | sum   | é                                                         | iii |

| A  | kno   | wledgments                                                | v   |

| Li | st of | Abbreviations                                             | vii |

| Li | st of | Symbols                                                   | ix  |

| 1  | Intr  | roduction                                                 | 1   |

|    | 1.1   | Background and motivation                                 | 1   |

|    | 1.2   | The thesis                                                | 5   |

|    |       | 1.2.1 Scope                                               | 5   |

|    |       | 1.2.2 Objectives of the thesis                            | 6   |

|    |       | 1.2.3 Main contributions                                  | 7   |

|    |       | 1.2.4 Structure of the thesis                             | 8   |

|    |       | 1.2.5 List of publications                                | 9   |

| 2  | Stat  | te of the art                                             | 11  |

|    | 2.1   | Storage elements and their integration                    | 11  |

|    |       | 2.1.1 Mechanical storage technologies                     | 11  |

|    |       | 2.1.2 Electrical storage technologies                     | 12  |

|    |       | 2.1.3 Electrochemical storage technologies                | 12  |

|    |       | 2.1.4 Hybrid Storage                                      | 13  |

|    | 2.2   | Topologies of multiport DC-DC converters                  | 14  |

|    |       | 2.2.1 Non-isolated converters                             | 15  |

|    |       | 2.2.2 Isolated converters                                 | 16  |

|    |       | 2.2.3 Resonant converters                                 | 17  |

|    | 2.3   | Basic switching cells topologies                          | 22  |

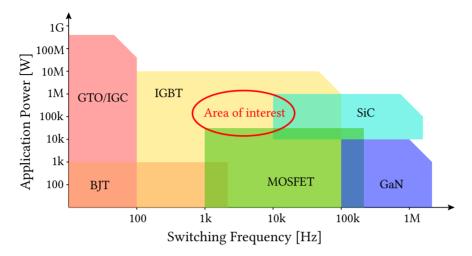

|    | 2.4   | Semiconductors                                            | 27  |

|    | 2.5   | Discussion                                                | 27  |

| 3  | Mu    | ltiport Energy Gateway: topology and operating principles | 29  |

|    | 3.1   | Converter structure                                       | 29  |

|    | 3.2   | Submodule structure                                       | 30  |

|    |       | 3.2.1 Resonant stage                                      | 31  |

|    |       | 3.2.2 Regulation stages                                   | 32  |

|    | 3.3   | Discussion                                                | 38  |

| 4  | Mod   | deling of the three-port resonant converter               | 39  |

|    | 4.1   | Model of the resonant stage                               | 39  |

|    | 4.2   | Three winding transformer                                 | 40  |

|    | 4.3   | LLC Resonant Converter                                    | 41  |

|   | 4.4              | Three-port LLC Converter                              | 48  |

|---|------------------|-------------------------------------------------------|-----|

|   |                  | 4.4.1 Model in DISO mode                              | 48  |

|   |                  | 4.4.2 Experimental Results                            | 59  |

|   |                  | 4.4.3 Model in SIDO mode                              | 59  |

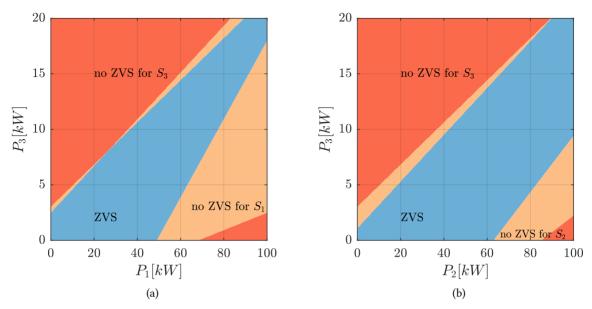

|   | 4.5              | Soft switching operation region                       | 65  |

|   | 1.3              | 4.5.1 ZVS conditions                                  | 66  |

|   |                  | 4.5.2 ZVS operation region                            | 67  |

|   |                  | 4.5.3 Efficiency approximation                        | 69  |

|   | 4.6              | Discussion                                            | 74  |

|   |                  |                                                       |     |

| 5 |                  | G design rules and guidelines                         | 75  |

|   | 5.1              | Converter ratings                                     | 75  |

|   | 5.2              | Number of levels and the semiconductors voltage class | 76  |

|   | 5.3              | Resonant stage - DC transformer                       | 79  |

|   |                  | 5.3.1 Switching frequency                             | 79  |

|   |                  | 5.3.2 Choice of $L_m$                                 | 81  |

|   |                  | 5.3.3 Power sharing ratio                             | 82  |

|   |                  | 5.3.4 Sizing of the resonant tank                     | 83  |

|   |                  | 5.3.5 DC bus capacitors $C_{DC,2}$                    | 86  |

|   | 5.4              | Regulation stage of the MV side                       | 87  |

|   |                  | 5.4.1 Switching frequency $f_{B_1}$                   | 87  |

|   |                  | 5.4.2 Inductor filter $L_{B_1}$                       | 89  |

|   |                  | 5.4.3 DC bus capacitors $C_{DC,1}$                    | 89  |

|   | 5.5              | Regulation stage of the ES side                       | 89  |

|   |                  | 5.5.1 Switching frequency $f_{B_3}$                   | 89  |

|   |                  | 5.5.2 Inductor filter $L_{B_3}$                       | 90  |

|   |                  | 5.5.3 DC bus capacitors $C_{DC,3}$                    | 90  |

|   | 5.6              | Summary of the designed parameters                    | 91  |

|   | 5.7              | Discussion                                            | 92  |

| 6 | Cor              | ntrol system design                                   | 93  |

|   | 6.1              | Plant modeling                                        | 93  |

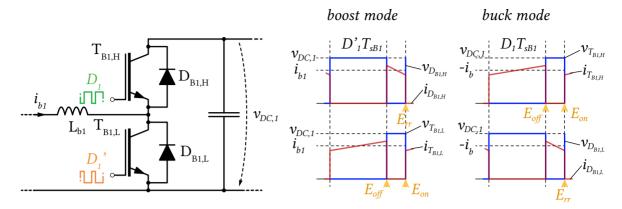

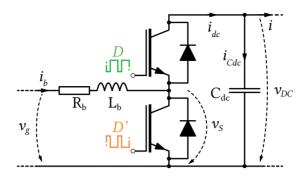

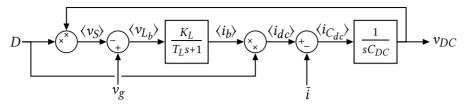

|   |                  | 6.1.1 Regulation stage                                | 94  |

|   |                  | 6.1.2 DC transformer in SISO mode                     | 95  |

|   |                  | 6.1.3 DC transformer in DISO mode                     | 98  |

|   |                  | 6.1.4 DC transformer in SIDO mode                     | 100 |

|   |                  | 6.1.5 DC Approximation                                | 100 |

|   |                  | 6.1.6 Complete converter model                        | 102 |

|   | 6.2              | Control Structure                                     | 103 |

|   |                  | 6.2.1 Controllers gain design                         | 103 |

|   | 6.3              | Simulation results                                    | 106 |

|   | 6.4              | Experimental results                                  | 110 |

|   | 6.5              | Discussion                                            | 113 |

| 7 | Cor              | nclusion                                              | 115 |

| 1 | 7.1              | Summary and Contributions                             | 115 |

|   | , · <del>·</del> |                                                       | 11) |

|    | 7.2  | Overall conclusion             | 117 |

|----|------|--------------------------------|-----|

|    | 7.3  | Perspective of future works    | 117 |

| AĮ | pend | lices                          | 119 |

| A  | RLC  | Circuit differential equations | 121 |

| В  | Low  | Voltage Prototype              | 123 |

|    | B.1  | Switching Cells                | 124 |

|    | B.2  | MFT                            | 124 |

|    | B.3  | Resonant Tanks                 | 126 |

|    | B.4  | Control Platform               | 125 |

# 1 Introduction

#### 1.1 Background and motivation

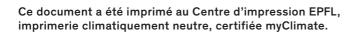

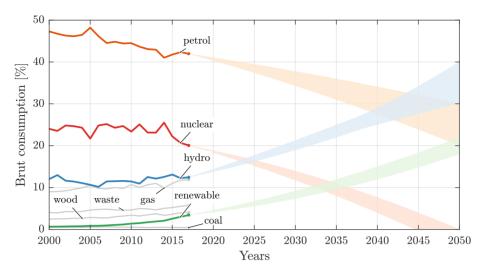

The global awareness of environmental issues and energy supply has led to many changes in the policies and strategies of governmental energy offices and at every link in the chain from producers to consumers. With regard to Switzerland, the evolution of the energy policy is dictated by two goals: First, the 2050 Energy Strategy (SE2050), signed in 2007 and reinforced in 2011 after the Fukushima nuclear disaster, aims for a gradual, but complete, exit of the nuclear power generation by 2050. Secondly, the ratification of the Paris Agreements in 2015 (COP21), aims for a 50% reduction in the emission of CO2 and greenhouse gases resulting from the use of fossil fuels (petroleum), by 2030 (see Fig. 1.1). This implies a complete replacement of nuclear energy generation as well as a partial or complete replacement of fossil fuels by renewable energies. These latter being currently very limited, it also implies a reduction of the energy consumption per capita by almost 54% by 2050 (see Fig. 1.2) and a decrease in electricity consumption by 18% [1]. These goals can only be achieved with an increase in efficiency and therefore a reduction in losses, as well as with a smarter use of the resources in all areas. This includes the energy transport (efficiency of whole chain from production to distribution and the resulting conversion steps) through improved infrastructures, and the end use of it in the households (certified appliances), in the transportation (hybrid or purely electric vehicles) as well as in the construction (thermal insulation).

Although the trend in energy consumption is not yet declining despite these strategic measures and the favorable climate of recent years (which required less heating energy) [3], it is stabilizing compared to previous years demographic and economic growth of the country. On the other hand, the substitution of fossil fuels by electricity is clearly visible in all domains [2], [4], such as households, industry, services or transport (with a growing tendency to favor electric vehicles for both public and individual transportation). These provisions will result in the end in a growing share of electricity in terms of final consumption and an energy production mostly from renewable resources.

Unlike controllable resources, from which the available energy can be estimated and which production can be controlled accordingly (e.g. hydro-power, biomass and geothermal), stochastic resources (such as wind-turbines or solar plants, which potential varies with the climate and the weather) cannot be controlled to meet a specific demand, although its production can be estimated on a very short horizon. Thus, the eventual mismatch between the production and the consumption, in terms of peak power or timing, can be overcome with the use of storage elements. In addition, the decentralization of these resources and storage elements is expected. This, by playing on the fact that with an increasing number of resources and their distribution over a large geographical area, the probability that the energy needed at a given time is available somewhere in the network is increased [5], [6]. The Swiss

1

**Figure 1.1** Part of the primary consumption (form of energy before conversions, transportation and storage) of Switzerland: actual number for past 15 years [2], and the objectives according to ES2050 scenario and COP21 for the future.

**Figure 1.2** Energy consumption in its final form and its targeted evolution according the Swiss Federal Council [1].

Federal Office of Energy (SFOE) predicts that by 2050, 10% to 20% of total Swiss production will come from distributed generation.

In addition to an increased stability and redundancy by means of the use of multiple and widespread elements, the local consumption of local production can help in terms of decongestion of the grid. The principle of self-consumption [7] may be implemented in the case of some buildings or groups of buildings where the use of energy from their own production is made possible thanks to the integration of storage elements such as batteries. It also makes it possible to play with market prices by using storage to store energy from the grid only when the prices are advantageous, thus indirectly

contributing to the stability of the grid. Decentralization, which concerns both renewable energy sources and storage elements, requires a good integration of these resources into the overall system and necessitates thus a powerful control structure and hardware with increased features.

From the software point of view, the digitalization of the world (IoT), which produces a constant flow of information (production, consumption, availability, etc...) is a dominant factor in progress [8]. With a smart analysis, it enables a more and more accurate forecast of the production allowing its optimization while giving flexibility to the demand. A national research project (NRP70) [9] funded by the Swiss National Science Foundation (SNSF) is currently developing a communication protocol between sources and loads and a control structure able to regulate electrical grids or islanded micro-grids with very low inertia, and with very high penetration rate of renewable energy (up to 100%) by monitoring in real-time the available potential of the sources, by controlling the demand accordingly and by playing with storage elements with various time constants such as thermal inertia of buildings, stationary electric vehicle battery or even a so-called "virtual storage" by shifting, over the time, the energy demand of non-critical applications.

If the evolution of the grid goes hand in hand with the development of control strategies, whose progress is already consequent with the concepts of smart-grids and smart-meters [10], it also goes with the upgrade of the hardware and the infrastructures. This is reflected with the need for new conversion and interconnection systems capable of providing highly dynamic control, increased reliability and high efficiency. The standard production-transport-distribution-consumption chain must evolve into a more complex meshed system with bidirectional links and nodes that can be both sources and loads, thus requiring new infrastructures or the modification of the existing ones. This is where the progress made in recent years in the fields of semiconductors and power electronics are key factors allowing a conversion with very high efficiency while providing high power density [11]. Indeed, if in the past, step-up and step-down conversion was not easily possible in direct current (DC) because of the absence of semiconductors, today's voltage and current levels reachable in the semiconductor field enable very high power DC/DC conversion without the need for the low frequency (50-60Hz) transformers which are used in alternating current (AC) domain.

Hence, DC technologies are promising solutions for the grids of the future: on one hand, at high and very high voltage, they allow a more efficient transport of bulk energy over long distances, getting rid of line effects and reactive power flows affecting AC systems [12]. The first high voltage DC (HVDC) transport lines have been commissioned already in the last century and are becoming more widespread for offshore transmission, reaching powers in the range of multiple of GW. On the other hand Low voltage DC (LVDC) distribution allows easy connection of storage elements that are inherently low voltage and DC (e.g. batteries and super-capacitors). It also reduces the number of conversion stages for the distribution to the loads which are also either DC (e.g. servers, computers and TV's) or using variable frequency and are therefore requiring a DC stage (e.g. rotating machines and household appliances). Additionally, the energy savings obtained using LVDC micro-grids at the level of residential buildings, or a group of them, haven been proven [13]. Therefore, the medium voltage DC (MVDC) grids come as a natural interface between the bulk transport using HVDC lines and the LVDC storage elements, loads or micro-grids. They allow a simplified interconnection of intermittent and variable voltage sources while avoiding the synchronization necessary for the AC grid which becomes very complex with a high number of resources, and therefore offers increased stability. If the current grids still use mainly AC, it is mainly for historical and cost reasons and the future scenario of DC grids or micro grids is taken very seriously [14].

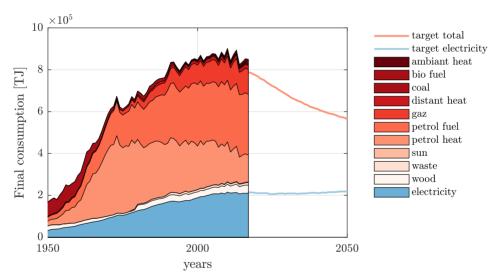

Figure 1.3 Various applications where MVDC technologies are promising and where the integration of storage will help in terms of performances: (a) Renewable generation: In the case of PV generation, the integration of storage will increase power quality, providing an energy buffer in order to be able to run, on one side, the MPPT algorithm and inject on the other side, a stable and controlled amount of power. Additionally, bulk power storage can compensate the drop of production in case of quick and partial shading [15]. In the case of large scale off-shore wind farms, the volatility of wind energy generation, either at LV or MV, would benefit from integrated energy buffer [16]. (b) Marine: The on-board MVDC grids will allow further frequency decoupling of the generation and distribution, improving the overall fuel efficiency. Moreover, the integration of storage will allow for regenerative breaking, peak shaving and support for black-start conditions. (c) Datacenters: The power to the chip is very critical, and storage elements can greatly increase the reliability of such systems with high power uninterruptible power supply (UPS). (d) DC micro-grids: Behaving part of the day as a source thanks to the renewable energy resources and part of the day as a load, due to the peaks of energy consumption during critical hours (home appliance, lighting, heating), micro-grids are relying on the integration of storage elements. They are key elements allowing the auto consumption of the energy produced inside the micro-grid and helping toward the decongestion of the distribution grid.

With regard to MVDC applications, one example is the first DC datacenter, built by ABB and Green CH [17], which has been in operation in Zurich area already for a few years. Often requiring installed powers above 1 MW, datacenters power supply is one of the most critical application and the use of storage elements can greatly improve the reliability. All CPUs, memory chips, and disk drives consume direct current, and the power-to-the-chip requires numerous conversion step in the conventional AC structure to achieve the low voltage levels required [18]. In this sense, DC systems enable a reduction in the number of conversion stages, a higher efficiency and a reduced volume while allowing an eased integration of UPS with hybrid storage elements [19].

Concerning MVDC grids or micro-grids, the most relevant example that can be mentioned is the marine field where on-board DC grids have many advantages [20], [21]. The electric ships have

the advantage of proposing not only a spatial decoupling of the generation and propulsion which offers great flexibility in ship design for a better spatial distribution of the loads, but also a frequency decoupling, which permits for the AC generators to run at optimal speed, improving the overall fuel efficiency. In addition, the integration of storage elements allows the support of power peaks due to startup sequences as well as the recovery of energy during braking.

At the distribution level, MVDC technologies are seen as good alternatives or complements to the existing grid. As a matter of fact, Siemens also recently announced one of the first commercial solutions for MVDC distribution networks [22].

#### 1.2 The thesis

#### 1.2.1 Scope

The few examples mentioned earlier and depicted in Fig. 1.3 highlight two main ideas:

- MVDC grids are a promising intermediary step between the HV (AC or DC) bulk transportation and the distribution or the collection. They allow great flexibility and ease the connection of volatile resources while providing a good efficiency.

- LVDC grids or micro-grids are a promising solution for the integration of local storage and renewable resources. They are, together with the storage, key elements allowing local consumption of the local production.

The interconnection of a MVDC grid, a LVDC grid and various storage elements reveals the need of new interfaces able to provide bidirectional power flow and good controllability while being able to withstand MV rating and provide high efficiency. The progress done in the domain of semiconductors during the past decades allows us now to handle higher voltages at higher frequencies, making the emerging concept of solid state transformer (SST) even more promising for further developments of the future grids [23]. The idea of increasing the efficiency and the reliability of the cycle storage-restitution by decreasing the number of conversion stages motivates the development of a fully bidirectional multiport power electronics interface. Moreover, the state-of-the-art developments propose either MV rated bi-port converters or LV and low power multiport converters, but no converters able to withstand MV rating while providing additional power ports has been reported so far.

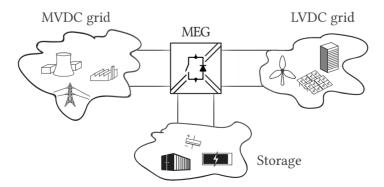

Taking, as background scenario, the application of the interface between a LVDC micro-grid and a MVDC grid with integrated storage such as depicted in **Fig. 1.4**, this work focuses on the elaboration of a new topology, inspired from said SST and derived to a multiport version, in order to provide full bidirectionality, galvanic isolation, compactness and efficiency.

The LVDC micro-grid, in the range of 750 V and 0.5 MW, represents a group of elements comprising resources such a PV arrays or wind-turbines and loads such as domestic consumers and servers. The LVDC side may behave either as a load or as a source depending on the time of the day and is subject to rapid variations in both production (quick cloud shading on the PV arrays) and consumption (inrush power, black start of machines, servers computation processes) in the range of seconds to several minutes.

The MVDC grid, characterized in the range of 10 kV, is a multi-terminal MVDC grid (of a ship for instance) or the intermediary stage between the HVAC transportation lines and the LV grid (such as in **Fig. 1.3d**). It is considered as a stiff grid, its voltage remains fixed and stable, and is bidirectional. In order to increase the stability and the power quality in this MVDC grid, the power flow from/to the LVDC grid has to be smoothed thanks to the storage elements.

The energy storage (ES) elements is a mix of batteries and super-capacitors able to absorb abrupt peaks of power as well as compensate slower small variations. They are considered as a support to the main power flow between the LVDC grid and the MVDC grid, and their power ratings are therefore reduced (20% of the nominal power).

The thesis is focused on the multiport DC-DC converter and especially on the proposition of the core structure: a multiport resonant DC-DC transformer. Although resonant converter topologies have been studied in the past, their multiport version is novel and only few literature references deal with its design and even less about its control. Thus, the main effort of this work is to assess the feasibility, the practicality and the relevance of such topology while developing models, design rules and a possible control structure. The assessments of the theoretical outcomes of the research are supported by the realization and the tests on a LV prototype of a single stage.

#### 1.2.2 Objectives of the thesis

The objectives of the thesis are:

- The elaboration of the structure of a converter comprising a MVDC terminal, a LVDC terminal and one or multiple terminal dedicated to the connection of LV storage elements. This structure has to provide:

- 10 kV from/to 750 V voltage adaptation for a rated power of 0.5 MW.

- Galvanic isolation between the various ports.

- Complete bidirectionality.

- Simple controllability of the various power flow.

**Figure 1.4** Scope of the thesis. The MEG as an interface between the storage and the future DC grids.

- The assessment of this structure in terms of feasibility, advantage over prior art structures, as well as its limits and drawbacks, by simulations and experiments.

- The elaboration of a control structure able to operate in all the modes operation linked to the targeted field of application.

- The development of tools and models necessary for further design and optimization of the developed topology.

The thesis focus on the overall topology at the system level. Therefore the following topics are excluded from the scope of this research:

- The design of the MFTs, their specification (dimensions, number of windings, sections), choice of the materials (core, isolation), their thermal analysis. The MFT models used in this work are thus ideal model without deep consideration of these last points.

- The storage technology and its design. The choice of the technology as well as the sizing in terms of power and energy are driven by specifications linked to the final application and are therefore not addressed in this work.

- The precise characterization of the hardware component, especially the semiconductors. The

models of the devices used in this work are their ideal models, sometimes taking into account the

losses parameters form the commercial datasheets. But no precise TCAD models are considered.

- The safety mechanism and the degraded operation of the converter. Over-voltage and short-circuit events are not addressed in this work.

#### 1.2.3 Main contributions

With respect to the objectives mentioned earlier, the main contributions of this thesis are:

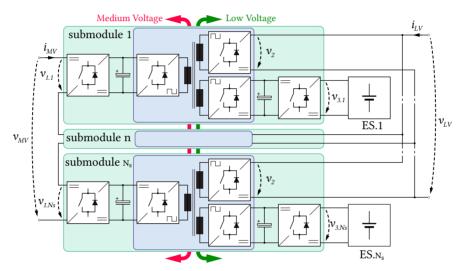

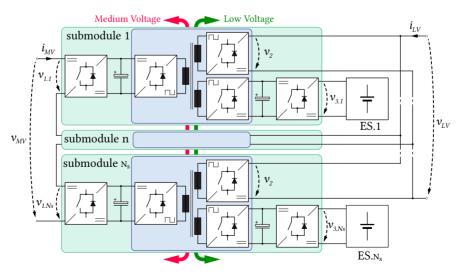

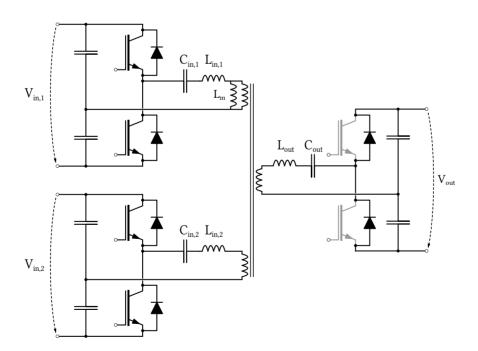

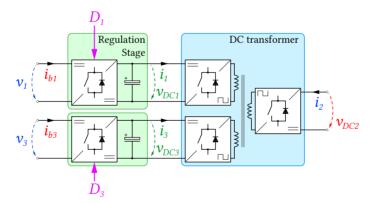

- The proposal of a new structure of DC-DC converter designated by "Multiport Energy Gateway" or MEG (see publication [C2]), as depicted in Fig. 1.5. Its novelty sits in the input-series-output-parallel (ISOP) combination of multiple resonant converters operated as DC-transformers. This makes it possible to interface a MV rated grid on one side, a LV rated grid on the second side and multiple LV storage elements on the additional ports. The topology and its modes of operation are presented and the main features as well as the principal operating constraints are highlighted.

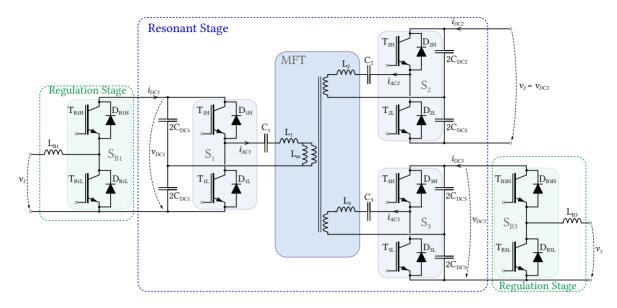

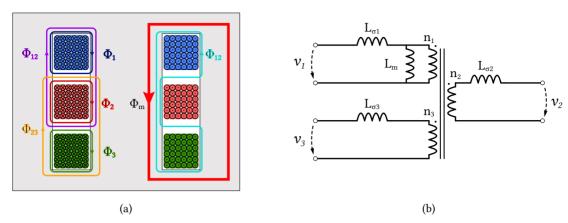

- The proposal of the extension of the well-known LLC converter to a multiport version of it (see publication [C4]). The coupling of a third winding on the medium frequency transformer (MFT) and the splitting of the resonant tank between the three sides enable a single stage, fully bidirectional and isolated interface between three different ports. The use of a resonant structure, enabling soft switching, makes possible the operation of such converter at relatively high frequencies, synonymous of compactness and efficiency.

- A simplified model and derived analytical expressions of this novel multiport resonant converter: the precise mathematical expressions of the voltage and current waveforms inside the multiport converter allow for the characterization of the natural power sharing (see publications [C1]

- and [J2]), the zero-voltage-switching (ZVS) operation and the dynamics of the system. By extension, the model leads to some insights to derive design rules.

- The proposal of a control structure and strategy for the Multiport Energy Gateway (MEG) topology: a control method involving multiple cascaded PI loops is presented. It makes it possible to operate the converter in all the various modes needed by the application and allows an independent control of each storage element (see publications [C3] and [J1]).

- The theoretical design of two converters: the first one, corresponding to targeted application, is rated for  $0.5 \, \text{MW}$ ,  $10 \, \text{kV}$  and serves as a study case for simulation examples. The second one is a  $10 \, \text{kW}/360 \, \text{V}$  lab-scale prototype built in order to provide experimental results.

**Figure 1.5** The MEG converter: an ISOP combination of multiport submodules, able to interface a MV grid, a LV grid and multiple storage elements.

#### 1.2.4 Structure of the thesis

The rest of this thesis is organized as follows:

- **The chapter 2** presents a brief overview of the state-of-the-art storage technologies and topologies used for MVDC/LVDC, multi-port and resonant conversion. The promising concept of SST and the examples of multiport resonant converter motivates the development of a topology based on the mix of both.

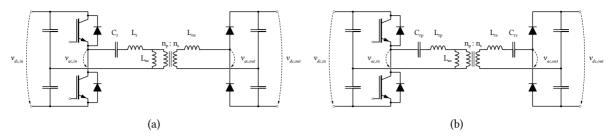

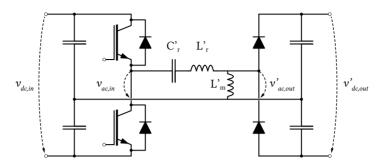

- **The chapter 3** presents the MEG topology, its principle and its use in all the modes of operation. Each functional block is described and the possible features are explained. A resonant stage is responsible for the voltage adaptation and the galvanic isolation, while additional regulation stages control the power flows.

- **The chapter 4** provides a detailed mathematical model of the multiport resonant DC-DC converter. It reveals that the natural power sharing ratio is depending on the ratio of the resonant impedances and their repartition between the different ports. This gives practical insights for the elaboration of design rules and control structures. Additionally, the ZVS operation range can be derived

- from the mathematical model, which allows a rough estimation of the efficiency. The focus is on the particular operating mode where two ports are actively feeding the third one.

- **The chapter 5** presents the sizing rules of the different parts of the system for a functional design. First, the choice of the various voltage levels and the number of submodules is explained and followed by the specific design of the regulation stage and the resonant conversion stage. It results in a set of realistic parameters which are used as a study case in the next chapter.

- **The chapter 6** proposes a control structure and its associated strategy. After the derivation of the dynamics model and the transfer functions, a control structure is proposed. The design of the various controllers are presented and assessed with simulations and experimental results. It is shown that this type of multiport converter can be controlled with a relatively simple structure, comprising only PI regulators. Moreover, even though the bandwidth is rather slow, only a limited number of measurements is required.

- **The chapter 7** concludes the work, highlights the main outcomes from the project and gives an overview of the future research perspectives or improvement opportunities on the topic.

- **The appendix A** gives some detailed mathematical derivations used to model the converter.

- **The appendix B** presents the lab-scale setup. The selection and the design of the components of the LV prototype are briefly explained.

#### 1.2.5 List of publications

#### Conference papers:

- C1. Y. Tran, F. D. Freijedo, and D. Dujic, "Open-loop power sharing of three-port dc-dc resonant converters," in *2019 IEEE Applied Power Electronics Conference and Exposition (APEC)*, Mar. 2019, pp. 2138–2144

- C2. Y. Tran and D. Dujic, "A multiport medium voltage isolated dc-dc converter," in *IECON 2016 42nd Annual Conference of the IEEE Industrial Electronics Society*, Oct. 2016, pp. 6983–6988

- C3. Y. Tran and D. Dujic, "A multiport isolated dc-dc converter," in 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Mar. 2016, pp. 156–162

- C4. Y. Tran, D. Dujić, and P. Barrade, "Multiport resonant dc-dc converter," in *IECON 2015 41st Annual Conference of the IEEE Industrial Electronics Society*, Nov. 2015, pp. 003 839–003 844

#### Journal papers:

- J1. Y. Tran, F. D. Freijedo, and D. Dujic, "Multiport energy gateway," *IET Electric Power Applications*, Apr. 2019

- J2. Y. Tran, F. D. Freijedo, and D. Dujic, "Open-loop power sharing characteristic of a three-port resonant llc converter," *CPSS Transactions on Power Electronics and Applications*, vol. 4, no. 2, pp. 171–179, Jun. 2019

# 2 State of the art

This chapter presents a short overview of conventional storage technologies as well as a brief state-of-theart in the field of high-power DC-DC conversion and more specifically multiport topologies. With the goal of developing a new structure to interface a medium-term storage (seconds to tens of minutes), a MVDC grid and a LVDC grid, the different existing technologies are compared and evaluated, leading to the proposal of the MEG topology which is studied in this thesis.

#### 2.1 Storage elements and their integration

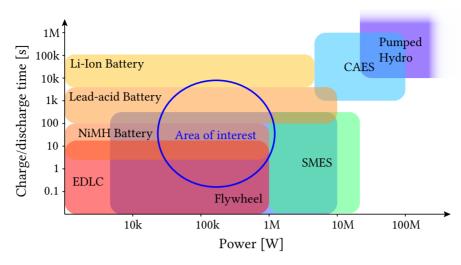

As mentioned in the introductory chapter, the transition to a fully renewable energy generation goes hand-in-hand with the integration of energy storage solutions. Currently, the storage technologies are of various natures, physics, and have very different specifications [24]. The **Fig. 2.3** presents a classification of different storage technologies [25], [26]. They are mainly of three different types: mechanical, electro-chemical, and electrical technologies. A mix of them is also an interesting option, often referred as hybrid storage.

#### 2.1.1 Mechanical storage technologies

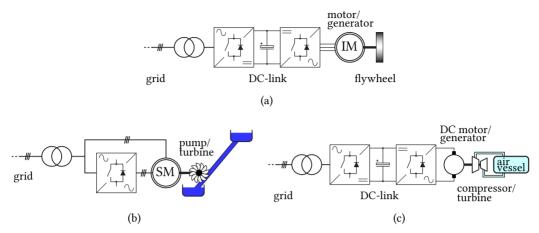

Mechanical technologies include kinetic energy storage (Flywheel) [27]–[29], potential energy storage (pumped hydro storage in accumulation lakes) [30]–[32] and compressed air energy storage (CAES) [33]–[35], as summarized in Fig. 2.1. Some of these technologies have the advantage of having a very large storage capacity (tens of GWh) as well as very large installed powers (up to several hundred MW). They are long-established and have proven their longevity and their high efficiency. Nevertheless, they require a conversion of the energy from its electrical form to its mechanical form and vice versa. This necessitates the use of rotating machines involving large, often complex, installations and therefore requires a consequent financial investment, a significant geographical impact and a very high maintenance. And even though their integration into DC grids would require less conversion steps than for conventional grids, the AC nature of the rotary machine necessitates more complex (four-quadrants) power electronics converters compared to DC only storage.

#### 2.1.2 Electrical storage technologies

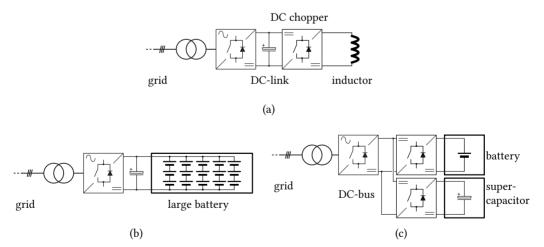

Electrical technologies include capacitive and inductive storage. Capacitive storage consists of storing the energy in the electric field between two electrodes separated by a dielectric. Thus, the storage

**Figure 2.1** Examples of mechanical storage technologies: (a) Flywheel for grid support, (b) pumped hydro for seasonal storage, (c) compressed air as shown in [33].

capacity relies mainly on the surface area of the electrodes and the distance between them. Advances in materials science offer porous materials with larger surfaces, known as electrical double layer capacitor (EDLC), and make this type of storage very attractive for application needing reduced volumes/weight, thanks to its power density, despite a reduced energy density. In terms of integration with the grid, this technology, intrinsically DC, requires only a two-quadrant DC-DC converter which makes it compelling for DC-grid. Inductive storage (SMES) [36], [37], which consists of storing energy in the magnetic field resulting from the flow of a current through an inductor, is ideal for high current and high power applications. However, these high currents require the use of (expensive) superconducting materials to avoid Joule losses and therefore necessitate installations at very low temperatures, which makes the use of these technologies very complex [38], [39] even though solutions integrating SMES are usually controlled with very simple power converters (chopper).

Figure 2.2 Examples of electrical and electrochemical storage technologies: (a) SMES, (b) BESS, (c) Hybrid storage

#### 2.1.3 Electrochemical storage technologies

Electrochemical technologies include battery storage and hydrogen storage. Battery storage is one of the oldest technologies. It uses the energy to be stored to generate a chemical reaction that separates the ions from two electrodes through an electrolytic material. Several processes and types of chemistry are used: lead, lithium-ion, nickel-cadmium, among others, and each has different power density, energy density and lifetime. The main advantage is a high energy density, which makes it the main technology used in electric mobility. This technology, referred as battery energy storage system (BESS) has also recently become an attractive option for mass storage in applications that complement renewable resources [40], support the grid [41]–[43] or provide secured power for critical applications such as datacenters [44]. Like EDLC, BESS are inherently DC and are thus easy to interface with DC grids. Nevertheless, their operation voltages are relatively low and require isolated converters when connected to high power and medium voltage applications or grids.

Hydrogen storage (fuel cell) consists in using the energy to be stored to electrolyze water and thus produce oxygen on one side and hydrogen on the other side, which will either be used as fuel for a combustion engine or used to reproduce electricity by a reverse process [45]. Possible applications range from 100 W to 100 kW, and from micro-grid support [46] to transportation [47]. The advantage is mainly the low standby hydrogen loss, however, the efficiency of the charge/discharge cycle as well as the operating voltages are relatively low.

#### 2.1.4 Hybrid Storage

For the use of a storage element in a medium power application, such as peak-shaving systems for intermittent renewable production [48]–[50] or distribution system stabilization [51], the storage system must support high power while providing good energy density and low standby loss, with time constants ranging from seconds to a few hours.

This is where the interest lies in a hybrid storage solution, also called hybrid energy storage system (HESS), combining both the advantages of batteries and those of super-capacitors [52]. Indeed, batteries, benefiting from a high energy density, are used for low power and long-terms balancing, while super capacitors, benefiting from a high power density, provide balancing during abrupt peaks of high power, such as partial shading on photo-voltaic (PV) farms or black-start of the machines in marine applications [53], for instance. In both production and distribution, systems have been set up and new techniques are constantly evolving. Research activities are mostly focused on the optimal ratio battery/super-capacitors [54] to be considered in the system and on the optimal control, power sharing [55], in order to benefit from better performance and longer component lifetime [56]. The advantages of hybrid storage systems have proven their effectiveness in the low voltage application field and therefore motivate the development of systems based on the same principle, mixing super-capacitors and batteries, for higher power ratings and for applications at the medium voltage (MV) collection and distribution level. Hybrid storage elements being mostly LVDC, the research has to focus on the interface between LVDC elements and MVDC grids.

**Figure 2.3** Area of use of the different storage technologies. In the case of medium power peak shaving application, hybrid solutions based on super-capacitors and batteries seem relevant.

#### 2.2 Topologies of multiport DC-DC converters

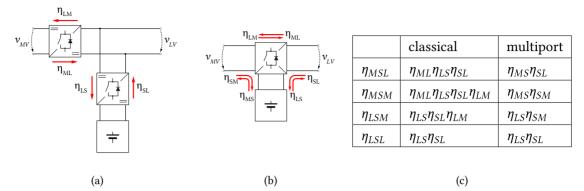

Except in the case of direct connection of storage elements to the application such as in [57], which imposes a voltage fluctuation with the state-of-charge, an interface between the storage elements and the grid(s) is necessary. In the case of a peak-shaving application, two grids are considered, one with a stochastic production or consumption of power and the other which power must be controlled and smoothed [58] with the help of storage elements. Three elements must therefore be interfaced and in this case provide a MV/LV voltage adaptation as well. When it comes to systems capable of interfacing more than two elements and in a bidirectional way, the concept of multiport converter appears as a logical and a necessary step to increase performance and reduce the footprint. Indeed, multiport converters are promising in terms of reliability, thanks to the reduction in the number of active components and therefore in the number of sources of failure, in terms of density, by the reduction of components in general (reduction of bill of material (BOM)) and in terms of efficiency, by reducing the number of conversion steps and therefore the losses of the overall charge/discharge cycle (cf. Fig. 2.4).

Examples of multiport converters for various applications and powers are referenced in the literature and can be classified into two families. The first is based on the interconnection of the different ports through a common DC bus (non-isolated converters) [59], and the second is based on the magnetic coupling of the different ports through a transformer (isolated converter).

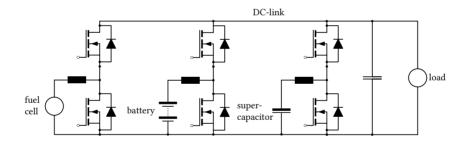

#### 2.2.1 Non-isolated converters

The general principle consists in connecting the *N* ports to a common DC bus via simple elementary converters (DC-DC converters). The power of each port can be controlled independently and the stability of the system is ensured by controlling the DC bus voltage (cf. **Fig. 2.5**). Although the simplicity of control and the small number of semiconductors are real advantages, this type of conversion topology is limited in terms of voltage range and DC bus voltage selection. The lack of

**Figure 2.4** Relative efficiency of the cycle charge/discharge of the storage from/to either MV grid or LV grid for the classical method (a) and with a multiport converter (b). Since each conversion step involves different voltage levels, the losses and thus the efficiency are considered different in both directions (i.e.  $\eta_{xy} \neq \eta_{yx}$ , where  $\eta_{xy}$  is the efficiency of the conversion from the voltage level x to the voltage level y). The overall efficiency of a charge/discharge cycle is given by the product of the efficiency of each conversion step (c). Intuitively, a reduction in the number of conversion steps would improve final performance. In this sens, multiport converters interfacing any of its ports through a single conversion step should be of some advantage compared to classical systems.

galvanic isolation makes this type of topology unsafe and therefore not feasible for high voltage levels and is only suitable for low voltage systems.

**Figure 2.5** Non-isolated multiport converter as in [60] which presents a fuel cell propulsion system with braking regeneration for electric vehicle.

#### 2.2.2 Isolated converters

In the case of isolated converters, the galvanic isolation is achieved by means of a transformer (magnetic coupling) which also allows much more freedom for the voltage transformation ratio. In addition, the high frequency applied to the transformer allows a reduction in the size of the magnetic components. The literature reports numerous converter examples, using a MFT for voltage adaptation and isolation [61]–[63]. These converters are generally composed of an active stage on the primary and a rectifier on the secondary side of the MFT. The bidirectionality of the system is based on the possibility to switch actively the secondary side switching cell in order to be able to reverse the power flow.

In the presence of several sources with the same voltage range, they can be combined on the MFT primary as in [64] where several sources are coupled in parallel. Based on the same topology, the converter presented in [65] incorporates not only a source-side storage element as an energy buffer but also a secondary active rectifier for voltage regulation. However, even if the isolation allows higher voltages and powers, only sources within the same voltage range can be connected together and the converter is unidirectional.

**Figure 2.6** (a) structure of a DAB converter. (b) equivalent circuit for the representation of the power flow. (c) vector representation on the duty-cycle control. (d) vector representation on the phase-shift control.

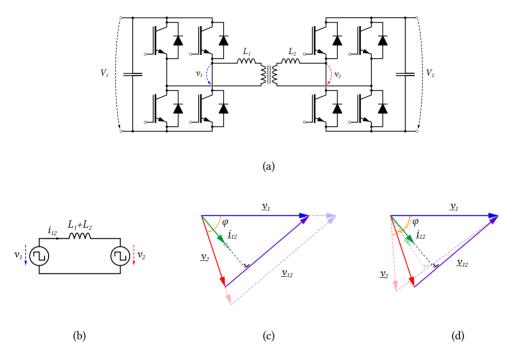

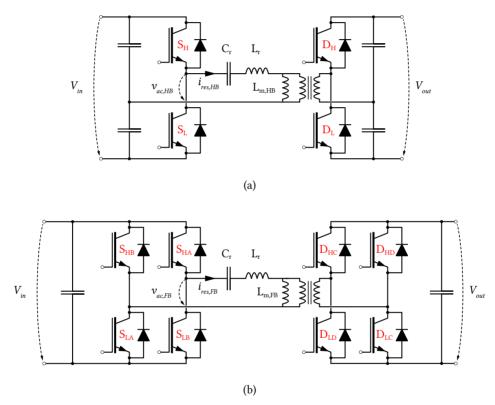

The Dual Active Bridge (DAB) topology is one of the best known and most widespread isolated bidirectional topology. With active switching cells on both sides of the MFT, it allows the voltage and the power flow to be controlled through the duty-cycle and the phase shift angle between the square-wave voltages applied on the primary and secondary, such as depicted in **Fig. 2.6**. In addition to the voltage adaptation possible through the MFT turn ratio, the dual active bridge (DAB) structure can be implemented in a modular way by connecting several DAB modules in series on the MV side to achieve higher voltage levels or reduce voltage stress on the semiconductors and by connecting them in parallel (ISOP structure) on the low voltage side to support large currents [66], such as depicted in **Fig. 2.10c**. This also allows to increase the overall reliability by adding redundant stages. The distribution of thermal stresses on the different stages is also possible. This is the principle used by the SST concept where the isolation stage is a combination of several DAB submodules [23], [67], [68].

The presence of a MFT allows a third port (or even more) to be coupled directly by an additional winding, resulting in an isolated and compact multiport structure (cf. **Fig. 2.10b**). This advanced version of DAB is reported in the literature as triple-active-bridge (TAB) [69], quadruple-active-bridge (QAB) [70] or generally multiple-active-bridge (MAB). Multiple windings offer great freedom in terms

of adaptation ratios and allow grids to be interfaced over a wide range of voltages. This is the case of the converter proposed by the authors of [70] which presents a QAB capable of interfacing, in theory, a high voltage grid, a low voltage grid and PV panels and a battery. Generally, in MAB structures, power control is performed by using phase shift methods, as presented in [71] and [72] (cf. **Fig. 2.7a**). A centralized control system allows the implementation of more complex controls (phase shift and duty cycle), in particular to improve the efficiency of the system by ZVS methods [73]. In addition, one way to reduce the number of semiconductors is to use half-bridges as indicated in [74] (cf. **Fig. 2.7b**), imposing a 50% duty-cycle. A three-phase version of this structure in order to achieve a higher power level is presented in [75].

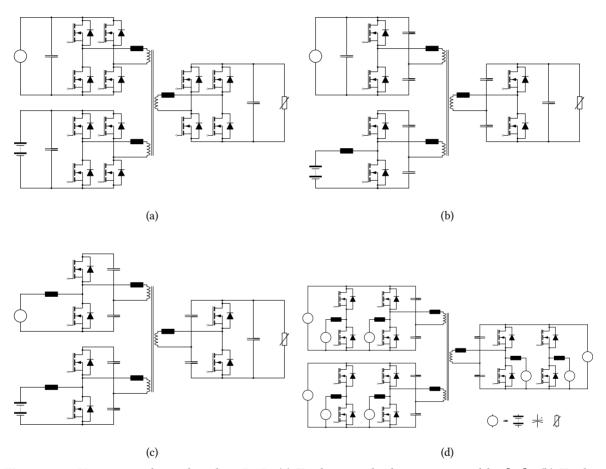

**Figure 2.7** Various topologies based on DAB: (a) Triple-active-bridge as presented by [71]. (b) Triple-half-bridge as presented by [74]. (c) Triple-half-bridge with current fed converters as presented in [76](2kW/28oV/20kHz). (d) TAB structure with three isolated DC-Bus couple converters as presented in [59].

Half-bridges also allow the use of current-fed structures using them in boost converter mode, as demonstrated by the authors of [76](cf. **Fig. 2.7c**). [59] presents a mix of isolated and non-isolated converter structure. Several sources and loads within the same voltage range are connected to each other by a common DC bus, while the different DC buses (of different voltages) are interfaced by a TAB stage (cf. **Fig. 2.7d**).

If the DAB has led to the SST for MV ratings, a multi-modular ISOP, or input-parallel-output-series (IPOS) combination of several MABs is very difficult to operate because of the instability consequent from the degree of freedom offered by power control. Indeed, an additional complex balancing stage for the different DC buses would be required. The authors of [77] show an example of the use of MABs in an ISOP structure, but only to share the stresses between the different ports and not in a multiport way (only one power flow is considered).

#### 2.2.3 Resonant converters

Although the DAB structure is relatively simple and the use of full-bridges and improved modulation schemes allow ZVS, the soft switching operation range remains limited and the trapezoidal waveforms make switching currents relatively high and cause substantial switching losses. In addition, the semiconductors suffer from high dv/dt constraints and voltage over-shoots [78]–[80]. These are some of the reasons to drive interest towards resonant converters. First, they offer extended soft switching operation range, and therefore benefit from limited switching losses which allow to reach higher switching frequencies [81]. Second, the resonant behavior offered by those structures implies quasi-sinusoidal current waveforms, and therefore a limited harmonic content requiring less filtering. Both result in a reduced volume dedicated the magnetics and passive components. This is why they are often used for high efficiency of high power density applications.

**Table 2.1** Different types of implementation of the resonant tank

|                     | LC series (SRC) | LC parallel (PRC) | LLC       | LCC     | CLL       |

|---------------------|-----------------|-------------------|-----------|---------|-----------|

|                     |                 |                   |           |         |           |

| Frequency variation | wide            | wide              | moderate  | narrow  | moderate  |

| Component stress    | lowest          | high              | low       | highest | high      |

| Soft Switching      | ZCS             | ZVS               | ZVS & ZCS | ZVS     | ZVS & ZCS |

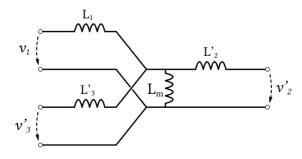

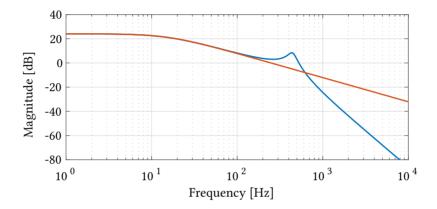

The series resonant converter (SRC) uses a resonant tank composed by the series connection of the transformer's leakage inductance and an additional resonant capacitor, and lead to the resonant topology that provides the smallest stresses on the components (cf. Table 2.1). SRC type is therefore particularly applicable for high voltage and high power converters [82]. Since the DC gain of such a structure is frequency sensitive (see Fig. 2.8a), it is generally operated at a fixed frequency and in discontinuous conduction mode (DCM) mode in order to benefit from ZCS for all transitions. In this operating mode, the voltage ratio is fixed and the output voltage closely follows the input voltage. Indeed, the amplitude of the resonant current, which is proportional to the power, depends on the excitation voltage applied to the resonant circuit, which relies on the voltage difference between the input and output DC buses. An increase in the load creates a slight drop in the voltage of the output bus and therefore an increase in the excitation voltage which leads to an increase in the power transferred. In other words, the power automatically adapts itself so that the two voltages are equal (except for any deviation due to losses) [83]. This behavior is associated with the DC transformer concept, which is characterized by its low output impedance and the lack of controllability of the system. Thus, the voltage regulation must be carried out on one side or the other by an additional stage. This is what is proposed in [84] which presents a SST based on the ISOP combination of submodule whose isolation stage is a SRC circuit. The balancing is ensured by this property of tight coupling of the inputs and the outputs while the voltage regulation must be carried out via the AC/DC input stage or the DC/AC output stage. Despite the advantages of soft-switching offered by the SRC circuits, the use of insulated-gate bipolar transistor (IGBT) results in switching losses due to the charges stored in the semiconductor [85], which explains an increased interest towards LLC topology.

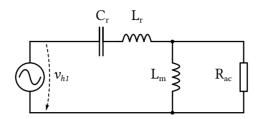

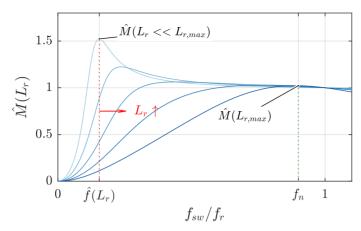

The LLC converter is a special case of the SRC family in which the magnetizing inductance is used as part of the resonant tank (cf. Table 2.1) and is dimensioned in such a way that the magnetizing current at switching instants is large enough to charge and discharge the output capacitances of the device to be turned off and the one to be turned on, respectively, in order to benefit from a zero voltage turn-on (ZVS) which becomes even more beneficial with high voltage class semiconductors[86]. Its characteristic allows a variable voltage gain through the switching frequency as shown in Fig. 2.8c. This is the principle commonly used at low voltage and low power in the field of switched-mode power supply with a wide range of voltage gain.

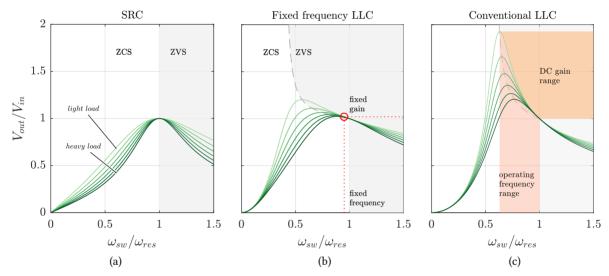

**Figure 2.8** DC gain characteristic over the normalized switching frequency for SRC converter (a), fixed frequency LLC converter (b) and conventional LLC converter (c). A capacitive behavior of the resonant tank (left hand side of the peak gain) implies that the voltage lags on the resonant current which allows for a ZCS turn-off of the primary side semiconductor. At the opposite, an inductive behavior (right hand side of the peak gain, gray area) implies that the resonant current lags on the voltage, which allows for ZVS turn-on of the primary side semiconductors. The operation of the converter below the resonant frequency allows a discontinuous conduction mode (DCM) of operation that ensures soft switching on the secondary side but forces a capacitive behavior in the case of the SRC whose peak gain is at  $\omega_{sw} = \omega_{res}$  for any load. In the case of the LLC converter, the displacement of the peak gain to the left thanks to the presence of the magnetizing inductance allows the converter to operate below the resonance frequency while remaining in the inductive area benefiting from ZVS. In addition, the fixed frequency operation allows a DC gain almost independent from the load, in contrast to the conventional LLC converter, which allows the DC gain to be varied with the switching frequency but becomes very sensitive to the load.

However, it is also possible to use an LLC converter in "DC transformer" mode by operating it at a fixed frequency and close to the resonant frequency (cf. **Fig. 2.8b**). In this case, the DC gain becomes quasi independent from the load and the tight coupling between input and output voltages is achieved,

as in the case of the SRC converter, while having the advantage of the ZVS. Even though phase shift control methods (needing therefore active rectification) or PWM modulation methods are feasible on the resonant stage [87]–[89], they go against the principle of load independent behavior offered by a DC-transformer. This is why, like the SRC topology, an LLC converter operated at a fixed voltage ratio requires an additional stage for the voltage regulation.

This additional stage introduces more complexity and losses but allows also a functional separation between the regulation stage and the isolation plus voltage adaptation stage which facilitates an optimal design of the components [90]. This is what the authors of [91], [92] propose with the concept of power electronic traction transformer (PETT). This SST concept dedicated to traction and consisting of an ISOP combination of submodules each including a DC transformer has been demonstrated at the industrial level with a MV prototype in [93]. Using nine submodules with 6.5 kV semiconductors, MV voltages of 15 kVac for a power of 1.2 MV A were achieved.

The authors of [94] demonstrate the use of an LLC converter in a bidirectional manner which shows its feasibility and its ZVS performances with a split resonant tank distributed on both the primary and the secondary of the MFT. The authors of [95] shows how to use a bidirectional LLC converter, but with a single tank. They prove the feasibility of such operation, but also point out of the higher switching losses in backward mode since the turn-off current (magnetizing current) is much higher on the low voltage side. In addition, the use of a full bridge for voltage control makes this solution less attractive, in terms of efficiency, than the basic DAB converter, for bidirectional use.

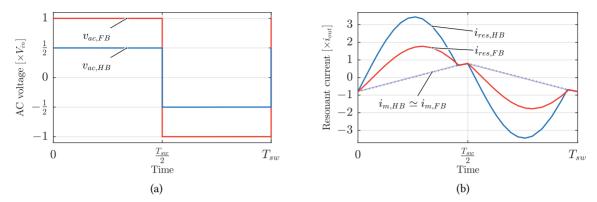

Nevertheless, the use of a fixed switching frequency implies the possibility of extending the concept to a multiport. As its frequency is common to all the ports and does not vary, the resonant tank can be distributed over several ports.

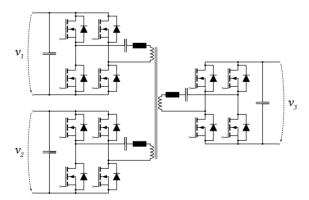

A three-port LLC converter was introduced in [97] and consists of a three-winding medium-frequency transformer with distributed resonant capacitors tuned to the leakage inductors to create a resonant tank. Each electrical port can be configured as a half or full bridge, and all ports are switched to the resonant frequency with the same phase and a duty cycle of 50%. The authors presented the configuration in which one port acts as a source, while two other ports act as a load. Experiments with a low power setup (300W) show good load self-regulation. In addition, the authors of [96] demonstrate

**Figure 2.9** Multiport resonant converter such as considered in [96]. The resonant tank is split between the three sides.

the operation of a similar topology in both single-input-dual-output and dual-input-single-output modes and highlight the good ZVS capabilities over the full power range for these two operating modes.

In addition to the work presented in [98], the authors of [99] present a similar topology where two ports are configured as sources and are equipped with resonant capacitors, while the third behaves like a load and has only one rectifier. They demonstrated that it is possible to regulate the power flow and distribute the load between the sources by means of phase shift control but at the cost of the loss of part of ZVS capabilities.

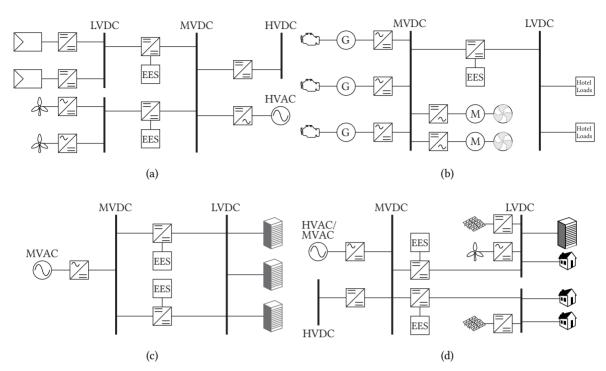

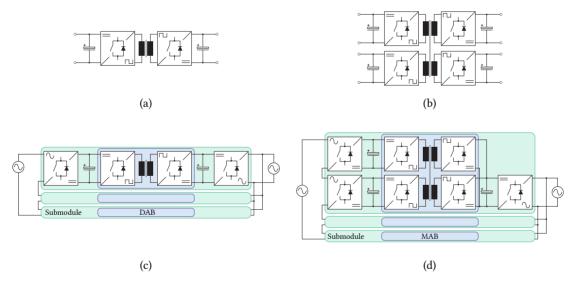

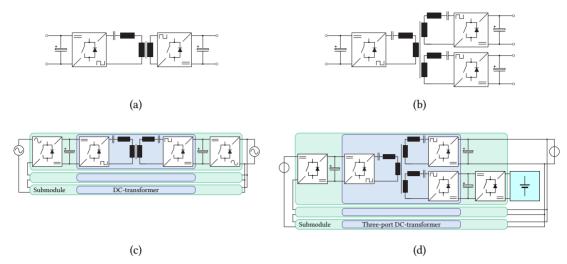

In brief, the DAB structure has proven its performances and it controllability as isolation stage and voltage adaptation stage for DC-DC converters. This structure has been used first in multi-modular type of converters, resulting in the concept of SST, and second as a possible way to provide multiport conversion with the various MAB converters. Additionally the ISOP combination of multiple MAB has been explored with the cascaded half-bridge rectifier (CHBR-MAB) in [77] but remains feasible only in a single-input-single-output structure, without providing additional power ports. The **Fig. 2.10** gives an overview of the various converters based on the DAB structure.

On the other hand, the increased efficiency provided by the SRC or LLC structure and it simplicity of control when used in DC-transformer has lead to the development of multi-modular structures [91] and multiport SRC converters [96]. The MEG converter presented in this work is the multi-modular-multiport version of the LLC converter with the advantage, in relation to DAB based structures, to provide additional power ports, dedicated to storage elements. The **Fig. 2.11** summarizes multi-modular and multiport converters based on a resonant structure.

**Figure 2.10** Various converters based on DAB structure. (a) basic DAB, (b) MAB: the multiport version of the DAB, (c) SST [67]: the ISOP version of the DAB, (d) CHBR-MAB [77]: the multiport-ISOP version of the DAB.

**Figure 2.11** Various converters based on LLC structure. (a) SRC/LLC converter. basic structure of the DC transformer, (b) three-port resonant converter, (c) PETT [91]: the ISOP version of the DC-transformer, (d) proposed MEG: the multiport-ISOP version of the DC-transformer with integrated storage.

# 2.3 Basic switching cells topologies

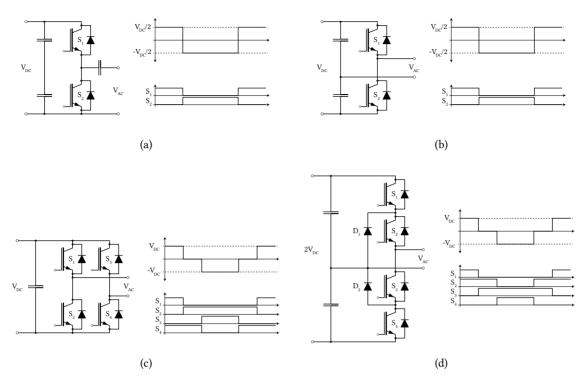

The isolation stage, MFT or resonant stage are usually driven by two-levels or three-levels elementary converters which comprise the half-bridge (HB), the full-bridge (FB) and the neutral-point-clamped converter (NPC).

The first type, the half-bridge consists of two switches and two capacitors that can be arranged in two different ways: in series-output configuration, or split DC-bus configuration. In the first case, one of the capacitors sees all the voltage of the DC-bus and the other, placed at the output of the converter serves to filter the DC voltage and sees only half of the DC-bus voltage but is crossed by the entire current (cf. **Fig. 2.12a**). In the second case, both capacitors are placed in series and both see half of the DC-bus voltage as well as half of the current. For this reason this structure is preferable in high power applications, when voltages and currents are high and thermal stresses need to be well distributed (cf. **Fig. 2.12b**). In both cases, only two levels of voltages are possible at the output  $(+V_{DC}/2)$  and  $-V_{DC}/2$  and the lack of substantial modularity is often compensated by a gain in efficiency when used in resonant structures.

The second type, the full-bridge (cf. **Fig. 2.12c**), requires four switches but no split DC-bus. It allows three output voltage levels  $+V_{DC}$ ,  $-V_{DC}$  and 0, when the current flows through one of the freewheeling diodes. This type of converter therefore allows a modulation controlled in duty cycle (including zero vector), and is commonly used in applications requiring pulsed modulation.

The third type, the neutral point clamped (NPC), is more complex since it includes four controlled switches with their anti-parallel diodes, two capacitors and two additional diodes (cf. **Fig. 2.12d**). Since the switches are configured in series, the structure can handle higher voltage levels for the same device blocking voltage, making it a popular converter in MV applications. This structure allows three output voltage level,  $+V_{DC}/2$ ,  $-V_{DC}/2$  and 0, or in other terms according to the switch configuration,  $+V_{DC}$ ,  $-V_{DC}$  and 0. The DC-bus voltage is equal to  $2V_{DC}$  in comparison to the full-bridge.

**Figure 2.12** (a) Half-Bridge with series-output capacitor. (b) Half-Bridge with split DC-bus. (c) Full-Bridge. (d) Neutral Point Clamped.

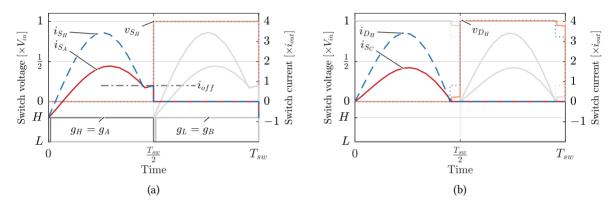

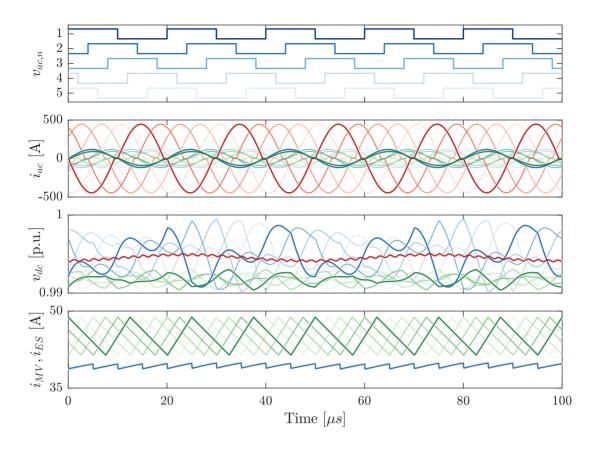

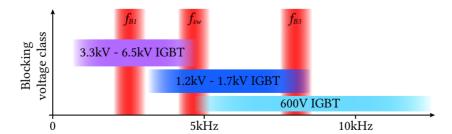

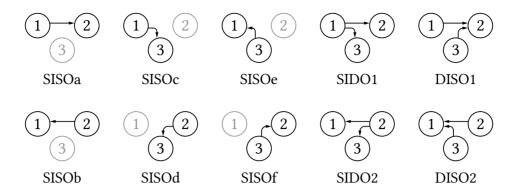

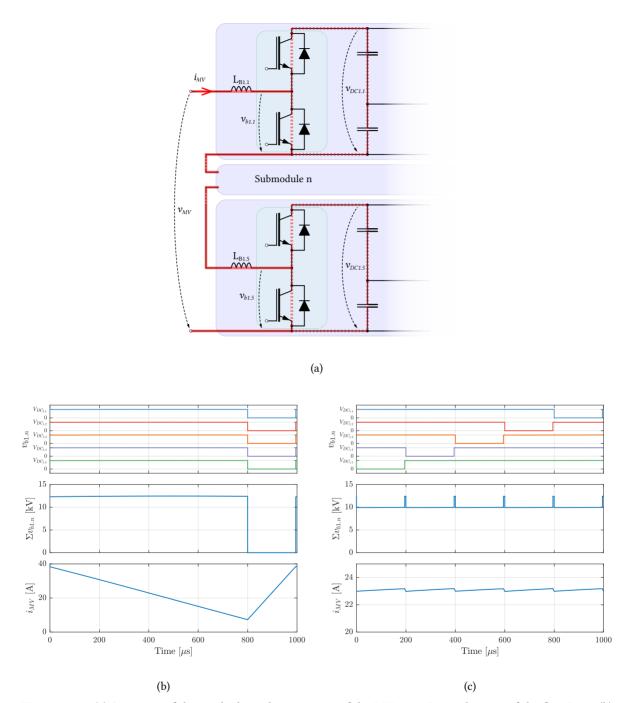

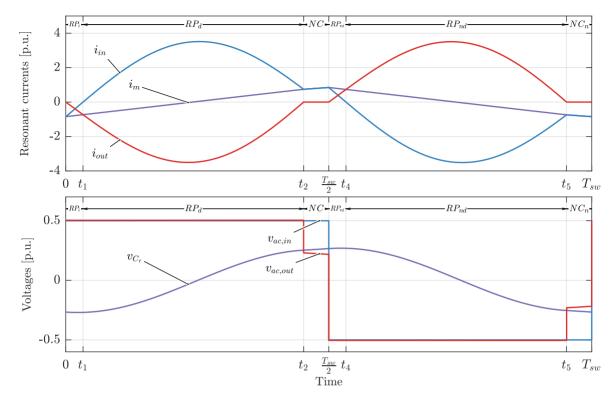

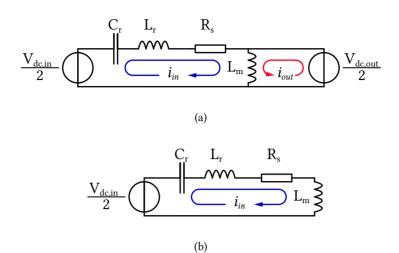

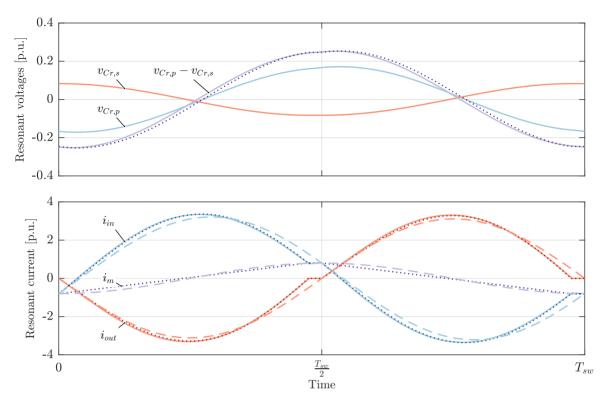

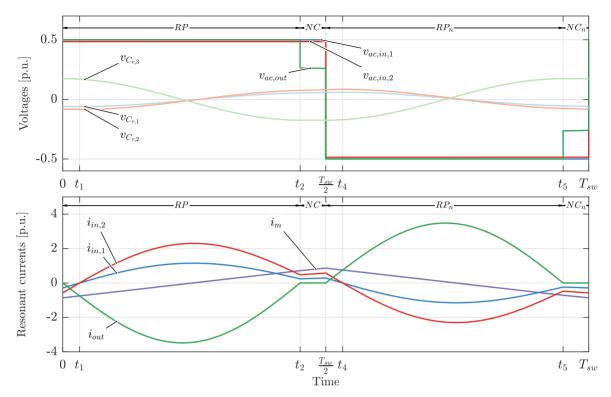

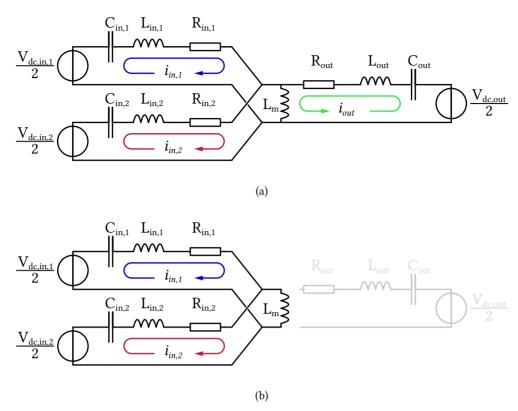

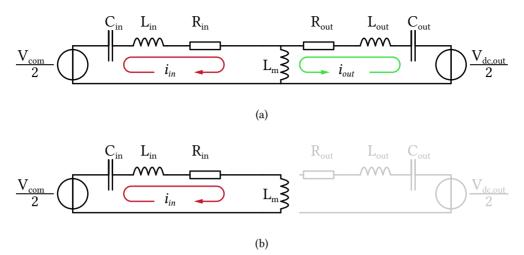

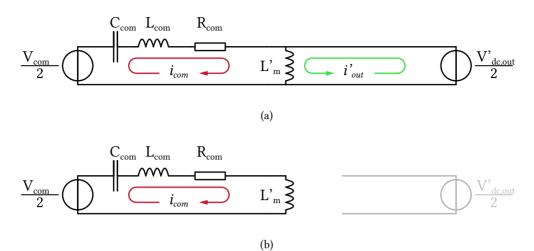

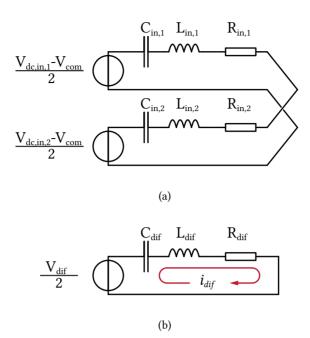

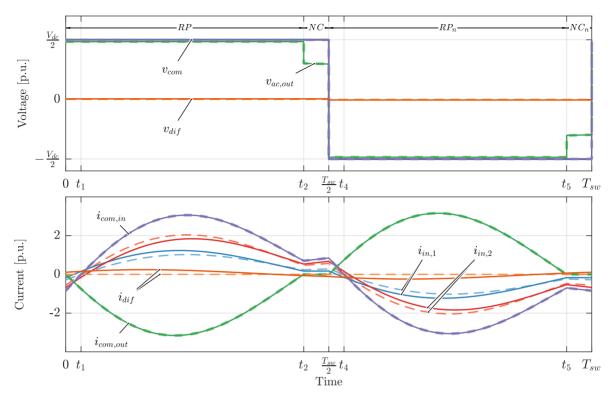

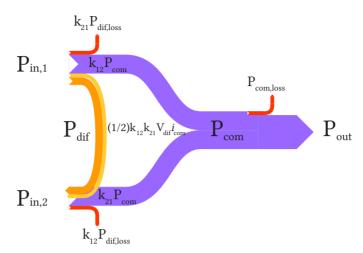

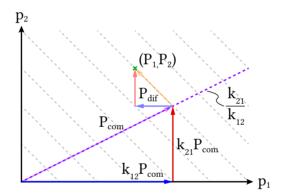

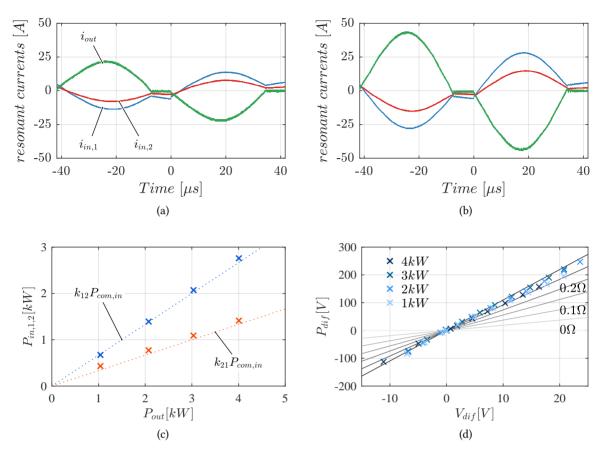

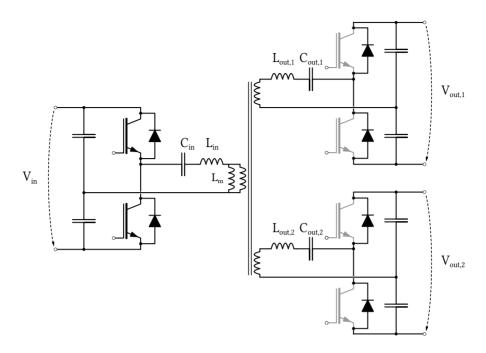

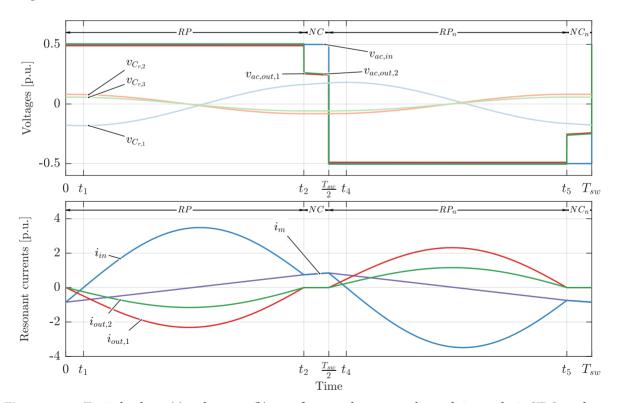

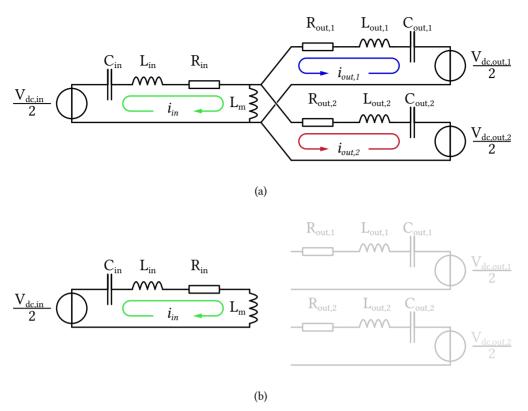

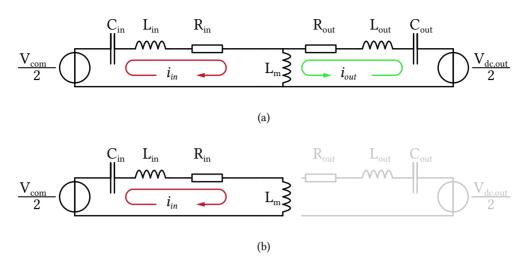

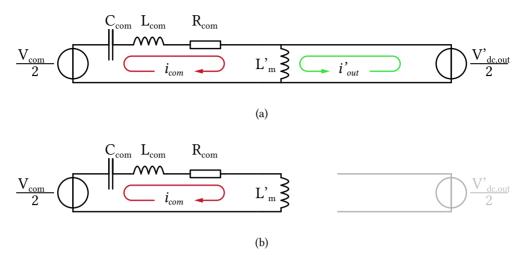

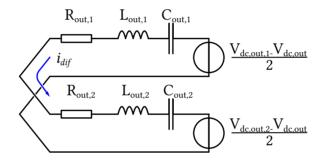

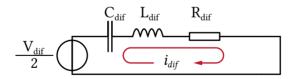

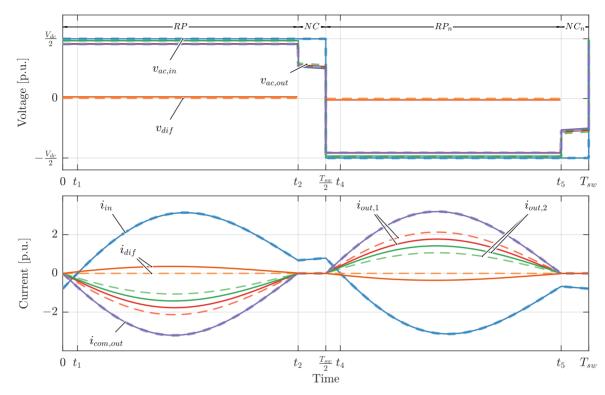

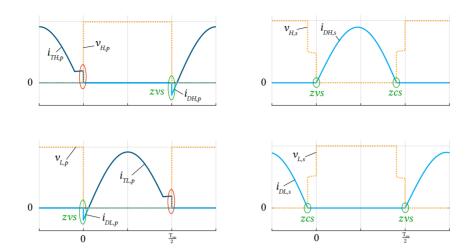

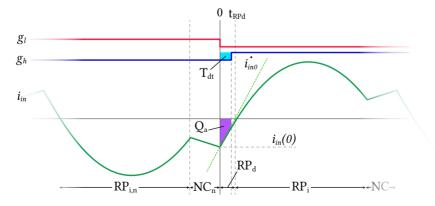

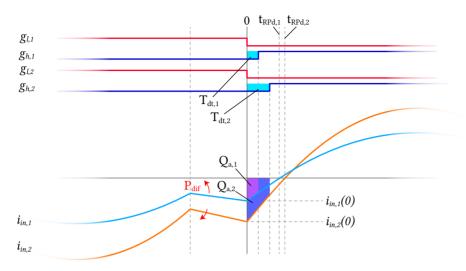

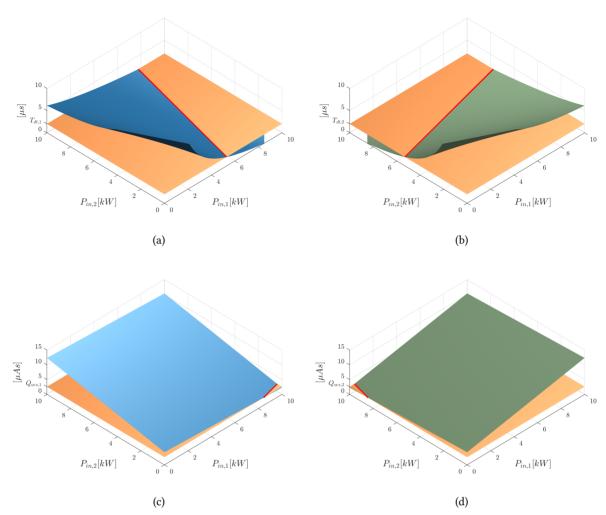

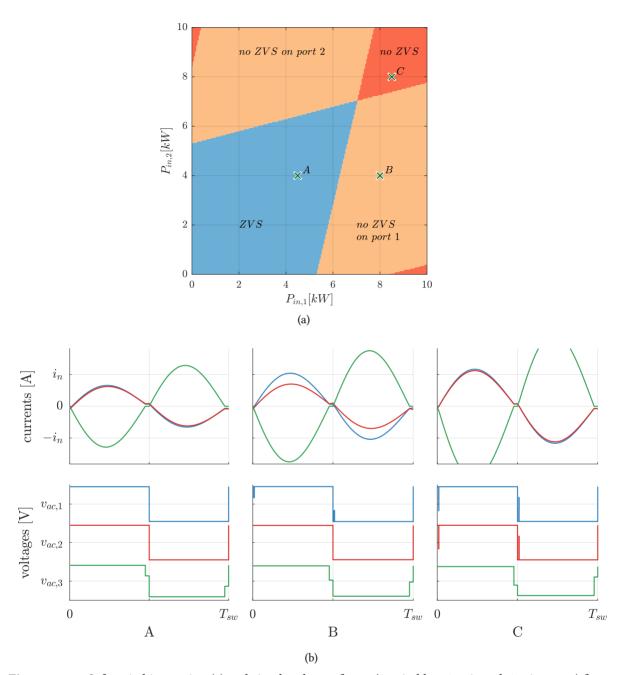

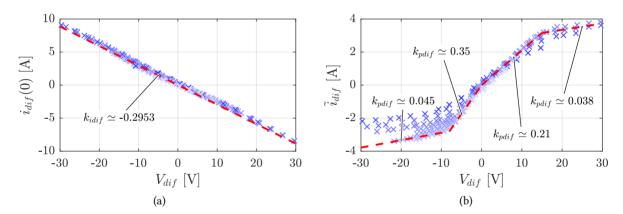

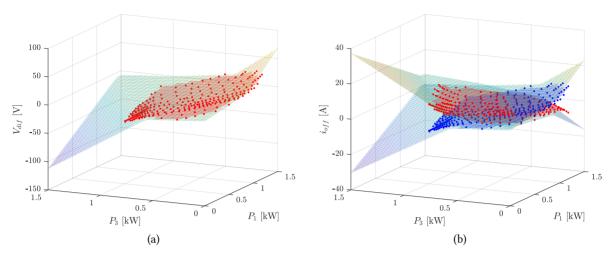

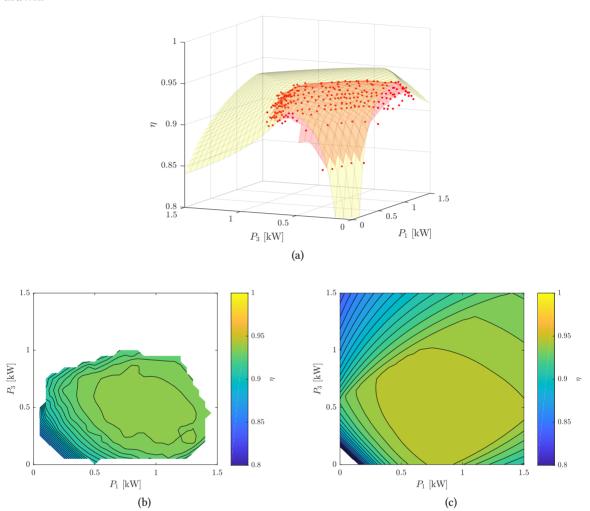

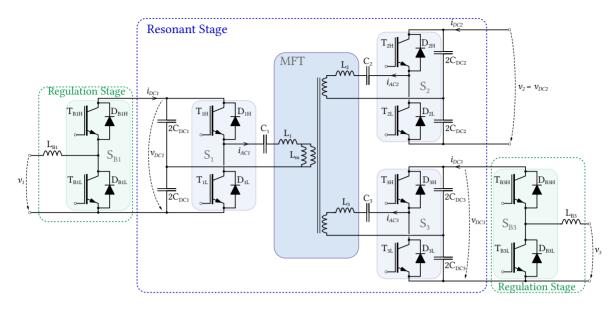

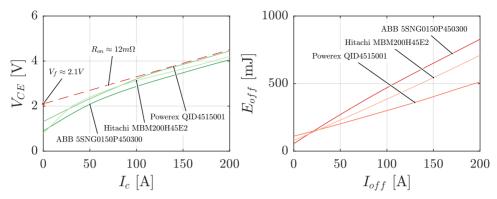

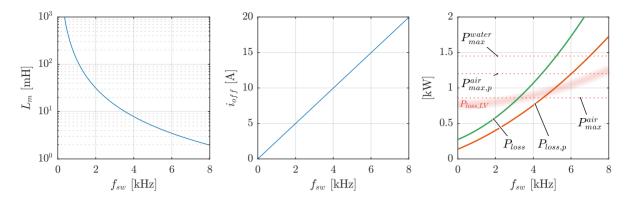

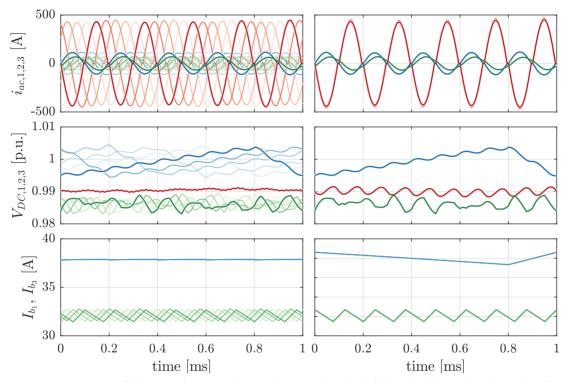

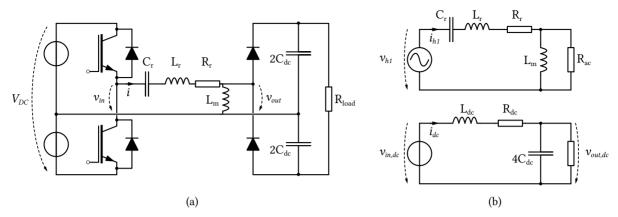

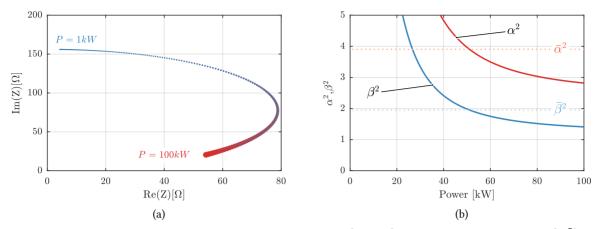

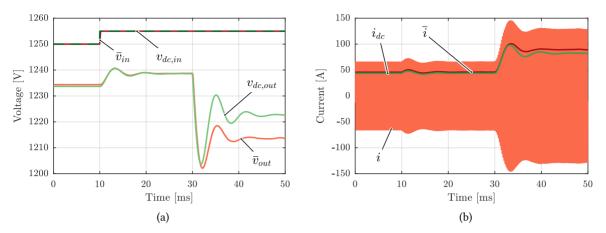

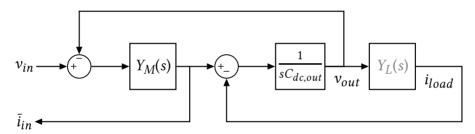

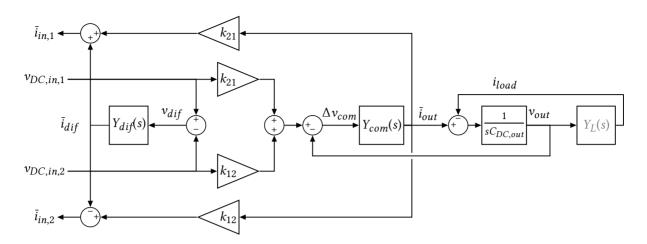

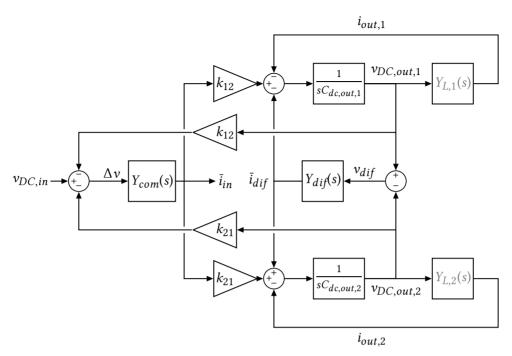

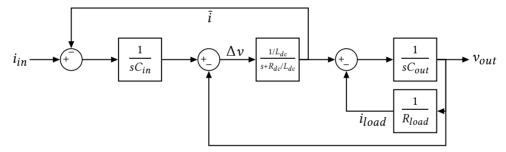

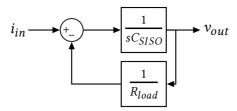

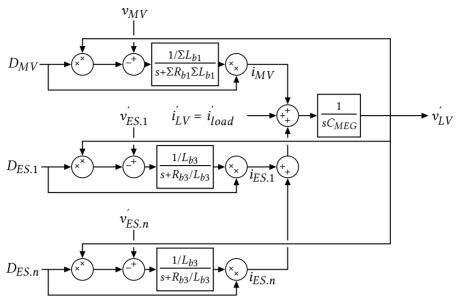

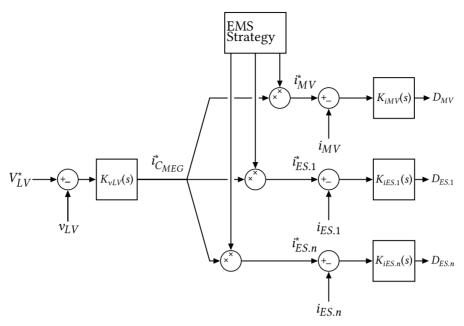

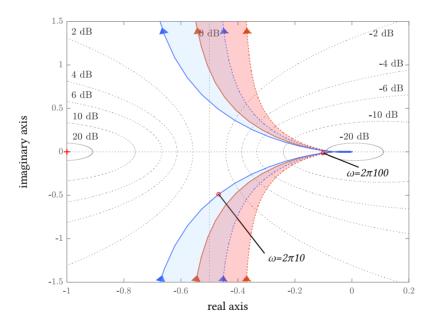

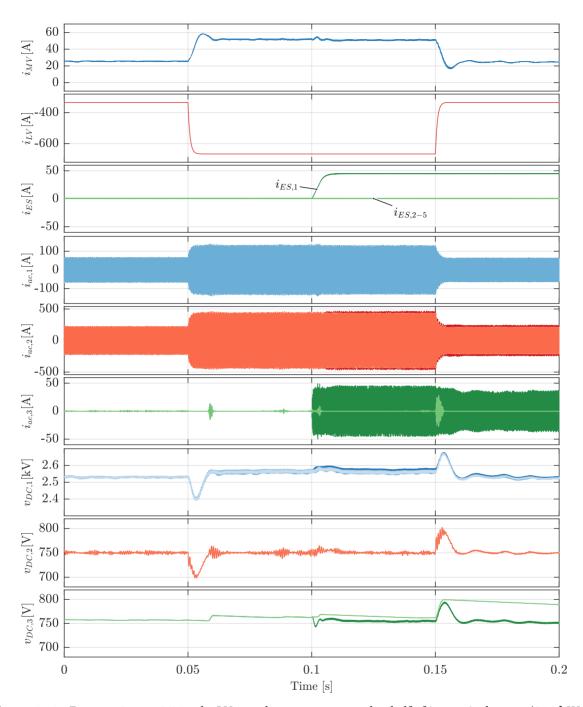

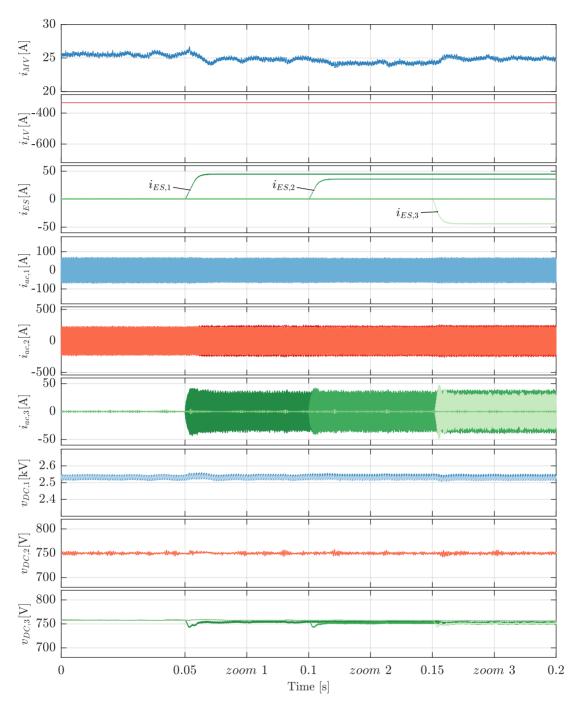

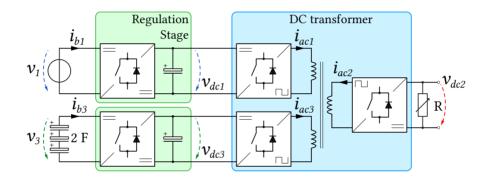

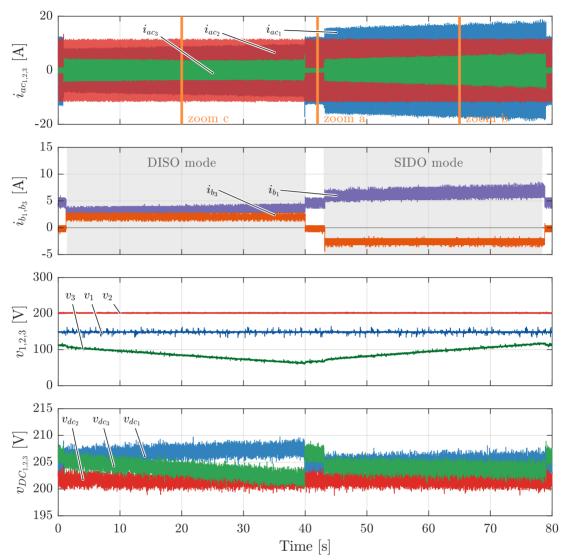

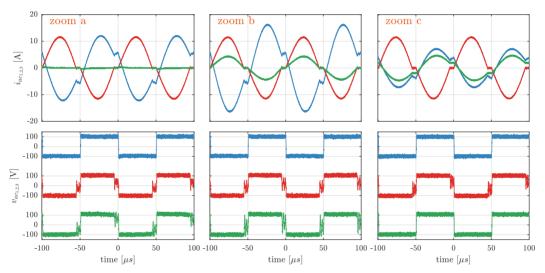

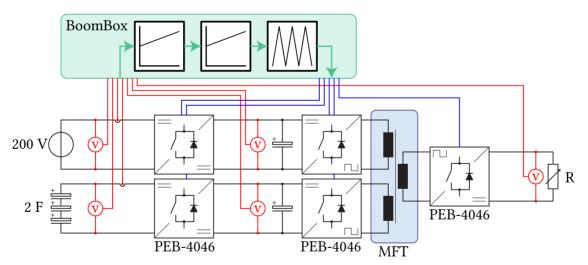

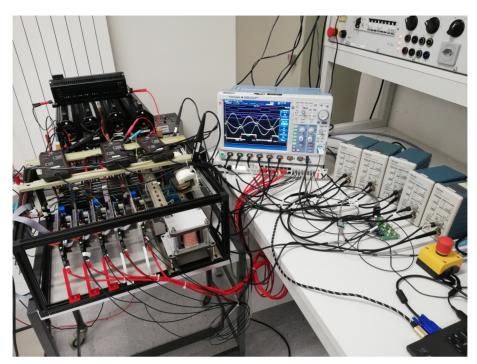

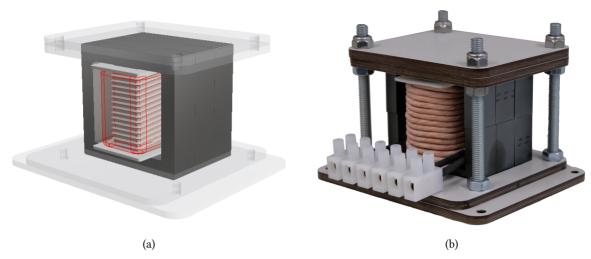

A LLC converter operated as a DC-transformer needs only two levels modulation on the primary side, without any active rectification or phase shift/duty cycle control [100]. Thus, on the secondary side, the stage behaves as passive rectifier and, in terms of switching pattern, there is no difference between converters based on half-bridges (cf. **Fig. 2.13a**) or full-bridges (cf. **Fig. 2.13b**). Moreover, resonant circuits driven by a NPC stage have also been explored in [101], but only in order to decrease the voltage stress on the semiconductors.