## Tri-gate technologies for high-performance power GaN devices

Thèse N°9652

#### Présentée le 9 août 2019

à la Faculté des sciences et techniques de l'ingénieur Laboratoire de dispositifs semiconducteurs de puissance Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

#### Jun MA

Acceptée sur proposition du jury

Prof. G. De Micheli, président du jury Prof. E. D. N. Matioli, directeur de thèse

Prof. D. Jena, rapporteur Prof. R. Quay, rapporteur

Prof. N. Grandjean, rapporteur

# Acknowledgements

First, I would like to express my very great appreciation to my advisor Prof. Elison Matioli. It has been such a pleasure to be his student and work on such an exciting field. His patience and trust always encourage me to work on new approaches, his training makes me a better and more comprehensive researcher, and the knowledge I learnt from him, not only in technical but also in many other aspects, will be highly valuable in my life.

I would like to thank my thesis committee Prof. Giovanni De Micheli, Prof. Nicolas Grandjean, Prof. Debdeep Jena and Prof. Rüdiger Quay. Their insights and advices are highly valuable for this work. Particularly I would like to thank Prof. Nicolas Grandjean for sharing the MOCVD in such a supportive manner.

I wish to acknowledge the high-quality GaN-on-Si wafers provided by Dr. Kai Cheng at Enkris Inc., which are of great importance in demonstrating the high-performance tri-gate devices and in developing the multi-channel tri-gate technology.

I am particularly grateful for the assistance given by my colleagues Dr. George Kampitsis, Catherine Erine, Giovanni Santoruvo and Reza Soleiman Zadeh in power circuits, device fabrication, e-beam lithography and thermal measurements, respectively. I wish to extend my gratitude to also other colleagues at POWERlab for their inspiring suggestions and helpful discussions, including Dr. Chao Liu, Riyaz Abdul Khadar, Minghua Zhu, Taifang Wang, Luca Nela, Mohammad Samizadeh, Remco van Erp, Armin Jafari, and Nirmana Perera.

I would also like to thank Muriel Bardet for her great help, and all the staff in CMi and ICMP clean-rooms at EPFL for their technical support.

Finally, I am very grateful to my mother Zhifang Liu and father Shuyuan Ma for their endless love and support. I am lucky to be your son, and I owe so much to you. This thesis is dedicated to you.

Lausanne, April 2019

i

## **Abstract**

GaN-based electronic devices have great potential for future power applications, thanks to their wide band-gap, high breakdown electric field, and high electron mobility. In addition, these devices can be integrated on large-size Si substrates and enable novel monolithic power integrated circuits (ICs), providing an exceptional cost-effective GaN-on-Si platform to revolutionize current power conversion systems with much higher power density and greater energy efficiency.

Despite all these remarkable advantages, the performance of current GaN-on-Si power devices is still far away from the prospect promised by this material, and further enhancement requires a significant reduction in the ON-resistance of a unit area ( $R_{ON}$ ·A) and an increase in the breakdown voltage ( $V_{BR}$ ) of the device. Moreover, the family of GaN-on-Si power devices is not yet complete, as high-voltage power GaN-on-Si Schottky barrier diodes (SBDs) are still missing on the market in spite of the great demand, restricting the full functionality of GaN-on-Si power solutions.

This thesis proposes tri-gate technologies to overcome these challenges. The common drawback of increased  $R_{\rm ON}$  in tri-gate GaN high electron mobility transistors (HEMTs) is resolved, and the exceptional merit of the tri-gate for high  $V_{\rm BR}$  is discovered. A novel slanted tri-gate structure is invented to improve the  $V_{\rm BR}$  for GaN-on-Si metal-oxide-semiconductor HEMTs (MOSHEMTs) at a fixed A, resulting in a much reduced  $R_{\rm ON}\cdot A$  product and a record high-power figure-or-merit among GaN-on-Si power transistors. High-voltage power GaN-on-Si SBDs are also achieved based on a judicious design of the tri-gated anode region, demonstrating unprecedented reverse-blocking performance that is dramatically improved from existing technologies, along with excellent integratability with GaN transistors, which is demonstrated in reverse-blocking GaN MOSHEMTs with record voltage-blocking capabilities. Furthermore, a novel multi-channel tri-gate structure is developed in this thesis, deploying multiple 2DEG channels to dramatically reduce the  $R_{\rm ON}\cdot A$  value while maintaining a high  $V_{\rm BR}$  thanks to the tri-gate, resulting in novel multi-channel tri-gate power GaN-on-Si normally-ON/OFF MOSHEMTs and SBDs with state-of the-art performance.

The results in this thesis reveal the extraordinary value of the tri-gate in enhancing the  $V_{BR}$  for high-voltage GaN power devices, demonstrate high-performance power GaN-on-Si SBDs that can be rated for 650 V, and unleash the enormous potential of the multi-channel tri-gate approach to dramatically

improve the performance of power GaN devices, offering a complete and effective platform towards the full capabilities of GaN for future efficient power conversion.

## Keywords

GaN, power, HEMTs, SBDs, tri-gate, tri-anode, slanted tri-gate, multi-channel tri-gate, breakdown voltage, on-resistance, leakage current.

# Contents

| Ackno   | wledgements                                                    | i   |

|---------|----------------------------------------------------------------|-----|

| Abstra  | et                                                             | iii |

| Conter  | nts                                                            | v   |

| List of | Figures                                                        | vii |

| List of | Tables                                                         | xv  |

| Chapte  | er 1 Introduction                                              | 1   |

| 1       | .1 Advantages of GaN for efficient power conversion            | 1   |

| 1       | .2 Cost-effective GaN-on-Si platform                           | 4   |

| 1       | .3 Current GaN-on-Si power device technologies                 | 7   |

| 1       | .4 Major challenges                                            | 10  |

| 1       | .5 Thesis outline                                              | 12  |

| Chapte  | er 2 Tri-gate technologies for GaN devices                     | 13  |

| 2       | .1 Introduction                                                | 13  |

| 2       | .2 Impact of fin width on transfer characteristics             | 15  |

| 2       | Dependence of threshold voltage on the fin width               | 17  |

|         | 2.3.1 Effect of the increased gate capacitance                 | 18  |

|         | 2.3.2 Effect of the strain relaxation and sidewall depletion   | 19  |

| 2       | .4 Eliminating degradation in on-resistance and output current | 21  |

|         | 2.4.1 Effect of the fin width                                  | 21  |

|         | 2.4.2 Effect of the fin length                                 | 22  |

|         | 2.4.3 Effect of the filling factor                             | 22  |

| 2       | .5 Additional trench-conduction channels                       | 24  |

|         | 2.5.1 Trench conduction in normally-on devices                 | 25  |

|         | 2.5.2 Trench conduction in normally-off devices                | 27  |

| 2       | .6 Improving thermal performance                               | 29  |

| 2       | .7 Reducing gate charge                                        | 30  |

| 2       | .8 Conclusion                                                  | 31  |

| Chapt  | ter 3 | Novel tri-gate field plates for high-voltage applications            | . 33 |

|--------|-------|----------------------------------------------------------------------|------|

| 3      | 3.1   | Introduction                                                         | . 33 |

| 3      | 3.2   | Principle and Concept                                                | . 34 |

| 3      | 3.3   | High-voltage tri-gate GaN-on-Si MOSHEMTs                             | . 35 |

| 3      | 3.4   | High-performance slanted tri-gate GaN-on-Si power MOSHEMTs           | . 40 |

| 3      | 3.5   | Conclusion.                                                          | . 42 |

| Chapt  | ter 4 | Tri-gate technologies for high-voltage and low-leakage SBDs          | . 45 |

| ۷      | 4.1   | Introduction                                                         | . 45 |

| ۷      | 4.2   | High-voltage tri-anode GaN-on-Si SBDs with low leakage current       | . 46 |

| ۷      | 4.3   | Field plate design for low leakage current in lateral GaN SBDs       | . 50 |

| ۷      | 4.4   | 2000 V slanted tri-gate SBDs with ultra-low leakage current          | . 55 |

| ۷      | 4.5   | 650 V reverse-blocking MOSHEMTs with slanted tri-gate Schottky drain | . 60 |

| ۷      | 4.6   | Conclusion                                                           | . 66 |

| Chapt  | ter 5 | Multi-channel tri-gate technologies for ultra-low on-resistance      | . 69 |

| 4      | 5.1   | Introduction                                                         | . 69 |

| 4      | 5.2   | High-voltage normally-on/off multi-channel tri-gate GaN MOSHEMTs     | . 71 |

| 4      | 5.3   | High-performance multi-channel tri-gate GaN power SBDs               | . 78 |

| 4      | 5.4   | Multi-channel tri-gate GaN devices with ultra-low on-resistance      | . 84 |

| 4      | 5.5   | Conclusion                                                           | . 89 |

| Chapt  | ter 6 | Conclusion                                                           | . 90 |

| 6      | 6.1   | Achieved results                                                     | . 90 |

| 6      | 6.2   | Future development                                                   | . 91 |

| Refere | ence. |                                                                      | . 93 |

| Curri  | culur | n Vitae                                                              | 105  |

| Apper  | ndix- | 1: the growth recipe for the 10x-channel GaN heterostructure         | 111  |

| Apper  | ndix- | 2: the code for the ATLAS simulation of SBDs                         | 135  |

| Apper  | ndix- | 3: the process flow of tri-gate GaN devices                          | 141  |

### List of Figures

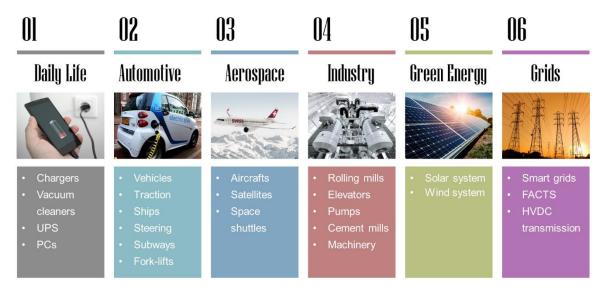

Figure 1.2: (a) Specific ON-resistance versus breakdown voltage benchmarks of Si, SiC and GaN power devices, showing the reduced resistive loss and enhanced power rating in GaN devices, obtained from https://www.eetimes.com/document.asp?doc\_id=1272514. (b) Comparison of switching losses in GaN and Si power transistors versus switching frequency, revealing the reduced switching loss and increased operation frequency of GaN devices, obtained from https://www.pi-innovo.com/gan/. (c) The much higher operation frequency of GaN power devices can greatly miniaturize current power conversion systems, resulting in a much higher power density, obtained from https://industrial.panasonic.com/ww/products/semiconductors/powerics/ganpower.... 2

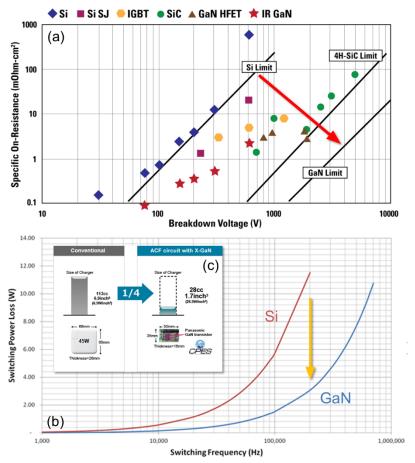

Figure 1.3: (a) Cross-sectional schematic of an AlGaN/GaN high electron mobility transistor (HEMT). (b) Simulated energy band structure of the AlGaN/GaN heterostructure, showing the 2DEG channel at the AlGaN/GaN interface. (c) A monolithic power integrated circuits (ICs) based on the AlGaN/GaN heterostructure. The circuit was demonstrated by Panasonic, and the image was obtained https://www.psma.com/sites/default/files/uploads/tech-forumssemiconductor/presentations/is164-unlocking-power-gan.pdf. (d) The significant advantages of all-Navitas, which in-GaN **ICs** presented by was https://www.psma.com/sites/default/files/uploads/tech-forums-semiconductor/presentations/is94-

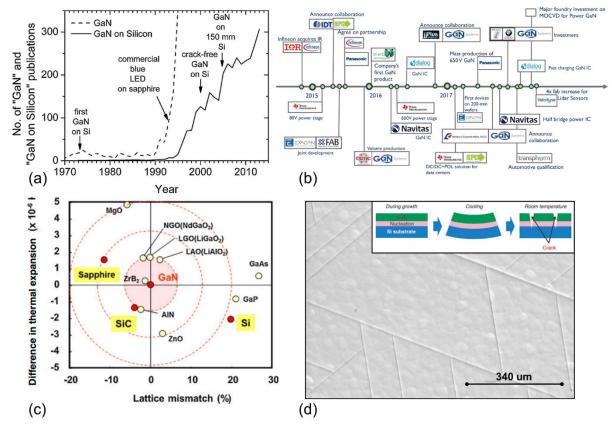

Figure 1.4: (a) Number of publications regarding GaN and GaN-on-Si, obtained from Ref. [10]. (b) Business models of current GaN power industry, revealing its bloom after the successful development of 6 inch GaN-on-Si technologies, which was generated by Yole and obtained from https://www.systemplus.fr/gan-power-device-industry-the-supply-chain-is-acting-to-support-market-growth/. (c) Summary of lattice and thermal mismatches between GaN and various substrates for epitaxial growth, obtained from https://iopscience.iop.org/article/10.7567/JJAP.53.100214/meta. (d) Nomarski optical micrograph showing the cracking of GaN grown on Si substrates, which was taken in HKUST. The inset in (d) shows the formation of cracks due to the thermal mismatch between GaN and Si, obtained from NTT at https://www.ntt-review.jp/archive/ntttechnical.php?contents=ntr201404fa8.html. .. 4

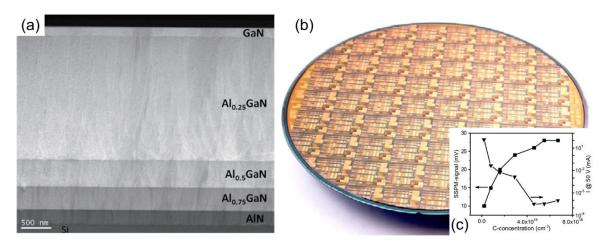

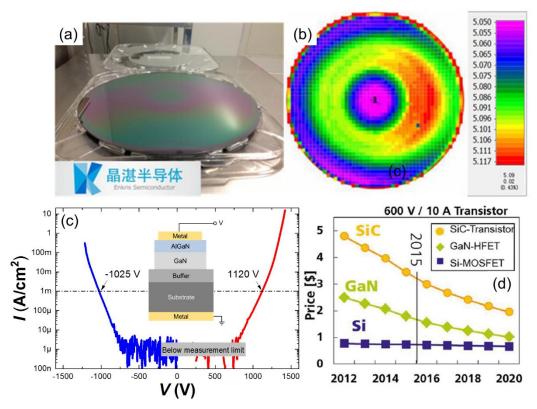

Figure 1.6: (a) A 8 inch creack-free GaN-on-Si wafer with 5 μm thick epi layers for 650 V-rated power devices, and (b) the measured total thickness of the epi layers across the entire wafer, which were grown by Enkris and obtained from https://www.pntpower.com/enkris-semiconductor-shows-1600v-breakdown-gan-hemt-on-200mm-si-wafer/. (c) Room-temperature vertical breakdown characteristics of a 5 μm-thick AlGaN/GaN-on-Si wafer. (d) Expected selling price of a single 600V/10A transistor based on Si, SiC and GaN, obtained from https://www.led-

| professional.com/resources-1/articles/led-retrofit-based-on-algan-gan-on-si-field-effect-transistor-drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

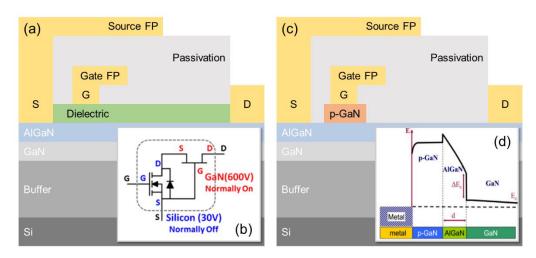

| Figure 1.7: (a) Schematic of a normally-ON GaN-on-Si MISHEMT. (b) Schematic of the cascode configuration, which was obtained from https://cpes.vt.edu/library/viewnugget/329. (c) Schematic of a normally-OFF GaN-on-Si HEMT using the p-GaN cap technology. (d) The energy band structure of the p-GaN/AlGaN/GaN heterostructure, which was obtained from https://www.sciencedirect.com/science/article/pii/S1369800117316554#f00057                                                                                                                                                                                                                                                                                   |

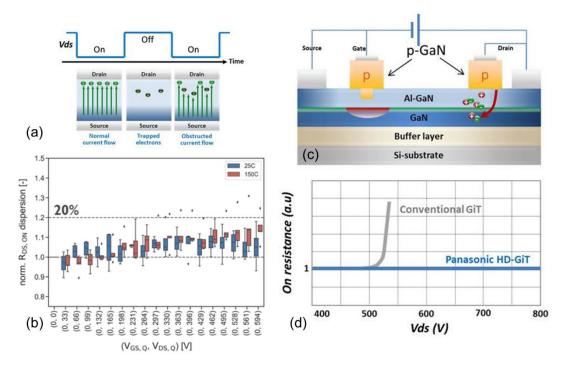

| Figure 1.8: (a) Schematic showing the physical origin of the current collapse. (b) Dynamic <i>R</i> <sub>ON</sub> dispersion of 600 V-rated GaN-on-Si HEMTs versus OFF-state drain voltage, demonstrated by IMEC. (c) Schematic of a normally-OFF GaN-on-Si HEMT with hybrid hole-injection drain electrode, invented by Panasonic. (d) The enhancement in dynamic performance of the device using the hybrid drain electrode. (a), (c) and (d) are obtained from https://na.industrial.panasonic.com/products/semiconductors/x-gan-power/power-devices, and (b) was obtained from https://www.electronicsweekly.com/news/business/imec-offers-gan-si-fab-technology-transfer-2017-06/.                                 |

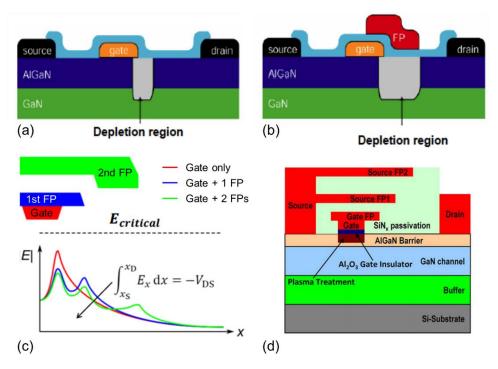

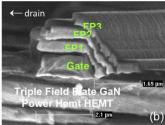

| Figure 1.9: (a) and (b) Schematics showing the effect of the FP, obtained from http://uef.fei.stuba.sk/moodle/mod/book/view.php?id=7920&chapterid=87. (c) Effect of FPs in distributing the electric field in GaN HEMTs, which was obtained from http://home.iitk.ac.in/~chauhan/ASM-HEMT_YSChauhan.pdf. (d) Schematic of the GaN-on-Si power MOSHEMTs with three FPs, demonstrate by HRL in Ref. [27]                                                                                                                                                                                                                                                                                                                  |

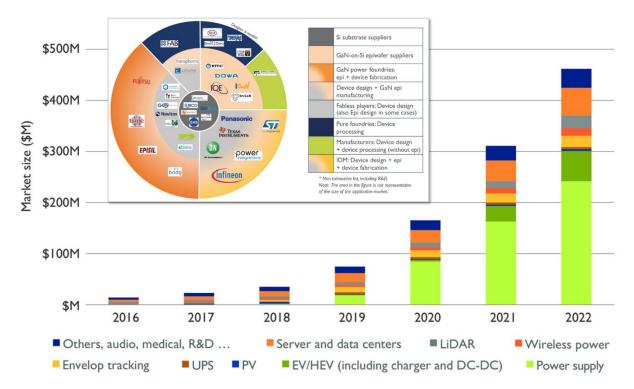

| Figure 1.10: The market size of GaN power devices, split by applications. The inset shows an overview of the power GaN industry in 2019. Both figures were obtained from http://www.yole.fr/2014-galery-CS.aspx#I0007a5e9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

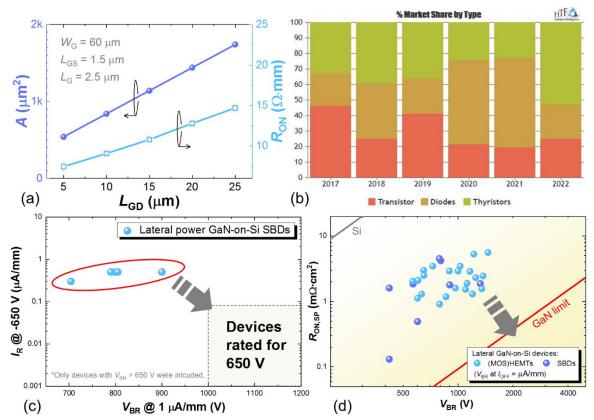

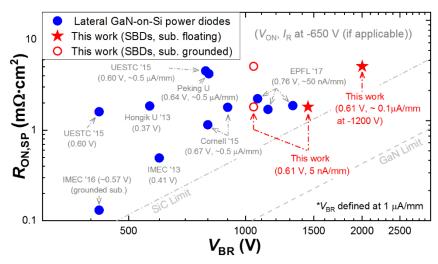

| Figure 1.11: (a) Dependence of area ( $A$ ) and ON-resistance ( $R_{\rm ON}$ ) of GaN-on-Si MOSHEMTs on the gate-to-drain distance ( $L_{\rm GD}$ ). (b) Market share of power semiconductor devices by device type, obtained from https://www.openpr.com/news/1001380/Latest-Report-of-Discrete-Power-Device-Market-Size-Share-Growth-Trends-and-Forecast-2018-2022.html. (c) Reverse leakage current ( $I_{\rm R}$ ) and $V_{\rm BR}$ of current lateral power GaN-on-Si SBDs. (d) Specific $R_{\rm ON}$ ( $R_{\rm ON,SP}$ ) versus breakdown voltage ( $V_{\rm BR}$ ) of current power GaN-on-Si devices, in which the $V_{\rm BR}$ was defined at a OFF-state leakage current ( $I_{\rm OFF}$ ) of 1 $\mu$ A/mm. 11 |

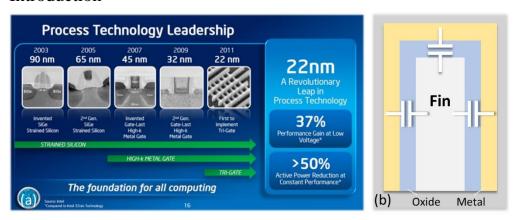

| Figure 2.1: (a) Roadmap of logic transistor technologies for processors, obtained at https://www.extremetech.com/. (b) Cross-sectional schematic of a tri-gate FinFET13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

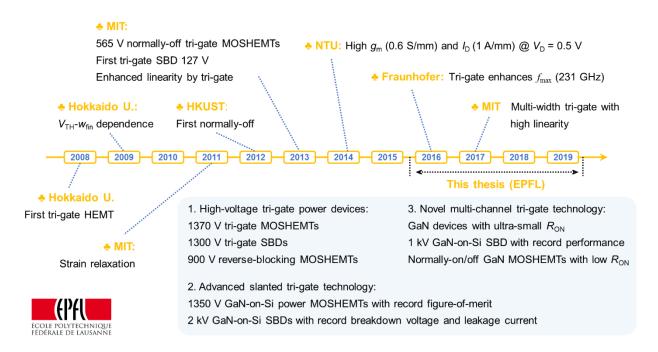

| Figure 2.2: Roadmap for tri-gate GaN electronics devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

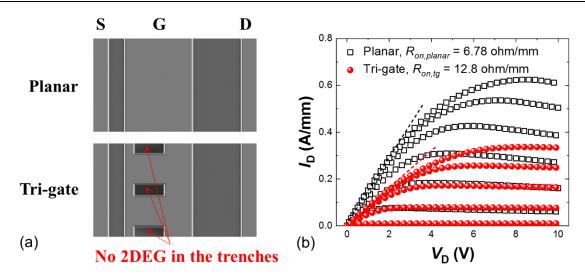

| Figure 2.3: (a) Top-view schematics of planar and tri-gate MOSHEMTs. (b) Output characteristics of a planar and tri-gate AlGaN/GaN MOS-HEMT, measured using $V_{\rm G}$ from -4 to 6 V with a step of 2 V and normalized by the width of device footprint of 150 $\mu$ m                                                                                                                                                                                                                                                                                                                                                                                                                                                |

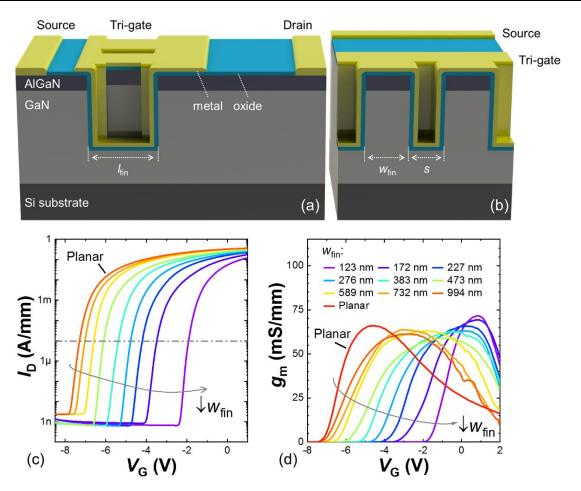

| Figure 2.4: Schematics of (a) the tri-gate MOSHEMTs and (b) its tri-gate region. The AlGaN/GaN epitaxy consisted of 3.75 $\mu$ m of buffer, 0.3 $\mu$ m of un-doped GaN (u-GaN) channel, 23.5 nm of AlGaN barrier and 2 nm of u-GaN cap layers. Average (a) $I_D$ - $V_G$ and (b) $g_m$ - $V_G$ characteristics in the tri-gate AlGaN/GaN MOSHEMTs with different $w_{\rm fin}$ , measured at $V_D$ = 5 V and normalized by the width of the device footprint. Published in Ref. [30]                                                                                                                                                                                                                                   |

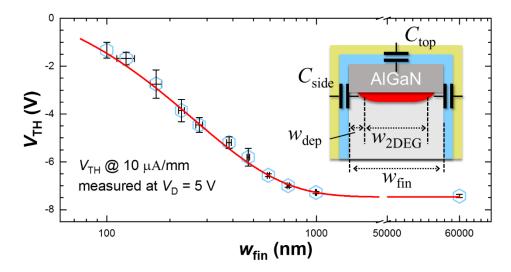

| Figure 2.5: Summarized dependence of $V_{\text{TH}}$ on $w_{\text{fin}}$ , in which $w_{\text{fin}}$ was measured by scanning electron microscopy (SEM) and the $V_{\text{TH}}$ was defined at 10 $\mu$ A/mm. The inset illustrates the effect of sidewall depletion in distributing the 2DEG across a fin. Published in Ref. [30]                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 2.6: (a) Schematic of the fabricated tri-gate MOS capacitor. (b) Cross-sectional SEM image of a tri-gate MOS structure fabricated on a dummy sample, tilted by 52°. (c) Average capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

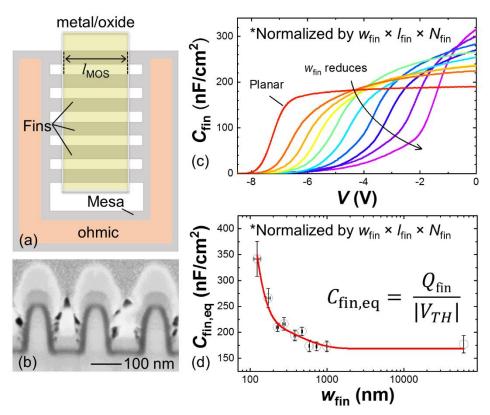

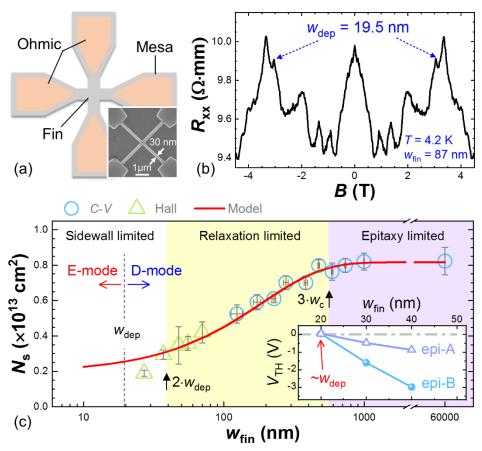

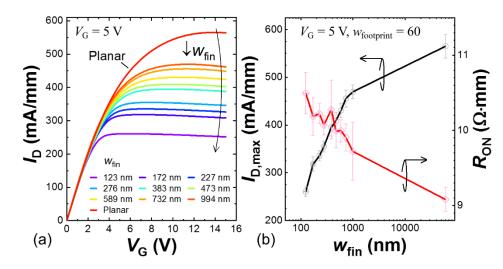

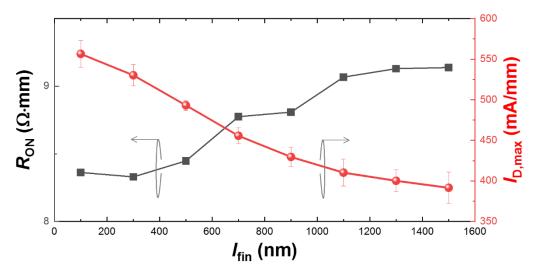

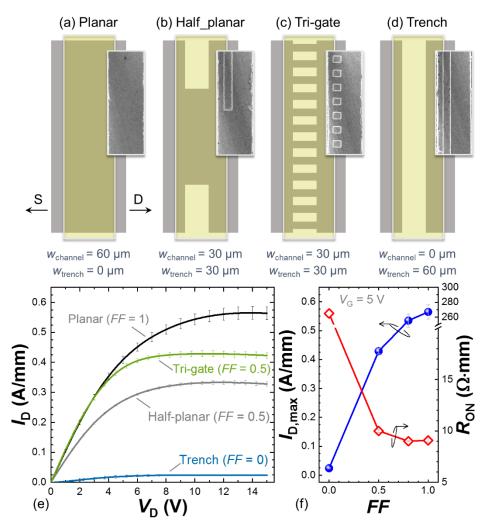

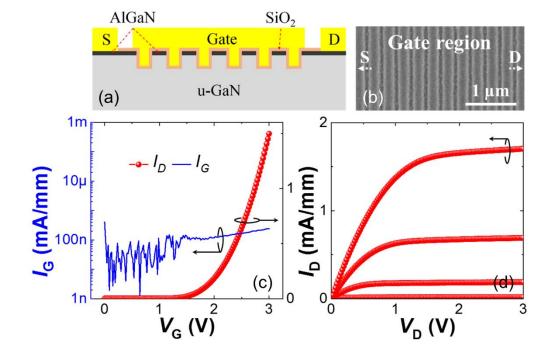

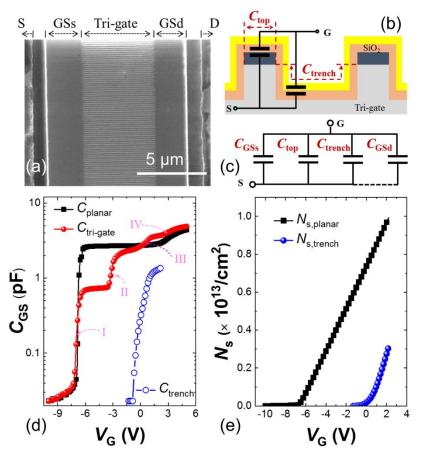

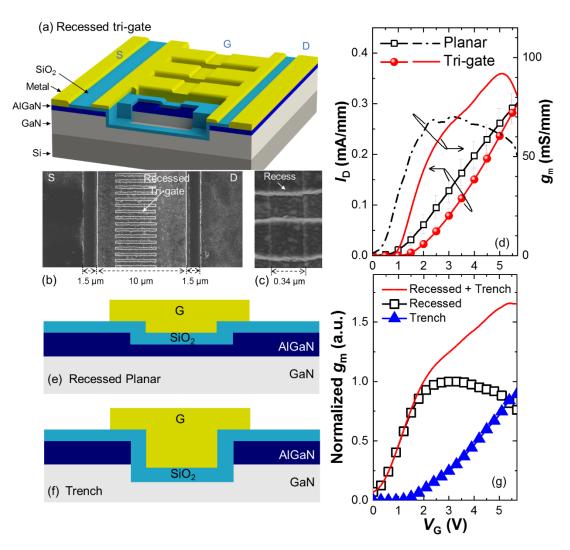

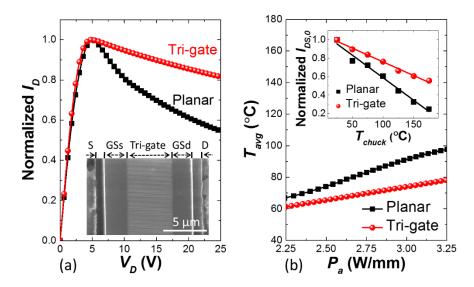

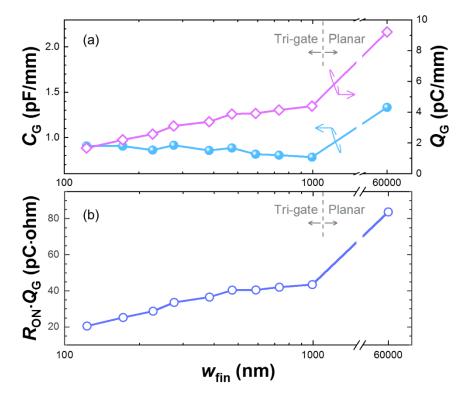

per fin area ( $C_{\text{fin}}$ ) with different wfin, measured at 1 MHz. (d) Calculated effective capacitance per fin area ( $C_{\text{fin,eq}}$ ) versus  $w_{\text{fin}}$ . All capacitors had the same wfootprint of 60  $\mu$ m and FF of 0.25. The length of the anode ( $l_{MOS}$ ) metal was 3  $\mu$ m and  $l_{fin}$  was 4  $\mu$ m. Capacitance values here were normalized by the top surface area of the fins  $(w_{\rm fin} \times l_{\rm MOS} \times N_{\rm fin})$  to understand the control of the 2DEG, in which  $N_{\text{fin}}$  refers to the number of fins in a single device. Published in Ref. [30].19 Figure 2.7: (a) Schematic and SEM image of the fabricated hall crosses. (b)  $R_{xx}$  versus magnetic field measured at 4.2 K. (c)  $N_s$  versus  $w_{\rm fin}$ , extracted from both MOS capacitors as well as Hall crosses, in which the  $N_s$  from C-V measurements was normalized by  $w_{\rm 2DEG} \times l_{\rm MOS} \times N_{\rm fin}$ , in which the  $w_{\rm 2DEG}$  was equal to  $(w_{\rm fin} - 2 \cdot w_{\rm dep})$ . The inset shows the  $V_{\rm TH}$  at 1  $\mu$ A/mm in tri-gate GaN MOSHEMTs with wfin from 20 nm to 40 nm using different epi structures, in which epi-A and epi-Figure 2.8: (a) Average output characteristics of tri-gate and planar MOSHEMTs, measured at  $V_G$ 5 V and normalized by  $w_{\text{footprint}}$ . (b) Summarized dependences of  $I_{\text{D,max}}$  and  $R_{\text{ON}}$  on  $w_{\text{fin}}$ . Published in Ref. [30]......21 Figure 2.9: Average  $R_{\text{ON}}$  and  $I_{\text{D,max}}$  of tri-gate GaN MOSHEMTs versus the length of the fins ( $l_{\text{fin}}$ ), with a fixed  $w_{\text{fin}}$ , measured at  $V_{\text{G}} = 5 \text{ V}$  and normalized by the width of the device footprint.22 Figure 2.10: (a)-(d) Top-view schematcs of the four types of transistors with similar dimensions but different gate regions. (e) Output characteristics at  $V_G = 5$  V. (f) Dependences of  $I_{D,max}$  and  $R_{ON}$  on FF at  $V_G = 5$  V with  $w_{\text{fin}} = 600$  nm and  $l_{\text{fin}} = 700$  nm. All current values are normalized by the width of device footprint ( $w_{\text{footprint}} = 60 \,\mu\text{m}$ ). Published in Ref. [30]......23 Figure 2.11: (a) Cross-sectional schematic and (b) top-view SEM observations in gate region of the periodically gate-recessed transistors; (c) transfer and (d) output characteristics of the transistors. Figure 2.12: (a) Top-view SEM image of the tri-gate MOSHETMs used for C-V measurements. (b) Equivalent circuit of  $C_{GS}$  for the tri-gate MOSHEMT. (c) Schematic of  $C_{top}$  and  $C_{trench}$  in the tri-gate region. (d) Measured C-V characteristics of the MOSHEMTs and extracted  $C_{\text{trench}}$ ; (e)  $V_{\text{G}}$ -dependent sheet carrier density  $(N_s)$  of the planar MOSHEMT and the trench MOSFET. Published in Ref. [28]. Figure 2.13: (a) Schematics of the recessed tri-gate MOSHEMT. (b) and (c) Top-view SEM observation of (b) the entire MOSHEMTs and (c) the recessed tri-gate. (d) Transfer characteristics of the recessed planar and tri-gate MOSHEMTs, measured at  $V_D = 5$  V and normalized by the width of the device footprint. Cross-sectional schematics of planarMOSHEMTs with (e) recessed and (f) trenches in the gate region and (g) the comparison of their normalized  $g_m$  versus  $V_G$ ........28 Figure 2.14: (a) Normalized  $I_D$ - $V_D$  characteristics of planar and tri-gate AlGaN/GaN MOSHEMT measured with similar  $V_G$  -  $V_{TH}$  (~5 V) and (b) extracted average temperature of the 150- $\mu$ m-wide transistors versus applied power normalized by device width; the insets of (a) and (b) show the SEM observation of the tri-gate transistor and the linear dependences of the extrapolated saturation drain Figure 2.15: (a) Dependence of  $C_G$  and  $Q_G$  on  $w_{fin}$  normalized by  $w_{footprint}$ , extracted at  $V_G = 0$  V. (b)

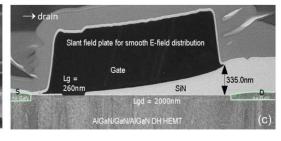

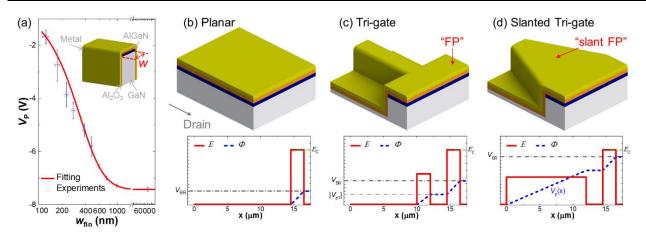

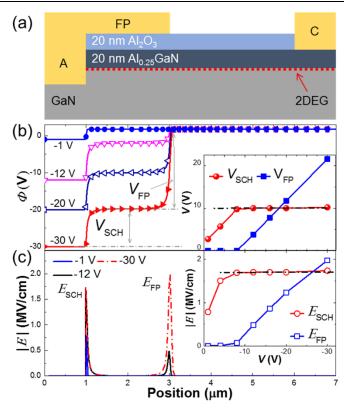

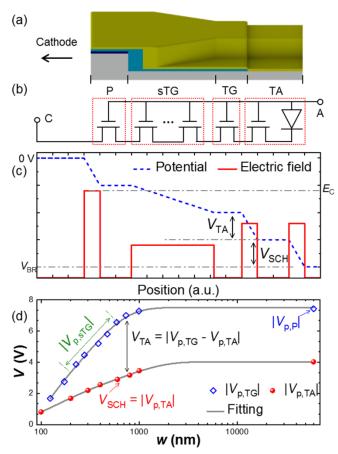

Figure 3.2: Schematics, equivalent circuits and distributions of potential  $(\Phi)$  and electric field (E) in lateral GaN transistors in OFF state with (a) no FPs, (b) a single FP, (c) two FPs and (d) a slant FP. Published in Ref. [31]......34

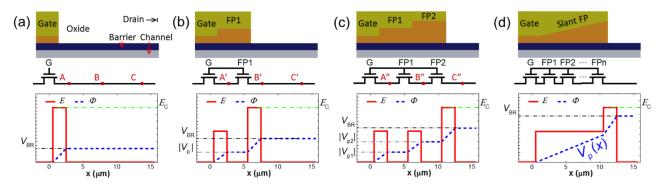

| Figure 3.3: (a) Dependence of $V_p$ on $w_{\rm fin}$ in tri-gate AlGaN/GaN MOS structures, in which the error bars were determined from about eight devices of each kind. The inset shows a schematic of the trigate structure. Schematics of structures of (b) a planar gate, (c) a single tri-gate, and (d) multiple trigates, along with the distribution of channel potential and electric field in them                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

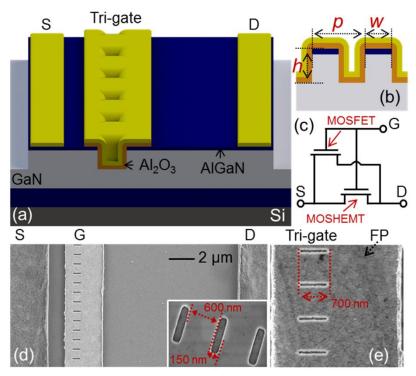

| Figure 3.4: (a) Schematic of the tri-gate MOSHEMTs. (b) Cross-sectional schematic of the tri-gate region. (c) Equivalent circuit of the tri-gate MOSHEMTs. (d)-(e) Top-view SEM images of the tri-gate MOSHEMTs. The inset shows a SEM image of the fins without the dielectric and gate metal layers. Published in Ref. [32]                                                                                                                                                                                                                                              |

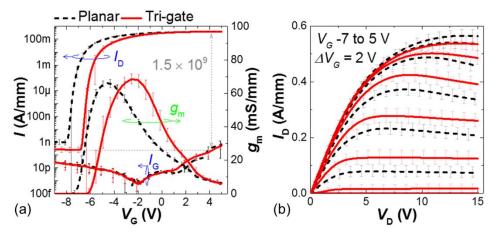

| Figure 3.5: (a) Transfer (at $V_D = 5$ V) and (b) output characteristics of the devices, normalized by the width of device footprint. The $L_{GS}/L_G/L_{GD}$ were 1.5/2.5/10 $\mu$ m, respectively. Published in Ref. [32]                                                                                                                                                                                                                                                                                                                                                |

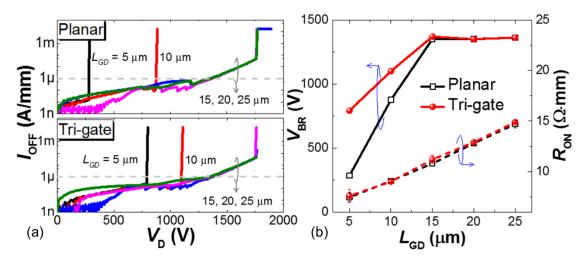

| Figure 3.6: (a) OFF-state breakdown characteristics of the planar and tri-gate ( $FF=0.8$ ) MOSHEMTs with different $L_{\rm GD}$ , measured with floating substrate. (b) Extracted $L_{\rm GD}$ -dependent $R_{\rm ON}$ and $V_{\rm BR}$ of the MOSHEMTs. The breakdown was defined at $I_{\rm OFF} \leqslant 1~\mu {\rm A/mm}$ . Published in Ref. [32]                                                                                                                                                                                                                   |

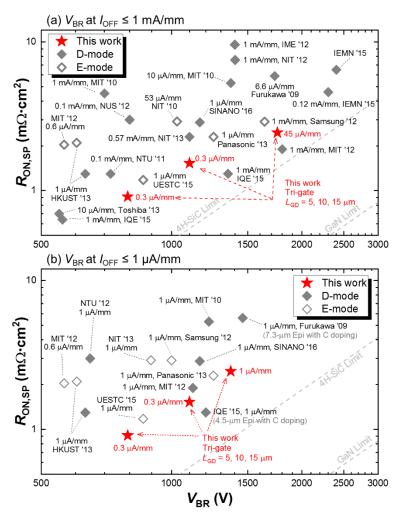

| Figure 3.7: $R_{\text{ON,SP}}$ versus $V_{\text{BR}}$ benchmarks of the tri-gate MOSHEMTs in this work against state-of-the-art GaN E/D-mode (MOS)HEMTs on Si by defining $V_{\text{BR}}$ at $I_{\text{OFF}}$ (a) $\leq 1$ mA/mm and (b) $\leq 1$ $\mu$ A/mm. For fair comparison, literature results with unspecified $R_{\text{ON}}$ or $I_{\text{R}}$ were not included. Published in Ref. [32]                                                                                                                                                                         |

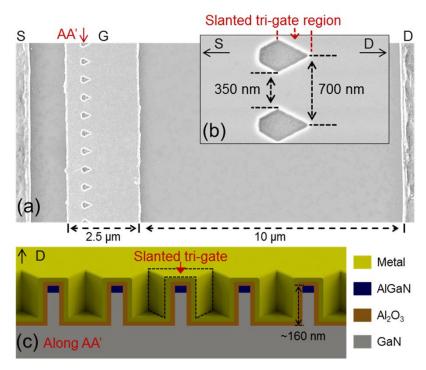

| Figure 3.9: Top-view SEM images of the slanted tri-gate MOSHEMT (a) with and (b) without the gate dielectric and the metal. (c) A cross-sectional schematic of the slanted tri-gate along the arrow AA'. Published in Ref. [31].                                                                                                                                                                                                                                                                                                                                           |

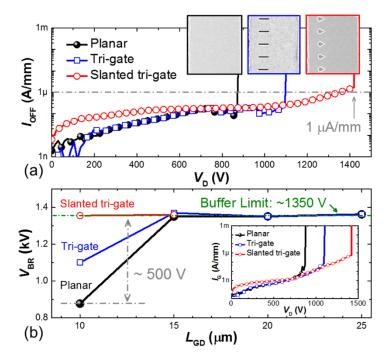

| Figure 3.9: Typical breakdown characteristics of the MOSHEMTs with planar gates, tri-gates and slanted tri-gates and (b) their $L_{\rm GD}$ -dependent $V_{\rm BR}$ (at 1 $\mu$ A/mm), measured at $V_{\rm G}$ of -10 V with a floating substrate. The insets in (a) show the top-view SEM images of the gate region of the three types of devices. The inset in (b) shows the gate leakage current of the devices. The $L_{\rm GS}/L_{\rm G}L_{\rm GD}$ are 1.5/2.5/10 $\mu$ m, respectively. Published in Ref. [31]                                                      |

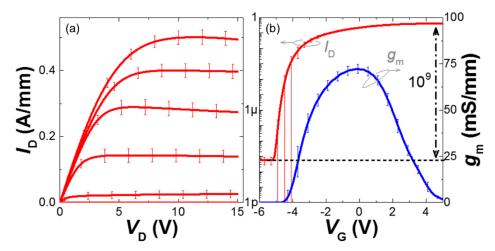

| Figure 3.10: (a) Average output and (b) transfer characteristics of the slanted tri-gate devices, normalized by their footprint width. The error bars were determined from measurements on six devices. The $L_{\rm GS}/L_{\rm G}/L_{\rm GD}$ were 1.5/2.5/10 $\mu$ m, respectively. Published in Ref. [31]42                                                                                                                                                                                                                                                              |

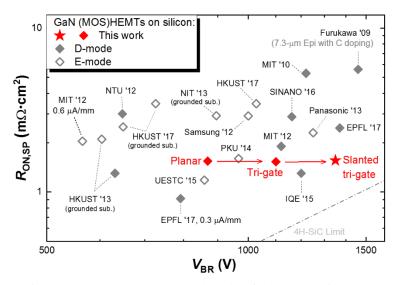

| Figure 3.11: Specific on-resistance ( $R_{\rm ON,SP}$ ) versus $V_{\rm BR}$ benchmarks of the slanted tri-gate MOSHEMTs against state-of-the-art GaN E/D-mode (MOS)HEMTs on silicon by defining the $V_{\rm BR}$ at $I_{\rm OFF} \leqslant 1~\mu$ A/mm. A 1.5- $\mu$ m transfer length for each ohmic contact was considered for calculation of the $R_{\rm ON,SP}$ , and the $V_{\rm BR}$ for all reference devices was re-calculated based on the reported data following the definition of $V_{\rm BR}$ at $I_{\rm OFF} \leqslant 1~\mu$ A/mm. Published in Ref. [31]43 |

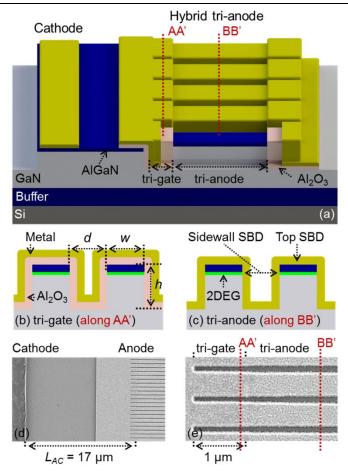

| Figure 4.1: (a) Schematic of the tri-anode SBDs. Cross-sectional schematics of (b) the tri-gate region along line AA' and (c) the tri-anode region along line BB'. (d) Top-view SEM image of the fabricated hybrid tri-anode SBDs. (e) Zoomed-in SEM image of the tri-gate and tri-anode regions. Published in Ref. [34]                                                                                                                                                                                                                                                   |

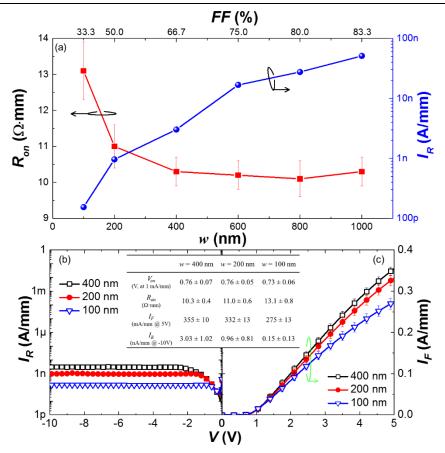

| Figure 4.2: (a) $R_{\rm ON}$ and $I_{\rm R}$ (at -10 V) of tri-anode SBDs with different $w_{\rm fin}$ . (b) Reverse and (c) forward $I$ - $V$ characteristics of the tri-anode SBDs with $w_{\rm fin}$ of 400, 200 and 100 nm, normalized by                                                                                                                                                                                                                                                                                                                              |

| the width of device footprint. The inset summarizes the performance of tri-gate SBDs with different $w_{\text{fin}}$ . Published in Ref. [34]                                                                                                                                                                                                                                                                                                                                                                                                                              |

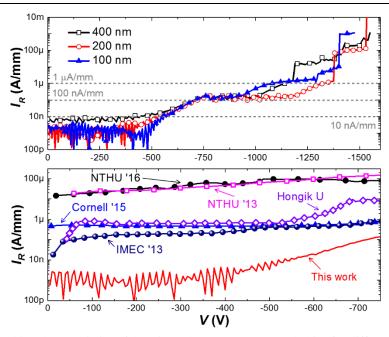

wfin and (b) comparison of  $I_R$  of the tri-anode SBD ( $w_{fin} = 200 \text{ nm}$ ) and state-of-the-art high-voltage

| GaN-on-Si lateral SBDs. The $I_R$ for the SBDs with $w_{fin}$ of 200 and 100 nm was likely around or below the measurement limit of our setup. Published in Ref. [34]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

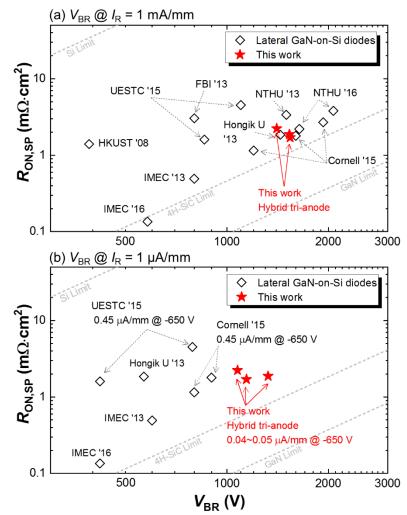

| Figure 4.4: $R_{\rm ON,SP}$ versus $V_{\rm BR}$ benchmarks of the tri-anode SBDs with state-of-the-art GaN lateral power diodes by defining $V_{\rm BR}$ at $I_{\rm R}=1$ mA/mm (a) and 1 $\mu$ A/mm (b). For fair comparison, literature results with unspecified $R_{\rm ON,SP}$ or $I_{\rm R}$ were not included. Published in Ref. [34]                                                                                                                                                                                                                                                                                                                |

| Figure 4.5: (a) A cross-sectional schematic of a lateral AlGaN/GaN SBD with typical planar FP. Simulated distributions of (b) potential ( $\Phi$ ) and (c) electric field ( $E$ ) at the channel in OFF state for different anode voltages, in which only in-plane electric field was considered. The insets show the summarized dependences of the $V_{\rm SCH}$ and the $E_{\rm SCH}$ on the voltage. Published in Ref. [33]. 51                                                                                                                                                                                                                         |

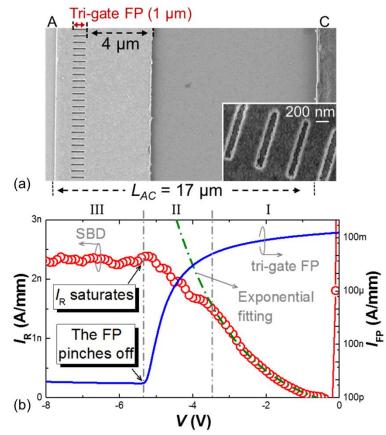

| Figure 4.6: (a) Top-view SEM images of the fabricated AlGaN/GaN SBD with a tri-gate FP. (b) $I_R$ of the SBDs and the pinch-off characteristic of the tri-gate FPs as a function of the voltage. All characteristics were averaged from about 8 devices of the same kind and normalized by the width of the device footprint (60 $\mu$ m). The turn-ON voltage ( $V_{ON}$ ) of these SBDs was $0.9 \pm 0.1$ V, extracted at a forward current of 1 mA/mm. Published in Ref. [33]                                                                                                                                                                           |

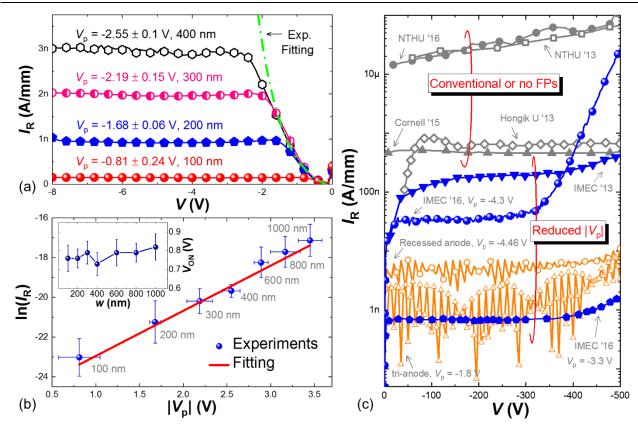

| Figure 4.7: (a) Comparison of the $I_R$ in hybrid tri-anode SBDs with different $w_{\rm fin}$ and thus different $V_{\rm p}$ . (b) A linear fitting of the $\ln(I_R)$ at -10 V and the $ V_{\rm p} $ . The inset shows the $V_{\rm ON}$ of these devices as a function of $w_{\rm fin}$ . The spacing between nanowires in these devices was 200 nm. $I_R$ was normalized by their total width of 60 $\mu$ m (the width of the device footprint) and the error bars were determined from about 8 devices of each kind. (c) Comparison of $I_R$ from AlGaN/GaN-on-Si SBDs with various FP designs in the literature and this thesis. Published in Ref. [33] |

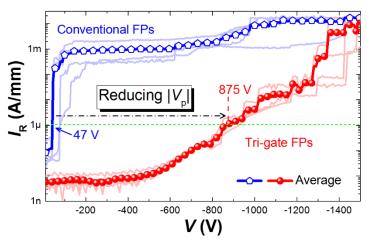

| Figure 4.8: Breakdown characteristics of the SBDs with and without the tri-gate FPs, measured with floating substrates. Published in Ref. [33].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

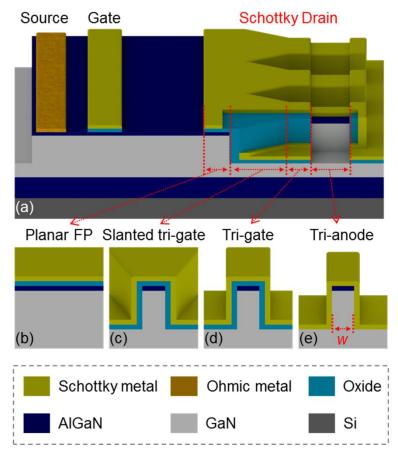

| Figure 4.9: (a) Schematic of the slanted tri-gate SBD and (b) a top-view scanning electron microscopy (SEM) image of the anode region. Cross-sectional schematics of the (c) planar (P), (d) slanted tri-gate (sTG), (e) tri-gate (TG) and (f) tri-anode (TA) regions composing the anode. Published in Ref. [35]                                                                                                                                                                                                                                                                                                                                          |

| Figure 4.10: (a) Schematic and (b) equivalent circuit of the slanted tri-gate SBDs. (c) Schematic showing the distribution of potential and electric field at the 2DEG channel in the SBD under large reverse bias. (d) Averaged absolute value of the pinch-off voltage ( $ V_p $ ) as a function of the fin width ( $w_{\rm fin}$ ) in tri-gated AlGaN/GaN structures, determined from about eight devices of the each type fabricated on a control sample with 20 nm Al <sub>2</sub> O <sub>3</sub> as the oxide. Published in Ref. [35] 56                                                                                                             |

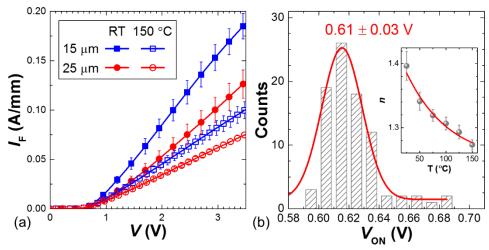

| Figure 4.11: (a) Forward $I$ - $V$ characteristics and (b) distribution of $V_{\rm ON}$ of the slanted tri-gate SBDs. The inset shows the dependence of the estimated ideality factor $(n)$ upon the temperature $(T)$ . Published in Ref. [35]                                                                                                                                                                                                                                                                                                                                                                                                            |

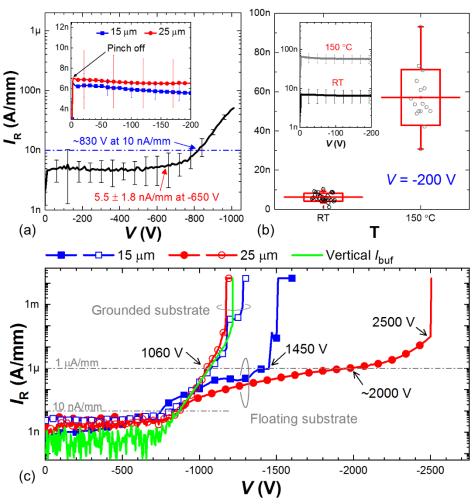

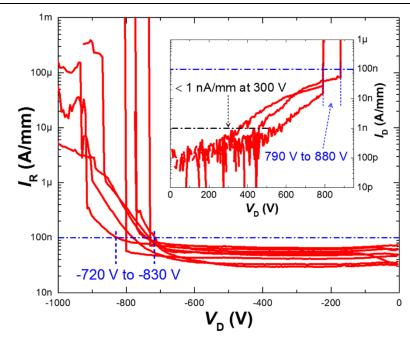

| Figure 4.12: (a) Average $I_R$ from ten devices measured at room-temperature (RT), which was independent on the substrate connection when $V$ was below -900 V. (c) Breakdown characteristics of the slanted tri-gate SBDs. The inset in (a) shows the $I_R$ with 15 $\mu$ m and 25 $\mu$ m of $L_{AC}$ at RT. (d) $I_R$ at RT and 150 °C measured under a voltage of -200 V. The inset in (b) shows the reverse $I$ - $V$ characteristics at different temperatures. Published in Ref. [35]                                                                                                                                                               |

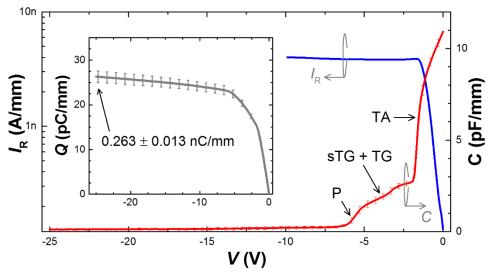

| Figure 4.13: The capacitance-voltage $(C-V)$ characteristics of the SBDs along with their $I_R$ . The inset shows the cumulative charge $(Q_C)$ of the devices. The $C-V$ measurements were performed at 1 MHz at room temperature, with negligible hysteresis observed from double-sweep measurements. Published in Ref. [35]                                                                                                                                                                                                                                                                                                                             |

| Figure 4.14: Specific on-resistance ( $R_{\rm ON,SP}$ ) versus $V_{\rm BR}$ benchmark of the slanted tri-gate SBDs against state-of-the-art lateral GaN-on-Si SBDs by defining the $V_{\rm BR}$ at $I_{\rm R}=1~\mu{\rm A/mm}$ . The $V_{\rm BR}$ for all reference devices was re-calculated based on the reported data following the definition of $V_{\rm BR}$ at                                                                                                                                                                                                                                                                                       |

| $I_R = 1 \mu A/mm$ . For fair comparison, devices with unspecified $R_{ON}$ or $I_R$ were not included. Published in Ref. [35]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.15: (a) Schematic of the MOSHEMTs with the slanted tri-gate Schottky drain. Cross-sectional schematics of the (b) planar FP, (c) slanted tri-gate (sTG), (d) tri-gate (TG) and (e) tri-anode (TA) regions. Published in Ref. [36].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

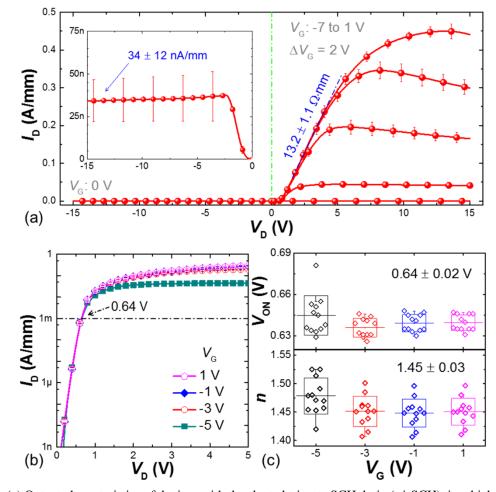

| Figure 4.16: (a) Output characteristics of devices with the slanted tri-gate SCH drain (tri-SCH), in which the inset shows the $I_R$ in the tri-SCH at $V_G = 0$ V, and (b) their turn-on characteristics. (c) Dependence of the $V_{\rm ON}$ and the ideality factor (n) on $V_{\rm G}$ . Published in Ref. [36]62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

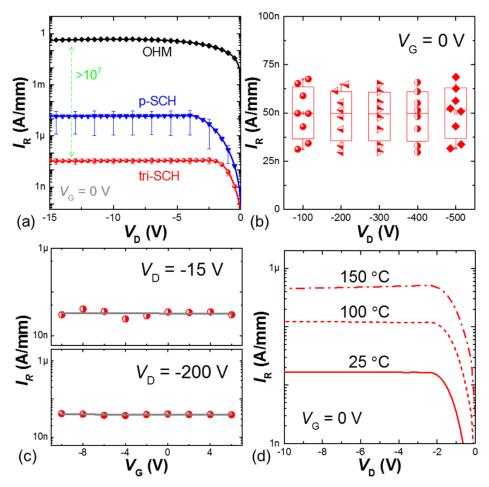

| Figure 4.17: (a) Comparison of $I_R$ in devices with ohmic (OHM), planar Schottky (p-SCH) and trianode Schottky (tri-SCH) drains. Dependence of the $I_R$ on $V_D$ (b) and $V_G$ (c) in the tri-SCH. (d) Dependence of the $I_R$ in tri-SCH on temperature. Published in Ref. [36]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

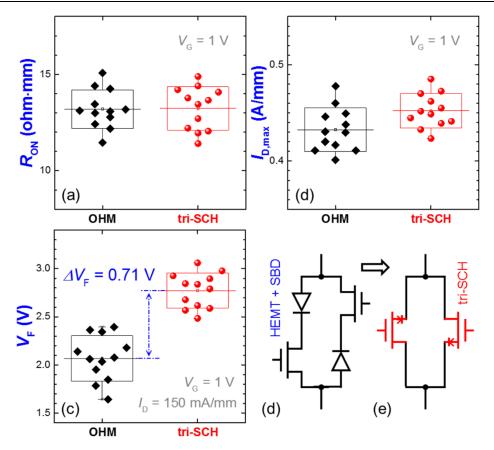

| Figure 4.18: Comparison of the tri-SCH and OHM in (a) $R_{ON}$ , (b) maximum $I_D$ ( $I_{D,max}$ ) and (c) forward voltage ( $V_F$ ). Examples of bi-directional power switches using (d) a conventional scheme including two HEMTs and two SBDs and (e) a more advanced scheme using only two reverse-blocking transistors as demonstrated in this work (tri-SCH). Published in Ref. [36]64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 4.19: Room-temperature breakdown characteristics of the tri-SCH, measured with grounded substrate. The $V_G$ for measuring the $V_{RB}$ and $V_B$ was 0 V and -10 V, respectively. Published in Ref. [36]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

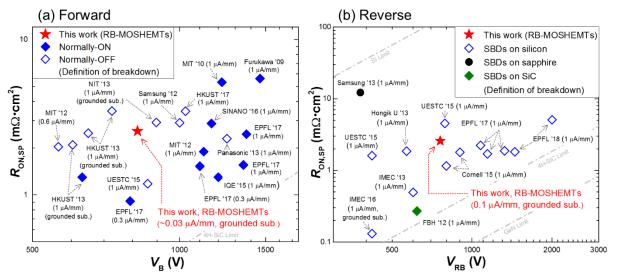

| Figure 4.20: $R_{\rm ON,SP}$ versus breakdown voltage benchmarks of (a) the forward performance of the tri-SCH (RB-MOSHEMTs) against discrete lateral GaN-on-silicon power (MOS)HEMTs and (b) their reverse performance against discrete lateral GaN SBDs on various substrates. The breakdown voltage for all reference devices was re-calculated based on the reported data following the definition of $V_{\rm B}$ at $I_{\rm OFF} \leqslant 1~\mu {\rm A/mm}$ . For fair comparison, literature results with unspecified $R_{\rm ON}$ or $I_{\rm R}$ were not included. Published in Ref. [36].                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

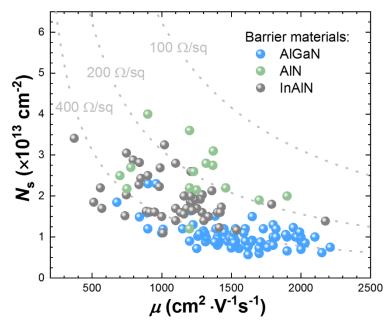

| Figure 5.1: Transport characteristics of the 2DEG in GaN heterostructures with different barrier materials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

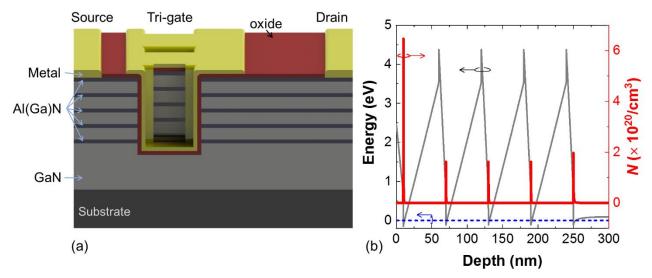

| Figure 5.2: (a) Schematic of proposed multi-channel tri-gate GaN MOSHEMT and (b) simulated energy band structure of a multi-channel AlGaN/GaN heterostructure showing five parallel 2DEG channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

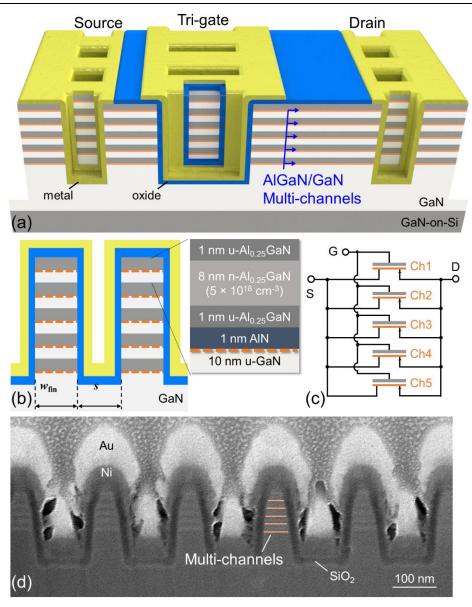

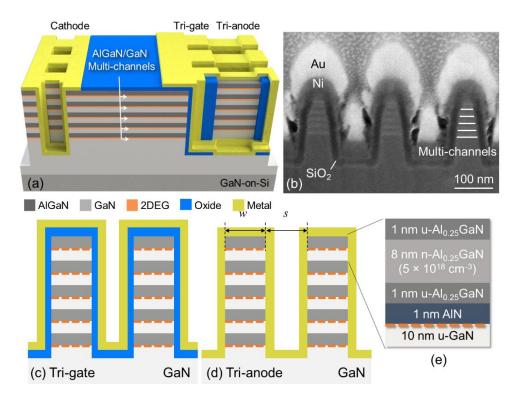

| Figure 5.3: (a) Schematic of the multi-channel tri-gate AlGaN/GaN MOSHEMT. (b) Cross-sectional schematic of the tri-gate region. The inset shows the heterostructure forming each of the multi-channels. (c) An equivalent circuit of the multi-channel tri-gate MOSHEMT, integrating multiple parallel transistors in a given device footprint for enhanced performance and reduced substrate cost. (d) A cross-sectional SEM image of the tri-gate region, tilted by 52°. Published in Ref. [38].71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

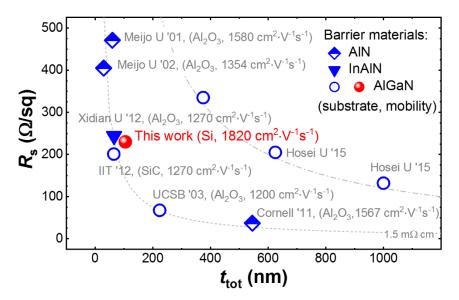

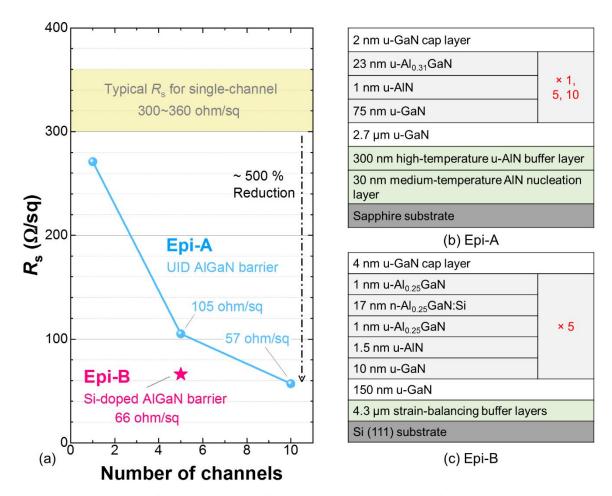

| Figure 5.4: Comparison of multi-channel structures in this work with literature results. The $t_{tot}$ refers to the total thickness of the multi-channel structure. For a fair comparison, multi-channel structures with unspecified $R_s$ were not included. Published in Ref. [38]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

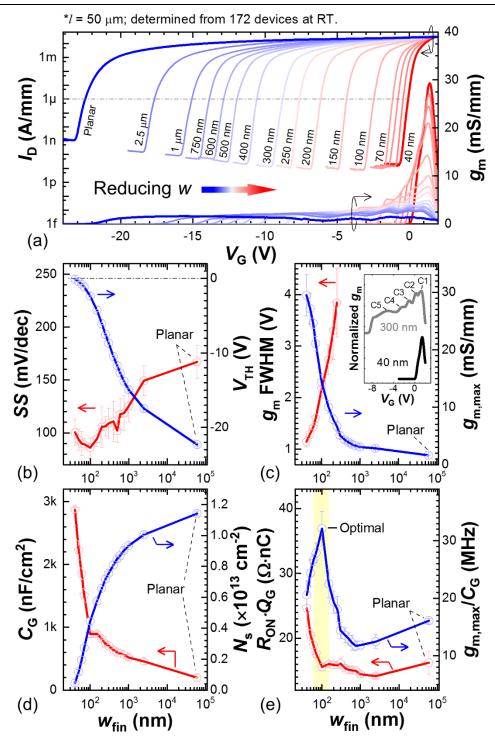

| Figure 5.5: (a) Transfer characteristics of multi-channel tri-gate MOSHEMTs with different $w_{\rm fin}$ from 60 µm (planar) to 40 nm, measured at $V_{\rm D}=0.5$ V. Width dependence of (b) SS and $V_{\rm th}$ (at 1 µA/mm), (c) $g_{\rm m,max}$ and $g_{\rm m}$ FWHM, (d) $C_{\rm G}$ and $N_{\rm s}$ , and (e) $R_{\rm ON}\cdot Q_{\rm G}$ ( $Q_{\rm G}$ refers to gate charge) and $g_{\rm m,max}/C_{\rm G}$ values. The inset in (c) shows normalized $g_{\rm m}$ - $V_{\rm G}$ plots of devices with $w_{\rm fin}$ of 40 nm and 300 nm. The $R_{\rm ON}$ , $C_{\rm G}$ and $Q_{\rm G}$ was extracted at $V_{\rm G}=2$ V, $N_{\rm s}$ was extracted at $V_{\rm G}=0$ V, and the $g_{\rm m,max}$ was the maximum value of the $g_{\rm m}$ - $V_{\rm G}$ characteristics, regardless of the several $g_{\rm m}$ peaks in transistors with $w>200$ nm. The $C_{\rm G}$ and $N_{\rm s}$ were normalized by the top surface area of the fins. The length of the gate electrode here ( $L_{\rm G}$ ) was 51 µm, covering the fins and extending 0.5 µm towards the source |

| and drain side. The gate-to-source ( $L_{\rm GS}$ ) and gate-to-drain ( $L_{\rm GD}$ ) lengths were 1.5 $\mu$ m. Published in Ref. [38]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

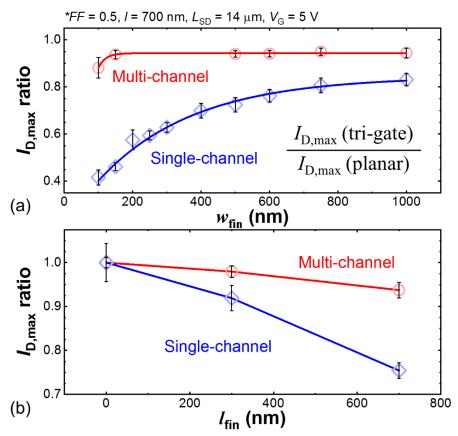

| Figure 5.6: Dependence of $I_{D,max}$ on (a) $w_{fin}$ and (b) $I_{fin}$ in single- and multi-channel tri-gate MOSHEMTs, all measured at $V_G = 5$ V and normalized by the width of device footprint. These devices had different $w_{fin}$ in their tri-gate regions, while sharing the same $FF$ of 0.5 and $I_{fin}$ of 700 nm. The distance between source and drain electrodes ( $I_{SD}$ ) was 14 $\mu$ m. Published in Ref. [38].75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

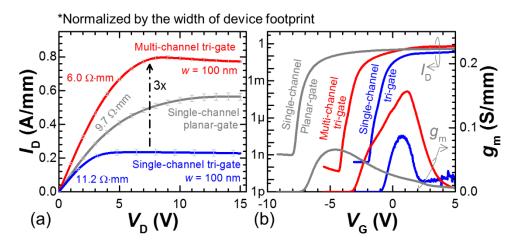

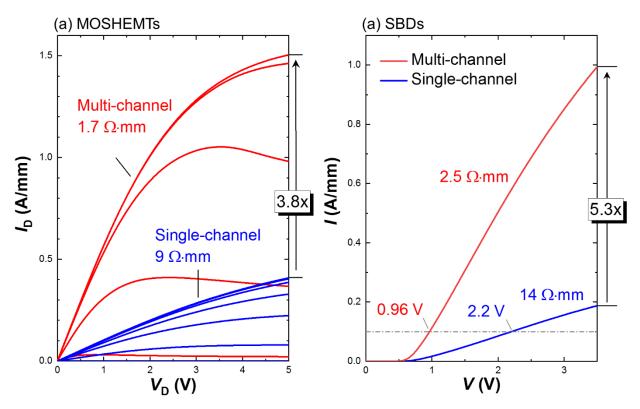

| Figure 5.7: (a) Output characteristics at $V_G = 5$ V and (b) transfer characteristics at $V_D = 5$ V of the transistors, normalized by the width of device footprint. The $w_{fin}$ and $FF$ in single-channel tri-gate and multi-channel tri-gate transistors are 100 nm and 50 %, respectively. Published in Ref. [38].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

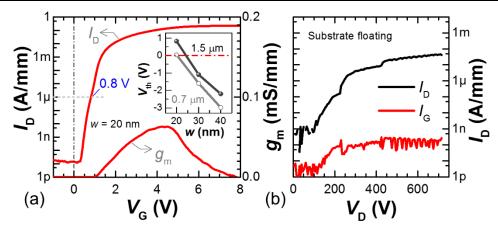

| Figure 5.8: (a) Transfer characteristics of multi-channel tri-gate transistors with $w_{\text{fin}}$ of 20 nm and $FF$ of 10 %. (b) OFF-state breakdown characteristics of the multi-channel tri-gate transistors measured with floating substrate. The inset in (a) shows the dependence of $V_{\text{TH}}$ (at 1 $\mu$ A/mm) in multi-channel tri-gate transistors on $w_{\text{fin}}$ and $l_{\text{fin}}$ . Published in Ref. [38]77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 5.9: (a) Schematic of the multi-channel tri-gate SBD. (b) Cross-sectional SEM image of the multi-channel tri-gate region, tilted by 52°. Cross-sectional schematics of the (c) tri-gate and (d) trigate regions. (e) Schematic of the heterostructure composing each channel in the multi-channel structure. Published in Ref. [39]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

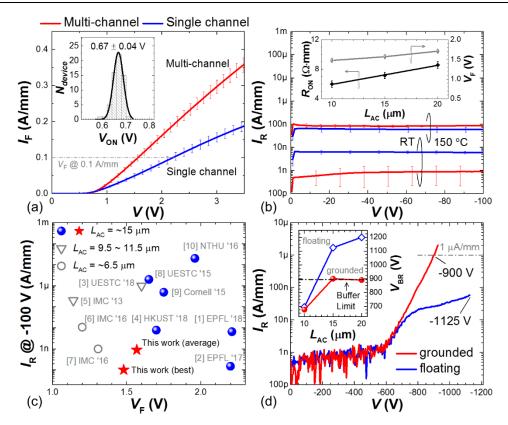

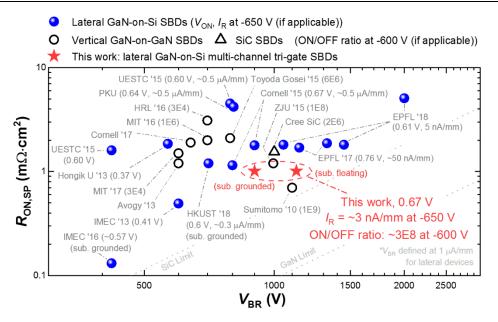

| Figure 5.10: (a) Forward and (b) reverse characteristics of the multi-channel tri-gate SBDs. (c) Comparison of $I_R$ and $V_F$ of the GaN-on-Si SBDs in this work and literature. (d) Breakdown characteristics of the multi-channel tri-gate SBDs. The inset in (a) shows the distribution of the $V_{ON}$ . The inset in (b) shows the dependence of $R_{ON}$ and $V_F$ upon $L_{AC}$ in multi-channel tri-gate SBDs. Published in Ref. [39]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 5.11: Specific on-resistance ( $R_{\rm ON,SP}$ ) versus $V_{\rm BR}$ benchmark of the multi-channel tri-gate SBDs against state-of-the-art lateral GaN SBDs. For fair comparison, the $V_{\rm BR}$ for all lateral devices was re-calculated based on the reported data following the definition of $V_{\rm BR}$ at $I_{\rm R}=1~\mu{\rm A/mm}$ , and devices with unspecified $R_{\rm ON}$ or $I_{\rm R}$ were not included. Published in Ref. [39]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

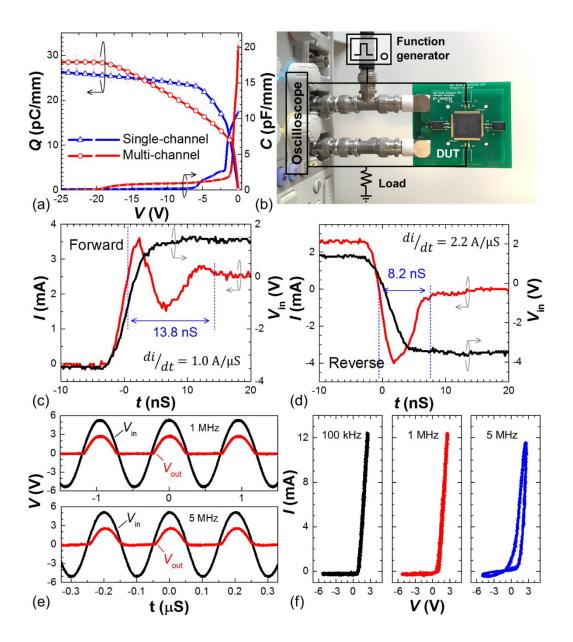

| Figure 5.12: (a) Capacitance ( $C$ ) and $Q$ in multi-channel and single-channel SBDs. (b) Setup for measuring the switching characteristics. The device was bonded onto a printed circuit board (PCB) and connected directly to the oscilloscope to minimize parasitic elements. (c) Forward- and (d) reverse-recovery characteristics of the multi-channel tri-gate SBDs. The devices were switched between 1.5 V to -3.5 V at 1 MHz (limited by the oscilloscope) using the internal oscilloscope function generator and a 50 $\Omega$ resistor as the load. (e) Input ( $V_{in}$ ) and output ( $V_{out}$ ) waveforms and (f) Lissajous $I$ - $V$ plots showing the rectification characteristics of the multi-channel tri-gate SBDs at different frequencies, using an external function generator and a 220 $\Omega$ resistor. The small phase shift in (e) between $V_{in}$ and $V_{out}$ was likely caused by parasitic elements in the circuit. Published in Ref. [39]. |

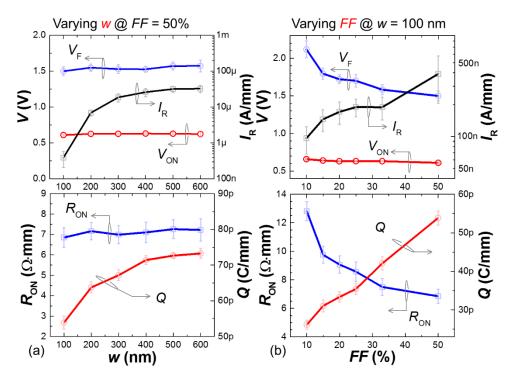

| Figure 5.13: Dependence of multi-channel tri-gate SBDs' characteristics upon (a) w and (b) FF in tri-gate and tri-anode regions. Published in Ref. [39]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

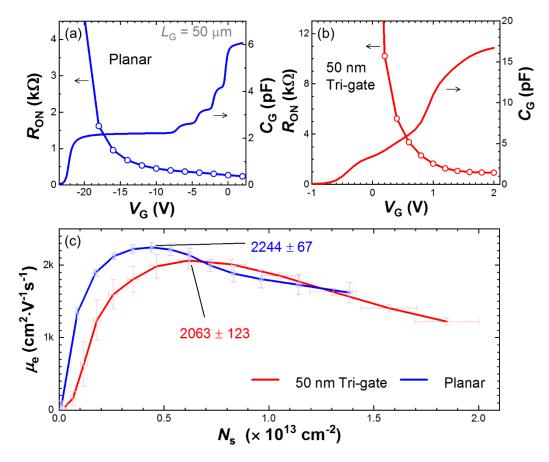

| Figure 5.14: Average $R_{\rm ON}$ and $C_{\rm G}$ in multi-channel MOSHEMTs with (a) planar-gates and (b) 50 nm-wide tri-gates. The $L_{\rm G}$ was 50 µm for both devices, and the gate-to-source and gate-to-drain distances were both 1.5 µm. $R_{\rm ON}$ was measured using drain voltages below 0.1 V, and $C_{\rm G}$ was measured at 1 MHz. (c) $\mu_{\rm e}$ versus $N_{\rm s}$ in the two devices. The $N_{\rm s}$ was normalized by the top surface area of the fins, which did not impact the determination of $\mu_{\rm e}$ . Published in Ref. [39] 84                                                                                                                                                                                                                                                                                                                                                                                                             |

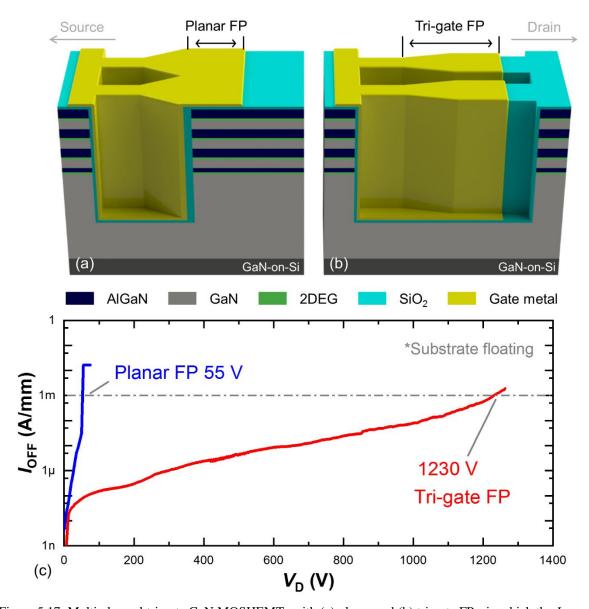

Figure 5.17: Multi-channel tri-gate GaN MOSHEMTs with (a) planar and (b) tri-gate FPs, in which the  $L_{\rm GD}$  was 10  $\mu$ m for both devices. (c) OFF-state breakdown characteristics of the two devices, which were measured with a floating substrate connection. The devices were fabricated using a multi-channel AlGaN/GaN epitaxy with  $R_{\rm S}$  of  $\sim$ 80  $\Omega$ /sq and exhibited  $R_{\rm ON}$  of  $\sim$ 3  $\Omega$ ·mm. The  $V_{\rm BR}$  here was defined at  $I_{\rm OFF}=1$  mA/mm. 88

# List of Tables

| Table 1.1: Comparison of Si and GaN for power applications                                                                                                                                                       | 2                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Table 4.1: Comparison of the tri-SCH in this work with other reverse-blocking C in the literature. <sup>a</sup> Substrate connection was not reported. <sup>b</sup> Results were obtained Published in Ref. [36] | ed from simulation.  |

| Table 5.1: Tri-gate geometry and device characteristics for the 50 $\mu$ m-long mutransistors presented. The $N_s$ here was normalized by the top surface area of the Ref. [38]                                  | e fins. Published in |

| Table 5.2: Comparison of the multi-channel AlGaN/GaN heterosturcture (Epi-Estate-of-the-art single- and multi-channel GaN heterostructures in the literature.                                                    | <i>'</i>             |

# Chapter 1 Introduction

#### 1.1 Advantages of GaN for efficient power conversion

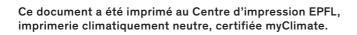

Figure 1.1: Applications of power electronics.

Power conversion is to control and convert electrical energy from one form to another, by modifying the current flow, voltage, frequency and other components of the power based on solid-state electronic devices and circuits. Power electronics is one of the key technologies that have cast the modern electronic era that we enjoy today, and is indispensable in our daily lives, modern industries, and among many others (Fig. 1.1), powering around 40% of the world's energy needs [1].

The key components of a power conversion system are power semiconductor devices, which can include transistors, diodes and thyristors according to different conversion topologies. While conventional Si-based power devices have steadily improved the efficiency and cost of power management in the past a few decades, the rate of such improvement is asymptotically approaching a limit, as a result of the fundamental constriction in the material capabilities of Si [2]. Now it has become a challenge to achieve new power Si devices with higher energy efficiency and power density to meet the growing demands in diminishing carbon emission and shifting to renewable energy.

On the other hand, Gallium nitride (GaN) has emerged as the front-running solution to these issues [3]–[8]. As an extraordinary representative of wide band-gap semiconductors, GaN offers the wide

Figure 1.2: (a) Specific ON-resistance versus breakdown voltage benchmarks of Si, SiC and GaN power devices, showing the reduced resistive loss and enhanced power rating in GaN devices, obtained from https://www.eetimes.com/document.asp?doc\_id=1272514. (b) Comparison of switching losses in GaN and Si power transistors versus switching frequency, revealing the reduced switching loss and increased operation frequency of GaN devices, obtained from https://www.pi-innovo.com/gan/. (c) The much higher operation frequency of GaN power devices can greatly miniaturize current power conversion systems, resulting in a much higher power density, obtained from https://industrial.panasonic.com/ww/products/semiconductors/powerics/ganpower.

band-gap, high electron mobility, high electron saturation velocity, and high breakdown field, yielding much higher Baliga Figure of Merit (BFM), Baliga High Frequency Figure of Merit (BHHFM) and Johnson's Figure of Merit (JFM) over Si (Tab. 1). The unique combination of these remarkable properties in GaN enables novel power devices with low resistive loss (Fig. 1.2(a)), low switching loss (Fig. 1.2(b)) and small switching delay, which are highly desirable to improve the energy efficiency, operation frequency (Fig. 1.2(b)) and power density (Fig. 1.2(c)) for the next generation of power converters.

Table 1.1: Comparison of Si and GaN for power applications.

|     | Electron<br>mobility<br>(cm²/V·s) | Electron Saturation velocity (× 10 <sup>7</sup> cm/s) | Band-<br>gap<br>(eV) | Breakdown<br>field<br>(10 <sup>6</sup> V/cm) | BFM | BHFFM | JFM  |

|-----|-----------------------------------|-------------------------------------------------------|----------------------|----------------------------------------------|-----|-------|------|

| Si  | 1350                              | 1                                                     | 1.12                 | 0.3                                          | 1   | 1     | 1    |

| GaN | 2200 (2DEG)                       | 2.2                                                   | 3.39                 | 3.3                                          | 850 | 98    | 1090 |

Figure 1.3: (a) Cross-sectional schematic of an AlGaN/GaN high electron mobility transistor (HEMT). (b) Simulated energy band structure of the AlGaN/GaN heterostructure, showing the 2DEG channel at the AlGaN/GaN interface. (c) A monolithic power integrated circuits (ICs) based on the AlGaN/GaN heterostructure. The circuit was demonstrated by Panasonic, and the image was obtained from https://www.psma.com/sites/default/files/uploads/tech-forums-semiconductor/presentations/is164-unlocking-power-gan.pdf. (d) The significant advantages of all-in-GaN power ICs presented by Navitas, which was obtained from https://www.psma.com/sites/default/files/uploads/tech-forums-semiconductor/presentations/is94-gan-power-ics-1-mhz-topologies-technologies-and-performance.pdf.

In addition to the superior material properties, GaN further enables novel high-voltage monolithic power integrated circuits (ICs) that could potentially revolutionize many power applications, thanks to the AlGaN/GaN HEMT technology. Different from conventional Si-based power devices, mainstream GaN power devices are based on a lateral AlGaN/GaN heterostructure, relying on the 2-dimensional electron gas (2DEG) at the AlGaN/GaN interface (Fig. 1.3(a)), generated by spontaneous and piezoelectric polarization effects of the AlGaN barrier layer (Fig. 1.3(b)) [9]. Such 2DEG channel presents excellent electric conductivity due to its high concentration ( $N_e$ ) and high mobility ( $\mu$ ), which is crucial to enhance the efficiency of a power device. In addition, the lateral current flow along the 2DEG channel results in a lateral scheme for GaN power devices, which greatly facilitates the monolithic integration of different devices and enables novel high-frequency power ICs with dramatically improved performance (Fig. 1.3(c)). As shown in Fig. 1.3(d), all-in-GaN power ICs can significantly

Figure 1.4: (a) Number of publications regarding GaN and GaN-on-Si, obtained from Ref. [10]. (b) Business models of current GaN power industry, revealing its bloom after the successful development of 6 inch GaN-on-Si technologies, which was generated by Yole and obtained from https://www.systemplus.fr/gan-power-device-industry-the-supply-chain-is-acting-to-support-market-growth/. (c) Summary of lattice and thermal mismatches between GaN and various substrates for epitaxial growth, obtained from https://iopscience.iop.org/article/10.7567/JJAP.53.100214/meta. (d) Nomarski optical micrograph showing the cracking of GaN grown on Si substrates, which was taken in HKUST. The inset in (d) shows the formation of cracks due to the thermal mismatch between GaN and Si, obtained from NTT at https://www.ntt-review.jp/archive/ntttechnical.php?contents=ntr201404fa8.html.

increase the operation frequency and dramatically enhance the efficiency of power converters from conventional technologies based on discrete devices, which are highly demanded for future compact and efficient power conversion.

#### 1.2 Cost-effective GaN-on-Si platform

GaN-on-Si technology is a key enabler for real-world GaN power solutions (Figs. 1.4(a) and (b)). While GaN devices have demonstrated tremendous prospects, they must be cost effective for commercialization, as many power applications are cost-sensitive. A major approach for the cost reduction is to construct GaN power devices on Si substrates based on a mature thin film process. GaN power devices are usually grown on foreign substrates using metalorganic chemical vapor deposition (MOCVD). Among the available substrates, Si is at present the most suited one for GaN power devices, offering low price (0.1 €/cm²), large sizes (up to 12 inch) and reasonable thermal conductivity,

Figure 1.5: (a) An AlGaN/GaN-on-Si heterostructure with step-graded AlGaN buffer layers and AlGaN back barrier layers, obtained from Ref. [11]. (b) GaN-on-Si MISHEMTs fabricated on 8 inch GaN-on-Si wafers, obtained from Ref. [12]. (c) Dependence of leakage current and signal strength (measured using scanning surface potential microscopy) on carbon concentration in GaN, which was obtained from Ref. [14].

while other substrates like SiC ( $10 \text{ } \text{€/cm}^2, \leq 6 \text{ inch}$ ) or sapphire ( $1 \text{ } \text{€/cm}^2, \leq 8 \text{ inch}$ ) are costly and small, and can be even thermally insulating as in sapphire [10].

However, the mismatch in thermal expansion coefficients between GaN and Si (Fig. 1.4(c)) results in huge thermal stress during the post-growth cooling process (inset in Fig. 1.4(d)), and constricts the maximum thickness of GaN-on-Si epi layers by generating cracks (Fig. 1.4(d)), limiting the voltage rating, the curvature, and the yield of the epi layers. This issue is mainly addressed by graded AlGaN [11], [12] or superlattice buffer layers [13] to provide compressive stress to the upper GaN layer during the cooling, thanks to the lattice mismatch between GaN and Al(Ga)N (Fig. 1.4(c)). These approaches have been widely used in the industry and successfully led to thick crack-free GaN-based epi layers on 8 inch Si substrates, as shown in Figs. 1.5(a) and (b). There are also other techniques that could diminish the thermal stress, such as different interlayers, yet they may feature either obvious disadvantages or complicated growth process, which are less approved for mass production.

The second challenge for growing GaN-on-Si power devices is the large buffer leakage current, which increases the OFF-state current ( $I_{OFF}$ ) and degrades the breakdown voltage of the device (usually defined at the voltage when  $I_{OFF}$  reaches 1  $\mu$ A/mm). This issue is firstly due to the n-type conductivity in unintentionally doped GaN, which is presumably caused by native defects and residual impurities, and degrades the resistivity of the GaN buffer layer. To address this problem, one approach is to dope the GaN layer with carbon atoms, by either methyl radicals or extrinsic precursors, which can introduce acceptor states and compensate the background carriers and impurities, resulting in an enhanced resistivity and a diminished leakage current (Fig. 1.5(c)) [14]. The carbon doping profile should be carefully optimized to minimize its impact on the dynamic performance of the device [15], [16].

Figure 1.6: (a) A 8 inch creack-free GaN-on-Si wafer with 5 µm thick epi layers for 650 V-rated power devices, and (b) the measured total thickness of the epi layers across the entire wafer, which were grown by Enkris and obtained from https://www.pntpower.com/enkris-semiconductor-shows-1600v-breakdown-gan-hemt-on-200mm-si-wafer/. (c) Room-temperature vertical breakdown characteristics of a 5 µm-thick AlGaN/GaN-on-Si wafer. (d) Expected selling price of a single 600V/10A transistor based on Si, SiC and GaN, obtained from https://www.led-professional.com/resources-1/articles/led-retrofit-based-on-algan-gan-on-si-field-effect-transistor-drivers.

The large buffer leakage current for GaN-on-Si is also limited by the defective AlN nucleation layer, along with the out diffusion of Si atoms from the substrate. So it is very important to improve the crystalline quality of the AlN nucleation layer to better isolate the 2DEG channel from the Si substrate. This is usually tackled by a careful optimization of the AlN nucleation layer, i.e. growth temperature, pressure, III/V ratio and so on.