## Asynchronous Simulation of Neuronal Activity

Thèse N° 7098

Présentée le 8 juillet 2019 à la Centres pour la recherche BBP-CORE Programme doctoral en neurosciences

pour l'obtention du grade de Docteur ès Sciences

par

## Bruno Ricardo DA CUNHA MAGALHÃES

Acceptée sur proposition du jury Prof. D. Ghezzi, président du jury Prof. F. Schürmann, Prof. T. L. Sterling, directeurs de thèse Prof. M. Diesmann, rapporteur Prof. J. Labarta, rapporteur Prof. S. Deparis, rapporteur

"I have no special talent. I am only passionately curious." — Albert Einstein

## Acknowledgements

I would like to express my most heartfelt gratitude to Prof. Felix Schürmann for the opportunity of performing the PhD thesis at the Blue Brain Project laboratory, and for his supervision and guidance throughout these four years. I sincerely appreciate the freedom he gave me in discovering and developing my research directions and to learn new side skills in many topics of personal interest.

I would like to extend my gratitude to Michael Hines at Yale University for the scientific discussions, and all my lab colleagues at EPFL for their companionship and technical support. A great thanks to Francesco Cremonesi for the very fruitful mathematical discussions. His positiveness and dedication to science were very inspiring.

Equally, I thank all the colleagues at the Center for Research in Extreme Scale Technologies at Indiana University, for the technical support and the rewarding moments spent in Bloomington. A special thanks to my thesis co-director, Professor Thomas Sterling, for the personal inspiration and motivation, and Tim Gilmanov and Sarah Carroll for their friendship and hospitality.

My warmest thanks to my Lausanne friends Ronny Hatteland, Henriette Gjaerde, Jessica Brühlmann, James King, Alexandre Chausson, Sheena Rupa, Luis Polo Carbayo, Ginal Schlatter and Dumas Galvez, for all the amazing moments and the strong friendship.

I express my sincere gratitude to my team mates at the Lausanne Natation waterpolo team, for all the moments of intense yet joyful physical training in the swimming pool, and all the moments of fun outside.

Last but not least, I would like to thank my parents, Alberto and Maria, and all my family for their unconditional support and love.

Lausanne, 1st July 2019

B. M.

## Abstract

Simulations of the electrical activity of networks of morphologically-detailed neuron models allow for a better understanding of the brain. Short time to solution is critical in order to study long biological processes such as synaptic plasticity and learning.

State-of-the-art approaches follow the Bulk Synchronous Parallel execution model based on the Message Passing Interface runtime system. The efficient simulation of networks of simple neuron models is a well researched problem. However, the efficient large-scale simulation of detailed neuron models — including topological information and a wide range of complex biological mechanisms — remains an open problem, mostly due to the high complexity of the model, the high heterogeneity of specifications in modern compute architectures, and the limitations of existing runtime systems.

In this thesis, we explore novel methods for the asynchronous multi-scale simulation of detailed neuron models on distributed parallel compute networks.

In the first study, we introduce the concept of distributed asynchronous branch-parallelism of neurons. We present a method that extracts variable dependencies across numerical resolution of neurons topological trees and the underlying algebraic solver. We demonstrate a method for the decomposition of the neuron simulation problem into interconnected resolutions of neuron subtrees. Results demonstrate a significant reduction in runtime on heterogeneous distributed, multi-core, Single Instruction Multiple Data (SIMD) computing environments.

In the second study, we complement the previous effort with graph-parallelism retrieved from mathematical dependencies across the systems of Ordinary Differential Equations (ODEs) that model the activity of neurons. We describe a method for the automatic extraction of read-after-write variable dependencies, concurrent variable updates, and independent ODEs. The automation of the methods expose a computation graph of biological mechanisms inter-dependency, and an embarrassingly-parallel SIMD execution of mechanism instances, leading to an acceleration of the simulation.

The third part of this thesis pioneers the fully-asynchronous parallel execution model, and the *exhaustive yet not speculative* stepping protocol. We apply it to our use case, and demonstrate that by removing collective synchronization of neurons in time, by utilising a memory-linear neuron representation, and by advancing neurons based on their synaptic connectivity, a substantial runtime speed-up is achievable through cache efficiency.

#### Abstract

The fourth and last part advances the aforementioned fully-asynchronous execution model with variable-order variable-timestep interpolation methods. We demonstrate low dependency of runtime and step count on volatility of solution, and a high dependency on synaptic events. We introduce a variable-step execution model that allows for non-speculative asynchronous stepping of neurons on a distributed compute network. We demonstrate higher numerical accuracy, less interpolation steps, and shorter time to solution, compared to state-of-the-art implicit fixed-step resolution.

This thesis demonstrates that utilising asynchronous runtime systems is a requirement to succeed in efficiently simulating complex neuronal activity at large scale. Most contributions presented follow from first principles in numerical methods and computer science, thus providing insights for applications on a wide range of scientific domains.

#### **Keywords**

Asynchronous simulation, neural networks, NEURON simulator, branch-parallelism, graphparallelism, cache-efficiency, variable timestep interpolation, asynchronous runtime systems, HPX, ParalleX

## Résumé

Il est possible de mieux comprendre le cerveau en simulant l'activité électrique de réseaux de neurones morphologiquement détaillés. Le temps d'exécution de ces modèles doit être le plus court possible afin d'étudier de longs processus biologiques tels que la plasticité synaptique et l'apprentissage.

L'état de l'art actuel suit le modèle d'exécution Bulk Synchronous Parallel basé sur l'environnement d'exécution Message Passing Interface. La simulation efficace de réseaux de modèles de neurones simples est un problème bien recherché. Néanmoins, la simulation efficace à grande échelle de modèles neuronaux détaillés — comprenant des informations topologiques et une vaste collection de mécanismes biologiques complexes — reste un problème ouvert, principalement en raison de la grande complexité du modèle, de la grande hétérogénéité des spécifications dans les architectures d'ordinateurs modernes et des limites des environnements d'exécution existants.

Dans cette thèse, nous explorons de nouvelles méthodes pour la simulation asynchrone multi-échelle de modèles de neurones détaillés sur des réseaux parallèles et distribués de calcul.

Dans la première étude, nous introduisons le concept de parallélisme de branche asynchrone et distribué de neurones. Nous présentons une méthode qui extrait des dépendances variables à travers la résolution numérique des arbres topologiques de neurones et du résolveur algébrique sous-jacent. Nous démontrons une méthode pour la décomposition du problème de simulation de neurones en résolutions interconnectées de sous-arbres de neurones. Les résultats démontrent une réduction significative du temps d'exécution dans des environnements informatiques hétérogènes distribués, multicœurs, à instruction unique, données multiples (SIMD).

Dans la deuxième étude, nous poursuivons l'effort précédent avec le parallélisme de graphe extrait des dépendances mathématiques des systèmes d'équations différentielles ordinaires (ODE) modélisant l'activité électrique des neurones. Nous décrivons une méthode d'extraction automatique des dépendances de variable lecture-après-écriture, des mises à jour de variables simultanées et des ODE indépendants. L'automatisation des méthodes expose un graphe de calcul d'interdépendance des mécanismes biologiques et une exécution SIMD et parallèle d'instances de mécanismes, conduisant à une accélération de la simulation.

#### Resumé

La troisième partie de cette thèse inaugure le modèle d'exécution complétement asynchrone et le domaine de simulation *exhaustif mais non spéculatif*. Nous l'appliquons à notre cas d'utilisation et démontrons qu'en supprimant la synchronisation collective de l'interpolation temporelle des neurones, en utilisant une représentation linéaire de neurones en mémoire et en faisant avancer les neurones dans le temps en fonction de leur connectivité synaptique, une accélération substantielle de l'exécution est possible grâce à un meilleur accès de la mémoire cache.

La quatrième partie compléte la méthode asynchrone susmentionnée avec une résolution numérique basée sur les méthodes implicites avec ordre et pas-de-temps variables. Nous analysons la sensibilité numérique de nos méthodes et démontrons une faible dépendance de l'exécution et du nombre d'étapes vis à vis de la volatilité de la solution, ainsi qu'une forte dépendance vis à vis des événements synaptiques. Nous introduisons un modèle d'exécution à pas-de-temps variable qui permet une interpolation asynchrone et non-spéculative de neurones sur un réseau de calcul distribué. Nous démontrons une plus grande précision numérique, moins de pas-de-temps d'interpolation et un temps de résolution plus court, par rapport à la résolution implicite de l'état de l'art.

Cette thèse démontre que l'utilisation de systèmes d'exécution asynchrones est une nécessité pour réussir à simuler efficacement activité neuronale complexe à grande échelle. La plupart des contributions présentées découlent des principes de base des méthodes numériques et de la science informatique, fournissant ainsi des pistes pour l'application dans un large éventail de domaines scientifiques.

#### **Mots-clés**

Simulation asynchrone, réseaux de neurones, simulateur NEURON, parallélisme de branche, parallélisme de graphe, efficacité d'appel de cache, interpolation à pas-de-temps variable, environnement d'exécution asynchrones, HPX, ParalleX

## Contents

| Acknowledgements |          |          | v                                                                                                               |      |

|------------------|----------|----------|-----------------------------------------------------------------------------------------------------------------|------|

| Al               | Abstract |          |                                                                                                                 | vii  |

| Re               | Resumé   |          |                                                                                                                 | ix   |

| Li               | st of ]  | Figures  | i de la constante de la constan | xiv  |

| Li               | st of '  | Tables   |                                                                                                                 | xvii |

| 1                | Intr     | oductio  | on                                                                                                              | 1    |

|                  | 1.1      | State of | of the Art                                                                                                      | 2    |

|                  |          | 1.1.1    | Single Compute Node Executions                                                                                  | 3    |

|                  |          | 1.1.2    | Branch-Parallelism                                                                                              | 3    |

|                  |          | 1.1.3    | Spatial Decomposition                                                                                           | 4    |

|                  |          | 1.1.4    | Variable Timestep Interpolation                                                                                 | 4    |

|                  |          | 1.1.5    | Distributed Compute Environments                                                                                | 5    |

|                  | 1.2      | Limita   | ations                                                                                                          | 7    |

|                  |          | 1.2.1    | Efficient Usage of Compute Resources                                                                            | 7    |

|                  |          | 1.2.2    | Handling of Complex Neuron Models                                                                               | 7    |

|                  | 1.3      | Motiva   | ation                                                                                                           | 8    |

|                  | 1.4      | Resear   | rch Scope                                                                                                       | 9    |

|                  | 1.5      | Runtir   | me Systems                                                                                                      | 9    |

|                  |          | 1.5.1    | MPI: Message Passing Interface                                                                                  | 11   |

|                  |          | 1.5.2    | HPX: High Performance ParalleX                                                                                  | 11   |

|                  | 1.6      | Refere   | ence Implementation                                                                                             | 12   |

|                  |          | 1.6.1    | Computational Model                                                                                             | 12   |

|                  |          | 1.6.2    | Spatial Discretization                                                                                          | 14   |

|                  |          | 1.6.3    | Branching                                                                                                       | 14   |

|                  |          | 1.6.4    | Fixed Step Interpolation                                                                                        | 15   |

|                  |          | 1.6.5    | Parallel Executions                                                                                             | 16   |

|                  |          | 1.6.6    | Workflow                                                                                                        | 17   |

|                  | 1.7      | Thesis   | Structure                                                                                                       | 18   |

|                  |          | 1.7.1    | Asynchronous Branch-Parallelism                                                                                 | 18   |

#### Contents

|   |      | 1.7.2 Asynchronous Graph-Parallelism 19                                     |

|---|------|-----------------------------------------------------------------------------|

|   |      | 1.7.3 Fully-Asynchronous Fixed-Step Execution Model                         |

|   |      | 1.7.4 Fully-Asynchronous Variable-Order Variable-Timestep Execution Model 2 |

| 2 | Asy  | nchronous Branch-Parallelism Extracted from Neuron Morphology 2             |

|   | 2.1  | Abstract                                                                    |

|   | 2.2  | Introduction                                                                |

|   | 2.3  | Methods 2                                                                   |

|   |      | 2.3.1    Dependency Parameters    2                                         |

|   |      | 2.3.2 Neuron Tree Decomposition and Parallel Execution 2                    |

|   |      | 2.3.3 Vector-based Acceleration                                             |

|   |      | 2.3.4 Asynchronous Execution of State Updates 22                            |

|   |      | 2.3.5 Distributed Load Balancing                                            |

|   | 2.4  | Benchmark                                                                   |

|   |      | 2.4.1 Implementation                                                        |

|   |      | 2.4.2 Use Case                                                              |

|   |      | 2.4.3 Hardware Specifications                                               |

|   |      | 2.4.4 SIMD vs Multi-core Trade-off Optimization 33                          |

|   |      | 2.4.5 Reference Branch-Parallel Implementation 33                           |

|   |      | 2.4.6 Scaling of Single Neurons                                             |

|   |      | 2.4.7 Scaling of Networks of Neurons 3.                                     |

|   | 2.5  | Discussion                                                                  |

| 3 | Asy  | nchronous Graph-Parallelism Extracted from ODE Dependencies 33              |

|   | 3.1  | Abstract                                                                    |

|   | 3.2  | Introduction                                                                |

|   | 3.3  | Methods 4                                                                   |

|   |      | 3.3.1 Dependencies from Model Specification                                 |

|   |      | 3.3.2 Application to NEURON Modelling Language                              |

|   |      | 3.3.3 Computation Graph from Individual Dependencies 4                      |

|   |      | 3.3.4 Vector-Parallelism of Mechanism Instances 4                           |

|   | 3.4  | Benchmark                                                                   |

|   |      | 3.4.1 Implementation                                                        |

|   |      | 3.4.2 Use Case                                                              |

|   |      | 3.4.3 Hardware Specifications                                               |

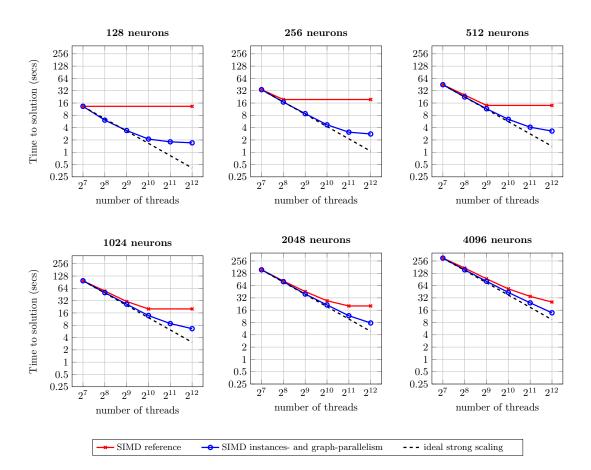

|   |      | 3.4.4 Strong Scaling                                                        |

|   |      | 3.4.5 Distributed Executions                                                |

|   | 3.5  | Discussion                                                                  |

| 4 | Full | y-Asynchronous Cache-Efficient Simulation 5                                 |

|   | 4.1  | Abstract                                                                    |

|   | 4.2  | Introduction                                                                |

|   | 4.3  | Methods 5                                                                   |

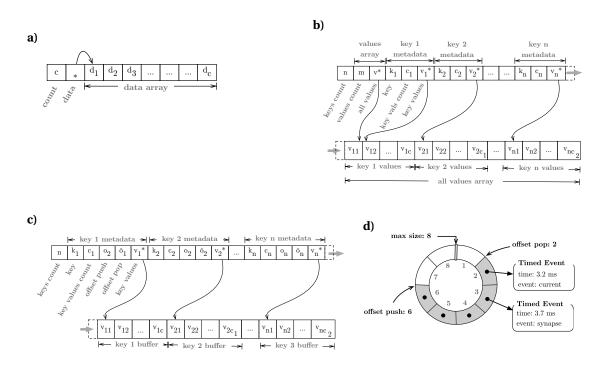

|   |      | 4.3.1 Linear Data Structures                                           |

|---|------|------------------------------------------------------------------------|

|   |      | 4.3.2 Time-Based Elements Synchronization and Stepping                 |

|   |      | 4.3.3 Neuron Scheduler                                                 |

|   |      | 4.3.4 Communication Reduce                                             |

|   | 4.4  | Benchmark                                                              |

|   |      | 4.4.1 Implementation                                                   |

|   |      | 4.4.2 Use Case                                                         |

|   |      | 4.4.3 Hardware Specifications                                          |

|   |      | 4.4.4 Linear Containers                                                |

|   |      | 4.4.5 Neuron Scheduler and Asynchronous Stepping                       |

|   |      | 4.4.6 Communication Reduce                                             |

|   |      | 4.4.7 Single Compute Node Executions                                   |

|   |      | 4.4.8 Distributed Executions                                           |

|   | 4.5  | Discussion                                                             |

| 5 | Full | y-Async. Fully-Implicit Variable-Order Variable-Timestep Simulation 69 |

|   | 5.1  | Abstract                                                               |

|   | 5.2  | Introduction                                                           |

|   | 5.3  | Methods                                                                |

|   |      | 5.3.1 Resolution of Simple and Complex Neuron Models                   |

|   |      | 5.3.2 Variable Step Implementation                                     |

|   |      | 5.3.3 Asynchronous Timestepping of Networks of Neurons                 |

|   | 5.4  | Results                                                                |

|   |      | 5.4.1 Numerical Accuracy 75                                            |

|   |      | 5.4.2 Performance Dependency on Solution Stiffness                     |

|   |      | 5.4.3 Performance Dependency on State Discontinuities                  |

|   |      | 5.4.4 Simulation of a Laboratory Experiment                            |

|   | 5.5  | Benchmark                                                              |

|   |      | 5.5.1 Implementation                                                   |

|   |      | 5.5.2 Use Case                                                         |

|   |      | 5.5.3 Fixed- vs Variable-Timestep Interpolators 82                     |

|   |      | 5.5.4 Variable Step Event Grouping                                     |

|   |      | 5.5.5 Fully-Asynchronous vs Bulk-Synchonous Execution Models 85        |

|   |      | 5.5.6 Runtime Dependency on Input Size and Spike Activity              |

|   |      | 5.5.7 Overall Runtime Speedup Estimation                               |

|   | 5.6  | Discussion                                                             |

| 6 | Gen  | eral Discussion and Conclusions 89                                     |

|   | 6.1  | Summary                                                                |

|   |      | 6.1.1 Micro-Parallelism of Detailed Neuron Models                      |

|   |      | 6.1.2 Fully-Asynchronous Execution Model                               |

|   | 6.2  | Contributions                                                          |

|   | 6.3  | Performance Outlook                                                    |

#### Contents

| 6.4     | Future Work                                                      | 97  |

|---------|------------------------------------------------------------------|-----|

|         | 6.4.1 Combined Micro-Parallelism Methods                         | 97  |

|         | 6.4.2 Automatic Tuning of Data Layout to Hardware Specifications | 97  |

|         | 6.4.3 Variable Timestepping Without Discontinuities              | 98  |

|         | 6.4.4 Finer-Tuned CVODE Execution and Parameters                 | 98  |

|         | 6.4.5 Asynchronous Speculative Execution                         | 98  |

|         | 6.4.6 Distributed Load Balancing                                 | 99  |

|         | 6.4.7 Support for Graphics Processing Units                      | 100 |

| 6.5     | Closing Discussion                                               | 100 |

| A Gen   | eralization: from Gaussian Elimination to Hines Solver           | 103 |

| B Met   | hods Availability and Reproducibility                            | 105 |

| C Scie  | entific Papers                                                   | 107 |

| Bibliog | Bibliography                                                     |     |

| Refe    | erences                                                          | 109 |

# List of Figures

| 1.1        | The scope of the simulation scale and morphologically detailed neuron models covered in this thesis                                                         | 2  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2        | Scope of the interpolation methods discussed                                                                                                                | 6  |

| 1.3        | The topological structure of a sample neuron, and its representative sparse tridiagonal tree representation                                                 | 15 |

| 1.4        | Workflow of one compute step of the numerical resolution of our simulation model                                                                            | 17 |

| 2.1        | Scope and key concepts of the branch-parallelism methods                                                                                                    | 23 |

| 2.2        | Algorithms of the initial matrix values set-up, Gaussian Elimination and voltage update methods                                                             | 25 |

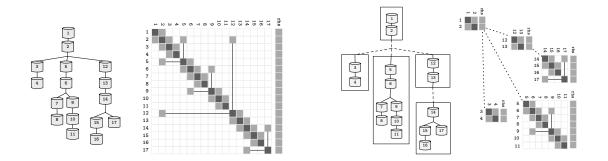

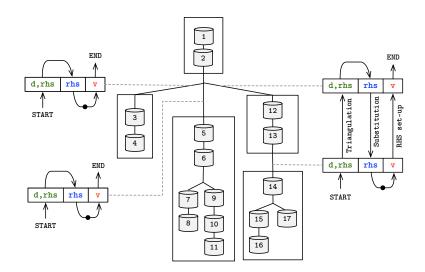

| 2.3        | A sample workflow of the algorithm that decomposes neuron morphologies into a tree of subtrees                                                              | 26 |

| 2.4        | The topological structure of a neuron and its representative matrix, before and after the subtree decomposition algorithm                                   | 27 |

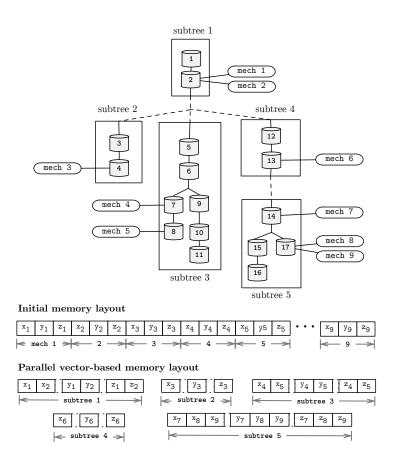

| 2.5        | The topological structure of a neuron after clustering into 5 subtrees, and mem-<br>ory layouts for the pre- and post- subtree clustering phases            | 28 |

| 2.6        | Overview of the asynchronous producer-consumer model for dependency vari-<br>ables                                                                          | 30 |

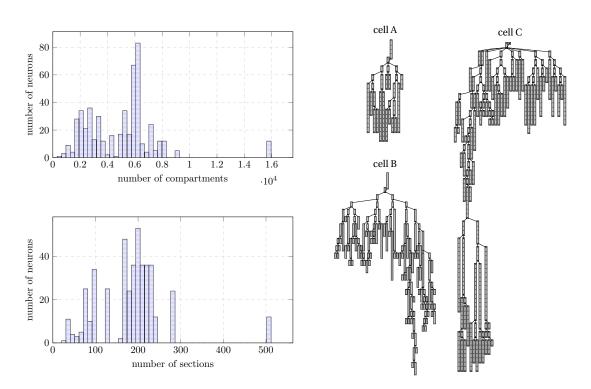

| 2.7        | Morphological structure of the Layer 5 neurons extracted from the digital recon-                                                                            |    |

| 2.8        | struction of the rodent neocortex used as input data                                                                                                        | 32 |

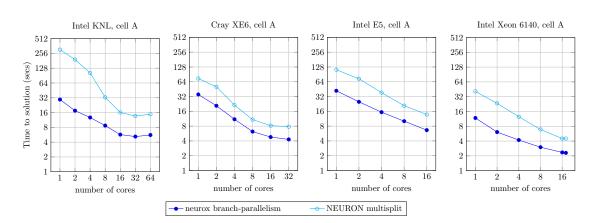

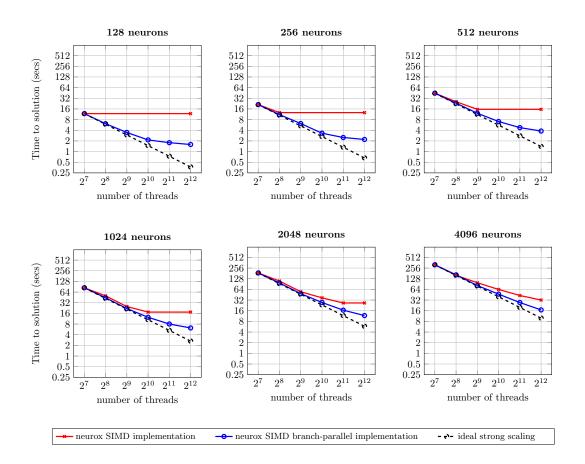

|            | of one cell, comparing the multisplit implementation in NEURON and our methods, benchmarked on four compute architectures                                   | 34 |

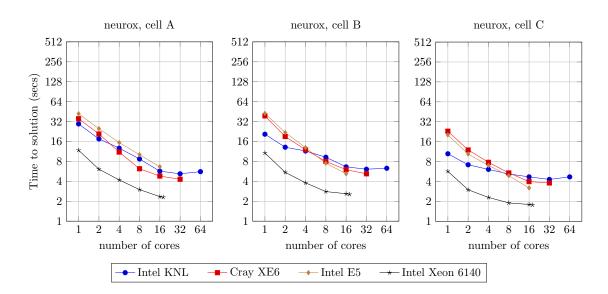

| 2.9        | Strong scaling benchmark for the simulation of one second of electrical activ-<br>ity of three different Layer 5 neuron models, benchmarked on four compute |    |

| 2.10       | architectures                                                                                                                                               | 35 |

|            | neurons, on a Cray XE6 cluster with 128 compute nodes                                                                                                       | 36 |

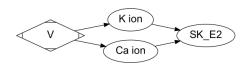

| 3.1<br>3.2 | Diagram of the flow dependencies of the SK_E2 potassium ion channel Diagram of the flow dependencies and concurrent outputs of the SK_E2 potas-             | 42 |

|            | sium ion channel                                                                                                                                            | 42 |

#### List of Figures

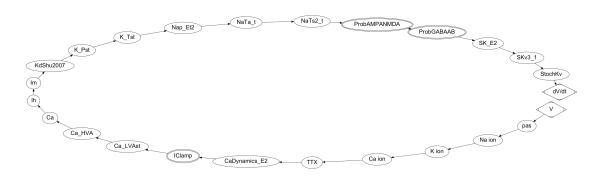

| 3.3        | Workflow of the state-of-the-art approach for the state update of a neuron mor-<br>phology with 23 mechanisms                                                                                                                                | 44       |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.4        | Computation graph for the parallel execution of the state update function with flow dependencies and concurrent updates                                                                                                                      | 45       |

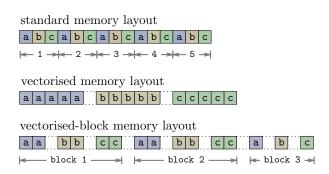

| 3.5        | Three alternative memory layouts for the processing of one mechanism with three state variables expressed in five instances                                                                                                                  | 46       |

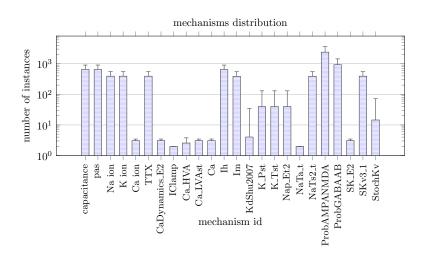

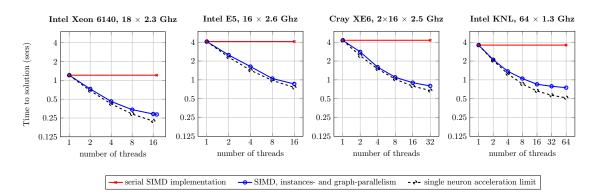

| 3.6        | Mean and standard deviation of the number of instances per mechanism, ex-<br>tracted from 1000 neurons in the layer 5 of the Somatosensory cortex of the<br>rodent brain                                                                     | 48       |

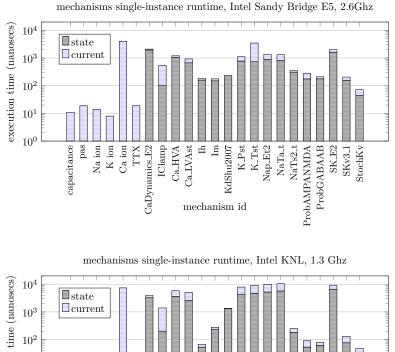

| 3.7        | Average execution time for the timestep update of single instances of the mecha-<br>nisms, extracted from 1000 neurons in the layer 5 of the Somatosensory cortex                                                                            |          |

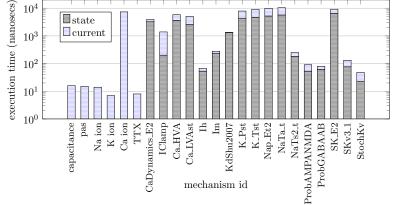

| 3.8        | of the rodent brain                                                                                                                                                                                                                          | 49<br>51 |

| 3.9        | Benchmark for the simulation of $100ms$ of electrical activity of the neocortex,<br>on a cluster of 128 Cray XE6 compute nodes                                                                                                               | 52       |

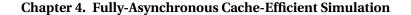

| 4.1        | Distribution of synaptic delays in terms of count and percentage of all synapses                                                                                                                                                             |          |

|            | in a network of 219.247 neurons                                                                                                                                                                                                              | 56       |

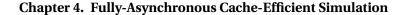

| 4.2<br>4.3 | Memory representation of linear data structures                                                                                                                                                                                              | 58       |

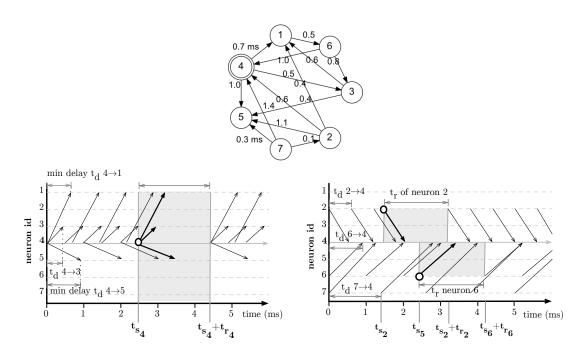

| 4.4        | nization of stepping and spikes, applied to a network of seven neurons A sample workflow of four iterations of the neuron scheduler applied to a net-                                                                                        | 60       |

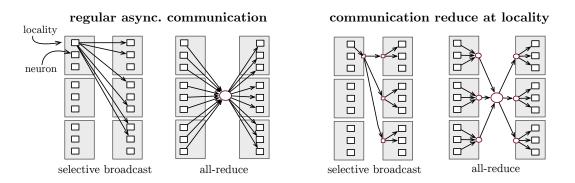

| 4.5        | work of seven neurons                                                                                                                                                                                                                        | 61       |

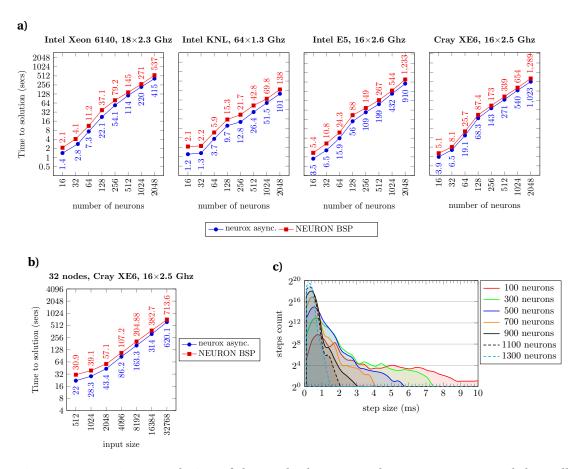

| 4.6        | reduce operations using regular versus locality-reduced communication<br>Benchmark of the synchronous versus Bulk Synchronous Parallel execution<br>models of the simulation of 100 <i>ms</i> of the electrical activity of different neural | 62       |

|            | networks, on four different hardware specifications                                                                                                                                                                                          | 66       |

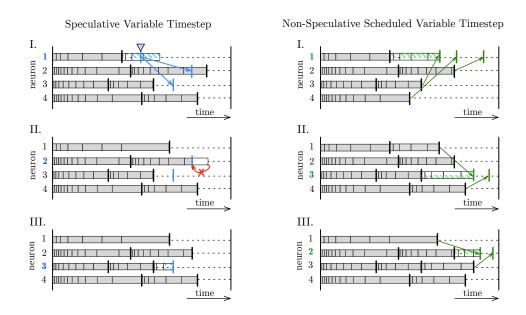

| 5.1        | Illustrative workflow of the speculative and the non-speculative scheduler-based variable timestep methods analysed                                                                                                                          | 73       |

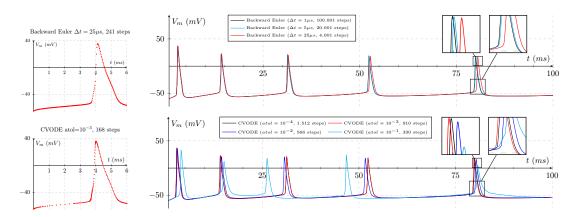

| 5.2        | Voltage potential at the soma and interpolation steps of a layer 5 pyramidal cell, during a $6ms$ and $100ms$ simulation of a $1.3mA$ continuous current injection .                                                                         | 75       |

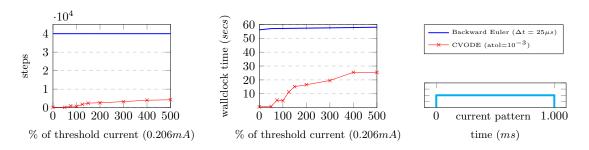

| 5.3        | Interpolation steps and runtime for the $1000ms$ simulation of the injection of a continuous constant current as a percentage of the threshold current (0.206 $mA$ ),                                                                        | -0       |

| 5.4        | on a layer 5 pyramidal cell                                                                                                                                                                                                                  | 76       |

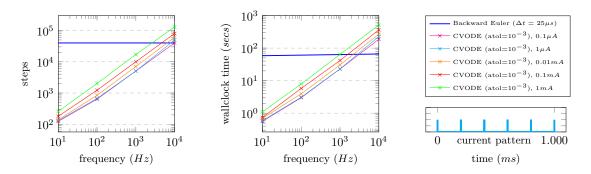

| 5.5        | layer 5 pyramidal cell                                                                                                                                                                                                                       | 77       |

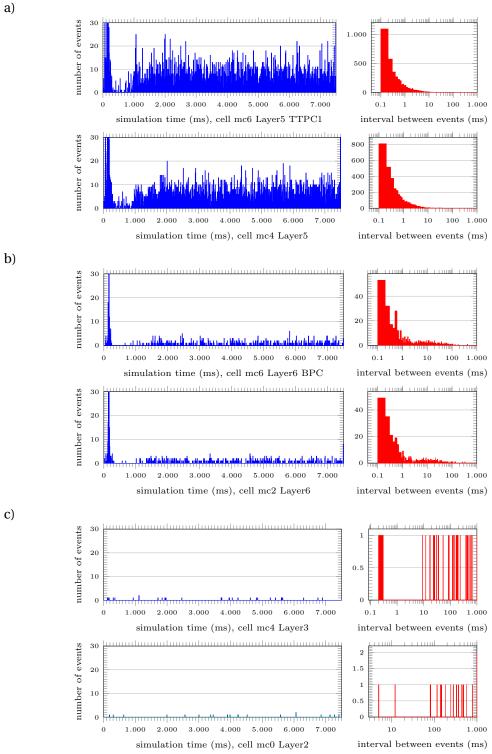

|            | three sample neurons throughout 7.5 seconds of simulation                                                                                                                                                                                    | 79       |

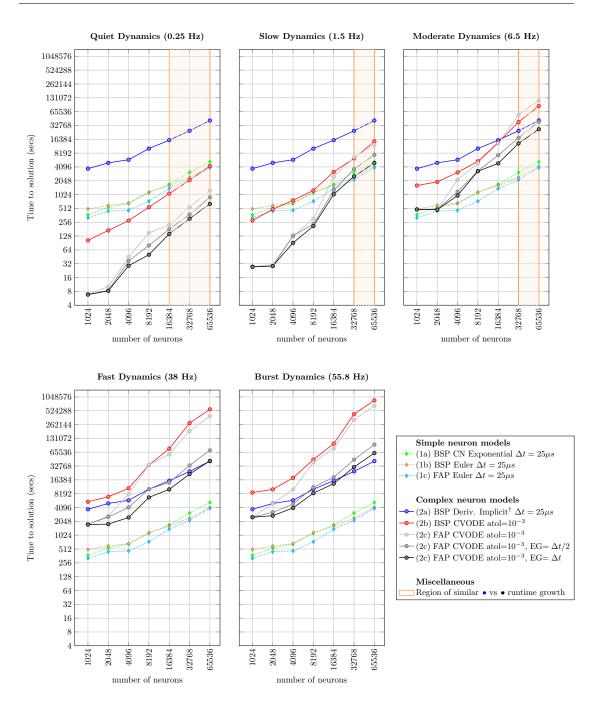

| 5.6 | Runtime for the simulation of one second of biological activity of five neuron  |    |

|-----|---------------------------------------------------------------------------------|----|

|     | networks described by different spiking rate dynamics                           | 83 |

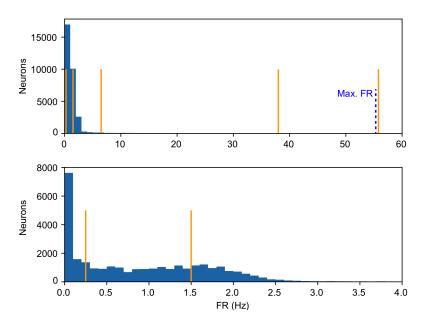

| 5.7 | Distribution of neuron counts by spiking rates collected from the central mini- |    |

|     | column of the network utilized in the simulation of the laboratory experiment,  |    |

|     | in the interval 2-4 secs                                                        | 85 |

# List of Tables

| 4.1 | Cache efficiency of linear and standard library containers, measured for the |    |

|-----|------------------------------------------------------------------------------|----|

|     | Asynchronous and Bulk Synchronous Parallel execution models                  | 65 |

| 4.2 | Performance of regular versus locality-reduced communication in terms of     |    |

|     | runtime, and number of point-to-point and reduce communications, on the      |    |

|     | Bulk Synchronous Parallel and asynchronous execution models                  | 67 |

## **1** Introduction

This chapter is adapted from the preprint version of the following articles:

**Magalhães B.**, Hines M., Sterling T., Schürmann F., "Exploiting Flow Graph of System of ODEs to Accelerate the Simulation of Biologically-Detailed Neural Networks", accepted at IEEE International Parallel & Distributed Processing Symposium (IPDPS) 2019

**Magalhães B.**, Hines M., Sterling T., Schürmann F., "Asynchronous Branch-Parallel Simulation of Detailed Neuron Models", submitted to Frontiers in Neuroinformatics 2019

**Magalhães B.**, Hines M., Sterling T., Schürmann F., "Fully-Asynchronous Cache-Efficient Simulation of Detailed Neural Networks", accepted at International Conference on Computational Science (ICCS) 2019

**Magalhaes B.**, Hines M., Sterling T., Schürmann F., "Fully-Asynchronous Fully-Implicit Variable-Order Variable-Timestep Simulation of Neural Networks", published on arXiv

Personal contributions: conceptualization, writing.

Over the past years, the simulation of the activity of large neural networks has received increasing interest (Kandel et al., 2013; Markram, 2012; Shepherd et al., 1998). Experimental advances such as high resolution recording of neurons *in vivo* and *in vitro* have supported quantitative modeling. Biologically inspired simulations of neural circuits present an enormous opportunity for understanding the behaviour of the brain. Simulations can be performed on different details of neurons activity (Brette et al., 2007), ranging from biochemical reactions to a conductance-based simulation, or a simpler model such as integrate-and-fire (Brunel & Hakim, 1999). Moreover, different scales can be simulated, from a point neuron representation to a more complete morphologically detailed neuron model.

Recent efforts (Markram et al., 2015) presented for the first time a simulation of a morphologically detailed model of the neocortical microcircuit, simulated in the NEURON scientific application (Hines & Carnevale, 1997; Carnevale & Hines, 2006). This effort was part of the main mission of the Blue Brain Project (Markram, 2006; Hill & Markram, 2008) to digitally reconstruct and simulate the brain. The simulation was based on the multi-compartment Hodgkin-Huxley (HH) formalism (Hodgkin & Huxley, 1952). The HH model computes an approximation of the current passing through a section of the neuron's membrane, as a capac-

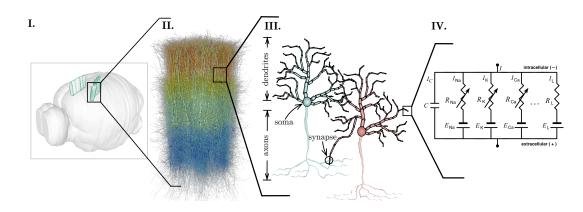

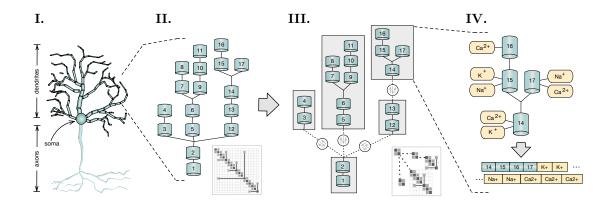

Figure 1.1 – The scope of the simulation scale and morphologically detailed neuron models covered in this thesis. I: The rodent brain with an exposed digital reconstruction of the lower limb of the primary somatosensory area; II: a cortical column of the previous brain region; III: model representation of two neurons and a synapse. Each neuron includes an axonic branch (south of soma, pictured in light) and a spatially-discretized representation of a tree of dendrites (north of soma, in dark). A synapse is a connection between an axon and a dendrite of different neurons; IV: the resistor–capacitor circuit (RC circuit) representing the electrical activity on the membrane of a single capacitor with ionic current leaks, also referred to as compartment.

itor with ionic conductances. Each neuron is modelled by a system of Ordinary Differential Equations (ODEs), that includes the change in voltage at the capacitor and the change in the opening and closing of the ion channels that drive the fluxes of ionic currents at the capacitor's membrane. Neurons are coupled with each other through synapses, that are electro-chemical transductors. For completeness, Figure 1.1 illustrates the scope and scale of the methods discussed.

Since it is not feasible to analytically solve complex HH equations, simulations typically employ numerical methods and standard time-discretized ODE solvers (Hines & Carnevale, 1994). The large number of equations involved in such systems leads to computationally costly simulations, that may be required to run for long periods of time (Helmstaedter & Mitra, 2012). The acceleration of such simulations is particularly relevant for the understanding of biological phenomena such as synaptic plasticity and learning. Such use cases may focus on the study of the dynamics between few neurons (Markram et al., 2012), small networks of neurons (Chindemi, 2018) or large populations of neurons (Morrison et al., 2007), with a biological time spanning from few minutes to several days to be expressed.

#### 1.1 State of the Art

Similarly to simulations in several scientific fields, acceleration of the simulation of such models typically follows the Bulk Synchronous Parallel (BSP) execution model (Gerbessiotis &

Valiant, 1994), computing several neurons simultaneously via a synchronized multi-thredead distributed execution (Tikidji-Hamburyan et al., 2017). Execution time is divided in equidistant time intervals, equivalent to the time duration of the shortest synaptic delay across all neuron pairs in the network (Migliore et al., 2006). The synaptic delay for a given synapse between a **pre-** and a **post-synaptic** neuron is defined by the time for current propagation from the soma of a pre-synaptic neuron to the extremity of the axon branch, and the neurotransmitter release to the post-synaptic receptor. Stepping of neurons is performed independently within the boundaries of each synchronization interval.

The theoretical limit of acceleration on the BSP model is dictated by the most complex compute kernel in the network, whose state update takes the longest to compute. The extent of a kernel, representing the activity of a group of neurons, a single neuron, a subsection of the neuron topology, a compartment, or a biological mechanism such as ion channels, varies extensively and depends on the implementation and scale of parallelism exposed, as detailed next.

#### 1.1.1 Single Compute Node Executions

Acceleration of the simulation of networks of point neuron models has been previously demonstrated with multi-core parallelism of individual neurons, combined with Single Instruction Multiple Data (SIMD or vectorized) computing of neuron state variables, in Brian (Goodman & Brette, 2008; Brette & Goodman, 2011), Auryn (Zenke & Gerstner, 2014) and NEST simulators (Gewaltig & Diesmann, 2007).

The acceleration of networks of branched morphologies utilising multi-core Singe Instruction Single Data (SISD) has been covered extensively by the NEURON simulator (Hines & Carnevale, 1997), with added SIMD capabilities demonstrated by the CoreNeuron (Kumbhar et al., 2016, 2019) and Arbor (Klijn et al., 2017) scientific applications. The SIMD methods proposed take advantage of the similarity across ODEs of individual neurons, allowing them to be grouped together in a SIMD-friendly memory layout, enabling full usage of the processor's register file width.

Multi-core execution of neurons is typically performed with OpenMP (Dagum & Menon, 1998) and/or POSIX threads (Butenhof, 1997), with synchronization of neurons stepping performed with a threading barrier executed at an interval equivalent to the shortest synaptic delay. This guarantees no overstepping of solution interpolation in time, and no missed synaptic events in the stepping interval between the current and the next synchronization instants.

#### 1.1.2 Branch-Parallelism

Further acceleration can be achieved on the strong scaling axis with finer-grained parallelism of individual neuron models, via the decomposition of simulation steps into smaller compute kernels, leading to the increase of compute units assigned to each neuron. Finer-grained parallelism efforts have been demonstrated based on branch sections parallelism, by extracting

variable dependencies across compartmental neuron trees, and performing a sub-sectioning of the topological structure of neurons. Related work has been presented on the NEURON scientific simulator (Hines et al., 2008), demonstrating parallelism of neuron subtrees on a network of single-core architectures with a Single-Instruction Single-Data (SISD) instruction stream.

#### 1.1.3 Spatial Decomposition

Orthogonal volumetric decomposition and parallel-distributed processing of volumetric regions have been explored for branched neuron models (Kozloski & Wagner, 2011). This approach is most suitable for the simulation of spatially organized and computationally costly elements, as the computation must be large enough to overlap the high communication required — executed at every computation timestep — between neighbouring spatial regions in different compute nodes. Memory-wise, such implementations based on spatial decomposition have been shown to yield a high memory overhead and load imbalance due to the duplication (*ghosting*) of branch sections in high density regions in networks of detailed neural networks (Magalhães et al., 2016).

Alternative implementations based on the tessellation of compartmental space has been presented for lower scales of simulations, with the main efforts driven by the STEPS simulator (Hepburn et al., 2012) for the stochastic simulation of reaction-diffusion systems at the molecular level of neuron models and extra-cellular space.

#### 1.1.4 Variable Timestep Interpolation

An acceleration based on improved numerical resolution is also possible by utilizing a method for variable-step interpolation of individual neurons, and has been presented and implemented in NEURON (Lytton & Hines, 2005). The method details an implementation of adaptive-step interpolation of individual neurons, by utilising the CVODE library (Cohen & Hindmarsh, 1996), a C implementation of the VODE algorithm (Brown et al., 1989), part of the SUNDIALS package (Hindmarsh et al., 2005). The VODE is a Backward Differentiation Formula (BDF) method of variable-order and variable-step for the resolution of Initial Value Problems (IVPs) for stiff ordinary differential equations (Cash, 1980). For a given function and time, it approximates the derivative of a function using information from previous steps (stored in the state history), thereby increasing the accuracy of the numerical resolution. The step size is tentatively computed in order to respect an user-provided absolute tolerance, thus adapting the step size to rapid variations of voltage trajectory. Current events that cause a discontinuity of solution force the integrator to start again with a new IVP. Interpolation methods presented allow for two distinct stepping models: (1) a globally synchronous step for all neurons, mostly suitable for models with short event delays and no discontinuities such as gap junction and simulations with detailed axon branching; or (2) a local variable step per neuron advancing neurons speculatively with reversal of state in the occurrence of overstepping and missed events.

#### 1.1.5 Distributed Compute Environments

Due to storage and compute requirements, large scale simulations require the use of supercomputing infrastructures. Similarly to single node implementations, executions follow the BSP execution model, extended to a network of compute nodes. Stepping synchronization and exchange of synapses are performed at the node and at the network level (Migliore et al., 2006; Plesser et al., 2007; Morrison et al., 2005). This is typically performed via Message Passing Interface (MPI) communication (Lusk et al., 2009), alongside local neurons synchronization via OpenMP or other threading control library. Synaptic communication is performed via collective communication calls as part of the previous synchronization step, with a collective scatter-gather (MPI\_Alltoall) or gather (MPI\_AllGather) operation. A hardware-specific and more scalable solution has been presented on an IBM BlueGene/P using the Deep Computing Messaging Framework (DCMF) runtime (Hines et al., 2011; Kumar et al., 2010), based on immediate selective broadcasts of spikes and a synchronization barrier at the end of every communication step.

Efficient usage of resources is possible when the input dataset is *large enough* to allow enough flexibility to balance neurons across compute units, in such way that static load balancing can be performed accurately beforehand. This has been demonstrated by the Least Processing Time (LPT) algorithm (Korf, 1998), yielding quasi-balanced workload distribution by iteratively assigning neurons to the compute node with the least total computation time.

Simulations at very large scales, particularly those requiring petascale compute power, have been covered extensively by the NEST simulator (Plesser et al., 2007) for point neuron models. At such scale, collective communication yields a significant overhead in the overall runtime. Memory and communication imbalance due to heterogeneous synaptic connectivity are the major scaling obstacles (Morrison et al., 2005; Kunkel et al., 2012). Studies have been conducted to analyse the technical aspects of running such simulations on large supercomputers and on the study of brain-scale networks, identifying memory overhead of the connection framework (i.e. synaptic connectivity) as the scaling limit of present implementations (Helias et al., 2012). However, the problem of memory imbalance is a hard problem for large network sizes, due to the heterogeneity in connectivity across synapses, and the overhead of MPI buffers required for accumulation of synapses throughout computation steps (Ippen et al., 2017). Communication-level optimizations are possible by taking advantage of the nature of the problem: neurons are connected to a small subset of other neurons that are held across a small fraction of the compute network. This allows for an optimization in communication by grouping synaptic target lists by types and number of synapses of a given type (Kunkel et al., 2014). Moreover, due to the upper limit of connectivity of single neurons, the connectivity sparsity across very large networks of neurons can be exploited by having a two-tier connectivity table that allows selective scatter-gather of synapses instead of the commonly-used collective

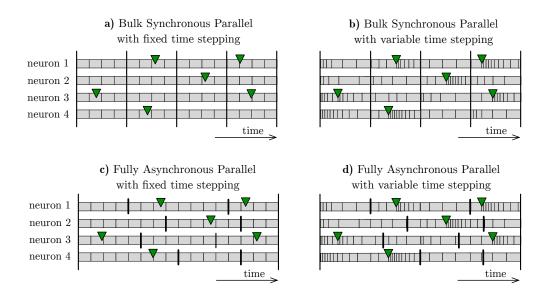

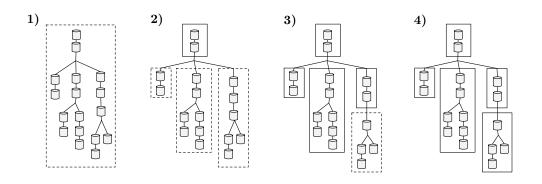

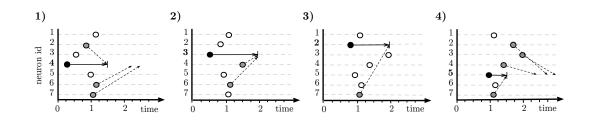

Figure 1.2 – Scope of the interpolation methods discussed, illustrated by four alternative approaches for the simulation of four neurons, on a left-to-right execution timeline. A gray cell represents a step of a neuron, with its width representing the timestep duration. Inverted green triangles represent delivery of synaptic events (solution discontinuities). Vertical bars across all neurons represent collective communication. Vertical bars across single neurons represent limit of stepping dictated by pre-synaptic neurons' time instants. **a**) Bulk Synchronous Parallel (BSP) model with fixed timestepping, and collective synchronization; **b**) BSP model with variable time step implemented in NEURON (Lytton & Hines, 2005) and collective synchronization. Backstepping operations are omitted; **c**) Fully-Asynchronous Parallel (FAP) execution model applied to fixed step interpolation, introduced in Chapter 4, with individual synchronization of neurons based on their connecting pre-synaptic neurons; **d**) FAP variable-step method presented in Chapter 5.

gather operation in NEURON, reducing the size of the MPI receive buffers, eliminating buffers' growth with the total number of processes, and yielding ideal scaling properties (Jordan et al., 2018).

An alternative provided by NEURON allows for a distributed execution with variable stepping, guaranteeing coherent time interpolation by enforcing neurons synchronization with a BSPbased communication barrier, therefore avoiding synaptic events being delivered in preceding instants in time (Migliore et al., 2006). Speculative stepping is allowed by a single step that traverses the synchronization instant, with posterior backstepping for missed events. The step size is limited to the instant of the nearest synaptic or discontinuity event.

For clarity, the BSP-based distributed implementations of fixed and variable timestep interpolations are illustrated in layouts a) and b) in Figure 1.2, respectively.

#### 1.2 Limitations

The problem of efficiently computing large scale networks of highly heterogeneous neuron models is then twofold.

#### 1.2.1 Efficient Usage of Compute Resources

At first, due to the large scale of data and computation involved in the problem specification, simulations require high performance computing techniques in order to compute the solution in a feasible time. Thus, acceleration efforts rely on the parallel and distributed computation of several neurons simultaneously.

The highly-heterogeneous specifications of modern compute architectures requires a computation model that adapts the problem to the host architecture. Due to the wide extent of scales and models required for different biological use cases, such a computation model should be flexible enough to fully utilize the available compute resources, independently of the complexity of the neuron and network models. However, state-of-the-art approaches are based on a wide collection of simulators that are often scale specific, and/or utilise only a reduced subset of the compute architecture capabilities.

Moreover, the commonly utilized MPI runtime provides a powerful communication and synchronization framework for collective operations on distributed compute nodes, with a minimal interface for point-to-point communication, making it most suitable for problems characterized by homogeneous data types and computation across compute nodes. Never-theless, it does not provide core-level parallelism, remote procedure calls, futures, callback methods, pointer addressing in distributed memory, data balancing primitives, remote flow-control objects such as semaphores and mutual exclusion gates. In practice, it lacks several features that would be essential for the resolution of more complex problems. In addition, any extra feature that is not part of the library requires a strenuous development effort combining third-party libraries and a user-programmed workflow performing communication of intermediate data structures across nodes. Complementary, state-of-the-art efforts for *on node* acceleration such as OpenMP (Dagum & Menon, 1998) and the ones provided by the C++20 standard (Standard C++ Foundation, 2019) provide parallelism and asynchronicity, yet are limited to a single compute node. The problem is therefore not trivial.

#### 1.2.2 Handling of Complex Neuron Models

As a second point, advancements in biological and computational neuroscience fields introduce new use cases that increase the complexity of the models currently being simulated, and that have not been properly accounted for by existing methods. To name a few:

• Higher resolution of morphological trees, combined with new ion channels and biologi-

cal mechanisms, that greatly increase the complexity of the model and the disparity in computational workload across neurons, and require micro-parallelism techniques that accelerate the simulation of individual neurons;

- Models of very large networks display highly-heterogeneous spatial and temporal activity across neurons and require an interpolation model that adapts the allocation of compute resources to the neuronal activity of significance during runtime;

- New models of synaptic plasticity require a dynamic reconfiguration of network connectivity throughout the simulation, in order to overcome the limitations of the staticconnectivity graphs currently utilised;

- New models of neuronal branching growth, require dynamic fine-tuning of neuron topological trees to the hardware specifications throughout execution;

- Further complexity from biological phenomena such as astrocytes, gap junctions, and learning models that are characterized by highly-correlated and non-linear ODEs, whose computational implications have not been covered by previous research;

- Multi-scale simulations that combine several physical and time scales, introducing new data dependencies that go beyond the synaptic delay connectivity utilised in common simulations.

#### 1.3 Motivation

These limitations motivate the search for a computation model that accelerates the simulation of networks of detailed neural models, independently of the network size, and on a wide range of compute architectures, fully utilising multi-core and vector-based capabilities on distributed networks of compute nodes.

Modern runtime systems such as the High Performance ParalleX 5 (HPX-5) (Sterling et al., 2014), Charm++ (Kale & Krishnan, 1996), Legion (Bauer et al., 2012), HPX-3 (Kaiser et al., 2014) and OmpSs (Duran et al., 2011) provide programming models and runtimes for asynchronous parallelism and heterogeneity, with the capability of handling heterogeneous tasks and control objects in distributed compute and memory architectures. Such tools increase the possibilities of new neural simulations use cases — until now restricted to the BSP paradigm and MPI communication model — and are of particular relevance in the simulation of morphologically detailed neuron models, due to their capabilities in handling connectivity, computation, and memory asynchronously. Moreover, better-parallelism of neurons should allow for better usage of computing resources in modern architectures, and consequently, for simulations to compute at a runtime closer to real time.

While there is an ongoing debate on the most appropriate execution model, with an open space of research being continuously pursued to improve current runtime systems, the functionalities provided by existing asynchronous execution models are worth exploring.

#### 1.4 Research Scope

With that in mind, this thesis explores the field of asynchronous simulation of morphologically detailed neural networks. Our objective is to investigate the efficient simulation of large networks of highly-heterogeneous neuron models characterized by diverse activity dynamics, executed on a network of compute nodes with a wide range of hardware specifications.

We will show that asynchronous runtime systems with distributed memory addressing is not only very suitable, but *very likely* the only solution able to handle the high complexity in such resolution.

Our methods provide novel insights on the development of neuron simulators targeting efficient executions of complex neuron models on heterogeneous distributed compute architectures. The extent of the contributions presented covers from micro-parallelism methods focused on individual neuron models, to the dynamics of medium- and large-sized networks of neurons. The range of analysis in this thesis includes multi-core and SIMD accelerations, cache-efficiency, network communication, numerical accuracy, computation flows from numerical resolution, network activity, applications to biological use cases, and reduction of overall time to solution.

The capabilities of our methods are demonstrated on a prototype implementation developed on the core compute kernel of the NEURON scientific application, yielding a fullyasynchronous distributed and parallel simulation of neuron networks. Asynchronicity capabilities are provided by the HPX-5 runtime system (Sterling et al., 2014) for the ParalleX execution model (Kaiser et al., 2009) on a global address memory space with transactional memory capabilities (Kulkarni et al., 2016). We provide implementation details, drawbacks and a comparison to the BSP counterpart based on MPI and OpenMP. The flexibility in the distributed, multi-core and vector parallelism methods presented is shown to fully utilise all computing resources across a wide spectrum of host architectures, when enough computation is available. To provide substantial evidence of our results, comparisons are provided on four heterogeneous compute architectures: Intel Xeon 6140, Intel Knights Landing, Intel E5 and Cray XE6. Performance on distributed executions are demonstrated on a network of Cray XE6 nodes.

Our work addresses several limitations and advances state-of-the-art methods for large scale neuron simulations and asynchronous computation. Nevertheless, most of the methods introduced follow from first principles of numerical simulation and computer science, thus being applicable to a wide range of scientific problems.

#### 1.5 Runtime Systems

A runtime system is a collection of components described as software (binaries, operative system, libraries), hardware, or both, that allows for an application to run on a system. The

runtime describes the set of instructions that run throughout the execution of the application. This includes user-introduced code (the application per se) and the instructions that were not written but are required for the proper execution of the program. Examples of runtime systems methods include communication, network bootstrapping, processor interfacing (threading control, atomic operations, etc.), hardware calls (IO and network), the hardware instructions set architecture (ISA), synchronization control methods (mutual exclusion objects, semaphores, atomic updates) and network operations (sending, receiving, querying and probing for messages), among others.

A wide collection of runtime systems is available nowadays with distinct features, with development of new components being actively pursued (Sterling et al., 2017). To name a few:

- GPU acceleration (Bueno et al., 2012), distributed asynchronous task-based parallelism (Bueno et al., 2011), hierarchical task-based programming (Planas et al., 2009) and self-adaptive tasks (Planas et al., 2013) in OmpSs (Duran et al., 2011);

- adaptive dynamic task scheduling to resources (Sterling & Zhang, 2018), message-drive computation (Brodowicz & Sterling, 2017), multi-level stack and hardware messaging (Autonomic Performance Environment on eXascale, APEX) (Huck et al., 2015), offload of computation to network cards (Anderson et al., 2017) in HPX-5 (Sterling et al., 2014);

- passive and active distributed global address space (Kulkarni & Lumsdaine, 2015) , and execution on embedded devices (van Wagensveld & Margull, 2017) in HPX-3 (Kaiser et al., 2014) and HPX-5; and

- automated mechanisms for data movement across compute nodes in Legion (Bauer et al., 2012).

In the context of our research, we will focus on the methods for asynchronism in Global Address Space (GAS). Asynchronism refers to the timing of compute, communication and synchronization operations across compute units not being synchronized, predetermined, or set at regular intervals. Instead, it is decided dynamically throughout the execution, typically when a previous operation is completed and the adequate hardware resource becomes available. A distributed memory space abstracts the addresses of physical memory (or memory page mapped by the Operative System) into an unique address representation across the whole network, managed by the runtime system. In practice, it allows unique data and functions addressing in the global address space across all physical compute nodes and distributed memory regions.

For brevity, we provide descriptions of two sample runtime systems, that will be utilized as the base of analysis in the following thesis: the synchronous MPI with no GAS, and the asynchronous HPX with GAS.

#### 1.5.1 MPI: Message Passing Interface

The Message Passing Interface (MPI) (Gropp et al., 1999) is a standard of a protocol that defines operations for communication, network control, Input/Output (IO), management of compute nodes on the network, among others, running a similar parallel process distributed across all compute nodes on a network. MPI is the dominant execution model used in high performance computing in current times (Sur et al., 2006).

The most common MPI-based execution workflow performs a synchronous computation of similar compute operations in distinct datasets stored across compute nodes, and exchanges data across nodes at predetermined collective communication steps. MPI works on a distributed memory environment, however data structures addressing is performed at the level of memory of individual nodes. Point-to-point messaging allows for selective messaging across pairs of nodes in the network. Selective broadcasts are possible on communication windows to a subset of the network. Other methods include collective and individual operations for input and output, network topology management, and one-way communication with get/put/accumulate methods on remote memory windows.

The MPI programming challenge is to properly load balance a distinct subset of input data across the network nodes, serialize and synchronize inter-node data exchange, and program the control of the execution flow of compute nodes, in order to avoid missed messages, incoherent data states, deadlocks, etc.

The newest MPI v3 (Forum, 2012) release provides non-blocking collective operations, inexistent in the previous version 2. These, alongside the point-to-point non-blocking routines in MPI v2, are sometimes also referred to as asynchronous communication routines, to refer an operation that can be performed without halting the execution on the initiator compute node, and without waiting for the destination processor to receive the message.

#### 1.5.2 HPX: High Performance ParalleX

The HPX-5 interface and runtime library (Sterling et al., 2014) is a realization of the ParalleX execution model for exascale execution (Cimini et al., 2011; Kulkarni et al., 2016; Kissel & Swany, 2016). It consists of lightweight threads and active message parcels, operating within the context of an active global address space, and synchronizing through lightweight local control objects (LCOs) such as futures or local reductions and distributed collectives that support dynamic and irregular participation.

The Global Address Space (GAS) is flat and byte addressable and supports block-based allocation through a *malloc/free* API. Blocks may be allocated locally or remotely, or as part of distributed arrays. Array distributions can be cyclic or user-defined. The mapping of blocks to physical compute nodes (henceforth also denominated as **localities**) can vary dynamically at runtime. Threads may access global data directly through local aliases, may access remote global data through an asynchronous memget/memput API, and/or may send parcels to global addresses.

Parcels contain immediate data, a specification of the action to perform, and continuation information such as "return to me" or "forward the computed value as an input to an LCO." When a parcel arrives at the locality associated with its target global address the HPX-5 runtime will invoke it as a new lightweight thread. The parcel-thread isomorphism and global address space are key to writing programs that work portably across shared memory, distributed memory, and hybrid architectures.

HPX-5 applications are written to be adaptive and data-driven. Parcels move computation to data while LCOs provide runtime-visible data and control dependent execution. Combined with the ability to remap global data, this design can minimize network traffic and allows a dynamic scheduler to map irregular computation onto the available resources.

#### 1.6 Reference Implementation

Our use case is the digital reconstruction of an *in vivo* laboratory experiment, applied to a previously published network of morphologically detailed neuron models (Markram et al., 2015).

The reference implementation follows the simulation workflow implemented in NEURON (Carnevale & Hines, 2006), categorized by the following properties: (1) neurons are branched representations of spatially-discretized capacitors with ionic current channels — hereinafter referred to as **compartments**; (2) neurons are represented by ODEs that define the current on the capacitor and the voltage-dependent opening of each ion channel or biological mechanism; and (3) ODEs are coupled with a time dependency, based on the synaptic connectivity between neurons. The mathematical formalism follows.

#### 1.6.1 Computational Model

The topology of a neuron is described by a tree of resistors, with capacitors and nonlinear resistive current flows at each node (compartment) connected to ground. The RC circuit that models the electrical current passing through the membrane of a compartment *n* is modelled by:

$$C\frac{dV_n}{dt} = -\sum_i g_i x_i (V_n - E_i) + I(t)$$

(1.1)

where  $g_i$  and  $E_i$  describe the conductance and reversal potential of the ionic channels, respectively. Synaptic currents or injected current stimuli, if any, are included in I(t). The term  $x_i$  models the opening probability of the transmembrane ion channel currents, typically described by a voltage-gated ODE. The RC circuit underlying the current passing through a compartment is illustrated in Figure 1.1 IV.

The original formulation of ionic activity was introduced by the Hodgkin-Huxley (HH) model, and includes the activity of the ion channel gating states that model the flux of sodium (index Na) and potassium (index K) currents. All remaining currents are included in the leak current (index L), leading to the formulation:

$$\sum_{i} g_{i} x_{i} (V_{n} - E_{i}) = g_{Na} m^{3} h (V_{n} - E_{Na}) + g_{K} n^{4} (V_{n} - E_{K}) + g_{L} (V_{n} - E_{L}).$$

(1.2)

For brevity, the equations of the voltage-dependent variables m, n and h describing the opening of the ion channels as first-order ODEs were omitted. Together with the current function in Equation 1.1, they describe the system of ODEs that describes the dynamics of a neuron defined by a single compartment, or a point neuron. A more detailed (extended) HH model includes a wider range of ion channels and currents such as Calcium. Refer to Channelpedia (Ranjan et al., 2011) for a collection of existing ion channel specifications.

The computational model does not describe capacitance, resistance and conductance as a total value but as a value per unit length instead, and adds the axial resistance of the neurites (between compartments) to the current expression in Equation 1.1, leading to an equation of the form:

$$C\Delta x \frac{dV}{dt} = -\sum_{i} g_{i} \Delta x (V - E_{i}) + I(t) \Delta x + \frac{V_{n+1} - V}{r_{n+1} \Delta x} - \frac{V - V_{n-1}}{r_{n-1} \Delta x}$$

(1.3)

where the subscripts n-1 and n+1 represent the indices of the previous and following compartments. The new contributions are provided by Ohm's Law and the neuronal cable theory (Niebur, 2008). The term r defines the axial resistance per unit length as a function of the diameter and the cytoplasmic resistivity. Dividing both sides of the equation by  $\Delta x$  leads to the final formulation:

$$C\frac{dV}{dt} = -\sum_{i} g_{i}(V - E_{i}) + I(t) + \frac{V_{n+1} - V}{r_{n+1}\Delta x^{2}} - \frac{V - V_{n-1}}{r_{n-1}\Delta x^{2}}.$$

(1.4)

We can simplify it using the definition of approximation  $(\lim_{x\to 0})$  of the second derivative using finite difference methods:

$$\frac{V_{n+1}-V}{r\Delta x^2} - \frac{V-V_{n-1}}{r\Delta x^2} = \frac{1}{r} \frac{V_{n+1}-2V+V_{n-1}}{\Delta x^2} \approx \frac{1}{r} \frac{d^2 V}{dx^2}.$$

(1.5)

We now replace Equation 1.4 with the value for the second derivative, leading to the final formulation:

$$C\frac{dV}{dt} = -\sum_{i} g_i (V - E_i) + I(t) + \frac{1}{r} \frac{d^2 V}{dx^2}.$$

(1.6)

#### 1.6.2 Spatial Discretization

As we cannot find an analytical solution on arbitrary neuron geometries/morphologies, we resort to discretization and numerical approximation as a way to make the problem tractable. Therefore, we perform a spatial discretization of the neuronal morphology — from biologically inspired to HH-based compartmental representation. Moreover, the model assumes the spatial discretization to be small enough, so that the second order correctness implies that the value at any spatial location is sufficiently close to the average value of the compartment, represented by the nodal value of the solution to the discretised problem.

Subsequently, it assumes the state of the axonic branches to be constant throughout the execution, therefore simulating only soma and dendrite sections. Thus, upon an action potential (known as a spike) of a neuron, the synaptic propagation delay between two neurons includes the current propagation from the soma (or axon initial segment) to the bouton in the axon, plus the time required for the electro-chemical reaction and neurotransmitter release at the synapse.

#### 1.6.3 Branching

A branched representation of a neuron allows for more details from the morphology, by adding the neighbouring compartments' contributions according to the neuronal cable theory for multiple compartments. Branched neuron trees include the terms defining the currents derived from the parent and children branches, extending Equation 1.3 to the final formulation:

$$C\frac{dV}{dt} = -\sum_{i} g_{i}(V - E_{i}) + I(t) + \frac{V_{p(n)} - V_{n}}{r_{p(n)} \Delta x^{2}} - \sum_{c: \ p(c)=n} \frac{V_{n} - V_{c}}{r_{c} \Delta x^{2}}$$

(1.7)

where  $p(c) : \mathbb{N} \to \mathbb{N}$  returns the index of the parent compartment of a given compartment *c* and  $r_c$  is the resistance of the connectivity to neighbouring compartments, if any. A parent compartment is the compartment immediately above on a sequence or tree structure. A converse logic holds for the definition of children compartments. Due to having no analytic solution, numerical methods are employed with a problem-optimized solver used for the resolution of the system of equations.

NEURON's algebraic solver (Hines, 1984) describes each neuron as a sparse-tridiagonal matrix that represents the voltage in a compartment as a function of the main diagonal of the matrix, the contributions from parents and children on the upper and lower diagonals respectively, and the mechanism contributions to the voltage on the right hand side of the matrix-vector multiplication. Following the compartment numbering convention used by NEURON (Hines et al., 2008), the tree of compartments is numbered using a depth-first search scheme from root to leaves, ensuring that the index of a parent compartment is larger than all its children and smaller than its parent. The aforementioned ordering rule guarantees that the matrix is symmetric and in each row i there exists a single non-zero element with columns index j

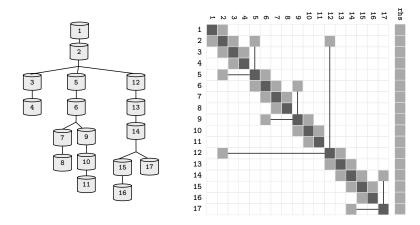

Figure 1.3 – The topological structure of a sample neuron, and its representative sparse tridiagonal dendritic tree representation. Lower and upper diagonals include parent and children contributions to the current function (*a* and *b* in Equation 1.8). Main diagonal (*d*) includes the changes to the compartment voltage dV/dt induced by the capacitance and mechanisms. Remaining terms are included in the right hand side (*rhs*) vector. Straight lines display connections between compartments with non-sequential indices (referenced by *p*).

such that j < i, i.e. a single parent compartment per branch. Upon the computation of all mechanism contributions, all compartments must solve:

$$b_{p(n)}V_{p(n)} + d_nV_n + \sum_{c: \ p(c)=n} a_cV_c = rhs_n$$

(1.8)

where  $d, a, b \in \mathbb{R}$  are the coefficients of the voltage contribution of the compartment n (as lower, upper and main diagonal respectively), its children and parent compartment, on a neuron with N compartments. For completeness, refer to Figure 1.3 for a sample neuron and its sparse tridiagonal matrix representation.

Given a tree with the aforementioned terms updated, the final solution of the system can be computed by a problem-specific implementation of the Gaussian Elimination, that only modifies the *d* and *rhs* vectors, as *a* and *b* are constant. Further details are provided later in Chapter 2, where branching structure is covered in detail.

#### 1.6.4 Fixed Step Interpolation

Fixed timestep interpolation is possible with either implicit Backward Euler or Crank-Nicholson methods. The gap between the analytic and numerically solved solution is particularly high when the system's voltage is changing rapidly, making the conditionally A-stable Forward Euler method particularly susceptible to oscillations and therefore not used (Carnevale & Hines, 2006). The Backward Euler method computes the solution of a set of nonlinear simultaneous equations at each step. To reduce the complexity and number of equations of the system at each timestep, NEURON uses staggered resolution, and offsets the calculation of gating

variables and compartment by half-step. Its numerical error is proportional to  $\Delta t$ , making it unable to deal *accurately* with discontinuities, in practice delivering events at the next timestep and yielding an error propagation with an average of  $\Delta t/2$  (Casalegno et al., 2016).

An alternative variant of Crank-Nicholson method applies Strang splitting to calculate the values of the compartment voltage and Hodgkin-Huxley gating states on interleaved time intervals, providing second-order accuracy (Carnevale & Hines, 2006). In practice, a direct solution of voltage equation using a linearized membrane current I(V, t) = g(V - E) at a timestep  $t \rightarrow t + \Delta t$  is possible if the conductance g and reversal potential E have second-order accuracy at time  $t + \Delta t/2$ . Since the conduction of HH-type channels is given by a function of state variables  $n(K^+)$ , m and  $h(Na^+)$ , this second-order accuracy at  $t + \Delta t/2$  is achieved by performing a calculation with a timestep offset of  $\Delta t/2$  from the current voltage timestep. Nevertheless, NEURON adopts Backward Euler as the default method, as Crank-Nicholson is not L-stable: its second-order accuracy yields high oscillations around solutions, particularly for events with infinitesimal small duration such as ideal current pulses and gap junctions.

Each fixed step iteration is defined by a fixed step size of length  $\Delta t$ , enough to capture the resolution of the fastest mechanism — typically the fast  $Na^+$  channels. The community-defined standard value for the fixed step size is  $25\mu s$ .

#### 1.6.5 Parallel Executions

Parallel executions require the synchronization of stepping across neurons in the simulation. The maximum time distance that a neuron can distance itself from a given pre-synaptic neuron is determined by the synaptic delay of the fastest synapse of the pair. The rationale is that in the event of a spike from a pre-synaptic neuron at time t, the state of the receiving post-synaptic neuron cannot have been resolved for a later time than  $t + t_{syn}$  — where  $t_{syn}$  is the synaptic delay between the pre- and the post-synaptic neuron — or the neuron will have *overstepped* and missed the interpolation instant. However, an alternative execution is possible with a *speculative* execution model. In practice, events delivered in past time instants are recovered by discarding the extra timesteps and *backstepping* the state of the neuron to the delivery time of the event. This topic will be covered in depth later in Chapter 5.

The event delay interval varies extensively across pairs of neurons. Therefore, the shortest propagation delay in a neural network that rounds down the multiple of the computation timestep is used as the collective synchronization and communication step size for the exchange of synapses to be delivered within the next interval. In our model, this is computed as 0.1 milliseconds, or equivalently four computation timesteps. An illustration of this synchronization protocol is illustrated in diagram a) in Figure 1.2.

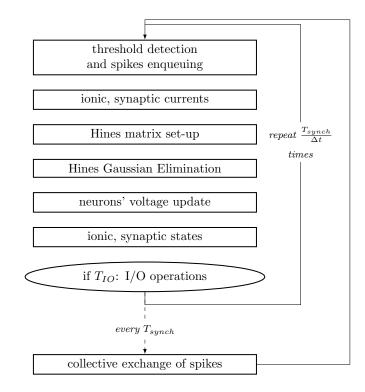

Figure 1.4 – Workflow of a compute step of the numerical resolution of a detailed neuron interpolation, based on interleaved voltage-states resolution.  $T_{synch}$  and  $T_{IO}$  are the communication and IO step intervals, respectively. Simulations on single compute nodes exclude the step for collective exchange of spikes.

### 1.6.6 Workflow