This is an open access article published under a Creative Commons Attribution (CC-BY) License, which permits unrestricted use, distribution and reproduction in any medium, provided the author and source are cited.

# Gate-Tunable Tunneling Transistor Based on a Thin Black Phosphorus-SnSe<sub>2</sub> Heterostructure

Junhong Na,\*<sup>,†,§</sup><sup>®</sup> Youngwook Kim,<sup>†</sup> Jurgen H. Smet,<sup>†</sup><sup>®</sup> Marko Burghard,<sup>†</sup> and Klaus Kern<sup>†,‡</sup>

<sup>†</sup>Max Planck Institute for Solid State Research, Heisenbergstrasse 1, D-70569 Stuttgart, Germany

<sup>‡</sup>Institut de Physique, École Polytechnique Fédérale de Lausanne, CH-1015 Lausanne, Switzerland

<sup>§</sup>Department of Energy Science, Sungkyunkwan University, 16419 Suwon, Republic of Korea

Supporting Information

ABSTRACT: Tunneling field-effect transistors (TFETs) are of considerable interest owing to their capability of low-power operation. Here, we demonstrate a novel type of TFET which is composed of a thin black phosphorus-tin diselenide (BP- $SnSe_2$ ) heterostructure. This combination of 2D semiconductor thin sheets enables device operation either as an Esaki diode featuring negative differential resistance (NDR) in the negative gate voltage regime or as a backward diode in the positive gate bias regime. Such tuning possibility is imparted by the fact that only the carrier concentration in the BP component can be effectively modulated by electrostatic

gating, while the relatively high carrier concentration in the SnSe<sub>2</sub> sheet renders it insensitive against gating. Scanning photocurrent microscopy maps indicate the presence of a staggered (type II) band alignment at the heterojunction. The temperature-dependent NDR behavior of the devices is explainable by an additional series resistance contribution from the individual BP and SnSe<sub>2</sub> sheets connected in series. Moreover, the backward rectification behavior can be consistently described by the thermionic emission theory, pointing toward the gating-induced formation of a potential barrier at the heterojunction. It furthermore turned out that for effective Esaki diode operation, care has to be taken to avoid the formation of positive charges trapped in the alumina passivation layer.

KEYWORDS: negative differential resistance, tunneling transistor, black phosphorus, tin diselenide, 2D van der Waals heterostructure

## INTRODUCTION

Modern electronic applications require integrated circuits of substantially reduced dynamic and static power consumption. However, the ultimate device scaling of conventional metaloxide field-effect transistors faces its limits. As an alternative, tunneling field-effect transistors (TFETs) are receiving increasing attention in particular because of their potential low-power operation.<sup>1-3</sup> Recent research on TFETs has focused on p-n homo- and heterojunctions based on Si, Ge, and III-V materials.<sup>4-8</sup> In general, the device performance of heterojunction-based TFETs has been proven to be superior to that of homojunction-based TFETs, as the former typically exhibits a steep band edge at the junction and furthermore allows selecting high mobility channel materials.<sup>1,9</sup> However, further progress along this direction is slowed down by the significant lattice mismatch that often occurs in heterojunctions.

Promising candidates for overcoming the lattice mismatch problem are two-dimensional (2D) van der Waals (vdW) materials which lack dangling bonds on their surface.<sup>10–12</sup> In addition, the great diversity of available 2D vdW materials enables efficient tailoring of the device properties of TFETs.<sup>13</sup> However, the realization of high-performance TFETs is still challenging due to the low current density and device stability as limiting factors in particular for vertical TFETs.<sup>14</sup> Another relevant goal is to achieve an efficient and reliable gate-tuning capability of the devices. To this end, a promising device component is the 2D vdW material black phosphorus (BP) which features a high carrier mobility in comparison to most transition-metal dichalcogenides such as MoS<sub>2</sub>.<sup>15-19</sup> One suitable counterpart to BP is the 2D vdW semiconductor tin diselenide (SnSe<sub>2</sub>), which displays a relatively high electron affinity as one of the prerequisites for high device performance of TFETs.<sup>20-24</sup> In both its bulk and few-layer forms, SnSe<sub>2</sub> is (unintentionally) highly n-doped, thereby rendering it difficult to deplete charge carriers by electrostatic gating.<sup>20,25,26</sup> By contrast, BP is only slightly p-doped, such that its carriers can be readily tuned by electrostatic gating and/or dielectric passivation in case of the few-layer form.<sup>17,27,28</sup> Thus far, BP-SnSe<sub>2</sub> heterostructure diodes displaying negative differential resistance (NDR) behavior have only been realized in the bulk form.<sup>29</sup>

Received: February 11, 2019 Accepted: May 21, 2019 Published: May 30, 2019

## **ACS Applied Materials & Interfaces**

Here, we demonstrate that stacking of a gate-tunable thin BP sheet onto a thin SnSe<sub>2</sub> sheet of high carrier density provides access to vertical TFETs whose operation can be tuned via electrostatic gating between a NDR and a backward diode mode, which at the same time exhibit a NDR peak current of unprecedented magnitude. Furthermore, by combining temperature-dependent charge transport experiments with scanning photocurrent microscopy (SPCM), we are able to unravel the presence of a gate-tunable type II staggered band alignment at the BP–SnSe<sub>2</sub> heterojunction.

## RESULTS AND DISCUSSION

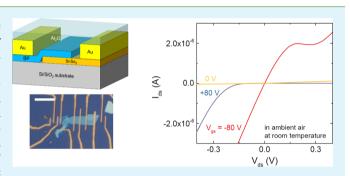

In Figure 1a, three subsequent stages of device fabrication are shown, starting with a mechanically exfoliated SnSe<sub>2</sub> sheet (top

**Figure 1.** (a) Optical images showing the fabrication of a heterostructure device, starting from a thin  $SnSe_2$  sheet (top), followed by deterministic transfer of a thin BP sheet on top (middle), then defining electrodes by e-beam lithography and metal evaporation, and finally deposition of an alumina layer by ALD (bottom). The scale bar is 10  $\mu$ m. (b) Schematic illustration of a finished thin BP-SnSe<sub>2</sub> heterostructure device. (c) Output characteristics of the device at  $V_{gs} = -80$ , 0, and +80 V, recorded under ambient conditions.

panel), the same SnSe<sub>2</sub> sheet after deterministic transfer of a BP sheet on top (middle panel), and the final BP-SnSe<sub>2</sub> heterostructure device with metal electrodes and a Al<sub>2</sub>O<sub>3</sub> passivation deposited on top (bottom panel). The passivation layer is needed to preserve the original structure and electronic properties of the BP and SnSe<sub>2</sub> sheets, as both slowly degrade in ambient air.<sup>28,30</sup> In general, the exposure of the BP and SnSe<sub>2</sub> sheets to ambient air was limited to several minutes before final device passivation. As determined by atomic force microscopy (AFM), the thickness of the BP and  $SnSe_2$  sheet is ~8.5 and ~12 nm, respectively (Figure S1). Details of the device fabrication process are provided in the Methods section. The BP-SnSe<sub>2</sub> heterostructure device is schematically illustrated in Figure 1b. The corresponding output curves recorded under ambient conditions at different gate voltages (-80, 0, and +80 V), shown in Figure 1c, signify a global back-gating effect on the device. The output curve at  $V_{gs} = -80$  V (red line) clearly features NDR, which is indicative of band-to-band tunneling. In comparison, application of the opposite gate bias ( $V_{gs} = +80$  V) resulted in a strongly different behavior, which is characteristic of a backward diode (blue line). More  $I_{ds}-V_{ds}$  and  $I_{ds}-V_{gs}$  data at different gate voltages and drain-source voltages are offered in the Supporting

Information. Hysteresis induced by charge trapping/detrapping at the trap sites between the heterostructure and gate oxide are observed in Figure S2, but this could not affect the main result associated with the heterojunction.

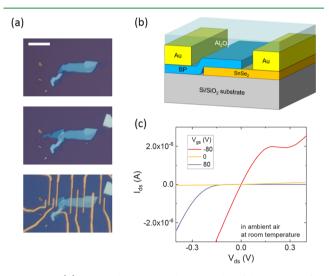

To determine the type of band alignment at the BP-SnSe<sub>2</sub> heterojunction, we used SPCM. This technique involves raster scanning of the sample through a confocal laser spot, while the photocurrent is recorded as a function of illumination position.<sup>31</sup> In Figure 2a, three SPCM maps of the device in Figure 1, obtained using different gate voltages, are displayed. At zero drain-source and gate voltage (middle panel of Figure 2a), a negative photocurrent of approximately -17 nA is observed near the BP-SnSe<sub>2</sub> heterojunction, pointing toward an energy band bending of type II (staggered), as shown in the corresponding diagram of Figure 2b. The formation of a tunneling barrier between the two types of layers (represented by the two vertical black lines) is most likely due to native oxide layers and/or organic residues from the mechanical transfer process. That the band alignment is indeed of type II (staggered) rather than type III (broken-gap) and is further supported by the negative photocurrent observed at zero bias in the output curves (plot in the middle of Figure 2c). By contrast, in close correspondence to a previous report on a bulk BP-SnSe<sub>2</sub> heterojunction,<sup>29</sup> we observed NDR behavior and positive photocurrent for a bulk BP-SnSe<sub>2</sub> heterojunction device, implying type III (broken-gap) band alignment in this case (see the Supporting Information for further details). First of all, this difference between the bulk and few-layer heterostructure likely originates from a thickness-dependent carrier density of BP, that is, a decreased doping concentration with decreasing BP thickness.<sup>32</sup> In the device comprising bulk BP, while the high carrier concentration principally favors the TFET operation, the resulting poor gate controllability is a significant drawback. Another plausible explanation of the difference between the bulk and few-layer heterostructure is possible fixed charges in the tunneling barrier. Note that in a III-V heterostructure the band alignment change induced by the fixed charges at the heterojunction has been reported.33

Owing to the weak p-type doping of the thin BP sheet, the SPCM response is influenced by the applied back-gate voltage, as apparent from the photocurrent maps at the top and bottom of Figure 2a. Under zero drain-source voltage and application of  $V_{gs} = -40$  V (top map), an increased negative photocurrent emerges near the heterojunction in the SPCM map. Such behavior indicates an upward energy band bending of the BP induced by the highly p-doped BP channel, as illustrated by the top diagram in Figure 2b. Under this condition, NDR behavior is observed in the forward bias regime of the output curve (top panel of Figure 2c). That only the BP channel part is tunable by the gate is confirmed by the observation that the heavily n-doped SnSe<sub>2</sub> channel, in contrast to the BP, cannot be turned off by the gate voltage (see Figure S4 in the Supporting Information). The electron concentration in the SnSe<sub>2</sub> sheet can be estimated from the simple equation,  $n = \sigma/(\mu q)$ , where *n*,  $\sigma$ ,  $\mu$ , and *q* are carrier concentration, conductivity, carrier mobility, and electronic charge, respectively. Thus, using the field-effect mobility in the SnSe<sub>2</sub> sheet extracted from the transfer curve, as described in the Supporting Information, an electron concentration on the order of  $10^{13}$  cm<sup>-2</sup> is obtained at zero gate voltage. Such high electron concentration is indeed expected to hinder effective gating. Correspondingly, when a positive gate bias of  $V_{gs}$  = +40 V is applied, a strong positive photocurrent at the heterojunction appears (see bottom panel of Figure 2a), which is consistent

**Figure 2.** (a) SPCM maps of the BP–SnSe<sub>2</sub> heterostructure device in Figure 1, acquired at room temperature with  $\lambda = 514$  nm. The maps were recorded at  $V_{ds} = 0$  V and  $V_{gs} = -40$  (top), 0 (middle), and +40 V (bottom). In each case, the corresponding optical image of the device is overlaid. The blue and yellow dotted lines mark the contours of the BP and SnSe<sub>2</sub> sheet, while "D" and "S" denote the drain and source electrode, respectively. The size of each SPCM map is  $7 \mu m \times 7 \mu m$ . (b) Band diagrams corresponding to the gating conditions in panel (a). (c) Measured output characteristics at high negative gate voltage (top), zero gate voltage (middle), and high positive gate voltage (bottom).  $E_f$  denotes the Fermi level position. For the zero gate voltage case (middle plot),  $I_{ds}$ – $V_{ds}$  curves were acquired in the dark and under illumination with different laser powers of 4.2, 16.9, 67.7, and 142  $\mu$ W, respectively.

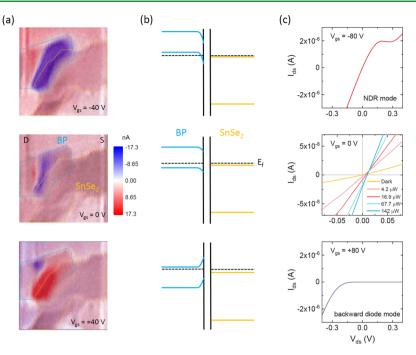

**Figure 3.** Temperature-dependent characteristics of the BP–SnSe<sub>2</sub> heterostructure device. (a)  $I_{ds}-V_{ds}$  curves at  $V_{gs} = -80$  V, recorded at various temperatures between 283 and 10 K. (b) Peak/valley voltages and PVCR as a function of temperature, as extracted from the NDR features in panel (a). (c) Two-probe resistances of the BP ( $R_{BP}$ ) and SnSe<sub>2</sub> ( $R_{SnSe_2}$ ) sheets and their sum ( $R_{BP} + R_{SnSe_2}$ ) as a function of temperature. The inset shows a simplified equivalent circuit of the device, comprising  $R_{BP}$ ,  $R_{SnSe_2}$ , and a resistance at the BP–SnSe<sub>2</sub> junction ( $R_{junction}$ ). (d)  $I_{ds}-V_{ds}$  curves at  $V_{gs} = +80$  V for various temperatures between 283 and 10 K [analogous to panel (a)]. (e) Arrhenius plots of  $\ln(I_{ds}/T^{3/2})$  vs 1000/*T*, at  $V_{gs} = +80$  V and in the negative bias regime ( $V_{ds} = -0.1, -0.2,$  and -0.3 V). The straight lines represent linear fits. (f) Extracted Schottky barrier heights for the BP–SnSe<sub>2</sub> heterostructure device in the negative bias regime and the BP device, both as a function of gate voltage.

with the resulting downward band bending in the BP channel, as depicted in the bottom diagram in Figure 2b. Under this condition, a conventional Schottky barrier is formed near the heterojunction, which in turn is responsible for the backward diode behavior (bottom plot of Figure 2c).

To evaluate the mechanism of charge transport across the BP–SnSe<sub>2</sub> p–n heterojunction, we performed temperaturedependent electrical measurements at high negative and positive gate voltages. The behavior in the NDR regime at  $V_{\rm gs} = -80$  V is shown in Figure 3a for the temperature range between 10 and

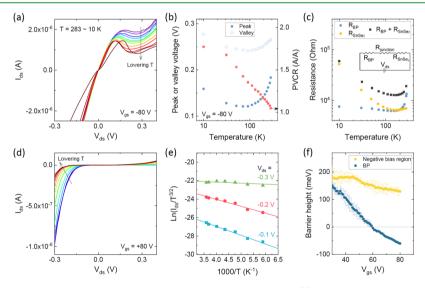

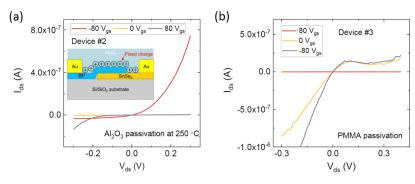

**Figure 4.** Effect of the nature of the passivation layer in the BP–SnSe<sub>2</sub> heterostructure devices. Output characteristics for the case of (a) an  $Al_2O_3$  passivation layer deposited at 250 °C and (b) a PMMA passivation layer, in both cases for  $V_{gs} = -80$ , 0, and +80 V, respectively. The inset in panel (a) shows a schematic diagram of the device, with fixed charges in the  $Al_2O_3$  passivation layer.

283 K. It is apparent that the peak current decreases upon cooling, which is unexpected at first sight because of the reduced tail of the Fermi–Dirac distribution function.<sup>29,34</sup> This temperature dependence of the peak current may be explained by a sizable excess current associated with a two-step process involving Shockley–Read–Hall (SRH) generation/recombination and trap-assisted tunneling.<sup>35,36</sup> It is noteworthy that for other materials such a decrease has been attributed to an increase of the energy band gap with decreasing temperature.<sup>37,38</sup> However, the present BP displays an anomalous temperature dependence of the band gap,<sup>39</sup> thus favoring the aforementioned alternative explanation.

The corresponding peak and valley voltages, along with the peak-to-valley current ratio (PVCR), are plotted in Figure 3b as a function of temperature. One plausible explanation for the observed overall trend of the peak and valley voltage positions is the contribution of a series resistance comprising an intrinsic and a contact-related component for each of the two sheets. To test this hypothesis, we measured the individual sheets' twoprobe resistance with the aid of additional electrodes as shown at the bottom of Figure 1a (see the Supporting Information for more details). In Figure 3c, thus obtained temperaturedependent resistances (blue and yellow data points, respectively) are plotted together with their sum (black data points) at  $V_{gs} = -80$  V. Based on the equivalent circuit in the inset of Figure 3c and assumption that the resistance of the heterojunction  $(R_{\text{iunction}})$  is insensitive to temperature at low drain-source bias (because the carrier injection is mostly the band-to-band tunneling process), the temperature dependence of the effective voltage drop across the heterojunction should be dominated by the temperature dependence of the series resistance. The decrease of both peak and valley voltages upon cooling from 300 to  $\sim 100$  K, as observed in Figure 3b, can then be attributed to the decrease of the series resistance within this temperature range. The subsequent increase of the peak/valley voltage upon further cooling below ~100 K is consistent with the increase of the series resistance in this range. Likewise, the increase of PVCR with decreasing temperature, reaching ~1.75 at 10 K (Figure 3b), can be related to the reduced excess current at lower temperatures. In general, the relatively small PVCR magnitude indicates considerable excess current, similar to other tunneling devices.<sup>37,40</sup> It may be possible to reduce the latter through mechanical transfer of the sheets under inert atmosphere, to ensure a cleaner interface.

For the backward diode operation regime at  $V_{gs}$  = +80 V, the temperature-dependent  $I_{ds}$ - $V_{ds}$  curves are shown in Figure 3d. The current decrease in the negative bias regime upon cooling

should be, according the bottom band diagram in Figure 2b, attributable to the forward bias regime of a Schottky diode. To confirm this assumption, we analyzed the data in the framework of classical thermionic emission theory (see the Supporting Information).<sup>41,42</sup> The Arrhenius plots of  $\ln(I_{ds}/T^{3/2})$  as a function of  $T^{-1}$ , shown in Figure 3e, are linear for the three drain-source voltages of -0.1, -0.2, and -0.3 V. The extracted Schottky barrier height is plotted as a function of gate voltage in Figure 3f, along with the value for the individual BP sheet. The Schottky barrier height determined for the heterostructure is positive over the entire gate voltage regime, with a reasonable value on the order of 150 meV. This observation confirms the validity of the thermionic emission theory for the heterojunction in the negative bias regime. On the other hand, the appearance of a negative Schottky barrier height for the BP device above  $V_{gs}$  = +60 V shows that the thermionic emission theory is invalid in the high gate voltage regime.<sup>42</sup>

A major parameter governing the device performance of TFETs is the subthreshold slope (SS). A comparison between the SS of the present devices and values previously reported for other 2D material-based TFETs can be found in Table S1, which includes also further device parameters. Although in the hole regime, the SS of the present heterostructure devices falls below that of the BP-only device (see Figure S8), it remains above ~4000 mV/dec. These relatively large values can be attributed to the thick gate insulator (300 nm  $SiO_2$ ), along with a sizable trap density at the interface between the 2D sheets and gate insulator, which determine the SS according to the equation SS =  $(1 + C_{it}/C_{ox}) \times k \times T/q \times \ln 10$ , where  $C_{it}$ ,  $C_{ox}$ , k, T, and q are the interface trap capacitance, gate oxide capacitance, Boltzmann constant, temperature, and electronic charge, respectively. One option to further decrease the SS would be to implement an ultrathin, high- $\kappa$  gate insulator with a high quality interface to the 2D sheets.

As a further observation of practical relevance, because of the small thickness of the BP and SnSe<sub>2</sub> sheets, the electrical behavior of the heterostructure devices is influenced by the nature of the passivation layer. Figure 4a shows gate-dependent  $I_{ds}-V_{ds}$  curves of another BP–SnSe<sub>2</sub> heterostructure (device #2, see the Supporting Information for details), whose Al<sub>2</sub>O<sub>3</sub> passivation layer was grown at the higher temperature of 250 °C. In contrast to the above described device (Figure 1) with the Al<sub>2</sub>O<sub>3</sub> passivation layer grown at 100 °C, no NDR behavior is observed in the present device, as apparent from Figure 4a. The Ohmic-like  $I_{ds}-V_{ds}$  curves, that are obtained by separate measurements on the BP and SnSe<sub>2</sub> sheets (see the Supporting Information), indicate that the non-Ohmic behavior detected

## **ACS Applied Materials & Interfaces**

for the heterostructure arises due to the heterojunction. One possible reason for the absence of NDR is that positive fixed charges induced by oxygen vacancies in the  $Al_2O_3$  layer (as depicted in the figure inset) hinder back gating, especially close to the heterojunction. In fact, it has been documented that sizeable oxygen vacancy densities can be induced with increasing growth temperature of the  $Al_2O_3$  layer, which could in turn result in a larger density of fixed positive charge.<sup>43,44</sup> In comparison, when a PMMA layer is used for passivation, NDR behavior is again observed in the negative gate voltage regime (see Figure 4b), like for the device with the  $Al_2O_3$  layer grown at 100 °C. This finding is in accord with the absence of fixed surface charges on PMMA, underlining the importance of properly choosing the passivation layer and its fabrication conditions.

#### CONCLUSIONS

In summary, we have successfully fabricated thin BP-SnSe<sub>2</sub> pn heterostructure devices whose operation mode is tunable by electrostatic gating between the NDR and backward diode regime. This tuning is enabled by the fact that application of a global back-gate predominantly affects the thin BP sheet because if its lower charge carrier density in comparison to the SnSe<sub>2</sub> sheets. Based on spatially resolved photocurrent data, we conclude that the band alignment at the heterojunction is of type II staggered. Furthermore, temperature-dependent electrical measurements on the devices revealed that the charge transport across the heterojunction occurs via a two-step process involving SRH generation/recombination and trap-assisted tunneling in the high negative gate voltage regime, and via thermionic emission in the high positive gate voltage regime. In addition, growth of the required Al<sub>2</sub>O<sub>3</sub> passivation layer at elevated temperature was found to suppress the NDR behavior, presumably because of fixed positive charges introduced at the interface. Taken together, our observations provide several clues for the further improvement of 2D vdW material-based tunneling devices.

## METHODS

The thin  $SnSe_2$  and BP sheets were mechanically exfoliated from bulk crystals by the Scotch tape method onto n<sup>+</sup>-doped silicon substrates deposited with a thermally grown, 300 nm thick SiO<sub>2</sub> layer and onto PDMS-based gel (Gel-Pak), respectively.<sup>45</sup> A carefully selected BP sheet on the PDMS-based gel was transferred by a deterministic transfer method onto the  $SnSe_2$  sheet on the Si/SiO<sub>2</sub> substrate. Contact electrodes were patterned by standard e-beam lithography, followed by an in situ Ar plasma treatment, thermal evaporation of the Ti/Au (2 nm/70 nm), and lift-off process. Atomic layer deposition (ALD) (Cambridge Nanotech ALD system) was performed with Al(CH<sub>3</sub>)<sub>3</sub> and H<sub>2</sub>O as precursors at 100 or 250 °C and a base pressure of 10 mTorr, to obtain a 20 nm thick Al<sub>2</sub>O<sub>3</sub> passivation layer. Alternatively, a 200 nm thick PMMA bilayer was spin-coated on the heterostructure.

AFM was used to determine the thickness of the sheets. The electrical transport and photocurrent measurements in Figures 1, 2, and 4 were carried out under ambient conditions. The temperature-dependent charge transport experiments were performed inside an Oxford cryostat. All of the electrical measurements were performed in dc configuration using two Keithley 2400 source meters and a Keithley 2000 multimeter. A confocal microscope (Leica TCS SP2, 50× objective lens with NA = 0.8) was used for the SPCM experiments, in which the samples were raster-scanned (lateral step size of ~100 nm) through the approximately 500 nm wide laser spot (linearly polarized light with  $\lambda = 514$  nm).

## ASSOCIATED CONTENT

#### **Supporting Information**

The Supporting Information is available free of charge on the ACS Publications website at DOI: 10.1021/acsami.9b02589.

Thickness information of the BP–SnSe<sub>2</sub> heterostructure, double-sweep output and transfer characteristics, electrical properties of the individual BP and SnSe<sub>2</sub> devices, and so forth (PDF)

#### AUTHOR INFORMATION

#### **Corresponding Author**

\*E-mail: j.na@fkf.mpg.de.

#### **ORCID**

Junhong Na: 0000-0002-5314-2868

Jurgen H. Smet: 0000-0002-4719-8873

#### Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

This research was supported by National Research Foundation of Korea (NRF-2014R1A6A3A03058936, NRF-2018R1D1A1B07050608). Moreover, J.N. and Y.K. acknowledge the support by the Alexander von Humboldt foundation. J.H.S. is grateful for the financial support from the graphene flagship.

#### REFERENCES

(1) Ionescu, A. M.; Riel, H. Tunnel Field-Effect Transistors as Energy-Efficient Electronic Switches. *Nature* **2011**, *479*, 329–337.

(2) Esseni, D.; Marco, P.; Pierpaolo, P.; Cem, A.; Tommaso, R. A Review of Selected Topics in Physics Based Modeling for Tunnel Field-Effect Transistors. *Semicond. Sci. Technol.* **2017**, *32*, 083005.

(3) Seabaugh, A. C.; Zhang, Q. Low-Voltage Tunnel Transistors for Beyond CMOS Logic. *Proc. IEEE* **2010**, *98*, 2095–2110.

(4) Moselund, K. E.; Ghoneim, H.; Bjork, M. T.; Schmid, H.; Karg, S.; Lortscher, E.; Riess, W.; Riel, H. In Comparison of VLS Grown Si NW Tunnel FETs with Different Gate Stacks. 2009 Proceedings of the European Solid State Device Research Conference, 14–18 Sep, 2009; pp 448–451.

(5) Mayer, F.; Royer, C. L.; Damlencourt, J.; Romanjek, K.; Andrieu, F.; Tabone, C.; Previtali, B.; Deleonibus, S. Impact of SOI, Si<sub>1-X</sub>Ge<sub>x</sub>OI and GeOI Substrates on CMOS Compatible Tunnel FET Performance. 2008 IEEE International Electron Devices Meeting, 15–17 Dec, 2008; pp 1–5.

(6) Krishnamohan, T.; Kim, D.; Raghunathan, S.; Saraswat, K. Double-Gate Strained-Ge Heterostructure Tunneling FET (TFET) with Record High Drive Currents and  $\ll 60 \text{mV/dec}$  Subthreshold Slope. 2008 IEEE International Electron Devices Meeting, 15–17 Dec, 2008; pp 1–3.

(7) Convertino, C.; Zota, C. B.; Schmid, H.; Ionescu, A. M.; Moselund, K. E. III-V heterostructure tunnel field-effect transistor. *J. Phys.: Condens. Matter* **2018**, *30*, 264005.

(8) Lu, H.; Seabaugh, A. Tunnel Field-Effect Transistors: State-of-the-Art. *IEEE J. Electron Devices Soc.* **2014**, *2*, 44–49.

(9) Wang, L.; Yu, E.; Taur, Y.; Asbeck, P. Design of Tunneling Field-Effect Transistors Based on Staggered Heterojunctions for Ultralow-Power Applications. *IEEE Electron Device Lett.* **2010**, *31*, 431–433.

(10) Britnell, L.; Ribeiro, R. M.; Eckmann, A.; Jalil, R.; Belle, B. D.; Mishchenko, A.; Kim, Y. J.; Gorbachev, R. V.; Georgiou, T.; Morozov, S. V.; Grigorenko, A. N.; Geim, A. K.; Casiraghi, C.; Neto, A. H. C.; Novoselov, K. S. Strong Light-Matter Interactions in Heterostructures of Atomically Thin Films. *Science* **2013**, *340*, 1311–1314.

(11) Gong, C.; Zhang, H.; Wang, W.; Colombo, L.; Wallace, R. M.; Cho, K. Band Alignment of Two-Dimensional Transition Metal

### **ACS Applied Materials & Interfaces**

Dichalcogenides: Application in Tunnel Field Effect Transistors. *Appl. Phys. Lett.* **2013**, *103*, 053513.

(12) Britnell, L.; Gorbachev, R. V.; Jalil, R.; Belle, B. D.; Schedin, F.; Mishchenko, A.; Georgiou, T.; Katsnelson, M. I.; Eaves, L.; Morozov, S. V.; Peres, N. M. R.; Leist, J.; Geim, A. K.; Novoselov, K. S.; Ponomarenko, L. A. Field-Effect Tunneling Transistor Based on Vertical Graphene Heterostructures. *Science* **2012**, 335, 947–950.

(13) Jena, D. Tunneling Transistors Based on Graphene and 2-D Crystals. *Proc. IEEE* 2013, 101, 1585–1602.

(14) Lv, Y.; Qin, W.; Wang, C.; Liao, L.; Liu, X. Recent Advances in Low-Dimensional Heterojunction-Based Tunnel Field Effect Transistors. *Adv. Electron. Mater.* **2019**, *5*, 1800569.

(15) Szabo, A.; Rhyner, R.; Carrillo-Nunez, H.; Luisier, M. Phonon-Limited Performance of Single-Layer, Single-Gate Black Phosphorus nand p-Type Field-Effect Transistors. 2015 IEEE International Electron Devices Meeting (IEDM), 7–9 Dec, 2015; pp 12.1.1–12.1.4.

(16) Kim, S.; Konar, A.; Hwang, W. S.; Lee, J. H.; Lee, J.; Yang, J.; Jung, C.; Kim, H.; Yoo, J. B.; Choi, J. Y.; Jin, Y. W.; Lee, S. Y.; Jena, D.; Choi, W.; Kim, K. High-Mobility and Low-Power Thin-Film Transistors Based on Multilayer MoS<sub>2</sub> Crystals. *Nat. Commun.* **2012**, *3*, 1011.

(17) Li, L.; Yu, Y.; Ye, G. J.; Ge, Q.; Ou, X.; Wu, H.; Feng, D.; Chen, X. H.; Zhang, Y. Black Phosphorus Field-Effect Transistors. *Nat. Nanotechnol.* **2014**, *9*, 372–377.

(18) Narita, S.; Akahama, Y.; Tsukiyama, Y.; Muro, K.; Mori, S.; Endo, S.; Taniguchi, M.; Seki, M.; Suga, S.; Mikuni, A.; Kanzaki, H. Electrical and Optical Properties of Black Phosphorus Single Crystals. *Physica B* +*C* **1983**, *117–118*, 422–424.

(19) Fivaz, R.; Mooser, E. Mobility of Charge Carriers in Semiconducting Layer Structures. *Phys. Rev.* **1967**, *163*, 743–755.

(20) Evans, B. L.; Hazelwood, R. A. Optical and electrical properties of SnSe2. J. Phys. D: Appl. Phys. **1969**, 2, 1507.

(21) Zhang, Q.; Li, M.; Lochocki, E. B.; Vishwanath, S.; Liu, X.; Yan, R.; Lien, H.-H.; Dobrowolska, M.; Furdyna, J.; Shen, K. M.; Cheng, G.; Hight Walker, A. R.; Gundlach, D. J.; Xing, H. G.; Nguyen, N. V. Band offset and electron affinity of MBE-grown SnSe2. *Appl. Phys. Lett.* **2018**, *112*, 042108.

(22) Xue, H.; Dai, Y.; Kim, W.; Wang, Y.; Bai, X.; Qi, M.; Halonen, K.; Lipsanen, H.; Sun, Z. High photoresponsivity and broadband photodetection with a band-engineered WSe2/SnSe2 heterostructure. *Nanoscale* **2019**, *11*, 3240–3247.

(23) Murali, K.; Dandu, M.; Das, S.; Majumdar, K. Gate-Tunable WSe2/SnSe2 Backward Diode with Ultrahigh-Reverse Rectification Ratio. *ACS Appl. Mater. Interfaces* **2018**, *10*, 5657–5664.

(24) Zhou, X.; Zhou, N.; Li, C.; Song, H.; Zhang, Q.; Hu, X.; Gan, L.; Li, H.; Lü, J.; Luo, J.; Xiong, J.; Zhai, T. Vertical heterostructures based on SnSe2/MoS2 for high performance photodetectors. *2D Mater.* **2017**, *4*, 025048.

(25) Pei, T.; Bao, L.; Wang, G.; Ma, R.; Yang, H.; Li, J.; Gu, C.; Pantelides, S.; Du, S.; Gao, H.-j. Few-layer SnSe2 transistors with high on/off ratios. *Appl. Phys. Lett.* **2016**, *108*, 053506.

(26) Su, Y.; Ebrish, M. A.; Olson, E. J.; Koester, S. J. SnSe2 field-effect transistors with high drive current. *Appl. Phys. Lett.* **2013**, *103*, 263104.

(27) Morita, A. Semiconducting Black Phosphorus. Appl. Phys. A: Solids Surf. 1986, 39, 227–242.

(28) Na, J.; Lee, Y. T.; Lim, J. A.; Hwang, D. K.; Kim, G.-T.; Choi, W. K.; Song, Y.-W. Few-Layer Black Phosphorus Field-Effect Transistors with Reduced Current Fluctuation. *ACS Nano* **2014**, *8*, 11753–11762.

(29) Yan, R.; Fathipour, S.; Han, Y.; Song, B.; Xiao, S.; Li, M.; Ma, N.; Protasenko, V.; Muller, D. A.; Jena, D.; Xing, H. G. Esaki Diodes in Van Der Waals Heterojunctions with Broken-Gap Energy Band Alignment. *Nano Lett.* **2015**, *15*, 5791–5798.

(30) Yan, X.; Liu, C.; Li, C.; Bao, W.; Ding, S.; Zhang, D. W.; Zhou, P. Tunable SnSe2 /WSe2 Heterostructure Tunneling Field Effect Transistor. *Small* **2017**, *13*, 1701478.

(31) Burghard, M.; Mews, A. High-Resolution Photocurrent Mapping of Carbon Nanostructures. *ACS Nano* **2012**, *6*, 5752–5756.

(32) Liu, X.; Qu, D.; Li, H.-M.; Moon, I.; Ahmed, F.; Kim, C.; Lee, M.; Choi, Y.; Cho, J. H.; Hone, J. C.; Yoo, W. J. Modulation of Quantum Tunneling Via a Vertical Two-Dimensional Black Phosphorus and Molybdenum Disulfide p-n Junction. *ACS Nano* **2017**, *11*, 9143–9150. (33) Zhu, Y.; Jain, N.; Vijayaraghavan, S.; Mohata, D. K.; Datta, S.; Lubyshev, D.; Fastenau, J. M.; Liu, W. K.; Monsegue, N.; Hudait, M. K. Role of Inas and Gaas Terminated Heterointerfaces at Source/Channel on the Mixed As-Sb Staggered Gap Tunnel Field Effect Transistor Structures Grown by Molecular Beam Epitaxy. *J. Appl. Phys.* **2012**, *112*, 024306.

(34) Borg, B. M.; Ek, M.; Ganjipour, B.; Dey, A. W.; Dick, K. A.; Wernersson, L.-E.; Thelander, C. Influence of Doping on the Electronic Transport in GaSb/InAs(Sb) Nanowire Tunnel Devices. *Appl. Phys. Lett.* **2012**, *101*, 043508.

(35) Lee, J.; Dae Woong, K.; Hyun Woo, K.; Jang Hyun, K.; Euyhwan, P.; Taehyung, P.; Sihyun, K.; Ryoongbin, L.; Jong-Ho, L.; Byung-Gook, P. Analysis on Temperature Dependent Current Mechanism of Tunnel Field-Effect Transistors. *Jpn. J. Appl. Phys.* **2016**, *55*, 06GG03.

(36) Sah, C. T. Electronic Processes and Excess Currents in Gold-Doped Narrow Silicon Junctions. *Phys. Rev.* **1961**, *123*, 1594–1612.

(37) Chynoweth, A. G.; Feldmann, W. L.; Logan, R. A. Excess Tunnel Current in Silicon Esaki Junctions. *Phys. Rev.* **1961**, *121*, 684–694.

(38) Majumdar, K.; Thomas, P.; Loh, W.-Y.; Hung, P. Y.; Matthews, K.; Pawlik, D.; Romanczyk, B.; Filmer, M.; Gaur, A.; Droopad, R.; Rommel, S. L.; Hobbs, C.; Kirsch, P. D. Mapping Defect Density in MBE Grown  $In_{0.53}Ga_{0.47}As$  Epitaxial Layers on Si Substrate Using Esaki Diode Valley Characteristics. *IEEE Trans. Electron Devices* **2014**, *61*, 2049–2055.

(39) Villegas, C. E. P.; Rocha, A. R.; Marini, A. Anomalous Temperature Dependence of the Band Gap in Black Phosphorus. *Nano Lett.* **2016**, *16*, 5095–5101.

(40) Bessire, C. D.; Björk, M. T.; Schmid, H.; Schenk, A.; Reuter, K. B.; Riel, H. Trap-Assisted Tunneling in Si-InAs Nanowire Heterojunction Tunnel Diodes. *Nano Lett.* **2011**, *11*, 4195–4199.

(41) Chen, J.-R.; Odenthal, P. M.; Swartz, A. G.; Floyd, G. C.; Wen, H.; Luo, K. Y.; Kawakami, R. K. Control of Schottky Barriers in Single Layer MoS<sub>2</sub> Transistors with Ferromagnetic Contacts. *Nano Lett.* **2013**, *13*, 3106–3110.

(42) Li, X.; Grassi, R.; Li, S.; Li, T.; Xiong, X.; Low, T.; Wu, Y. Anomalous Temperature Dependence in Metal-Black Phosphorus Contact. *Nano Lett.* **2018**, *18*, 26–31.

(43) Varun, I.; Bharti, D.; Raghuwanshi, V.; Tiwari, S. P. Multi-Temperature Deposition Scheme for Improved Resistive Switching Behavior of  $Ti/AlO_x/Ti$  MIM Structure. *Solid State Ionics* **2017**, *309*, 86–91.

(44) Shin, B.; Weber, J. R.; Long, R. D.; Hurley, P. K.; Walle, C. G. V. d.; McIntyre, P. C. Origin and Passivation of Fixed Charge in Atomic Layer Deposited Aluminum Oxide Gate Insulators on Chemically Treated Ingaas Substrates. *Appl. Phys. Lett.* **2010**, *96*, 152908.

(45) Castellanos-Gomez, A.; Michele, B.; Rianda, M.; Vibhor, S.; Laurens, J.; Herre, S. J. v. d. Z.; Gary, A. S. Deterministic Transfer of Two-Dimensional Materials by All-Dry Viscoelastic Stamping. 2D *Mater* **2014**, *1*, 011002.