# Polarity-Controllable Devices and Circuits for Doping-Free 2D Electronics

Thèse N°9458

Présentée le 28 juin 2019

à la Faculté informatique et communications Laboratoire des systèmes intégrés (IC/STI) Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

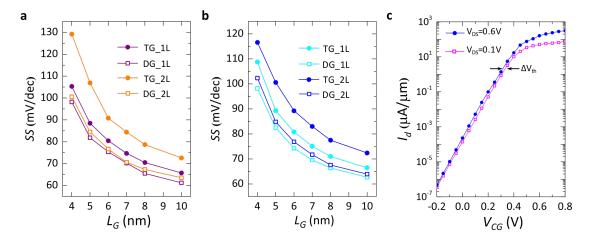

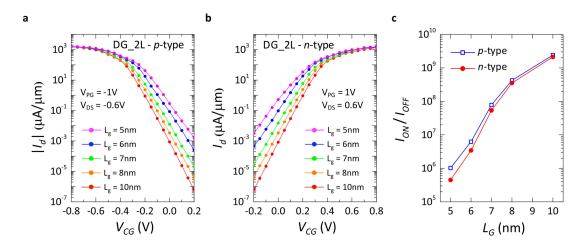

### Giovanni Vincenzo RESTA

Acceptée sur proposition du jury

Prof. M. A. Ionescu, président du jury

Prof. G. De Micheli, Prof. P.-E. J. M. Gaillardon, directeurs de thèse

Prof. S. Mitra, rapporteur Dr I. Radu, rapporteuse Prof. A. Kis, rapporteur

Love with your heart, use your head for everything else.

— Alan Melikdjanian a.k.a. Captain Disillusion

To my Family... To my Friends... To Mish.

### Acknowledgements

It is a common conception that scientists suffer for their art. Like many such impressions, there is some truth behind this one also. Several studies conducted by academic institutions as well as by independent organizations have found that a high percentage of PhD students are at risk of developing depression. While it is difficult to make conclusive claims, and conditions vary considerably between different universities, some of the statistics reported are alarming at best. I was recently reading that a 2014 study at University of California, Berkeley (see http://go.nature.com/2HwlL4v) found that up to 47% of PhD students (out of the 790 in the survey) met the criteria to be classified as depressed. A Nature survey in 2017 (see go.nature.com/2kzo890) showed that among the 1574 students that participated 45% had sought professional help for anxiety or depression caused by their PhD studies.

I then started to think about my own experiences in research and reflect on how fortunate I have been over the course of my PhD at LSI. Like any PhD student, I have gone through some stressful times, and I realize that it is mainly thanks to the people that have been around me that they never got the better of me.

First, I wish to thank my advisor Prof. Giovanni De Micheli (Nanni) and my co-advisor Prof. Pierre-Emmanuel Gaillardon for their guidance and support during this PhD thesis. While the current mentality in the research world often puts the need to publish ahead of the quality of the scientific work, I always felt that both Nanni and Pierre-Emmanuel focused on the soundness and cohesiveness of my research and never pressured me to over-publish. They always made me feel appreciated and respected, both as a person and a scientist. I still remember one of the first conversations I had with Nanni when he said that his hope for his PhD students is that they become more successful that he has been (quite a hard task!).

A special thanks goes to Prof. Francky Catthoor, Dr. Iuliana Radu and Dr. Dennis Lin for supporting my PhD at IMEC and for all their invaluable feedback throughout my research. I extend my gratitude to the members of my oral committee Prof. M.A. Ionescu and Prof A. Kis from EPFL, and Prof S. Mitra from Stanford.

EPFL is a great place to do a PhD, and these 4 years spent at LSI have been

amazing. I want to thank for the bottom of my heart Eleonora, Francesca C., Francesca S., Giulia, Ivan, Nadja, Aya and all the other members of the LSI lab. We have always been supportive to each other, shared the joy for each other achievements as you do in a family and not in a competitive work environment. These guys always made the office feel like another home, a place where you are happy to go every morning. More than just coworkers, they have become lifelong friends. I will always hold dear the memories of our years together! I also want to acknowledge few friends that stopped by the lab for a little while, bringing fresh energy and enthusiasm. Diego, Marcello, Eleonora, Matilda, Kate, Lucia, Sofia and Simone, it was such a pleasure meeting all of you. I would also not forget about Peanut, one of the newest addition to my life, who aside from bringing much joy, has made the lab slightly less safe on many Fridays (sorry Nanni!). A special thanks goes to Christina and Carole for their invaluable help in the daily life of the LSI lab.

During my PhD I have been fortunate to work in IMEC, where I have had the chance and the privilege to meet some amazing people and to reunite with some old friends. I want to thank Abhinav, Aditi, Abhitosh, Alessandra, Flavia, Dimitri, Yashwanth and Swati for their friendship and for the nice memories I will always cherish. I hope we will have many more adventures together! A really special thanks goes to one of my dearest friend Odysseas and to his wife Argyro. Your friendship is invaluable to me.

My biggest grazie goes to Mamma, Papà and Elisa for their love and support. I could have never hoped for a better family, I love you so much.

Last, but surely not least, Mish, my partner in life. No obstacle is too big with you on my side. Thank you.

Gjiovani V. Resta

April 26, 2019

### Abstract

The growth of information technology in recent decades has been sustained by the miniaturization of Complementary Metal-Oxide-Semiconductor (CMOS) Field-Effect Transistors (FETs), with the number of devices per unit area constantly increasing, as exemplified by Moore's law. Modern digital Integrated Circuits (ICs) contain billions of transistors and logic gates, fabricated with CMOS technology. As scaling of conventional silicon-based electronics is reaching its ultimate limit, considerable effort has been devoted to find new materials and new device concepts that could ultimately outperform standard silicon transistors. Among the materials that are studied for charge-based devices, Two-Dimensional (2D) materials of the Transition Metal Di-Chalcogenides (TMDCs) family show promising opportunities, thanks to their electrical and physical properties. In order to enable 2D electronics to be integrated in the Back-End-Of-the-Line (BEOL) with conventional CMOS it is essential to achieve complementary operation of the transistors, in order to benefit from the low standby power consumption enabled by CMOS logic. In CMOS, silicon is physically doped during the fabrication process with ion implantation to create unipolar devices with Ohmic contacts. Ion implantation requires high temperature annealing to repair damages in the silicon and achieve proper dopant activation, and this high temperature process is not compatible with the process for monolithic 3D CMOS, which requires a low thermal budget. Physical doping, through ion-implantation, of 2D material has not proven to be successful due to extreme thinness of the 2D semiconductors. The possibility of introducing dopant atoms during growth of the 2D material has been reported, but lacks selectivity and does not allow for any control of the doping profile. Several chemical and molecular doping techniques have been developed, but are often non-stable and non-CMOS compatible. A device concept that does not rely on any physical or chemical doping, and use instead un-doped materials, would be of great interest in this regard.

In this thesis, we report the first experimental demonstration of a doping-free, polarity-controllable device fabricated on few-layer tungsten di-selenide (WSe<sub>2</sub>). We show how modulation of the Schottky barriers at drain and source by a separate gate, named polarity gate, can enable the selection of the carriers injected in the channel, and achieve controllable polarity behaviour with ON/OFF current ratios  $> 10^6$  for both electrons

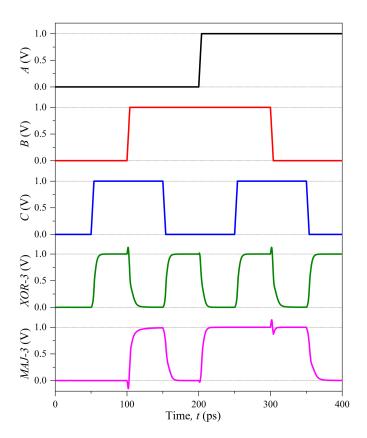

and holes conduction. Following this demonstration, we fabricate and characterize a variety of polarity-controllable logic gates such as Inverter (INV), NOT-AND (NAND), NOT-OR (NOR), that are the building primitives used in the logic synthesis frameworks for conventional CMOS logic. Moreover, we experimentally show 2-Input Exclusive OR (XOR-2), 3-Input Exclusive OR (XOR-3) and Majority (MAJ) gates that, thanks to the polarity-controllable devices, can be realized with fewer transistors as compared to what is achievable in conventional CMOS. We demonstrate a complete standard cell library with the possibility of fabricating compact, highly-expressive logic gates that can be exploited to gain advantages at circuit level, using XOR and MAJ functions as logic primitives. Moreover, for the first time, we study scaling trends and evaluate the performances of polarity-controllable devices realized with undoped mono- and bi-layer 2D materials. Using ballistic self-consistent quantum simulations, combined with TCAD simulations, it is shown that, with the suitable channel material, such polarity-controllable technology can scale down to sub-10 nm gate lengths, while showing performances comparable to the ones of unipolar, physically-doped 2D electronic devices.

Keywords: nanotechnology, scaling, CMOS, beyond-CMOS, novel materials, 2D semi-conductors, transition-metal-dichalcogenides, WSe<sub>2</sub>, doping-free, electrostatic-doping, Schottky-barrier, polarity-control, 2D logic gates, fabrication, testing, simulations.

### Sommario

La crescita della tecnologia dell'informazione nei decenni passati è stata resa possibile dalla miniaturizzazione dei transistor Complementary Metal-Oxide-Semiconductor (CMOS), con il numero di dispositivi per unità di area che ha continuato a raddoppiare ogni circa 2 anni, come predetto dalla legge di Moore. I circuiti integrati moderni contengono miliardi di transistor e porte logiche, fabbricati in tecnologia CMOS. La miniaturizzazione dei tradizionali dispositivi basati sul silicio sta raggiungendo i suoi limiti, e nella comunità scientifica vi è un notevole interesse nello scoprire nuovi materiali e nuovi tipi di dispositivi che potrebbero dimostrare prestazioni superiori ai transistor in silicio. Tra i nuovi materiali che sono studiati come canale semiconduttore per dispositivi a base di carica elettrica, i materiali Two-Dimensional (2D) della famiglia dei Transition Metal Di-Chalcogenides (TMDCs) sono tra i più promettenti, grazie alle loro proprietà elettriche e fisiche.

Nella tecnologia CMOS, il silicio viene drogato tramite impiantazione ionica durante la fabbricazione, per creare dispositivi unipolari con contatti omici. L'impiantazione ionica richiede però alte temperature di tempratura, necessarie per riparare i danni provocati alla struttura cristallina del silicio e per attivare gli atomi droganti. Queste alte temperature non sono compatibili con i processi di integrazione monolitica per 3D CMOS, che richiedono un budget di temperatura basso, per non danneggiare i dispositvi già construiti. Inoltre con le lunghezze dei canali che si avvicinano ai 20 nm, l'impiantazione ionica è diventata sempre più difficile da controllare. L' impiantazione ionica non si è dimostrata possibile per i materiali 2D, ed altre tecniche di doping che utilizzano drogaggio chimico o molecolare sono state sviluppate. Tutavia queste tecniche risultano essere non stabili e non sono compatibili con i processi CMOS tradizionali, non permettendo quindi l'integrazione dei dispositivi nel *Back-End-Of-the-Line* (BEOL). Un dispositivo che non richieda alcuna impiantazione ionica o drogaggio chimico, e si basi su materiali non drogati sarebbe di grande interesse in questo campo.

In questa tesi, presentiamo la prima dimostrazione sperimentale di un dispositivo senza drogaggio fisico o chimico, la cui polarità può essere controllata dinamicamente, realizzato su tungsten di-selenide (WSe<sub>2</sub>). Dimostriamo come la modulazione delle barriere Schottky presenti ai contatti di source e drain da parte di un terminale aggiuntivo,

chiamato terminale di polarità, permetta di selezionare i di portatori di carica (elettroni o lacune) che vengono iniettati nel canale. Grazie a questa struttura, otteniamo il controllo della polarità del dispositivo, con un rapporto tra corrente di ON e OFF  $> 10^6$  sia per la conduzione di elettroni che di lacune, sullo stesso dispositivo. I dispositivi con controllo della polarità realizzati su WSe<sub>2</sub> permettono di realizzare porte logiche compatte, in grado di aumentare la densità computazionale dell'elettronica 2D. Riportiamo sulla fabbricazione e caratterizzazione di una varietà di porte logiche fabbricate con transistor a controllo di polarità, come *Inverter* (INV), *NOT-AND* (NAND), *NOT-OR* (NOR) che sono i blocchi fondamentali usati per la sintesi di funzioni logiche in CMOS. Inoltre, dimostriamo sperimentalmente porte XOR a 2 ingressi, XOR a 3 ingressi e porte di maggioranza a 3 ingressi, che possono essere realizzate con un numero di transistor minore rispetto a quanto possibile in logica CMOS tradizionale. Per la prima volta, studiamo l'andamento delle prestazioni dei dispositivi a controllo di polarità realizzati su 1 o 2 layer di WSe<sub>2</sub>, rispetto alla loro miniaturizzazione. Usando delle simulazioni quantistiche balistiche e autoconsistenti dimostriamo come, con il materiale di canale appropriato, i dispositivi a controllo di polarità possano essere miniaturizzati sino a lunghezze di canale di 5 nm, mantenendo prestazioni comparabili a quelle dei dispositivi unipolari, realizzati su materiali 2D drogati fisicamente.

Parole Chiave: nanotecnologie, miniaturizzazione, CMOS, oltre CMOS, nuovi materiali, semiconduttori 2D, transition-metal-dichalcogenides, WSe<sub>2</sub>, assenza di drogaggio, drogaggio elettrostatico, barriere Schottky, controllo di polarità, porte logiche 2D, fabbricazione, misure, simulazioni.

## Contents

| A            | cknov  | wledgements                                               | V          |

|--------------|--------|-----------------------------------------------------------|------------|

| $\mathbf{A}$ | bstra  | ct / Sommario                                             | vi         |

| Li           | ist of | Figures                                                   | ΧV         |

| Li           | st of  | Tables                                                    | xix        |

| Li           | ist of | Acronyms                                                  | xxi        |

| 1            | Intr   | roduction                                                 | 1          |

|              | 1.1    | Thesis Motivation                                         | 3          |

|              | 1.2    | Novel Materials and Devices for Future Electronic Systems | 4          |

|              | 1.3    | Multiple-Independent-Gate FETs                            | 7          |

|              | 1.4    | Thesis Objectives and Achievements                        | 8          |

|              | 1.5    | Thesis Organization                                       | 9          |

| 2            | TM     | DCs for 2D Electronics                                    | 11         |

|              | 2.1    | Material Properties                                       | 11         |

|              | 2.2    | Synthesis and transfer of 2D TMDCs                        | 13         |

|              | 2.3    | Experimental State-of-the-Art in 2D Electronics           | 15         |

|              | 2.4    | Value of Ambipolarity                                     | 19         |

| 3            | Mu     | tiple Independent Gate Devices                            | <b>2</b> 1 |

|              | 3.1    | Multiple-Independent-Gate Silicon Nanowires Transistors   | 22         |

|              |        | 3.1.1 Polarity Control                                    | 23         |

|              |        | 3.1.2 Sub-Threshold Slope Control                         | 26         |

|              |        |                                                           |            |

|   |      | 3.1.3 Threshold Voltage Control                                              |     | 28 |

|---|------|------------------------------------------------------------------------------|-----|----|

|   | 3.2  | Novel Materials for Polarity-Controllable Devices                            |     | 30 |

|   |      | 3.2.1 Germanium Nanowires                                                    |     | 30 |

|   |      | 3.2.2 Carbon Nanotubes                                                       |     | 31 |

|   |      | 3.2.3 Graphene                                                               |     | 34 |

|   | 3.3  | Circuit-Level Opportunities                                                  |     | 34 |

|   | 3.4  | Summary                                                                      |     | 39 |

| 4 | Pola | ${f arity-Controllable\ WSe_2\ FETs}$                                        |     | 41 |

|   | 4.1  | Fabrication Process                                                          |     | 42 |

|   | 4.2  | Achieving Ambipolarity                                                       |     | 46 |

|   | 4.3  | Demonstration of Polarity-Controllable Behavior $\ \ldots \ \ldots \ \ldots$ |     | 47 |

|   | 4.4  | Summary                                                                      |     | 52 |

| 5 | Dop  | ing-Free WSe <sub>2</sub> Logic Gates                                        |     | 55 |

|   | 5.1  | Fabrication of Logic Gates                                                   |     | 56 |

|   |      | 5.1.1 Design Regularity                                                      |     | 56 |

|   | 5.2  | Device Characterization                                                      |     | 58 |

|   |      | 5.2.1 Physical Characterization                                              |     | 58 |

|   |      | 5.2.2 Switching Properties                                                   |     | 59 |

|   | 5.3  | Demonstration of Logic Gates                                                 |     | 62 |

|   |      | 5.3.1 Inverter                                                               |     | 63 |

|   |      | 5.3.2 Two-Input Logic Gates                                                  |     | 64 |

|   |      | 5.3.3 Three-Input Logic Gates                                                |     | 66 |

|   | 5.4  | Summary                                                                      |     | 67 |

| 6 | Scal | ed Devices and Logic Gates Simulations                                       |     | 69 |

|   | 6.1  | Quantum Mechanical Simulations                                               |     | 70 |

|   |      | 6.1.1 Methodology                                                            |     | 70 |

|   |      | 6.1.2 Simulated Transfer Characteristics for 2D-WSe $_2$                     |     | 72 |

|   |      | 6.1.3 Analysis and Comparison of Transfer Characteristics                    |     | 73 |

|   |      | 6.1.4 Simulated Transfer Characteristics for Reduced Band-Gap MX             | 2 . | 77 |

|              | 6.2   | TCAD          | Simulations                                                     | . 7 | <sup>7</sup> 8 |

|--------------|-------|---------------|-----------------------------------------------------------------|-----|----------------|

|              |       | 6.2.1         | Fit with Quantum Simulation                                     | . 7 | <b>7</b> 8     |

|              |       | 6.2.2         | Optimized Device Structure and Switching Characteristics        | . 8 | 30             |

|              |       | 6.2.3         | Detailed Analysis of Transfer Characteristics for a XOR gate $$ | . 8 | 32             |

|              |       | 6.2.4         | Logic Gates Simulations                                         | . 8 | 36             |

|              | 6.3   | Summ          | ary                                                             | . 8 | 38             |

| 7            | Con   | clusio        | as and Future Perspectives                                      | 9   | 3              |

|              | 7.1   | Overvi        | iew of Thesis contribution                                      | . 9 | )4             |

|              | 7.2   | Future        | Research                                                        | . 9 | 95             |

| A            | Clea  | aning I       | Procedures and Characterization                                 | 9   | 7              |

| В            | Con   | tact A        | nnealing                                                        | 10  | )1             |

| $\mathbf{C}$ | Effe  | ct of C       | Oxide Encapsulation                                             | 10  | 13             |

| Bi           | bliog | graphy        |                                                                 | 10  | 17             |

| Cı           | arric | ulum <b>V</b> | Vitae                                                           | 12  | 27             |

# List of Figures

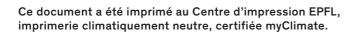

| 1.1  | Evolution of modern ICs and comparison with vacuum tube technology                                                                 | 2  |

|------|------------------------------------------------------------------------------------------------------------------------------------|----|

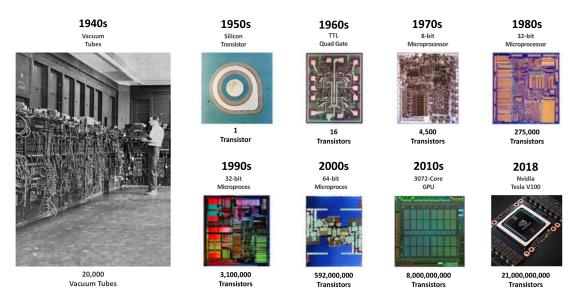

| 1.2  | Three eras of CMOS technology scaling                                                                                              | 3  |

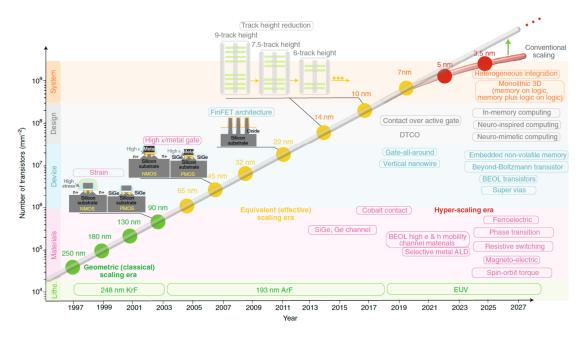

| 1.3  | Novel materials and new device concepts                                                                                            | 5  |

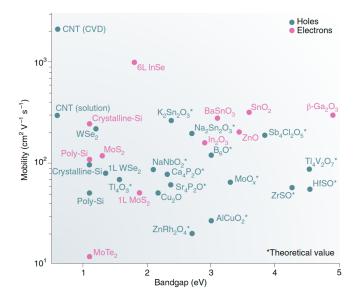

| 1.4  | Materials considered for Back-End-Of-the-Line devices                                                                              | 7  |

| 2.1  | The transition-metal di-chalcogenide family                                                                                        | 12 |

| 2.2  | Benefit of 2D-TMDCs for electronic applications                                                                                    | 13 |

| 2.3  | Relevant metrics for synthesis and transfer of 2D materials                                                                        | 14 |

| 2.4  | $2D-MoS_2$ electronics                                                                                                             | 16 |

| 2.5  | Complementary devices on 2D materials                                                                                              | 18 |

| 2.6  | Ambipolarity on 2D materials                                                                                                       | 20 |

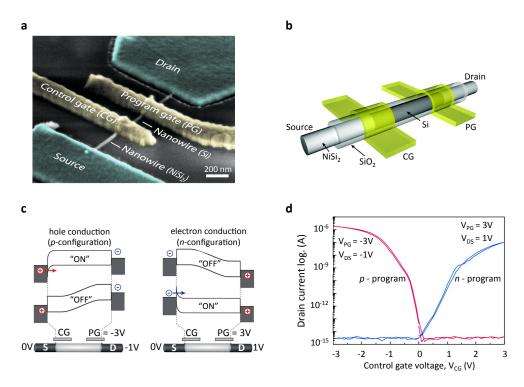

| 3.1  | The reconfigurable silicon nanowire FET with independent gates                                                                     | 24 |

| 3.2  | Double-independent-gates silicon nanowires                                                                                         | 25 |

| 3.3  | Conceptual band diagrams for the $Double$ -Independent-Gate (DIG)-Field-Effect $Transistor$ (FET) in the different operation modes | 25 |

| 3.4  | Silicon-nanowires DIG-FET transfer characteristics                                                                                 | 27 |

| 3.5  | Subthreshold-slope control mechanisms and experimental transfer characteristics                                                    | 28 |

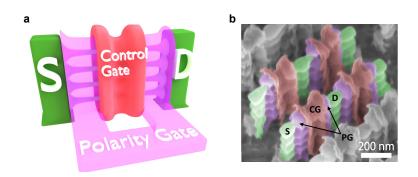

| 3.6  | Three-independent-gate FET                                                                                                         | 29 |

| 3.7  | Band diagrams relative to the 6 allowed operation modes for TIG-FETs                                                               | 29 |

| 3.8  | Experimental transfer characteristics of the three-independent-gate device, showing the threshold-voltage control mode             | 31 |

| 3.9  | OFF-current leakage suppression and polarity control in a Germanium nanowire transistor                                            | 32 |

| 3.10 | Polarity control in carbon nanotubes FETs                                                                                          | 33 |

|      |                                                                                                                                    |    |

| 3.11 | Polarity-control in graphene FETs                                                                               | 35 |

|------|-----------------------------------------------------------------------------------------------------------------|----|

| 3.12 | DIG-FET circuit symbol and device abstraction                                                                   | 35 |

| 3.13 | XOR behavior of the DIG-FET when loaded with resistor                                                           | 36 |

| 3.14 | Fully complementary logic gates with polarity-controllable SiNWs-FETs                                           | 37 |

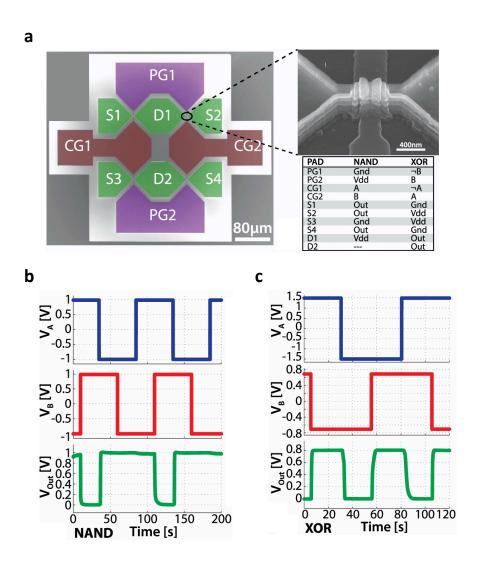

| 3.15 | Experimental demonstartion of NAND and XOR logic gates with DIG-FETs. $$                                        | 38 |

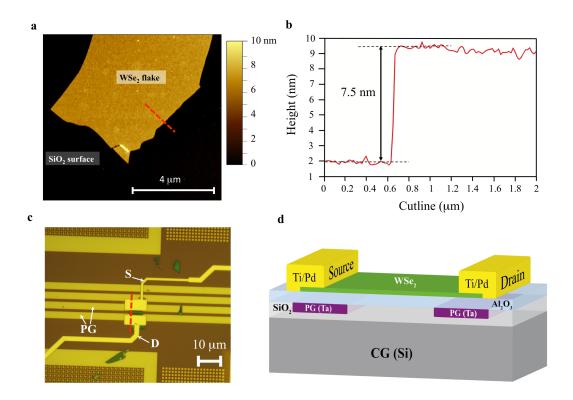

| 4.1  | WSe <sub>2</sub> flake properties and device fabrication                                                        | 43 |

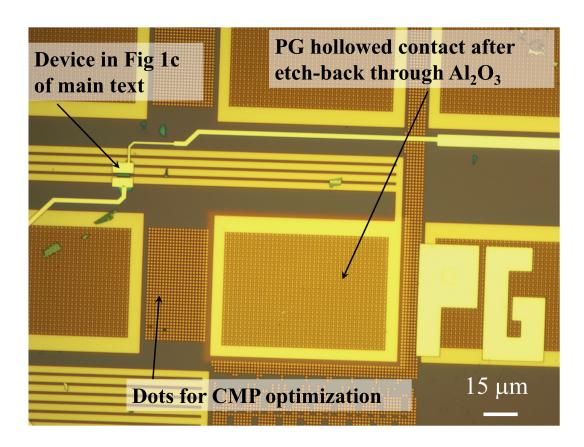

| 4.2  | Fabrication of buried features                                                                                  | 44 |

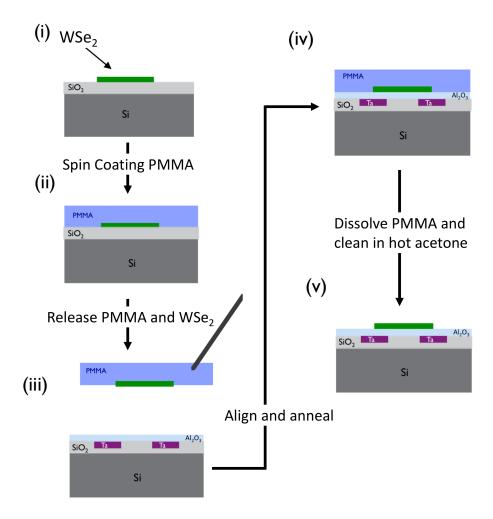

| 4.3  | Transfer procedure                                                                                              | 45 |

| 4.4  | Characterization of ambipolar behavior                                                                          | 47 |

| 4.5  | Device transfer characteristics                                                                                 | 48 |

| 4.6  | Mobility Extraction                                                                                             | 50 |

| 4.7  | $I_{DS} - V_{DS}$ characteristics                                                                               | 51 |

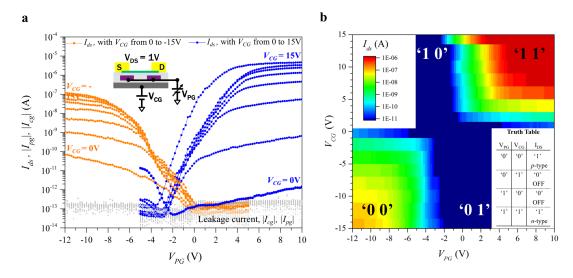

| 4.8  | Polarity change "on-the-fly" and XOR behaviour                                                                  | 51 |

| 4.9  | Additional device characteristics                                                                               | 53 |

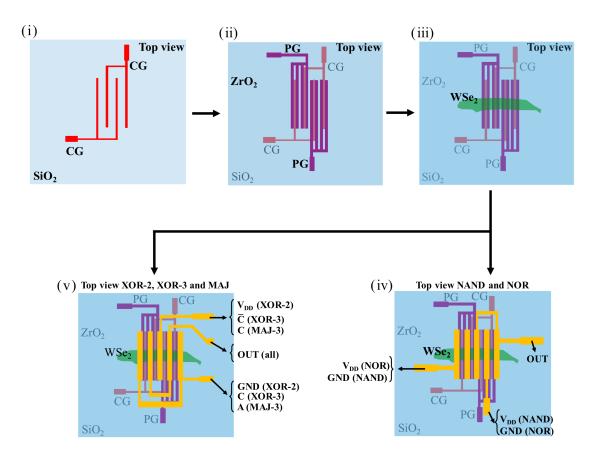

| 5.1  | Detailed fabrication process                                                                                    | 57 |

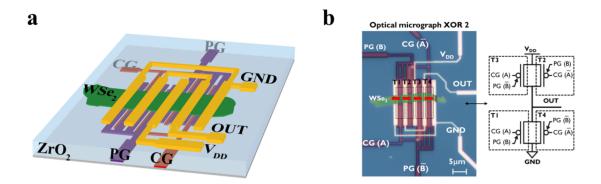

| 5.2  | 2D-WSe <sub>2</sub> polarity-controllable two-input XOR                                                         | 58 |

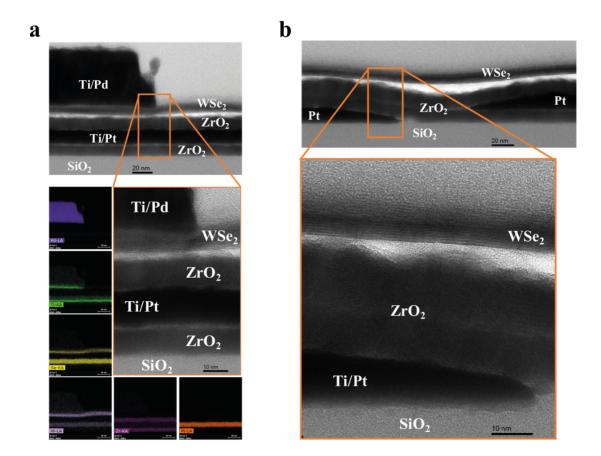

| 5.3  | Cross-sectional TEM with EDX mapping                                                                            | 59 |

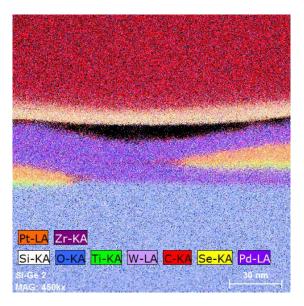

| 5.4  | Full EDX Mapping.                                                                                               | 60 |

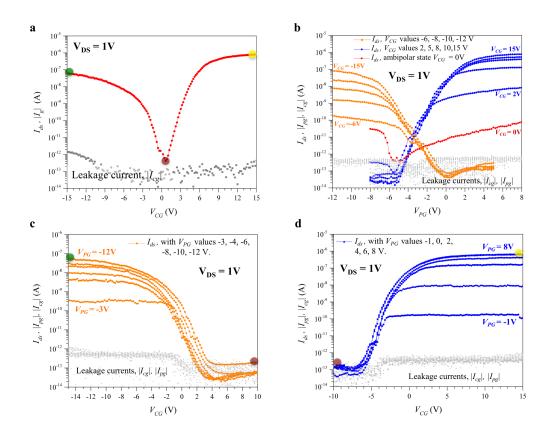

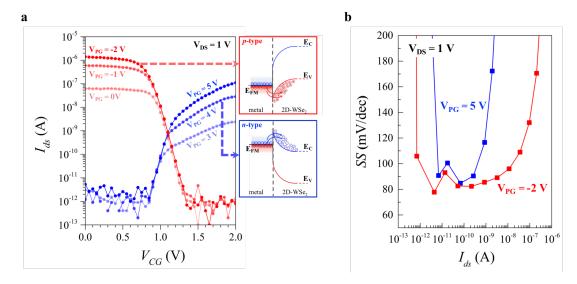

| 5.5  | Polarity-controllable device characteristics                                                                    | 61 |

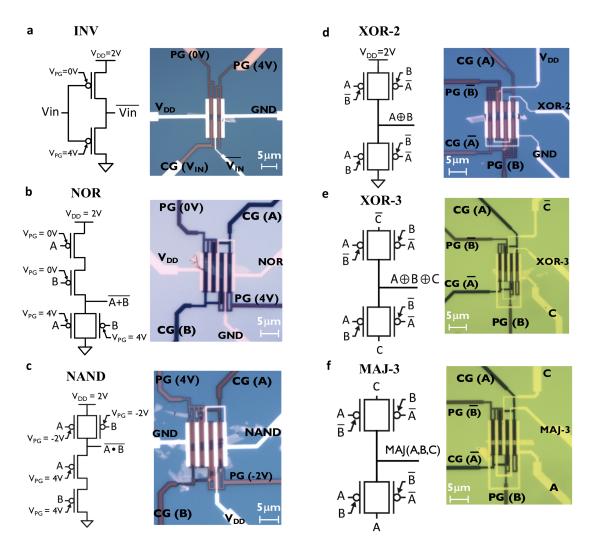

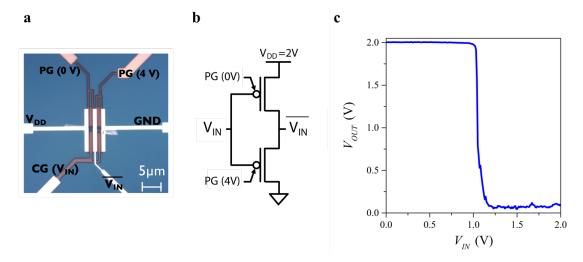

| 5.6  | Circuit schematic and optical micrograph of fabricated and tested devices.                                      | 63 |

| 5.7  | Inverter behavior                                                                                               | 64 |

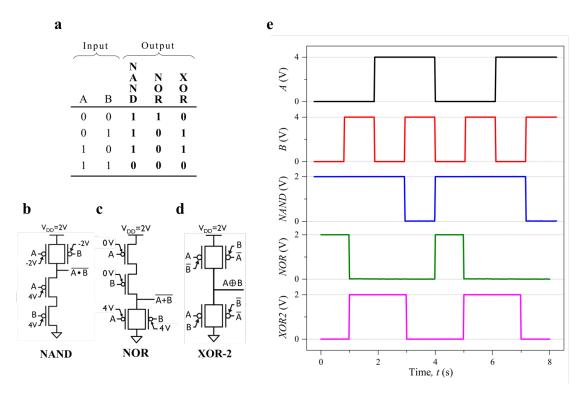

| 5.8  | Two-input logic gates                                                                                           | 65 |

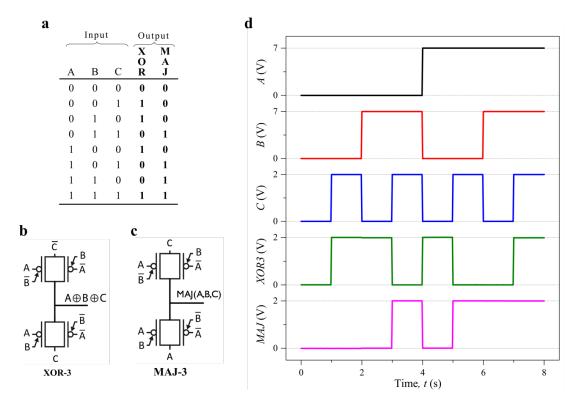

| 5.9  | Three-input logic gates                                                                                         | 66 |

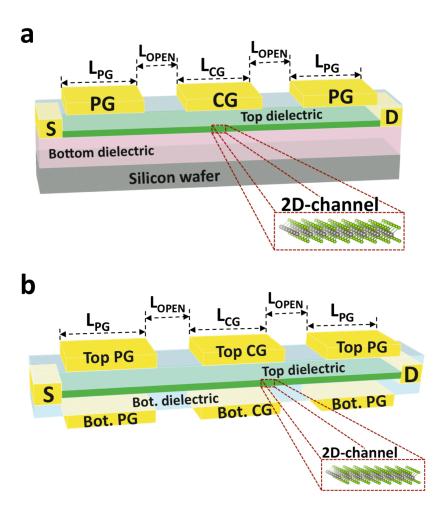

| 6.1  | 3D schematic of the simulated devices                                                                           | 71 |

| 6.2  | Band-diagrams of the 4 regions of operation extracted from the simulation                                       | 11 |

| 0.2  | with 1L-WSe <sub>2</sub> at $L_G = 8$ nm                                                                        | 73 |

| 6.3  | Simulated transfer characteristics for 1L-WSe <sub>2</sub> polarity-controllable FETs at different gate lengths | 74 |

| 6.4  | Simulated transfer characteristics for $2L\text{-WSe}_2$ polarity-controllable FETs                             |    |

|      | at different gate lengths                                                                                       | 75 |

| 6.5  | Benefits of double-gate geometry in 2L-WSe <sub>2</sub> n-type FETs                                                        |

|------|----------------------------------------------------------------------------------------------------------------------------|

| 6.6  | Evaluation of sub-threshold slope and DIBL                                                                                 |

| 6.7  | Analysis of performances for double-gate polarity-controllable device with $Bi\text{-}Layer$ (2L)-MX <sub>2</sub> material |

| 6.8  | Comparison of transfer characteristics simulated with ViDES and Synopsis Sentaurus                                         |

| 6.9  | Comparison between optimized, TG and DG structures                                                                         |

| 6.10 | Matched $I_{ds}V_{CG}$ and $I_{ds}V_{PG}$ transfer characteristics                                                         |

| 6.11 | Complete current map of the device                                                                                         |

| 6.12 | Simulated output characteristics                                                                                           |

| 6.13 | Analaysis of transistors behavior in XOR gate                                                                              |

| 6.14 | Transfer characteristics for positive and negative $V_{DS}$ for both $n$ - and $p$ -type operation                         |

| 6.15 | Switching behavior of the simulated fan-out of 4 inverter                                                                  |

| 6.16 | Switching behavior of the simulated NAND and 2-Input Exclusive OR (XOR-2) logic gates                                      |

| 6.17 | Switching behavior of the simulated 3-inputs logic gates                                                                   |

| 6.18 | Energy-Delay Product for selected logic gates compared with other devices reported in BCB 3.0                              |

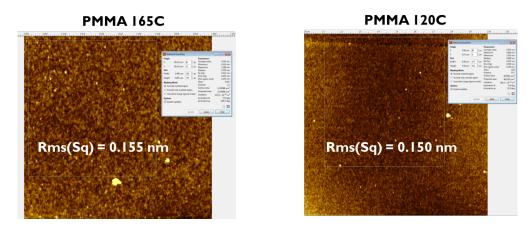

| A.1  | Surface roughness of bare $SiO_2$ blancket                                                                                 |

| A.2  | Residues on the Sio <sub>2</sub> surface after lift-off of e-beam markers for 3 different processes                        |

| A.3  | Removal of residues on the Sio <sub>2</sub> surface after lift-off of e-beam markers for PMMA-based processes              |

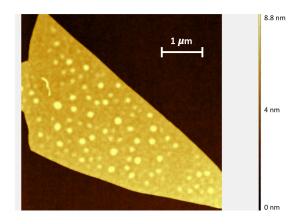

| A.4  | AFM image showing tape residues on exfoliated flake                                                                        |

| A.5  | AFM image showing the exfoliated flake after cleaning procedure 99                                                         |

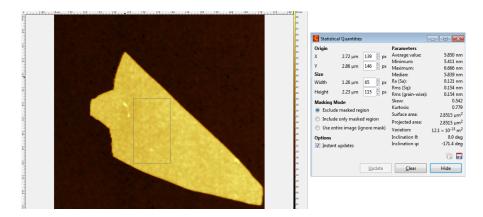

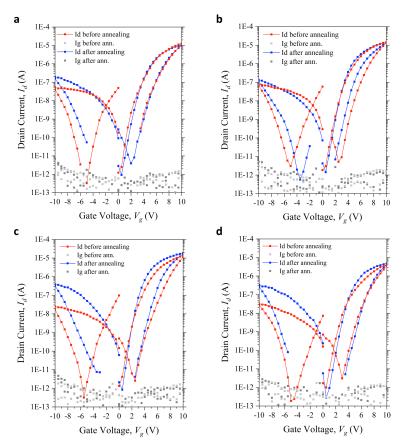

| В.1  | Effect of contact annealing on several WSe <sub>2</sub> flakes                                                             |

| C.1  | Effect of aluminum oxide encapsulation with ALD-Savannah 104                                                               |

| C.2  | Effect of aluminum oxide encapsulation with ALD-Polygon 105                                                                |

| C.3  | Effect of zirconium oxide encapsulation with ALD-Centura III-V 106                                                         |

## List of Tables

6.1  $\,$  Material properties used to construct the effective mass Hamiltonian  $\,\ldots\,\,70$

### List of Acronyms

. . . . . . . . . . . . . . . . OFF-current  $V_{DD}$  . . . . . . . . . . . . . . . . . Supply Voltage  $V_{TH}$  . . . . . . . . . . . . . . . . . Threshold Voltage  $\phi_{SB}$  . . . . . . . . . . . . . . . . . . Schottky-barrier height 1L . . . . . . . . . . . . . . . . . Mono-Layer AFM .... Atomic Force Microscope  $Al_2O_3$  . . . . . . . . . . . . . . aluminium oxide ALD . . . . . . . . . . . . . . . . . Atomic Layer Deposition Au . . . . . . . . . . . . . . . . gold BCB . . . . . . . . . . . . . . . . . Beyond-CMOS Benchmark

| CG       | Control Gate                                    |

|----------|-------------------------------------------------|

| CMOS     | $Complementary\ Metal-Oxide-Semiconductor$      |

| CMP      | Chemical Mechanical Polishing                   |

| CNTs     | Carbon Nano-Tubes                               |

| CVD      | Chemical Vapor Deposition                       |

| $D_{it}$ | Interface-Trap Density                          |

| DAC      | Design Automation Conference                    |

| DCM      | $di	ext{-}chloro	ext{-}methane$                 |

| DG       | Double-Gate                                     |

| DIBL     | Drain-Induced Barrier Lowering                  |

| DIG      | $Double\hbox{-}Independent\hbox{-}Gate$         |

| DOS      | Density Of States                               |

| DTCO     | Design Technology Co-Optimization               |

| EDLT     | Electric Double-Layer Transistors               |

| EDP      | Energy-Delay Product                            |

| EDX      | Energy-Disperse X-ray                           |

| EOT      | Equivalent Oxide Thickness                      |

| EUV      | Extreme Ultra-Violet                            |

| FEOL     | $Front	ext{-}End	ext{-}Of	ext{-}the	ext{-}Line$ |

| FET      | Field-Effect Transistor                         |

| FETs     | Field-Effect Transistors                        |

| FO4      | Fan-Out of 4                                    |

| GAA      | $Gate	ext{-}All	ext{-}Around$                   |

| $H_2O$   | water                                           |

| 77.0     |                                                 |

| Hf       | hafnium                                         |

$HRTEM \ \dots \ \dots \ \dots \ High-Resolution \ Trasmission \ Electron \ Microscope$

ICs . . . . . . . . . . . . . . . . . Integrated Circuits

INV .... Inverter

IPA ..... isopropyl alcohol

LOR1A . . . . . . . . . . . . . Lift-Off Resist 1A

MAJ . . . . . . . . . . . . . . . . . Majority

MIBK . . . . . . . . . . . . . . methyl-isobutyl ketone

Mo . . . . . . . . . . . . . . . molybdenum

MOCVD . . . . . . . . . . . . . Metal-Organic Chemical Vapor Deposition

$MoS_2$  . . . . . . . . . . . . . . . molybdenum di-sulphide

$MoSe_2 \dots molybdenum di-selenide$

${

m MOSFET}$  . . . . . . . . . . . . . . . Metal-Oxide-Semiconductor Field-Effect-Transistor

$MoTe_2 \dots molybdenum di-telluride$

$N_2$  . . . . . . . . . . . . . . . . . . nitrogen

NAND . . . . . . . . . . . . . . . . NOT-AND

Nb . . . . . . . . . . . . . . . niobium

NCFETs . . . . . . . . . . . . . . Negative-Capacitance Field-Effect Transistors

NEGF . . . . . . . . . . . . . . . . Non-Equilibrium Green Function

OPD5262 . . . . . . . . . . . . . tetramethylammonium hydroxide

P . . . . . . . . . . . . . phosphorus

Pd . . . . . . . . . . . . . palladium

PECVD . . . . . . . . . . . . . . . . Plasma-Enhanced Chemical Vapor Deposition

PG . . . . . . . . . . . . . . . . . . Polarity Gate

PMMA . . . . . . . . . . . . . polymethyl methacrylate

Pt . . . . . . . . . . . . . . platinum

PTW . . . . . . . . . . . . . . . . Partner Technical Week

Re . . . . . . . . . . . . . . . . . rhenium

RFET . . . . . . . . . . . . . . . . . . Reconfigurable FET

SB . . . . . . . . . . . . . . . . . . Schottky-Barrier

SB-FETs . . . . . . . . . . . . . . . . Schottky-Barrier Field Effect Transistors

SCE . . . . . . . . . . . . . . . . . Short-Channel Effects

SCS . . . . . . . . . . . . . . . Semiconductor Characterization System

Se . . . . . . . . . . . . . selenium

Si . . . . . . . . . . . . . . . . . silicon

$SiO_2$  . . . . . . . . . . . . . . . . silicon di-oxide

SS . . . . . . . . . . . . . . . . Sub-threshold Slope

STCO . . . . . . . . . . . . . . . . System Technology Co-Optimization

Ta . . . . . . . . . . . . . . . . . tantalum

TB . . . . . . . . . . . . . . . . Tight-Binding

TCAD . . . . . . . . . . . . . . . Technology Computer-Aided Design

Te . . . . . . . . . . . . . . . . . tellurium

$TEMAZ \ \dots \ \dots \ \dots \ tetrakis (ethylmethylamino) zirconium$

TFETs ..... Tunnel Field-Effect Transistors

Ti .... titanium

TIG . . . . . . . . . . . . . . . . . . Triple-Independent-Gate

xxiv

$WS_2$  . . . . . . . . . . . . . . . . . . tungsten di-sulfide

. . . . . . . . . . . . . . . . trimethylaluminium

$WSe_2$  . . . . . . . . . . . . . . . . . tungsten di-selenide

XOR-3 ..... 3-Input Exclusive OR

${\rm ZrO}_2$  . . . . . . . . . . . . . . . . . . zirconium di-oxide

1 Introduction

Se vogliamo che tutto rimanga com'è, bisogna che tutto cambi.

— Il Gattopardo, Giuseppe Tomasi di Lampedusa

Electronics is ubiquitous in our daily activities, pervades our lives and shapes the way we communicate and interact with the world. What we have experienced in the last 70 years, in terms of technological advances, is almost unprecedented in human history, and it has all been enabled by the invention and constant advances in the performances of Integrated Circuits (ICs). To understand the magnitude of this technological revolution we can consider what a modern IC would look like if it had to be realized with vacuum tubes, the technology that preceded the invention of the integrated circuit. A system like ENIAC, Electronic Numerical Integrator and Compute, built in 1945 by John Mauchly and J. Presper Eckert at University of Pennsylvania under commission of the US Army, consisted of 20000 vacuum tubes, occupied 167 m<sup>2</sup> and consumed 150 kW to work at a clock cycle of 200 µs. The cost (corrected to match 2018) was 7 million dollars. If we consider each vacuum tube as a transistor and scale up to the size of today systems we have that in order to fit 10 billion devices (as are today in our phones) we would need  $83.5\,\mathrm{km^2}$  and  $75\,\mathrm{GW}$  of power at a whopping cost of 3.5 trillion dollars (as a reference the US GDP in 2017 was 19 trillion dollars, Manhattan occupies 59 km<sup>2</sup> and a nuclear power plant produces roughly 4 GW.

This is of course an extreme example, but such is the advancement that modern ICs have enabled and still providing nowadays. ICs have themselves seen a tremendous improvements in performances, with the computational power of a 20 years old supercomputer being now provided by the processor in our new phone. The increase in performances has been enabled by the constant miniaturization of modern transistor, with an exponential increase in the number of devices that fit in a die (as shown in Fig. 1.1). This trend was first predicted in 1965 by Intel co-founder Gordon Moore, who stated that the number of devices in integrated circuits would double every two year,

Figure 1.1 – Evolution of modern ICs and comparison with vacuum tube technology. Adapted from [1] and [2].

a prediction now commonly referred to as Moore's law [3]. In 1974 Robert Dennard formalized the guidelines that effectively enabled conventional geometrical scaling to stand until the early 2000s [4] (see Fig. 1.2). Dennard rules are based on the concept constant field scaling, *i.e.* reducing the critical dimension while keeping the electrical field constant yields higher speed and a reduced power consumption of a digital MOS device. Using a typical scaling factor of  $0.7\times$  per technology node, results in a doubling of transistor in a given area, with the power density remaining constant and the device and circuit speed inceasing by  $1.4\times$ . As stated by former Intel chief architect for the Pentium microprocessors Bob Colwell at the Design Automation Conference (DAC) in 2013 "... Moore's law gives us more transistors... Dennard scaling made them useful".

It is remarkable to appreciate that between 1975 and 2004, a time known as geometric scaling era, the core building block of modern ICs, the Metal-Oxide-Semiconductor Field-Effect-Transistor (MOSFET), remained virtually unchanged from his first experimental demonstration in 1959 at Bell lab by John Atalla and Dawon Khang. Until 2004, the miniaturization of devices had in fact been solely enabled by advancements in the lithographic process that allowed the definition of smaller features. It is equally staggering to realize that virtually every modern digital IC is based on Complementary Metal-Oxide-Semiconductor (CMOS) logic, that was originally developed by Frank Wanlass in 1963. Starting in 2005 with the 90 nm node technology boosters needed to be introduced, first at a material level, and then at a device level, in order to enable scaling to continue (equivalent (effective) scaling era in Fig. 1.2). These boosters include the use of strained Si and SiGe, the introduction of high-κ dielectric, metal gates and ultimately the development of the first 3D device structure (Fin-Field-Effect Transistor (FET)) at the 22 nm node. The next era of scaling (defined in Fig. 1.2 as hyper-scaling) will be

enabled by innovations at different technological level, starting from *Design Technology Co-Optimization* (DTCO) and up to *System Technology Co-Optimization* (STCO), where heterogeneous integration of functionally diverse integrated circuits and novel materials is envisioned. Using the words of Shekhar Borkar, former head of Intel's microprocessor technology research: "*Moore's law simply states that user value doubles every two years*", and in this form, the law will continue as long as the industry will be able to keep increasing the device functionality [5].

Figure 1.2 – Three eras of CMOS technology scaling. Past, present and future trend of transistor density scaling, depicting three distinct eras of scaling: geometric (or classical) scaling, equivalent (or effective) scaling, and hyper-scaling (or functional diversification). Proportional scaling of the various aspects of the transistor such as gate oxide, junctions, channel doping and physical gate length characterized the era of geometric scaling. The equivalent scaling era saw the introduction of unconventional materials such as silicon–germanium, hafnium-based high-κ dielectric and non-planar device structures such as FinFETs that scaled the effective mobility, the electrical gate oxide thickness and the effective transistor width, respectively. In the future, innovations in materials, devices with both logic and memory functions and heterogeneous integration technologies will enable the era of hyper-scaling in advanced electronics. Reproduced with permission from [6]. Copyright 2018 Springer Nature.

#### 1.1 Thesis Motivation

The main motivation behind this thesis is the growing interest of the electronics industry and research institutions in novel device concepts and in new semiconducting materials for next-generation beyond-CMOS electronics. More specifically we are motivated by the

need to develop a device that could easily be monolithically integrated in the *Back-End-Of-the-Line* (BEOL) with conventional CMOS electronics. Dimensional scaling has been the main drive of the silicon industry in the last decades, with the exponential growth of information technology being sustained by the miniaturization of CMOS *Field-Effect Transistors* (FETs) [4], with the number of devices per unit area constantly increasing, as exemplified by Moore's law [3].

Nowadays, scaling of silicon devices is reaching its ultimate limit, as shown is Fig. 1.2, and the exploration of novel semiconducting materials, that could be heterogeneously integrated with silicon, is an open and exciting research field, with Two-Dimensional (2D) Transition Metal Di-Chalcogenides (TMDCs) materials being one of the key players in this field. In order to enable 2D electronics to be integrated with conventional CMOS it is essential to achieve complementary operation of the transistors, in order to benefit from the low standby power consumption enabled by CMOS logic. In CMOS, silicon is physically doped during the fabrication process with ion implantation to create unipolar devices with Ohmic contacts. The doping process irreversibly sets the polarity of the transistors (n- or p-type) according to the dopant ions implanted in the silicon substrate (arsenic (As) for electron and phosphorus (P)) for hole doping). With the physical gate length of modern devices approaching 10 nm, ion implantation has become increasingly more complicated to control [7] [8], and fluctuations in number of dopant atoms present in the transistor channel are responsible for an increased variability of the threshold voltage of the devices [8]. In addition, ion implantation requires high temperature annealing to repair damages in the silicon and achieve proper dopant activation [9] [10] and this high temperature step is not compatible with the process for monolithic 3D-CMOS, which requires a low thermal budget.

Physical doping, through ion-implantation, of 2D material has not proven to be successful due to extreme thinness of the 2D semiconductors, with ions just implanting in the substrate. The possibility of introducing dopant atoms during growth of the 2D material as been reported, but lacks selectivity and does not allow for any control of the doping profile [11–15]. Several chemical and molecular doping techniques have been developed, but are often non-stable and non CMOS compatible, thus not allowing integration of chemically-doped 2D devices in the BEOL [16–18]. A device concept that does not rely on any physical or chemical doping, and use un-doped materials, would be of great interest in this regard.

# 1.2 Novel Materials and Devices for Future Electronic Systems

Research on innovative device concepts and novel semiconducting materials has produced an amount of results that would be impossible to summarize in a brief section of this thesis. Here, we have selected few of the most exciting concepts, as a representative class for the plethora of solutions that have been proposed for beyond-CMOS scaling. In this а b InGaAs d C All Spin Logic (ASLD) Spin Wave Device (SWD)

thesis we will focus on 2D-TMDCs, that are introduced in more depth in Ch. 2.

Figure 1.3 – Novel materials and new device concepts. (a) TEM image of an optimized high-mobility InGaAs device. Reproduced with permission from [19]. Copyright 2015 IEEE. (b) Experimental demonstration of a 3D nanosystem integrating silicon and Carbon Nano-Tubes (CNTs) electronics with resistive memories and sensors. Adapted with permission from [20]. Copyright 2017 Springer Nature. (c) Schematic illustration of a monolayer 2D-FET. Reproduced with permission from [21]. Copyright 2011 Springer Nature. (d) Proposed spin and magnetic devices for non-charge-based devices. Adapted with permission from [22]. Copyright 2015 IEEE.

**Near-term scaling** The era of equivalent scaling (see Fig. 1.2) is expected to continue until around 2025, enabled by innovative DTCO efforts and novel devices structures such as Gate-All-Around (GAA) nanowires and vertical nanowires [6]. Moreover Extreme Ultra-Violet (EUV) lithography is expected to be used for the most critical layers to reduce multi-pattern process complexity while achieving aggressive die area scaling, as shown in Fig. 1.2. Industries such as Taiwan Semiconductor Manufacturing Company (TSMC) have already invested billion of dollars in the development of the 5 nm technology node, that is expected to reach the market in 2021.

Nanomagnetic Logic (NML)

Long-term scaling For long-term scaling there is no clear path yet. Industries and research institutions are currently looking at innovations in materials, devices with both logic and memory functions, devices with lower *Sub-threshold Slope* (SS), high-performance memories beyond static random-access memory (SRAM) and dynamic random-access memory (DRAM), monolithic 3D integration of logic and memory and heterogeneous integration technologies [6]. Here we focus on the novel materials and device concepts that could provide a successful scaling beyond 2025.

- III-V materials have been extensively studied for the fabrication of *Tunnel Field-Effect Transistors* (TFETs), but the field appears to have come to a hard stop since the effect of charge-impurities at the interface between epitaxially-grown III-V materials seems to not allow the achievement of steep SS. III-V materials (see Fig. 1.3d) are however still considered for conventional devices, especially for radio-frequency applications, thanks to the high mobility of charge carriers (in particular of holes). III-V materials are not currently considered for monolithic 3D and BEOL integration, given the high temperatures needed to grow the materials and the non-feasibility of a transfer process.

- CNTs have shown great potential both for polarity-controllable applications (see Chapter 3) as well as for standard CMOS-like devices, and are still to-date one of the most promising materials for long-term scaling (> 10 years) thanks to their optimal electrostatic control, high mobility and considerable energy band-gap (see Fig. 1.3b). The recent demonstration of a 3D nanosystem that has multiple layers of CNTs logic and resistive memory and sensors stacked on a conventional CMOS die show the promise of such technology [20] (as shown in Fig. 1.4, CNTs are amongst the materials considered for BEOL integration).

- While CNTs and III-V semiconductors have been studied for over two decades the field of 2D semiconducting materials is relatively new, with the most seminal paper (the demonstration of monolayer molybdenum di-sulphide (MoS<sub>2</sub>) FETs by Radisavljevic et al. [21]) dating only to 2011 (see Fig. 1.3e). Despite the novelty of the field 2D materials have sparked high hopes and are being considered both for the fabrication of ultra-scaled CMOS-like devices, as well as for the realization of TFETs and Negative-Capacitance Field-Effect Transistors (NCFETs). Thanks to the possibility of low-temperature fabrication (see Ch. 2 for a more in depth discussion) 2D-TMDCs materials are amongst the candidates for the realization of molithically integrated BEOL transistors (as shown in 1.4).

- A completely disruptive scaling alternative would be to transition to non-charge-based electronics and use spin-, magnetic- or plasmonic-logic (see Fig. 1.3g). The selling point of such devices is the possibility of ultra-low-power and voltage applications, although several technological issues are still to be addressed [23]. A more in-depth discussion on such non-charge-based devices falls outside the scope of this thesis, and we refer the interest reader to the following publications [23–27].

Figure 1.4 – Materials considered for BEOL devices. Depending on the bandgap and mobility of the materials possible applications ranges from logic to memory and power delivery. Reproduced with permission from [6]. Copyright (2018) Spriger Nature.

#### 1.3 Multiple-Independent-Gate FETs

Multiple-Independent-Gate (MIG) FETs are a novel class of devices with multiple gate regions, that independently control the switching properties of the device. The key enabler of such concept is the exploitation and control of the inherently ambipolar behavior, also known as ambipolarity, of Schottky-Barrier (SB) FET, for the realization of doping-free devices and circuits. Ambipolarity arises in Schottky-Barrier Field Effect Transistors (SB-FETs) since the conduction property are determined by the bands alignment at the source and drain contacts, and by the gate-induced modulation of the Schottky-barriers. Both electrons and holes can be injected in the intrinsic device channel depending on the voltage applied to the gate. Ambipolarity is usually considered a drawback in standard CMOS devices, since it allows the conduction of both charge carriers in the same device, deteriorating the OFF-state of the transistor. As a result, ambipolarity is suppressed thanks to the doping process that creates strictly unipolar devices.

In MIG-FETs instead, the device polarity is not set during the fabrication process, but it can be dynamically changed thanks to the additional gate electrode (Polarity Gate (PG)), which modulates the SB at source and drain, and therefore enables to select the carrier type to inject into the channel. The transistor can then be switched ON and OFF by using the other gate electrode, namely  $Control\ Gate\ (CG)$ . This device concept does not require any ion-implantation doping, thus there is no need for the separate development of n- and p-type device, to the benefit of fabrication simplicity and device regularity. Moreover the absence of a doping step during the fabrication process eliminates the need for high-temperature dopant annealing, making the device

attractive for 3D monolithic integration. An added advantage of this class of devices is that the dynamic control of the transistor polarity enables the realization of compact operators, such as 4-transistor 2-Input Exclusive OR (XOR-2) and 3-Input Majority (MAJ-3) operators, that can be used as the building blocks to realize circuits with higher computational density with respect to CMOS. This class of devices, of core importance for the work presented in this thesis, is introduced in greater details in Ch. 3.

#### 1.4 Thesis Objectives and Achievements

This thesis was conducted in collaboration with IMEC research center in Leuven, Belgium, where all the experimental work presented here has been performed. The main objective of this thesis is to exploit a Multiple-Independent-Gate (MIG) device structure to explore doping-free polarity-controllable technologies for Two-Dimensional (2D) electronics. Since physical doping of 2D materials is still an open challenge, the realization of Complementary Metal-Oxide-Semiconductor (CMOS) logic gates on 2D semiconductors has only been achieved with the use of chemical doping and different metal contacts or using two different 2D materials for n- and p-type devices. Both methods greatly complicate the fabrication process and in the case of chemical doping make it non-scalable and non-compatible with conventional CMOS fabrication.

When no physical or chemical doping is introduced, contact to a 2D-semiconductor usually results in the creation of a Schottky barrier. Thus, the use of electrostatic doping of the contact regions, to reversibly select the polarity of the transistor, adapts perfectly to these emerging class of materials, and provides a path for the realization of CMOS logic with the use of a single 2D ambipolar semiconductor. The main achievements of this thesis are here summarized:

- The demonstration of the first polarity-controllable tungsten di-selenide (WSe<sub>2</sub>) transistor, and the first device on any 2D semiconductor to exhibit polarity-control with  $I_{ON}/I_{OFF}$  ratios greater than 10<sup>6</sup> for both polarities on the same device. This achievement is the focus of Ch. 4 and resulted in the following publications [28], [29] and [30]. The results are also featured in two book chapter dedicated to MIG devices [31] and polarity-controllable WSe<sub>2</sub> devices [32].

- The demonstration of the first logic gates realized with doping-free polarity-controllable Field-Effect Transistors (FETs) on 2D-WSe<sub>2</sub>. A complete standard-cell library (Inverter (INV), NOT-AND (NAND), NOT-OR (NOR), 2-Input Exclusive OR (XOR-2), 3-Input Exclusive OR (XOR-3) and Majority (MAJ)) is experimentally shown. This library can be the basis for conventional logic synthesis tools to map any logic functionality. These results are described in detail in Ch. 5 and resulted in the following publications [33] and [34]. The achievements described in the chapter have also been featured in an oral presentation at the 2018 Flatlands beyond graphene conference.

- The study of scaling trends and performance evaluation for polarity-controllable devices on WSe<sub>2</sub> and on low-bandgap 2D-Transition Metal Di-Chalcogenides (TMDCs). The simulations performed show a successful scaling path for low-bandgap 2D-TMDCs in the sub-10 nm dimensions. These results are described in detail in Ch. 6 and resulted in the following publication [35] and [29]. They are also featured in a book chapter dedicated to polarity-controllable WSe<sub>2</sub> devices [32].

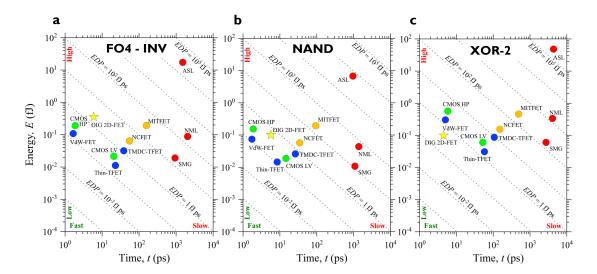

- The evaluation of the propagation delay and *Energy-Delay Product* (EDP) for a variety of logic gates that are simulated within the Sentaurus TCAD environment, using an optimized device structure. The extracted propagation delays and EDP are compared to the ones of other emerging technologies studied in BCB 3.0 [25], showing how the implementation of XOR-2 gates with 2D *Double-Independent-Gate* (DIG) FETs can provide around 10× lower EDP than any other emerging technology. These results are still unpublished.

Overall this thesis has helped to push the field of doping-free MIG in the realm of 2D electronics, providing experimental proof-of-concepts devices and demonstrating a library of doping-free logic gates, as well as accurate simulations assessing the performances of ultra-scaled transistors and logic gates. The work presented has also contributed to the IMEC beyond-CMOS core program and has been presented at the internal *Partner Technical Week* (PTW), where IMEC core partners (such as Intel, Samsung, Global Foundries, TSMC, etc...) are updated on the recent results achieved at IMEC.

### 1.5 Thesis Organization

This thesis is organized as follows:

- Chapter 2 TMDCs for 2D Electronics This chapter introduces TMDCs and gives a broad overview of the recent advances in the research field, spanning from growth to 2D electronics. Finally it focuses on the importance of ambipolarity for polarity-controllable devices.

- Chapter 3 Multiple Independent Gate Devices In this chapter we introduce the concept of MIG and review the state-of-the-art of the research field. We describe the basic opration principle of MIG devices and show how they have been realized on silicon and on novel materials that are of interest for beyond-CMOS electronics. We finally introduce the circuit-level advantages that are enabled by the use of MIG transistors.

- Chapter 4 Polarity-Controllable WSe<sub>2</sub> FETs This chapter presents the original research work conducted on 2D-WSe<sub>2</sub> and focuses on the demonstration of the first WSe<sub>2</sub> polarity controllable devices. The fabrication process of the devices is described in detail and the full characterization of the experimental devices is presented.

- Chapter 5 Doping-Free WSe<sub>2</sub> Logic Gates This chapter in combination with Ch. 4 forms the backbone of this thesis and describes the demonstration of first polarity-controllable doping-free logic gates fabricated on WSe<sub>2</sub>. We first review the fabrication process of the devices and the improvements made with respect to the transistors presented in Ch. 4 and then focus on the characterization of the demonstrated logic gates (INV, NAND, NOR, XOR-2, XOR-3 and MAJ), creating a complete standard-cell library for use in logic synthesis tools.

- Chapter 6 Scaled Devices and Logic Gates Simulations This chapter is dedicated to the simulation study of scaled polarity-controllable devices and logic gates. To estimate the electrical characteristics of such ultra-scaled devices, we first use ballistic self-consistent quantum simulations in the Non-Equilibrium Green Function (NEGF) formalism. We explore scaling for devices based on WSe<sub>2</sub>, the most promising material for which experimental results are available (as shown in Ch. 4 and Ch. 5), and then focus on the selection of novel 2D semiconductors, for which experimental demonstrations are still lacking, to enhance the performances of the device. Finally, in order to study the performances of logic gates we develop a Sentaurus TCAD simulation that is able to reproduce the switching characteristics simulated with the quantum-transport simulations and perform transient simulations for the logic gates switching.

- Chapter 7 Conclusions and Future Perspectives Finally, this last chapter is

dedicated to concluding this thesis and highlight future perspectives for 2D-TMDCs

and polarity-control.

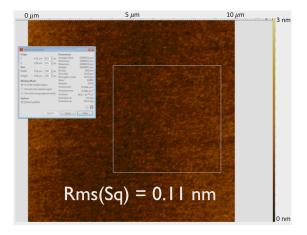

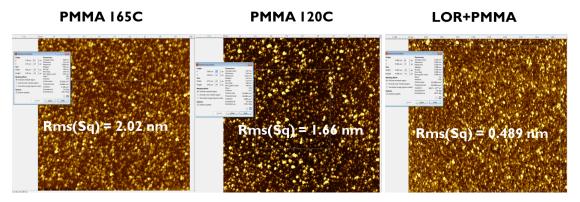

- Appendix The appendix of this thesis provide additional insight in the fabrication and characterization of the polarity-controllable devices and logic gates. In Appendix A we show the steps that are needed to properly clean the dielectric surface before exfoliation, as well as the flakes, after they have been exfoliated or transferred. In Appendix B we report other measurements on different WSe<sub>2</sub> flakes that strengthen our claims regarding the effect of contact annealing presented in Section 4.2. Finally, in Appendix C, we describe the effect of oxide encapsulation, that was studied in order to realize top-gated devices, on the ambipolar characteristics of WSe<sub>2</sub> devices.

## TMDCs for 2D Electronics

There is plenty of room at the bottom

— Lecture at Caltech, 1959

Richard Feynman

This thesis targets the development of doping-free polarity-controllable devices fabricated with Two-Dimensional (2D) Transition Metal Di-Chalcogenides (TMDCs). Atomically-thin 2D materials belonging to the TMDCs family are, thanks to their physical and electrical properties, an exceptional vector for the exploration of next-generation semi-conductor devices. Research on 2D materials has experienced remarkable growth in the last decade. Major semiconductor companies are looking with interest at this novel class of materials in the hope of addressing the shortcomings that are making scaling of silicon-based electronic devices increasingly difficult. Among TMDCs, thanks to the possibility of ambipolar conduction, tungsten di-selenide (WSe<sub>2</sub>) provides a platform for the efficient implementation of Multiple-Independent-Gate (MIG) polarity-controllable transistors (that will be introduced in Ch. 3).

This chapter is dedicated solely to 2D-TMDCs and aims at giving a broad overview of the research field, and the progresses that have been made in recent years, spanning from growth in Sec. 2.2 to 2D-electronics in Sec. 2.3. Finally in Sec. 2.4 we focus on the ambipolar properties of certain 2D materials, that will be a key feature of the devices studied in this thesis.

## 2.1 Material Properties

Despite the diversity in conduction properties and atomic composition, all 2D materials are composed by covalently-bonded in-plane layers that are held together by weak Vander-Waals interactions to form a 3D crystal. Each layer has a uniform thickness ranging from 0.3 to 0.7 nm, depending on the atomic structure of the layer, with the thinnest material being graphene, which is composed by a single layer of carbon atoms. A TMDCs layer with general formula MX<sub>2</sub>, is composed by a transition metal (M) of group IV, V

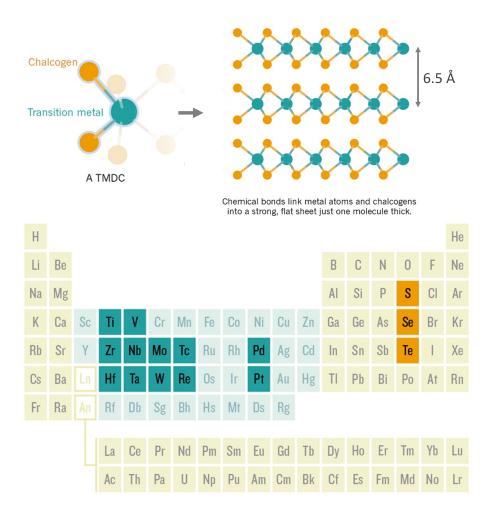

**Figure 2.1** – The transition-metal di-chalcogenide family. Reproduced with permission from [36]. Copyright 2015 Springer Nature.

or VI, such as molybdenum (Mo), tungsten (W), hafnium (Hf), etc., sandwiched between two chalcogen atoms (X), such as sulfur (S), selenium (Se) or tellurium (Te) [37,38]. The composition of a generic MX<sub>2</sub> material is shown in Fig. 2.1. The weak Van-der-Waals interaction are present in the out-of-plane direction thanks to the pristine surface of each layer, i.e. presence of no dangling bonds. The peculiar layered structure of graphite and of TMDCs was already known in the early 1970's, and certain optical and electrical properties had already been discovered [37,38]. It wasn't however until the pioneering work of Novoselov et al. in 2004 that a graphite monolayer (now commonly know as graphene) was isolated and studied [39], effectively marking the beginning of 2D electronics. However, the semimetallic nature of graphene prevents it to be used as the primary vehicle for novel digital transistors and circuits. Amongst TMDC materials, the ones formed by group VI (Mo and W) and group IV (Zr and Hf) metals show a semiconducting behaviour and have exhibited excellent electrical properties [40–42], that

will be further analyzed in Sec. 2.3. The presence of a sizeable bandgap (1-2 eV) makes TMDCs materials appealing for electronics applications, as it allows us to realize devices with low leakage floor and high ON/OFF current ratios [17,18,43,44]. Amongst the other

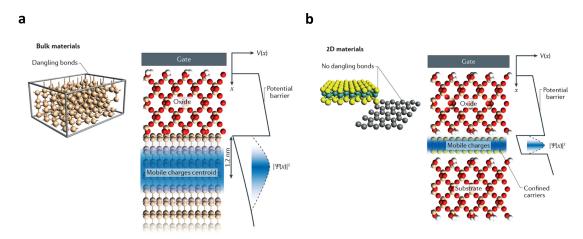

Figure 2.2 – Benefit of 2D-TMDCs for electronic applications. (a) Case of a bulk material. (b) Case of a 2D material. Adapted with permission from [45]. Copyright 2016 Springer Nature.

remarkable features of TMDCs, their layered structure provides 2D films of controllable uniform thickness with dangling-bonds free interfaces. Moreover, their extreme thinness enables optimal electrostatic control and carrier confinement (see Fig. 2.2). The low in-plane dielectric constant alleviates Short-Channel Effects (SCE) and Drain-Induced Barrier Lowering (DIBL) [46,47] which are detrimental to device performances. The high effective mass of charge carriers (especially with respect to III-V materials) helps reducing direct source-to-drain tunneling at ultra-scaled dimensions [48,49] providing a better control of the device OFF-state by the gate terminals. 2D materials are also attractive for monolithic integration on top of Complementary Metal-Oxide-Semiconductor (CMOS) or multi-stacking of TMDCs layers [50], thanks to the low thermal budget needed in the fabrication process. Moreover several semiconducting TMDCs show a transition between an indirect few-layer bandgap to a direct monolayer band-gap, thus enabling the possible use of these monolayers for optoelectronics applications [41, 51]. Beyond their use in established transistor architectures, 2D TMDCs can be used to form heterostructures that present interesting physical phenomena, such as tightly bound excitons [52,53] and plasmonic effects [54,55], which can lead to new device concepts for future electronics.

## 2.2 Synthesis and transfer of 2D TMDCs

The first demonstrations of novel devices based on 2D semiconductors were carried out mainly thanks to the exfoliation technique originally developed for graphene [56]. Although this top-down technique allows for the production of high quality thin flakes, with dimensions as big as tens of microns, this method is not scalable, does not allow

any systematic control of the flake size and thickness and makes the fabrication much more challenging. In order to enable the creation of a reliable technology based on 2D-TMDCs, that would go beyond the simple demonstration of few working devices, it is essential to develop bottom-up methods for the productions of large-area, defect-free, atomically thin films with uniform electrical, optical and structural properties. Current methods for the growth of TMDCs materials are based on *Chemical Vapor*

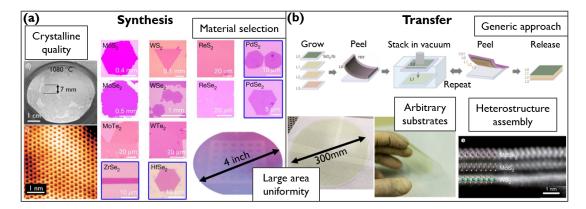

Figure 2.3 – Relevant metrics for synthesis and transfer of 2D materials. (a) Crystalline quality and wide material selection are important to allow high performance devices. (b) Transfer is a generic approach to allow integration in arbitrary substrates or assembly of heterostructures. Large area uniformity is essential to both synthesis and transfer, to allow low variability in material properties over wafer scales. Adapted with permission from [57–62].

Deposition (CVD) [63–72], Van der Waals epitaxy [73,74] and Metal-Organic Chemical Vapor Deposition (MOCVD) [50]. These techniques have shown promising results for mono(few)-layer MoS<sub>2</sub> [50,63–65,67,68,74], WSe<sub>2</sub> [70–72,75], WS<sub>2</sub> [50,66] and for the creation of 2D heterostructures [69,70] that researchers are exploring for the realization of efficient Tunnel Field-Effect Transistors (TFETs). Basic operational circuits [63,76] have been demonstrated on CVD grown MoS<sub>2</sub> and single devices have shown gigahertz radio frequency performances [67] combined with high current densities, exceeding 200  $\mu$ A/ $\mu$ m, and intrinsic low-field mobility up to 55 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>. Multilayer WSe<sub>2</sub> grown by CVD using graphene as seed material has shown p-type mobility higher than 80 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, when using oxygen as doping material [72]. Recently uniform growth of monolayer MoS<sub>2</sub> and WS<sub>2</sub> has been demonstrated [50] on a 4-inch wafer, using MOCVD, with a resulting device yield of 99%. However, this process has the downside of being very time consuming (26 hours needed to grow a uniform 4-inch monolayer).

Fig. 2.3a presents relevant metrics for synthesis of 2D materials, namely the crystalline quality (e.g. grain size) of the grown layers, the possibility of growing a number of different materials and the large area uniformity of the synthetic layer. Two main synthesis approaches exist, first growth directly on the device wafer, as often done for TMDCs [57, 59, 77], and second, the growth on an optimized growth substrate,

such as metal films for graphene [58,78] or hexagonal-Boron Nitride (hBN) [79] and sapphire for TMDCs [80,81], with a subsequent transfer step [60,82] for integration. Direct growth is limited by the maximum temperature allowed at different process steps, specially when 2D materials are co-integrated with a standard silicon CMOS technology. However, if growth is limited at 450° C, for back-end-of-the-line (BEOL) integration, the resulting material, in particular 2D TMDCs, is highly defective [83,84]. Besides prohibitive temperatures, the growth environment (corrosive or metal-containing gases) can also result in lower reliability of the dielectric where the 2D material is grown. When using a dedicated growth substrate, the temperature limitations are lifted, which allows this approach to achieve high crystalline quality [78,80]. The growth substrate can be carefully selected and tailored to achieve the best possible synthesis, where layer-by-layer growth has been demonstrated with precise atomic control and reduction of strain and doping effects [85].

This temperature flexibility comes at the expense of an additional transfer step, which decouples the growth parameters from the device integration. Transfer allows high quality 2D materials to be integrated onto arbitrary substrates, which ranges from standard CMOS wafers (either in the Front-End-Of-the-Line (FEOL) or Back-End-Of-the-Line (BEOL)) to flexible substrates [60]. It is, in principle, a generic approach, which allows the manipulation of different 2D materials with the same method [62]. In the context of logic devices, uniform transfer of large area 2D materials is a key challenge. Transfer relies on interface interactions between the original substrate, 2D material, and the target wafer, and is normally done using water or acid assisted intercalation [60, 82, 86, 87]. Understanding those interactions and being able to develop an all-dry process is critical to achieve uniform and repeatable transfer which has minimal impact on the 2D material. By allying 300 mm growth capabilities with standard wafer bonding tools, a uniform 300 mm dry transfer was recently reported [61]. Fig. 2.3b illustrates the transfer process, with notable examples of each of these metrics. Besides transferring the 2D materials onto arbitrary substrates, understanding the interactions present after transfer and the impact of different substrates is also necessary. During this integration step, the 2D material is transferred onto a wafer surface, which may have a series of non-idealities such as roughness, surface chemistry, contamination, among others. Due to the atomically thin nature of the 2D material, it is highly sensitive to the surrounding environment, and these non-idealities can cause unintentional doping, strain and increased defectivity. This surface must be carefully engineered in order to result in stable and reliable transistor operation. Current understanding is that other 2D materials are the ideal substrates for both graphene and TMDC devices [88–90].

## 2.3 Experimental State-of-the-Art in 2D Electronics

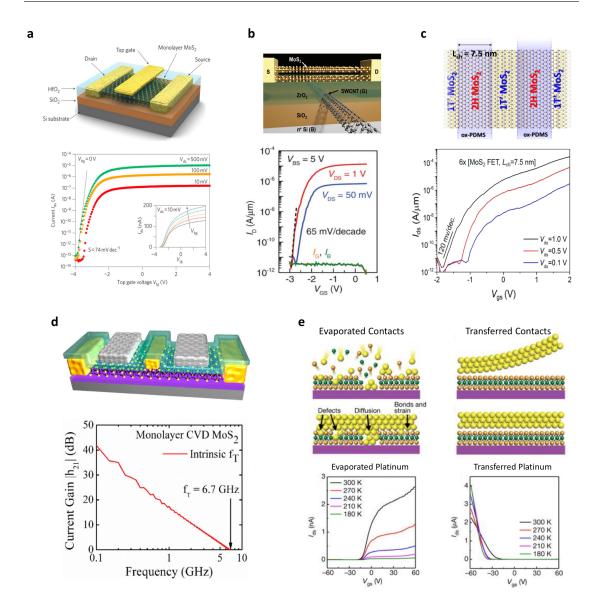

Since the first demonstration of a Mono-Layer (1L)  $molybdenum\ di-sulphide\ (MoS_2)$  transistor with high mobility and high ON/OFF current ratios in 2011 by Radisavljevic

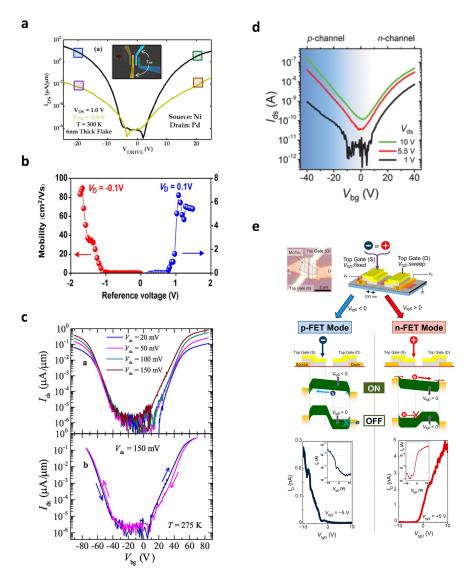

Figure 2.4 – 2D-MoS<sub>2</sub> electronics. (a) Adapted with permission from [21] (b) Adapted with permission from [91]. (c) Adapted with permission from [92] (d) Adapted with permission from [67]. (e) Adapted with permission from [93]

et al. [43] (see Fig. 2.4a) the field of 2D electronics has gained worldwide traction with a constant increase in the number of publications and a growing interest of the research community. Among the several semiconducting materials belonging to the TMDCs family, and introduced in Sec. 2.2, the most appealing for electronic application have been Molybdenum (MoS<sub>2</sub>, molybdenum di-telluride (MoTe<sub>2</sub>) and molybdenum di-selenide (MoSe<sub>2</sub>)) and Tungsten compounds (WSe<sub>2</sub> and tungsten di-sulfide (WS<sub>2</sub>)). These semiconducting materials are stable in air, even in their monolayer form, are easily exfoliated from commercially available bulk-crystal and are also grown with high-quality in large-area, as shown in Sec. 2.2. Several major results presented in the

following sections have been achieved using mechanical exfoliation, which, despite being a non-scalable approach, provides high-quality flakes that are used to gain insights on the properties of these materials and assess their potential for electronic applications. The most known TMDC material, MoS<sub>2</sub>, has proven to be a viable solution for the realization of n-MOS transistors [43,44,94–96] and ultra-scaled devices have been recently demonstrated [91, 92, 97] (see Fig. 2.4(b,c)). In Fig. 2.4b a single carbon nanotube was used to gate a transistor with MoS<sub>2</sub> semiconducting channel, proving the superior electrostatic control achievable thanks to the ultra-thin MoS<sub>2</sub> [91]. In Fig. 2.4c devices with gate length below 10 nm were realized by inducing a metallization of the MoS<sub>2</sub> with a lithium solution. This process also allows for a reduced contact resistance thanks to the metallic MoS<sub>2</sub> forming a seamless contact scheme with the 3D metal [98]. High-frequency operation of CVD-grown MoS<sub>2</sub> has also been reported, see Fig. 2.4d. To date, the largest circuit reported on 2D MoS<sub>2</sub> is a 1-bit microprocessor composed of 115 transistors [76], and other small circuits have also been previously demonstrated [44, 63, 94]. However, due to considerable difficulties in achieving p-type behavior in  $MoS_2$  [99] all these circuits adopt a non-complementary n-MOS logic, that is not power-efficient. It has recently been demonstrated how p-type conduction can be achieved on  $MoS_2$  by transferring metal contacts on top of the 2D material, rather than evaporating it [93]. Using this innovative technique it has been possible to show an almost linear relationship between the work function of the contact metal and the height of the Schottky barrier created, and p-type conduction has been achieved with high work function metals (such as gold (Au) and platinum (Pt)).

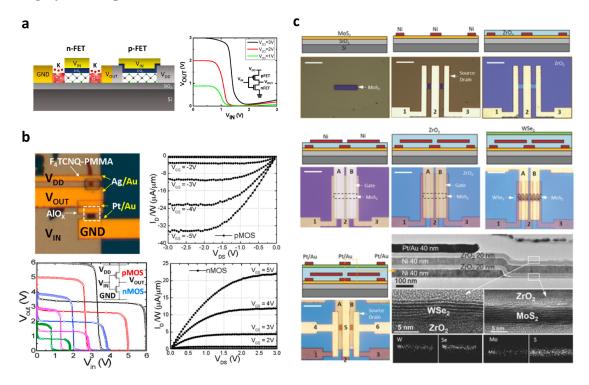

Being able to develop both n- and p-type devices on the same semiconducting material is extremely important in order to achieve complementary operation of logicgates and circuits (see Fig. 2.5). Conventional CMOS uses ion implantation to physically dope silicon creating low-resistance ohmic contacts and irreversibly setting the polarity of the fabricated device (n- or p-type) according to the dopant atoms used (arsenic (As) for electron and *phosphorus* (P) for hole doping). Since a reliable physical doping technique for 2D materials is still lacking, chemical doping techniques have been explored to both reduce contact resistance (thus achieving higher ON-current) and to realize complementary behavior [16–18, 72, 100, 101]. Using WSe<sub>2</sub> as semiconducting material complementary operations of inverters and other small logic gates has been recently shown (see Fig. 2.5(a,b)) [17,18]. However, chemical doping is often non-scalable, non-stable and non-compatible with conventional CMOS fabrication. An innovative doping strategy has recently been proposed where a strong light source is used to locally create defects in MoTe<sub>2</sub> semiconducting channels, that upon oxidation induce p-type doping [102]. This technique has allowed the realization of photovoltaic cells and Bipolar-Junction Transistor (BJT) arrays [102]. The possibility of using two separate 2D semiconductors to separately develop n- and p-type transistors has been explored in [103], that have used  $MoS_2$  to fabricate n-MOS device and monolithically integrate  $WSe_2$  p-type devices on top, demonstrating complementary logic gates. This work shows the potential of 2D materials to be used in combination with CMOS for 3D monolithic integration, as

displayed in Fig. 2.5c.

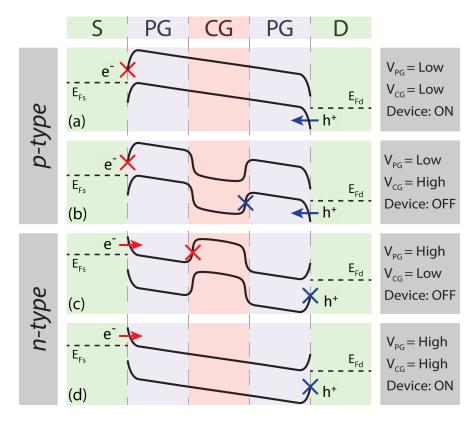

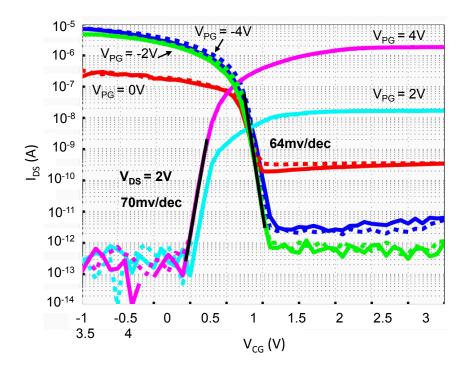

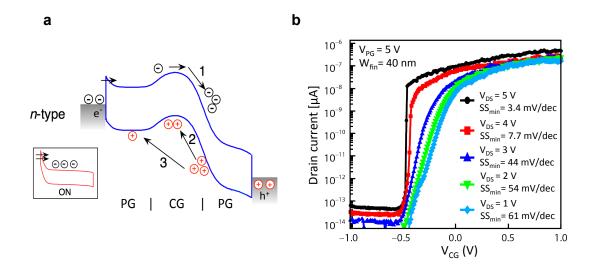

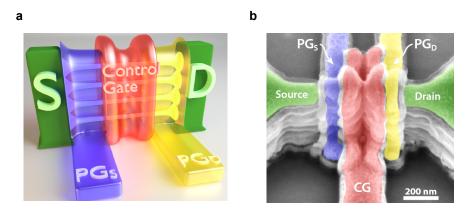

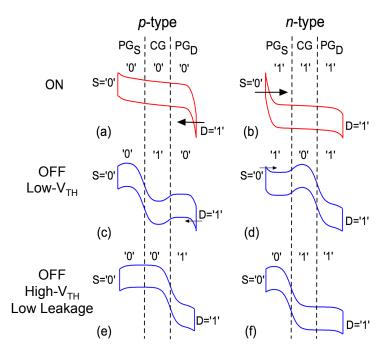

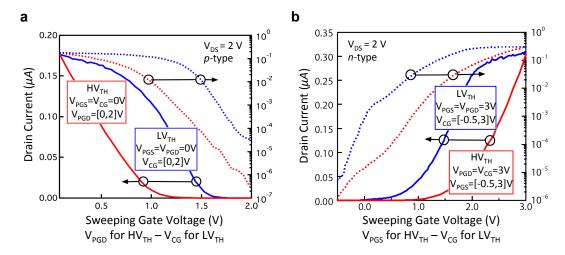

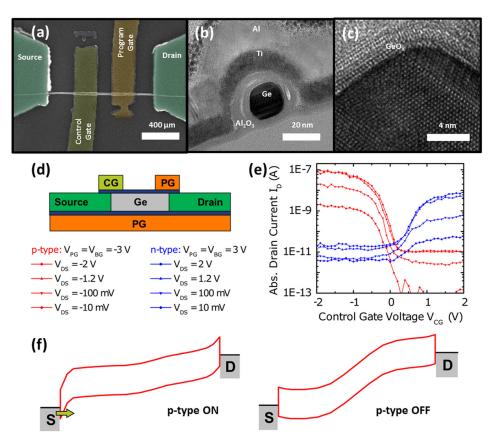

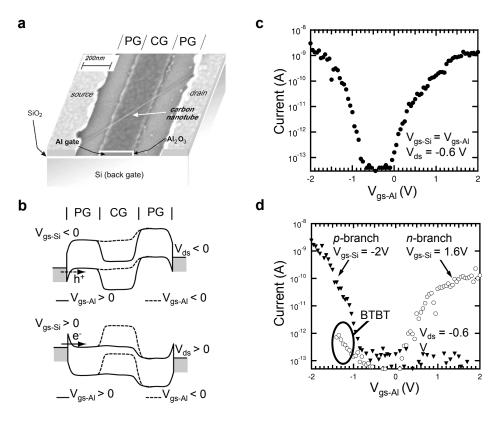

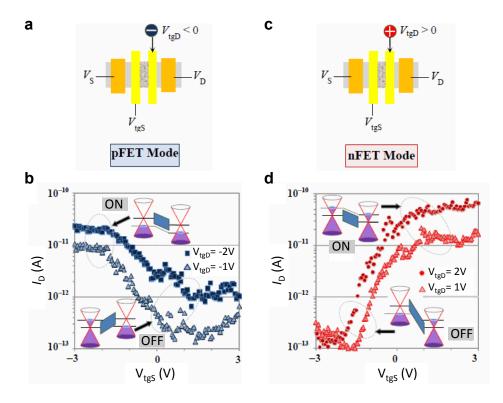

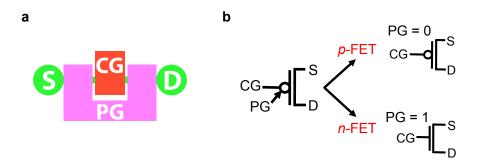

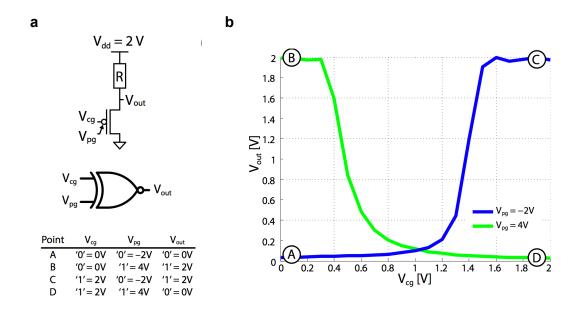

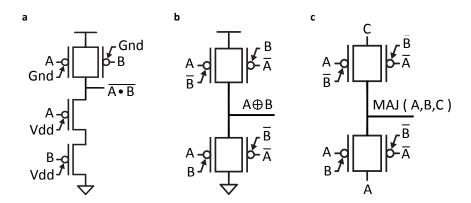

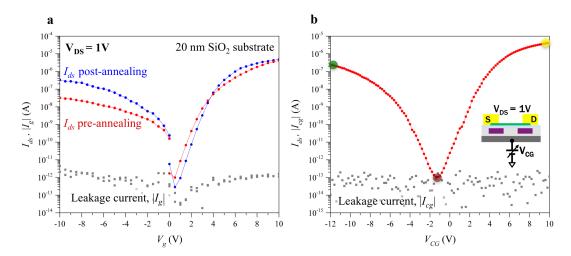

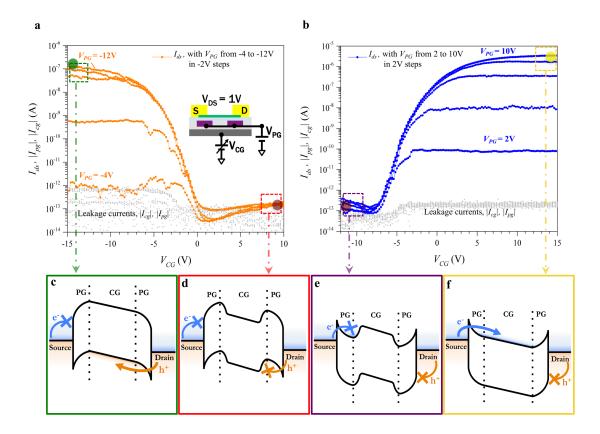

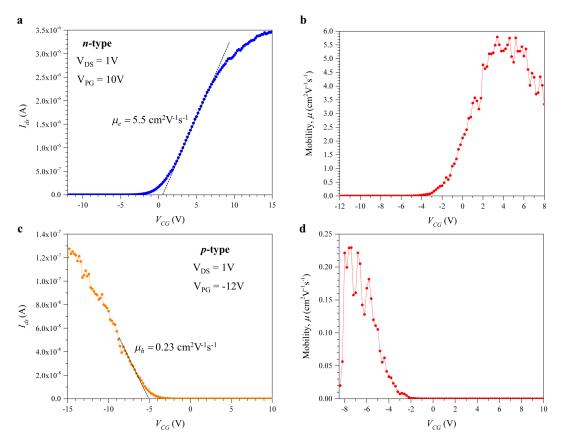

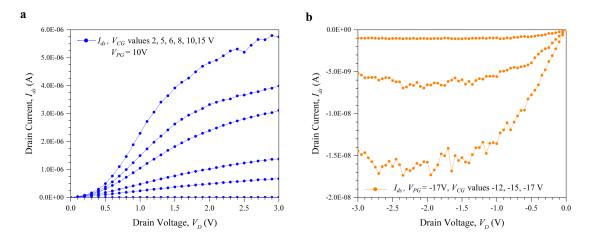

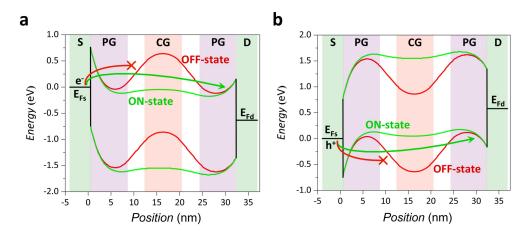

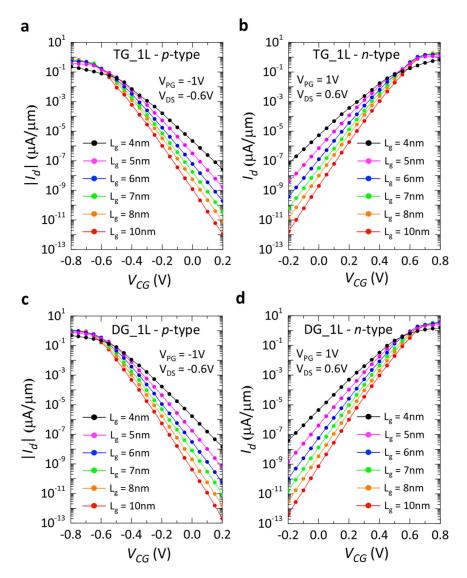

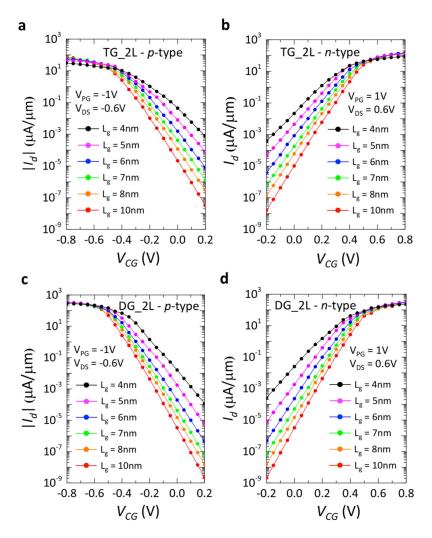

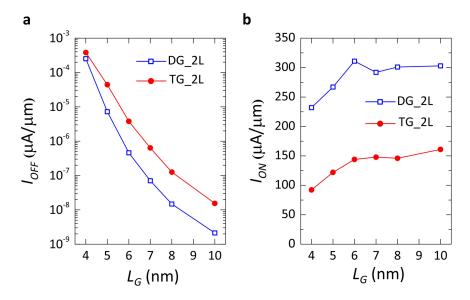

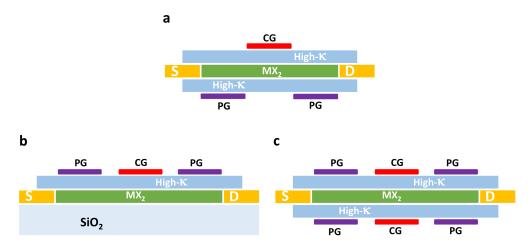

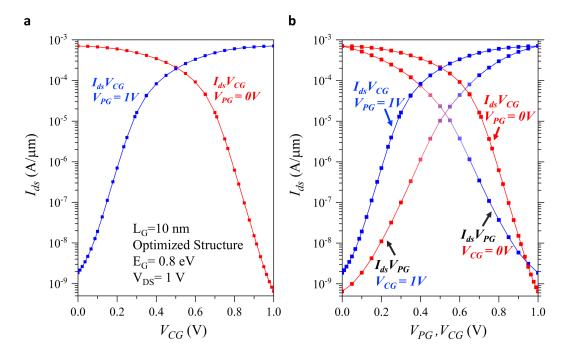

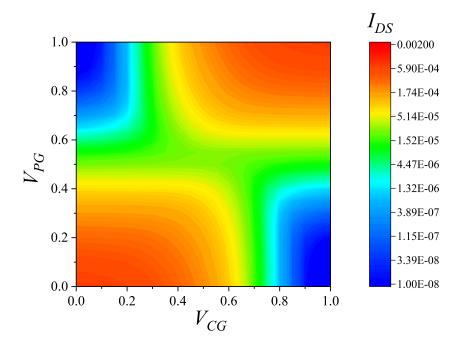

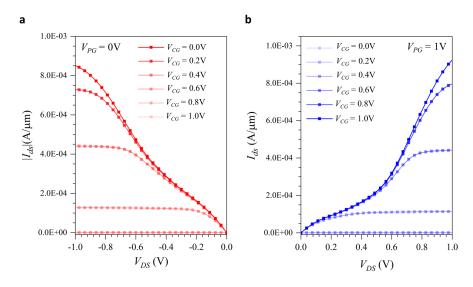

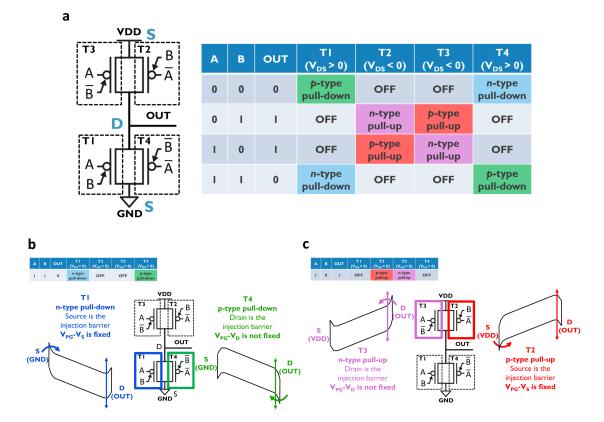

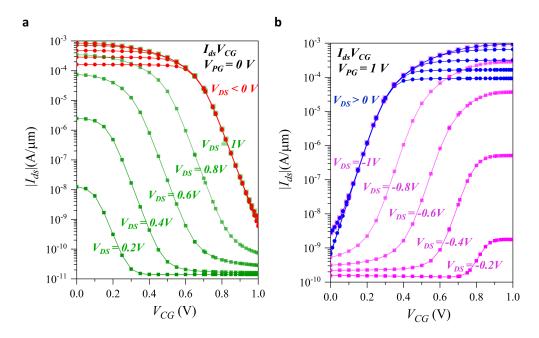

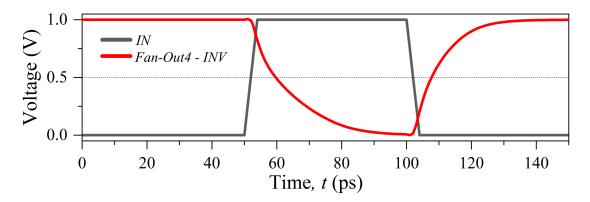

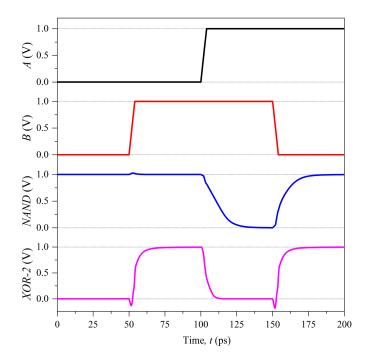

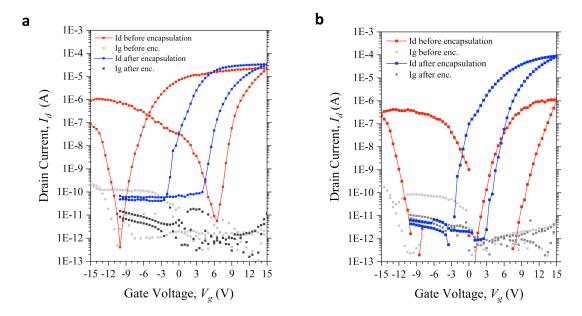

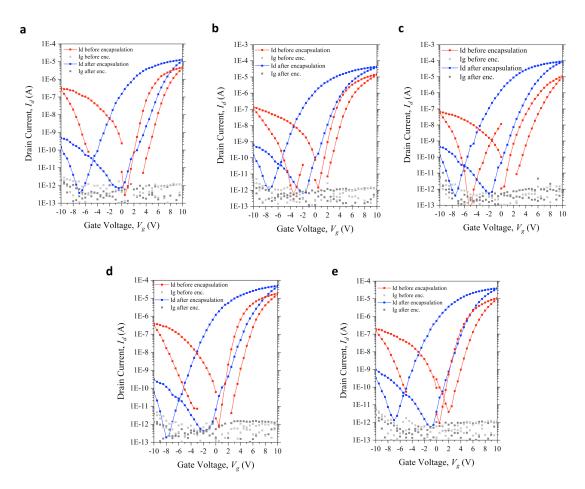

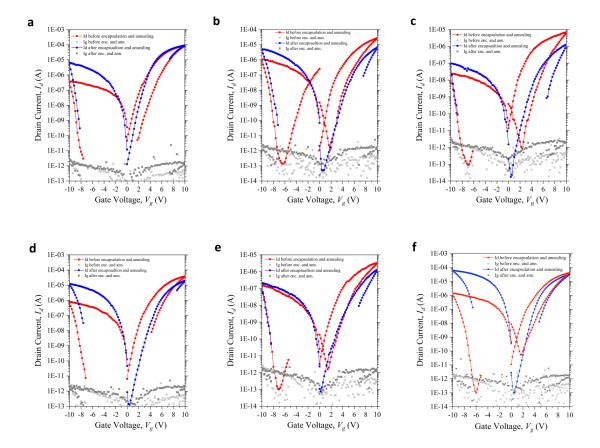

Figure 2.5 – Complementary devices on 2D materials. (a) Schematic depiction of the fabricated WSe<sub>2</sub> inverter with chemically-doped contacts for *n*-type Field-Effect Transistor (FET) and measured device characteristics. Notice the different contact metal used (Gold and Platinum) for the *n*- and *p*-type FET respectively. Reprinted with permission from [17]. Copyright 2015 American Chemical Society. (b) Complementary devices realized on WSe<sub>2</sub> with different metal contacts for *n*- and *p*-type and stable chemical doping. Output characteristics and inverter behavior. Reprinted with permission from [18]. Copyright 2015 American Chemical Society. (c) Fabrication process for monolithically integrated 2D logic gates. NAND, NOR and INV are demonstrated with the use of MoS<sub>2</sub> for *n*-type and WSe<sub>2</sub> for *p*-type. Reprinted with permission from [103]. Copyright 2016 John Wiley and Sons.