#### **Exploration of Negative Capacitance Devices and Technologies**

Thèse N°9340

Présentée le 21 juin 2019

à la Faculté des sciences et techniques de l'ingénieur Laboratoire des dispositifs nanoélectroniques Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

#### Ali SAEIDI

Acceptée sur proposition du jury

Prof. G. De Micheli, président du jury Prof. M. A. Ionescu, directeur de thèse Prof. L.-E. Wernersson, rapporteur Prof. S. Salahuddin, rapporteur Prof. C. Enz, rapporteur

Do the difficult things while they are easy and do the great things while they are small. A journey of a thousand miles must begin with a single step.

— Lao Tzu

To my parents...

### Acknowledgements

It would not have been possible to write this doctoral thesis without the help and support of the kind people around me, to only some of whom it is possible to give a particular mention here.

My deepest thanks go to my thesis advisor Professor Adrian Ionescu for providing me this unique opportunity of working in NANOLAB of EPFL as well as his kind supervision during my Ph.D. work, which allowed me to gain insights in the scientific approach and research in a fascinating environment.

A special thanks to Dr. Igor Stolichnov and Dr. Montserrat Fernandez-Bolanos for their scientific advice and helping me whenever I needed. Without them, this work would not have been possible.

My family in Iran, my father, my mother, and my brothers. I want to thank for their support in any direction and for always being there for me even from distance for the last four years.

I am grateful to all the members of the NANOLAB for making me feel very welcome in the group and helping me a lot during all steps of my work. Special thanks to Isabelle Buzzi and Karin Jaymes not only for all the administrational guidance but also for her support and kindness making everything much simpler. Thanks to Arnab Biswas and the technical staff of Center of MicroNanoTechnology for their immense patience in teaching me and guiding me through the experiments. And my thanks to all my great colleagues, Huel, Emanuele, Nicolo, Francesco, Fatemeh, Maneesha, Erik, Teodor, Andrei, Matteo, Junrui, Wolfgang, Mariazel, and Carlotta.

Last but not least, many thanks to all friends for calming me down when I was in doubt and despair. Especially Sogol, Amir, Mohammadreza, Soroosh, Nastaran, Fatemeh, Morteza and countless others who are my biggest support and deserves my greatest gratitude.

Lausanne, 11 Jan 2019

Dr. Ali!

### Abstract

Conventional device scaling has been the main guiding principle of the MOS device engineering over these past years. However, this aggressive scaling would be eventually limited due to the inability to remove the heat generated by MOSFET devices. The power dissipation would be lowered significantly if FETs could be operated at lower voltages, which is in contrast with having a sufficiently high on-current. In that pursuit, it was proposed that the minimum voltage requirement could be overcome if the ordinary gate oxide could be replaced by another stack that provides an effective negative capacitance (NC). For a MOSFET, a negative capacitor in the gate stack can make the total capacitance, looking into the gate, larger than the classical MOS capacitance. Thus, to induce the same amount of charge in the channel, one would require a smaller voltage than what would be needed classically. It is well established that ferroelectric materials can provide an effective NC in a certain range of polarization.

The objective of this thesis is to study the negative capacitance effect of ferroelectrics on the performance of field-effect transistors. For this purpose, various NC-FETs and NC-TFETs have been designed and characterized. First, this work proposes a matching condition between the ferroelectric's NC and the gate intrinsic capacitance of the reference transistor to ensure the maximum enhancement due to the NC effect as well as optimizing the hysteretic behavior. Afterward, based on the proposed condition, hysteretic, low hysteresis, and non-hysteretic NC-FETs using 28 nm CMOS node planar MOSFETs and FD-SOI FETs are experimentally demonstrated. In another device structure, the impact of the ferroelectric NC on TFETs is investigated and discussed. It is validated that by combining the advantages of band-to-band tunneling as the carrier injection mechanism and the NC of ferroelectrics, it is possible to obtain steep slope energy efficient switches with improved analog and digital performances. Novel InAs/InGaAsSb/GaSb nanowire TFETs and InGaAs planar TFETs are employed as the reference transistors. The potentials of the recently proposed CMOS compatible ferroelectric, silicon-doped HfO<sub>2</sub>, as the NC booster is investigated. The results show that further engineering and advancement is required to optimize the leakage and remanent polarization of this type of ferroelectrics. This work also suggests that a ferroelectric TFET using Si:HfO<sub>2</sub> can be considered as an energy efficient 1T memory that can be scaled down to sub-100 nm technology nodes. Overall, this Ph.D. work highlights and validates the potentials of ferroelectric field-effect transistors for both steep slope and memory applications.

### Résumé

La miniaturisation conventionnelle des dispositifs a été le principe directeur principal de l'ingénierie des dispositifs MOS au cours de ces dernières années. Cependant, cette miniaturisation agressive serait finalement limitée en raison de l'impossibilité d'éliminer la chaleur générée par les transistors à effet de champ à grille isolée (MOSFET). La dissipation énergétique serait considérablement réduite si les transistors à effet de champ (FET) pouvaient fonctionner à des tensions plus basses, ce qui rentre en contradiction avec l'obtention d'un courant 'On' suffisamment élevé. Dans cette optique, il a été hypothétisé la possibilité de surmonter cette exigence de tension minimale en remplaçant l'oxyde de grille ordinaire par un autre empilement de matériaux fournissant une capacité négative effective (NC). Pour un MOSFET, un condensateur négatif dans l'empilement de la grille peut rendre la capacité totale, en regardant dans la grille, plus grande que la capacité MOS classique. Il faudrait ainsi une tension inférieure à celle qui serait nécessaire de manière classique pour induire la même quantité de charge dans le canal. Il est bien établi que les matériaux ferroélectriques peuvent fournir une NC effective dans une certaine plage de polarisation. L'objectif de cette thèse est d'étudier l'effet de capacité négative des ferroélectriques sur les performances des transistors à effet de champ. À cet effet, divers NC-FET et NC-TFET ont été conçus et caractérisés. Dans un premier lieu, ce travail propose une condition d'adaptation entre la NC du ferroélectrique et la capacité intrinsèque de la grille du transistor de référence pour assurer une amélioration maximale découlant de l'effet de NC ainsi qu'une optimisation du comportement hystérétique. Dans un second lieu, sur la base de la condition proposée, des NC-FET hystérétiques, peu hystérétiques, et non hystérétiques utilisant des MOSFET planaires dans un nœud CMOS de 28 nm et des FD-SOI FET sont expérimentalement démontrés. Dans une autre structure de dispositif, l'impact de la NC ferroélectrique sur les FET à effet tunnel (TFET) est étudié et discuté. On prouve qu'en combinant les avantages de l'effet tunnel bande à bande en tant que mécanisme d'injection de porteurs de charge et la NC des ferroélectriques, il est possible d'obtenir des commutateurs à forte pente à haute efficacité énergétique offrant de meilleures performances analogiques et numériques. De nouveaux TFET basés sur des nanofils de InAs/InGaAsSb/GaSb et des TFET planaires de InGaAs sont utilisés comme transistors de référence. Le potentiel du HfO2 dopé au silicium, récemment proposé comme ferroélectrique compatible avec la technologie CMOS, en tant qu'amplificateur de NC est étudié. Les résultats montrent que plus d'ingénierie et de progrès sont nécessaires afin d'optimiser les fuites et la polarisation rémanente de

#### Résumé

ce type de ferroélectriques. Ce travail suggère également qu'un TFET ferroélectrique utilisant du Si : $HfO_2$  peut être considéré comme une mémoire 1T à basse consommation énergétique pouvant être miniaturisée à des nœuds technologiques inférieurs à 100 nm. Globalement, ce travail de doctorat met en évidence et valide le potentiel des transistors à effet de champ ferroélectriques pour les applications de commutateurs à forte pente et de mémoire.

### Acronyms

AC Alternate Current

AFM Atomic Force Microscopy

BHF Buffered Hydrofluoric acid

CMOS Complementary Metal-Oxide Semiconductor

DC Direct Current

FET Field-Effect Transistor

MOSFET Metal Oxide Semiconductor Field-Effect Transistor

GND Ground

IC Integrated Circuit

LTO Low Thermal Oxide

MEMS Micro Electro Mechanical System

MIS Metal Insulator Semiconductor

NEMS Nano Electro Mechanical System

NVM Non Volatile Memory

PZT Lead Ziconate Titanate

RT Room Temperature

SEM Scanning Electron Microscopy

SOI Silicon On Insulator

FD-SOI Fully Depleted Silicon On Insulator

TEM Transmission Electron Microscopy

VLSI Very Large Scale Integration

SBT Strontium Bismuth Tantalate

$Si:HfO_2$  Silicon-doped  $HfO_2$

## Units of measurements

- $^{o}\mathrm{C}$  Celsius degree

- A Ampere

- C Coulomb

- eV electron Volt

- J Joule

- <sup>o</sup>K Kelvin degree

- kg Kilogram

- m Meter

- N Newton

- s Second

- V Volt

- W Power

- $\Omega \quad \text{Ohm} \quad$

# SI decimal prefixes

```

\mathbf{10}^{12}

Tera

{f T}

\mathbf{G}

\mathbf{10}^{9}

Giga

10^6

Mega

\mathbf{M}

10^3

kilo

\mathbf{10}^2

hecto

\mathbf{h}

\mathbf{10}^{1}

Deca

da

1

10^{-1}

\mathbf{deci}

10^{-2}

centi

10^{-3}

milli

10^{-6}

micro

10^{-9}

nano

10^{-12}

pico

10^{-15}

\mathbf{f}

femto

```

## Physical constants

```

\begin{array}{llll} \text{Elementary Charge} & e \; (\text{or} \; q) & = 1.60206 \times 10^{-19} \; \text{C} \\ \\ \text{Planck Constant} & h & = 6.62606896 \times 10^{-34} \; \text{J.s} \\ \\ \text{Boltzmann Constant} & k_B & = 8.617343 \times 10^{-5} \; \text{eV.K}^{-1} \\ \\ \text{Free Space Permittivity} & \epsilon_0 & = 8.85418782 \times 10^{-12} \; \text{F.m}^{-1} \\ \\ \text{Air Relative Permittivity} & \epsilon_r & = 1 \\ \\ \text{Speed of Light} & c & = 2.99792458 \times 10^8 \; \text{m.s}^{-1} \\ \\ \text{Number Pi} & \pi & = 3.14159265 \\ \end{array}

```

## Contents

| A                | cknov  | vledge  | ements                                          | V    |

|------------------|--------|---------|-------------------------------------------------|------|

| $\mathbf{A}$     | bstra  | ct (En  | nglish/Français)                                | vi   |

| A                | crony  | ms      |                                                 | xi   |

| $\mathbf{U}_{1}$ | nits o | of mea  | surements                                       | xiii |

| $\mathbf{SI}$    | deci   | mal p   | refixes                                         | xv   |

| Ρl               | hysica | al cons | stants                                          | xvii |

| $\mathbf{Li}$    | st of  | figure  | $\mathbf{s}$                                    | xxi  |

| Li               | st of  | tables  |                                                 | xxvi |

| 1                | Intr   | oducti  | ion                                             | 1    |

|                  | 1.1    | CMOS    | S scaling and MOSFET limitations                | 2    |

|                  | 1.2    | Conce   | pt of ideal switch                              | 8    |

|                  | 1.3    | Small   | swing switches                                  | S    |

|                  |        | 1.3.1   | Impact Ionization MOSFETs                       | 10   |

|                  |        | 1.3.2   | Tunneling Field-Effect Transistors              | 11   |

|                  |        | 1.3.3   | Nano ElectroMechanical Field-Effect Transistors | 13   |

|                  |        | 1.3.4   | Ferroelectric Field-Effect Transistors          | 14   |

|                  | 1.4    | Ferroe  | electric materials                              | 15   |

|                  |        | 1.4.1   | History                                         | 15   |

|                  |        | 1.4.2   | Ferroelectricity                                | 16   |

|                  |        | 1.4.3   | Landau's theory                                 | 18   |

|                  | 1.5    | Negati  | ive Capacitance MOSFETs                         | 21   |

|                  | 1.6    | Ferroe  | electric materials comparison                   | 22   |

|                  |        | 1.6.1   | Lead Zirconate Titanate (PZT)                   | 24   |

|                  |        | 1.6.2   | Silicon-doped $HfO_2$                           | 25   |

|                  | 1.7    | Thesis  | s overview                                      | 26   |

|                  | 1.8    | Summ    | ary                                             | 28   |

#### Contents

| 2 | $\mathbf{Th}\epsilon$ | ory of   | Negative Capacitance Transistors                                      | <b>29</b> |

|---|-----------------------|----------|-----------------------------------------------------------------------|-----------|

|   | 2.1                   | Condi    | tion to obtain Negative Capacitance in FeFETs                         | 30        |

|   |                       | 2.1.1    | Theory                                                                | 30        |

|   |                       | 2.1.2    | Experimental verification                                             | 36        |

|   | 2.2                   | Capac    | itance matching condition                                             | 39        |

|   |                       | 2.2.1    | Theory                                                                | 39        |

|   |                       | 2.2.2    | Simulation method and device structure                                | 42        |

|   |                       | 2.2.3    | UTBB FDSOI NC-FET                                                     | 45        |

|   |                       | 2.2.4    | Double Gate NC-FET                                                    | 50        |

|   | 2.3                   | Summ     | ary                                                                   | 53        |

| 3 | Neg                   | gative ( | Capacitance MOSFETs                                                   | 55        |

|   | 3.1                   | •        | ive Capacitance as performance booster of CMOS                        | 56        |

|   | 3.2                   |          | electric materials                                                    | 59        |

|   |                       | 3.2.1    | $Pb(Zr,Ti)O_3$                                                        | 59        |

|   |                       | 3.2.2    | Silicon-doped $HfO_2$                                                 | 61        |

|   |                       | 3.2.3    | Training procedure of ferroelectrics                                  | 66        |

|   | 3.3                   | Capac    | itance matching and hysteresis tuning                                 | 67        |

|   | 3.4                   |          | hysteresis NC-FETs                                                    | 68        |

|   |                       | 3.4.1    | p-type NC-FET                                                         | 69        |

|   |                       | 3.4.2    | n-type NC-FET                                                         | 71        |

|   | 3.5                   | Low h    | ysteresis NC-FETs                                                     | 74        |

|   |                       | 3.5.1    | n-type NC-FET                                                         | 74        |

|   |                       | 3.5.2    | p-type NC-FET                                                         | 76        |

|   | 3.6                   | Hyster   | resis-free NC-FET                                                     | 78        |

|   | 3.7                   | Design   | a considerations of ferroelectric properties for Negative Capacitance |           |

|   |                       | MOSF     | FETs                                                                  | 82        |

|   |                       | 3.7.1    | PZT-based NC-FET                                                      | 83        |

|   |                       | 3.7.2    | Si:HfO <sub>2</sub> -based NC-FET $\dots$                             | 83        |

|   | 3.8                   | Summ     | ary                                                                   | 86        |

| 4 | Neg                   | gative ( | Capacitance Tunneling Field-Effect Transistors                        | 87        |

|   | 4.1                   | Negati   | ive Capacitance as performance booster of Tunnel FETs                 | 88        |

|   | 4.2                   | Predic   | etive simulations                                                     | 91        |

|   | 4.3                   | Exper    | imental demonstration of NC-TFETs                                     | 92        |

|   | 4.4                   | Silicon  | n nanowire array NC-TFETs                                             | 93        |

|   |                       | 4.4.1    | Results and discussions                                               | 95        |

|   | 4.5                   | InAs/    | InGaAsSb/GaSb nanowire NC-TFETs                                       | 98        |

|   |                       | 4.5.1    | Baseline TFET                                                         | 99        |

|   |                       | 4.5.2    | Nanowire growth                                                       | 99        |

|   |                       | 4.5.3    | Detailed of the fabrication process of TFETs                          | 101       |

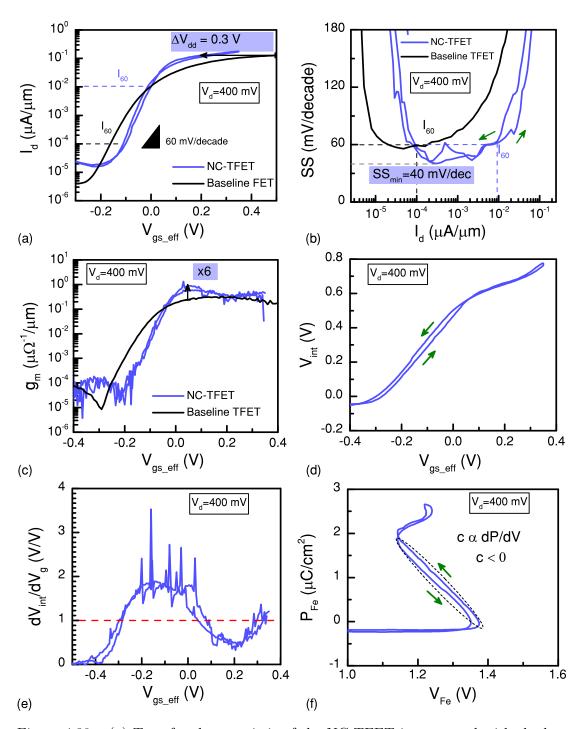

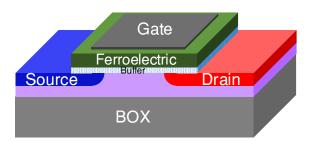

|   |                       | 4.5.4    | PZT-based NC-TFET                                                     | 102       |

|   |                       | 4.5.5    | Si:HfO <sub>2</sub> -based NC-TFET $\dots$                            | 106       |

| A | App  | 6.2.3<br>6.2.4<br>pendix: | Frequency measurements                                                                                   |     |

|---|------|---------------------------|----------------------------------------------------------------------------------------------------------|-----|

|   |      |                           |                                                                                                          | 144 |

|   |      | 6.2.3                     | Frequency measurements                                                                                   | 144 |

|   |      |                           |                                                                                                          | 144 |

|   |      | 6.2.2                     | Modeling of Negative Capacitance effect                                                                  | 144 |

|   |      | 6.2.1                     | Fabrication challenges                                                                                   | 144 |

|   | 6.2  | Perspe                    | ectives                                                                                                  | 144 |

|   |      | 6.1.5                     | Ferroelectric TFET as low power nonvolatile memory $\ \ldots \ \ldots$                                   | 143 |

|   |      | 6.1.4                     | Comparison between silicon doped $\mathrm{HfO}_2$ and $\mathrm{Pb}(\mathrm{Zr},\mathrm{Ti})\mathrm{O}_3$ | 143 |

|   |      |                           | TFETs                                                                                                    | 143 |

|   |      | 6.1.3                     | Experimental demonstration of hysteretic and non-hysteretic NC-                                          |     |

|   |      |                           | FETs                                                                                                     | 142 |

|   |      | 6.1.2                     | Experimental demonstration of hysteretic and non-hysteretic NC-                                          |     |

|   |      | 6.1.1                     | Negative capacitance matching condition                                                                  | 142 |

| - | 6.1  |                           | sions                                                                                                    | 142 |

| 6 | Coc  | lusions                   | s and Perspectives                                                                                       | 141 |

|   | 5.4  | Summ                      | ary                                                                                                      | 140 |

|   | 5.3  | 0 0                       | scaled FeTFET                                                                                            | 139 |

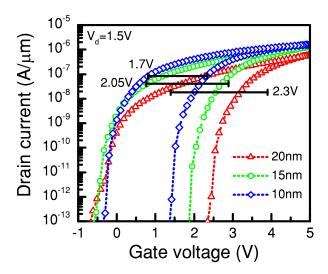

|   | _ ~  | 5.2.3                     | Ferroelectric thickness                                                                                  | 138 |

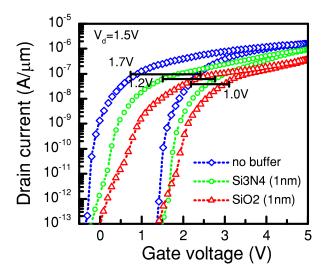

|   |      | 5.2.2                     | Buffer layer                                                                                             | 136 |

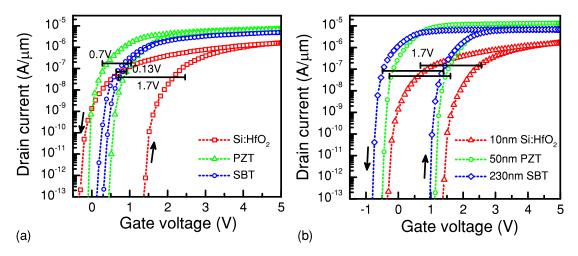

|   |      | 5.2.1                     | Ferroelectric material                                                                                   | 135 |

|   | 5.2  |                           | ry window                                                                                                | 135 |

|   |      | 5.1.4                     | Numerical analysis technique $\dots \dots \dots \dots \dots \dots$                                       | 132 |

|   |      | 5.1.3                     | Dipole polarization                                                                                      | 132 |

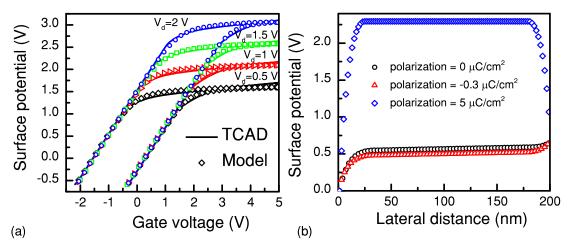

|   |      | 5.1.2                     | Model                                                                                                    | 128 |

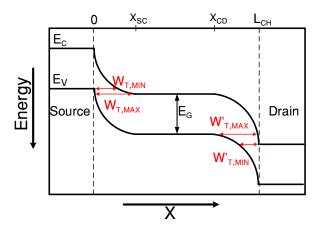

|   |      | 5.1.1                     | Approach and defenitions                                                                                 | 127 |

|   | 5.1  |                           | modeling                                                                                                 | 127 |

| 5 | Feri | roelect                   | ric Tunnel FET as Low Power non-Volatile Memory                                                          | 125 |

|   | 4.7  | Summ                      | ary                                                                                                      | 121 |

|   | 4 7  | 4.6.4                     | Near Hysteresis-free (sub-10 mV) In<br>GaAs planar NC-TFET                                               | 120 |

|   |      | 4.6.3                     | InGaAs planar NC-TFET with a sub-30 mV hysteresis                                                        | 116 |

|   |      | 4.6.2                     | Single crystalline PZT as ferroelectric                                                                  | 115 |

|   |      | 4.6.1                     | InGaAs planar TFETs                                                                                      | 115 |

|   | 4.6  |                           | s planar NC-TFETs                                                                                        | 113 |

|   |      | 4.5.6                     | Current normalization                                                                                    | 113 |

|   |      |                           |                                                                                                          | 110 |

# List of Figures

| 1.1  | First transistor                                                                |

|------|---------------------------------------------------------------------------------|

| 1.2  | Moore's law                                                                     |

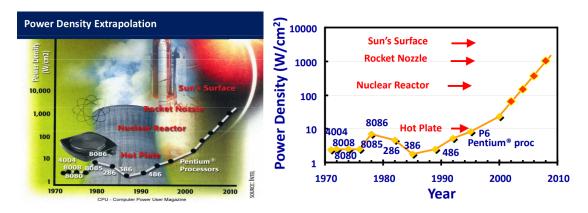

| 1.3  | Power density extrapolation                                                     |

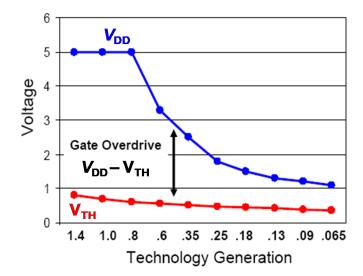

| 1.4  | $V_{DD}$ and $V_{TH}$ scaling                                                   |

| 1.5  | MOSFET scaling                                                                  |

| 1.6  | Boltzmann limit and the increasing static power challenge                       |

| 1.7  | Energy per cycle of a transistor                                                |

| 1.8  | Transfer characteristic of an ideal switch vs. MOSFET                           |

| 1.9  | Structure of an I-MOSFET                                                        |

| 1.10 | Transfer characteristic of an I-MOSFET                                          |

| 1.11 | Operation principle of a TFET                                                   |

| 1.12 | Best reported experimental TFET                                                 |

| 1.13 | Suspended-gate MOSFET                                                           |

| 1.14 | Negative Capacitance MOSFETs                                                    |

| 1.15 | Crystal structure of BaTiO $_3$                                                 |

| 1.16 | Phase transition in $BaTiO_3$                                                   |

| 1.17 | Relationship of Landau theory and first-principles calculations 19              |

| 1.18 | Free energy of paraelectric and ferroelectric materials                         |

| 1.19 | Second order phase transition of ferroelectrics                                 |

| 1.20 | Negative capacitance of ferroelectrics                                          |

| 1.21 | Ferroelectric Lead Zirconate Titanate (PZT) 24                                  |

|      | Ferroelectric silicon-doped $HfO_2$                                             |

| 2.1  | NC-FET schematic                                                                |

| 2.2  | Intersection of the transistor charge line with ferroelectric polarization . 32 |

| 2.3  | Stability condition in an NC-FET                                                |

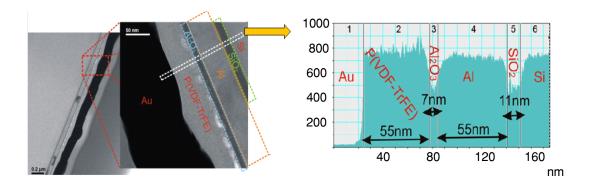

| 2.4  | TEM analysis of the FeFET                                                       |

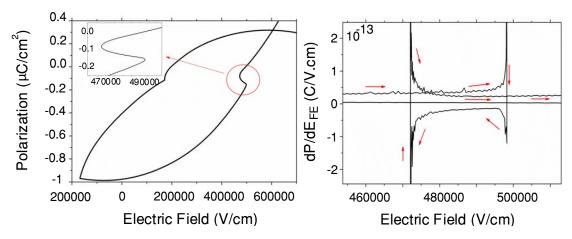

| 2.5  | Ferroelectric S-shape polarization                                              |

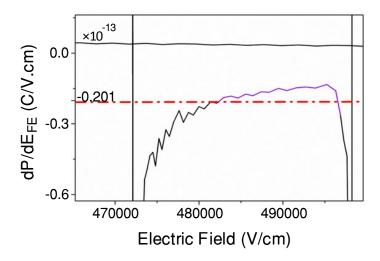

| 2.6  | Ferroelectric polarization derivative of the NC-FET                             |

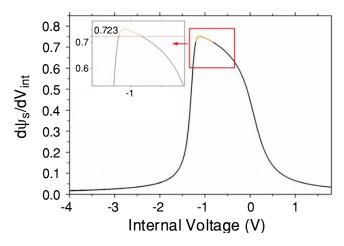

| 2.7  | Surface potential derivative of the NC-FET                                      |

| 2.8  | Transfer characteristic of an NC-FET vs. MOSFET                                 |

| 2.9  | Device schematic of single and double gate NC-FETs                              |

| 2.10 | Electrical characterization of polycrystalline PZT                              |

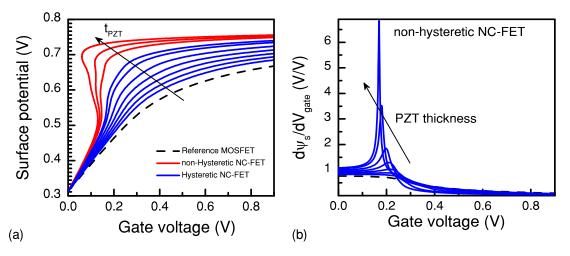

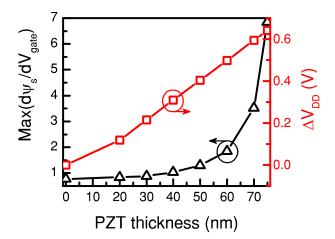

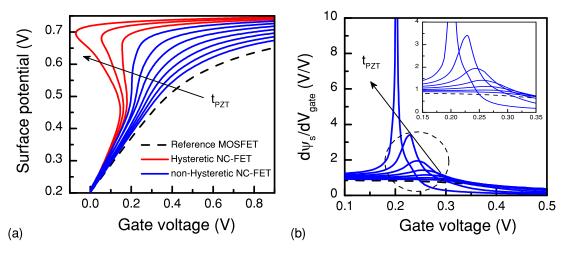

| 2.11 | Transfer characteristic of UTBB FDSOI NC-FET                                          | 46       |

|------|---------------------------------------------------------------------------------------|----------|

| 2.12 | Surface potential enhancement in the UTBB FDSOI NC-FET                                | 47       |

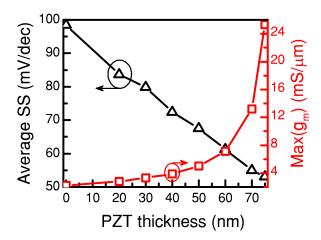

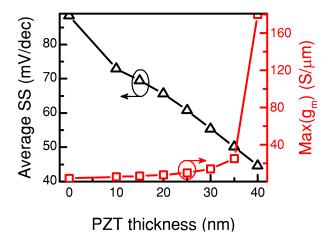

| 2.13 | Average SS and $Max(g_m)$ of UTBB FDSOI NC-FET                                        | 48       |

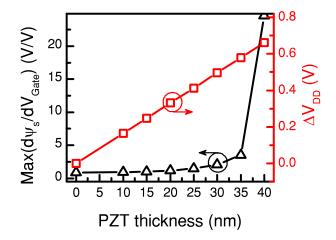

| 2.14 | Supply voltage reduction of the UTBB FDSOI NC-FET as a consequence                    |          |

|      | of NC effect                                                                          | 49       |

| 2.15 | Transfer characteristic of DG NC-FET                                                  | 50       |

| 2.16 | Surface potential enhancement in the DG NC-FET                                        | 51       |

| 2.17 | Average SS and $Max(g_m)$ of DG NC-FET                                                | 52       |

| 2.18 | Supply voltage reduction of the DG NC-FET as a consequence of NC effect               | 53       |

| 3.1  | Negative Capacitance in ferroelectric materials                                       | 57       |

| 3.2  | Schematic of the performance boosting in n- and p-type negative capaci-               |          |

|      | tance MOSFETs                                                                         | 58       |

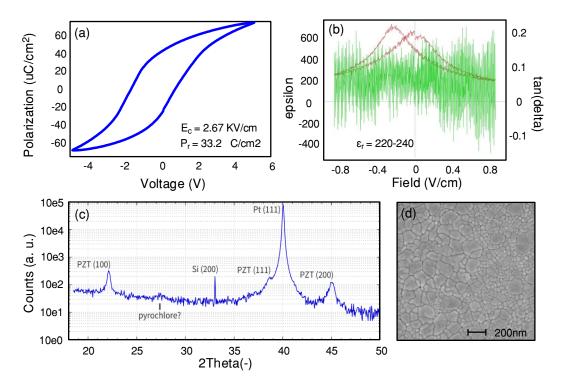

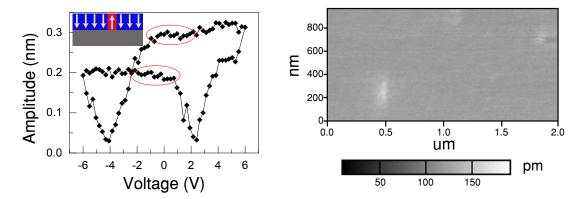

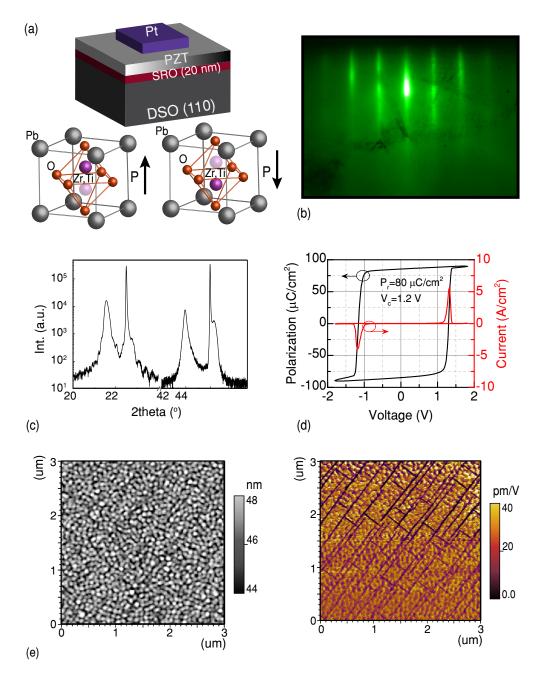

| 3.3  | Electrical characterization of the 46 nm thick PZT film                               | 60       |

| 3.4  | Physical characterization of the 46 nm thick PZT film                                 | 60       |

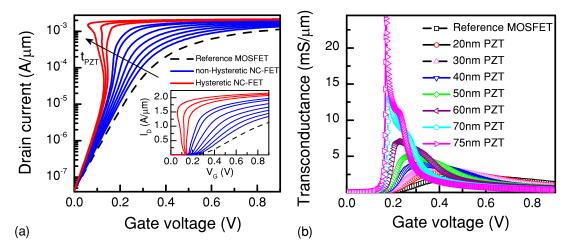

| 3.5  | Polarization characteristic of PZT thin film                                          | 61       |

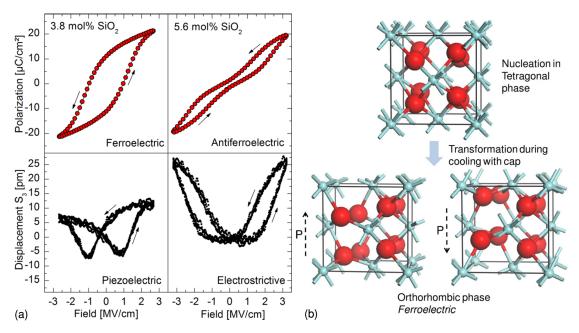

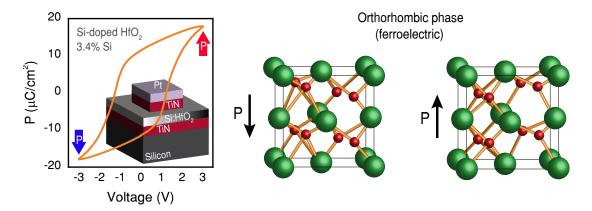

| 3.6  | Ferroelectricity in silicon-doped $HfO_2$                                             | 62       |

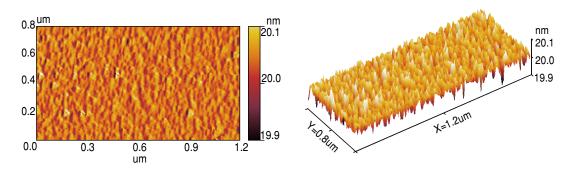

| 3.7  | AFM analysis of silicon-doped $HfO_2$                                                 | 62       |

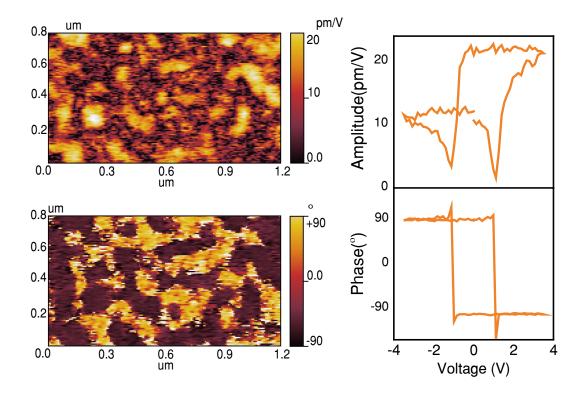

| 3.8  | PFM analysis of silicon-doped HfO <sub>2</sub>                                        | 63       |

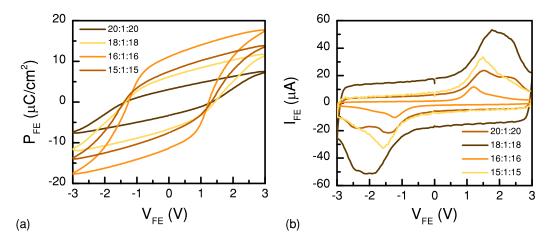

| 3.9  | Impact of Si% on ferroelectric properties of Si:HfO <sub>2</sub>                      | 64       |

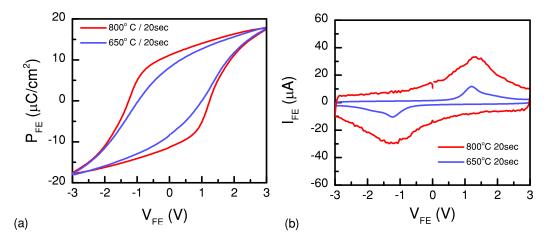

|      | Impact of annealing temperature on ferroelectric properties of Si:HfO $_2$ .          | 64       |

|      | Impact of layer thickness on ferroelectric properties of Si:HfO $_2$                  | 65       |

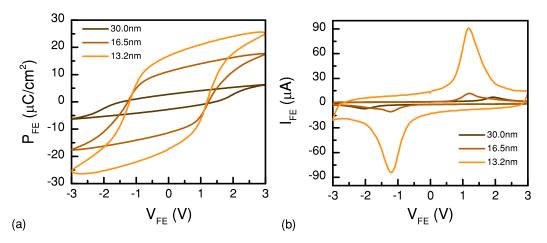

| 3.12 | Electrical properties of the developed ferroelectric Si:HfO <sub>2</sub> vs. previous | 0.5      |

| 0.10 | reports                                                                               | 65       |

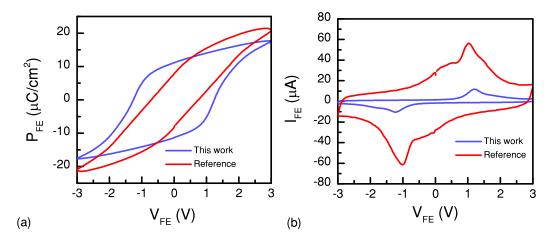

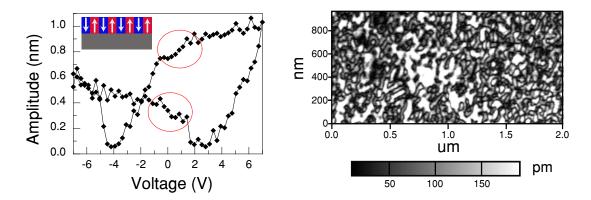

|      | Piezoelectric response of the as-fabricated PZT thin film                             | 66       |

|      | Piezoelectric response of the trained PZT thin film                                   | 67       |

| 3.15 | Investigated experimental configuration of the NC-FET together with its               | 00       |

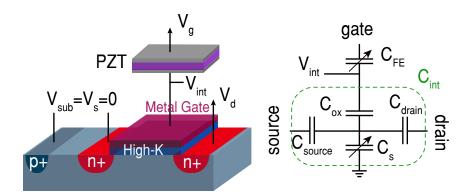

| 0.10 | capacitance model                                                                     | 68       |

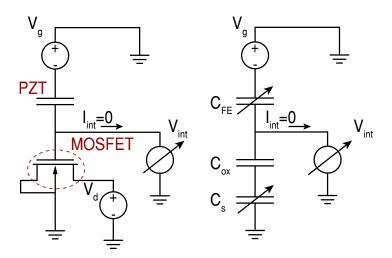

|      | Measurement setup utilized for the characterization of the NC-FET                     | 69       |

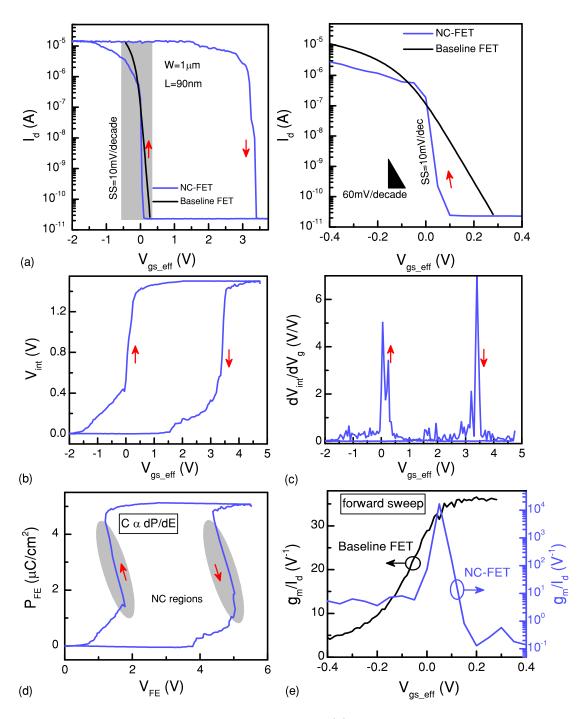

|      | Large hysteresis p-type NC-FET                                                        | 70       |

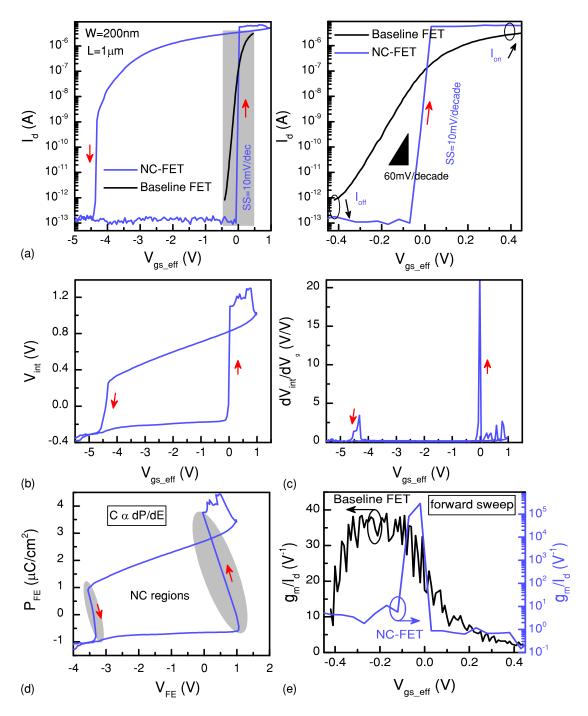

|      | Large hysteresis n-type NC-FET(1)                                                     | 72       |

|      | Large hysteresis n-type NC-FET(2)                                                     | 73       |

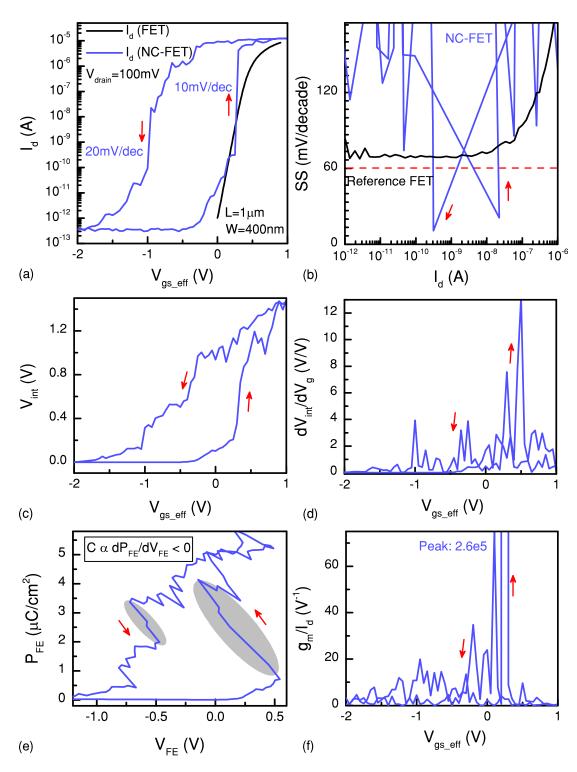

|      | Low hysteresis n-type NC-FET                                                          | 75<br>77 |

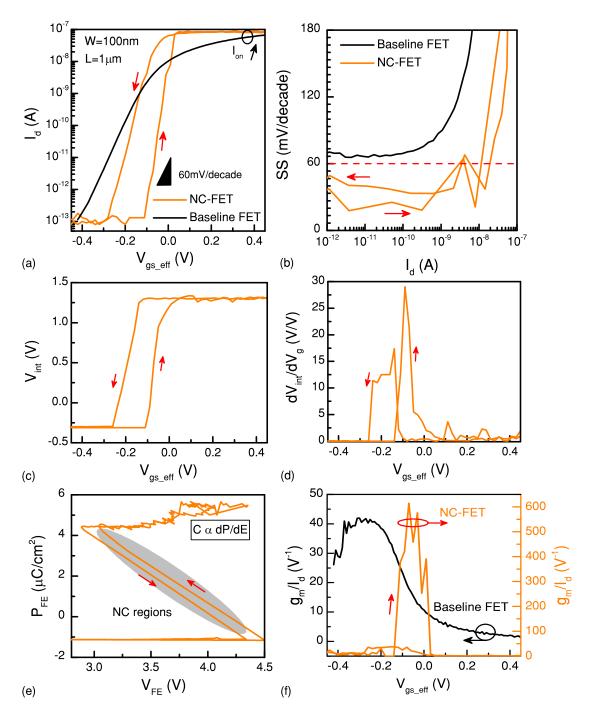

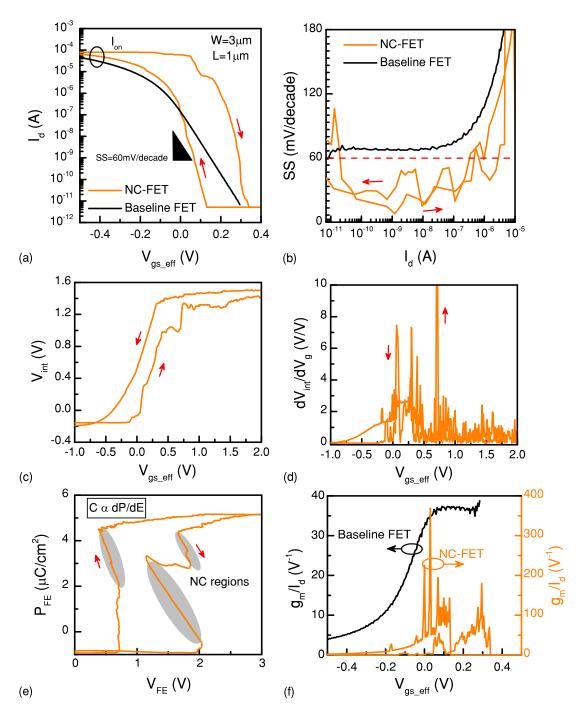

|      | Low hysteresis p-type NC-FET                                                          | 77       |

|      | Impact of the source-to-drain electric field on the performance of an NC-FET          | 78       |

| 3.23 | Schematic diagram of the expected transfer characteristic of a non-hysteretic NC-FET  | 79       |

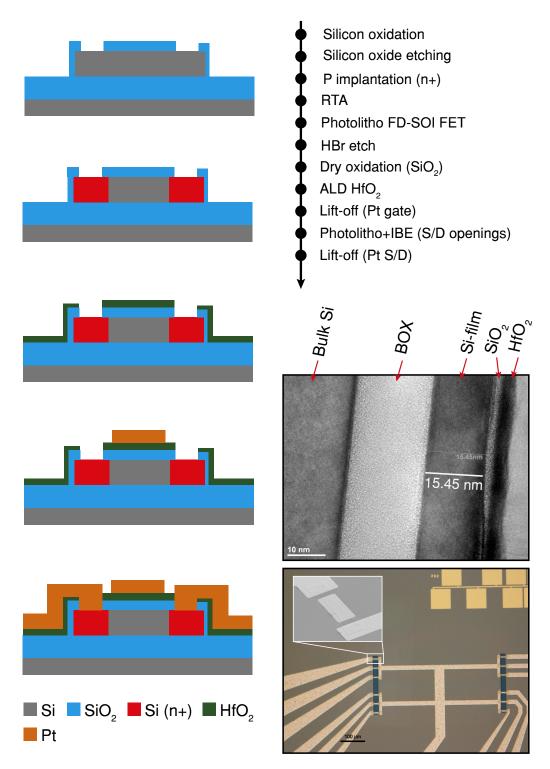

| 3.24 | Fabrication process of the reference MOSFET                                           | 80       |

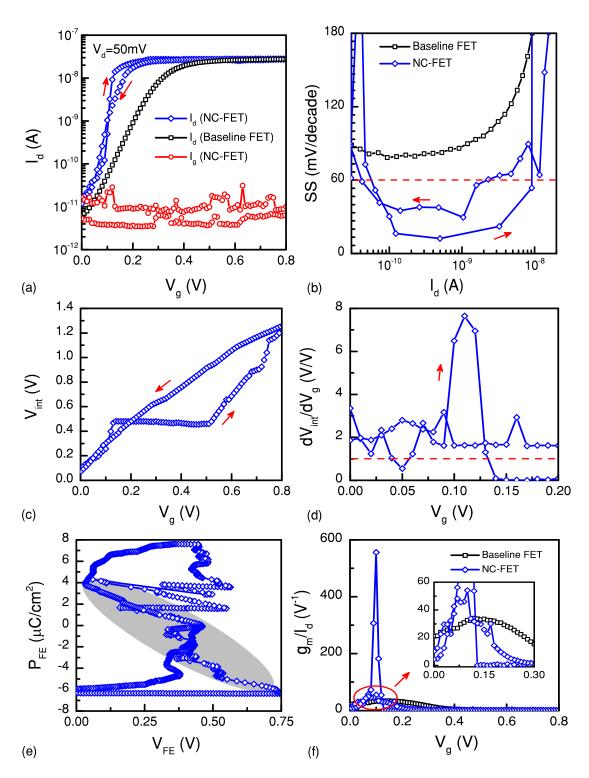

|      | Hysteresis-Free NC-FET                                                                | 81       |

| 3.26 | Impact of the drain voltage on the operation of the non-hysteretic NC-FET             | 82       |

| 3.27 | Ferroelectric properties of Si:HfO $_2$ vs. PZT                                       | 84       |

| 3.28 | Electrical properties of the Si:HfO <sub>2</sub> -based NC-FET                        | 85       |

| 4.1  | Schematic diagram of the negative capacitance of ferroelectrics                                   | 89  |

|------|---------------------------------------------------------------------------------------------------|-----|

| 4.2  | NC-TFET operation principle                                                                       | 90  |

| 4.3  | Device schematic of an NC-TFET                                                                    | 91  |

| 4.4  | Predictive simulations of an NC-TFET                                                              | 92  |

| 4.5  | Schematic diagram of the nanowire array NC-TFET                                                   | 94  |

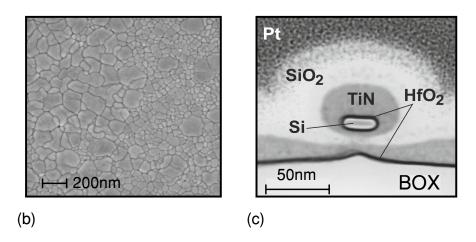

| 4.6  | Physical characterization of the NW array NC-TFET                                                 | 94  |

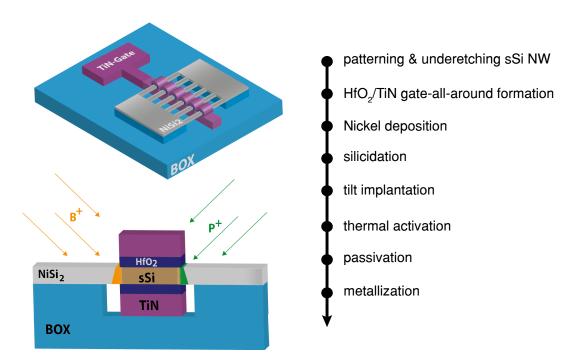

| 4.7  | sSi NW array TFET fabrication process                                                             | 95  |

| 4.8  | Transfer characteristics of a non-hysteretic and a hysteretic Silicon NW                          |     |

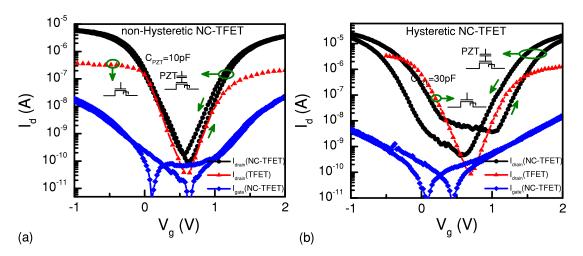

|      | array NC-TFET                                                                                     | 96  |

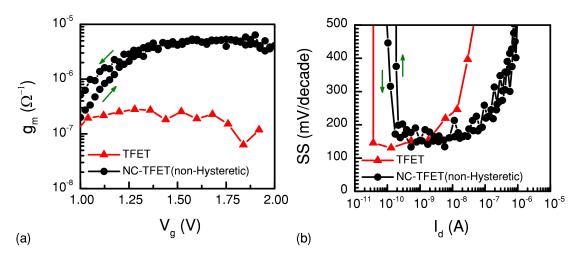

| 4.9  | Experimental performance improvement of the non-hysteretic NC-TFET                                | 97  |

| 4.10 | Experimental performance improvement of the hysteretic NC-TFET $$                                 | 98  |

| 4.11 | Baseline TFET structure and electrical characterization                                           | 100 |

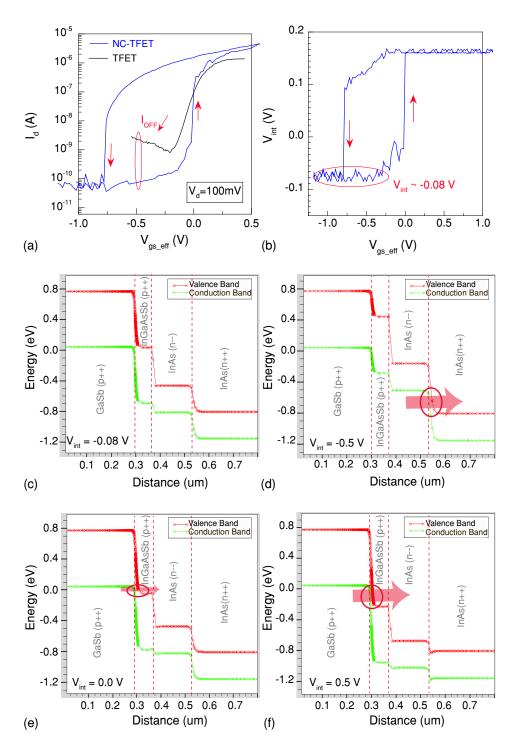

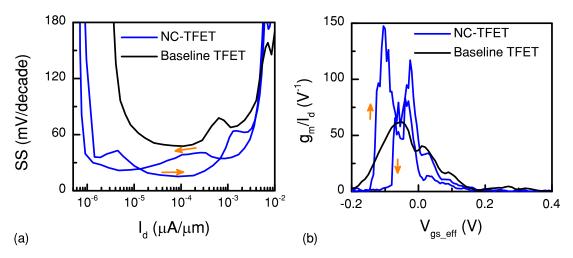

| 4.12 | Transfer characteristic of the PZT-based NC InGaAs nanowire TFET $$ .                             | 102 |

| 4.13 | Internal voltage amplification of the PZT-based NC InGaAs nanowire                                |     |

|      | TFET                                                                                              | 103 |

| 4.14 | Performance improvement in the PZT-based NC InGaAs nanowire TFET                                  | 103 |

| 4.15 | Impact of the ferroelectric capacitor on the off-current of the NC-TFET                           | 105 |

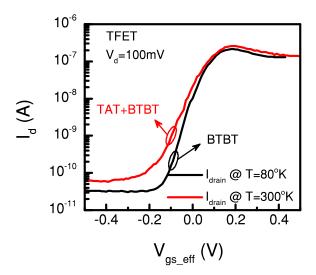

| 4.16 | Impact of the temperature on the operation of reference TFETs                                     | 107 |

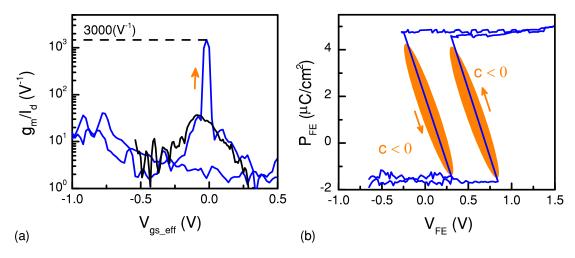

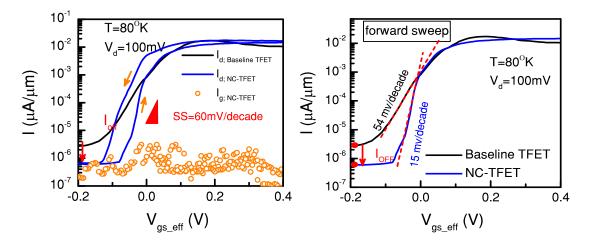

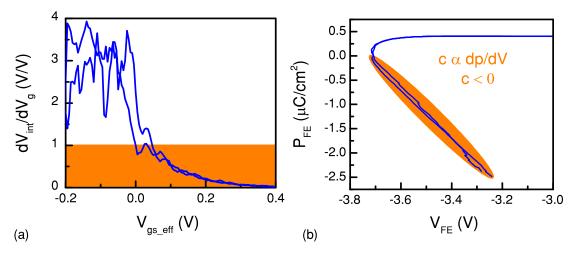

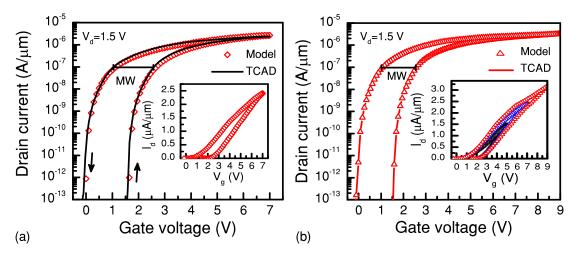

| 4.17 | Transfer characteristic of the Si: $HfO_2$ -based NC InGaAs nanowire TFET                         | 108 |

| 4.18 | Performance improvement in Si:HfO2-based NC InGaAs nanowire TFET                                  | 109 |

| 4.19 | Internal voltage amplification in Si:HfO2-based NC InGaAs nanowire TFET                           | 109 |

| 4.20 | Impact of the source-to-drain electric field on the performance of Si:HfO2- $$                    |     |

|      | based NC-TFET                                                                                     | 110 |

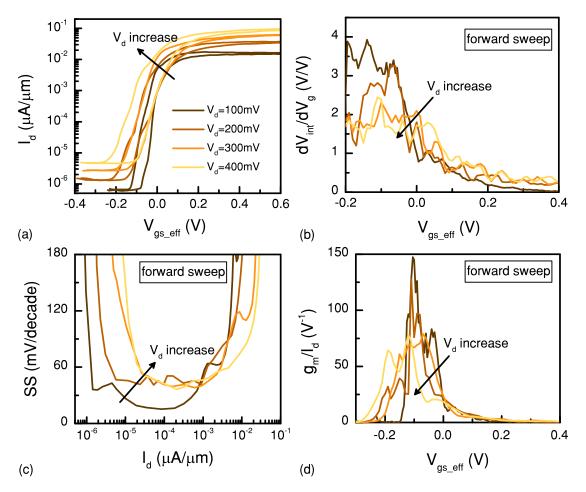

| 4.21 | Impact of NC on output transfer characteristic of Si:HfO2-based NC-TFET                           | 111 |

| 4.22 | Normalizing the measured current of nanowire InGaAs TFETs $\ \ldots \ \ldots$                     | 113 |

|      |                                                                                                   | 114 |

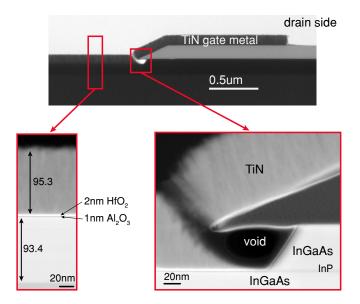

| 4.24 | TEM image of the InGaAs planar TFET                                                               | 115 |

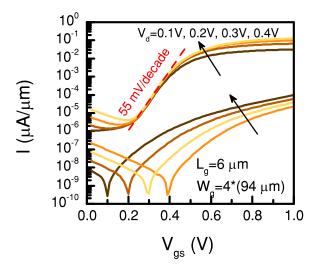

| 4.25 | $\mathbf{I}_d\text{-}\mathbf{V}_g$ and $\mathbf{I}_g\text{-}\mathbf{V}_g$ plots of an InGaAs TFET | 116 |

| 4.26 | Single crystalline PZT as NC booster                                                              | 117 |

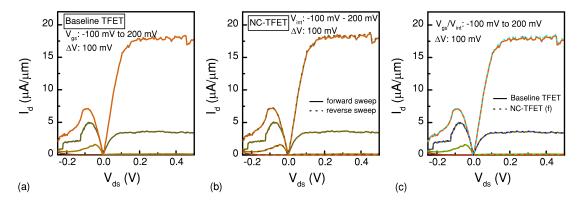

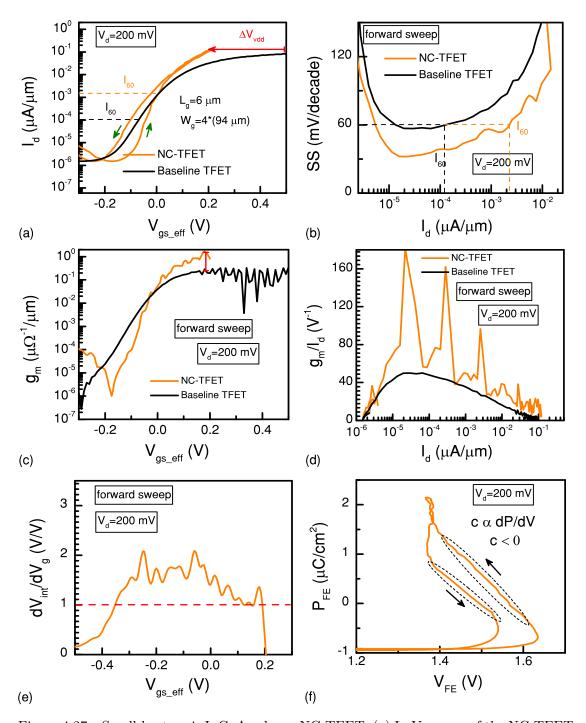

| 4.27 | Small-hysteresis InGaAs planar NC-TFET                                                            | 118 |

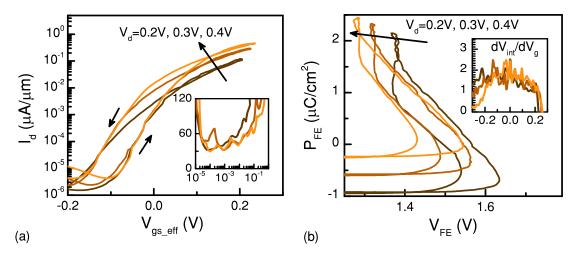

| 4.28 | Impact of the drain voltage variation on the InGaAs NC-TFET                                       | 119 |

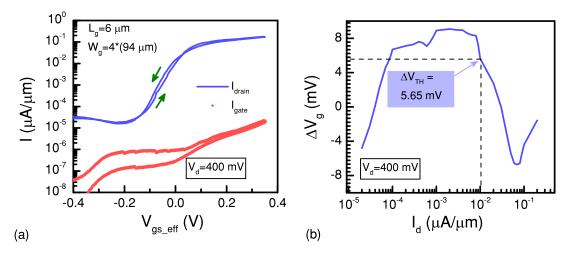

| 4.29 | Hysteresis-free InGaAs planar NC-TFET                                                             | 120 |

| 4.30 | Electrical performances of the hysteresis-free InGaAs planar NC-TFET                              | 122 |

| 5.1  | Device schematic of an SOI FeTFET                                                                 | 127 |

| 5.2  |                                                                                                   | 130 |

| 5.3  |                                                                                                   | 133 |

| 5.4  |                                                                                                   | 134 |

| 5.5  | Relation between the memory window and the ferroelectric material and                             | -51 |

|      | •                                                                                                 | 136 |

| 5.6  |                                                                                                   | 137 |

| 5.7  | Impact of the Si:HfO <sub>2</sub> thickness on the transfer characteristic of the FeTFET          |     |

| T • 1 | C   | T7.            |

|-------|-----|----------------|

| List  | OT. | <b>Figures</b> |

|       | O.  | - 15 at 00     |

## List of Tables

| 1.1 | Dennard's scaling rules                                                                     | 4   |

|-----|---------------------------------------------------------------------------------------------|-----|

|     | Performance of reported NC-FETs compared to the proposed Si:HfO <sub>2</sub> -based NC-TFET | 112 |

| 4.2 | Digital and analog performances of the hysteresis-free InGaAs planar NC-TFET                | 121 |

| 5.1 | Comparison of the ferroelectric properties of PZT, SBT, and Si:HfO $_2$                     | 135 |

| 5.2 | Ferroelectric properties of Si:HfO <sub>2</sub> regarding the film thickness                | 138 |

### 1 Introduction

#### Abstract:

In this chapter, a general introduction to the CMOS scaling and the increasing power challenge, arising from physical limitations of MOSFET switches, is presented. It is remarked that the increasing power dissipation issue can be addressed by the evolution of small swing switches. The solutions that have been found by now to achieve a subthreshold swing below the 60 mV/decade thermal limit of MOSFETs, are introduced. Next in this chapter, the operation principle of negative capacitance transistors, as one of the most important steep slope switch candidates, will be demonstrated. By exploiting the general theory of ferroelectrics and the approach of the Landau model, it is explained that ferroelectric materials can provide an effective negative capacitance in a certain range of operation. The negative capacitance region of ferroelectric materials can be utilized to reduce the subthreshold swing of conventional transistors. Exploration of negative capacitance devices is the main topic of this thesis. The rest of this chapter dedicates to the comparison of ferroelectric materials and their potentials for the integration with the CMOS technology. Lastly, a quick overview of this Ph.D. work is presented.

#### 1.1 CMOS scaling and MOSFET limitations

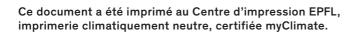

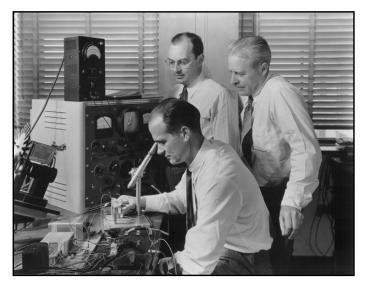

Microelectronics was among the most leading technologies in the past recent years. All the developed industries that are affecting the everyday life of human beings owe their achievements to the advancement of microelectronics. Everything started with the invention of the transistor by W. Shockley, J. Bardeen, and W. Brattain in 1947 [1]. The transistor was the first manufactured device that could turn the signal on or off and amplify it in the on-state. This was called "the most important invention of 20th century" and it was just the beginning of a long road toward modern electronics and integrated circuits. It is no understatements to say that modern electronic devices could not be able to function without a transistor processing electrical signals [2].

Figure 1.1 – John Bardeen, William Shockley, and Walter Brattain (left) and their first transistor (right) [1].

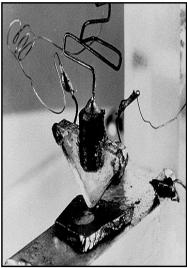

The silicon technology has advanced with an exponential rate in terms of performance and productivity during past decades, which was anticipated by Moore in 1965 [3]. Moore's Law was actually based on observation regarding the optimized density of transistors in terms of cost. It arises from the fact that the cost decreases by increasing the number of transistors, but it also increases the chance of having defects. Moore stated that the number of transistors on an integrated circuit would be doubled every two years. This law became a self-fulfilling prophecy for the semiconductor industry and was valid until now, which is evidenced by the International Roadmap for Semiconductors (ITRS) [4].

The scaling in microelectronics has been driven by the demand for a higher density integration in order to minimize the fabrication cost and also increase the speed. The switching energy of a silicon MOSFET can be calculated by  $0.5\epsilon_d(V_{DD} \times L_{ch})^2/d_d$  where  $\epsilon_d$  refers to the dielectric permittivity,  $V_{DD}$  is the supply voltage,  $L_{ch}$  represents the

Figure 1.2 – Moore's law over time [3].

channel length, and  $d_d$  is the dielectric thickness. The switching energy and switching delay, i.e.  $\tau_d \ l_{ch}/\nu_s$  where  $\nu_s$  is the saturation velocity of carriers, are proportional to the channel length. It means that having more efficient devices requires the aggressive scaling to continue [5].

The scaling based on Moore's law did not confront any sever obstacles until these past years, which the transistor dimensions reached the sub-100 nm regime. By increasing the number density of transistors, the power consumption increases exponentially. The problem started with the advancement of technology and the quest for faster calculations, which translates to higher frequencies. The consumed power was mostly dissipated during the switching of transistors. Hence, increasing the number density of transistors results in an exponential rise in the power consumption. It is anticipated that the aggressive scaling will finally stop due to the inability to remove the heat generated by transistors. We will discuss this increasing power challenge in CMOS scaling and possible solutions later in this chapter.

The first scaling rules for CMOS were proposed by R. H. Dennard in 1974 [7]. Dennard recommended that the device dimensions and the applied voltage should be scaled in a way to maintain the same electric field inside the gate dielectric. Therefore, Dennard and his team proposed that all dimensions and applied voltages should be scaled by a factor of 1/K, while the doping of the source and drain should be increased by a factor of K. At the time of this proposal in 1974, commercially available circuits were using

Figure 1.3 – Increasing power challenge involved in the scaling of CMOS [3, 6].

MOSFETs with the minimum gate length of 5  $\mu$ m, but devices with smaller gate lengths were already built in laboratories that were demonstrating the benefits of further scaling. The scaling principles by Dennard were quickly adopted by the semiconductor industry as the roadmap. The results of the Dennard's scaling rules are summarized in Table 1.1.

|             |            |         | _        | _                  | _       | _   |          |          | F. 7 |   |

|-------------|------------|---------|----------|--------------------|---------|-----|----------|----------|------|---|

| Table 1.1 – | 13 17      | 1:      | 1        | - <del>-</del> - 1 | -1      | l   | _::+     | 1 1      | 171  |   |

| Table L L — | Tiennara s | SCALING | rilles : | at the             | CHANICE | ฆทด | CHECHILE | IEVEIS   | 111  |   |

| 10010 1.1   | Domaia     | DOMINIS | I UICD C | LU UIIC            | acvice  | and | CIICUIU  | IC V CID |      | • |

| Device and circuit parameters       | Scaling factor   |

|-------------------------------------|------------------|

| device dimension: $t_{ox}$ , W, L   | 1/K              |

| doping concentration: $N_A$ , $N_D$ | K                |

| voltage                             | 1/K              |

| current                             | $1/\mathrm{K}$   |

| capacitance $A\epsilon/t$           | $1/\mathrm{K}$   |

| delay time $VC/I$                   | $1/\mathrm{K}$   |

| power dissipation VI                | $1/\mathrm{K}^2$ |

| power density VI/A                  | 1                |

| electric field                      | 1                |

The proposed ideas by Dennard and Moore set the course of semiconductor industry on developing new integrated processes and products on a regular pace and providing consistent improvements in the transistor density, performance, and power. Each new generation of technology was expected to reduce the minimum feature size by a factor of 0.7 (K  $\sim$  1.4). Indeed by applying the rules of scaling, the dissipated power remains constant and the frequency, f, increases by K. These rules have been fulfilled ever since, until sub-65 nm technology nodes. Below the 65 nm CMOS technology node, the Dennard's scaling rules are no longer working as well as they did before due to the challenges involved in the voltage scaling.

Figure 1.4 –  $V_{DD}$  scaled more than  $V_{TH}$  which leads to the reduction of the gate overdrive,  $(V_{DD}-V_{TH})$  [9].

The voltage scaling has an extremely important role in the CMOS scaling due to numerous reasons such as reliability, lowering the transistor power, and maintaining the constant power density. Dennard assumed that the threshold voltage,  $V_{TH}$ , of transistors, would scale down along with the supply voltage and provides improved performance and power. However, Dennard ignored the impact of the sub-thermal leakage of the transistor on the total power consumption of the chip. This sub-thermal leakage was low by the time (back in 1970s) and was a small fraction of the logic circuits power consumption. Nevertheless, after years of scaling,  $V_{TH}$  has been scaled to the point where the leakage current has increased significantly. Thereby, it is impossible to further scale  $V_{TH}$  and hence, scale the operation voltage. This can be clearly observed in Figure 1.4, which shows the scaling trend of  $V_{DD}$  and  $V_{TH}$  from the 1.4  $\mu$ m technology node to 65 nm. The supply voltage is decreased down to 20% of its starting value while the threshold voltage could not be scaled more than 50% [8].

The main consequence of the supply voltage scaling without a sufficiently scaled threshold voltage is the decrease of the overdrive voltage,  $V_{OV}=V_{DD}-V_{TH}$ . This results in a reduced on-current, which can be formulated as  $I_{ON}=0.5\mu C_{OX}(W/L)\times(V_{DD}-V_{TH})^2$  when the device is working in the saturation region. Hence, the performance and the dynamic speed of the transistor,  $C_gV_{DD}/I_{ON}$ , decreases. The first solution to overcome this issue and provide an acceptable performance/overdrive is slowing down the supply voltage scaling.

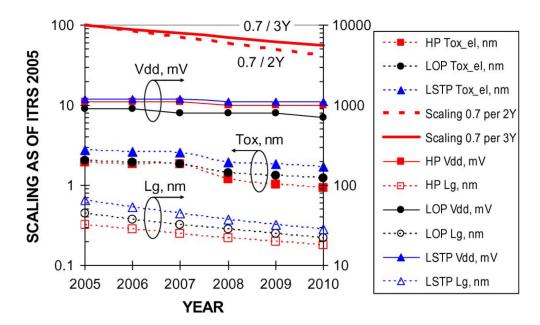

Figure 1.5 depicts the scaling of the channel length, gate dielectric thickness, and the supply voltage. The scaling of the channel length,  $L_g$ , is the only parameter that has been scaled down properly. In contrast, the scaling of  $V_{DD}$ , as well as that of the electrical oxide thickness, is clearly deficient. The supply voltage almost remains constant

Figure 1.5 – Scaling of the supply voltage, gate dielectric thickness, and the gate length [9].

because of many reasons, but the most important one is the race for the performance.

In case of the ideal scaling of the supply voltage along with device dimensions, the power density  $(I_{ON}V_{DD}/A)$  remains constant. This means that the energy needed to drive the chip and the resulting heat generated by the transistors remains constant. When  $V_{DD}$  does not scale down along with the device dimensions, the power density increases. The total energy dissipation of each transistor can be calculated by sum of the dynamic power (the dissipated power during the switching of the transistor) and the static power (consumed power in the off-state).

The dynamic power is usually modeled by equation 1.1, where f is the frequency and  $C_L$  is the total switching capacitance load:

$$P_{dyn} = f \times C_L \times V_{DD}^2. \tag{1.1}$$

The static power originates from the leakage of transistors during their off-state:

$$P_{static} = I_{leakage} \times V_{DD}, \tag{1.2}$$

where  $I_{leakage}$  is the total leakage current of the transistor while it is operating in the off-state. The scaling of the transistor dimensions without a sufficient reduction of the supply voltage leads to a considerable increase in the power consumption [10].

The second possibility to have a sufficiently high overdrive, rather than keeping  $V_{DD}$

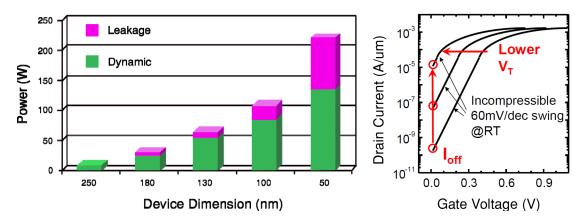

Figure 1.6 – Static power is increasing much faster than the dynamic power (left) [12] due to the incompressibility of the SS and scaling of the threshold voltage [13].

high, is to scale down the threshold voltage. The scaling of  $V_{TH}$  is actually the main reason for the faster increase of the static power comparing the dynamic power which can be traced back to a physical limitation in MOSFET switches. The steepness of the off-to-on transition of a switch is characterized as the minimum gate voltage required for a 10-fold increase in the drain current, known as the subthreshold swing (SS). The general expression for the subthreshold swing of a MOSFET is [11]:

$$SS = \left[\frac{\partial V_g}{\partial (log_{10}I_d)}\right] = \frac{\partial V_g}{\partial \psi_s} \times \frac{\partial \psi_s}{\partial log_{10}I_d},\tag{1.3}$$

where  $\psi_s$  denotes to the surface potential of the semiconducting channel. The first term of the right-hand side of equation 1.3, which is known as the m-factor (body factor), generally has a value greater than one since  $V_g$  is linked to  $\psi_s$  through a capacitive voltage divider.

The second term, n-factor, has a lower limit of (kT/q)ln10, 60 mV/decade at  $300^o$  K, in a conventional MOSFET or any device using the thermionic injection of carriers over an energy barrier as the main operating principle. This limit is a consequence of the thermally broadened Fermi-distribution of carriers which is irrespective of dimensionality or the material in use. The reduction of the threshold voltage by 60 mV under the noted limit will translate in increasing the *off*-current by a factor of 10 and hence, increase of the static power (Figure 1.6). It should be noted that the minimum swing of a MOSFET can be also written as

$$SS = \left(1 + \frac{C_s}{C_{ins}}\right) \frac{kT}{q} ln 10, \tag{1.4}$$

where  $C_s$  and  $C_{ins}$  are the semiconductor and insulator capacitances, k is the Boltzmann constant, and q is the elementary charge.

Today, the static power (the consumed power in the off-state of transistors) is

Figure 1.7 – Increased leakage (static) power dominates over the dynamic power in modern chips [15].

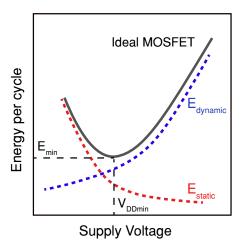

dominated over the switching (dynamic) power and became the most important challenge of the CMOS industry. This is mainly because of the Boltzmann limit on the subthreshold swing of MOSFETs and also the broken scaling rules. Figure 1.7 shows the constraint of the dynamic and static power that defines the minimum energy per cycle of operation [14].

#### 1.2 Concept of ideal switch

Rescue strategies for the increasing leakage power challenge can be followed in two main directions: (i) circuit level by developing new software/hardware techniques dedicated to power saving and (ii) device level by identifying novel power aware or energy efficient device architectures. The most reasonable approach is to find a device level solution by identifying energy efficient switches, having a transfer characteristic closer to the one of the ideal switch.

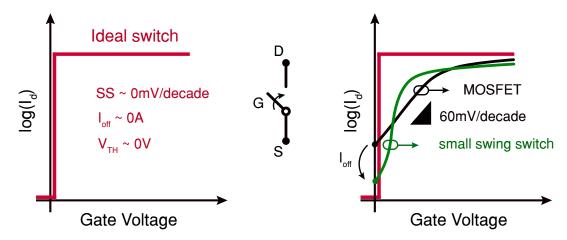

An ideal switch supposes to provide an on-current as high as possible together with an almost zero off-current, thus maximizing the  $I_{ON}/I_{OFF}$  ratio (Figure 1.8). Additionally, the ideal switch should have a super steep off-to-on transition, near 0 mV/decade, in order to make us eligible to scale down the threshold voltage without increasing the leakage current.

Due to the fact that it is impossible to actually demonstrate an ideal switch, small swing switches would provide a more realistic device level solution. A small swing switch should have sub-thermal SS and a smaller *off*-current in comparison with a conventional MOSFET. Therefore, a small swing switch makes it possible to reduce the supply voltage

Figure 1.8 – Transfer characteristic of an ideal switch (left) and comparison of an ideal switch, a MOSFET, and a small swing switch (right).

without performance loss and simultaneously deals with the increasing static power issue. Figure 1.8 shows and compares the transfer characteristic of a conventional transistor with a small swing switch and also an ideal MOSFET.

Considering equation 1.3, a sub-thermal swing can be achieved by two means:

- (i) reducing the second term in the right-hand-side (RHS) of equation 1.3, known as the n-factor, below 60 mV/decade (at room temperature). This can happen by employing other physics principles, rather than the thermionic injection of carriers over a barrier, to inject charge carriers into the channel.

- (ii) another prominent way of reducing the subthreshold swing to lower the body factor, the first term in the RHS of equation 1.3, is integrating new materials or physics into the gate stack of transistors. In a conventional MOSFET, the body factor, which relates to the electrostatic coupling of the gate to the channel, is always greater than 1.

# 1.3 Small swing switches

To overcome the so-called "Boltzmann Tyranny", several steep switching devices are proposed to provide a sub-thermal swing by either reducing the n-factor or body factor of transistors. Lowering one of the two terms could lead to a steeper switching compared to the conventional MOSFETs.

Any attempt to modify the subthreshold slope of transistors must necessarily involve either modifying the mode of carrier injection from diffusion-based to tunneling-based mechanisms or steepening the nonlinearity using an amplifier.

Among alternative structures, Tunneling Field-Effect Transistors (TFETs) [15], Im-

Figure 1.9 – Device schematic of an I-MOSFET [20].

pact Ionization MOSFETs (I-MOSFETs) [16], NanoElectromechanical FETs (NEMFETs) [17], and Negative Capacitance MOSFETs (NC-FETs) [18] have been extensively studied as the promising steep slope switches. In the following, we briefly describe each of the noted candidates.

# 1.3.1 Impact Ionization MOSFETs

Use of an amplifier to enhance the on-state and suppress the off-state seems to be an interesting solution, but this approach needs to address the following major challenges [19]:

- (i) the amplification mechanism must be internal to the device and must arise from some gain within the device.

- (ii) the device must not latch up and a fast mechanism such as drift, rather than recombination, must remove all the injected carriers while the device is switching from on to off-state.

- (iii) the most important challenge arises is that a finite bandwidth associated with every gain mechanism and the gain-bandwidth product may impose fundamental limitations on the intrinsic switching speed of the device.

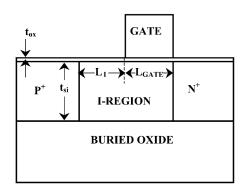

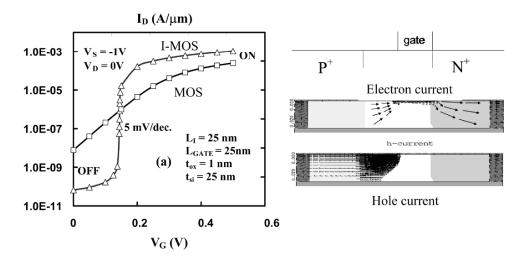

The impact ionization related breakdown was found such a gain mechanism that fulfills all the noted conditions. In this regard, impact ionization MOSFET (I-MOSFET) is proposed by employing the modulation of the avalanche breakdown voltage of a gated-structure to switch from *off*-to-on and vice-versa [21, 22]. In this type of transistors, a p-n junction diode is used in the post-breakdown mode (i.e., with voltages higher than the breakdown voltage). The delay of an I-MOSFET is proportional to the logarithm of the desired gain and hence, it is very fast. As a result, the subthreshold swing of an I-MOSFET can reach values much lower than the (kT/q)ln10 limit of a conventional MOSFET [23, 24].

Figure 1.10 – Simulated transfer characteristic of an I-MOSFET with a sub-thermionic swing [20].

The device structure of an n-channel SOI impact ionization MOSFET is presented in Figure 1.9. This n-channel device has an overlap with the drain (n+) and an offset toward the source (p+) side of the device. Figure 1.10 demonstrates the simulated results of the described structure, achieving a swing of about 5 mV/decade. Experimental reports also confirm the possibility of having a sub-thermionic swing in an I-MOSFET [21].

The main challenge of impact ionization MOSFETs relates to their reliability over time. An avalanche breakdown requires the presence of hot carriers in high densities that compromises the reliability. Hot electrons can be trapped in the oxide after a period of time which changes the threshold voltage [25].

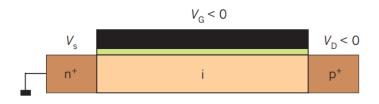

## 1.3.2 Tunneling Field-Effect Transistors

Tunnel field-effect transistors (TFETs) [26] have attracted a great deal of attention for achieving a steep subthreshold swing by employing quantum mechanical band-to-band tunneling (BTBT) of careers from source to the channel (reducing n-factor to values below 60 mV/decade) [27]. The current of a TFET is the integral of the transmission probability,  $T_{WKB}$ , of the interband tunneling over the source-channel junction, which can be approximated as [28]:

$$T_{WKB} \approx exp\left(-\frac{4\lambda\sqrt{2m^{\star}}\sqrt{E_g^3}}{3q\left(E_g\ \Delta\Phi\right)}\right),\tag{1.5}$$

where  $m^*$  is the effective mass and  $E_g$  is the bandgap. Here,  $\lambda$  is the screening tunneling length that describes the spatial extent of the transition region at the source-channel interface. In a TFET (Figure 1.11), at a constant drain voltage ( $V_d$ ), the increase of the

Figure 1.11 – Schematic cross-section of a p-type TFET (top). The energy band diagram (bottom) of the TFET is presented for its on-state (red line) and off-state (dashed blue line)[15].

gate voltage  $(V_g)$  modulates the device surface potential, which reduces  $\lambda$  and increases the energetic difference between the conduction band in the source and the valence band in the channel  $(\Delta\Phi)$ .

The subthreshold swing of a TFET can be calculated as:

$$SS = \frac{\partial V_g}{\partial (log_{10}Id)} = ln(10) \left[ \frac{\partial V_d}{V_d \partial V_g} + \frac{E \ b}{E^2} \frac{\partial E}{\partial V_g} \right]^{-1}, \tag{1.6}$$

where  $V_d$  is the drain voltage, E is the electric field, and b is a constant. Equation 1.6 reveals that the SS of a TFET is not limited by the Boltzmann electron energy distribution.

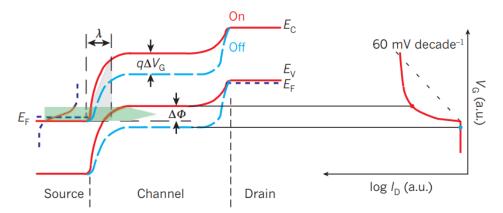

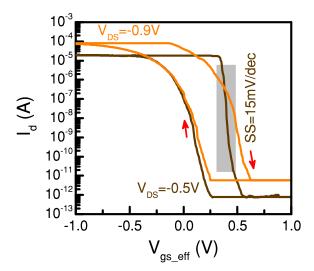

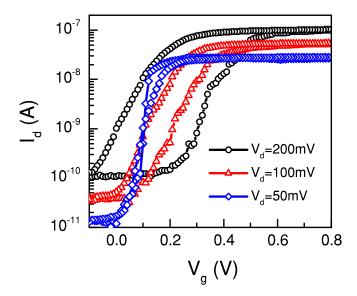

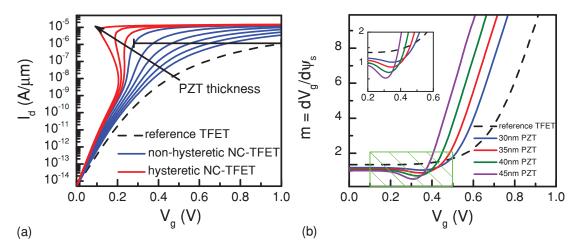

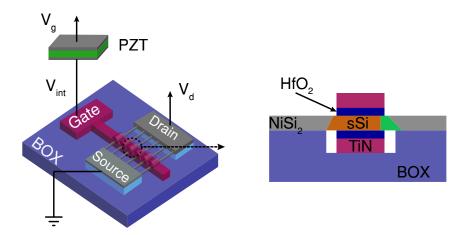

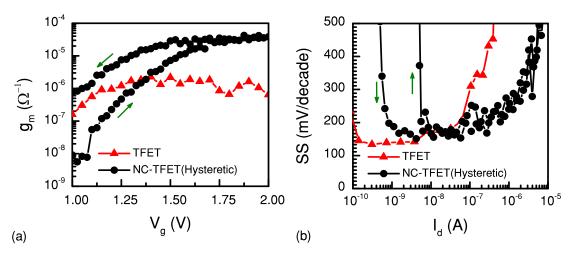

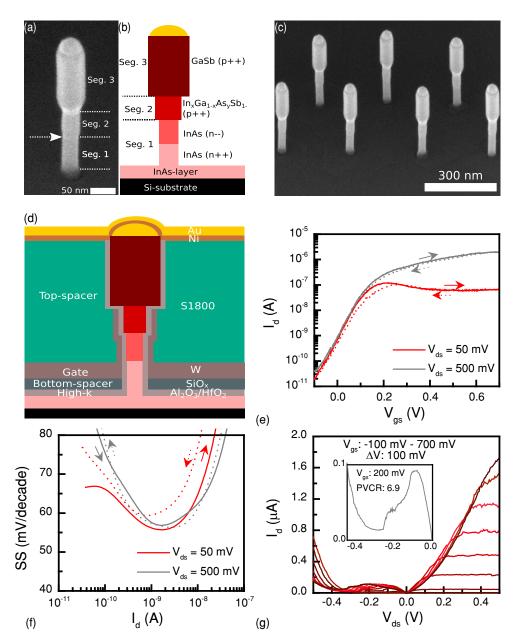

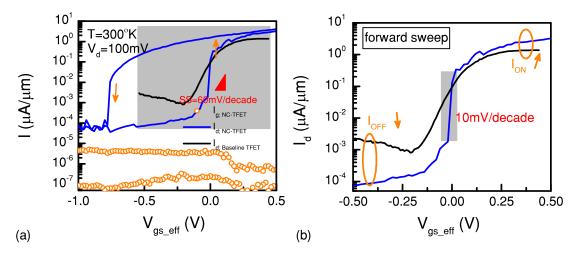

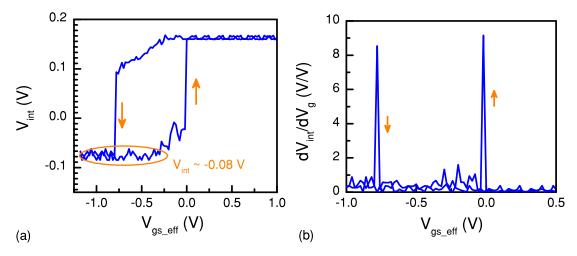

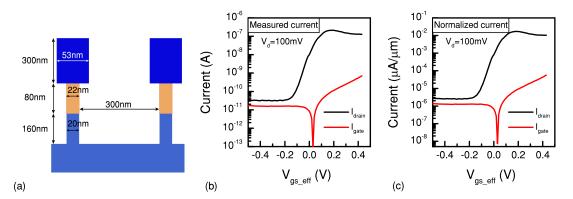

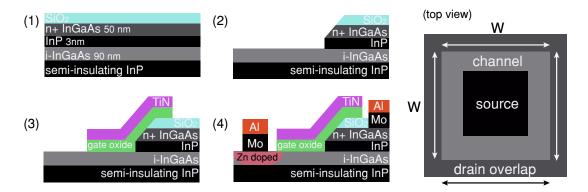

Recently, highly scaled vertical InAs/InGaAsSb/GaSb nanowire TFETs with well below 60 mV/decade subthreshold swings are experimentally fabricated [29, 30]. The nanowire structure and the corresponding electrical measurements of TFETs are depicted in Figure 1.12. Some of the presented devices show the ability to reach a value of SS down to 43 mV/decade. This outstanding performance has been achieved by realizing an extremely low defect interface regarding the III-V heterojunction, which is one of the main limitations to achieve an SS well below the thermal limit of MOSFETs in III-V TFETs.

However, the on-current of TFETs is unacceptably low for a technology which

Figure 1.12 – Nanowire structure (left) and electrical measurements (right) of vertical InAs/InGaAsSb/GaSb nanowire TFETs, showing a sub-thermionic swing [30].

would like to replace the CMOS technology. Moreover, achieving SS < 50 mV/decade is extremely challenging in the most fabricated TFETs and the steep slope region is typically limited to 1-3 decades of the drain current, which is far less than that of a MOSFET (4-6 orders). Therefore, providing an acceptable  $I_{ON}/I_{OFF}$  ratio together with a sufficiently low SS has emerged as one of the most important technology issues involved in the fabrication of TFETs.

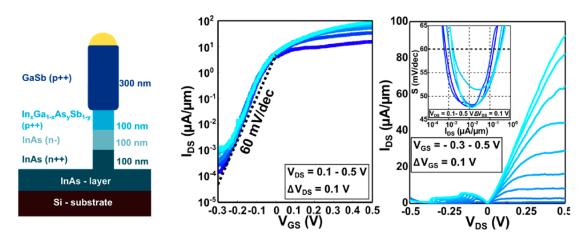

#### 1.3.3 Nano ElectroMechanical Field-Effect Transistors

The convergence of silicon CMOS and MEMS technologies in terms of functionality added devices that combine MEMS and solid-state principles, such as NanoElectroMechanical (NEM) FETs or Suspended-Gate (SG) MOSFETs [31]. This type of transistors has been suggested to break theoretical limitations of the solid-state MOSFET, such as the 60 mV/decade limit on the subthreshold swing [32].

The principle of the SG-MOSFET is shown in Figure 1.13 where a metal gate is suspended over the oxide or semiconducting channel of an MOS transistor by supporting arms (with an equivalent stiffness of k). When the gate voltage is set at 0 V, the air-gap between the gate and channel make the off-current of the transistor at its lowest possible value. By applying a voltage on the gate, a combined electro-mechanical action results: while the inversion of the channel is forming, the gate deflects vertically and increases the gate to channel capacitance. This leads to a super-exponential dependence of the inversion charge on the applied gate voltage in the subthreshold regime. The gate approaches the channel and at a point, when the equilibrium condition of the mechanical elasticity and the electric field is not anymore fulfilled, the gate collapses and sticks to the substrate. This results in an abrupt increase in the drain current [17].

Figure 1.13 – Schematic and operation principle of an SG-MOSFET (top) along with an experimentally fabricated device and its electrical characteristic (bottom) [33].

Figure 1.13 also shows the Scanning Electron Microscopy (SEM) image of a fabricated suspended-gate MOSFET with a physical length of 20  $\mu$ m and a width of 4  $\mu$ m. The transfer characteristic of the described switch demonstrates a super steep transition of 2 mV/decade. The main drawback of this kind of switches is the need for a high pull-in voltage (tens of volts). The suspended-gate MOSFET switch also suffers from the hysteresis of the drain current due to the additional force, which is required to eliminate the sticking energy and separate the gate from the substrate.

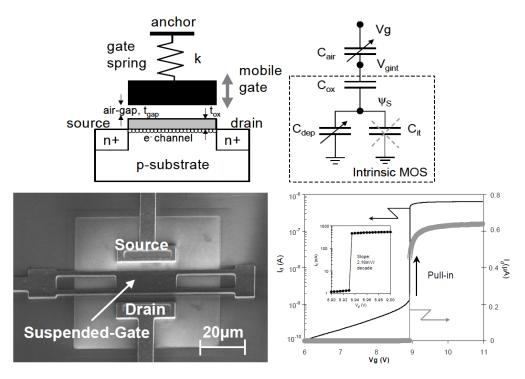

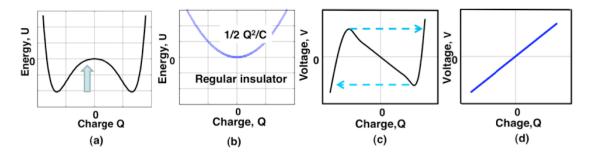

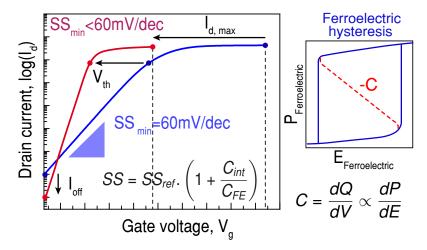

#### 1.3.4 Ferroelectric Field-Effect Transistors

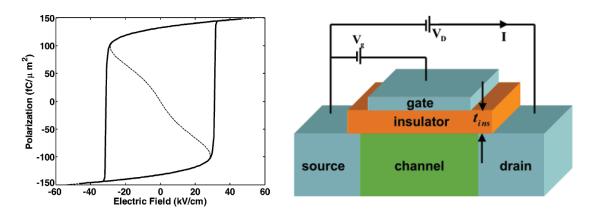

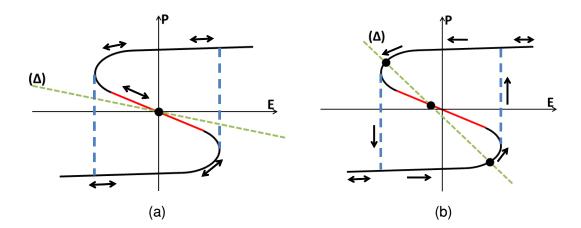

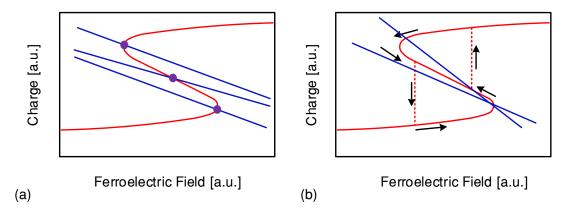

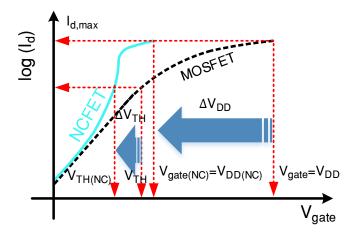

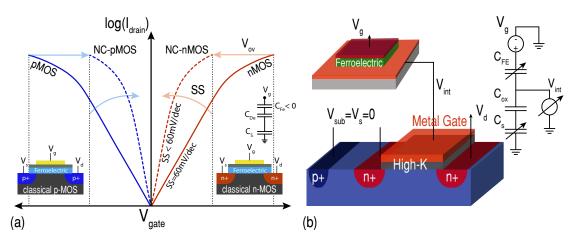

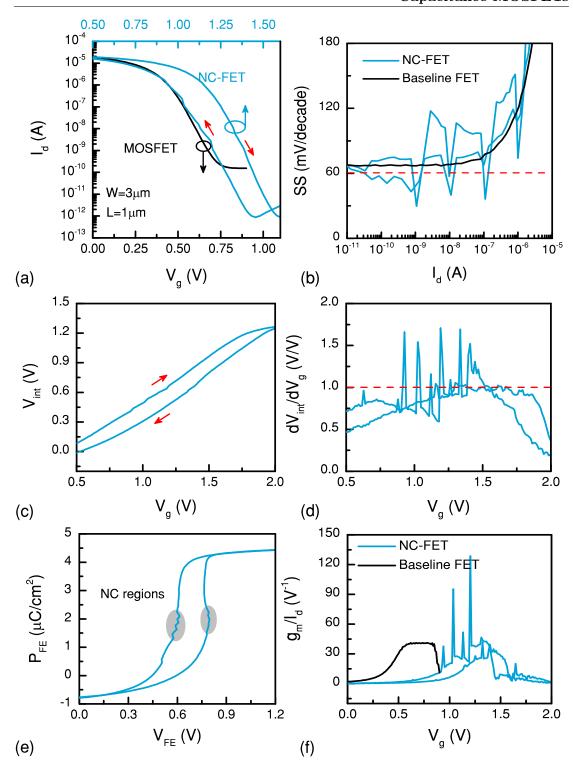

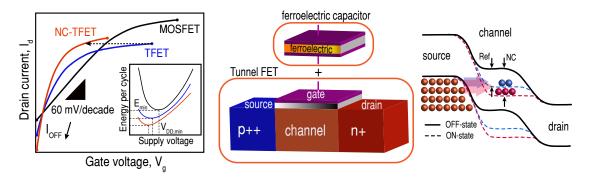

It has been proposed that if we integrate a ferroelectric insulator, having a polarization characteristic as described in Figure 1.14, into the gate stack of a conventional MOSFET, it is possible to obtain values of the body factor less than one and hence a value of SS below 60 mV/decade at  $300^{\circ}$  K [34, 35]. This can be understood by considering the fact that a ferroelectric capacitor can perform as an effective negative capacitance (NC) around the origin (Q = 0) [36]. This negative slope of the polarization is ordinarily unstable and cannot be observed in experiments, exhibiting hysteretic jumps in the polarization. However, it is evidenced that the noted negative segment can be stabilized if the ferroelectric placed in series with a positive capacitor of proper value [37].

Figure 1.14 – Polarization characteristic of a ferroelectric material and its ability to provide an effective NC while integrated to the gate of an MOS device [18].

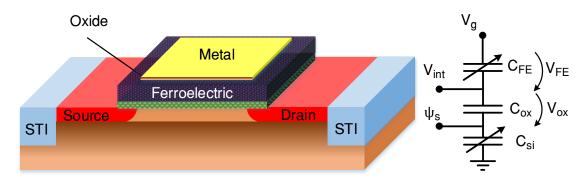

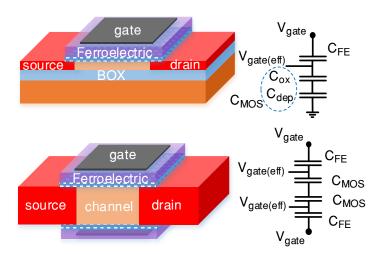

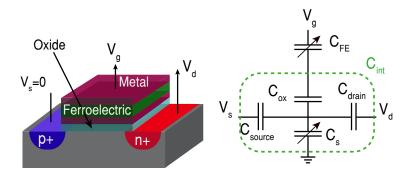

A ferroelectric capacitor interconnecting with the gate stack of an MOS transistor creates a series connection between the ferroelectric capacitor  $(C_{FE})$  and the gate intrinsic capacitance of the MOS transistor  $(C_{MOS})$ . The ferroelectric capacitor can increase the total capacitance of the gate  $(C_{total}^{-1} = C_{FE}^{-1} + C_{MOS}^{-1})$  if it operates in the NC regime. Accordingly, an NC booster can provide an internal voltage amplification which results in a body factor reduction, leading to an improved subthreshold [38].

The rest of this chapter is dedicated to ferroelectric materials, physics behind the negative capacitance of ferroelectrics, and the operation principle of NC transistors which are the main topics of interest in this thesis.

## 1.4 Ferroelectric materials

#### 1.4.1 History

The phenomenon of ferroelectricity was discovered in 1921 by J. Valasek who was investigating the dielectric properties of Rochelle salt (NaKC<sub>4</sub>H<sub>4</sub>O<sub>6</sub>.4H<sub>2</sub>O) [39]. At its early age, ferroelectricity was considered only as an academic curiosity with a little application value. Certainly, one of the major turning points in ferroelectricity came in the early 1940s with the discovery of unusual dielectric properties of mixed oxides that crystallize in the perovskite structure. Barium Titanate (BaTiO<sub>3</sub>) was discovered to be a robust ferroelectric in 1943 by A. Van Hippel. Since then, ferroelectric oxides were widely used as capacitors in the electronics industry. Afterward, until the 80s, the main challenges in ferroelectric materials were the modeling of the operation principle of ferroelectrics as well as the discovery of novel materials. Perhaps the most significant theoretical development in ferroelectricity occurred in 1960 with the formulation of the elegant soft-mode description of the ferroelectric transition made almost simultaneously and independently by Cochran and Anderson [40]. This was followed by integration of

ferroelectric thin films on silicon integrated circuits [41].

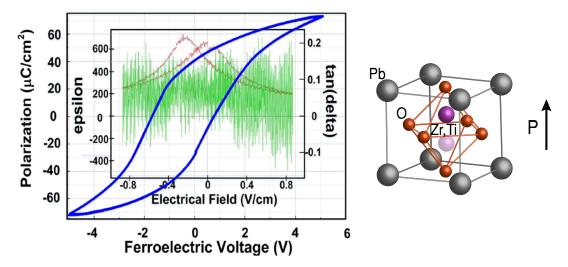

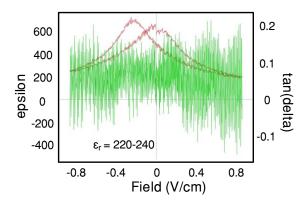

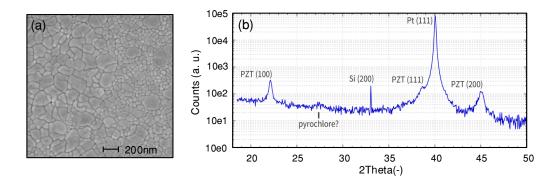

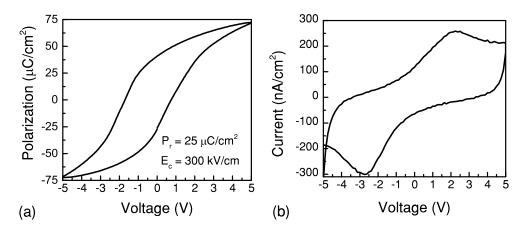

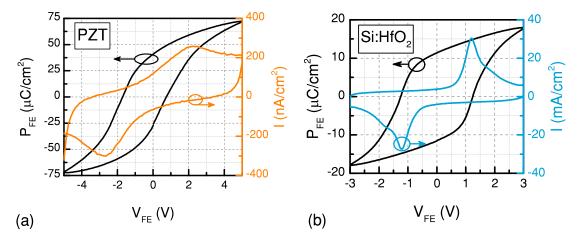

The development of ferroelectric thin films was a significant step towards the integration of this type of materials in electronic components. This can be highlighted by taking into account the polarization reversal of ferroelectrics as their main functionality. The base characteristic of all ferroelectric materials is the hysteretic behavior relating the polarization (P) to the electric field (E). There is a nominal threshold, called the coercive field ( $E_c$ ), above which the polarization changes sign. The polarization of a typical ferroelectric requires an electric field of about 50 kV/cm. This means that a 1 mm bulk ferroelectric needs about 5 kV to switch from one stable polarization state to the other one which is not suitable for any kind of electronic devices. However, for a thin film with a thickness of micrometer/nanometer range, the coercive voltage would be less than 5 V which opens a path to the integration of ferroelectrics in ICs [42].

The most important use of ferroelectric materials relates to the memory applications. Ferroelectrics offer an electrically switchable, two-state device. Such a device could encode the 1 and 0 states required for the Boolean algebra of binary computer memories [43]. Nowadays, there are several research directions regarding ferroelectricity such as ferroelectric memories (DRAM and FeRAM), finite size effect, substrate-film interface, piezoelectric devices, developing novel CMOS compatible ferroelectrics, and ferroelectric transistors as steep slope switches.

This thesis is focused on the applications of steep switching transistors by exploiting the negative capacitance region of ferroelectrics. A CMOS compatible ferroelectric, silicon-doped HfO<sub>2</sub>, is developed along this Ph.D. work. Additionally, the potentials of this type of ferroelectric as a negative capacitance booster of MOS transistors is investigated.

### 1.4.2 Ferroelectricity

A ferroelectric is a sort of materials that provide a permanent electric dipole. The name "ferroelectric" is taken from "ferromagnetic" as ferromagnetic materials have a permanent magnetic dipole. In fact, in one of the earliest observations of ferroelectricity by Rochelle, the salt was described as "analogous to the magnetic hysteresis in the case of iron" [39]. Ferroelectricity can be understood by looking in the physics of small molecules. A non-symmetric molecule has a dipole moment which is defined as

$$\overrightarrow{P} = \int dV \rho(\overrightarrow{r}) \overrightarrow{r}, \qquad (1.7)$$

Figure 1.15 – Crystal structure of BaTiO<sub>3</sub> in its two different polarization states [44].

where  $\rho(\overrightarrow{r})$  is the charge density of the molecule. Considering atoms as point charges  $Q_i$  at the corresponding position of  $R_i$ ;

$$\overrightarrow{P} = \sum Q_i \overrightarrow{R_i}. \tag{1.8}$$

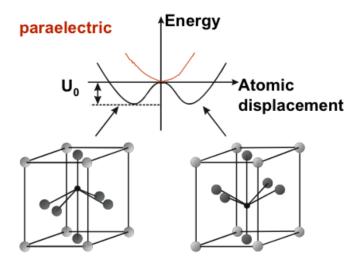

The ferroelectricity is prohibited if there is a center of symmetry. Otherwise, the crystal classes have one or more polar axis. Those with a unique polar axis are ferroelectric and provide spontaneous polarization. The rest demonstrate a piezoelectric effect, inducing an electric polarization under mechanical stress [37]. In another word, the spontaneous polarization of ferroelectrics originates from the atomic arrangement of ions in the crystal structure. A crystal with a polar group can provide a non-zero spontaneous polarization. However, in the case of ferroelectric materials, the polarization should be switchable between two stable states. The example of BaTiO<sub>3</sub>, as the first discovered robust ferroelectric, is depicted in Figure 1.15. The Ti ion displaced between two different states, breaking the symmetry.

In an electric field of  $\overrightarrow{E}$ , the two stable states no longer have the same energy due to the electric polarization energy of  $\overrightarrow{P}.\overrightarrow{E}$  and the wells get tilted by the externally applied electric field. It should be noted that the polarization does not switch immediately because there is a barrier to be overcome. In an ideal case, there will be hysteresis as it is presented in Figure 1.16 which simply explains the hysteretic behavior of a ferroelectric material. However, it should be noted that the mentioned explanation is too simple to describe the operation principle of real ferroelectrics due to the fact that all dipoles never switch together. Nucleation of the polarization reversal usually occurs in particular locations in a real ferroelectric. Each time that the polarization gets switched, domains

Figure 1.16 – Phase transition of ferroelectric BaTiO<sub>3</sub> [44].

nucleate at the same favorable sites. Afterward, the nucleate sites grow. The period of the domain growth strongly depends on the properties of the material itself, geometry, and the strength of the applied electric field [37].

#### 1.4.3 Landau's theory

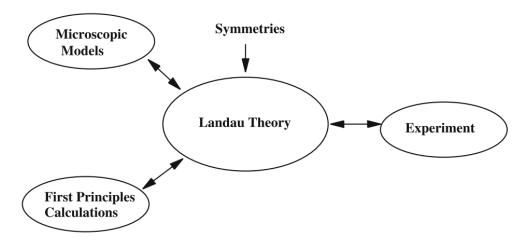

The Landau-Ginzburg-Devonshire theory (simply called Landau's theory) can provide a reliable description of a system's behavior near a phase transition based on symmetry considerations. The Landau's theory defines a phenomenological description of the macroscopic properties [46]. Generally, the thermodynamic state of a system in equilibrium can be determined by specific variables. In the case of bulk ferroelectrics, temperature (T), polarization (P), electric field (E), stress ( $\sigma$ ), and strain ( $\eta$ ) are the mentioned variables. A fundamental postulate of the applied thermodynamics to a ferroelectric is that its free energy G can be expressed as a function of 10 variables. The Landau theory actually expands the free energy in powers of the dependent variables, with known coefficients that can be fitted with experiments [34]. This approach is a straightforward phenomenology to link measurable thermodynamic quantities in the vicinity of a phase transition. It should be remarked that the Landau theory is a macroscopic model and cannot explain the microscopic physics behind the phase transition. Figure 1.17 depicts the schematic of the relationship between Landau's theory, first-approach calculations, microscopic models, and experimental data. In general, Landau's theory can be calculated from the first order calculation or a microscopic model and validated experimentally.

Here, we take a simple example and expand the free energy in terms of a single component of the polarization and ignore other variables, which can be adequate for a

Figure 1.17 – Relationship between the Landau theory and first-principles calculations, microscopic models, and experiment in the vicinity of a phase transition [45].

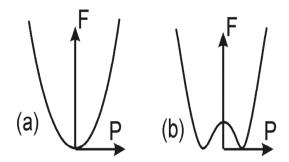

Figure 1.18 – Free energy as a function of polarization in case of a paraelectric (a) and a ferroelectric material (b) [37].

uniaxial ferroelectric. Therefore, the free energy can be written as [47]

$$G = \frac{1}{2}aP^2 + \frac{1}{4}bP^4 + \frac{1}{6}cP^6 + \dots - EP, \tag{1.9}$$

where we have dropped the vector signs as we have assumed one-dimensional spatial variation. In equation 1.9, E denotes to the electric field and a, b, and c are the material dependent parameters. The minima of the free energy defines the equilibrium condition, where we shall have

$$\frac{\partial G}{\partial P} = 0. \tag{1.10}$$

If the material coefficients of a, b, c, etc. are positive, the free energy performs a

Figure 1.19 – (a) Free energy as a function of the polarization at  $T>T_0$ ,  $T=T_0$ , and  $T<T_0$ . (b) Spontaneous polarization as a function of temperature. (c) Invers of the suseptibility,  $\chi$  [37].

minimum at the origin. In this case, equation 1.10 can be simplified as

$$\frac{\partial G}{\partial P} = aP - E = 0. \tag{1.11}$$

Equation 1.11 shows a linear relationship between the polarization and the electric field ( $\chi = P/E = 1/a$ ), which is actually the dielectric suseptibility of a paraelectric material.

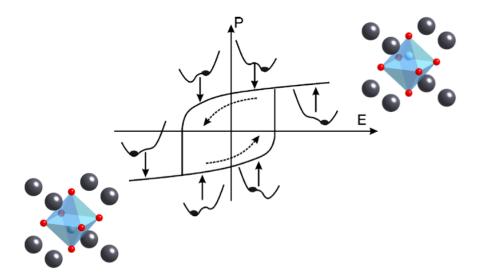

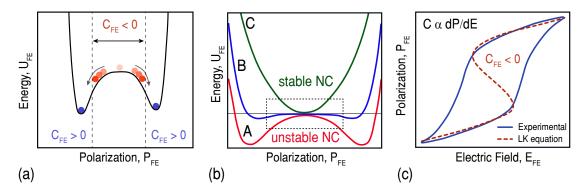

On the other hand, if a gets negative values, the free energy will look like Figure 1.18-b. In this case, the material is ferroelectric as it has a spontaneous polarization at its ground state. The behavior of ferroelectric materials suggests that a should be a temperature dependent parameter that changes sign at a specific temperature  $(T_0)$ . Thereby, a simple description of ferroelectrics can be obtained by a linear approximation of  $a = a' \times (T - T_0)$ . This approximation will predict the demonstrated free energy, polarization, and susceptibility in Figure 1.19. Therefore, a ferroelectric material is traditionally modeled using a double well energy landscape. In equilibrium the ferroelectric resides in one of the wells, providing spontaneous polarization.

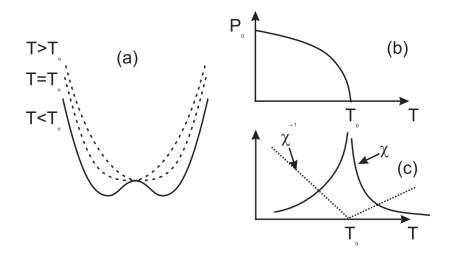

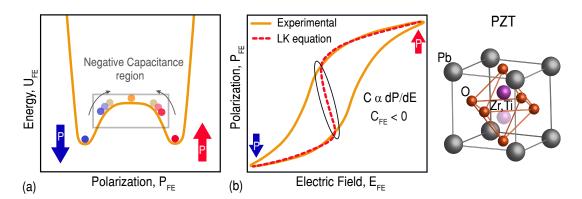

The capacitance of a ferroelectric material can be determined by

$$C_{FE} = \left[\frac{d^2 U_{FE}}{dQ_{FE}^2}\right]^{-1},\tag{1.12}$$

while  $Q_{FE} \propto P_{FE}$  and  $U_{FE}$  is the energy of the capacitor. Considering the curvature of the  $E_{FE}$  vs.  $P_{FE}$  of a ferroelectric near the noted wells (Figure 1.18-b), the capacitance of

Figure 1.20 – Eenrgy landscape and dU/dQ vs. Q plots of a ferroelectric and a linear dielectric [49].

a ferroelectric capacitor is positive in its equilibrium states. Nevertheless, this curvature is negative around the origin  $(Q_{FE} = 0)$  while the material is switching from one stable polarization state to the other one.

The negative capacitance has been proven elusive for ferroelectrics in isolation and cannot be observed in experiments, exhibiting hysteretic jumps in the polarization. However, it is evidenced that this negative segment can be stabilized if it is placed in series with a positive capacitor of the proper value. It should be remarked that NC refers to the "negative differential capacitance" due to the small signal concept of the capacitance and relationship between  $C_{FE}$  and  $U_{FE}$  (equation 1.12).

# 1.5 Negative Capacitance MOSFETs

It has been proposed that if the conventional insulator of a MOSFET transistor replaced with a stack includes a ferroelectric capacitor, it should be possible to obtain values of m-factor below 1 (Figure 1.14). A negative capacitor integrated into the gate stack of the transistor leads to a subthreshold swing below the thermal limit of MOSFETs. This can be further explained by considering equation 1.4 and taking into account that a ferroelectric can provide an effective negative capacitance. The main advantage of using NC to achieve a sub-60 mV/decade swing is that it does not change the operation principle of the MOS transistor and can be applied in parallel with any other performance boosters of CMOS technology [48].

The relation between the polarization (charge) and electric field (voltage) in a ferroelectric capacitor can be derived by the simplified form of the Landau's theory [48]:

$$E_{FE} = a'(T - T_0)P + b(T)P^3 + c(T)P^5.$$

(1.13)

Therefore, as demonstrated in Figure 1.20, the energy landscape and the dU/dQ vs. Q curve of a ferroelectric capacitor explains that how a ferroelectric material can provide

an effective NC near the origin.

It was previously noted that the negative slope part of the polarization is unstable and cannot be separately measured. This NC segment can be stabilized if a positive capacitor attached in series with the ferroelectric, making the total capacitance of the structure positive. If we replace the conventional insulator of a MOSFET with a ferroelectric one (or a stack that consists of a ferroelectric and a linear dielectric), the NC can be stabilized by the semiconductor capacitance (or the series of the semiconductor and linear dielectric capacitances). Indeed the negative permittivity of ferroelectrics can provide a signal amplification which can be understood in terms of a positive feedback mechanism. A non-linear capacitor can be modeled using the following equation [49]:

$$Q = C_0(V + \alpha Q). \tag{1.14}$$

In equation 1.14, the charge of the capacitor  $(C_0)$  is a function of the applied voltage (V) plus a voltage feedback of  $\alpha Q$ . Therefore, the capacitance of the ferroelectric insulator can be written as

$$C_{ins} = C_0/(1 - \alpha C_0).$$

(1.15)

In the case of negative capacitance,  $\alpha C_0$  is greater than one, which leads to instability until the non-linear term limits the charge.

In case of the proposed structure of the NC transistor in Figure 1.14, the negative capacitance part of ferroelectric can be stabilized by the semiconductor capacitance,  $C_s$ , and hence, the body factor can be defined as

$$\frac{\partial V_g}{\partial \psi_s} = 1 + \frac{C_s}{C_{ins}} = 1 - \frac{C_s}{C_0} (\alpha C_0 - 1). \tag{1.16}$$