© 2019 IEEE

PCIM Europe 2019; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management; Proceedings of

# Low Voltage Modular Multilevel Converter Submodule for Medium Voltage Applications

M. Utvic, I. Lobos, and D. Dujic

This material is posted here with permission of the IEEE. Such permission of the IEEE does not in any way imply IEEE endorsement of any of EPFL's products or services. Internal or personal use of this material is permitted. However, permission to reprint / republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to pubs-permissions@ieee. org. By choosing to view this document, you agree to all provisions of the copyright laws protecting it.

# Low Voltage Modular Multilevel Converter Submodule for Medium Voltage Applications

Milan Utvić, Ignacio Polanco Lobos, Dražen Dujić

Power Electronics Laboratory, École Polytechnique Fédérale de Lausanne (EPFL), Switzerland

Corresponding author: Milan Utvić, milan.utvic@epfl.ch

The Power Point Presentation will be made available after the conference.

#### **Abstract**

Modular multilevel converters have been subject to various research topics in the area of medium voltage conversion. The basic building block of all modular multilevel converters is the submodule, which despite being simple in terms of its topology, poses significant integration challenges when it comes to practical implementation. This paper provides an insight into the structure, design considerations and operation of the modular multilevel converter low voltage submodule for medium voltage applications. Special attention was paid to the submodule specific power and control parts, which were all experimentally tested, with all results being presented in the paper.

#### 1 Introduction

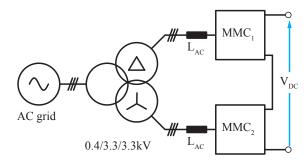

Emergence of Medium Voltage (MV) DC grids creates the need for a highly flexible and efficient DC power source. One such possibility is presented in Fig. 1, where the conventional twelve pulse transformer (commonly used in combination with diode/thyristor rectifiers) is connected with two Modular Multilevel Converters (MMCs) having their DC terminals connected in series. Replacement of the diode/thyristor rectifiers with the MMCs enables the grid current controllability, fast and flexible DC voltage generation, able to counteract the short circuits across the converter DC terminals. Converter being developed is rated at 500 kVA and should be able to generate arbitrary voltage in the range of  $\pm 10\,\mathrm{kV}$  at its DC terminals.

So far, a number of MMC research prototypes have been reported in the literature, yet most of them developed as a Low Voltage (LV) prototypes [1]–[4], with rated power up to 45 kW [1]. Notable exception from academia of a 2 MW rated power MMC based AC/AC converter is presented in [5], whereas very few information from industry could be found. Integration of various technologies for an IGBT Submodule (SM) has been presented in [6], whereas [7] provides a

Fig. 1: Structure of the MMC based rectifier

thorough comparison between IGBT and IGCT semiconductor technologies in MMCs for AC/AC railway power supply applications, thus being valuable resource from the industry.

This paper presents the overall structure, design considerations and operation of the MMC SM for MV applications. Descriptions are accompanied by the experimental results, validating the correctness of the design procedure. SM is realized with LV semiconductors, and it could be used in any other MMC based topology, providing voltage and power ratings of the SM are not violated.

#### 2 Submodule Structure

The use of MMC provides an opportunity to realize a highly flexible, bipolar DC source, given that a bipolar SMs are used [8]. Although various topologies of a bipolar SMs exist in the literature [9], developed SM is realized utilizing Full Bridge (FB) topology, mainly due to simplicity reasons. Despite simple in terms of its topology, practical implementation of MMC SM being used in MV application poses significant integration challenges, such as the need for an auxiliary power supply, proper insulation coordination, employment of internal protection, proper thermal design, current and voltage measurements, certain communication links with upper level controllers, etc.

Utilizing commercially available LV power components was the foundation for the converter design, and it was mainly driven by low cost design targets. Therefore, bipolar property of the submodule has been achieved with 1200 V IGBT H-bridge module, with a possibility of effortless mechanical reconfiguration to the unipolar structure. The choice of the 1200 V rated IGBT module and 5 kV DC voltage rating of a single MMC imposed the need for N=8 SMs per single MMC branch, with each SM average voltage being set as 625 V.

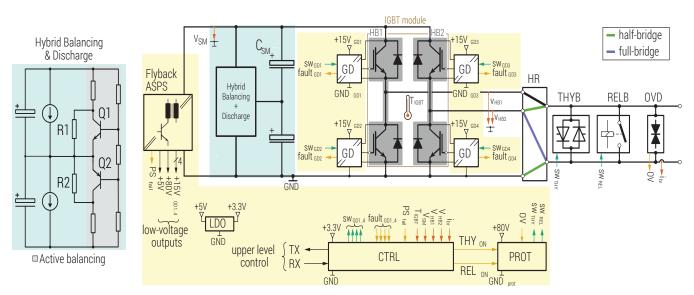

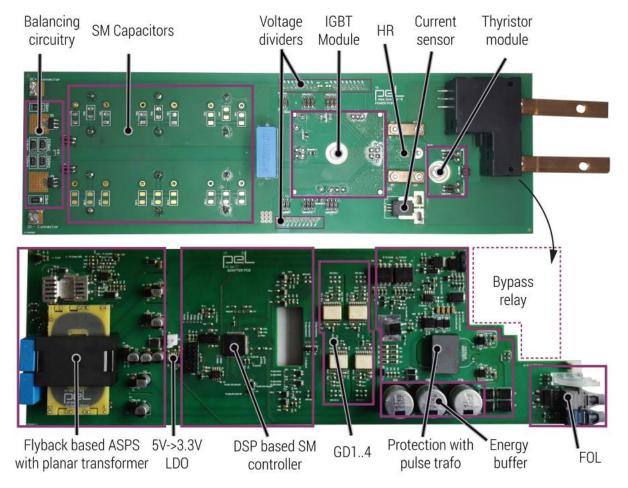

The structure of realized SM is shown in Fig. 2. It has several electronic circuits performing different functions, which are organized and split between two interconnected Printed Circuit Boards (PCBs): Power PCB and Control PCB, as described in details, hereafter.

#### 3 Power PCB

Power PCB is a power processing part of the SM, hosting its main power components: IGBT H-bridge module and the bank of electrolytic capacitors. Apart from the key components, Power PCB also accommodates SM voltage and current measurement circuits, SM protection devices, capacitor balancing and discharge circuit, power terminals and board-to-board connectors with the Control PCB.

#### 3.1 IGBT module

IGBT module from Semikron is rated at 1200 V/50 A, and features NTC temperature sensor [10]. By means of mechanical reconfiguration (HR in Fig. 2), also hosted at the Power PCB, it is possible to change the SM structure to unipolar, thus doubling its current capability to 100 A.

# 3.2 SM capacitor bank

Submodule capacitor bank was designed according to the permissible energy ripple within a MMC branch (determines the capacitance value), as well as according to the admissible AC current ripple per capacitor (determines the number of paralleled capacitors).

Series connection of two electrolytic capacitors within the SM is necessary as the SM rated voltage (625 V) is higher than the rated voltages of commercially available electrolytic capacitors (450 V in our case). Therefore, the SM capacitor

Fig. 2: MMC Submodule structure. Parts hosted at the Control PCB are labeled yellow.

Fig. 3: Developed MMC Submodule: Power PCB (Top), Control PCB (Bottom)

capacitor branches, each one of them consisting of a series connection of two 1.5 mF capacitors, giving the equivalent capacitance of  $C_{SM}$ = 2.25 mF. Employment of series connection of 450 V maximum rated capacitors within the SM, demands the insulation coordination being conducted for maximum expected SM voltage of  $V_{SMmax}$ =900 V. Furthermore, appropriate control and protective measures have to be taken in order to ensure that capacitor voltage does not exceed the limits. As expected, the problem of voltage sharing between such two capacitor groups arises, therefore hybrid balancing circuitry is utilized.

bank is realized as a parallel connection of three

#### 3.3 Hybrid balancing circuit

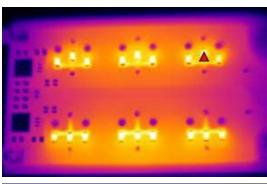

Initially, simple and well known passive balancing circuit was considered and implemented in the design. In order to maintain the voltage difference between the upper and the lower capacitor banks

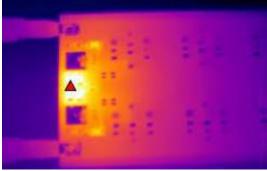

of the SM within the range of  $\pm 7$  V, three passive balancing resistors of  $62\,\mathrm{k}\Omega$  are mounted in parallel with each SM capacitor. Experiments (c.f. Fig. 4 (top)) have proven that this arrangement of resistors provides the balancing function, yet with the cost of prohibitively high power losses (30 W at  $V_{\text{SM}}$ =650 V).

Another approach was to consider hybrid balancing with the aim of reducing power losses, while preserving balancing performance. As shown in Fig. 2, it consists of Active Balancing (AB) circuit introduced in [11], reinforced with the two additional resistors, R1 and R2, in parallel with the transistors Q1 and Q2, respectively. Those two resistors aim to prevent over-voltages across the accompanied transistors, as well as to serve as a backup solution in case of fault of any of the transistors within the AB circuit. Under the faulty terms, additional resistors take over the role of passive balancing circuit.

Experiment with hybrid balancing was conducted

**Fig. 4:** Thermal images of the passive (top) and hybrid balancing (bottom)

(c.f. Fig. 4 (bottom)), and the power consumption was measured to be 4.7 W. Therefore, hybrid balancing shows great advantage over the passive balancing method in terms of significant power consumption reduction for the same balancing performance, without penalizing the circuit reliability and cost.

#### 3.4 Voltage and current measurements

Voltage and current measurements within the SM are hosted at the Power PCB. Current sensing (i<sub>br</sub> in Fig. 2) is realized with Allegro ACS759 Hall-effect-based linear current sensor with 100  $\mu\Omega$  internal resistance, having the performance optimized at 3.3 V. Measured current values are passed on to the SM's main controller.

Voltage measurements are performed at the three specific points within the SM: SM capacitor voltage ( $V_{SM}$  in Fig. 2), as well as the Half-Bridge (HB) voltages of the IGBT module with respect to SM ground ( $V_{HB1}$  and  $V_{HB2}$  in Fig. 2). Measurements are performed by means of resistive voltage dividers, and adjusted to match the 3.3 V range, suitable to the SM's main controller. HB voltage measurements are of particular importance to the SM's protection logic, as they provide feedback

information about the protection activation.

#### 3.5 Protection devices

Submodule's protection consists of protection devices, situated between the SM's terminals, and protection logic that activates the devices, which is hosted at the Control PCB. Protection is realized by means of bypass thyristor module (THYB) and bypass relay (RELB), which bypass the SM in case of fault, as well as Over-Voltage Diodes (OVDs), aiming at over-voltage detection and protection activation.

### 4 Control PCB

Control logic of the SM is accommodated at the socalled Control PCB. Layout of the Control PCB is presented in Fig. 3, from which several mutually independent circuits can be identified: Auxiliary Submodule Power Supply (ASPS),SM's main controller, gate drivers' circuits, SM's protection logic and fiber-optic communication link (FOL). By means of board-to-board connectors, which provide both mechanical support and electrical connection, Control PCB is mounted on the top of the Power PCB.

#### 4.1 Auxiliary Submodule Power Supply

In order to simplify insulation requirements in the surrounding of the SM, as well as due to the simplicity of implementation, a Flyback converter with multiple outputs, supplied from the SM's capacitor, was chosen as a solution for the ASPS. Its simplicity lies in the fact that a single switch controls multiple transformer's secondary outputs by means of cross-regulation. Flyback transformer is realized as a planar transformer with PCB integrated windings, and hosts seven secondary windings in total. Feedback voltage used in regulation is a +5 V output, which is further on regulated to +3.3 V by means of Linear Dropout Regulator (LDO), for the purpose of the SM's main controller supply. Another secondary output provides +15 V, used as a self-supply to the main Flyback PWM controller. Apart from this secondary, four +15 V secondaries with floating grounds supply the four IGBT gate drivers. Proper insulation coordination between upper and lower gate drivers was considered. Protection trigger

**Fig. 5:** Flyback based ASPS operation: startup (top), normal operation (middle), SM bypass and ASPS shutdown (bottom)

circuitry is powered by +80 V secondary output with floating ground. This voltage level was chosen so as to provide enough energy reserve within the protection trigger circuitry, utilizing relatively small storage capacitors. This energy reserve is of particular importance in case of ASPS fail, when the protection activation relies solely upon the energy reserve.

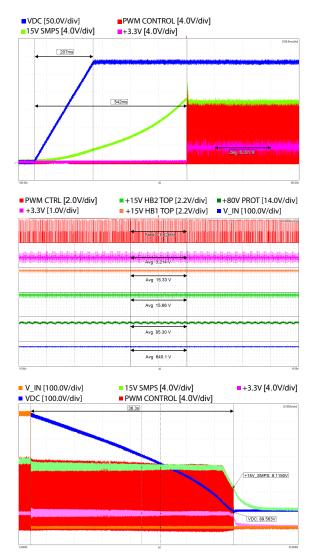

Fig. 5 presents the results of the experiments conducted to verify the ASPS functionality. Due to the fact that ASPS is internally supplied, SMs have to be passively charged, until the ASPS is activated. During charging of the MMC SMs from the AC side terminals, externally installed precharge resistors limit the inrush currents. During that period SMs are charged through their freewheeling diodes, until

each SM attains 290 V, which corresponds to the peak line voltage divided by the total number of SMs per phase leg. This voltage is sufficient to activate the Flyback based ASPS, which boots the SM's main controller and establishes communication with upper layer controller, bringing the MMC into operational state.

In order to emulate this process, the SM is connected to the controllable power supply, which attains 290 V within 200 ms, corresponding to the real charging conditions in the prototype under development. Fig. 5 (top) shows that it takes around 500 ms for the ASPS to start the normal operation. The same figure (middle) shows the normal ASPS operation, where the SM is connected to 650 V Direct Current (DC) power supply, which closely corresponds to its normal operating point. Finally, at bottom part of the figure the shutdown process of the ASPS is shown. SM is bypassed, therefore due to the consumption of the ASPS the SM capacitor is being discharged (voltage labeled as VDC in Fig. 5). Once the ASPS is turned-off resistors within the hybrid balancing circuit provide a slow discharge of the residual energy.

#### 4.2 Main SM controller

controller is realized SM by means TMS320F28069 Digital Signal Processor (DSP). It handles multiple functions, such as: communication with upper level control (through Fiber Optic Link (FOL)), voltage and current measurements (V<sub>SM</sub>, V<sub>HB1</sub>, V<sub>HB2</sub>, i<sub>br</sub>), decentralized modulation through gate driver switching signals (SW<sub>GD1..4</sub>), monitoring the SM condition (IGBT module temperature (T<sub>IGBT</sub>), IGBT gate driver fault state (fault GD1..4), ACPS failure with PS<sub>fail</sub>, etc). In case of fault on any of these devices, SM protection is activated and the SM is bypassed. Controller communication with the upper level control system is achieved through the FOL, where valuable information are exchanged, such as command signals, SM state-of-charge, etc.

#### 4.3 Gate drivers

SM gate drivers are realized by means of Avago ACPL-332J optocouplers, ideally suited for driving IGBTs in a voltage range up to 1200 V and 150 A. Short circuit supervision along with desaturation detection is implemented, and feedback signals are provided to SM's main controller.

**Fig. 6:** SM protection test: bypass thyristor activation (top), bypass relay activation (middle), overvoltage detection (bottom)

#### 4.4 SM Protection

Protection of the SM is realized by means of antiparallel thyristors, providing the temporary bypass, and permanent bypass implemented with bi-stable relay. Once the faulty condition is detected within the SM, its main controller issues the command for protection activation. At first, bypass thyristor module is activated, and its primary role is to provide temporary path to the branch current until the relay closes its contacts, thus providing permanent bypass of the SM.

SM is also protected against an excessive voltages across its power terminals. It is realized utilizing transil OVDs, which go into the breakdown once the voltage across the SM's terminals exceeds  $V_{SMmax}$ =900 V. Over-voltage detection results in both bypass thyristor and relay activation.

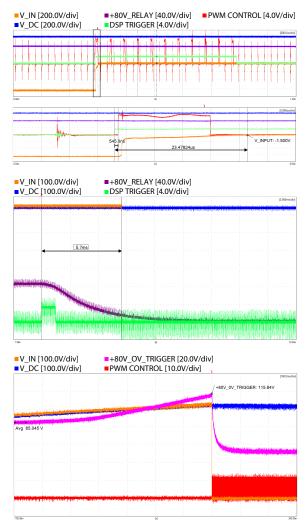

Functionality of the SM protection has been thoroughly experimentally tested and three different scenarios are shown in Fig. 6.

In the first case, bypass thyristor has been triggered from the SM's main controller and it took 545 ns for the protection circuitry to fire its first thyristor turn-on pulse. It can be noticed from the Fig. 6 (top) that the thyristor bypassed the SM terminals 23  $\mu s$  after the DSP command was issued. Two anti-parallel-connected thyristors are pulsed with 10 kHz (with 10 % duty cycle) signal, thus providing the path for either current direction.

Middle plot of Fig. 6 demonstrates the functionality of the bypass relay. It has been measured that the relay closes its contacts within 5.7 ms from the moment when the DSP command is issued. This confirms the need for the anti-parallel-connected thyristors as a fast, temporary bypass. Should the SM be unprotected for this amount of time, it would be exposed to the hazardous risks.

Finally, activation of the SM's protection in case of over-voltage detected at the terminals is demonstrated in the Fig. 6 (bottom). Down-scaled test has been carried out, where the voltage across the SM's terminals was gradually increased up to the point where it triggered the protection. In this case, SM's main controller did not issue any command, but the protection was activated owing to the breakdown of the transil OVD diodes, detected by the protection circuitry.

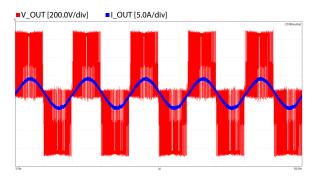

## 5 Power test

Finally, scaled down power test of the SM is conducted (limited due to ratings of the used power supplies). SM capacitor bank was connected to the constant DC power supply, whereas an inductive load was connected to its power terminals. This test aimed to verify the functionality of the SM's main controller, gate drivers, and IGBT module. Fig. 7 shows the pulse-width-modulated output voltage as well as the SM output current. Bipolar modulation is implemented, and test is conducted at SM rated voltage, with the switching frequency of 1 kHz. Even though the switching frequency was higher than the one intended for the SM regular operation, it was possible at the cost of reduced output current during the test.

Fig. 7: Power test of the developed SM

# 6 Submodule integration

From the converter point of view, various analyses were conducted which influenced the SM design. Although their complexity and objectives exceed the scope of this paper, its worth mentioning it for the sake of completeness.

# 6.1 Thermal design

Proper SM evaluation in terms of the IGBT module and capacitor power losses has been conducted, considering real operating conditions. simulations were performed and apart from the fundamental AC current component, both DC and second harmonic circulating currents are Apparent switching frequency of considered. 3 kHz, corresponding to a SM switching frequency of  $f_{SW_{SM}}$  = 250 Hz was used in simulations, as presented in [12]. It has been shown that the worst operating condition in terms of IGBT power losses corresponds to the unity power factor with 58 W of losses, whereas in terms of capacitor losses it has been shown that the peak value of 5W occurs at the zero power factor. Taking the former losses into consideration, along with the most critical ambient conditions, proper heatsink was chosen.

SM's enclosure, besides its mechanically protective and field shaping functions, has the role of providing the proper airflow path through the SM's heatsink and around the capacitors. Cabinet level cooling is conceived to be realized as forced air cooling with the airflow at the SM's outtake being 45 m<sup>3</sup>/h. FEM simulations have been carried out and verified the performance of the cooling system [12].

#### 6.2 Insulation coordination

Necessary insulation clearance and creepage distances wihin the SM are determined in accordance with the UL 840 standard, whereas the insulation coordination at the converter level has been conducted considering safety standard IEC 61800-5-1.

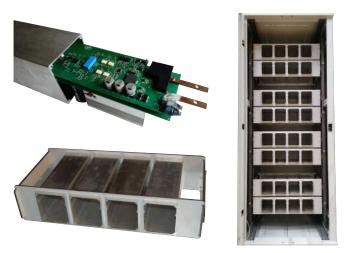

Each SM is enclosed in an aluminum box, providing shielding, protection and shaping of the surrounding electric field at the corners below the critical levels, considering air insulation inside the cabinet. Its protruded front and back leads provide path to the air flow of the cooling system. Detailed analysis of the overall converter insulation has been conducted in [13], while the realized mechanical subsystems are shown in Fig. 8.

#### 7 Conclusion

This paper presented the structure and design considerations of the LV MMC SM for MV applications. Although simple at the first glance, owing to the simple schematics of the power circuit, developing a reliable MMC SM requires a lot of engineering effort. Integration of various part, with different tasks being assigned to them, was demonstrated, showcasing the excellent and reliable operating performance of the constructed SM. Realized MMC platform allows for great flexibility in conducting various research activities, results of which will be reported in the near future.

**Fig. 8:** SM with aluminum enclosure (top), SM's drawer (bottom), MMC cabinet (right)

# **Acknowledgment**

This research project is part of the Swiss Competence Center for Energy Research SCCER FURIES of the Swiss Innovation Agency Innosuisse.

#### References

- [1] J. Yu, R. Burgos, N. R. Mehrabadi, and D. Boroyevich, "Design of a SiC-based modular multilevel converter for medium voltage DC distriution system", in 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), 2017, pp. 467–473.

- [2] D. Peftitsis, G. Tolstoy, A. Antonopoulos, J. Rabkowski, J. Lim, et al., "High-Power Modular Multilevel Converters With SiC JFETs", IEEE Transactions on Power Electronics, vol. 27, no. 1, pp. 28–36, 2012.

- [3] G. Konstantinou, S. Ceballos, I. Gabiola, J. Pou, B. Karanayil, and V. G. Agelidis, "Flexible prototype of modular multilevel converters for experimental verification of DC transmission and multiterminal systems", in 2017 Asian Conference on Energy, Power and Transportation Electrification (ACEPT), 2017, pp. 1–6.

- [4] L. Bessegato, A. Narula, P. Bakas, and S. Norrga, "Design of a Modular Multilevel Converter Prototype for Research Purposes", in 2018 20th European Conference on Power Electronics and Applications (EPE'18 ECCE Europe), 2018, P.1–P.10.

- [5] M. Glinka, "Prototype of multiphase modular-multilevel-converter with 2 MW power rating and 17-level-output-voltage", in 2004 IEEE 35th Annual Power Electronics Specialists Conference (IEEE Cat. No.04CH37551), vol. 4, 2004, 2572–2576 Vol.4.

- [6] D. Cottet, F. Agostini, T. Gradinger, R. Velthuis, B. Wunsch, et al., "Integration technologies for a medium voltage modular multi-level converter with hot swap capability", in 2015 IEEE Energy Conversion Congress and Exposition (ECCE), 2015, pp. 4502–4509.

- [7] D. Weiss, M. Vasiladiotis, C. Banceanu, N. Drack, B. Odegard, and A. Grondona, "IGCT based Modular Multilevel Converter for an AC-AC Rail Power Supply", in PCIM Europe 2017; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 2017, pp. 1–8.

- [8] A. Christe and D. Dujic, "Virtual Submodule Concept Applied to the Modular Multilevel Converter", in PCIM Europe 2017; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 2017, pp. 1–8.

- [9] G. Konstantinou, J. Zhang, S. Ceballos, J. Pou, and V. G. Agelidis, "Comparison and evaluation of sub-module configurations in modular multilevel converters", in 2015 IEEE 11th International Conference on Power Electronics and Drive Systems, 2015, pp. 958–963.

- [10] Semikron. (23-03-2016). SK50GH12T4T Datasheet, [Online]. Available: https:// www.semikron.com/dl/service-support/ downloads/download/semikron-datasheetsk-50-gh-12t4-t-24915220.pdf.

- [11] C. Odell Arthur B. (Cupertino. (2004). Method and apparatus for balancing active capacitor leakage current, [Online]. Available: http://www.freepatentsonline.com/6738277.html.

- [12] E. Coulinge, A. Christe, and D. Dujic, "Electro-Thermal Design of a Modular Multilevel Converter Prototype", in *PCIM Europe 2016; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management*, 2016, pp. 1–8.

- [13] A. Christe, E. Coulinge, and D. Dujic, "Insulation coordination for a modular multilevel converter prototype", in 2016 18th European Conference on Power Electronics and Applications (EPE'16 ECCE Europe), 2016, pp. 1–9.