# Design of approximate and precision-scalable circuits for embedded multimedia and neural-network processing

Thèse N°9144

Présentée le 1<sup>er</sup> février 2019

à la Faculté des sciences et techniques de l'ingénieur Laboratoire de circuits intégrés Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

# Vincent Frédéric CAMUS

Acceptée sur proposition du jury

Prof. C. Dehollain, présidente du jury Prof. C. Enz, directeur de thèse Dr M. Pons Solé, rapporteur Prof. M. Verhelst, rapporteuse Dr A. Vachoux, rapporteur

I am just a child who has never grown up. I still keep asking these 'how' and 'why' questions. Occasionally, I find an answer.

— Stephen Hawking

# Acknowledgements

First and foremost, I would like to thank my thesis advisor, Prof. Christian Enz, for his continuous support. Besides all his technical advices, he has always kept me motivated and has encouraged me to push myself and aim for the highest goals.

My sincere thanks also go to Prof. Marian Verhelst, who offered me an opportunity to join her team and to conduct thrilling studies in the field of Machine Learning. She has helped me a lot with insightful advices and the finest guidance towards new research directions.

I would also like to thank all the members of my thesis committee, Prof. Catherine Dehollain, Dr. Marc Pons Sole, Dr. Alain Vachoux, Prof. Marian Verhelst and Prof. Christian Enz for carefully reading my manuscript and for their constructive questions and comments.

Thank you to Lysiane Bourquin, Sandrine Piffaretti, Marcella Giovannini, Lucie Auberson and Marie Halm for their administrative support, to Dr. Alain Vachoux for his support with CAD tools, as well as Aymeric, Alex, Nadine, Patrick, Ryan and all the members of the MBC for their technical support.

A big thanks to my colleagues, Jérémy, Mattia, Vladimir, Raffaele, Francesco, Sammy, Camilo, Arnout, Chunmin, Alessandro, Farzan, Nino, Assim, Minhao, Daniel, Marta, Huaiqi, Claudio, Raghav, Anurag and Maria-Anna. They all made the time spent at work enjoyable, with fun or serious conversations, technical or non-technical discussions, and French or Italian food! I would like to dedicate a special shout-out to the colleagues and friends at LMTS (EPFL) and MICAS (KU Leuven) to have integrated me in the social life of their labs.

Finally I would like to thank my parents, my sister and my family, who always supported me in my life and in my studies, and all my friends who are bringing joy and fun to my life. Last but not least, I want to thank my wife Saki who always encourages me and continuously fills my life with love and happiness.

Vincent Camus December 18, 2018

# Abstract

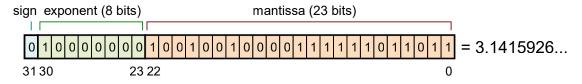

Density, speed and energy efficiency of integrated circuits have been increasing exponentially for the last four decades following Moore's law. However, power and reliability pose several challenges to the future of technology scaling. Approximate computing has emerged as a promising candidate to improve performance and energy efficiency beyond scaling. Approximate circuits explore a new trade-off by intentionally introducing errors to overcome the limitations of traditional designs. This paradigm has led to another opportunity to minimize energy at run time with precision-scalable circuits, which can dynamically configure their accuracy or precision. This thesis investigates several approaches for the design of approximate and precision-scalable circuits for multimedia and deep-learning applications.

This thesis first introduces architectural techniques for designing approximate arithmetic circuits, in particular, two techniques called Inexact Speculative Adder (ISA) and Gate-Level Pruning (GLP). The ISA slices the addition operation into multiple shorter sub-blocks executed in parallel. It features a shorter speculative overhead and a novel error correction-reduction scheme. The second technique, GLP, consists in a CAD tool that removes the least-significant logic gates from a circuit in order to reduce energy consumption and silicon area. These conventional techniques have been successfully combined together or with overclocking.

The second part of this thesis introduces a novel concept to optimize approximate circuits by fabrication of false timing paths, i.e. critical paths that cannot be logically activated. Codesigning circuit timing together with functionality, this method proposes to monitor and cut critical paths to transform them into false paths. This technique is applied to an approximate adder, called the Carry Cut-Back Adder (CCBA), in which high-significance stages can cut the carry propagation chain at lower-significance positions, guaranteeing a high accuracy.

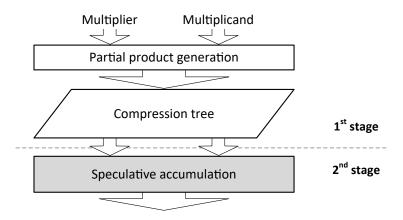

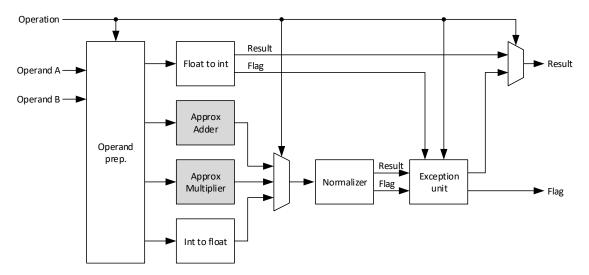

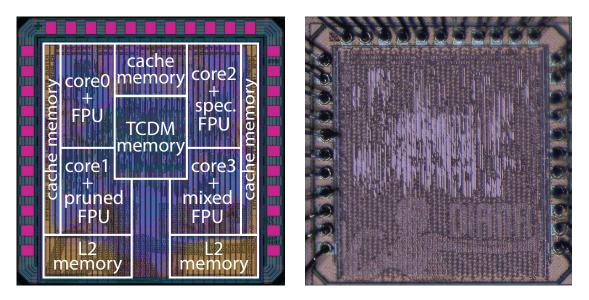

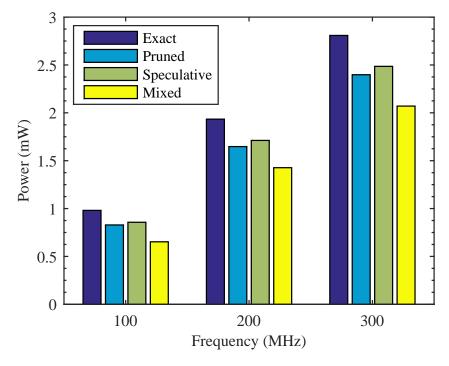

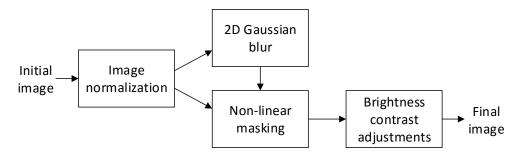

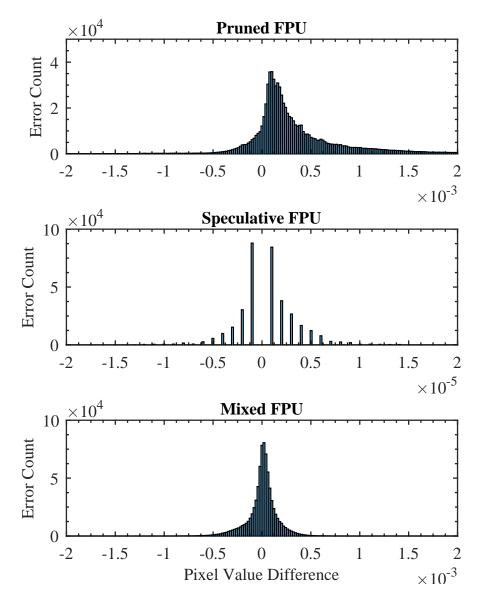

The third part of this thesis investigates approximate circuits within bigger datapaths and applications. The ISA concept is extended to a novel Inexact Speculative Multiplier (ISM). ISM, ISA and GLP techniques are then used to build approximate Floating-Point Units (FPU) taped-out in a 65nm quad-core processor. Approximate FPU circuits are validated through a High-Dynamic Range (HDR) image tone-mapping application. HDR imaging is a rapidly growing area in mobile phones and cameras extensively using floating-point computations. Results of the application show no visible quality loss, with image PSNR ranging from 76 dB using the pruned FPU to 127 dB using the speculative FPU.

## Abstract

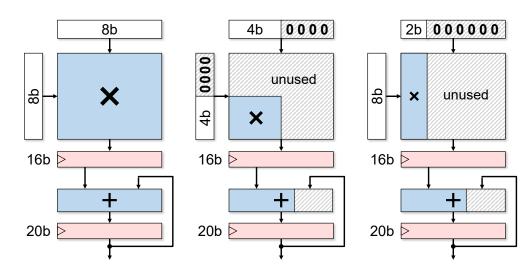

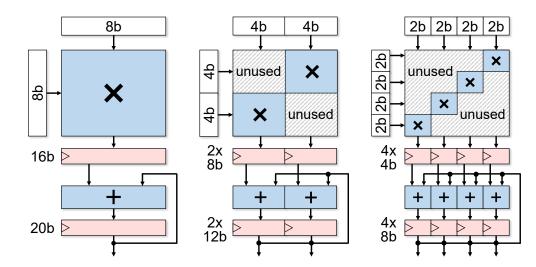

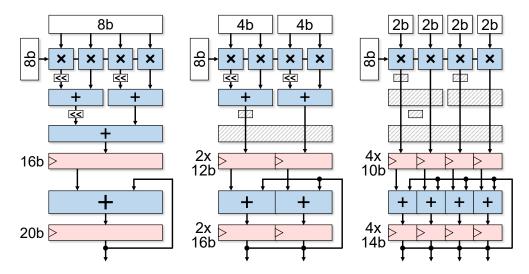

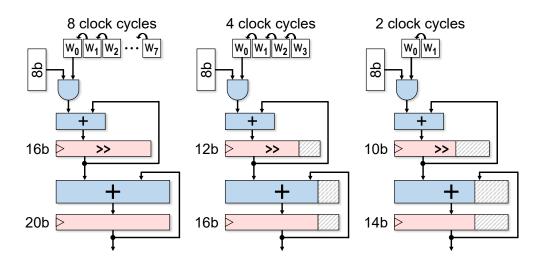

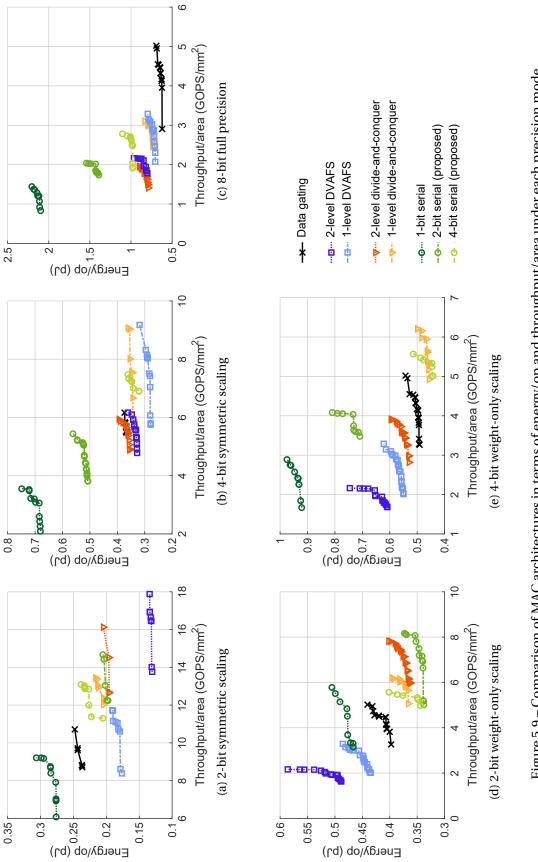

The final part of this thesis reviews and complements precision-scalable Multiply-Accumulate (MAC) accelerators for deep learning applications. Deep learning has come with an enormous computational need for billions of MAC operations. Fortunately, reduced precision has demonstrated benefits with minimal loss in accuracy. Many works have recently shown configurable MAC architectures optimized for neural-network processing, either with parallelization or bit-serial approaches. In this thesis, the most prominent ones are reviewed, implemented and compared in a fair way. A hybrid precision-scalable MAC design is also proposed. Finally, an analysis of power consumption and throughput is carried out to figure out the key trends for reducing computation costs in neural-network processors.

## Keywords

Approximate computing, approximate circuits, low-power digital circuits, approximate adders, speculative adders, approximate multipliers, floating-point unit (FPU), multiply-accumulate (MAC), false timing paths, timing errors, scalable precision, neural networks, high-dynamic range (HDR), image tone mapping.

# Résumé

La densité, la vitesse et l'efficacité énergétique des circuits intégrés ont augmenté de façon exponentielle au cours des quatre dernières décennies, se conformant à la remarquable prédiction de Gordon Moore. Cependant, la consommation énergétique et la fiabilité des circuits posent plusieurs défis risquant de freiner cette progression. Le *calcul approximatif* (approximate computing) est apparu comme une méthode prometteuse pour continuer à réduire la consommation ou augmenter les performances malgré les difficultés liées à la miniaturisation. La conception de *circuits approximatifs* explore ce nouveau compromis en acceptant ou introduisant intentionnellement des erreurs pour surmonter les limites des circuits traditionnels. Ce paradigme a ouvert la voie à de nouvelles techniques de réduction dynamique de consommation, notamment grâce aux *circuits à précision variable*, qui permettent de configurer de manière dynamique leur exactitude ou précision. Cette thèse examine plusieurs approches de conception de circuits approximatifs et à précision variable pour applications en multimédia et en intelligence artificielle.

Cette thèse présente d'abord les techniques architecturales permettant de concevoir des circuits arithmétiques approximatifs, en particulier deux techniques appelées *Inexact Speculative Adder (ISA)* et *Gate-Level Pruning (GLP)*. La première technique, l'ISA, divise l'opération d'addition, c'est-à-dire la propagation de la chaîne de retenue, en plusieurs sous-blocs exécutés en parallèle en utilisant des retenues internes spéculées. L'ISA est doté d'un bloc de spéculation plus rapide et d'un nouveau mécanisme de réduction et correction d'erreurs. La deuxième technique, GLP, est un outil de CAO qui supprime les portes logiques les moins importantes d'un circuit afin d'en réduire la consommation d'énergie et la surface de silicium. Couplé à un modèle de prédiction d'erreurs de timing, l'ISA démontre une forte résistance à l'overclocking, ce qui offre un autre degré de liberté entre énergie et précision.

La deuxième partie de cette thèse introduit un nouveau concept permettant d'optimiser les circuits approximatifs en fabriquant de *faux chemins critiques*, c'est-à-dire des chemins critiques qui ne peuvent pas être logiquement activés. Optimisant à la fois les délais du circuit et sa fonctionnalité, cette méthode propose de surveiller et de couper les chemins critiques pour les transformer en faux chemins critiques. Un additionneur approximatif appelé *Carry Cut-Back Adder (CCBA)* est proposé, dans lequel certains calculs de retenue en aval de l'addition peuvent interrompre la chaîne de propagation de retenue à des positions en amont,

### Résumé

de moindre importance, garantissant ainsi une grande précision tout en apportant d'énormes gains en énergie.

La troisième partie de cette thèse étudie l'intégration de techniques d'approximation au sein de plus grandes unités de calcul ainsi que leur application pour le traitement d'images. Le concept de l'ISA est d'abord étendu pour concevoir un multiplicateur spéculatif, l'*Inexact Speculative Multiplier (ISM)*. Les techniques ISM, ISA et GLP sont ensuite utilisées pour construire des unités à virgule flottante (FPU) approximatives, intégrées dans un processeur multi-cœur. Ces circuits FPU approximatifs sont validés par le biais d'une application embarquée de mappage ton local d'images HDR (à grande gamme dynamique). L'imagerie HDR est un domaine en pleine croissance dans les téléphones mobiles et les appareils photo utilisant de manière extensive les calculs en virgule flottante. Les résultats de l'application ne montrent aucune perte de qualité visible, avec un PSNR d'image allant de 76 dB avec la FPU prunée à 127 dB avec la FPU spéculative.

La dernière partie de cette thèse passe en revue, compare et complète les accélérateurs de multiplication-accumulation (MAC) à précision variable pour les applications d'apprentissage profond. L'apprentissage profond a engendré un énorme besoin en calcul pour des milliards d'opérations MAC. Heureusement, l'utilisation de précisions réduites a démontré de gros bénéfices avec une détérioration de qualité minime, ouvrant la voie à l'intelligence artificielle embarquée dans les appareils mobiles et l'Internet des Objets (IoT). De nombreux travaux ont récemment présenté des architectures MAC configurables à faible précision spécialement optimisées pour le traitement de réseaux de neurones, avec des capacités de parallélisation ou des approches sérielles. Dans cette thèse, les plus importantes sont passées en revue, mises en œuvre et comparées de manière équitable. Un MAC hybride sériel multi-bit est également proposé. Enfin, une analyse de la consommation d'énergie et du débit selon différents scénarios de précision est réalisée afin de réduire les coûts de calcul des réseaux de neurones.

### Mots clés

Calcul approximatif, circuits approximatifs, circuits numériques à basse consommation, additioneurs approximatifs, additioneurs spéculatifs, multiplieurs approximatifs, unités à virgule flottante (FPU), multiplication-accumulation (MAC), faux chemins critiques, circuits à précision variable, réseaux de neurones, high-dynamic range (HDR), mappage ton local.

# Contents

| Ac  | Acknowledgements     v        |         |                                                |      |  |  |

|-----|-------------------------------|---------|------------------------------------------------|------|--|--|

| Ab  | Abstract (English/French) vii |         |                                                |      |  |  |

| Lis | List of figures xvi           |         |                                                |      |  |  |

| Lis | st of ta                      | ables   |                                                | xvii |  |  |

| No  | omeno                         | clature |                                                | xix  |  |  |

| 1   | Intro                         | oductio | n and related work                             | 1    |  |  |

|     | 1.1                           | Introd  | uction                                         | 1    |  |  |

|     | 1.2                           | State o | f the art                                      | 4    |  |  |

|     |                               | 1.2.1   | Approximate circuits using technological knobs | 5    |  |  |

|     |                               | 1.2.2   | Circuit-level design techniques                | 7    |  |  |

|     |                               | 1.2.3   | Software-level approximations                  | 9    |  |  |

|     |                               | 1.2.4   | Discussion                                     | 10   |  |  |

| 2   | Spec                          | ulative | and pruned arithmetic circuits                 | 11   |  |  |

|     | 2.1                           | Inexac  | t speculative adder (ISA)                      | 12   |  |  |

|     |                               | 2.1.1   | Proposed architecture                          | 12   |  |  |

|     |                               | 2.1.2   | COMP block implementation                      | 15   |  |  |

|     |                               | 2.1.3   | Analysis of error compensation                 | 16   |  |  |

|     |                               | 2.1.4   | The ISA design strategy                        | 17   |  |  |

|     |                               | 2.1.5   | Results and comparison                         | 19   |  |  |

|     | 2.2                           | Gate-le | evel pruning (GLP)                             | 24   |  |  |

|     |                               | 2.2.1   | Proposed framework                             | 24   |  |  |

|     |                               | 2.2.2   | Results                                        | 26   |  |  |

|     | 2.3                           | Combi   | ination of speculation and pruning             | 28   |  |  |

|     |                               | 2.3.1   | Proposed method                                | 28   |  |  |

|     |                               | 2.3.2   | Results and comparison                         | 28   |  |  |

|     | 2.4                           | Overcl  | ocking of speculative adders                   | 31   |  |  |

|     |                               | 2.4.1   | Proposed method for timing-error prediction    | 31   |  |  |

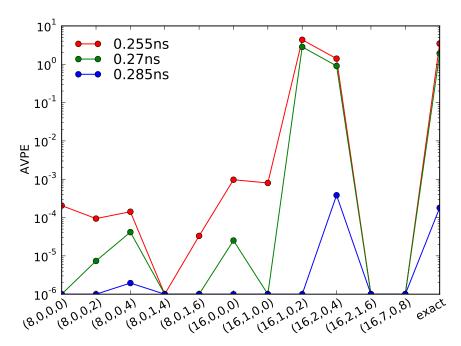

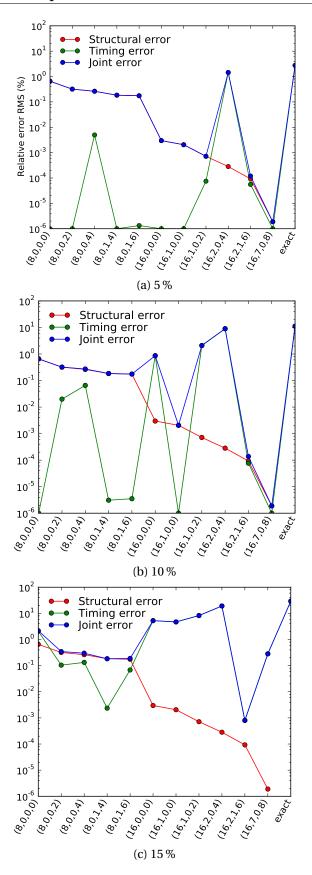

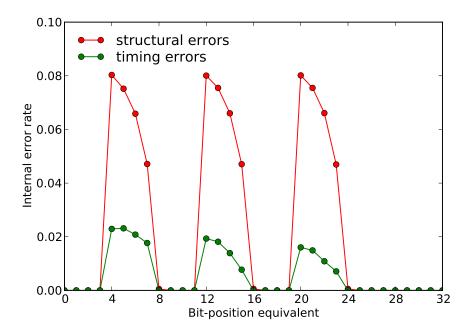

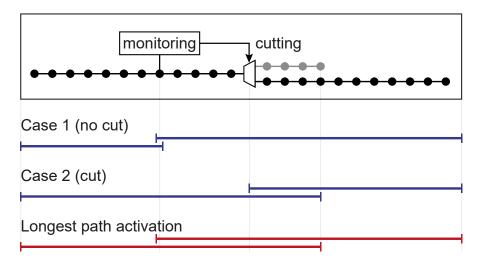

|     |                               | 2.4.2   | Combining structural and timing errors         | 32   |  |  |

# Contents

|   |                                                                                           | 2.4.3                                                                                                                                | Experimental study                                                                                                                                                                        | 34                                                                                      |

|---|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|   |                                                                                           | 2.4.4                                                                                                                                | Results                                                                                                                                                                                   | 35                                                                                      |

|   | 2.5                                                                                       | Conclu                                                                                                                               | usion                                                                                                                                                                                     | 40                                                                                      |

| 3 | App                                                                                       | roxima                                                                                                                               | te circuits by fabrication of false timing paths                                                                                                                                          | 41                                                                                      |

|   | 3.1                                                                                       | Appro                                                                                                                                | ximate circuit design and optimization by fabrication of false paths                                                                                                                      | 42                                                                                      |

|   |                                                                                           | 3.1.1                                                                                                                                | False-path fabrication                                                                                                                                                                    | 42                                                                                      |

|   |                                                                                           | 3.1.2                                                                                                                                | Significance-driven cuts                                                                                                                                                                  | 43                                                                                      |

|   | 3.2                                                                                       | Carry                                                                                                                                | cut back adder (CCBA)                                                                                                                                                                     | 45                                                                                      |

|   |                                                                                           | 3.2.1                                                                                                                                | State-of-the-art approximate adders                                                                                                                                                       | 45                                                                                      |

|   |                                                                                           | 3.2.2                                                                                                                                | Proposed architecture                                                                                                                                                                     | 46                                                                                      |

|   |                                                                                           | 3.2.3                                                                                                                                | Circuit timing                                                                                                                                                                            | 49                                                                                      |

|   |                                                                                           | 3.2.4                                                                                                                                | Arithmetic and errors                                                                                                                                                                     | 50                                                                                      |

|   |                                                                                           | 3.2.5                                                                                                                                | Worst-case error and floating-point precision                                                                                                                                             | 52                                                                                      |

|   |                                                                                           | 3.2.6                                                                                                                                | Design and implementation strategy                                                                                                                                                        | 54                                                                                      |

|   |                                                                                           | 3.2.7                                                                                                                                | Design-space minimization                                                                                                                                                                 | 56                                                                                      |

|   | 3.3                                                                                       | Result                                                                                                                               | s and comparison                                                                                                                                                                          | 58                                                                                      |

|   |                                                                                           | 3.3.1                                                                                                                                | Methodology                                                                                                                                                                               | 58                                                                                      |

|   |                                                                                           | 3.3.2                                                                                                                                | CCBA results                                                                                                                                                                              | 59                                                                                      |

|   |                                                                                           | 3.3.3                                                                                                                                | Comparative study                                                                                                                                                                         | 62                                                                                      |

|   | 3.4                                                                                       | Conclu                                                                                                                               | usion                                                                                                                                                                                     | 66                                                                                      |

|   |                                                                                           |                                                                                                                                      |                                                                                                                                                                                           |                                                                                         |

| 4 | App                                                                                       |                                                                                                                                      | te accelerators and applications                                                                                                                                                          | 67                                                                                      |

| 4 | <b>App</b><br>4.1                                                                         | roxima                                                                                                                               | 11                                                                                                                                                                                        | <b>67</b><br>68                                                                         |

| 4 |                                                                                           | roxima                                                                                                                               | ximate floating-point units                                                                                                                                                               |                                                                                         |

| 4 |                                                                                           | <b>roxima</b><br>Appro                                                                                                               | ximate floating-point units                                                                                                                                                               | 68                                                                                      |

| 4 |                                                                                           | roxima<br>Appro<br>4.1.1                                                                                                             | ximate floating-point units                                                                                                                                                               | 68<br>69                                                                                |

| 4 |                                                                                           | roxima<br>Appro<br>4.1.1<br>4.1.2<br>4.1.3                                                                                           | ximate floating-point units                                                                                                                                                               | 68<br>69<br>70                                                                          |

| 4 | 4.1                                                                                       | roxima<br>Appro<br>4.1.1<br>4.1.2<br>4.1.3                                                                                           | ximate floating-point units                                                                                                                                                               | 68<br>69<br>70<br>71                                                                    |

| 4 | 4.1                                                                                       | roxima<br>Appro<br>4.1.1<br>4.1.2<br>4.1.3<br>Applic                                                                                 | ximate floating-point units          Inexact speculative multiplier (ISM)          Approximate FPU architecture          Measurement and results          ation to HDR image tone-mapping | 68<br>69<br>70<br>71<br>74                                                              |

| 4 | 4.1                                                                                       | Appro:<br>4.1.1<br>4.1.2<br>4.1.3<br>Applic<br>4.2.1<br>4.2.2                                                                        | ximate floating-point units                                                                                                                                                               | 68<br>69<br>70<br>71<br>74<br>74                                                        |

| 4 | 4.1<br>4.2<br>4.3                                                                         | roxima<br>Appro<br>4.1.1<br>4.1.2<br>4.1.3<br>Applic<br>4.2.1<br>4.2.2<br>Conclu                                                     | ximate floating-point units                                                                                                                                                               | 68<br>69<br>70<br>71<br>74<br>74<br>75                                                  |

|   | 4.1<br>4.2<br>4.3                                                                         | Appro<br>4.1.1<br>4.1.2<br>4.1.3<br>Applic<br>4.2.1<br>4.2.2<br>Conclu                                                               | ximate floating-point units                                                                                                                                                               | 68<br>69<br>70<br>71<br>74<br>74<br>75<br>78                                            |

|   | <ul><li>4.1</li><li>4.2</li><li>4.3</li><li>Precenting</li></ul>                          | roxima<br>Appro<br>4.1.1<br>4.1.2<br>4.1.3<br>Applic<br>4.2.1<br>4.2.2<br>Conclu<br>cision-se<br>Introd                              | ximate floating-point units                                                                                                                                                               | 68<br>69<br>70<br>71<br>74<br>75<br>78<br><b>79</b>                                     |

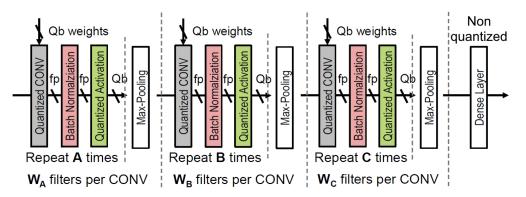

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>Preconstruction</li> <li>5.1</li> </ul>   | roxima<br>Appro<br>4.1.1<br>4.1.2<br>4.1.3<br>Applic<br>4.2.1<br>4.2.2<br>Conclu<br>cision-se<br>Introd                              | ximate floating-point units                                                                                                                                                               | 68<br>69<br>70<br>71<br>74<br>75<br>78<br><b>79</b><br>80                               |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>Preconstruction</li> <li>5.1</li> </ul>   | Appro:<br>4.1.1<br>4.1.2<br>4.1.3<br>Applic<br>4.2.1<br>4.2.2<br>Conclu<br><b>:ision-s</b><br>Introd<br>Consid                       | ximate floating-point units                                                                                                                                                               | 68<br>69<br>70<br>71<br>74<br>75<br>78<br><b>79</b><br>80<br>81                         |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>Preconstruction</li> <li>5.1</li> </ul>   | roxima<br>Appro<br>4.1.1<br>4.1.2<br>4.1.3<br>Applic<br>4.2.1<br>4.2.2<br>Conclu<br>consid<br>5.2.1<br>5.2.2                         | ximate floating-point units                                                                                                                                                               | 68<br>69<br>70<br>71<br>74<br>75<br>78<br><b>79</b><br>80<br>81<br>81<br>81             |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>Prec</li> <li>5.1</li> <li>5.2</li> </ul> | roxima<br>Appro<br>4.1.1<br>4.1.2<br>4.1.3<br>Applic<br>4.2.1<br>4.2.2<br>Conclu<br>consid<br>5.2.1<br>5.2.2                         | ximate floating-point units                                                                                                                                                               | 68<br>69<br>70<br>71<br>74<br>74<br>75<br>78<br><b>79</b><br>80<br>81<br>81             |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>Prec</li> <li>5.1</li> <li>5.2</li> </ul> | roximat<br>Appro.<br>4.1.1<br>4.1.2<br>4.1.3<br>Applic<br>4.2.1<br>4.2.2<br>Conclu<br>ision-se<br>Introd<br>5.2.1<br>5.2.2<br>Multip | ximate floating-point units                                                                                                                                                               | 68<br>69<br>70<br>71<br>74<br>75<br>78<br><b>79</b><br>80<br>81<br>81<br>81<br>81       |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>Prec</li> <li>5.1</li> <li>5.2</li> </ul> | roxima<br>Appro<br>4.1.1<br>4.1.2<br>4.1.3<br>Applic<br>4.2.1<br>4.2.2<br>Conclu<br>consid<br>5.2.1<br>5.2.2<br>Multip<br>5.3.1      | ximate floating-point units                                                                                                                                                               | 68<br>69<br>70<br>71<br>74<br>75<br>78<br><b>79</b><br>80<br>81<br>81<br>81<br>82<br>82 |

## Contents

|              | 5.3.5               | Multi-bit serial design                                                        | 85   |  |  |

|--------------|---------------------|--------------------------------------------------------------------------------|------|--|--|

| 5.4          | Result              | s and comparative study                                                        | 86   |  |  |

|              | 5.4.1               | Precision-scaling energy breakdown                                             | . 86 |  |  |

|              | 5.4.2               | Comparative study                                                              | . 88 |  |  |

| 5.5          | Concl               | usion                                                                          | 90   |  |  |

| Conclu       | sions ar            | nd perspectives                                                                | 91   |  |  |

| Append       | dix                 |                                                                                | 95   |  |  |

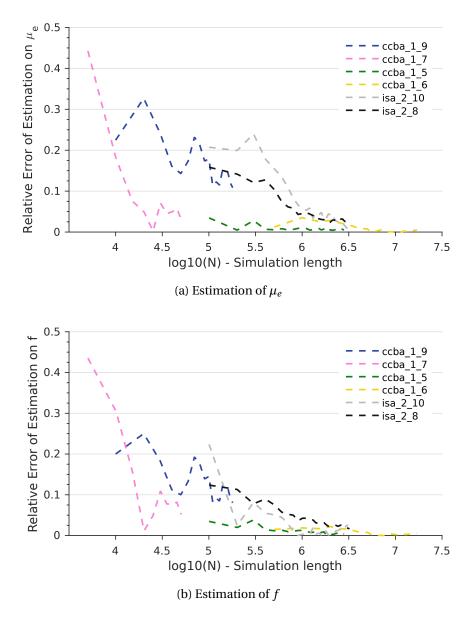

| А            | Chara               | cterization with adaptive sample-size inferential statistics (CASSIS) $\ldots$ | 95   |  |  |

|              | A.1                 | CASSIS method                                                                  | 95   |  |  |

|              | A.2                 | Experimental study                                                             | 96   |  |  |

|              | A.3                 | Results                                                                        | . 97 |  |  |

|              | A.4                 | Conclusion                                                                     | . 99 |  |  |

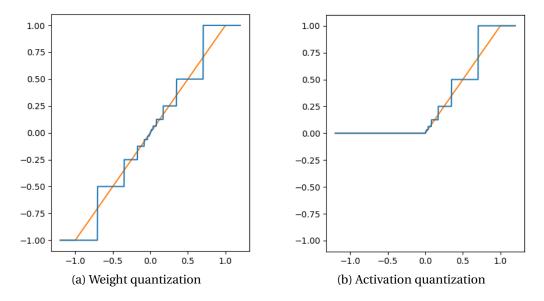

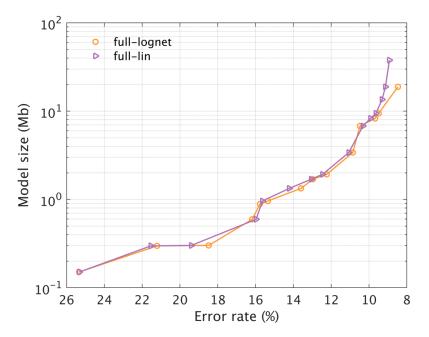

| В            | Neura               | l networks using logarithmic quantization                                      | 101  |  |  |

|              | B.1                 | Log-quantized neural-network framework                                         | 101  |  |  |

|              | B.2                 | Considerations                                                                 | 102  |  |  |

|              | B.3                 | Results                                                                        | 102  |  |  |

|              | B.4                 | Remarks and perspectives                                                       | 103  |  |  |

| Bibliography |                     |                                                                                |      |  |  |

| List of J    | publicat            | ions                                                                           | 113  |  |  |

| Curricu      | Curriculum vitae 11 |                                                                                |      |  |  |

# List of figures

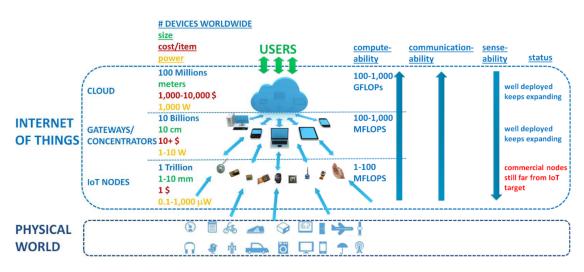

| Growth and architecture of the IoT expected for 2025                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

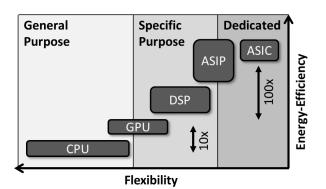

| Energy efficiency versus flexibility for different deep-learning platforms        | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

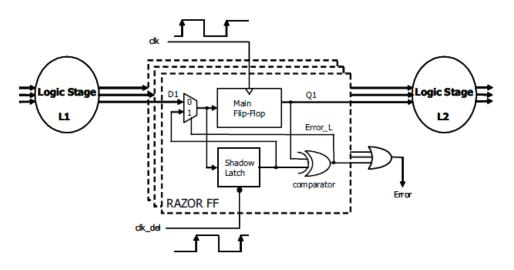

| Pipeline augmented with Razor flip-flops.                                         | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

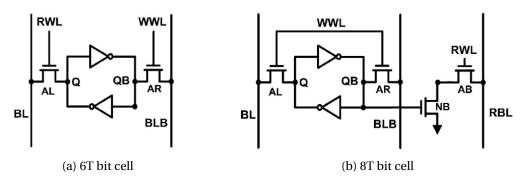

| Schematics of 6T (a) and 8T (b) SRAM bit cells.                                   | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

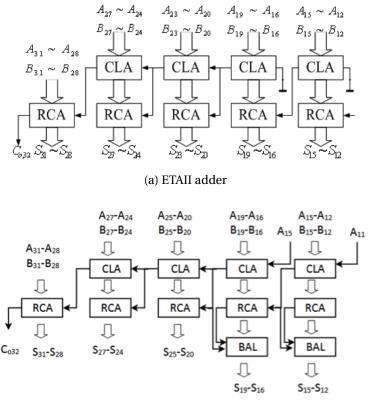

| Block diagrams of the ETAIIM (a) and the ETBA (b) speculative adders. $\ldots$    | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

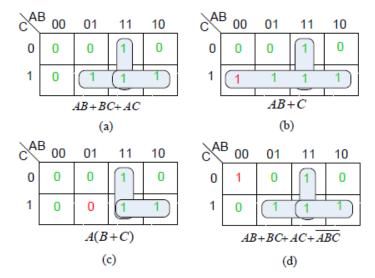

| Example of logic minimization.                                                    | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

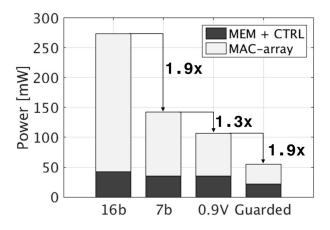

| Influence of different techniques on the CNN power consumption                    | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

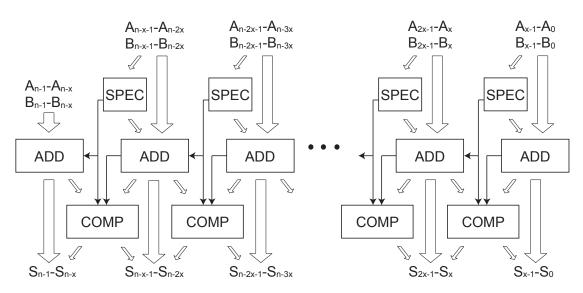

| General block diagram of the Inexact Speculative Adder (ISA)                      | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

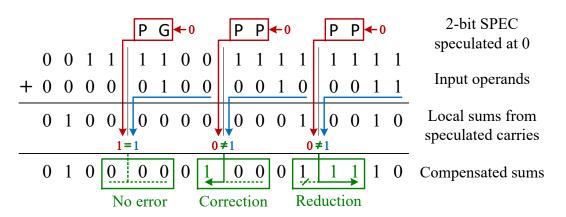

| Example of ISA addition arithmetic.                                               | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

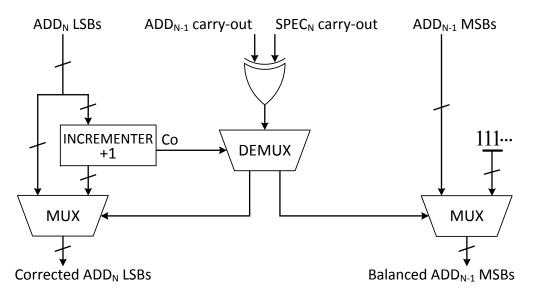

| COMP block implementation.                                                        | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

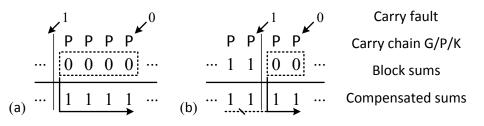

| Relative error equivalence between compensation with balancing only (a) and       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| combined with correction (b) in case of non-correctable error. $\ldots$           | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

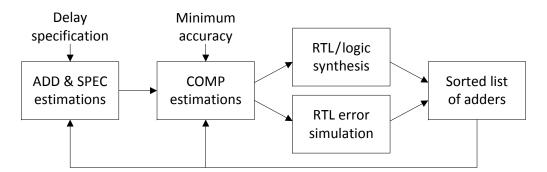

| CAD framework for ISA design.                                                     | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

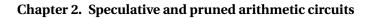

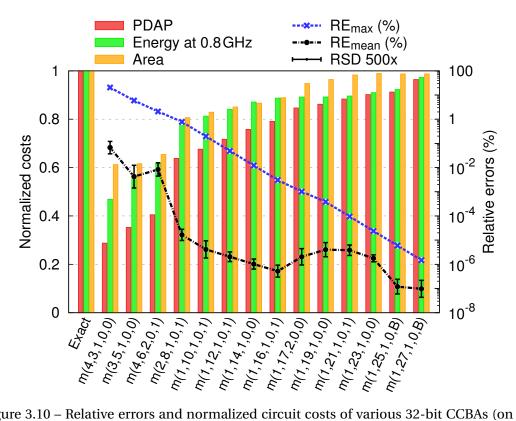

| Error characteristics and normalized cost of 32-bit ISA adders.                   | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

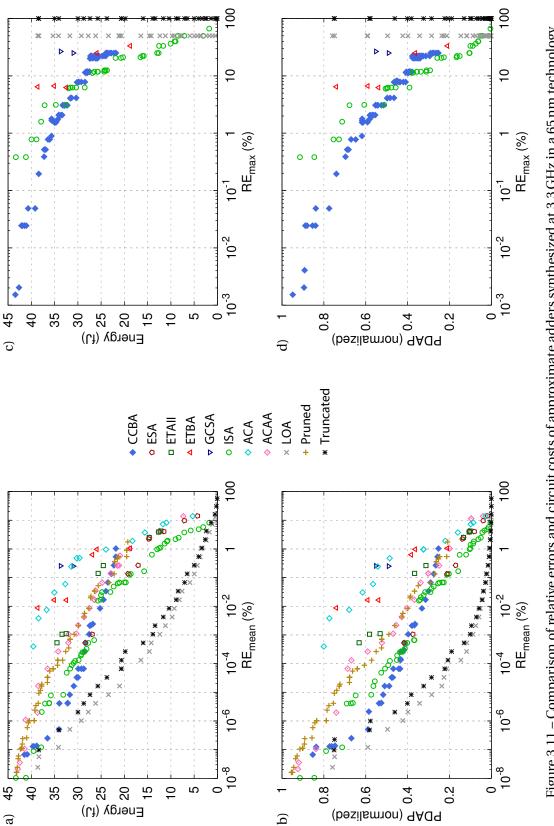

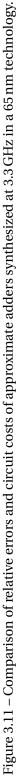

| Comparison of ISA with state-of-the-art adders.                                   | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

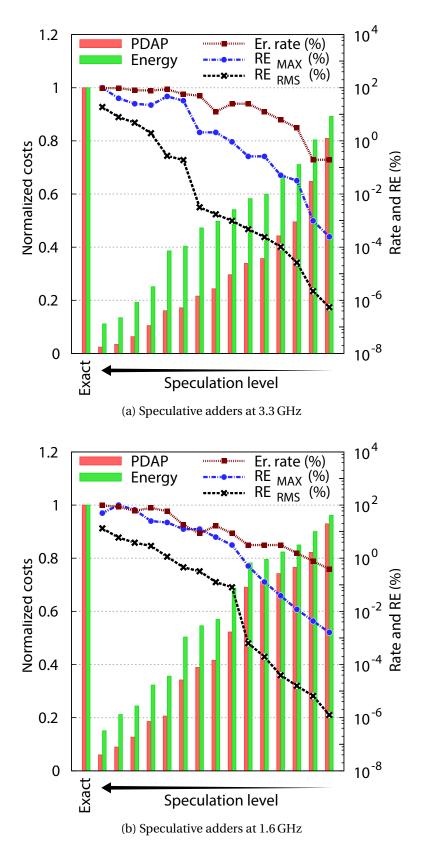

| CAD framework for Gate-Level Pruning.                                             | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

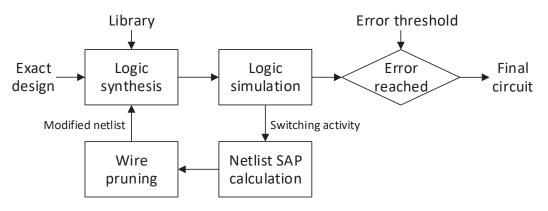

| Example of GLP flow with a 3-bit adder.                                           | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

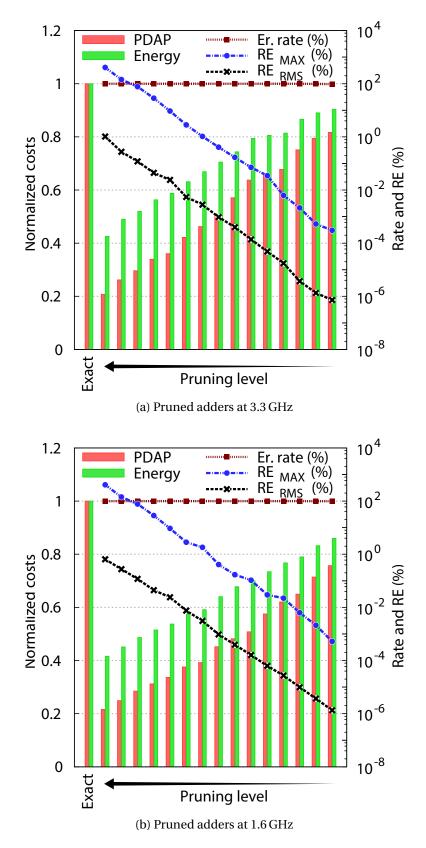

| Error characteristics and normalized cost of 32-bit pruned adders                 | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

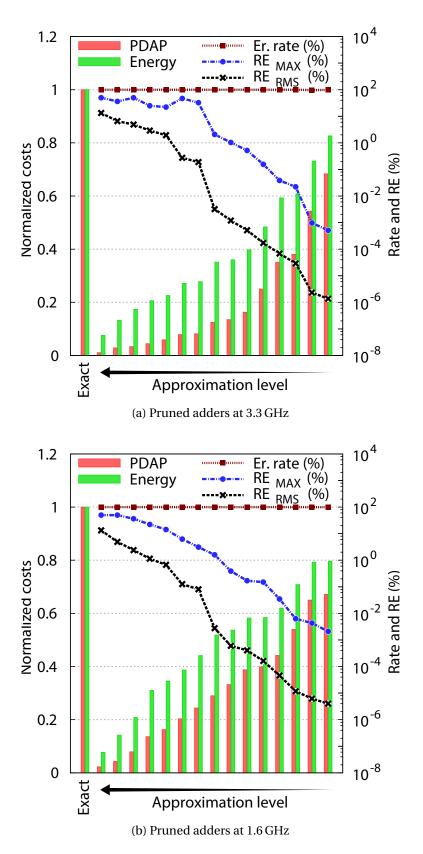

| Error characteristics and normalized cost of 32-bit mixed adders                  | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

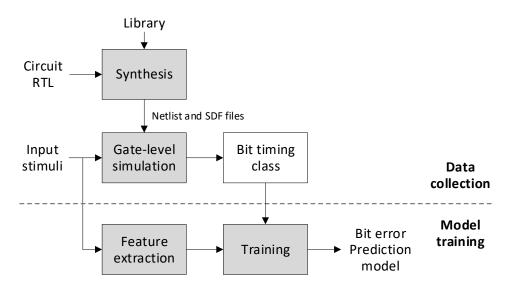

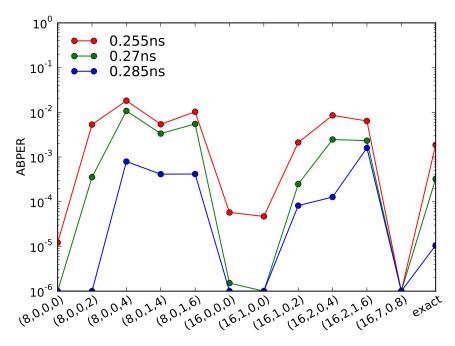

| Bit-level timing error prediction model construction flow.                        | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Example of additive errors.                                                       | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Example of compensating errors.                                                   | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Pseudo-code computing the mean arithmetic error of over-clocked ISAs with         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

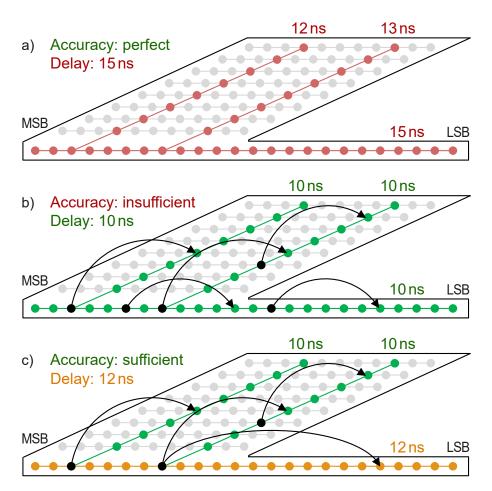

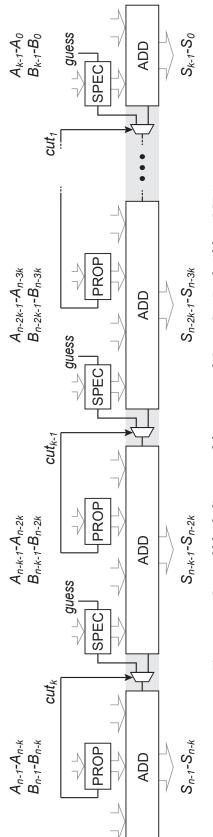

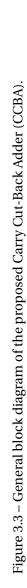

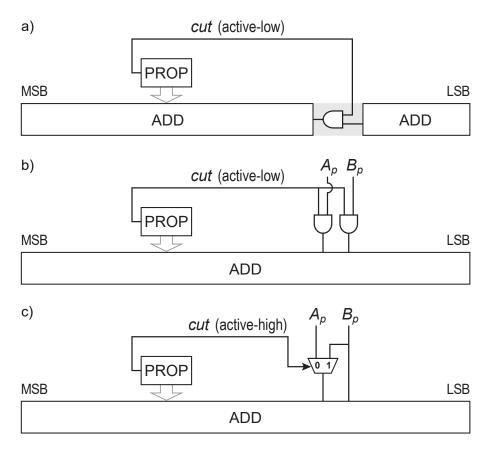

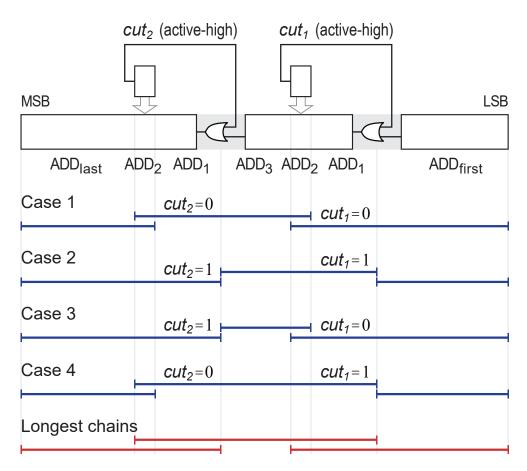

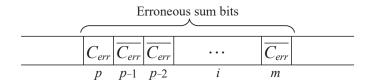

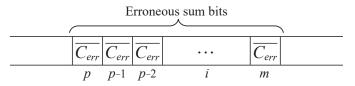

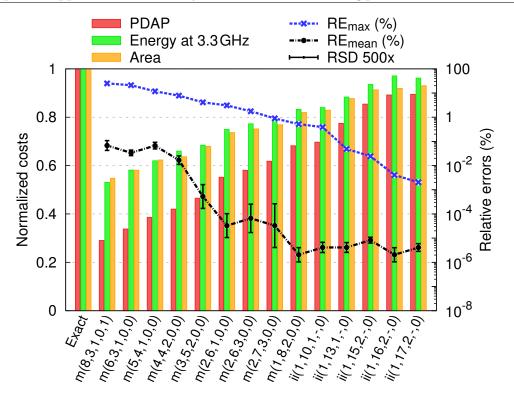

| structural and timing errors.                                                     | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |