# Compact Modeling of Charge Transfer in Pinned Photodiodes for CMOS Image Sensors

Raffaele Capoccia, Assim Boukhayma, Farzan Jazaeri, and Christian Enz

Abstract—In this paper we propose a physics-based compact model of the pinned photodiode (PPD) combined with the transfer gate (TG). A set of analytical expressions is derived for the 2D electrostatic profile, the pinned photodiode capacitance, and the charge transfer current. The proposed model relies on the thermionic emission current mechanism, the barrier modulation and the full-depletion approximation to obtain the charge transfer current. The proposed physics-based model is fully validated with technology computer-aided design (TCAD) simulations i.e. stationary and opto-electrical simulations. The development of such a compact model for PPD represents an essential step towards the design, simulation and optimization of PPDbased pixels in CMOS image sensors.

Index Terms—Compact Modeling, Pinned Photodiode (PPD), CMOS Image Sensors (CISs), Charge Transfer.

### I. INTRODUCTION

**P**INNED photodiodes (PPDs) are key components in CMOS image sensors (CIS). They are mainly used into mass market applications e.g. smartphones, tablets and digital cameras, but also advanced high-end scientific and industrial applications. The PPD has been first introduced in Charge Coupled Devices (CCDs)[1]. Nowadays, PPDs are the photodetecting element in CIS, determining their performance in terms of sensitivity, image lag, dark current, and full well capacity (FWC) [2]-[4]. The PPD is usually associated with a TG, which transfer the electrons accumulated during illumination within the photodiode to the sense node (SN), having lower capacitance and hence providing a readable voltage variation. The PPD/TG interface is becoming more critical for further improvements [5] in advanced applications e.g. sub-electron read noise levels [6], [7], high frame rates [8], [9], and Time of Flight (ToF) [10], [11]. Moreover, the nonideal effects due to the charge transfer mechanism from the PPD to the SN, which affects both the static and dynamic operations, has recently become a new research topic [12]-[14].

The compact modeling of PPD-based pixels is still at its early stage of development and to the best of our knowledge, no compact model has been developed so far. A charge transfer model based on thermionic emission theory has been recently developed in [12]. This model shows that the floating diffusion (FD) capacitance and the area of the photodiode also affect the charge transfer. However, this work does not model the

R. Capoccia, A. Boukhayma, F. Jazaeri, and C. Enz are with Integrated Circuits Laboratory (ICLAB) in École Polytechnique Fédérale de Lausanne (EPFL), Lausanne 1015, Switzerland (e-mail: Raffaele.Capoccia@epfl.ch). Manuscript received on May 2018. potential barrier,  $V_{\rm b}$ , and does not give a closed form expression for the charge transfer current. Given the advantages of using explicit expressions for compact modeling purposes, we developed a physics-based model of the PPD together with the TG. A detailed electrostatic analysis of the PPD and TG is carried out, allowing to derive the electrical parameters. The potential barrier between the PPD and TG voltages and other physical parameters. This leads to a physics-based model of the charge transfer current of the photogenerated electrons from the PPD to the SN. The proposed model is verified and validated with Synopsys<sup>®</sup> TCAD [15] simulation results.

The paper is organized as follows: in Section II, the operation principle of the PPD together with the TG is briefly explained. Section III addresses a detailed analysis of the static parameters, validated by TCAD simulations. Section IV is devoted to the influence of the potentials and physical parameters on the potential barrier, supported by transient simulations performed in TCAD. In Section V, adopting thermionic emission current mechanism approach, a physics-based model of the charge transfer current is developed and validated with TCAD simulation results. Finally the conclusions are drawn in Section VI.

## II. PRINCIPLE OF OPERATION AND DEVICE STRUCTURE

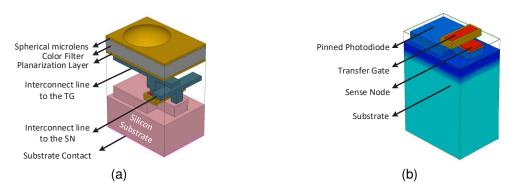

A PPD is a device made by a n-well buried in a p-substrate. On top of this well, a thin layer of highly p-doped semiconductor takes place. Even though the structure does not differ a lot from a standard p-n photodiode, the working principle of this device is quite different. A PPD operates as a unipolar charge accumulator, where the photogenerated electrons,  $N_{\rm e}$ , can be stored. Lowering the energy barrier (below the energy at the PPD well), by imposing a positive voltage to the TG next to the PPD, allows the accumulated charge to move towards the SN. This node is initially set to a positive reset voltage e.g. 2.5 V. It should be noted that the TG isolates the PPD and SN capacitances, leading to a lower capacitance at the SN. Due to the fact that the SN capacitance,  $C_{\rm SN}$ , is lower than the PPD capacitance,  $C_{PPD}$ , the transferred electrons cause a higher voltage variation that can be processed by the readout circuitry  $\left[\Delta V_{\rm SN} = \left(q N_{\rm e}\right) / C_{\rm SN}\right]$ . The 3D geometry of the back-end is depicted in Fig. 1a, including the silicon at the bottom, the two metal interconnects, connected through a via to the TG and the SN contacts. As illustrated, a color filter is sandwiched between a layer of deposition on the bottom and a spherical microlens on the top. The color filter is indeed chosen accordingly to the wavelength used for the input light.

Fig. 1. (a) Back-end: the microlens, the color filter and the interconnections. (b) Front-end: the pinned photodiode, the TG and the SN.

In this paper, an ideal red color filter is used centered at a wavelength equal to 650 nm. Fig. 1b is a 3D view of the frontend of the device, including the photodiode, the TG made in polysilicon and surrounded by an insulating material, and the SN diffusion. Blue, red and light blue are corresponding to the p<sup>+</sup>type, n<sup>+</sup>type regions and p substrate respectively.

# **III. PPD DEVICE**

# A. Electrostatics in PPD Device

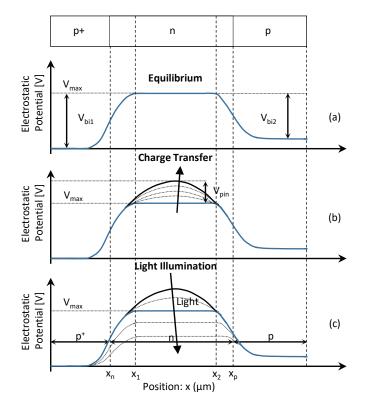

On the top of Fig. 2, the simplified cross-section of a PPD is shown, made by a p<sup>+</sup>np structure. In this figure, the electrostatic potentials of the PPD is also shown under different conditions. Fig. 2a corresponds to the equilibrium condition, while the impact of charge transfer is sketched in Fig. 2b and the one of light in Fig. 2c. At the equilibrium condition, the n-well region is partially neutral and the electrostatic potential remains almost constant. The two built-in potentials,  $V_{bi1}$  and  $V_{\rm bi2}$ , are illustrated in Fig. 2a. The doping concentration in the  $p^+$  layer is typically higher than the one in the p substrate. Hence, the built-in potential of the pn junction,  $V_{\rm bi2}$ , is lower than the one with the  $p^+$  layer,  $V_{bi1}$ . After the free carriers are transferred from the PPD, the maximum value of the electrostatic potential increases, allowing to make the n-well fully depleted of the carriers. In Fig. 2b, V<sub>pin</sub> is retrieved as the maximum variation of the electrostatic potential, in consistency with the definition given in [16]. On the other hand, when the photodiode is exposed to the light, the entire electrostatic potential moves towards the flat-band condition as shown in Fig. 2c.

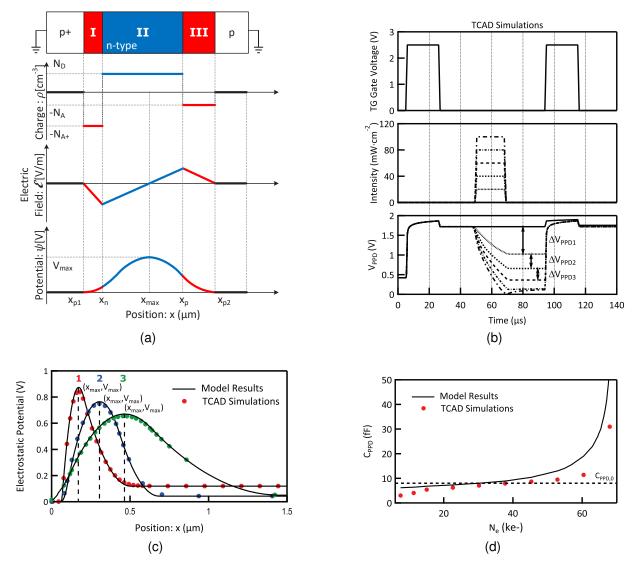

In this paper, the electrostatic analysis of the PPD is performed for the structure depicted in Fig. 3a. This structure is characterized by a fully depleted n-well. The full-depletion of the n-well can be achieved as soon as all the accumulated charges are transferred to the SN during the reading operation. Since a full-depletion approximation is assumed along the device, the free carrier concentrations is negligible compared to the fixed charge density. In TCAD simulations the fulldepletion is reached by a proper choice of the physical parameters, hence the two depleted regions intersects in one point. This is a particular case where the maximum of the electrostatic potential,  $V_{\rm max}$ , is equal to the highest builtin potential, namely the one of the p<sup>+</sup>n junction,  $V_{\rm bi1}$ . If the length of the n-well is further reduced, the structure is still pinned, but  $V_{\rm max}$  is lower than  $V_{\rm bi1}$ . In the simplified cross-section of a PPD illustrated in Fig. 3a, the left side corresponds to the top of the structure shown in Fig. 1b. To simplify the analysis, the following assumptions are added: a) an abrupt transition between the neutral and the depleted region is used for both junctions; b) both the applied voltages in the substrate and at the pinned layer are set equal to zero. This condition is required to impose the boundary conditions. Under these assumptions, the total charge density  $\rho(x)$  along the PPD is plotted in Fig. 3a. Solving the Poisson equation  $\nabla^2 \psi(x) = -\rho(x)/\varepsilon_{\rm s}$ , analytical expressions of the electric

Fig. 2. Sketches of the electrostatic potential of the PPD: (a) at equilibrium condition, two built-in potentials,  $V_{bi1}$  and  $V_{bi2}$ , and maximum potential,  $V_{max}$ , are shown. The maximum value of the electrostatic potential increases until the empty condition is reached while transferring the charges from the PPD to the SN, as shown in (b). The maximum variation of the electrostatic potential is the pinning voltage,  $V_{pin}$ , as defined in [16]. In (c), the potential moves towards the flat-band condition due to the applied illumination.

TABLE I

MAIN PARAMETERS OF THREE CASES OF PINNED PHOTODIODES

|                             | Case 1           | Case 2            | Case 3            |

|-----------------------------|------------------|-------------------|-------------------|

| $N_{A^+} (cm^{-3})$         | 10 <sup>18</sup> | 10 <sup>17</sup>  | 10 <sup>16</sup>  |

| $N_{\rm D}~({\rm cm}^{-3})$ | $10^{17}$        | $2 	imes 10^{16}$ | $5 	imes 10^{15}$ |

| $N_A (cm^{-3})$             | $10^{16}$        | 1015              | $10^{15}$         |

| <b>x</b> <sub>n</sub> (nm)  | 70               | 100               | 120               |

| $\mathbf{x}_{p}$ (nm)       | 200              | 430               | 630               |

| x <sub>max</sub> (nm)       | 170              | 305               | 460               |

| $\mathbf{V}_{\max}$ (V)     | 0.84             | 0.76              | 0.67              |

field,  $\mathcal{E}(x)$ , and electrostatic potential,  $\psi(x)$ , are derived and reported in Appendix A. The  $\mathcal{E}(x)$  and  $\psi(x)$  are depicted in Fig. 3a. The maximum of the electrostatic potential,  $V_{max}$ , and its corresponding position,  $x_{max}$ , are obtained and given by the following expressions

$$x_{\max} = x_{n} + \frac{N_{A^{+}}}{N_{D}} \left( x_{n} - x_{p1} \right) = x_{p} - \frac{N_{A}}{N_{D}} \left( x_{p2} - x_{p} \right),$$

(1)

$$V_{\rm max} = \frac{qN_{\rm A^+}}{2\varepsilon_{\rm s}} \cdot \frac{N_{\rm A^+} + N_{\rm D}}{N_{\rm D}} \left(x_n - x_{\rm p1}\right)^2, \qquad (2)$$

where  $N_{\rm A^+}$  and  $N_{\rm D}$  are the doping concentrations in the p<sup>+</sup> and the n-well regions, q is the electron charge and  $\varepsilon_{\rm s}$  is the absolute permittivity of silicon. The maximum of the potential occurs at  $x_{\rm max}$ , corresponding to the point where the electric field is equal to zero. Hence,  $x_{\rm max}$  is obtained by solving  $\mathcal{E}(x) = 0$  in the depleted n region resulting in (1). Imposing the charge neutrality between the depleted p and n regions, given by

$$N_{\rm A}x_{\rm p2} - N_{\rm A^+}x_{\rm p1} = (N_{\rm A} + N_{\rm D})x_{\rm p} - (N_{\rm A^+} + N_{\rm D})x_{\rm n}$$

(3)

leads to the RHS of (1). The two derived expressions of (1) confirm that  $x_{\max}$  is comprised between  $x_n$  and  $x_p$ . Inserting  $x_{\text{max}}$ , obtained from (1), into (A.2) leads to the expression for the maximum of the electrostatic potential,  $V_{\text{max}}$ , given by (2). Fig. 3c shows the TCAD simulation results for the electrostatic potential profile along the device, for different geometrical parameters, reported in Table I. The potential profile of this device obtained with TCAD simulations and the model are plotted. The agreement between the model and TCAD simulations is excellent. The Equilibrium Full Well Capacity (EFWC) is defined in [17] as the maximum photogenerated charges that can be accumulated in the PPD in dark conditions and neglecting the TG leakage current. Following this definition, the EFWC can be accurately estimated by the number of electrons stored in the PPD at equilibrium condition. The full well number of photogenerated electrons in the PPD volume between  $x_2$  and  $x_1$  (see Fig. 2) is given by  $N_{e,EFWC}$  =  $A_{\rm PPD}(x_2 - x_1)N_D$ , where  $A_{\rm PPD}$  is the area of the PPD.

### B. PPD Capacitance

During illumination, the electrostatic potential inside the nwell decreases proportionally to the intensity of the light [18]. The ratio of the accumulated charges and the voltage variation corresponds to the capacitance  $C_{\rm PPD} = (q N_{\rm e})/\Delta V_{\rm PPD}$ . Whereas a detailed analytical model has been proposed in [19], the well-known expression of the junction capacitance [20] has been used in [2] and [21] to obtained an analytical expression of  $C_{\rm PPD}$ . Therefore,  $C_{\rm PPD}$  can be expressed as

$$\left(\frac{C_{\rm PPD}}{A_{\rm PPD}}\right)^2 = \frac{q\,\varepsilon_{\rm s}}{2\left(V_{\rm max} - \Delta V\right)} \frac{N_{\rm D} \cdot N_{\rm A^+}}{N_{\rm D} + N_{\rm A^+}}\,,\qquad(4)$$

where  $\Delta V$  is the variation of the electrostatic potential due to photo-generation. Typically for PPDs,  $N_{A^+} \gg N_D$  while  $\Delta V$ can be expressed as a function of  $N_e$ , equal to  $N_e/C_{PPD}$ . After some mathematical manipulations, the derived expression is

$$\left(\frac{C_{\rm PPD}}{A_{\rm PPD}}\right)^2 \approx \frac{q\,\varepsilon_{\rm s}\,N_{\rm D}}{2\,V_{\rm max}\left(1-\frac{N_{\rm e}}{N_{\rm e,0}}\right)}\,,\tag{5}$$

where  $N_{\rm e}$  and  $N_{\rm e,0}$  are respectively the number of photogenerated electrons and the amount of electrons in the nwell at the equilibrium, equal to  $C_{PPD} \cdot V_{max}$ . In order to validate the proposed formula of  $C_{PPD}$ , a TCAD transient simulation with different values of light intensity is carried out. The light is represented by a linearly polarized plane wave for which the intensity, the wavelength and the angle of incidence can be properly set. In the performed TCAD simulations, the illumination is set to have a wavelength of 650 nm and a normal angle with respect to the surface of the device. The applied voltage to the TG, the pulses of light and the PPD voltage with respect to time are depicted in Fig. 3b. First, to deplete the PPD from the charges a positive potential is applied to the gate. Then the PPD is exposed to a pulse of light which generates an amount of photoelectrons. Increasing the light intensity leads to an increase of the PPD voltage variation. To evaluate the  $C_{\rm PPD} = N_{\rm e}/\Delta V_{\rm PPD}$ ,  $N_{\rm e}$ and the maximum voltage variation,  $\Delta V_{\rm PPD}$ , are required to be extracted properly using TCAD simulations. The  $\Delta V_{\rm PPD}$  can be readily determined from Fig. 3b for each value of the light intensity. In addition,  $N_{\rm e}$  is estimated in TCAD simulations using the optical generation parameter, providing informations of the semiconductor charge density. This parameter is integrated over the active volume and then multiplied by the integration time. To validate the proposed model the equivalent capacitance of the PPD is obtained through (5) and compared to TCAD simulations in Fig. 3d. The agreement between the numerical calculation and the model is reasonable.

# **IV. POTENTIAL BARRIER MODELING**

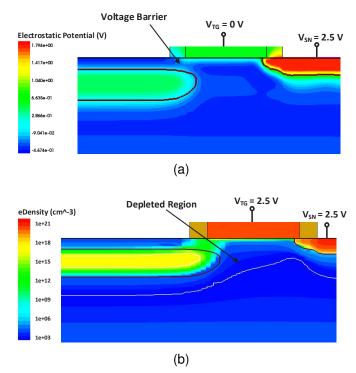

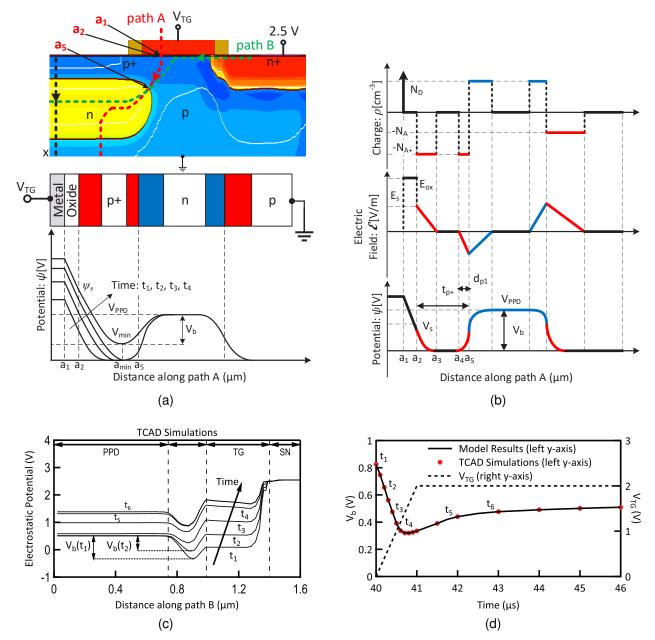

In this section, a physics-based model for the charge transfer from the PPD to the SN is derived. This approach relies on the transfer mechanism limited by the interface properties between the PPD and TG. This assumption is verified for relatively short devices which are not limited by internal diffusion mechanism [22]. The np junction between the PPD n-well and the TG results in a potential barrier between the charge accumulation region and the semiconductor beneath the gate, as shown in Fig. 4a. This barrier has been already reported in [12] and measurements are performed in [23]. A model of this potential barrier is proposed here, predicting its

Fig. 3. (a) Simplified cross-section of a PPD under the assumptions of full depletion and abrupt transition:  $\rho(x)$  is the charge distribution,  $\mathcal{E}(x)$  the electric field and  $\psi(x)$  the electrostatic potential along the position x.  $x_n$  is the junction boundary between  $p^+$  and n layers,  $x_p$  the junction boundary between n and substrate,  $x_{p1}$  and  $x_{p2}$  are the limits of the depletion regions on the  $p^+$  and p regions of the two junctions, respectively. Expressions for the electric field and the electrostatic potential are given in Appendix A. (b) Opto-electrical transient simulations: the gate voltage applied to the TG, the intensity of the incident wave and the electrostatic potential inside the PPD. The changes in the electrostatic potential are proportional to the incident light and can be used to derive the PPD capacitance. (c) Electrostatic potential inside the PPD structure for Case 1, 2 and 3 reported in Table I: the profile simulated in TCAD is compared with the expression derived in the proposed model.  $x_{max}$  is at 170 nm and 0.76 V in case II, and 460 nm and 0.67 V in case III. (d) PPD capacitance as function of the photogenerated electrons: TCAD simulations are compared with the proposed model.

behavior with respect to the applied voltage to the TG and PPD voltage. For this purpose an equivalent 2D structure of all the regions crossed by path A is shown in Fig. 5a. The proposed structure is a stretched version of the effective charge transfer path from the PPD to the SN and contains the MOS part, the  $p^+$  layer, the n-well, and the p substrate. Path A is used to perform an electrostatic analysis deriving the potential barrier from Fig. 5b and illustrating the impact of the TG voltage. On the other hand, Path B corresponds to the current path and it is introduced to derive the proposed model of the transfered charges, validated by TCAD simulation results. As shown in Fig. 4b, the region beneath the TG is depleted of electrons along the effective charge transfer path. The SN is biased to the value of 2.5 V, leading to the fully depleted region of the carriers around this node due to the high shift in the

quasi-Fermi potential. In such configuration, with a positive voltage applied to TG, there is no inversion layer under the gate. The presence of mobile charges under the transfer gate can impact the barrier height. However, in this particular case where the SN is kept to a high voltage value and the substrate to ground, any mobile charge under the transfer gate will move towards the corresponding contact. Moreover, it is assumed that the SN voltage is constant, allowing to neglect the impact of its variation on the charge transfer [12]. The workfunction difference between the metal and the surface potential,  $\psi_s$ . During the rising edge of the  $V_{TG}$ , all the electrostatic potential of the MOS structure is shifting up, as illustrated in Fig. 5a. On the other hand, we define the potential barrier  $V_b$  as the voltage difference between the voltage inside the n-well,

$V_{\rm PPD}$ , and the minimum voltage in the p-doped semiconductor beneath the transfer gate,  $V_{\rm min}$ . This allows to predict the behavior of the barrier during all the transfer time and leads to

$$V_{\rm b}(t) = V_{\rm PPD}(t) - V_{\rm min}(t).$$

(6)

The term  $V_{\rm PPD}(t)$  can be derived by the following expression

$$V_{\rm PPD}(t + \Delta t) = V_{\rm PPD}(t) + \frac{i(t)\,\Delta t}{C_{\rm PPD}},\tag{7}$$

where i(t) is the charge transfer current and  $\Delta t$  the time interval between two consecutive instances along the discretized time axis. Starting from the initial value,  $V_{\rm PPD,0}$ , the values of  $V_{\rm PPD}(t)$  are calculated at each iteration by the potential variation due to the amount of transferred charges,  $i(t)\Delta t$ .

On the other hand, Fig. 5a depicts the potential along path A at different instants during the rise of  $V_{TG}$ . It clearly shows that the the potential barrier  $V_b$  is reduced due to the increase of the TG gate voltage, which enables the transfer of the charges to the SN. Using again the full-depletion approximation, the charge distribution, electric field and electrostatic potential along the proposed path are derived and plotted in Fig 5b. The expressions for the electric field and electrostatic potential are presented in Appendix B. Starting from  $a_2$ , the solution of the Poisson equation is equal to

$$\psi(a) = \psi_{\rm s} - E_{\rm s}(a - a_2) + \frac{qN_{\rm A^+}}{2\varepsilon_{\rm s}}(a - a_2)^2.$$

(8)

The increase in the gate voltage will increase the depletion region beneath the gate, until merging with the depleted region around the n-well. Under this assumption,  $\rho(a)$  can be considered to be equal to  $-qN_{A^+}$  for  $a_2 \leq a \leq a_5$ .  $V_{\min}(t)$  is the minimum value of the electrostatic potential in the region between the PPD and the semiconductor beneath the TG, while  $a_{\min}$  is the position of  $V_{\min}$  ( $V_{\min} = \psi(a_{\min})$ ). Since in this point the value of the electric field must be zero,  $a_{\min}$  is equal to  $a_2 + t_{p^+} - d_{p1}$ , where  $t_{p^+}$  is the thickness of the  $p^+$  layer and  $d_{p1}$  is the width of the depletion region of the  $p^+n$  junction in the  $p^+$  region (see Fig. 5b). The solution of the Poisson equation allows to obtain an analytical expression of the barrier, which includes the effect of  $V_{\rm TG}$ . By using the expression of the depletion region in a metal-oxide-semiconductor as a function of the applied gate voltage (reported in Appendix B) and after some mathematical manipulations,  $V_{\min}$  results in

$$\begin{aligned} V_{\min}(t) &= \frac{q N_{\rm A^+}}{2 \varepsilon_{\rm s}} \left( t_{\rm p^+} - d_{\rm p1} \right)^2 + \\ &- \left( t_{\rm p^+} - d_{\rm p1} \right) \frac{q N_{\rm A^+}}{C_{\rm ox}} \left[ 1 - \sqrt{1 + \frac{C_{\rm ox}^2}{2q \varepsilon_{\rm s} N_{\rm A^+}}} V_{\rm TG}(t) \right] + \ (9) \\ &+ \frac{q \varepsilon_{\rm s} N_{\rm A^+}}{2 C_{\rm ox}^2} \left[ 1 - \sqrt{1 + \frac{C_{\rm ox}^2}{2q \varepsilon_{\rm s} N_{\rm A^+}}} V_{\rm TG}(t) \right]^2 . \end{aligned}$$

From the proposed formula, it can be seen that the height of the potential barrier is a function of  $V_{\rm TG}$ , the doping concentration in the semiconductor and the thickness of the p<sup>+</sup> layer  $t_{\rm p^+}$ , which defines the position of the n-well. To verify the validity of the proposed analytical expression of the potential barrier

Fig. 4. a) Electrostatic Potential of the interface between the PPD and the TG when  $V_{TG} = 0 \text{ V}$ . Evidence of a potential barrier between the n-well and the semiconductor beneath the TG. b) Interface region is fully depleted along the effective charge transfer path, for a  $V_{TG} = 2.5 \text{ V}$  and  $V_{SN} = 2.5 \text{ V}$ .

and its variation over time, a transient simulation in TCAD is performed. This simulation decouples the illumination from the charge transfer, by having first a pulse of light and then a pulse of voltage applied to the TG. Thus the light does not affect the potential barrier during the transfer and its impact is not taken into account in the proposed model of  $V_{\rm b}$ . To guarantee a full charge transfer, the width of the TG pulse is set to be longer than needed. Moreover, in the specific case in which the transfer time is set to be shorter, i.e. high-speed applications such as ToF, the dynamic effects of the charge transfer, which are not considered in this derivation, have to be included. During this simulation, the SN is kept at the constant voltage of 2.5 V and a constant value equal to 7 fF has been used as a good approximation of  $C_{\text{PPD}}$  within the range of interest. The potential profile along the path B (Fig. 5a) is plotted during different instants of time in Fig. 5c. The simulation results show that this potential barrier is modulated by the gate voltage, as predicted by (6). All different values of  $V_{\rm b}$  are calculated from each potential profile and plotted as function of the simulation time in Fig. 5d. Initially, the barrier decreases following the linear slope of the  $V_{TG}$  rising edge. Once the gate voltage reaches the maximum value and remains constant, the potential barrier also starts to saturate and is slowly changing due only to the charge transfer. As shown in Fig. 5d, the simple model given by (6) is in excellent agreement with the TCAD simulation results. Increasing  $V_{TG}$ lowers  $V_{\rm b}$  until  $V_{\rm TG}$  reaches the threshold voltage of the MOS structure, above which the surface potential,  $\psi_{s}$ , only increases logarithmically with  $V_{TG}$  and most of the voltage drop occurs

Fig. 5. (a) Section of the interface between the TG and PPD with the 2D equivalent stretched version. Electrostatic potential at the interface between the PPD and the TG during the sweep of the gate voltage. The barrier voltage is changed by the TG and PPD voltage values. (b) The charge distribution, electric field, and electrostatic potential under the assumptions of fully depletion and abrupt transitions. (c) Electrostatic potential along the path B crossing the PPD well, the interface, the area beneath the TG and the SN, for different time instants.  $t_1 - t_4$  corresponds to the rising edge of  $V_{TG}$ , while  $t_5 - t_6$  refer to  $V_{TG}$  constant. (d) Value of the potential barrier during time along the charge transfer period. The behavior of the barrier is well predicted by the proposed model.

across the oxide [24]. This means that above threshold, the surface potential will almost not be influenced by  $V_{\rm TG}$  and no additional potential barrier reduction is achieved. On the other hand, a higher voltage will force the surface p<sup>+</sup> layer to be further depleted. Once this layer is fully depleted, the pinned structure is no longer present and the potential inside the n-well is then determined by the  $V_{\rm TG}$  voltage.

## V. CHARGE TRANSFER MODELING IN PPD

## A. Charge transfer across a potential barrier

Once the analytical expression of the potential barrier is developed and validated with TCAD simulations, it can be used to derive an expression of the charge transfer current. Relying on the thermionic emission mechanism, the transfer current crossing a potential barrier is obtained. The thermionic emission theory states that the electrons which have enough thermal velocity in the transfer direction will cross the barrier on the charge transfer path [20] and it has been used to model the charge transfer between the PPD and the SN [12], [25]. In TCAD simulations, path A is chosen as the path with the minimum barrier and therefore the highest current density. In the model, the assumption is that all the current is flowing along the minimum barrier path, path A. Based on this transportation mechanism, the expression of the charge transfer current that embeds the effects of both the PPD and TG voltages and the other physical parameters on  $V_{\rm b}$  is

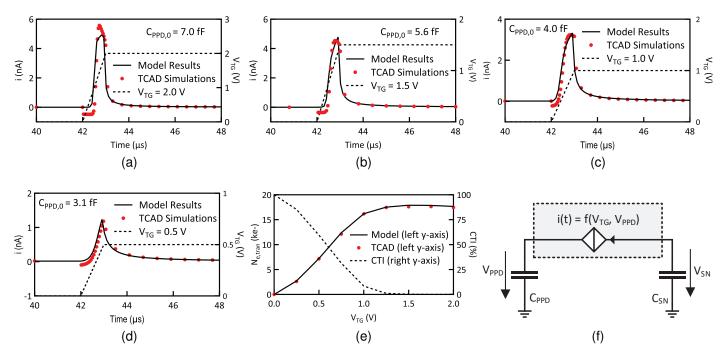

Fig. 6. (a,b,c,d) Current pulses representing the charge transfer from PPD to SN for four different  $V_{TG}$  values: TCAD simulations are compared with the proposed model. (e) Total number of transferred electrons from PPD to SN and CTI as a function of  $V_{TG}$ , derived when integrating the current over the time. (f) Proposed equivalent circuit for the PPD, TG, and SN, where the function f is given in (10).

derived. The charge transfer current is given by

$$i(t) = I_0 \cdot \exp\left[-\frac{V_{\rm b}(t)}{U_T}\right],\qquad(10)$$

where  $V_{\rm b}$  is given by Equations (6) and (9) and  $I_0$  is equal to  $A S_A T^2$ , with A equal to the Richardson constant [20], and  $S_A$  the area of the cross-section on the charge transfer path at the barrier position. To validate this expression, the total current that flows through the SN can be extracted from the transient TCAD simulation results. The latter is shown in Fig. 6a-d for different values of  $V_{TG}$ : 2.0 V, 1.5 V,  $1.0\,\mathrm{V}$  and  $0.5\,\mathrm{V}$ . The simulation results obtained during the charge transfer can be compared with (10). The agreement between TCAD simulation results and the proposed model is good and confirms that the derived expression predicts the characteristic of the charge transfer from the PPD to the SN. The exact values of the cross-section  $S_A$  have to be extracted from TCAD by looking at the current density distribution during the charge transfer. Based on the analysis of  $C_{\text{PPD}}$  shown in Section III-B, we initially considered  $C_{\text{PPD}}$ as a constant parameter of the model, named  $C_{\rm PPD,0}$ , for the specific value of light used during simulation. The value of  $C_{\rm PPD,0}$  is equal to 7 fF and is shown in Fig. 3d. However, to obtain such an agreement between TCAD simulations and the proposed model, the constant value  $C_{\text{PPD},0}$  has been used as a fitting parameter. Thus, the value of  $C_{\text{PPD},0}$  has been reported for each simulated case in Fig. 6a-d. This variation is reasonably predicted in Fig. 3d, where the value of  $C_{\rm PPD}$ is not independent of the number of electrons stored in the photodiode. Although the dynamic modeling of  $C_{\text{PPD}}$  will need a further investigation, its use as a fitting parameter allows to verify the proposed expression for the charge transfer current. All the current pulses in Fig. 6a-d exhibit almost zero

transferred charges till the TG voltage reaches a precise value. The voltage beneath the gate has to be higher than the PPD voltage in order to allow an efficient transfer of the integrated charge. The delayed charge transfer with respect to the TG voltage is consistent with [26]. When the final value of  $V_{\rm TG}$ is below  $V_{\rm PPD}$ , it results in an incomplete charge transfer. The latter is shown in the last two cases in Fig. 6c-d, where the pulse of current is considerably smaller than Fig. 6a-b. On the other hand, initially the current exhibits negative values in transient simulations. This negative current can be explained as a capacitive coupling (overlap) between the TG and the SN. The calculated current through the proposed model does not include this phenomena, hence the two curves substantially differ in this interval of time. The data of Fig. 6a-d can be used to evaluate the charge transfer inefficiency (CTI) for a total integrated charge of 18.000 e<sup>-</sup> in the PPD as a function of  $V_{\rm TG}$ , over a transfer time of 10 µs. Once integrating the current over the time, the total transferred charge is obtained and plotted in Fig. 6e, which is in excellent agreement with results of TCAD simulation. The CTI is plotted together with the amount of transferred electrons,  $N_{\rm e,tran}$ , in Fig. 6e.

## B. Model Implementation and Equivalent Circuit of PPD

In order to simulate the transient behavior with the proposed model, a quasi-static assumption together with Equations (5), (6) and (10) are used. An equivalent circuit for the charge transfer from the PPD to the SN is given in Fig. 6f. The PPD and the SN are replaced by two equivalent linear and time invariant capacitors,  $C_{\rm PPD}$  and  $C_{\rm SN}$ . The TG is replaced by a voltage-controlled current-source (VCCS). Since in a p<sup>+</sup>np PPD the electrons are transferred to the SN, the VCCS indicates a current flowing from the SN to the PPD. Relying on the proposed model, the transfer current is expressed as function of  $V_{\rm TG}$  and  $V_{\rm PPD}$  according to (10). This equivalent circuit, together with the proposed expressions, represent an essential step towards the circuit-level design of PPD-based pixels in CMOS image sensors. This model covers the case where the charge transfer is limited by the potential barrier between the PPD and the TG, with the SN voltage remaining at a constant voltage and always higher than the PPD maximum voltage and the TG channel voltage.

#### VI. CONCLUSION

In this paper, a physics-based compact model for the PPD with the TG is developed and fully validated with TCAD opto-electrical simulations. This model is able to predict the electrical behavior of the charge transfer from the PPD to the SN for different values of the physical parameters, when the transfer is only limited by the potential barrier between the PPD and TG. The proposed model relies on the thermionic emission current mechanism, full-depletion approximation and barrier modulation due to  $V_{\rm TG}$  and  $V_{\rm PPD}$  to express the charge transfer current with respect to the physical parameters. The presented physics-based model provides the core of a more complete future PPD compact model, enabling the design and circuit-level simulations of PPD-based pixel in CMOS image sensors.

### **A**PPENDIX

#### A. Electrostatics in PPD device

Solving Poisson equation, the electric field and the potential profiles in the PPD device are respectively given by

$$\begin{split} \mathcal{E}(x) &= \\ &- \frac{q N_{\rm A^+}}{\varepsilon_{\rm s}} (x - x_{\rm p1}) \left[ u(x - x_{\rm p1}) - u(x - x_{\rm n}) \right] + \\ &+ \left[ \frac{q N_{\rm D}}{\varepsilon_{\rm s}} (x - x_{\rm n}) + \mathcal{E}(x_{\rm n}) \right] \left[ u(x - x_{\rm n}) - u(x - x_{\rm p}) \right] + \\ &+ \left[ - \frac{q N_{\rm A}}{\varepsilon_{\rm s}} (x - x_{\rm p2}) + \mathcal{E}(x_{\rm p}) \right] \left[ u(x - x_{\rm p}) - u(x - x_{\rm p2}) \right], \end{split}$$

(A.1)

$$\begin{split} \psi(x) &= \\ &+ \frac{qN_{\rm A^+}}{2\varepsilon_{\rm s}} (x - x_{\rm p1})^2 \left[ u(x - x_{\rm p1}) - u(x - x_{\rm n}) \right] + \\ &\left[ -\frac{qN_{\rm D}}{2\varepsilon_{\rm s}} (x - x_{\rm n})^2 + \frac{qN_{\rm A^+}}{\varepsilon_{\rm s}} (x_{\rm n} - x_{\rm p1}) \, x + \psi(x_{\rm n}) \right] \\ &\left[ u(x - x_{\rm n}) - u(x - x_{\rm p}) \right] + \\ &+ \left[ \frac{qN_{\rm A}}{2\varepsilon_{\rm s}} (x - x_{\rm p2})^2 + \psi(x_{\rm p}) \right] \left[ u(x - x_{\rm p}) - u(x - x_{\rm p2}) \right], \end{split}$$

(A.2)

where  $u(x - x_0)$  is the step function and is equal to unity when  $x > x_0$  and zero elsewhere.

#### B. Electrostatics along path A

Solving Poisson equation under full-depletion approximation leads to the electric field  $\mathcal{E}(a)$  and electrostatic potential  $\psi(a)$  along the path A between  $a_2$  and  $a_5$ , given by the following expressions

$$\begin{split} \mathcal{E}(a) &= \\ & \left[ E_{\rm s} - \frac{qN_{\rm A^+}}{\varepsilon_{\rm s}}(a-a_2) \right] \left[ u(a-a_2) - u(a-a_5) \right], \\ \psi(a) &= \\ & \left[ \psi_{\rm s} - E_{\rm s}(a-a_2) + \frac{qN_{\rm A^+}}{2\varepsilon_{\rm s}}(a-a_2)^2 \right] \\ & \left[ u(a-a_2) - u(a-a_5) \right], \end{split}$$

(B.1)

where  $\psi_{\rm s}$  is the surface electrostatic potential and  $E_{\rm s}$  the electric field at the surface, obtained by  $\psi_{\rm s} = x_{\rm d}^2 q N_{\rm A^+}/2 \varepsilon_{\rm s}$  and  $E_{\rm s} = -x_{\rm d} q N_{\rm A^+}/\varepsilon_{\rm s}$ . Moreover, to obtain (9), the following expression for the depletion region,  $x_{\rm d}$ , in a metal-oxide-semiconductor is used

$$x_{\rm d} = -\frac{\varepsilon_{\rm s}}{C_{\rm ox}} + \sqrt{\left(\frac{\varepsilon_{\rm s}}{C_{\rm ox}}\right)^2 + \frac{\varepsilon_{\rm s}}{2qN_{\rm A^+}}}V_{\rm TG}\,.\tag{B.2}$$

This has been derived by solving Poisson equation of the TG MOS structure [27].

#### REFERENCES

- N. Teranishi, A. Kohno, Y. Ishihara, E. Oda, and K. Arai, "An Interline CCD Image Sensor with Reduced Image Lag," *IEEE Transactions on Electron Devices*, vol. 31, no. 12, pp. 1829–1833, 1984.

- [2] V. Goiffon, M. Estribeau, J. Michelot, P. Cervantes, A. Pelamatti, O. Marcelot, and P. Magnan, "Pixel Level Characterization of Pinned Photodiode and Transfer Gate Physical Parameters in CMOS Image Sensors," *IEEE Journal of the Electron Devices Society*, vol. 2, no. 4, pp. 65–76, 2014.

- [3] B. Mheen, Y. J. Song, and A. J. P. Theuwissen, "Negative Offset Operation of Four-Transistor CMOS Image Pixels for Increased Well Capacity and Suppressed Dark Current," *IEEE Electron Device Letters*, vol. 29, no. 4, pp. 347–349, 2008.

- [4] J. P. Carrre, S. Place, J. P. Oddou, D. Benoit, and F. Roy, "CMOS image sensor: Process impact on dark current," in 2014 IEEE International Reliability Physics Symposium, 2014.

- [5] E. R. Fossum and D. B. Hondongwa, "A Review of the Pinned Photodiode for CCD and CMOS Image Sensors," *IEEE Journal of the Electron Devices Society*, vol. 2, no. 3, pp. 33–43, 2014.

- [6] A. Boukhayma, A. Peizerat, and C. Enz, "A Sub-0.5 Electron Read Noise VGA Image Sensor in a Standard CMOS Process," *IEEE Journal* of Solid-State Circuits, vol. 51, no. 9, pp. 2180–2191, 2016.

- [7] M. W. Seo, S. Kawahito, K. Kagawa, and K. Yasutomi, "A 0.27 e<sub>rms</sub> Read Noise 220 μV/e- Conversion Gain Reset-Gate-Less CMOS Image Sensor with 0.11 μm CIS Process," *IEEE Electron Device Letters*, vol. 36, no. 12, pp. 1344–1347, 2015.

- [8] Y. Tochigi, K. Hanzawa, Y. Kato, R. Kuroda, H. Mutoh, R. Hirose, H. Tominaga, K. Takubo, Y. Kondo, and S. Sugawa, "A globalshutter CMOS image sensor with readout speed of 1Tpixel/s burst and 780 Mpixel/s continuous," in 2012 IEEE International Solid-State Circuits Conference, 2012.

- [9] Z. Cao, Y. Zhou, Q. Li, L. Liu, and N. Wu, "Design of pixel for high speed CMOS image sensor," in *Proceedings of the International Image Sensor Workshop*, 2013.

- [10] F. Acerbi, M. Moreno-Garcia, G. Kkl, R. M. Gancarz, B. Bttgen, A. Biber, D. Furrer, and D. Stoppa, "Optimization of Pinned Photodiode Pixels for High-Speed Time of Flight Applications," *IEEE Journal of the Electron Devices Society*, vol. 6, pp. 365–375, 2018.

- [11] T. C. Millar, N. Sarhangnejad, N. Katic, K. Kutulakos, and R. Genov, "The Effect of Pinned Photodiode Shape on Time-of-Flight Demodulation Contrast," *IEEE Transactions on Electron Devices*, vol. 64, no. 5, pp. 2244–2250, 2017.

- [12] L. Han, S. Yao, and A. J. P. Theuwissen, "A Charge Transfer Model for CMOS Image Sensors," *IEEE Transactions on Electron Devices*, vol. 63, no. 1, pp. 32–41, 2016.

- [13] S. Takahashi, Y.-M. Huang, J.-J. Sze, T.-T. Wu, F.-S. Guo, W.-C. Hsu, T.-H. Tseng, K. Liao, C.-C. Kuo, T.-H. Chen, W.-C. Chiang, C.-H. Chuang, K.-Y. Chou, C.-H. Chung, K.-Y. Chou, C.-H. Tseng, C.-J. Wang, and D.-N. Yaung, "A 45 nm Stacked CMOS Image Sensor Process Technology for Submicron Pixel," *Sensors*, vol. 17, no. 12, 2017.

- [14] O. Marcelot, V. Goiffon, F. Nallet, and P. Magnan, "Pinned Photodiode CMOS Image Sensor TCAD Simulation: In-Depth Analysis of in-Pixel Pinning Voltage Measurement for a Diagnostic Tool," *IEEE Transactions* on Electron Devices, vol. 64, no. 2, pp. 455–462, 2017.

- [15] Synopsys.com, "Technology computer aided design (TCAD)." [Online]. Available: https://www.synopsys.com/silicon/tcad.html

- [16] A. Pelamatti, "Estimation and Modeling of Key Design Parameters of Pinned Photodiode CMOS Image Sensors for High Temporal Resolution Applications," Ph.D. dissertation, Université de Toulouse, 2015.

- [17] A. Pelamatti, V. Goiffon, M. Estribeau, P. Cervantes, and P. Magnan, "Estimation and Modeling of the Full Well Capacity in Pinned Photodiode CMOS Image Sensors," *IEEE Electron Device Letters*, vol. 34, no. 7, pp. 900–902, 2013.

- [18] Y. Xu, X. Ge, and A. Theuwissen, "Investigating Transfer Gate Potential Barrier by Feed-Forward Effect Measurement," in *Proceedings of the International Image Sensor Workshop*, 2015.

- [19] H. Alaibakhsh and M. A. Karami, "A New Analytical Pinned Photodiode Capacitance Model," *IEEE Electron Device Letters*, vol. 39, no. 3, pp. 379–382, 2018.

- [20] S. Sze and K. Ng, Physics of Semiconductor Devices. Wiley, 2006.

- [21] C. Cao, B. Shen, B. Zhang, L. Wu, and J. Wang, "An Improved Model for the Full Well Capacity in Pinned Photodiode CMOS Image Sensors," *IEEE Journal of the Electron Devices Society*, vol. 3, no. 4, pp. 306–310, 2015.

- [22] A. Pelamatti, V. Goiffon, A. Chabane, P. Magnan, C. Virmontois, O. Saint-P, and M. B. de Boisanger, "Charge Transfer Speed Analysis in Pinned Photodiode CMOS Image Sensors based on a Pulsed Storage-Gate Method," in 45th European Solid State Device Research Conference, 2015.

- [23] C. Chen, Z. Bing, W. Junfeng, and W. Longsheng, "Measurement of charge transfer potential barrier in pinned photodiode CMOS image sensors," *Journal of Semiconductors*, vol. 37, no. 5, p. 054007, 2016.

- [24] C. Enz and E. Vittoz, Charge-Based MOS Transistor Modeling: The EKV Model for Low-Power and RF IC Design. Wiley, 2006.

- [25] E. R. Fossum, "Charge Transfer Noise and Lag in CMOS Active Pixel Sensors," in *Proceedings IEEE Workshop Charge-Coupled Devices and Advanced Image Sensors*, 2003.

- [26] Y. Xu, X. Ge, and A. J. P. Theuwissen, "A Potential-Based Characterization of the Transfer Gate in CMOS Image Sensors," *IEEE Transactions* on *Electron Devices*, vol. 63, no. 1, pp. 42–48, 2016.

- [27] J. Janesick, Scientific Charge-Coupled Devices. SPIE Press, 2001.

Assim Boukhaym obtained his Ph.D. at Ecole Polytechnique Fédérale de Lausanne, Lausanne, Switzerland, and Commissariat a l'Energie Atomique (CEA-LETI), Grenoble, France, with Prof. Christian Enz, on the subject of CMOS image sensors. He is currently working as researcher leader at Integrated Circuits Laboratory at EPFL.

Farzan Jazaeri received the Ph.D. degree in microelectronics from the Ecole Polytechnique Fédérale, Lausanne, Switzerland, in 2015. He joined the Integrated Circuits Laboratory, EPFL, involving in electron-device modeling, where he is currently a Research Scientist and Project Leader. His current research interests include solid state physics and advanced semiconductor devices for operation within extreme harsh environments, i.e., high energy particle background and cryogenic temperatures for space applica-

tions and quantum computations.

Christian Enz (M84S12) received the M.S. and Ph.D. degrees in electrical engineering from the Ecole Polytechnique Fédérale de Lausanne (EPFL), Lausanne, Switzerland, in 1984 and 1989, respectively. In 2013, he joined EPFL as a Full Professor, where he is currently the Director of the Institute of Microengineering and also the Head of the Integrated Circuits Laboratory. His technical interests and expertise are in the fields of very low-power analog and RC IC design and semiconductor device modeling.

**Raffaele Capoccia** received his B.Sc. and M.Sc. degrees in electrical engineering from Polytechnic University of Turin, Italy, in 2012 and 2014, respectively. He is currently a Doctoral Assistant with the Integrated Circuits Laboratory, École Polytechnique Fédérale de Lausanne, Lausanne, Switzerland, where he is involved in the research on CMOS image sensors. The focus of his work is on the design of lownoise readout circuits and device modeling for CMOS image sensors.