# Low-Power Design of Digital VLSI Circuits around the Point of First Failure

## Thèse N° 9180

Présentée le 25 janvier 2019

à la Faculté des sciences et techniques de l'ingénieur Laboratoire de circuits pour télécommunications Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

## **ANDREA BONETTI**

Acceptée sur proposition du jury

Prof. C. Enz, président du jury Prof. A. P. Burg, Dr A. S. Teman, directeurs de thèse Prof. M. Alioto, rapporteur Prof. D. Bol, rapporteur Prof. Y. Leblebici, rapporteur

## Acknowledgements

First of all, I would like to thank my thesis advisor, Prof. Andreas Burg, for giving me the opportunity to join his laboratory and for his continuous support and guidance throughout my doctoral studies. I am very grateful for every technical discussion we had, which always pushed me to look at research from different perspectives, helping me to continuously discover new aspects in digital VLSI design. I also would like to thank my thesis coadvisor, Dr. Adam Teman, especially for his invaluable support during the steep learning curve over the first years of my doctoral studies.

I would like to thank Prof. Christian Enz (Integrated Circuits Laboratory, EPFL) for acting as president of my PhD jury, Prof. Yusuf Leblebici (Microelectronic Systems Laboratory, EPFL), Prof. Massimo Alioto (Green IC Group, National University of Singapore) and Prof. David Bol (Electronic Circuits and Systems Group, Université Catholique de Louvain) for serving as examiners for my thesis defense.

I feel very lucky for having conducted my doctoral studies at the Telecommunications Circuits Laboratory, EPFL. There, I had the chance to meet and work with incredibly talented people who made the laboratory a very supportive and stimulating environment. For the great time we had, I would like to thank: Alexios Balatsoukas-Stimming, Andrew Austin, Christian Senning, Christoph Müller, Ester Vicario Bravo, Georgios Karakonstantis, Ioanna Paniara, Jeremy Constantin, Lorenz Schmid, Marco Widmer, Matthieu Cotting, Nicholas Preyss, Nicolas Frigerio, Orion Afisiadis, Pascal Giard, Pascal Meinerzhagen, Pavle Belanovic, Reza Ghanaatian, Ricardo Gómez Gómez, Robert Giterman, Shrikanth Ganapathy and Yann Kurzo.

Finally, I would like to thank my family: Marisa, Marco and Dirce for their continuous support and for having always believed in me.

Lausanne, January 1st 2019

Andrea Bonetti

## Abstract

As an increase of intelligent and self-powered devices is forecasted for our future everyday life, the implementation of energy-autonomous devices that can wirelessly communicate data from sensors is crucial. Even though techniques such as voltage scaling proved to effectively reduce the energy consumption of digital circuits, additional energy savings are still required for a longer battery life. One of the main limitations of essentially any low-energy technique is the potential degradation of the quality of service (QoS). Thus, a thorough understanding of how circuits behave when operated around the point of first failure (PoFF) is key for the effective application of conventional energy-efficient methods as well as for the development of future low-energy techniques. In this thesis, a variety of circuits, techniques, and tools is described to reduce the energy consumption in digital systems when operated either in the safe and conservative exact region, close to the PoFF, or even inside the inexact region.

A straightforward approach to reduce the power consumed by clock distribution while safely operating in the exact region is dual-edge-triggered (DET) clocking. However, the DET approach is rarely taken, primarily due to the perceived complexity of its integration. In this thesis, a fully automated design flow is introduced for applying DET clocking to a conventional single-edge-triggered (SET) design. In addition, the first static true-single-phase-clock DET flip-flop (DET-FF) that completely avoids clock-overlap hazards of DET registers is proposed. Even though the correct timing of synchronous circuits is ensured in worst-case conditions, the critical path might not always be excited. Thus, dynamic clock adjustment (DCA) has been proposed to trim any available dynamic timing margin by changing the operating clock frequency at runtime. This thesis describes a dynamically-adjustable clock generator (DCG) capable of modifying the period of the produced clock signal on a cycle-by-cycle basis that enables the DCA technique. In addition, a timing-monitoring sequential (TMS) that detects input transitions on either one of the clock phases to enable the selection of the best timing-monitoring strategy at runtime is proposed.

Energy-quality scaling techniques aim at trading lower energy consumption for a small degradation on the QoS whenever approximations can be tolerated. In this thesis, a low-power methodology for the perturbation of baseline coefficients in reconfigurable finite impulse response (FIR) filters is proposed. The baseline coefficients are optimized to reduce the switching activity of the multipliers in the FIR filter, enabling the possibility of scaling the power consumption of the filter at runtime.

The area as well as the leakage power of many system-on-chips is often dominated by embedded memories. Gain-cell embedded DRAM (GC-eDRAM) is a compact, low-power and

## Abstract

CMOS-compatible alternative to the conventional static random-access memory (SRAM) when a higher memory density is desired. However, due to GC-eDRAMs relying on many interdependent variables, the adaptation of existing memories and the design of future GC-eDRAMs prove to be highly complex tasks. Thus, the first modeling tool that estimates timing, memory availability, bandwidth, and area of GC-eDRAMs for a fast exploration of their design space is proposed in this thesis.

**Key Words:** Digital VLSI Circuits, Low-Power Design, Nanometer Nodes, Clock Distribution, Dual-Edge-Triggered Clocking, Dual-Edge-Triggered Registers, Timing Monitoring, Dynamic-Timing Margins, Dynamic Clock Adjustment, Multipliers, FIR Filters, Approximate Computing, Gain-Cell Embedded DRAMs, Memory Design, Architecture Optimization.

## Sommario

Dato che un incremento di dispositivi intelligenti e autoalimentati è previsto in futuro, la progettazione di dispositivi energeticamente autonomi che telecomunichino i dati raccolti da sensori è cruciale. Sebbene tecniche come l'abbassamento della tensione di alimentazione riducano efficientemente l'energia consumata dai circuiti digitali, ulteriori risparmi energetici sono richiesti per aumentare la durata della batteria. Uno dei limiti di essenzialmente ogni tecnica a basso consumo di energia è la potenziale degradazione della qualità del servizio. Perciò, la comprensione di come i circuiti si comportino quando operati attorno al primo punto di malfunzionamento è essenziale per ridurre il consumo energetico. In questa tesi, circuiti, tecniche e strumenti sono descritti per ridurre l'energia consumata in sistemi digitali quando operati nella conservativa regione libera da imprecisioni, vicino al primo punto di malfunzionamento o in presenza di errori.

Considerando la regiona libera da imprecisioni, un approccio ben conosciuto per ridurre la potenza consumata nella distribuzione del segnale di clock è l'uso del dual-edge-triggered (DET) clocking. Tuttavia, l'approccio DET è raramente scelto, primariamente a causa della percepita complessità della sua integrazione. In questa tesi, un flusso di progettazione automatico è introdotto per l'applicazione del DET clocking ad un circuito inizialmente progettato con il convenzionale single-edge-triggered (SET) clocking. In aggiunta, il primo flip-flop DET statico con true-single-phase-clock che rimuove il rischio di clock overlap presente nei convenzionali registri DET è proposto in questa tesi.

Sebbene il corretto timing di circuiti sincroni è verificato nelle peggiori condizioni, il percorso critico può non sempre essere attivato. Per questo motivo, la regolazione dinamica del segnale di clock può rimuovere la presenza di qualsiasi margine dinamico di timing con la modifica della frequenza di clock durante il tempo di esecuzione. Per abilitare questa tecnica, un generatore di clock capace di modificare la frequenza del segnale prodotto ad ogni ciclo è descritto in questa tesi. In aggiunta, un flip-flop capace di avvertire transizioni di segnale al suo ingresso durante una delle due fasi di clock è proposto.

Le tecniche di computazione approssimale puntano a ridurre l'energia consumata al costo di una degradazione della qualitá del servizio qualora queste approssimazioni possano essere tollerate. In questa tesi, la perturbazione dei coefficienti di base di un filtro finite impulse response (FIR) programmabile è usata per ridurre la potenza consumata dal filtro. I coefficienti di base sono ottimizzati per ridurre l'attività di commutazione dei moltiplicatori del filtro FIR, permettendo la possibilità di ridurre la potenza consumata del filtro durante il tempo di esecuzione.

## Sommario

L'area così come la potenza di leakage di diversi system-on-chip è spesso dominata dalle memorie integrate. Le gain-cell embedded DRAM (GC-eDRAM) sono valide alternative alle convenzionali static random-access memory (SRAM) grazie alla loro compattezza, basso consumo di potenza e compatibilità con la tecnologia CMOS qualora un'alta densità di memoria è desiderata. Tuttavia, l'integrazione di GC-eDRAM già esistenti e la progettazione di GC-eDRAM future sono processi complessi a causa della dipendenza di queste memorie su numerose variabili interdipendenti. In questa tesi, il primo modello di timing, disponibilità, banda e area delle GC-eDRAM è proposto per una rapida esplorazione del loro spazio di progetto.

**Parole Chiave:** Circuiti Digitali, Progettazione a Basso Consumo di Potenza, Tecnologie Nanometriche, Distribuzione del Segnale di Clock. Dual-Edge-Triggered Clocking, Timing Monitoring, Margini Margini Dinamici di Timing, Regolazione Dinamica del Segnale di Clock, Moltiplicatori, Filtri FIR, Computazione Approssimale, Gain-Cell Embedded DRAMs, Progettazione di Memorie, Ottimizzazione delle Architetture.

# Contents

| Ac | knov  | wledge  | ments     |                                                      | i   |

|----|-------|---------|-----------|------------------------------------------------------|-----|

| Ał | ostra | ct (Eng | lish/Ital | iano)                                                | iii |

| 1  | Intr  | oducti  | on        |                                                      | 1   |

|    | 1.1   | Contr   | ibutions  |                                                      | 3   |

|    | 1.2   | Thesi   | s Outline |                                                      | 7   |

|    | 1.3   | Select  | ted Publi | cations                                              | 8   |

|    | 1.4   | Third   | -Party Co | ontributions                                         | 9   |

| 2  | Du    | al-Edg  | e-Trigge  | red Clocking for Low-Power Operation                 | 11  |

|    | 2.1   | Autor   | nated Int | tegration of Dual-Edge Triggered Clocking            | 13  |

|    |       | 2.1.1   | Motivat   | tion and Tradeoffs in DET Clocking                   | 14  |

|    |       | 2.1.2   | Design    | and Implementation of DET Library Cells              | 17  |

|    |       | 2.1.3   | Propose   | ed DET Digital Design Flow                           | 20  |

|    |       |         | 2.1.3.1   | Initial SET Synthesis                                | 20  |

|    |       |         | 2.1.3.2   | Post-Synthesis Conversion to DET                     | 21  |

|    |       |         | 2.1.3.3   | DET Automatic Place and Route Flow                   | 22  |

|    |       |         | 2.1.3.4   | Methodology for Mixed SET/DET Integration            | 23  |

|    |       | 2.1.4   | Implem    | nentation and Results                                | 24  |

|    |       |         | 2.1.4.1   | Test Cases and Implementation                        | 25  |

|    |       |         | 2.1.4.2   | Power Savings                                        | 28  |

|    |       |         | 2.1.4.3   | Area Overhead                                        | 30  |

|    |       | 2.1.5   | Conclu    | sion                                                 | 31  |

|    | 2.2   | An Ov   | verlap-Co | ontention Free True-Single-Phase Clock DET Flip-Flop | 32  |

|    |       | 2.2.1   | Clock-0   | Overlap Failure Risk in DET-TGLM Cells               | 32  |

|    |       |         | 2.2.1.1   | Overview of the DET-TGLM                             | 33  |

|    |       |         | 2.2.1.2   | Clock-Overlap Failure Risk                           | 34  |

|    |       | 2.2.2   | Propos    | ed SDET-TSPCFF                                       | 36  |

|    |       | 2.2.3   | Simulat   | tions and Results                                    | 38  |

|    |       | 2.2.4   | Conclu    | sion                                                 | 40  |

### Contents

| 3 | Cir | cuits an | nd Techniques to Monitor and Trim Dynamic Timing Margins              | 41       |  |  |  |  |

|---|-----|----------|-----------------------------------------------------------------------|----------|--|--|--|--|

|   | 3.1 | A Cloc   | k Generator for Cycle-by-Cycle Dynamic Clock Adjustment               | 43       |  |  |  |  |

|   |     | 3.1.1    | Concept of Dynamic Clock Adjustment                                   | 44       |  |  |  |  |

|   |     | 3.1.2    | Dynamically-Adjustable Clock Generator                                | 45       |  |  |  |  |

|   |     | 3.1.3    | Test Chip and Measurements Results                                    | 46       |  |  |  |  |

|   |     |          | 3.1.3.1 Characterization of the DCG                                   | 47       |  |  |  |  |

|   |     |          | 3.1.3.2 Application of the DCG to a DCA-Enabled Microprocessor        | 48       |  |  |  |  |

|   |     | 3.1.4    | Conclusion                                                            | 49       |  |  |  |  |

|   | 3.2 | A Timi   | ng-Monitor Sequential for Forward and Backward Error-Detection        | 50       |  |  |  |  |

|   |     | 3.2.1    | Proposed Timing-Monitoring Sequential                                 | 52       |  |  |  |  |

|   |     | 3.2.2    | Timing Analyses Enabled by the TMS                                    | 54       |  |  |  |  |

|   |     | 3.2.3    | Simulations Results and Measurements                                  | 55       |  |  |  |  |

|   |     |          | 3.2.3.1 Post-Layout Simulations of the TMS                            | 55       |  |  |  |  |

|   |     |          | 3.2.3.2 Measurements of a Multiplier Using TMS Cells                  | 57       |  |  |  |  |

|   |     | 3.2.4    | Conclusion                                                            | 58       |  |  |  |  |

|   |     |          |                                                                       |          |  |  |  |  |

| 4 | -   | -        | Hardware Properties at the Algorithm Level for Energy-Quality Scaling | 59       |  |  |  |  |

|   | 4.1 | 0        | Multipliers                                                           | 62       |  |  |  |  |

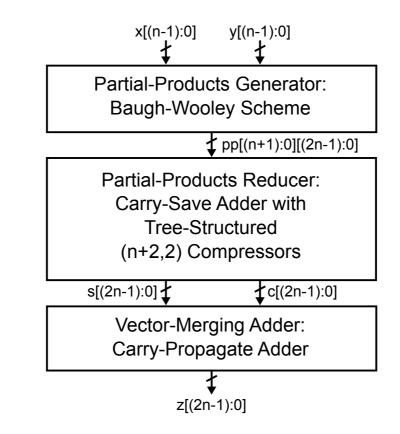

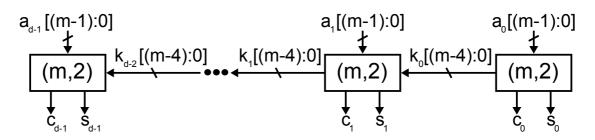

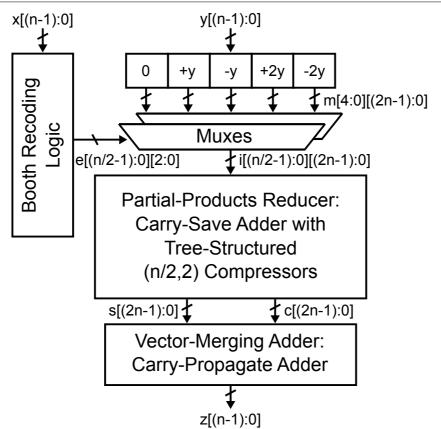

|   |     |          | Radix-2 Bough-Wooley Multiplier                                       | 64       |  |  |  |  |

|   |     |          | Radix-4 Booth-Recoded Multiplier                                      | 64       |  |  |  |  |

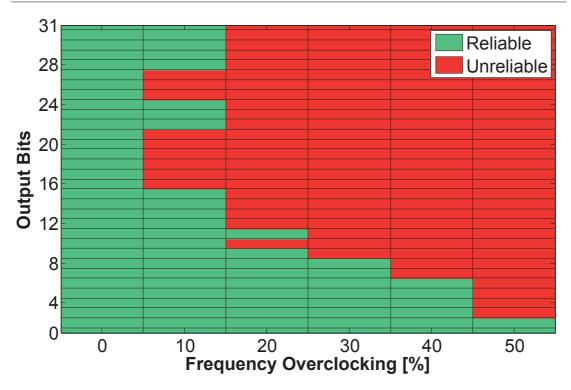

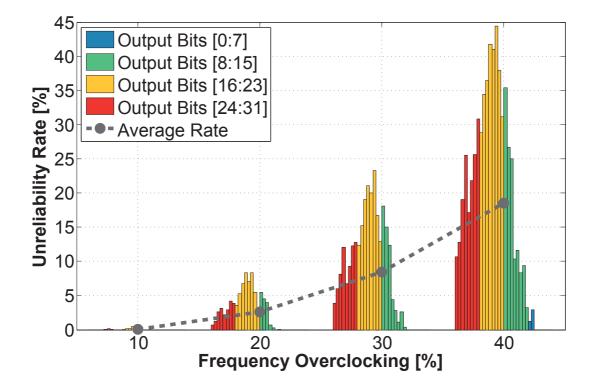

|   | 4.2 |          | e Over-Scaling                                                        | 65       |  |  |  |  |

|   |     |          | Overclocking a Multiplier                                             | 65       |  |  |  |  |

|   |     |          | Limitations of Voltage Over-Scaling                                   | 68       |  |  |  |  |

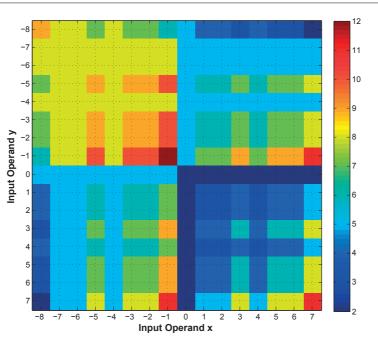

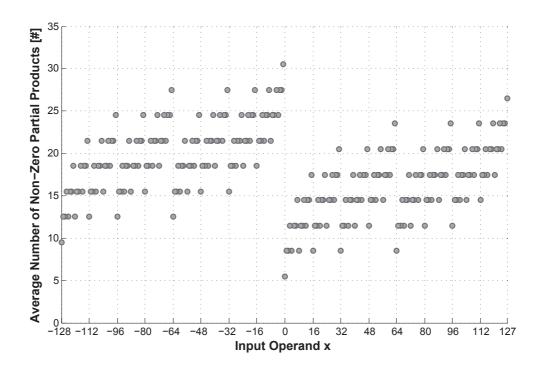

|   | 4.3 |          | ing Activity in Multipliers                                           | 69       |  |  |  |  |

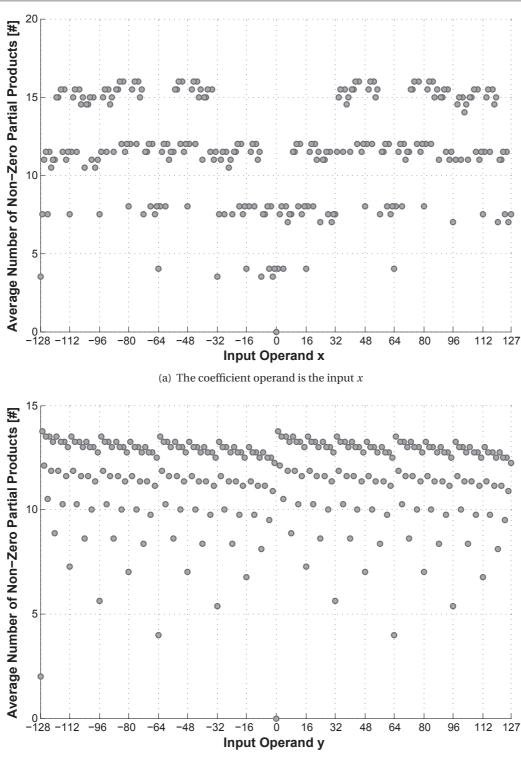

|   |     |          | Radix-2 Bough-Wooley Multiplier                                       | 69       |  |  |  |  |

|   |     |          | Radix-4 Booth-Recoded Multiplier                                      | 71       |  |  |  |  |

|   | 4.4 |          | Level Characterization of Multipliers                                 | 71       |  |  |  |  |

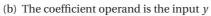

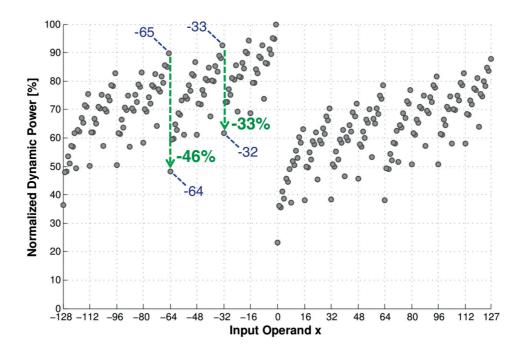

|   |     |          | Power Characterization                                                | 73       |  |  |  |  |

|   |     |          | Timing Analysis                                                       | 77       |  |  |  |  |

|   | 4.5 |          | ation to an FIR Filter                                                | 78       |  |  |  |  |

|   |     |          | Optimization Algorithm                                                | 80       |  |  |  |  |

|   |     |          | Simulations Results                                                   | 81       |  |  |  |  |

|   |     |          | Test Chip and Measurements Results                                    | 84       |  |  |  |  |

|   | 4.6 | Conclu   | usion                                                                 | 87       |  |  |  |  |

| 5 | Gai | n-Cell I | Embedded DRAMs: Modeling and Design-Space Exploration                 | 89       |  |  |  |  |

| J | 5.1 |          | d Work                                                                | 91       |  |  |  |  |

|   | 5.2 |          |                                                                       |          |  |  |  |  |

|   | 0.2 | 0        | Gain Cell                                                             | 92<br>93 |  |  |  |  |

|   |     |          | Memory Organization in GC-eDRAMs                                      | 95<br>95 |  |  |  |  |

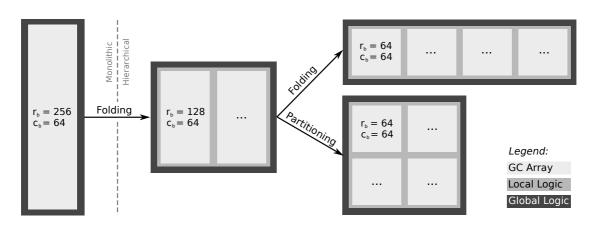

|   |     |          | Architectural Transformations in GC-eDRAMs                            | 93<br>97 |  |  |  |  |

|   |     |          | Features of GC-eDRAMs                                                 | 97<br>97 |  |  |  |  |

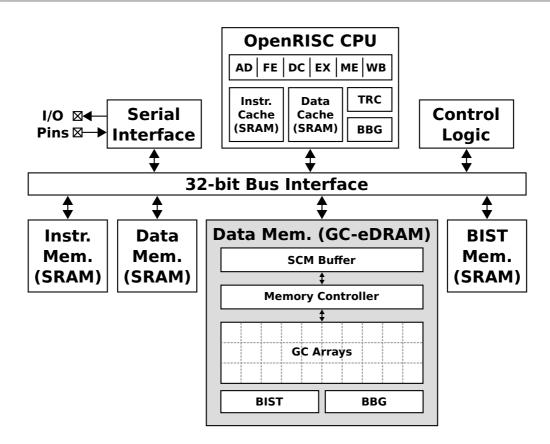

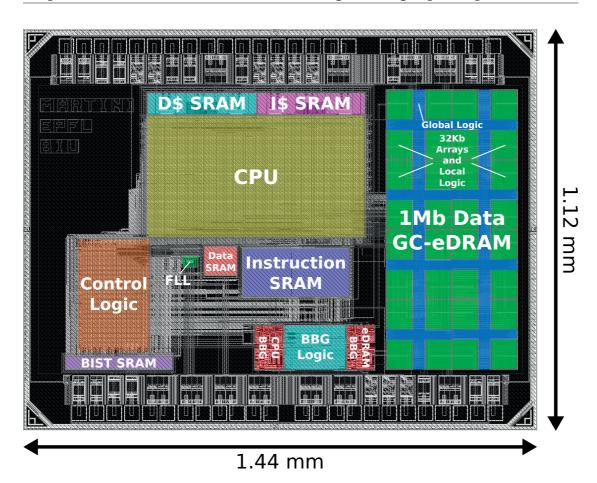

|   |     |          | Computing with GC-eDRAMs: Application to a 32-bit Microprocessor      | 97<br>98 |  |  |  |  |

|   |     | 5.2.5    | computing with GC-CD Mais. Application to a 52-bit Microprocessor .   | JQ       |  |  |  |  |

## Contents

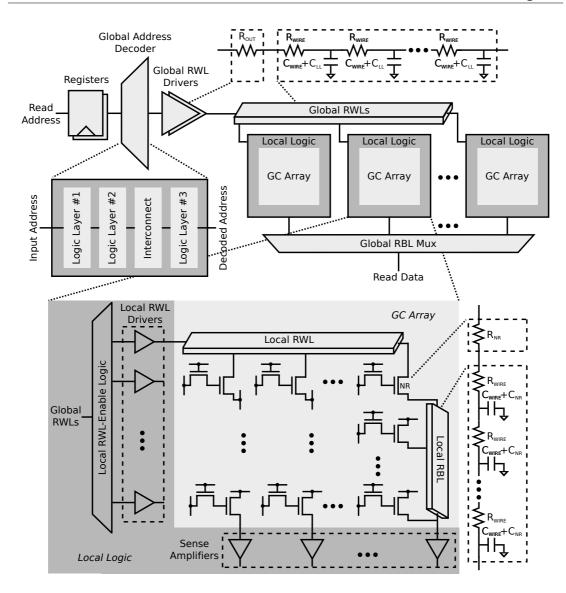

|                           |                                             | 5.2.5.1 System Architecture                                           | 98                       |

|---------------------------|---------------------------------------------|-----------------------------------------------------------------------|--------------------------|

|                           |                                             | 5.2.5.2 GC-eDRAM Subsystem                                            | 99                       |

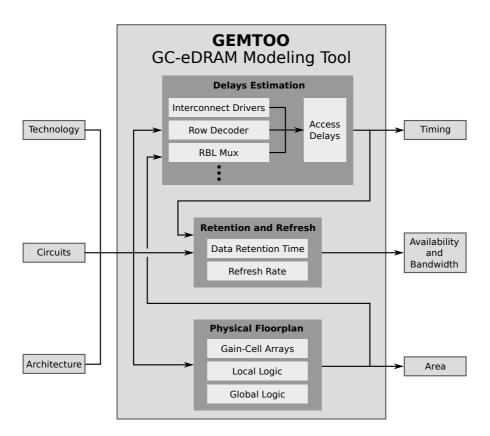

|                           | 5.3                                         | GEMTOO: GC-eDRAM Modeling Tool                                        | 101                      |

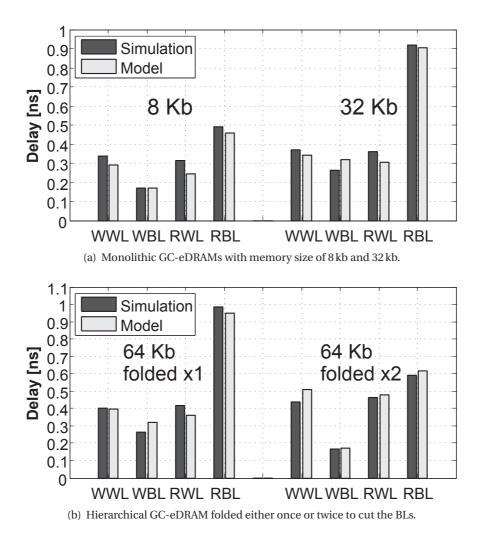

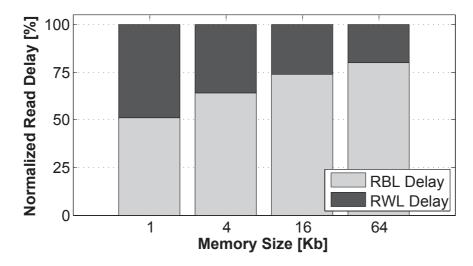

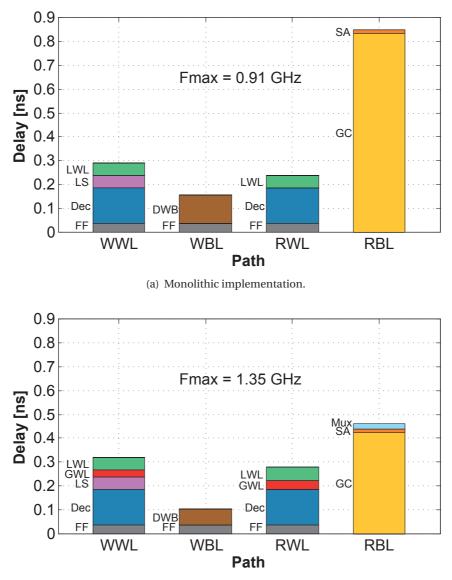

|                           |                                             | 5.3.1 Timing                                                          | 103                      |

|                           |                                             | 5.3.2 Memory Availability and Bandwidth                               | 105                      |

|                           |                                             | 5.3.3 Area and Utilization                                            | 107                      |

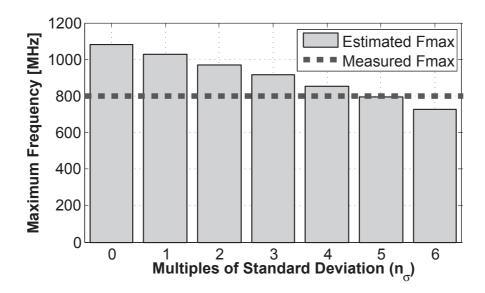

|                           | 5.4                                         | Validation                                                            | 107                      |

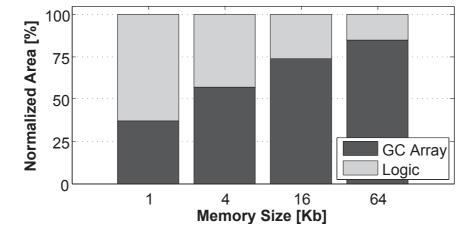

|                           | 5.5                                         | Design-Space Exploration                                              | 109                      |

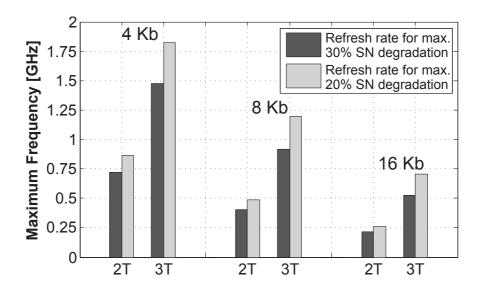

|                           |                                             | 5.5.1 Optimization for Operating Frequency                            | 109                      |

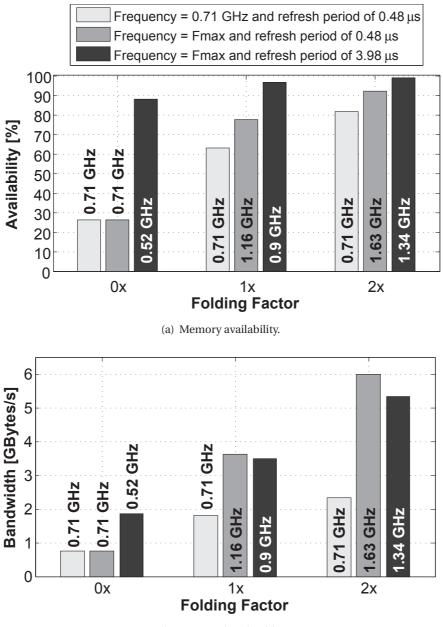

|                           |                                             | 5.5.2 Optimization for Memory Availability and Bandwidth              | 111                      |

|                           |                                             | 5.5.3 Optimization for Memory Density                                 | 116                      |

|                           | 5.6                                         | Conclusion                                                            | 117                      |

|                           |                                             |                                                                       |                          |

| 6                         | Con                                         | clusions and Outlook                                                  | 119                      |

| -                         |                                             | clusions and Outlook<br>er Tradeoffs in Dual-Edge-Triggered Clocking  | 119<br>125               |

| A                         | Pow                                         |                                                                       |                          |

| A<br>Bi                   | Pow                                         | er Tradeoffs in Dual-Edge-Triggered Clocking<br>raphy                 | 125                      |

| A<br>Bi<br>Ac             | Pow<br>bliog<br>crony                       | er Tradeoffs in Dual-Edge-Triggered Clocking<br>raphy                 | 125<br>138               |

| A<br>Bi<br>Ac<br>Li       | Pow<br>bliog<br>crony<br>st of 1            | er Tradeoffs in Dual-Edge-Triggered Clocking<br>raphy<br>ms           | 125<br>138<br>141        |

| A<br>Bi<br>Ac<br>Li<br>Li | Pow<br>bliog<br>crony<br>st of i<br>st of i | er Tradeoffs in Dual-Edge-Triggered Clocking<br>raphy<br>ms<br>ìgures | 125<br>138<br>141<br>145 |

## **1** Introduction

Energy efficiency is one of the main drivers for the rapid proliferation of portable and batterypowered devices. The increasing interest in embedded applications, such as the Internet of Things (IoT), is expected to boost this growth even further as the production of a trillion new IoT nodes is forecasted between now and 2035, according to ARM [1]. Beside the constant need for long-battery life, the design requirements on IoT nodes are driven by an increasing demand for flexibility to support different applications and intelligence to perform complex tasks. Thus, improvements in energy efficiency without any limitation on the performance are crucial for a widespread use of smart IoT nodes.

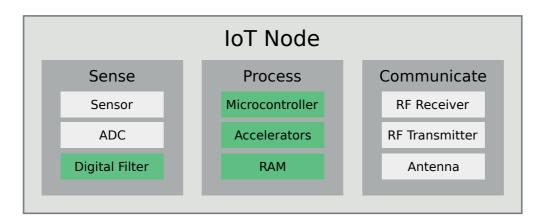

IoT nodes (i.e., the "things") are composed of many modules, as shown in Fig. 1.1. The primary tasks of these end nodes are the collection of data from sensors, the embedded processing of the retrieved data, and the wireless communication with the network. As IoT nodes should ideally operate without battery replacement, the application of effective low-energy techniques is mandatory to ensure the full functionality of the devices for several months or even for years. In this context, the processing modules play a key role as the collected raw data is filtered by either the microcontroller or by dedicated accelerators to limit the amount of data that needs to be stored and wirelessly transmitted. Thus, size reduction of the processed data can relax the requirements on the storage and the implementation of smaller memories enables lower standby power. Furthermore, the wireless transmission of a smaller amount of data allows to use the radio for a shorter period of time, therefore saving a large amount of active power. Hence, the addition of embedded processing modules to extract only the essence from the collected data is key for the development of energy-efficient devices. This approach is generally referred as *edge computing*.

Given the relevance of the computing tasks that are required to be performed by IoT nodes, several processing modules are often implemented within battery-limited devices. As an analog-to-digital converter (ADC) is used to translate the collected data into a digital signal, digital filters are often required to eliminate the signal components that are out of the frequency band of interest or to perform matched filtering. The need for flexible IoT nodes that can support different applications is fulfilled by a programmable and general-purpose module,

Figure 1.1: Modules embedded in a node for the Internet of Things (IoT). The modules highlighted in green are targeted for energy efficiency by the circuits, techniques, and tools proposed in this thesis.

such as a microcontroller. Furthermore, dedicated accelerators are often implemented due to the increasing demand for complex and specialized tasks, such as encryption and feature extraction. Beside the presence of modules for signal processing, the filtered data is collected or stored in a random-access memory (RAM), during processing or simply waiting for being transmitted.

Due to the need for embedded filtering and feature-extraction tasks, edge computing can grow the number and the complexity of the implemented processing modules. Thus, circuits and techniques that aim at reducing the energy consumption of this large variety of integrated modules are crucial for the design of flexible and intelligent IoT nodes that have to meet the tight energy budget. In this context, dynamic voltage and frequency scaling (DVFS) [2] is one of the most effective technique to reduce the dynamic power consumption in digital circuits due to the quadratic dependence of the supply voltage. As conventional six-transistor (6T) static random-access memory (SRAM) is typically the first module to fail when operated at low voltages, alternative SRAM bitcells have been proposed [3,4] to operate static embedded memories even in the near-threshold regime. Costly guard bands are typically added on top of the nominal supply voltage to ensure always-correct operation under any operating condition. However, the system can often be operated reliably without the need of these large and conservative design margins as some of the dynamic variations, such as temperature and aging, have rather long time constants. Thus, many error-detection sequentials (EDSs) have been proposed [5–10] to monitor any change on the critical paths of the design to adaptively trim the guard bands whenever they are not needed, therefore maximizing the power savings. For additional power savings when real-time constraints limit the available safe range for voltage scaling, voltage over-scaling (VOS) [11–14] has been proposed for operating below the critical supply voltage and applying various techniques to handle the timing errors that may occur. Even these conventional techniques already proved to effectively reduce the energy consumption of digital circuits, additional energy savings are still required due to the

increasing demand for long-lasting IoT devices and the physical limitations of the traditional low-energy techniques (e.g., nanometer circuits are highly impacted by process variations when operated at scaled voltages). Given this context, supplementary circuits and techniques should be explored to ideally eliminate any excess of energy consumption.

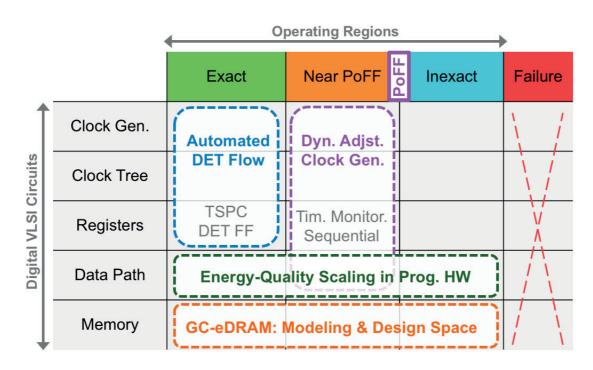

The application of essentially any low-energy technique is often limited by the potential degradation of the quality of service (QoS). For example, an excessive application of voltage scaling can lead to a severe failure of the system due to timing violations. Thus, a thorough understanding of how circuits behave when operated *around* the point of first failure (PoFF), which traditionally identifies where an entire system stops working properly, is key for the effective application of conventional energy-efficient methods as well as for the development of future low-energy techniques. In this regard, four main regions can actually be identified:

- *Exact region:* the vast majority of the energy-efficient techniques reported in the literature target digital systems that are supposed to operate in the safe and conservative exact region. Further improvements in this field of research are constantly needed to reduce the energy consumption of functionally-critical components, such as controllers.

- *Near-PoFF region:* the dynamic adaptation to the operating conditions of a system is key for the runtime elimination of potentially any excess of energy consumption. However, this approach often requires the system to operate *close* to the PoFF, therefore increasing the risk of potential errors (e.g., timing violations). In this context, the implementation of error detection and correction (EDAC) mechanisms is generally required to avoid any penalty on the QoS whenever an error occurs.

- *Inexact region:* abandoning the error-free paradigm (i.e, crossing the PoFF boundary) can eliminate some of the limitations of conventional energy-efficient techniques and allow for additional energy savings whenever a small degradation on the QoS can be tolerated. In this regard, a deep understanding and modeling of the inexact circuit operation as well as of potential reliability issues is key to maximize the energy benefits for a limited and graceful degradation on the QoS.

- *Failure region:* the presence of an overwhelming amount of errors is unacceptable as the QoS might be excessively degraded or the the entire system might stop from working. Thus, systems cannot be operated within this region.

## **1.1 Contributions**

The contributions of this thesis focus on circuits, techniques, and tools for the design of energy-efficient digital very-large-scale integration (VLSI) modules when operated in either the exact, near-PoFF, or inexact region, as summarized in Fig. 1.2. A large variety of circuits are optimized for low-energy consumption, such as the clock-distribution network, sequentials, signal-processing modules for the data path, and embedded memories among others. In

#### **Chapter 1. Introduction**

Figure 1.2: Contributions of this thesis classified by targeted operating region and addressed circuit topology.

particular, the energy savings on the distribution of the clock signal due to the adoption of dual-edge-triggered (DET) clocking are enabled by the proposed automated flow that converts a digital block initially designed for single-edge-triggered (SET) operation into a fully DET component. A static true-single-phase-clock (TSPC) DET flip-flop is also proposed to solve race conditions when using both clock phases. Considering the application of DVFS for energy efficiency, the exploitation of dynamic-timing margins is enabled by the described dynamically-adjustable clock generator (DCG) that is capable of immediate and glitch-free changes on the frequency of the generated clock signal to apply the dynamic clock adjustment (DCA) technique. Furthermore, a timing-monitoring sequential (TMS) is proposed for advanced DVFS techniques where transitions on the input data can be detected on either one of the clock phases to select the best timing-monitoring strategy. Focusing on the data path, properties of programmable hardware are used to enable an energy-quality scaling technique on the algorithmic level. In this regard, the power consumption of the multipliers contained in a programmable finite impulse response (FIR) accelerator is reduced by the runtime adaptation of the filter coefficients, to consume less energy whenever a small degradation on the QoS is tolerated and provide the baseline performance whenever needed. Concerning embedded memories, this thesis proposes the first modeling tool for gain-cell embedded DRAM (GC-eDRAM), which proved to be a compact and low-leakage alternative to conventional SRAM. The described tool enables a practical exploration of the vast and complex design space to scale existing GC-eDRAMs or design future memories through the estimation of their

maximum operating frequency, availability, bandwidth, and memory density. A more detailed description of the contributions of this thesis is provided as follows.

## **Dual-Edge-Triggered Clocking for Low-Power Operation**

The adoption of a DET clocking scheme in synchronous designs is an effective approach for the reduction of the energy consumed in clock distribution when the system is operated inside the safe and conservative exact region. In this thesis, power trade-offs of DET clocking are initially analyzed, providing the means to rapidly identify the characteristics of systems that have the highest potential to benefit from DET clocking for low-power operation. Furthermore, a design flow for the fully automatic implementation of a DET clocking scheme within the standard digital design flow is proposed. The described methodology can be applied to any digital component and it does not require any overhead in the logic-design process. The proposed design flow enables seamless transformation of a digital block, initially designed for SET operation, into a fully DET component. The systematic and full integration of DET clock gating in the digital standard design flow is presented, to the best of the author's knowledge, for the first time. DET operation is applied to three digital components, implemented in a commercial 40 nm CMOS process technology, showing the power-performance benefits of this approach on different real-life designs with post-layout simulations.

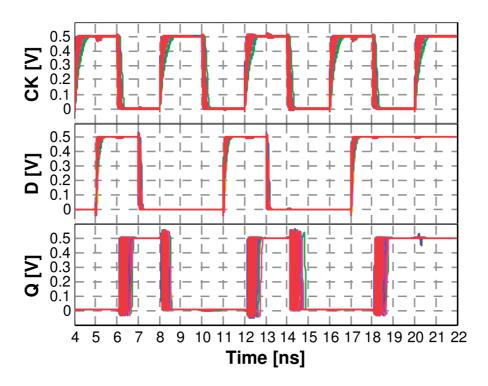

In order to solve race conditions that arise when using both clock phases and that might lead to a loss of data due to overwriting in conventional DET flip-flops, the first static TSPC DET flip-flop is proposed in this thesis. By implementing the cell with TSPC circuits and an internal dual-feedback mechanism, completely static and robust operation is achieved under voltage scaling and process variations. To demonstrate the robustness of the proposed DET flip-flop in nanometer technologies, the register was implemented in a 40 nm CMOS process technology, showing full functionality at a near-threshold supply voltage of 0.5 V and under extensive Monte Carlo statistical simulations for both global and local variations. In addition, the proposed flip-flop provides the lowest CK-to-Q delay and the best power-delay product when compared to other leading DET flip-flops.

## Circuits and Techniques to Monitor and Trim Dynamic Timing Margins

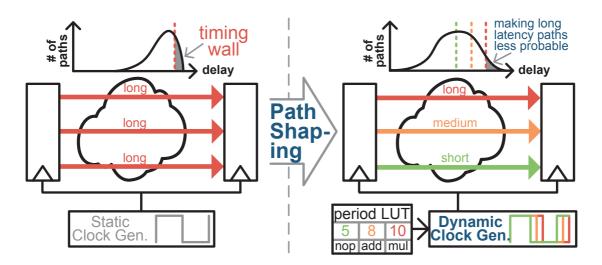

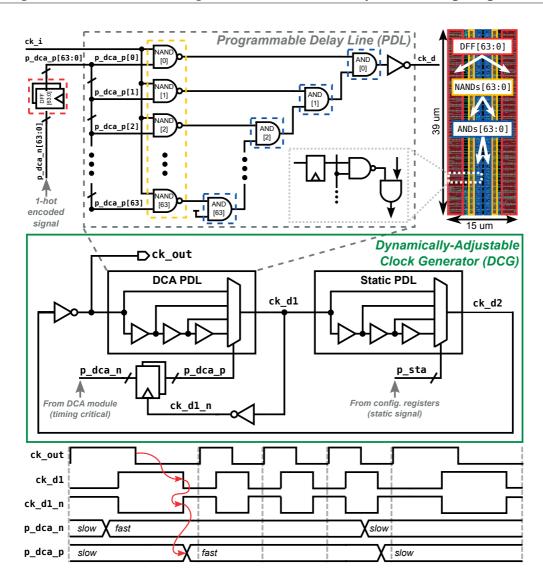

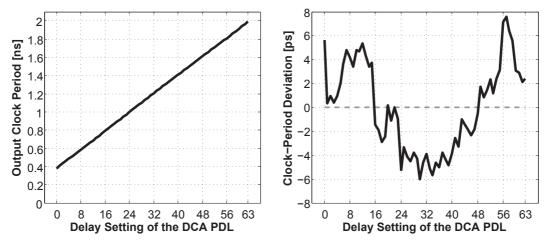

According to DCA techniques, the exploitation of dynamic-timing margins for the operation of the system inside the near-PoFF region is enabled by the DCG proposed in this thesis. The DCG is a digitally-controlled ring oscillator (DCRO) that produces a clock signal whose period can be changed at every clock cycle, as required by techniques relying on DCA. To modify the propagation delay inside the ring, the oscillator includes a programmable delay unit implemented with a cascade of AND gates that have been placed with a controlled floorplan to produce an accurate range of clock periods. The cycle-by-cycle operation is ensured by using a one-hot encoded period setting for the programmable delay unit and by sampling this delay setting with a set of additional registers that have been placed close to the programmable

#### **Chapter 1. Introduction**

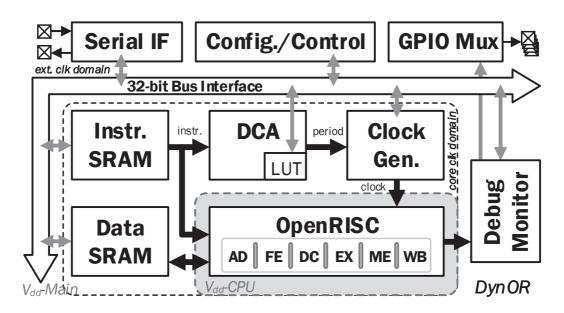

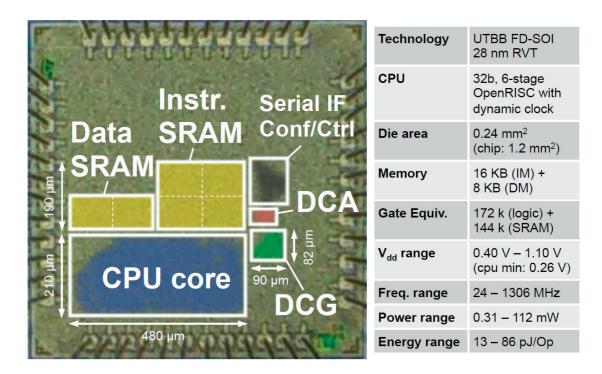

delay unit to minimize both their propagation delays as well as the delay of the clock signal they receive from the ring oscillator. Silicon measurements of a 28 nm FD-SOI test chip are provided to characterize the proposed clock generator and demonstrate the exploitation of dynamic-timing margins in a DCA-enabled embedded processor that uses the described DCG as clock source.

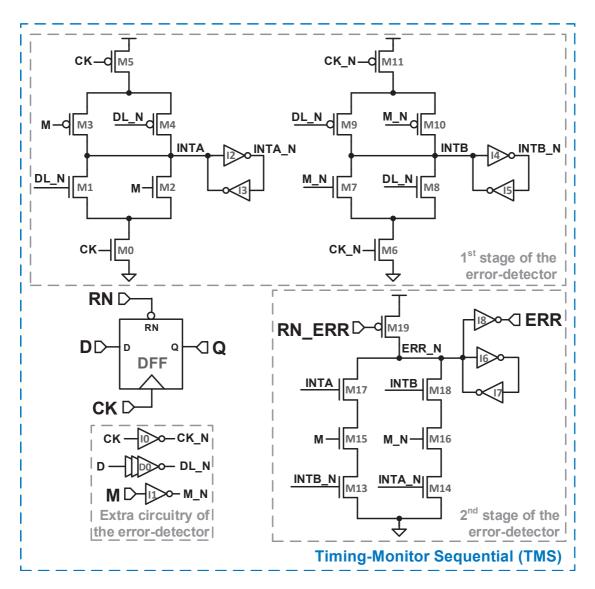

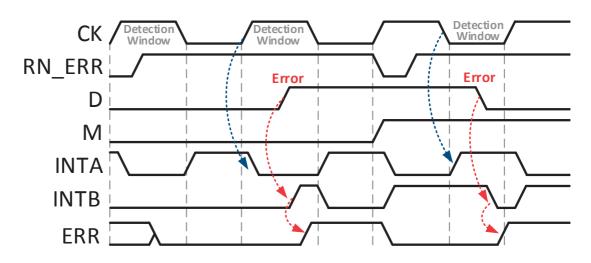

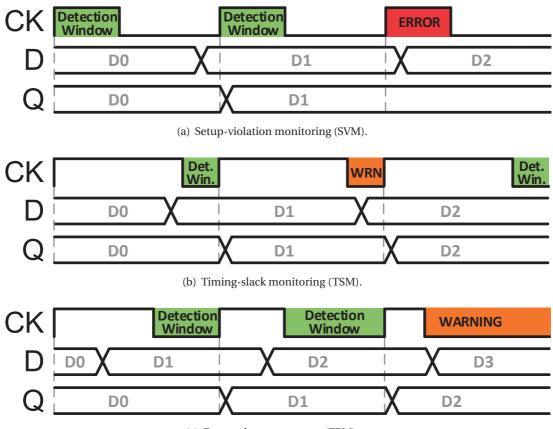

A TMS capable of detecting transitions on the input data during either the high or the low phase of the clock to enable and select the best timing-monitoring strategy is proposed. The use of the TMS together with the control of the clock duty-cycle enables three different timing analyses: the conventional monitoring of any setup violation, the measurement of the available and positive timing slack that can be performed either during a safe calibration phase or even at runtime, and the measurement of fast paths (i.e., paths that are far from being setup-timing critical) to evaluate the potential benefits in the exploitation of dynamic-timing margins provided by the DCA approach. The TMS is implemented on a 28 nm FD-SOI test chip and verified with silicon measurements.

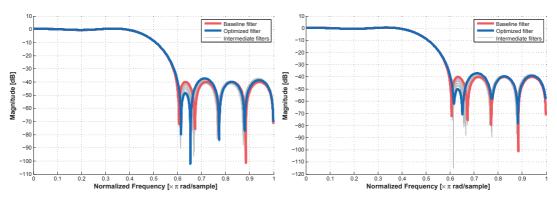

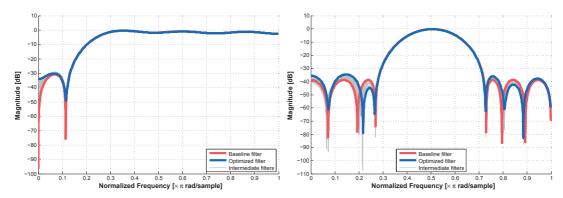

## Exploiting Hardware Properties at the Algorithm Level for Energy-Quality Scaling

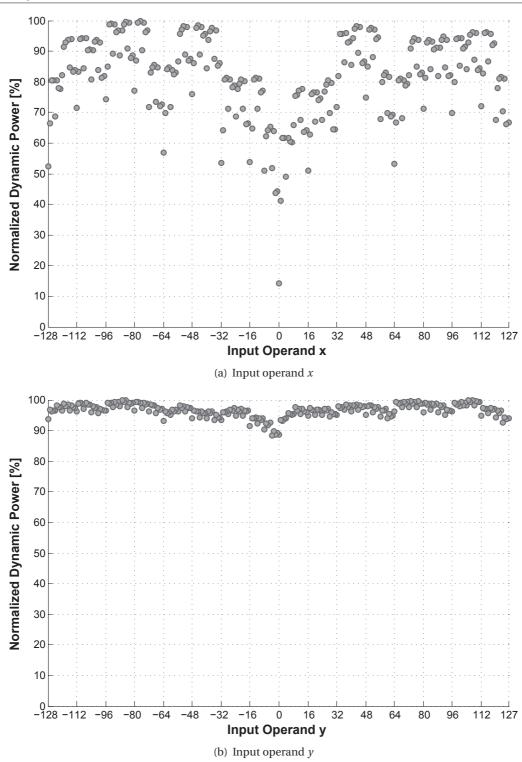

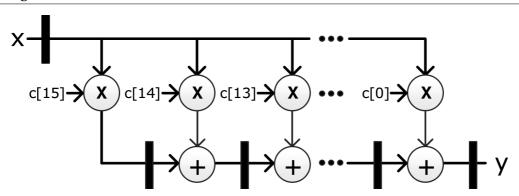

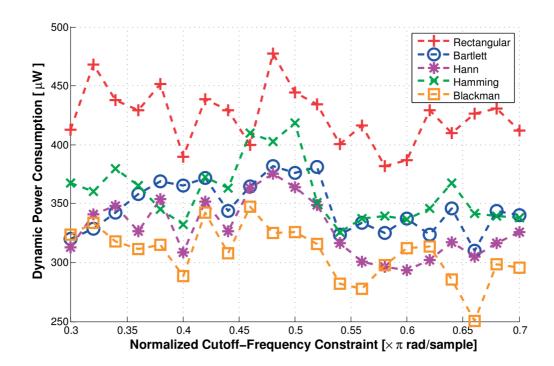

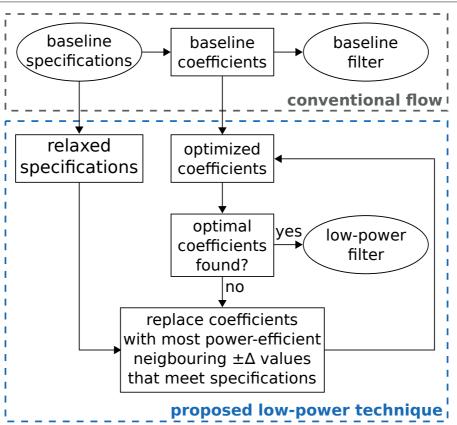

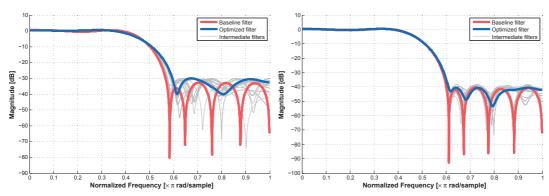

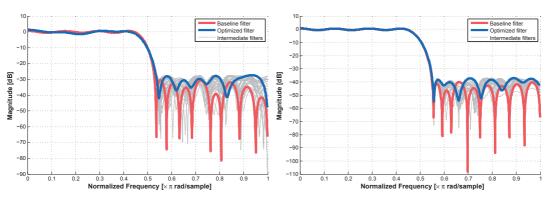

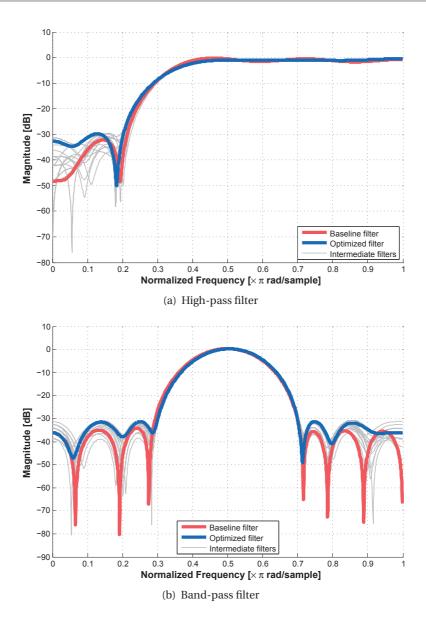

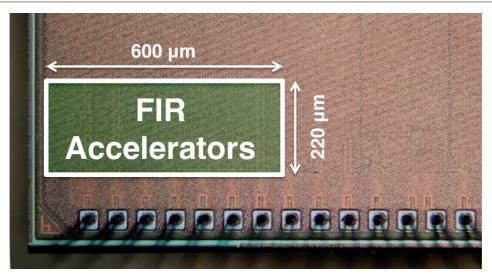

Even though significant energy savings can be achieved through VOS several factors limit the application of such an aggressive energy-efficient technique when operating inside the inexact region: a steep degradation in the QoS is often experienced as soon as the first timing errors appear and the degradation of the QoS can be hardly predicted or controlled. To avoid the use of such risky strategies, in this thesis, energy-quality scaling is enabled by an algorithmiclevel technique that reduces the switching activity of multipliers by carefully choosing the programmable parameters of an FIR accelerator. First, an analysis of the switching activity of multipliers based on the number of non-zero generated partial-product bits is described. The obtained results are confirmed by the dynamic-power characterization of the considered multipliers through accurate post-layout simulations, showing that the achievable power savings might differ depending on which of the two input ports is assigned to the constant coefficient. The power consumption of the multipliers implemented in a programmable FIR filter is reduced by perturbing the baseline coefficients of the filter based on the extensive power characterization of the implemented multiplier topology. The implementation of the power-optimized FIR filter does not require any design overhead except for the additional memory that might be required to store the perturbed coefficients. For the proposed technique, the baseline performance is always ensured when operating with the reference coefficients and the power consumption of the FIR filter can be reduced at runtime, when a less accurate operation of the filter is tolerated. The described technique is applied to several FIR filters, demonstrating the obtainable power reductions. These savings are confirmed through measurements of filters fabricated on a 28 nm FD-SOI test chip.

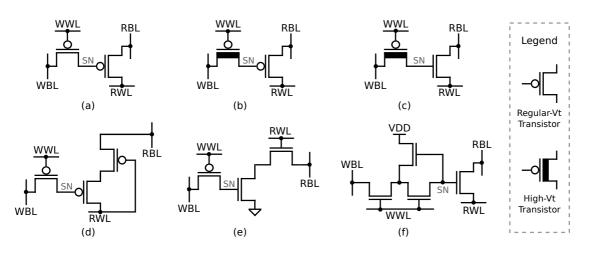

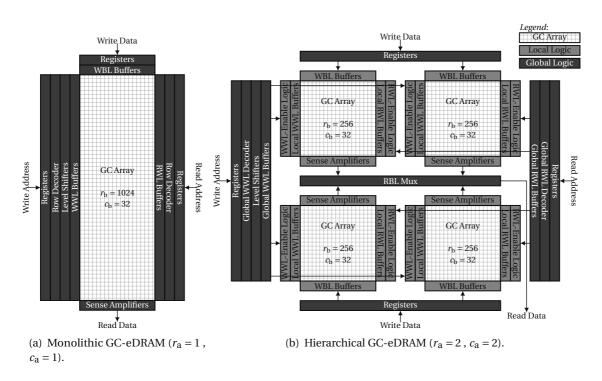

## Gain-Cell Embedded DRAMs: Modeling and Design-Space Exploration

GC-eDRAM is a high-density and low-leakage alternative to conventional SRAM and can be operated either inside the safe exact region or even within the inexact region as it gracefully degrades when the refresh rate is relaxed for energy-quality scaling. In this thesis, the first modeling tool for GC-eDRAMs is proposed for a practical exploration of their complex and vast design space and in support of their design and integration within low-power computing systems. The proposed modeling tool is based on input parameters related to technology, circuits, and memory organization of GC-eDRAMs, therefore allowing for an exploration of a large design space. The physical floorplan of the GC-eDRAM is considered in the estimation of memory metrics, therefore accounting for the impact of the memory organization as well as of the load given by the interconnects. An accurate timing estimation is provided by modeling the effect of the deterioration of the stored data in the gain cell. The tool is implemented in a modular structure to allow for the selection or the introduction of different modeling strategies and the code of the tool is open source as well as publicly available. The timing estimation of the modeling tool is validated against transistor-level simulations of different GC-eDRAMs implementations which include both resistive and capacitive parasitics from post-layout extraction as well as against silicon measurements of a previously fabricated GCeDRAM in 28 nm CMOS process technology. Multiple case studies of design-space exploration are presented based on the proposed modeling tool to find the best design choices that fulfill the most critical memory requirements, such as highest operating frequency, availability, bandwidth, and memory density.

## 1.2 Thesis Outline

In Chapter 2, the motivation and tradeoffs for the application of DET clocking are first described to identify the conditions where DET clocking is effective in reducing the energy consumption. The intricacies in the design and implementation of DET flip-flops and clock gates are then analyzed and a design flow for the fully-automated implementation of DET clocking is proposed. To evaluate the benefits of DET clocking, three IP blocks are implemented in 40 nm CMOS process technology with both SET and DET clocking schemes. Post-layout power simulations are performed to quantize the energy benefits when DET clocking is applied. Within the same chapter, logic failures due to clock overlap in DET flip-flops are described and solved by the proposition of the first TSPC DET flip-flop. The proposed DET flip-flop is implemented in 40 nm CMOS process technology, verified at the near-threshold voltage of 0.5 V and compared to to the state-of-the-art solutions for DET registers.

Chapter 3 describes a DCG capable of immediate and glitch-free changes on the frequency of the generated clock signal. The proposed clock generator is a crucial module for the application of techniques that aim at trimming dynamic timing margins through DCA. Furthermore, a TMS capable of detecting transitions on the input data on either one of the clock phases to enable and select the best timing-monitoring strategy is described in the same chapter. The

## **Chapter 1. Introduction**

proposed TMS can either detect setup violations, warn when a path is *close* to become critical, or even measure fast paths to evaluate potential dynamic timing margins. Both the reported clock generator and the TMS have been fabricated on 28 nm FD-SOI test chips, verified, and characterized with silicon measurements.

In Chapter 4, the impact of VOS on the reliability of a multiplier is analyzed, showing that the application of VOS is a high-risk low-energy technique due to the unpredictable, steep, and severe degradation of the QoS. As an alternative, hardware properties of programmable FIR filters are exploited to reduce the switching activity in multipliers in a proposed energy-scaling technique applied at the algorithmic level. As multipliers account for the largest amount of power consumed in a programmable FIR filter, their dynamic power consumption is extensively characterized for different fixed input operands that coincide with the coefficients of the FIR filter. The power characterization of the multipliers is used to perturbate the coefficients of a baseline filter and obtain a set of power-optimized coefficients for a small degradation on the QoS. The proposed technique is applied and verified with silicon measurements on filter accelerators fabricated on a 28 nm FD-SOI test chip for different topologies of multipliers and filters.

Chapter 5 describes the first modeling tool for GC-eDRAMs. The tool estimates timing, memory availability, bandwidth, and area of GC-eDRAMs based input parameters related to technology, circuits, and memory organization of GC-eDRAMs. The use of the proposed tool is useful for memory design to scale existing the performance of existing memories and predict the metrics of future memories as well as for architectural optimization of systems in which the memories are implemented. The timing estimation of the described modeling tool is validated against both simulated and measured GC-eDRAMs in 28 nm CMOS process technology. The proposed modeling tool is also used to show the intricacies in design optimization of GC-eDRAMs and, based on the results, optimal design practices are derived.

Conclusions and outlook are provided in Chapter 6.

## **1.3 Selected Publications**

This thesis is largely based on the following publications.

#### **Dual-Edge-Triggered Clocking for Low-Power Operation**

<u>A. Bonetti</u>, A. Teman, and A. Burg, "An Overlap-Contention Free True-Single-Phase Clock Dual-Edge- Triggered Flip-Flop", *IEEE International Symposium on Circuits & Systems (ISCAS)*, May 2015.

<u>A. Bonetti</u>, N. Preyss, A. Teman, and A. Burg, "Automated Integration of Dual-Edge Clocking for Low-Power Operation in Nanometer Nodes", *ACM Transactions on Design Automation of Electronic Systems (TODAES)*, May 2017.

## Circuits and Techniques to Monitor and Trim Dynamic Timing Margins

J. Constantin, <u>A. Bonetti</u>, A. Teman, Christoph Müller, Lorenz Schmid, and A. Burg, "DynOR: A 32-bit Microprocessor in 28nm FD-SOI with Cycle-By-Cycle Dynamic Clock Adjustment", *European Solid-State Circuits Conference (ESSCIRC)*, September 2016.

<u>A. Bonetti</u>, J. Constantin, A. Teman, and A. Burg, "A Timing-Monitoring Sequential for Forward and Backward Error-Detection in 28 nm FD-SOI", *IEEE International Symposium on Circuits & Systems (ISCAS)*, May 2018.

## Exploiting Hardware Properties at the Algorithm Level for Energy-Quality Scaling

<u>A. Bonetti</u>, A. Teman, P. Flatresse, and A. Burg, "Multipliers-Driven Perturbation of Coefficients for Low-Power Operation in Reconfigurable FIR Filters". *IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS-I)*, September 2017.

## Gain-Cell Embedded DRAMs: Modeling and Design-Space Exploration

<u>A. Bonetti</u>, R. Golman, R. Giterman, A. Teman, and A. Burg, "Gain-Cell Embedded DRAMs: Modeling and Design Space", *Under revision*, 2018.

## 1.4 Third-Party Contributions

All third-party contributions to the work presented in this thesis are listed in this section.

I worked in close collaboration with Nicholas Preyss during the development of the automated flow for the insertion of the DET clocking scheme. Nicholas supported me in various stages of the project, providing the IP block and the testbench for the case-study A, the development of the DET automatic place-and-route flow, and the timing evaluation of all the considered IP blocks. Adam Teman oversaw the whole project providing many valuable solutions for the place-and-route flow and power simulations. Christian Senning and Reza Ghanaatian provided the IP blocks and the testbenches for the case-studies B and C, respectively.

The proposed DCG has been integrated in DynOR, a DCA-enabled embedded processor, that has been designed, fabricated, and tested as a result of a collaboration within many people: Jeremy Constantin, main frontend designer and leader of the DynOR project, Adam Teman, who supervised the backend tasks, Christoph Müller, who contributed to the backend flow, and Lorenz Schmid, who worked on chip testing.

The programmable FIR filters used for the evaluation of the proposed energy-quality scaling technique and the described timing monitoring sequentials have been integrated in PolarBear, a 28 nm FD-SOI test chip that was the result of a team effort: Lorenz Schmid integrated the accelerators, the timing monitoring sequentials, and the testing circuitry in the chip,

while Christoph Müller designed the top-level control logic, lead the backend tasks and gave invaluable contributions during the power measurements of the accelerators.

Different people contributed to the design and fabrication of the described processor implementing a GC-eDRAM as data memory. Jeremy Constantin supported me in the very first design stages to integrate the implemented OpenRISC core in the system. Robert Giterman designed the custom arrays of the GC-eDRAM and provided support for the backend tasks. Christoph Müller designed the implemented body-bias voltage generators as well as their control logic. Ivan Miro-Panades provided the frequency-locked loop (FLL) used for internal clock generation.

# 2 Dual-Edge-Triggered Clocking for Low-Power Operation

Power reduction in integrated circuits (ICs) continues to be one of the primary objectives in the field of digital system design, especially in light of the increasing throughput required by modern systems [15]. The majority of these systems are fully or primarily synchronous, requiring the distribution of one or more clock signals across the entire chip. The necessary clock networks typically drive a large capacitive load and they are always toggling when clock gating is not active. Thus, a significant amount of power is consumed for clock distribution and can account for 30%–60% of the total chip power [16–20].

A well-known technique for reducing the dynamic power dissipation of a synchronous IC is dual-edge-triggered (DET) clocking. As opposed to the conventional single-edge-triggered (SET) solution, which samples the data only on the rising-edge of the clock, DET operation uses both the rising and the falling edges for data sampling, thereby requiring only half of the clock frequency of the SET approach for the same throughput. As shown analytically by Nedovic *et al.* [17, 18], the resulting dynamic power reduction in clock distribution can exceed 50%, and DET clocking is always more power-efficient if the clock load capacitance of the DET storage elements is less than twice as large as that of their SET counterparts. In addition, since DET flip-flops (DET-FFs) have been shown to be more energy-efficient than their SET counterparts for high-speed applications [21–23] and have comparable or even *lower* propagation delay [17, 21–23], power reduction can often be achieved with a similar or even a slightly higher throughput than with conventional SET clocking.

In addition to the power advantages of DET clocking, the reduced clock frequency also relaxes many of the issues that are introduced by high-speed architectures. The effect of the electromagnetic interference (EMI) typically produced by high-frequency sources is attenuated, thereby reducing noise coupling. Since the transient activity on the current drawn from the supply is reduced, the noise on the power supply voltage caused by the presence of an equivalent impedance is also reduced. DET clocking also eases many of the challenges and constraints on producing a clock signal that is twice the speed of the data, as the maximum toggle frequency of the clock is identical to the maximum toggle frequency of the data. Finally, by enabling DET blocks within a primarily SET system, a high performance block can be implemented with DET standard cells and be operated at twice the speed of the system without the need for generating and distributing an additional faster clock.

The implementation of storage cells that are triggered on both clock edges is a well-researched topic [19, 24-28]. Several works have investigated and compared the performance of DET-FFs with that of conventional SET flip-flops (SET-FFs) [18, 21–23, 29, 30], showing that DET-FFs outperform SET storage cells in both low-power and high-speed applications [21-23]. The main drawbacks of DET-FF implementations are that they occupy a larger silicon area and consume higher leakage currents than SET flip-flops, especially in deep nanometer nodes, making DET operation less appropriate for systems or components characterized by long sleep periods or with frequent clock-gating [18]. For this reason, these tradeoffs have to be carefully analyzed at the system level in order to choose the most power-efficient clocking scheme. Architectures in which the clock network and the registers are active most of the time and consume a large portion of the total power are the most promising candidates for DET clocking. Power-efficient design of the implemented DET-FFs will further contribute to the power savings in register-heavy systems. For example, many signal processing applications, such as cryptography, digital filtering, neural networks, and communication systems are often realized with register-based architectures featuring deep pipeline structures, rendering them perfect candidates for DET implementation, as long as the area penalty can be tolerated.

In this chapter, circuits and an automated design flow are proposed to enable the implementation of DET clocking:

- In Section 2.1, the most promising conditions for achieving low-power operation with DET clocking are identified and a fully-automated design flow for applying DET to a conventional SET design is presented.

- Section 2.2 describes the clock-overlap failure risk in DET registers and proposes a DET flip-flop with a true-single-phase clock that completely avoids clock overlap hazards by eliminating the need for an inverted clock edge for functionality.

## 2.1 Automated Integration of Dual-Edge Triggered Clocking

Even if many applications are promising candidates for DET clocking, the design of DET systems and their implementation within the digital standard design flow are considered to be cumbersome and are almost entirely neglected in the literature. In fact, only very few digital architectures that incorporate DET clocking have been reported in the literature (e.g., [31]). The emphasis of the majority of all previous publications discussing DET clocking has been on the design and implementation of stand-alone DET-FFs, neglecting the intricacies of the electronic design automation (EDA) for DET-based system integration. In addition, most standard cell libraries are equipped only with SET storage elements and clock-gating circuits and the definition of DET constraints for static timing analysis (STA) and clock-tree synthesis (CTS), especially with clock-gating, is non-trivial. Therefore, DET is often relegated to a minor role in synchronous design, used only for specific applications and in niche products.

In this section, the main practical concerns are reconsidered and addressed to make DET clocking a viable and easy-to-use technique for low-power operation of synchronous digital circuits. To that end, the most promising conditions for large power savings through DET clocking are identified and subsequently a seamless and fully-automated design flow for the integration of DET clocking into a digital IC is presented. The proposed design flow transforms a synchronous block, initially designed for SET clocking, into a fully DET implementation, thereby enabling a rapid and accurate comparison between the two implementations for each block. In this way, the direct tradeoff between the power reduction of DET clocking and its unavoidable area and leakage overheads can be considered at the block level. Thereafter, the system designer can select the best clocking scheme for each component to provide an energy-efficient full system solution, while maintaining the initial SET throughput. This provides the basis for a design methodology which integrates DET and SET clocked components within a single system.

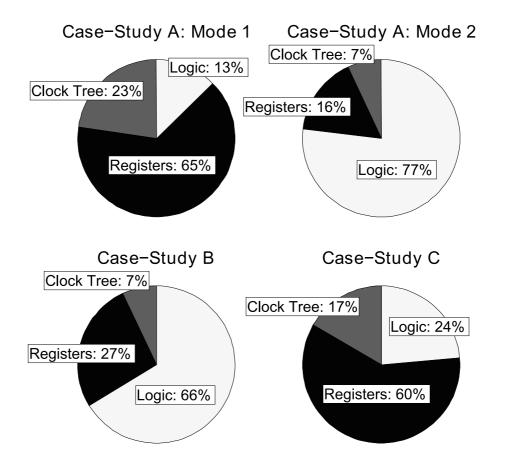

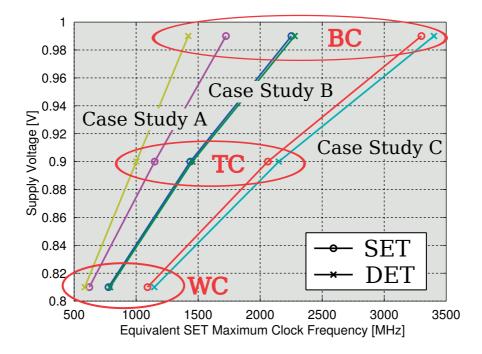

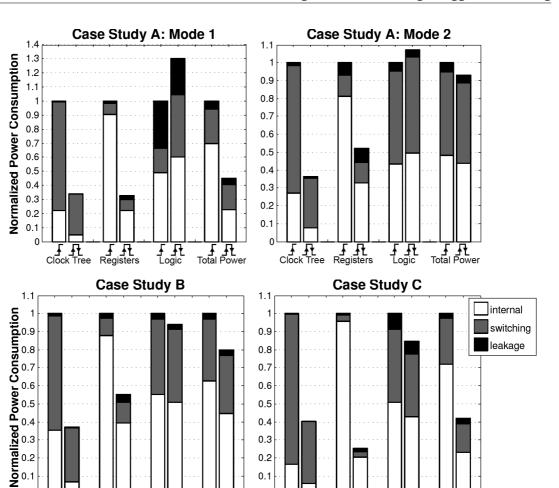

The proposed approach is implemented exclusively with commercial EDA tools and it is applied to three representative digital blocks in a standard 40 nm CMOS process technology. The DET approach was shown to halve the power consumption in the clock tree for all test cases and to significantly reduce the dynamic power of the registers, leading to a 58% total power reduction for one of the benchmark circuits whose power is dominated by registers and clock buffers. All DET implementations are shown to retain similar throughput as compared to their SET counterparts across standard operating corners, showing that the two clocking schemes can be freely interchanged within a given specification.

**Contributions** The primary contributions of this section can be summarized as follows:

• Power tradeoffs in DET clocking are analyzed, providing the means to rapidly identify the characteristics of systems that have the highest potential to benefit from DET clocking for low-power operation.

## Chapter 2. Dual-Edge-Triggered Clocking for Low-Power Operation

- A design flow for the fully-automatic implementation of a DET clocking scheme within the standard digital design flow is proposed. The presented methodology can be applied to any digital component and it does not require any overhead in the logic-design process.

- The proposed design flow enables a seamless transformation of a digital block, initially designed for SET operation, into a fully DET component. This can be used either to benefit from the power savings of the DET approach or for a straightforward and accurate comparison between the two clocking approaches applied to a given block.

- To the best of the author's knowledge, this is also the first work presenting a systematic and full integration of DET clock gating in the digital standard design flow.

- DET operation is applied to three digital accelerators, implemented in a commercial 40 nm CMOS process technology, showing the power benefits of this approach on different real-life designs with post-layout simulations.

The rest of this section is as follows: the motivation for DET clocking and the tradeoffs between applying SET and DET clocking are discussed in Section 2.1.1; a brief overview of the DET-FF and the DET clock gate (DET-CG) used in the proposed benchmark implementations is given in Section 2.1.2, before introducing the proposed DET design flow in Section 2.1.3; Section 2.1.4 presents the application of the proposed flow on three example designs and the resulting power savings; Section 2.1.5 concludes this section.

## 2.1.1 Motivation and Tradeoffs in DET Clocking

A standard clock-distribution network is composed of digital gates, synchronous registers, and wires that connect them. The dynamic power consumption  $P^{dyn}$  of each of the cells in such a network can be described as:

$$P^{\rm dyn} = f \cdot K \cdot E^{\rm dyn},\tag{2.1}$$

where f is the toggling (clock) frequency, K is the activity factor of the gate (defined as the number of transitions per clock cycle) and  $E^{dyn}$  is the energy consumed per transition by the gate. This leads to the straightforward concept of power savings through DET clocking: a reduction of the clock frequency by 50% by using both clock edges for state transitions into sequential elements can cut dynamic power consumption due to activity on the clock net in half. Unfortunately, this simple conclusion neglects several issues which limit the efficiency of the DET approach. First of all, while the power reduction of components on the clock network can be substantial, this may only be a small fraction of the total power for some systems, especially those with a small ratio of registers to combinatorial logic or systems

with high clock-gating efficiency<sup>1</sup>. Second, the implementation of DET clocking requires the replacement of SET registers with their DET counterparts, and while these gates can be designed to be more energy-efficient, they typically present higher area and leakage power, which may not be acceptable, especially in nanoscaled processes. These factors must be taken into account when deciding upon the clocking scheme of a system. This section evaluates both the power benefits and tradeoffs of applying DET clocking to a given design to provide the system architect with a basis for making this decision.

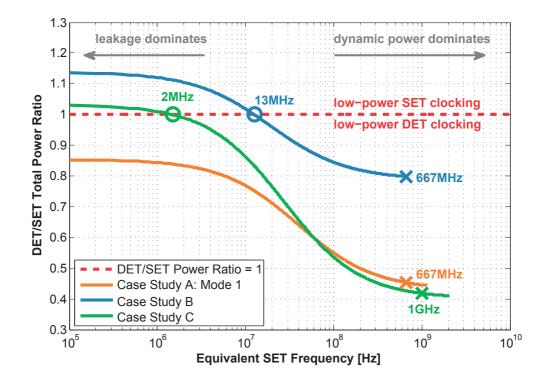

An analytical evaluation of the power tradeoffs in DET clocking is described in Appendix A. Considering the result of (A.7), it is possible to state that DET clocking is more power-efficient than the conventional clocking scheme when the dynamic power savings (mainly obtained on the clock tree and registers) are larger than the increase in leakage power. In particular, (A.7) depends on different parameters that are analyzed as follows:

- DET clocking can reduce the dynamic power of both registers and clock tree. Therefore DET clocking will be most efficient, when applied to an SET design with a large portion of dynamic energy consumed in the clock tree ( $E_{tre}^{dyn}$ ) and registers ( $E_{reg}^{int}$  and  $E_{reg}^{sw}$ ), as well as relatively low leakage power.

- The dynamic power savings depend on the activity factors *K*<sub>tre</sub> and *K*<sub>reg</sub>, meaning that designs that spend a considerable percentage of time in clock-gated sleep states are generally not recommended for DET clocking.

- Both  $\alpha_{reg}$  and  $\beta_{reg}$  depend on the power comparison between the implemented SET-FFs and the DET-FFs and their values can be obtained and improved with analog simulations and various circuit-level design techniques [22, 23]. For a favourable energy-efficient DET clocking, these scaling factors need to be kept as small as possible in order to minimize the leakage power overhead and to save dynamic power in the registers.

- The register scaling factors,  $\alpha_{reg}$  and  $\beta_{reg}$ , solely depend on the design of the implemented DET-FFs as compared to the SET-FFs. Reduction of these factors is fundamental for overall power savings, especially when considering register-dominated designs. In general,  $\alpha_{reg}$  is often expected to be larger than one due to the higher leakage current that characterizes the DET-FFs, while  $\beta_{reg}$  (i.e., the internal energy ratio of DET vs. SET registers for a single transition) is required to be smaller than one to efficiently save power at high operating frequencies. The requirement on  $\beta_{reg}$  is easily met by many DET-FF topologies, primarily due to the internal power consumption of SET-FFs on the non-sampling edge of the clock – a phenomenon that is non-existent in DET-FFs. For

$$G_{\text{eff}} = \frac{R_{\text{cg}} \cdot \overline{C_{\text{cg}}}}{R_{\text{tot}} \cdot C_{\text{tot}}}.$$

<sup>&</sup>lt;sup>1</sup>In this context, clock-gating efficiency ( $G_{\text{eff}}$ ) is defined as the number of registers that can be clock-gated ( $R_{\text{cg}}$ ) multiplied by the average number of clock cycles where a register is clock-gated ( $\overline{C_{\text{cg}}}$ ), divided by the product of the total number of registers ( $R_{\text{tot}}$ ) times the total number of clock cycles ( $C_{\text{tot}}$ ):

the registers considered in this work, these scaling factors have been estimated considering the average performance of the implemented SET and DET flip-flops, resulting in  $\alpha_{reg}$  and  $\beta_{reg}$  being equal to 1.50 and 0.40, respectively.

- The clock tree that is built in the SET design is likely to be very similar to the DET clock tree, since the buffers implemented in the clock tree generally have balanced inputto-output delays to avoid a degradation of the duty cycle in the clock propagation and under the assumption that the load on the clock pin is kept the same for both SET and DET registers. The latter condition can be easily satisfied by having the clock pin of the SET-FFs and of their DET counterparts connected to the same digital gate (i.e., a clock buffer) and ensuring the correct clock distribution inside the standard cell during the transistor-level design phase of the DET-FF. In addition to this, dynamic power savings will still be achieved, even in the case of a more complex DET clock tree, due to the operation of the DET implementation at half of the SET clock frequency. For this reason, both  $\Omega_{tre}$  and  $\Phi_{tre}$  can be assumed to be equal to one, in a first-order approximation.

- The conversion of an SET design to a DET implementation, as described in Section 2.1.3, is achieved by replacing SET clock gates and flip-flops with their DET counterparts without any inherent modification of the combinatorial logic. Thus, the power consumption of the logic gates is ideally unchanged and the scaling factors  $\Omega_{log}$  and  $\Phi_{log}$  can be approximated to one. However, the implementation of faster DET-FFs might result in the need for additional hold buffers, leading to scaling factors that are slightly larger than one. Nevertheless, the overall power consumption can still be efficiently reduced by DET clocking when this power overhead is limited and assuming that the additional slack from faster DET-FFs can be exploited in other parts of the logic to relax timing constraints.

- The choice on the most power-efficient clocking scheme depends also on the operating frequency. DET clocking is more energy-efficient than SET clocking at higher frequencies, where dynamic power dominates, but is less suited to slow designs, where a large portion of the total power consumption is due to leakage currents.

- In general, the area overhead of applying DET should be taken into account, in addition to the potential power savings. However, for many systems a slight area penalty can be tolerated, especially for pad-limited ICs.

This analysis shows that while not all digital blocks are good candidates for DET clocking, systems and components with certain characteristics will significantly benefit from this approach. However, as previously mentioned, two primary factors still prevent widespread application of DET clocking in digital systems. The first is the lack of DET-FFs and DET clock gates in standard libraries, and the second is the lack of a methodology and guidelines for the integration of DET clocking in the digital standard design flow. Therefore, the next section presents the registers and clock-gating circuits used in this work, followed by a detailed methodology

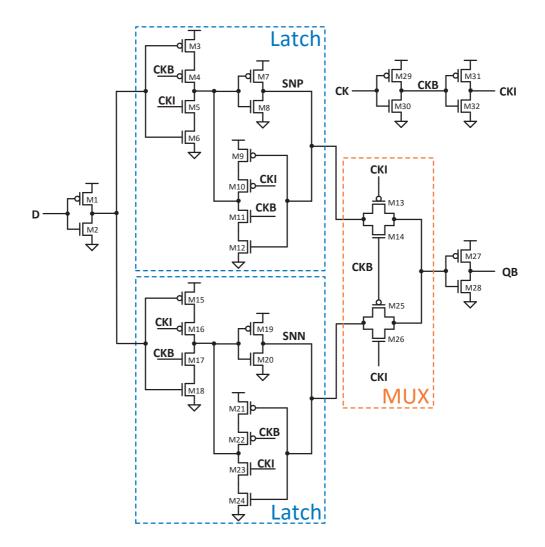

Figure 2.1: Schematic of the DET-TGLM flip-flop used in this work.

for the physical implementation and verification of DET clocking within the digital standard design flow.

## 2.1.2 Design and Implementation of DET Library Cells

The design of DET-FFs is crucial for achieving both low power consumption and high performance in synchronous digital systems. For this reason, many different implementations of DET-FFs have been proposed in the literature, including the transmission-gate latch-MUX (DET-TGLM) [24], the C<sup>2</sup>MOS latch-MUX (DET-C2LM) [25], the pulse-triggered DET-FF [26], the conditional discharge flip-flop (DET-CDFF) [19], symmetric pulse-generator flip-flop (DET-SPGFF) [27] and the C-element flip-flops (DET-CFFs) [32]. Of these, the DET-TGLM is the most popular, due to its simple implementation and its relatively short CK-to-Q delay. In addition, this topology has proven to be one of the most energy-efficient DET-FFs for high-speed

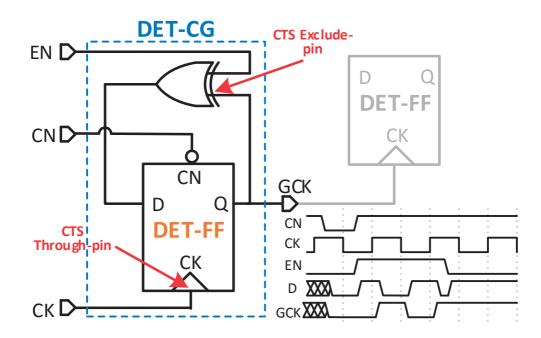

Figure 2.2: Schematic of the DET clock gate (DET-CG) [33] used in this work, characteristic waveforms and clock-tree synthesis (CTS) directives.

operation [21–23]. Thus, in this work, the DET-TGLM topology is chosen for demonstrating the application of DET clocking to full digital blocks. However, all of the proposed topologies are equivalently applicable, provided that they meet the  $\beta_{reg} < 1$  requirement of (A.7).

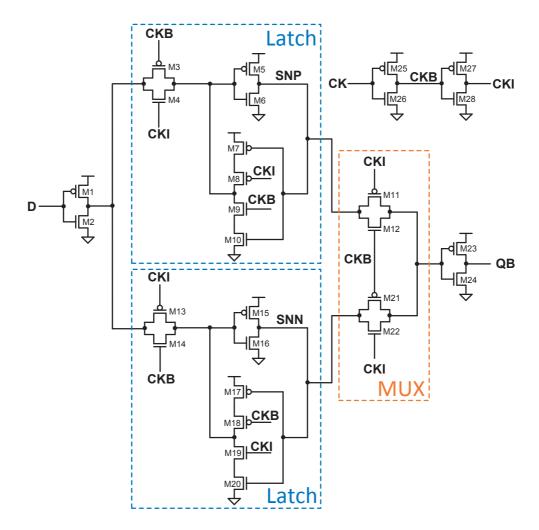

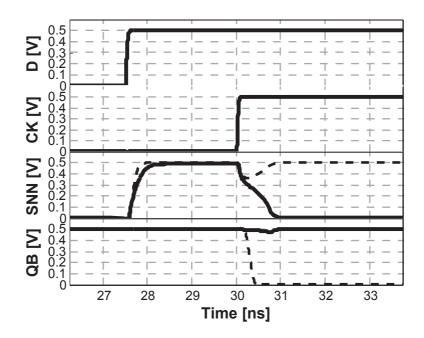

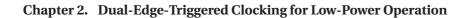

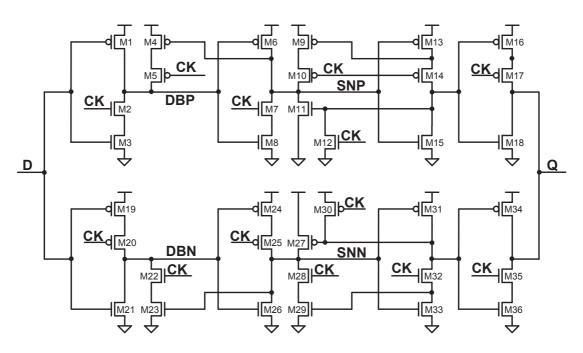

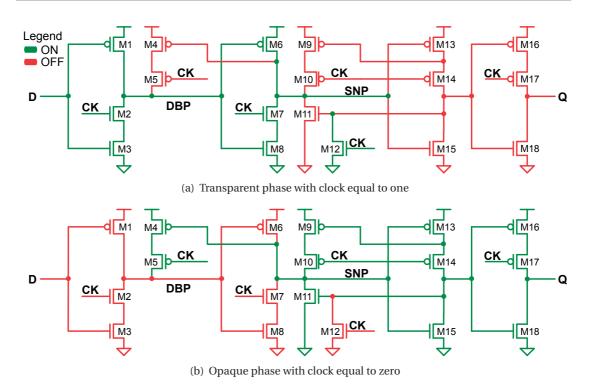

The DET-TGLM, shown in Fig. 2.1, is composed of two separate latches (M3-M12 and M15-M24), whose storage nodes are connected to an output multiplexer (MUX). During each phase of the clock, only one latch is transparent, while the other one is opaque. This allows the transparent latch to follow the data at the input, while the other latch drives the output (QB) through the MUX. The MUX is based on transmission gates (TGs) (M13–M14 and M25– M26), which have a low propagation delay, to minimize the overall CK-to-Q delay. The total device count of this DET circuit is 32 transistors, while the clock load, defined as the number of transistors controlled by any clock signal, is 16 transistors. As the clock load of the corresponding SET-FF is 12 transistors, the ratio bewtween the DET and the SET clock load is 1.34 that is significantly lower than the clock-load-ratio limit of 2 for energy-efficient DET design, as defined in [17, 18]. The implemented DET-TGLMs also present the same clock-pin load as the replaced SET-FFs to ensure a similar load condition for the clock network. This is done by connecting the clock pin to the input of the inverter that is identical in both types of registers (M29–30 for DET-TGLMs in Fig. 2.1). In addition, while input glitching will result in some internal power consumption, the same happens for a standard SET-FF during one clock phase and, as previously mentioned, since the power consumed in DET-FFs is associated to only one clock edge per cycle, as opposed to SET-FFs, the dynamic power ratio ( $\beta_{reg}$ ) is much lower than one, as required to meet the inequality of (A.7).

#### 2.1. Automated Integration of Dual-Edge Triggered Clocking

Figure 2.3: Flow chart for the proposed DET implementation within the digital standard design flow.

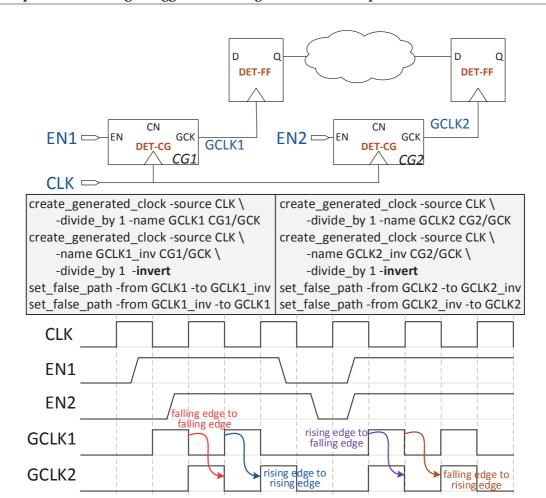

The most commonly applied technique for reducing the power consumption of the clock network is clock gating. However, in the majority of the discussions about the potential efficiency of DET operation, clock gating is not addressed. Contrary to the many DET-FF implementations that have been proposed, to the best of the author's knowledge, only two implementations of a DET-CG have been published [33, 34]. In this work, the more straightforward one of these two circuits is chosen, comprising a DET-FF and a feedback XOR gate, as shown in Fig. 2.2. By choosing this circuit, the DET-CG can be defined as a structural Verilog model, rather than a fully custom standard cell, significantly reducing the design effort for integrating clock-gating in a DET design.

To demonstrate the operation of the DET-CG, the inset of Fig. 2.2 provides a set of typical waveforms. The XOR conditionally inverts the output (Q) of the internal DET-FF according to the enable (EN) signal, and feeds the result into the input (D) of the DET-FF. The clock input of the gate (CK) is directly connected to the clock pin of the DET-FF and the gated clock output (GCK) is connected to its Q pin. When the EN input is high, the XOR gate always feeds back the inverted output to the input of the DET-FF, causing the output clock to toggle on both edges of the clock. As soon as EN is set to '0', the DET-FF will continue sampling the same input value, forcing GCK to remain stable.

It is worth noting that unlike an SET clock gate (SET-CG), the output of a DET-CG depends on its initial state, providing either the same or the inverted phase relative to the root clock, depending on the activation cycle. The implications of this characteristic on the digital standard design flow are outlined in detail in Section 2.1.3. In addition, if the output of the DET-FF of the clock-gating cell is not forced to an initial state, the undefined value on the output of the DET-FF will propagate to its input through the XOR gate, creating an undefined logic level. Even though, in reality, this issue is mostly an artifact of the model appearing during gate-level simulation, a resettable DET-FF was used to implement the DET-CG, adding a reset input (CN) to the gate to set the output to a well-defined level during power-on.

## 2.1.3 Proposed DET Digital Design Flow

While the digital design flow for SET operation is extensively discussed in the literature and in textbooks [35], the implications of implementing a DET clocking scheme are rarely considered. This is probably due to the lack of DET gates in commercial standard-cell libraries along with the non-trivial requirements for DET timing analysis, especially when clock gating is used. This section introduces an automated flow for integrating DET operation into a block that is initially designed for standard SET operation and for then continuing through the digital standard design flow to provide a final, validated design database. This methodology enables an easy investigation of the DET power-efficiency for a given block and a seamless integration of DET blocks with SET blocks in a digital system. The only prerequisite for this flow is the existence of DET-FFs and DET-CGs, such as the ones previously described.

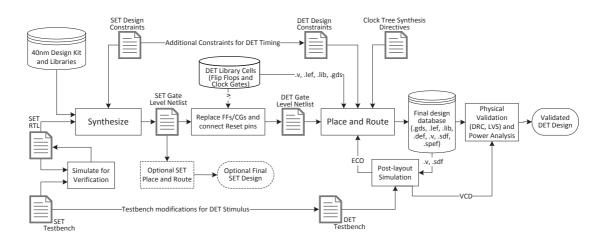

The proposed DET flow, illustrated in Fig. 2.3, is composed of three phases: first, a registertransfer level (RTL) description is provided for SET operation and standard synthesis is performed with SET timing constraints. Then, the design is translated into an equivalent DET netlist, primarily by replacing the SET registers and clock-gates with their DET counterparts. Finally, the adapted netlist is loaded back into the EDA tools and the digital standard design flow is continued with DET timing constraints to provide a final design database. The following subsections describe the intricacies of each of these phases, pointing out the directives and constraints that are required by the EDA tools for accurate DET timing analysis.

#### 2.1.3.1 Initial SET Synthesis

The synthesis stage of the proposed flow follows the common SET digital standard design flow. An SET RTL description of the design is verified with a logic simulator and then mapped to a standard-cell library using a synthesis tool and a set of SET design constraints, including the automatic insertion of clock gates. At this stage, care must be taken to restrict the mapping of registers to SET-FFs for which equivalent DET gates are available in terms of interface and functionality (set, reset, scan, drive strength, etc.). Considering the gate-level implementation of the sequential elements, the synthesis tool instantiates SET master-slave D flip-flops with  $C^2MOS$  gates and latch-based clock gates, both provided by the standard library. The synthesized netlist is a fully operational SET version of the design, which can optionally be used for automated place-and-route (APR) and for the derivation of a final design.

The definition of timing constraints is a crucial stage in the proposed design flow and methodology for mixing SET and DET blocks within a given system. In the proposed flow, a reference frequency ( $f_{ref}$ ) is defined according to the SET clock frequency, with the DET clocking frequency derived from this one ( $f_{det} = f_{ref}/2$ ). All interface constraints (i.e., input and output delays) are defined with a virtual clock toggling at  $f_{ref}$ , as virtually all STA tools assume I/O toggling according to a single-edged clock. This is further clarified through the example Synopsys design constraints (SDC) commands of Fig. 2.4. By defining the interface constraints relative to a clock that is always toggled at the original SET frequency and is separate from

```

# create virtual reference clock with SET frequency

create_clock -name reference_clock -period $t_ref

# set i/o delays relative to reference clock

set_input_delay $input_dly -clock reference_clock \

[remove_from_collection [all_inputs] [get_ports clk_in]]

set_output_delay $output_dly -clock reference_clock [all_outputs]

# Core logic clock definition:

# For SET (e.g., during synthesis)

create_clock -name core_clk -period $t_ref [get_ports clk_in]

# For DET (e.g., during DET P&R)

create_clock -name core_clk -period [expr $t_ref/2] [get_ports clk_in]

```

Figure 2.4: Example of SDC commands for defining a virtual reference clock and interface constraints.

the core logic clock, the interface constraints can be left unchanged when applying the DET clock frequency during the APR stage. This definition not only ensures correct STA with regard to interface delays, but also allows to keep constraint definitions and testbench structures synchronized throughout all stages of the flow.

Note that DET clocking incurs stricter design requirements on the clock signal than SET clocking and may incur some overhead in the clock network due to the need for slightly increased margins (depending on how well the duty cycle can be balanced across all corners), primarily due to the relevance of duty cycle variation on timing. Ideally, a 50% duty cycle as well as sharp rising and falling transitions are desirable for the clock signal provided to the DET flip-flops. To account for this during synthesis, the clock uncertainty constraint (intended primarily for jitter) must be adjusted according to the specifications of the primary clock source of the system and to the expected duty-cycle uncertainty. Nevertheless, fast and balanced transition times are generally ensured by the cells of the clock standard-cell library, which are used for clock tree synthesis during APR. Any remaining deviations in duty cycle caused by inequalities in rise and fall times along the clock network will then be accounted for by the STA tools according to gate and parasitic wire delays, allowing the APR tool to ensure correct timing of the design across variations. Any resulting overhead from more stringent timing constraints in the critical paths is fully accounted for in the reported results.

## 2.1.3.2 Post-Synthesis Conversion to DET

Once the SET netlist is obtained, the conventional SET-FFs and clock gating cells have to be substituted with their corresponding DET versions. This substitution is easily performed by simple string replacements on the gate-level netlist, assuming that a corresponding DET gate

is available for each SET-FF and SET-CG. Under the assumption that all rules of synchronous design [35] have been followed during the design and there are no macros included, the resulting netlist is now a functionally equivalent DET version of the original design where the registers are now sensitive to both clock edges and the DET-CGs perform the same clock-gating operation of the original SET-CGs.

One further consideration is the need to force the DET-CGs into a defined state, as described in Section 2.1.2. This requires connecting the DET-CG reset pin (CN in Fig. 2.2), which is usually not present in DET-CGs, to the global reset network. In order to not over-complicate the DET conversion script, the reset connection can be performed in the synthesis tool after reloading the modified netlist.

### 2.1.3.3 DET Automatic Place and Route Flow

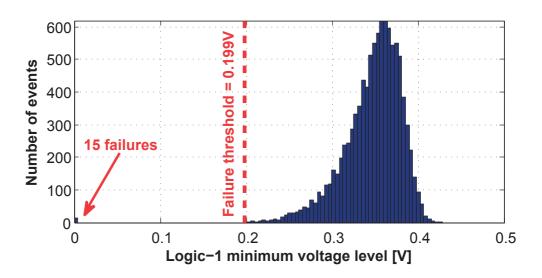

The translated netlist is now the starting point for a fully-DET-aware APR flow. A working SET APR flow is assumed for the design, therefore only the differences required for the DET version will be explained. As previously described, the interface timing constraints are defined relative to a virtual clock, and therefore they can be used without any modification. The only required change is the constraint on the clock input of the DET block to  $f_{ref}/2$  to reflect that now both edges are active. An example of this modification is shown in Fig. 2.4.