#### Smart Camera Architectures for Wireless and Multi-Sensor Vision Applications

THÈSE Nº 9204 (2018)

PRÉSENTÉE LE 20 DÉCEMBRE 2018 À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR LABORATOIRE DE SYSTÈMES MICROÉLECTRONIQUES PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

#### Selman ERGÜNAY

acceptée sur proposition du jury:

Prof. A. Kis, président du jury Prof. Y. Leblebici, directeur de thèse Prof. R. Carmona-Galan, rapporteur Prof. M. E. Yalcin, rapporteur Prof. J.-Ph. Thiran, rapporteur

It is not a bug, it is a feature. — Anonymous

To my wife, Şerife...

## Acknowledgements

First of all, I would like to express my sincere gratitude to my advisor Prof. Yusuf Leblebici for the opportunity he gave me to start this PhD work and his continuous support, patience, guidance and motivation. I learned a lot from him, not only from his broad research and engineering perspective, but also his personality. I am very thankful for the experience that I have acquired during the years of my PhD.

I am also grateful to the committee members, Prof. Andras Kis, Prof. Ricardo Carmona Galán, Prof. Müştak Erhan Yalçın and Prof. Jean-Philippe Thiran, for evaluating my work, their constructive comments and discussions.

I have found the opportunity of working with many people from different areas, and this allowed me to broaden my perspective. I would like to thank to the Master and Bachelor degree students with whom I have collaborated in different parts of my PhD work: Michaël Juillard, Alexis Michoud, Benoît d'Aramon, Benoit Alibert, Gökçen Nurlu, Jovan Blanusa, Hasret Sarıyer, Linda Özmen, Jeroen Buitendijk, Süha Köse, Yoann Biard, Çagri Erbağcı, Berk Olçum and Adrien Cellier.

I also would like to thank to my colleagues that I have collaborated with: Mustafa Kılıç, Kerim Türe, Bilal Demir, Jonathan Narinx, Vladan Popovic, Fırat Çelik, Ayça Akkaya, Duygu Kostak and Arda Uran. I also learned a lot from the discussions with Tuğba Demirci, Kerem Seyid, Ömer Çoğal and Kadir Akın and benefited from their experinces.

My thanks also go to the armasuisse team, Dr. Beat Ott and Dr. Peter Wellig, for their collaboration on the development and field test of the GigaEye-II system and on data collection for the polarimetry application.

Thanks to Dr. Alain Vachoux for his support on CAD tools and VHDL language, and Dr. Alexandre Schmid for his support with computing infrastructure. Thanks to Peter Brühlmeier and Sylvain Hauser for PCB design and mounting.

I would like to thank to my friends in LSM, Cosimo Aprile, Jonathan Narinx, Reza Ranjandish, Jury Sandrini, Behnoush Attarimashalkoubeh, Kiarash Gharibdoust, Elmira Shahrabi,

#### Acknowledgements

Gain Kim, Sebastian Rodriguez, Wen-Yang Hsu, Igor Krawczuk, Clemens Nyffeler and Takao Marukame for funny and joyful moments we shared.

I am very much thankful to my close friend and officemate Mustafa and his wife Züleyha. With Mustafa, we shared a lot of fun, pleasant, enjoyable as much as difficult, stressful, tense moments during 5 years. His sincere friendship always helped me to enjoy any moment at the office. I also appreciate good friendships that I had with many people in our lab as well as at EPFL, namely, Ömer & Betül Çoğal, Kerem & Gizem Seyid, Kadir Akın, Şeniz & Deniz Eroğlu, Tuğba Demirci, Abdulhamid Kavranoğlu, Gülperi Özsema, Ayça Akkaya, Fırat Çelik, İrem Boybat, Duygu Kostak, Can Baltacı, Gözen Köklü & Ali Galip Bayrak, Işınsu Katırcıoğlu and Aysu Okur.

I have had the chance of having great people during my PhD life, to whom I am very much grateful for sharing memorable moments in Switzerland. First of all, I should acknowledge the unprecedented accompany and friendship of the couple Fatih & Filiz Karakoyun. Their unconditional presence made my PhD life more entertaining, pleasant and 'socialized'. I am also very much thankful to Ahmet & Elif Bekdemir, Enver & Berra Kılınç, Halil & Hilal Okur, Kerim & Edibe Türe for having unforgettable moments in our 'big' gatherings in Lausanne, which I always enjoyed very much.

Of course, I am very much grateful to my father Selahattin, my mother Naime, my sister Dilek and my brother Hakan. I always feel their unconditional support and love in every stage of my life.

And finally, I appreciate every moment I spent with my beloved wife, Şerife for standing with me during these challenging times, believing and motivating me. Without her support, it would be much more difficult.

Lausanne, 9 December 2018

S. E.

## Abstract

Advances in camera sensor technology and its manufacturing process now allow high quality image acquisition with low-cost devices. Moreover, the latest significant increase in computational capacity of the processing units enables incorporation of more complex machine learning and deep learning methods within vision systems, expanding the capabilities of a typical camera system. A potential limitation of such complex and highly accurate machine learning and data processing methods is their high cost in terms of power and area. This limitation becomes more critical when multiple and/or wireless camera systems and come into question since such systems need to operate with limited power, memory and processing resources. Even though custom hardware solutions could solve this limitation problem, they however lack flexibility and hence are less practical. An embedded vision system with extended capabilities needs to be designed with a good trade-off between quality, speed, power consumption and flexibility.

A good trade off for an enhanced wireless multi-camera vision system may be provided by optimizing the system design at different levels. A common system-level approach to high-complexity systems is to partition the computational load and distribute it into local nodes. This corresponds to embedding computationally heavy operations into the camera units in a vision system which would reduce the bandwidth and overall power consumption. A camera equipped with a processing unit and memory that locally processes image data is called smart camera and can help overcome power, memory and processing resource limitations.

This thesis aims at designing a novel smart camera concept, and presents the hardware solutions to the proposed system design. Accordingly, in this thesis is proposed a flexible smart camera architecture which processes the pixel stream on-the-fly and produces metadata with low-latency, still providing high power and area efficiency. In particular, three processing blocks namely moving object detection, keypoint detection and description and cellular neural networks were implemented to illustrate the system design. In addition, proposed blocks are used in several applications such as omnidirectional image reconstruction, high resolution surveillance, polarimetry and wireless smart camera networks to show the flexibility of use of the proposed system in a wide-range applications.

## Résumé

Les progrès sur la technologie des capteurs d'image et de son processus de fabrication permettent désormais l'acquisition d'images de haute qualité avec des appareils à faible coût. De plus, l'augmentation significative dernièrement de la capacité de calcul des unités de traitement permet l'incorporation de méthodes d'apprentissage automatique et d'apprentissage profond plus complexe au sein des systèmes de vision en étendant les capacités des systèmes d'imageur typiques. Le coût élévé en terme de taille et de puissance est une limitation potentielle de ces méthodes d'apprentissage automatique et d'apprentissage profond complexes et extrémement précis. Cette limitation devient plus critique lorsque plusieurs systèmes de caméra et/ou sans fil sont mis en question, puisque ces systèmes doivent fonctionner avec une puissance, une mémoire et des ressources de traitement limitées. Même si des solutions matérielles personnalisées pouvaient résoudre ce problème, elles manquent cependant de fléxibilités et sont donc moins pratiques. Un système de vision embarqué avec des capacités étendues doit être conçue avec un bon compromis entre qualité, vitesse, faible consommation de puissance et flexibilité.

Un bon compromis pour un système de vision multi-caméras sans fil amélioré peut être obtenu à travers l'optimisation de la conception du système à différents niveaux. Une approche haut-niveau commune sur les systèmes très complexes consiste à partitionner la charge de calcul et à la répartir dans des nœuds locaux. Ceci correspond à l'incorporation d'opérations lourdes de calcul au sein d'une seul unité de caméra dans un système de vision, ce qui réduirait la bande passante et la consommation énergétique globale. Une caméra équipée d'une unité de traitement et d'une mémoire qui traite localement les données d'image s'appelle caméra intelligente et peut aider à surmonter les limitations liés à l'alimentation, la mémoire et les ressources de traitement.

Cette thèse vise à concevoir un nouveau concept de caméra intelligente et présente les différenes solutions matériels pour la conception du système proposé. En conséquence, une architecture de caméra intelligente et flexible est proposé dans cette thèse, traitant le flux de pixels à la volée et produisant des métadonnées avec une faible latence, offrant toujours une grande efficacité en termes de puissance et de surface. En particulier, trois blocs de traitements nommément détection d'objets en mouvement, détection et description de points-clés, et réseaux de cellules neuronales ont été mis en place pour illustrer la conception du système. En outre, les blocs proposés sont utilisés dans plusieurs applications telles que la reconstruction

#### Abstract

d'image omnidirectionnelle, la surveillance haute résolution, la polarimétrie et des réseaux de caméras intelligentes sans fil pour montrer la flexibilité d'utilisation du système proposé dans une large gamme d'applications.

# List of acronyms

| ADC           | Analog to Digital Converter                |

|---------------|--------------------------------------------|

| AHB           | Advanced High Performance Bus              |

| AMBA          | Advanced Microcontroller Bus Architecture  |

| APB           | Advanced Peripheral Bus                    |

| ASIC          | Application-Specific Integrated Circuit    |

| BRAM          | Block RAM                                  |

| BRISK         | Binary Robust Invariant Scalable Keypoints |

| CCD           | Charge Coupled Device                      |

| CIF           | Common Intermediate Format                 |

| CMOS          | Complementary Metal-Oxide-Semiconductor    |

| CNN           | Cellular Neural Network                    |

| <b>CNN-UM</b> | Cellular Neural Network Universal Machine  |

| CPU           | Central Processing Unit                    |

| DAC           | Digital to Analog Converter                |

| DC            | Direct Current                             |

| DDR           | Double Data Rate                           |

| DolP          | Degree of Linear Polarization              |

| FAST          | Feature Accelerated Segment Test           |

| FIFO          | First In First Out                         |

| FOV           | Field of View                              |

| FPGA          | Field Programmable Gate Array              |

| FREAK         | Fast Retina Keypoint                       |

| fps           | frame per second                           |

| FSM           | Finite State Machine                       |

| FMC           | FPGA Mezzanine Card                        |

| GUI           | Graphical User Interface                   |

| GPU           | Graphical Processing Unit                  |

| HD            | High Definition                            |

|               |                                            |

| HoG    | Histogram of Gradients              |

|--------|-------------------------------------|

| HPP    | Hybrid Processor Population         |

| IC     | Integrated Circuit                  |

| I/O    | Input/Output                        |

| ΙοΤ    | Internet of Things                  |

| LBD    | Local Binary Descriptor             |

| LBP    | Local Binary Pattern                |

| LUT    | Look-Up Table                       |

| LVDS   | Low-Voltage Differential Signaling  |

| MCU    | Microcontroller Unit                |

| MOG    | Mixture of Gaussians                |

| NMS    | Non-Maximal Suppression             |

| OpenCV | Open Source Computer Vision Library |

| ORB    | Oriented FAST and Rotated BRIEF     |

| PC     | Personal Computer                   |

| PCB    | Printed Circuit Board               |

| PLL    | Phase Locked Loop                   |

| PTZ    | Pan Tilt Zoom                       |

| QDR    | Quad Data Rate                      |

| RADAR  | Radio Detection and Ranging         |

| RAM    | Random Access Memory                |

| RF     | Radio Frequency                     |

| RGB    | Red-Green-Blue                      |

| RISC   | Reduced Instruction Set Computer    |

| SIFT   | Scale-Invariant Feature Transform   |

| SoC    | System on Chip                      |

| SRAM   | Static Random Access Memory         |

| SURF   | Speeded-Up Robust Features          |

| UAV    | Unmanned Aerial Vehicle             |

| VGA    | Video Graphics Array                |

| VGA    | Variable Gain Amplifier             |

| VHSIC  | Very High Speed Integrated Circuit  |

| VHDL   | VHSIC Hardware Description Language |

| WVSN   | Wireless Visual Sensor Network      |

| XGA    | eXtended Graphics Array             |

|        |                                     |

## Contents

| Ac | knov                         | vledge   | ments                          | v      |

|----|------------------------------|----------|--------------------------------|--------|

| Ab | bstract (English/Français) v |          |                                | vii    |

| Li | List of acronyms x           |          |                                | xii    |

| Li | List of figures x            |          |                                | xvi    |

| Li | stof                         | tables   |                                | xix    |

| 1  | Intr                         | oducti   | on                             | 1      |

| 2  | Stat                         | e of the | e art                          | 7      |

|    | 2.1<br>2.2                   | -        | bound camera systems           | 7<br>9 |

| 3  | Arcl                         | hitectu  | re                             | 13     |

|    | 3.1                          | Overv    | iew                            | 13     |

|    | 3.2                          | Movir    | ng Object Detection            | 15     |

|    |                              | 3.2.1    | Background Subtraction         | 18     |

|    |                              | 3.2.2    | Morphologic Filter             | 21     |

|    |                              | 3.2.3    | Connected Components Labeling  | 23     |

|    |                              | 3.2.4    | Result                         | 28     |

|    | 3.3 Feature Extraction       |          | re Extraction                  | 29     |

|    |                              | 3.3.1    | FAST Corner Detection          | 33     |

|    |                              | 3.3.2    | FREAK Description              | 37     |

|    | 3.4                          | •        | d Processor Population         | 42     |

|    |                              | 3.4.1    | Cell Model                     | 44     |

|    |                              | 3.4.2    | Connectivity Rules             | 45     |

|    |                              | 3.4.3    | Example Network Configurations | 46     |

|    |                              | 3.4.4    | Realization                    | 48     |

|    |                              | 3.4.5    | Conclusion                     | 49     |

|    | 3.5                          | Result   | t                              | 50     |

| 4  | Арр                          | licatio  | ns                             | 53     |

#### Contents

|    | 4.1   | Omni   | directional Image Reconstruction         | 53  |

|----|-------|--------|------------------------------------------|-----|

|    |       | 4.1.1  | Method                                   | 53  |

|    |       | 4.1.2  | Central Approach                         | 55  |

|    |       | 4.1.3  | Distributed Approach                     | 57  |

|    |       | 4.1.4  | Distributed and Parallel Implementation  | 57  |

|    |       | 4.1.5  | Interconnected Network of Cameras        | 58  |

|    |       | 4.1.6  | Novel hybrid architecture                | 60  |

|    | 4.2   | Polari | metry                                    | 63  |

|    |       | 4.2.1  | Method                                   | 66  |

|    |       | 4.2.2  | Result                                   | 71  |

|    |       | 4.2.3  | Conclusion                               | 72  |

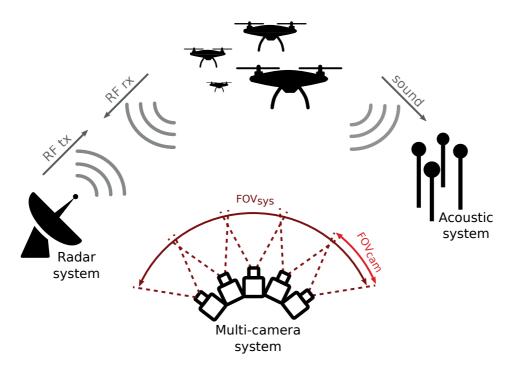

|    | 4.3   | Visior | n-based surveillance for drone detection | 74  |

|    |       | 4.3.1  | System overview                          | 76  |

|    |       | 4.3.2  | Result                                   | 80  |

|    | 4.4   | Wirele | ess Smart Camera Networks                | 82  |

|    |       | 4.4.1  | Introduction                             | 82  |

|    |       | 4.4.2  | Requirement Analysis                     | 83  |

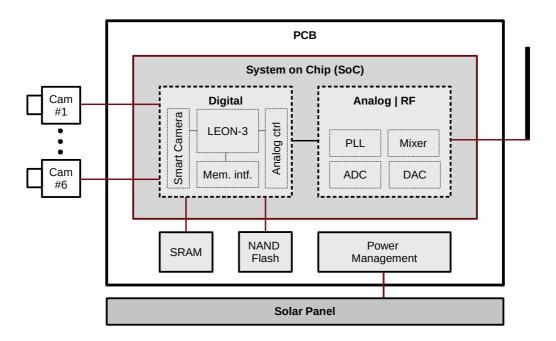

|    |       | 4.4.3  | System overview                          | 86  |

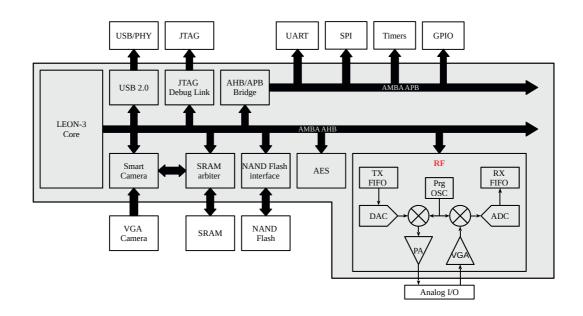

|    |       | 4.4.4  | Electronics Design                       | 89  |

|    |       | 4.4.5  | Conclusion                               | 92  |

| 5  | Con   | clusio | n                                        | 93  |

|    | 5.1   | Archit | tecture                                  | 93  |

|    | 5.2   | Applie | cations                                  | 94  |

|    | 5.3   | Futur  | e prospects                              | 94  |

| Сι | irric | ulum V | /itae                                    | 109 |

# List of Figures

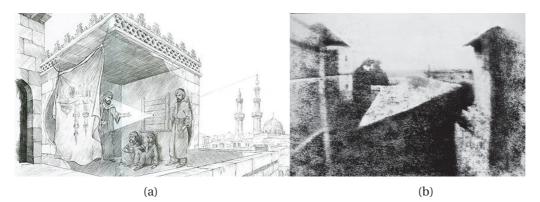

| 1.1  | (a) Illustration of camera obscura of Ibn al-Haytham (b) The first permanent photograph taken by Niepce | 1  |

|------|---------------------------------------------------------------------------------------------------------|----|

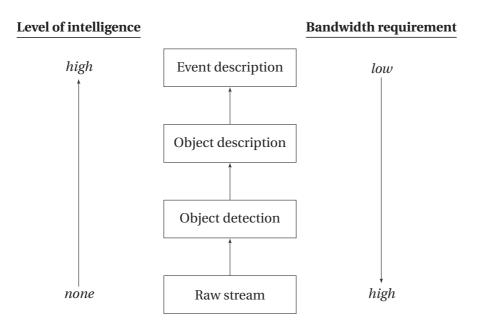

| 1.2  | Intelligence vs. bandwidth [4]                                                                          | 4  |

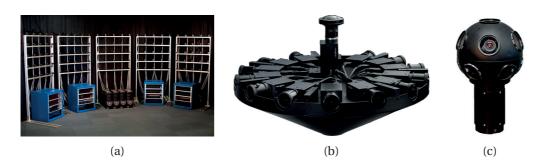

| 2.1  | (a) Stanford camera array [5] (b) Facebook surround 360 (c) Google street view [6]                      | 8  |

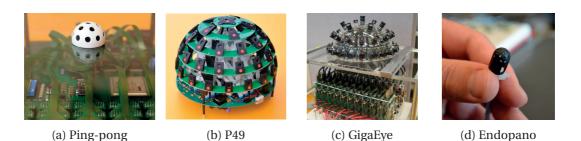

| 2.2  | Multi-camera systems with different dimensions developed in LSM/EPFL $\ldots$                           | 9  |

| 2.3  | Smart camera examples                                                                                   | 10 |

| 3.1  | Block diagram of the smart camera                                                                       | 13 |

| 3.2  | Image analysis chip of the smart camera                                                                 | 14 |

| 3.3  | Moving object detection pipeline                                                                        | 17 |

| 3.4  | Frame states for background subtraction block                                                           | 18 |

| 3.5  | Advanced evaluation of the pixels                                                                       | 20 |

| 3.6  | Content of a memory row stores information of one pixel                                                 | 21 |

| 3.7  | Example operation of a $2 \times 2$ erosion filter                                                      | 22 |

| 3.8  | Hardware implementation of the erosion filter                                                           | 23 |

| 3.9  | Data structure representing an instance                                                                 | 24 |

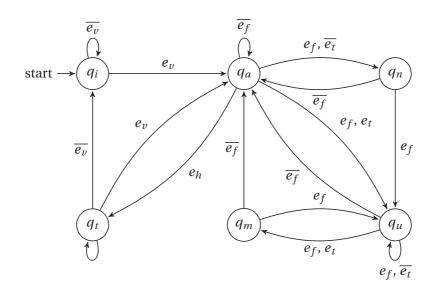

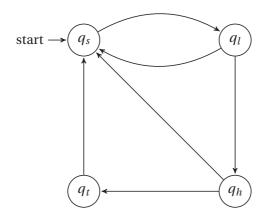

| 3.10 | FSM for connected component labeling                                                                    | 25 |

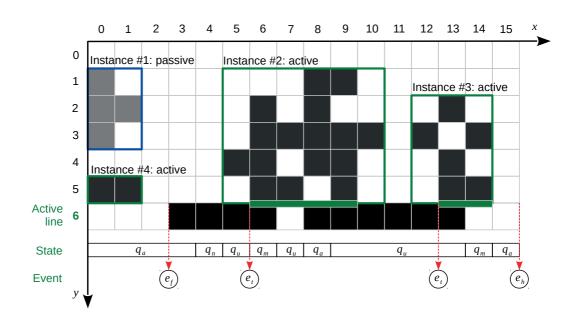

| 3.11 | Connected components labeling example operation                                                         | 27 |

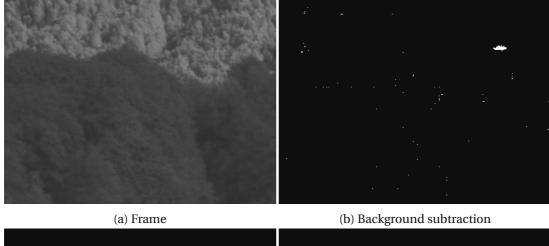

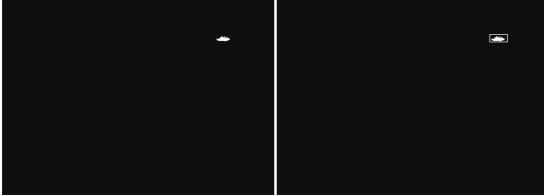

| 3.12 | Foreground detection results of the proposed method                                                     | 28 |

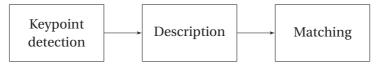

| 3.13 | Feature extraction pipeline                                                                             | 29 |

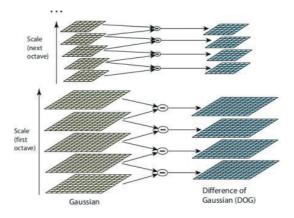

| 3.14 | Difference of Gaussians in SIFT [60]                                                                    | 30 |

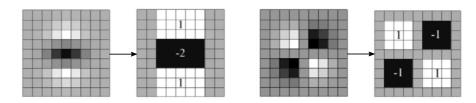

| 3.15 | Square box approximation in SURF [61]                                                                   | 31 |

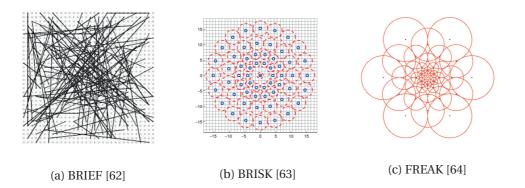

|      | Comparison points in binary descriptor                                                                  | 32 |

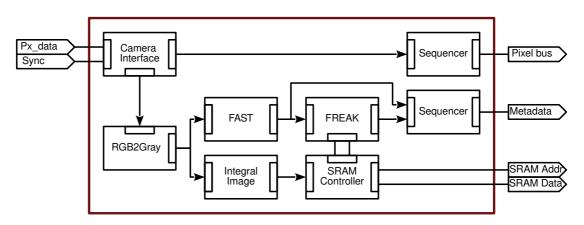

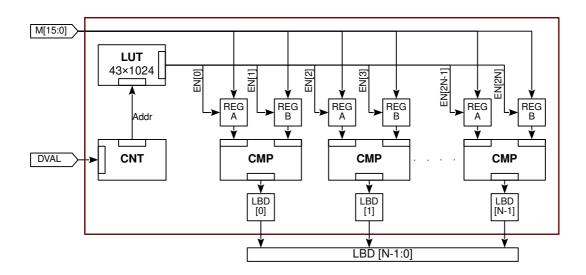

| 3.17 | Hardware block diagram for local binary description                                                     | 33 |

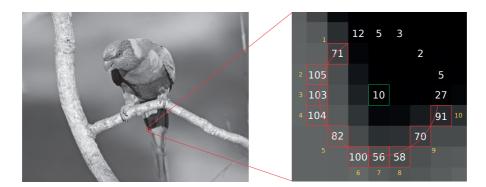

| 3.18 | A FAST corner on an example image                                                                       | 34 |

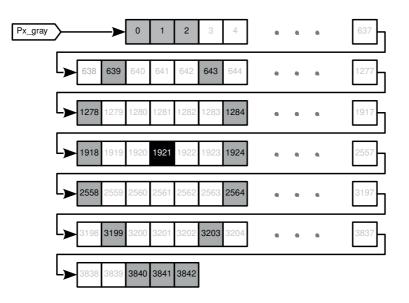

| 3.19 | Buffer used in FAST corner detection. Pixel numbers are for VGA resolution                              | 34 |

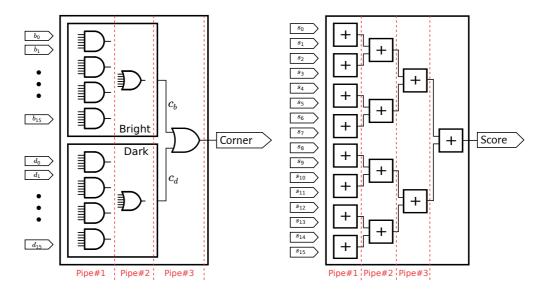

| 3.20 | Hardware blocks for FAST corner test and score computation                                              | 35 |

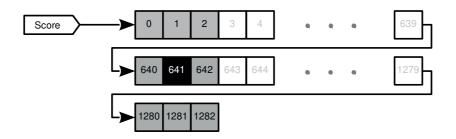

| 3.21 | Buffering of scores for non-max suppression                                                             | 36 |

| 3.22 | Hardware simulation results of the FAST block                                                           | 36 |

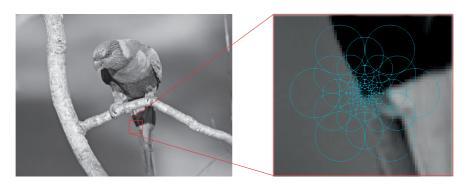

| 3.23 | FREAK pattern applied on a corner                                                                       | 37 |

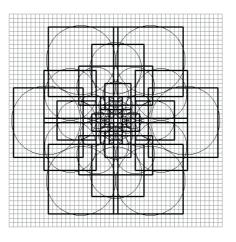

| 3.24 | FREAK pattern and box approximation                                                                     | 37 |

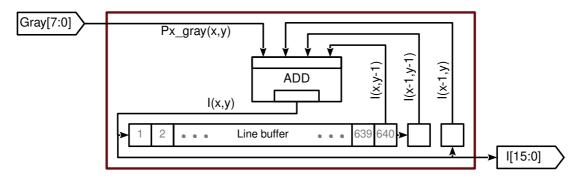

| 3.25 | Integral image calculation block                                                                        | 38 |

#### List of Figures

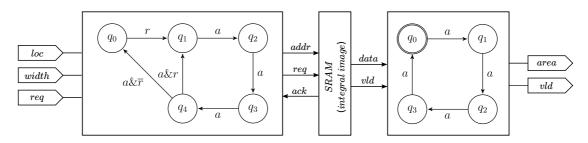

| 3.26 | Hardware of the box area computation                                                                                                                                                           | 39 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

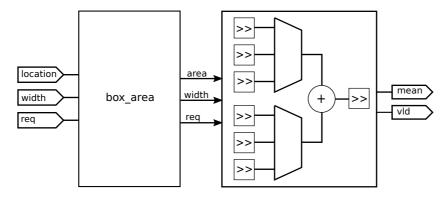

| 3.27 | Hardware of the box area computation                                                                                                                                                           | 40 |

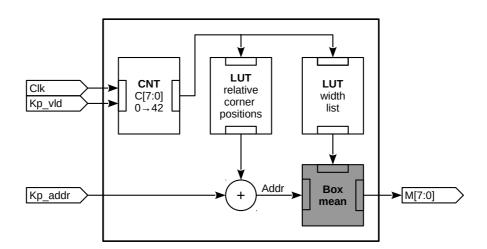

| 3.28 | Instantiating the box mean intensity computation block for FREAK pattern                                                                                                                       | 41 |

| 3.29 | Parallel comparison of mean intensities                                                                                                                                                        | 42 |

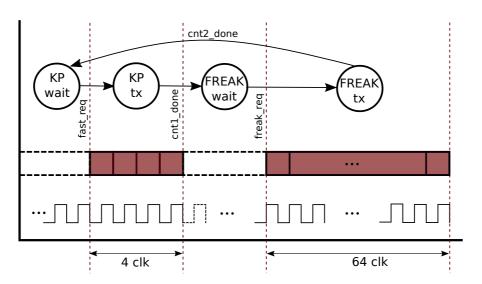

| 3.30 | FSM and timing diagram of metadata sequencer                                                                                                                                                   | 43 |

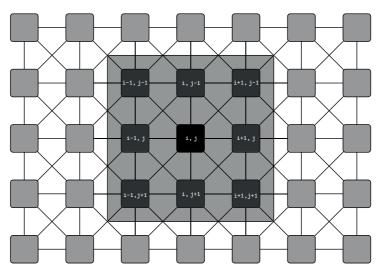

| 3.31 | Cell connections in CNN                                                                                                                                                                        | 43 |

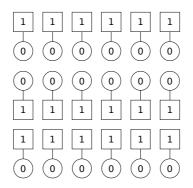

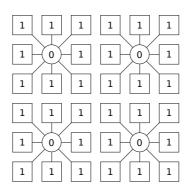

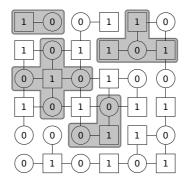

| 3.32 | A network configuration for LBDs                                                                                                                                                               | 47 |

| 3.33 | A network configuration for LBPs                                                                                                                                                               | 48 |

| 3.34 | Randomly distributed inhibitory and excitatory cells under limited connectivity                                                                                                                |    |

|      | rules.                                                                                                                                                                                         | 48 |

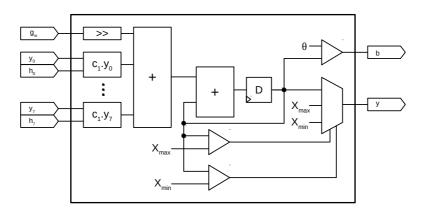

| 3.35 | Hardware of a single cell in HPP                                                                                                                                                               | 49 |

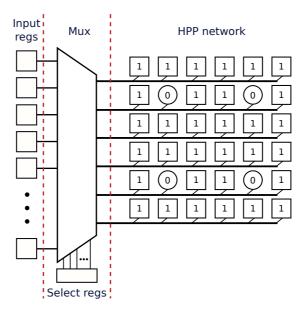

| 3.36 | Multiplexing the inputs for HPP                                                                                                                                                                | 49 |

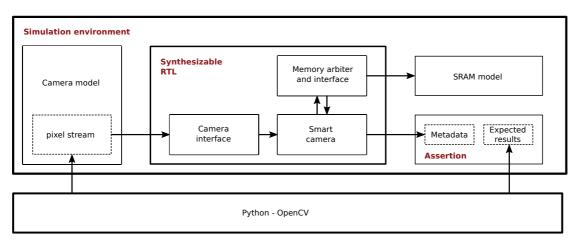

| 3.37 | Hardware simulation environment of smart camera                                                                                                                                                | 50 |

| 4 1  | (a) Compared contributions to the dimension $\vec{t}$ (b) contributions given by stitute on                                                                                                    |    |

| 4.1  | (a)Cameras contributing to the direction $\vec{\omega}$ , (b) contributing pixel positions on<br>the image frame of the contributing cameras for direction $\vec{\omega}$ , (c) projections of |    |

|      | camera centers contributing to direction $\vec{\omega}$ onto planar surface normal to $\vec{\omega}$ .                                                                                         | 54 |

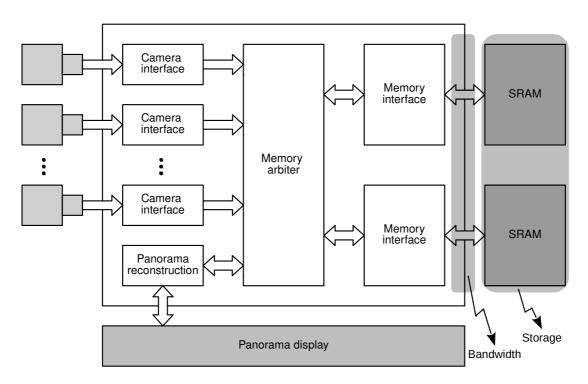

| 4.2  | Centralized implementation approach to the reconstruction algorithm. Camera                                                                                                                    | 54 |

| 4.2  | data is saved onto one of the SRAMs, via camera interface and memory interface.                                                                                                                |    |

|      | Panorama reconstruction algorithm access the camera data which belongs to                                                                                                                      |    |

|      |                                                                                                                                                                                                | 56 |

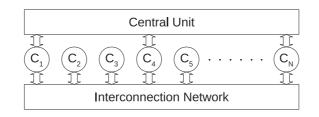

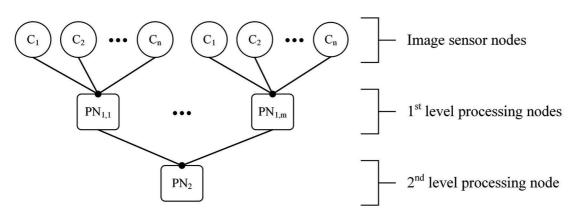

| 4.3  | High level model of an interconnected network of cameras. All cameras $C_i$ are                                                                                                                | 50 |

| 1.0  | connected via interconnection network and some cameras have direct access to                                                                                                                   |    |

|      |                                                                                                                                                                                                | 58 |

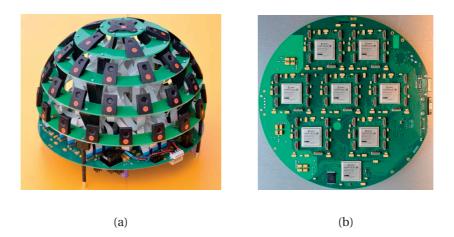

| 4.4  | (a) The network-based Panoptic prototype with 5 floors and 49 cameras. The                                                                                                                     |    |

|      | sphere diameter of the prototype is $2r_{\odot} = 30$ cm. (b) Top view of the Panoptic                                                                                                         |    |

|      |                                                                                                                                                                                                | 59 |

| 4.5  | Network with tree topology of depth 2. PN1 operates on images collected by                                                                                                                     |    |

|      | C and PN2 stitch partially reconstructed images by PN1. Maximum supported                                                                                                                      |    |

|      | number of cameras is determined by fanout of PN1 and PN2 ( <i>m</i> , <i>n</i> , respectively)                                                                                                 | 60 |

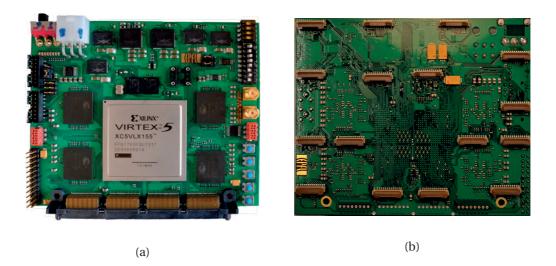

| 4.6  | (a) Front view of the horizontal board carrying FPGA, memories, power units and                                                                                                                |    |

|      | misc. devices (b) Back view of the horizontal board carrying 16 camera connectors                                                                                                              | 61 |

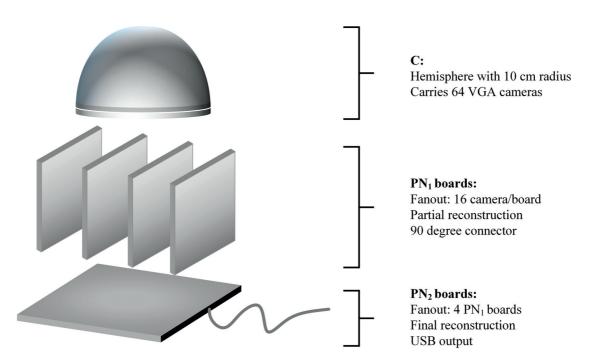

| 4.7  | Hardware solution for a system which has single PN2. Cameras is placed on                                                                                                                      |    |

|      | hemisphere, and collected images are transmitted to vertical boards which                                                                                                                      |    |

|      | represents PN1. Omnidirectional image is completed on horizontal board, PN2,                                                                                                                   |    |

|      | processing of stitched image by PN1.                                                                                                                                                           | 62 |

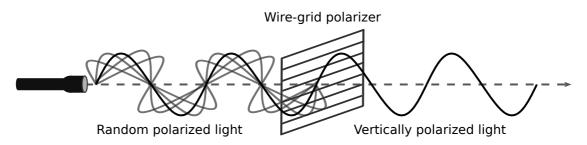

| 4.8  | Horizontally placed wire-grid polarizer absorbs the horizontal components                                                                                                                      | 63 |

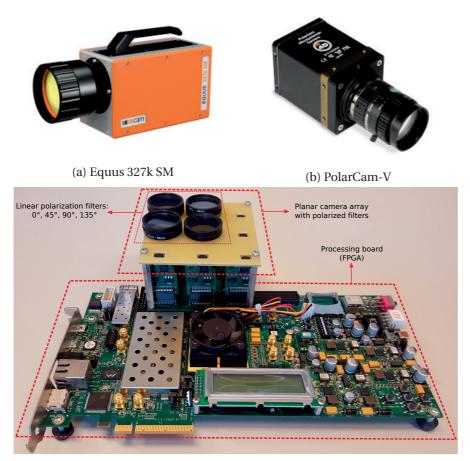

| 4.9  | Polarization camera examples                                                                                                                                                                   | 64 |

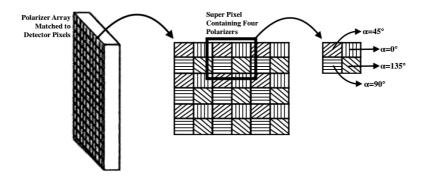

| 4.10 | Super-pixel structure                                                                                                                                                                          | 65 |

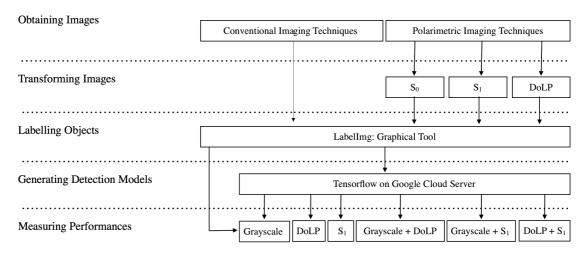

| 4.11 | Steps followed in this study                                                                                                                                                                   | 67 |

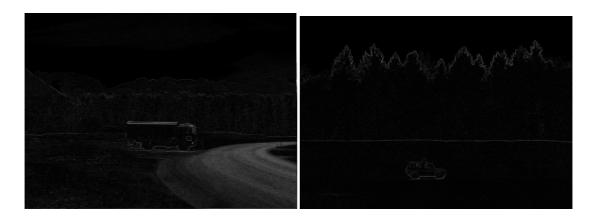

| 4.12 | Raw polarimetric images                                                                                                                                                                        | 68 |

| 4.13 | Transformed polarimetric images                                                                                                                                                                | 69 |

#### List of Figures

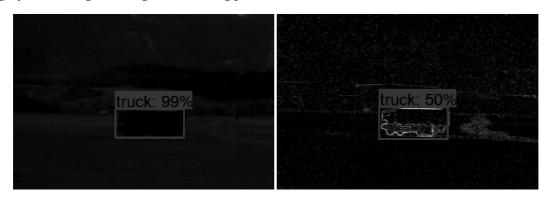

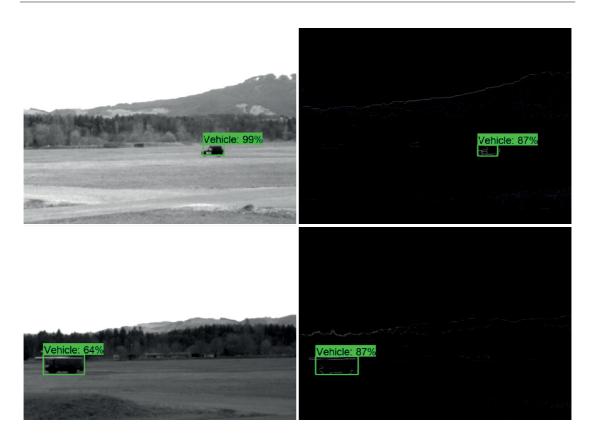

| 4.14 Initial detection                                                | 70 |

|-----------------------------------------------------------------------|----|

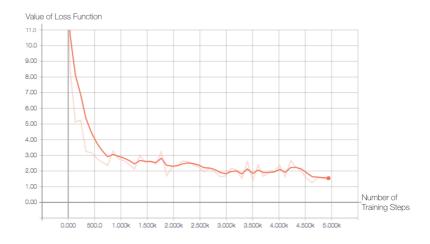

| 4.15 Training loss                                                    | 71 |

| 4.16 Detected objects                                                 | 73 |

| 4.17 Drone detection methods                                          | 74 |

| 4.18 GigaEye-II, captured in drone detection days of armasuisse, 2016 | 77 |

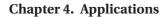

| 4.19 GigaEye-II connectivity with single PC via 10 Gb ethernet        | 78 |

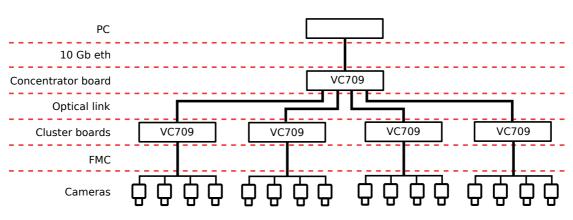

| 4.20 GigaEye-II connectivity with dual PC via PCIe                    | 78 |

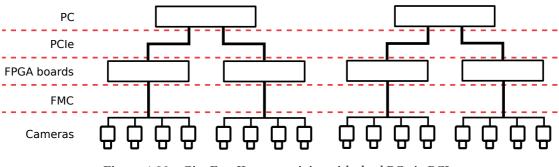

| 4.21 Smart camera concept applied to the GigaEye system               | 79 |

| 4.22 Operation of the drone detection software for GigaEye platform   | 79 |

| 4.23 Moving Object Detection stages                                   | 80 |

| 4.24 Moving Object Detection stages                                   | 81 |

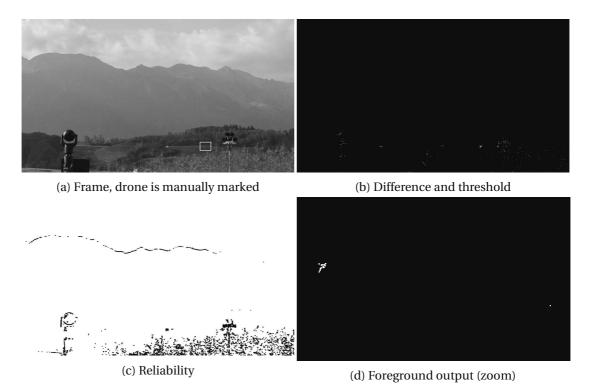

| 4.25 Wide area surveillance with distributed camera nodes             | 82 |

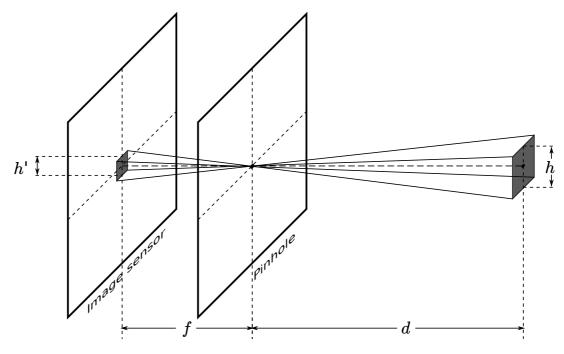

| 4.26 Pin-hole camera model                                            | 83 |

| 4.27 WVSN node block diagram                                          | 87 |

| 4.28 FSM for operation of the WVSN                                    | 88 |

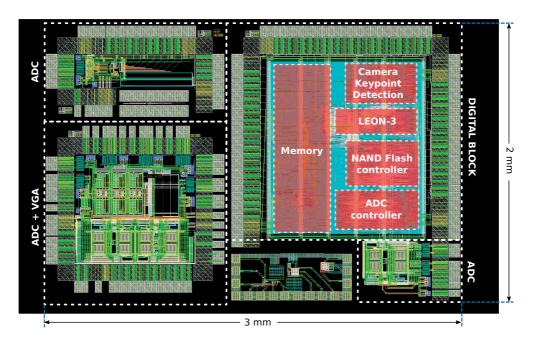

| 4.29 Block diagram of the processing chip                             | 89 |

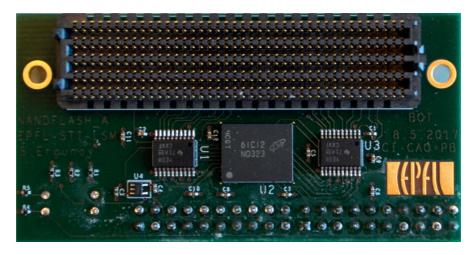

| 4.30 NAND Flash interface board equipped with FMC connector           | 89 |

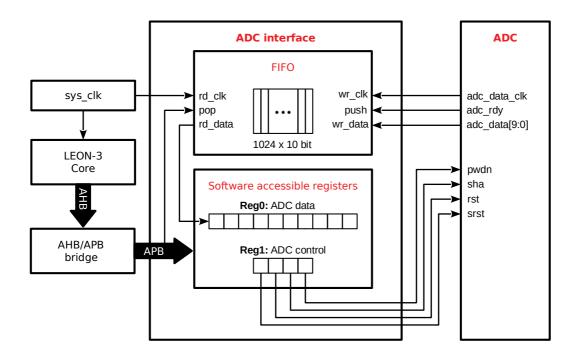

| 4.31 Block diagram of ADC interface                                   | 90 |

| 4.32 Tapeout in 65-nm TSMC technology                                 | 91 |

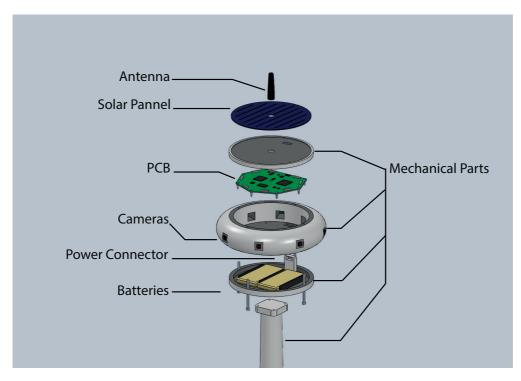

| 4.33 3D view of the energy autonomous camera system                   | 92 |

|                                                                       |    |

## List of Tables

| 3.1 | LUT approximation of $A \div r^2$ for FREAK pattern                        | 39 |

|-----|----------------------------------------------------------------------------|----|

| 3.2 | Resource allocation                                                        | 51 |

| 3.3 | Performance comparison for Moving Object Detection                         | 51 |

| 3.4 | Performance comparison for Keypoint Description                            | 51 |

|     |                                                                            |    |

| 4.1 | Storage and bandwidth comparison of the Panoptic systems                   | 62 |

| 4.2 | Details regarding to the camera systems used in this study                 | 65 |

| 4.3 | Accuracy of the trained models                                             | 72 |

| 4.4 | Wireless power analysis                                                    | 85 |

| 4.5 | Solar irradiance $[kWh/m^2/day]$ on a horizontal surface in Lausanne [116] | 85 |

| 4.6 | Harvested energy per day in the worst case                                 | 85 |

|     |                                                                            |    |

## **1** Introduction

Although development of the camera technology is presumed to belong to the last centuries, its roots go back to the fifth century BC in the ancient Greece. Micius, Aristotle and Euclid built the basic working principle of the pinhole camera. They found that the light travels as straight lines and when it passes through a pinhole, it projects an inverted image of the scene. In addition to this, they also realized that smaller pinhole aperture enables sharper projection [1]. Based on this principle, the first camera obscura was designed by Arab scientist Ibn al-Haytham in 9th century, illustrated in Figure 1.1a. This camera obscura, or pin-hole camera, forms the basis of photography. During the following centuries, many scientists have contributed to the development of the pinhole camera. The earliest cameras that are built until 17th century were room-sized and the produced images were only preserved by manual tracing. In the 17th century, first portable model is invented by Robert Boyle and Robert Hooke and the first permanent photographic image (see Figure 1.1b) was made by a French inventor Nicephore Niepce in the early 19th century [2]. The inventions regarding photographic process, called Daguerrotype process which is followed by dry plates, photographic films etc.

Figure 1.1 – (a) Illustration of camera obscura of Ibn al-Haytham (b) The first permanent photograph taken by Niepce

#### **Chapter 1. Introduction**

With the emergence of digital cameras, the technology has been progressed drastically. Today's digital camera era, two types of camera sensor are available in the market: Charge Coupled Device (CCD) and Complementary Metal-Oxide-Semiconductor (CMOS) sensors. CCD sensors which provides high quality and low-noise images require a special manufacturing process to transport the charge across the chip without distortion. Charge to voltage conversion is performed before the output buffer of the readout circuit. For this process, very high quality sensors with high light sensitivity is needed. After exposure is completed, CCD transfers charge packet of the each pixel sequentially via a shift register structure.

In the CMOS sensor technology, each pixel has several transistor next to it. This reduces the light sensitivity and consequently the image quality. However, CMOS sensors consumes much less power than CCD and its digital memory style readout faster readout circuitry allows to reach high frame rates. Moreover, its low-cost manufacturing process allows to produce much cheaper sensors and this makes the CMOS sensors widely spread.

Developments in memory, smart phone and cloud technologies together, make the storage of the photos or sharing them much easier. Moreover, advanced computer vision methods, image understanding capabilities of the computers with the help of graphical processing units are extremely increased and computationally heavy deep learning blocks can be operated on these powerful devices. Such advances in hardware and software units have brought new functionalities to the camera technology, making cameras more accessible to end-users and enlarging its use areas.

Even though the camera systems have evolved much more than expected in the last decades, there are still many open issues and challenges. One of the limitations of the today's camera systems is their limited angle of view. Although the available fish-eye lenses extend the angle of view, they inevitably bring distortion and non-uniform resolution. Curved sensor and micro-lens arrays could be an alternative solution but they require special manufacturing process making them cost-inefficient. Multiple camera systems can provide less-distorted and low-cost solution to angle-of-view limitation of the current camera systems.

Another issue is power efficiency of the camera systems. Wireless camera systems have been popular in the last decade due to its large number of application areas including surveillance. Wireless nodes in such systems are designed either as battery-operated or as self-powered. In either case, they have limited power budget. Therefore, this limitation usually does not allow broadcasting. As data to be transferred through such systems is limited, it should be pre-processed in advance and only salient information should be transmitted to the central units. This requires a wireless node to be able to process the frames locally before transmission.

Increasing number of cameras connected to a single processing unit may also suffer from bandwidth limitations. In wired systems, pin count of the processing unit, PCB path and connector types determines the bandwidth. In wireless systems, carrier frequency, transmission power and range are major delimiters.

Considering these limitations and issues, distributing the computational load into local nodes, or in other words, increasing intelligence of the nodes, gives a solution. In this case, each peripheral unit in a multiple and/or wireless camera systems has to be designed as data-aware cameras. Each camera is accordingly has its own processing unit operating according to the assigned task. The good organization of those cameras is able to eliminate the limitations of typical multiple and wireless camera systems. We refer such a data-aware camera with extended functionalities as *Smart Camera* and is the main focus of this thesis.

There are different definitions of smart camera used in the literature and industry [3]. For instance, auto-exposure or auto-focus can also be referred as smart camera. However, in this work we use the smart camera concept as the camera not only taking images, but also providing information about the image content by local processing. The objective of a smart camera system is not broadcasting or high quality imaging, therefore it performs in highly energy-efficient way and requires low bandwidth. A big advantage of a smart camera is obviously its appropriateness for wireless camera systems requiring low-bandwidth and low energy consumption. With the current trend of wireless communications, the necessity of designing energy and data-efficient wireless systems is high and smart cameras can provide good solution for such important camera systems.

The relation between the level of intelligence and bandwidth requirement is depicted in Figure 1.2. In a standard camera where only raw data is streamed, the bandwidth requirement is at its maximum since it lacks of the ability to local data processing, hence all the pixels captured are sent to the central processing unit. As the level of the intelligence increases by different data processing steps such as object detection, object description and event description, bandwidth requirement reduces. In those cases, the data to be transferred can be pixel information of the related area of the figures, keypoints of the area of interest or classification of the object of interest instead of the whole image scene. This could decrease the transmission bandwidth and processing load in the central units providing faster and more efficient data communication.

With the aforementioned capabilities, smart cameras have many application areas and new applications emerge with the development of electronics and software technology. For instance, with the emergence of drone technology, the use of smart cameras in drones is a new topic to be explored nowadays. Many similar applications will be appearing in the future, which makes the efficient design and use of smart cameras crucial for the literature and the industry. Applications of the smart cameras cover a wide range listed below, but not limited to:

- Surveillance for security

- Disaster-related surveillance

- Wireless healthcare applications

- Industrial monitoring and control

Figure 1.2 - Intelligence vs. bandwidth [4]

- Environmental and habitat monitoring

- Drone applications

- Simultaneous localization and mapping (SLAM)

In this thesis, we propose a smart camera architecture for wireless and multi-camera applications. This architecture aims at utilizing an external image sensor and performs its operations by processing the sensor pixel stream on-the-fly. Smart camera provides the output information as metadata with minimum latency. As processing blocks, we implemented moving object detection, keypoint detection, binary description, and Cellular Neural Network blocks. The smart camera system that we propose in this work is not the unique or exact solution to the problem. Yet, it provides a better tradeoff than its counterparts in terms of flexibility, power and timing efficiency.

#### Key contribution of this thesis

The details of the contributions regarding to the architecture and applications are below:

- Architecture:

- A power and area efficient low-complexity moving object detection method is proposed and implemented in FPGA. Its algorithm which consists of background subtraction, morphological filtering and connected component labeling is detailed.

- A resource efficient hardware implementation of a keypoint detection combined with local binary description is presented. Particularly, FAST corner detection and FREAK description algorithms are designed with VHDL and implemented for both FPGA and ASIC.

- A CNN-like network, Hybrid Processor Population is integrated to the smart camera system. Different network configurations which can help local computations is given.

- Applications:

- A hybrid architecture for multi-camera systems are proposed and its hardware is realized. Its PCB design consisting of FPGA and QDR-II memories are presented.

- A high-resolution vision based drone detection method and its realization is presented.

- A deep learning method is applied for polarimetry applications. We collected data from polarimetric cameras, train the networks by testing different polarimetry components. Finally we proposed a multi-camera polarimetry hardware.

- A wireless smart camera node is proposed exploiting the smart camera blocks. System consists of Leon-3 open source RISC processor for system management, NAND Flash interface for data storage, and analog blocks for sub-1 GHZ wireless transmission.

#### **Thesis outline**

The outline of this thesis is as follows: in Chapter 2, we give a brief state of the art concerning the smart camera systems. Chapter 3, explains the components constitutes of our smart camera architecture. Particularly, moving object detection, keypoint detection and description and Cellular Neural Network blocks are explained and their hardware implementation details are given. In Chapter 4, 4 different example applications are given. Drone detection, omnidirectional reconstruction, polarimetric imaging and wireless smart camera network problems are examined and smart camera solutions are presented. Finally, Chapter 5 concludes the thesis and present future research directions.

## **2** State of the art

In Chapter 1, a brief introduction of the smart camera systems is given as well as our motivation to this work and the challenges is explained. In this chapter, state of the art in multiple and wireless camera systems will be presented. State of the art regarding the methods and algorithms used in this work can be found in related sections.

Considering the difference in application areas and challenges, multiple camera systems can be examined in two groups: (i) compound and (ii) distributed camera systems. While the compound camera systems usually target to obtain wide FOV images, in distributed camera systems environment is observed partially by each wireless node in a power efficient way.

#### 2.1 Compound camera systems

One of the main restrictions of the single conventional cameras is their limited angle of view. Several solutions for acquiring omnidirectional images and their application have been presented in [7]. In fact, successful examples of wide angle viewing are available in the nature as well. For instance, compound eyes of common fly is an appropriate example, which contains hundreds of optical units providing panoramic field of view [8]. Ideally this structure can be mimicked by curved sensors, however since their manufacturing process is very difficult, this solution is very expensive and has low resolution [9].

Another way is combination of special lenses and convex mirrors, but distortion and nonuniform resolution is inevitable in this case [10]. Among the alternatives, multiple camera systems have been gaining importance in the recent years due to their benefits such as uniform and high resolution output, in addition to the reduced distortion. Moreover, the conventional cameras are broadly available and low-cost technology, therefore can provide much more costeffective solution compared to the aforementioned methods requiring special manufacturing process.

Compound camera systems are composed of outward looking multiple cameras placed on a planar, spherical or cylindrical surface. A number of multiple camera systems are designed

Figure 2.1 – (a) Stanford camera array [5] (b) Facebook surround 360 (c) Google street view [6]

with different features in terms of dimensions, real-time capability, number of cameras, output format and resolution.

One of the first examples of compound camera systems is FlyCam [11] which offers a PC based stitching. It consists of 5 inexpensive and low-resolution cameras. The Stanford Camera Array [5] is the other early example of multiple camera systems. It consists of 100 cameras connected to 4 PCs as shown in Figure 2.1a. It has a limited processing capability in the camera level. The system is used for recording the videos to be later stitched offline.

Google Street View [6] is a popular example for polydioptric data acquisitions systems. 15 of 5-megapixel CMOS image sensors are placed on a spherical surface as shown in Figure 2.1c. It is a 360° imaging system comprising 15 5MP cameras, which covers 80% of its surroundings. This system is used to generate contents for street view property of Google Maps.

Another panorama system with high resolution output, OmniCam is presented in [12]. This scalable system supports up to 12 HD cameras, and output panorama is stitched in post-production.

In order to reach higher output resolution, number of cameras and sensor resolution can be increased. An example camera system which is able to acquire an image frame with more than 1 Gigapixel resolution was presented in [13]. The system uses a very complex lens system comprising a parallel array of micro cameras to acquire the image. Due to the extremely high resolution of the image, it suffers from a very low frame rate of three frames per minute.

Generating the panoramas offline is useful in many cases, but real-time stitching have been a demanding task especially in interactive applications. In [14] real-time systems with six cubically arranged cameras are presented. These systems utilize high resolution imagers with a low number of cameras.

The Panoptic Camera, introduced in [15] is capable of real-time data processing and omnidirectional view generation. Hardware implementation of different blending algorithms on this system is presented in [16]. The details of the Panoptic Camera is introduced in Section 4.1. Based on the proposed algorithm, different systems have been developed [16], [17], [18] and integrated with VR interface [19] in LSM (Microelectronic Systems Laboratory) at EPFL. Hard-

#### 2.2. Distributed camera systems

Figure 2.2 - Multi-camera systems with different dimensions developed in LSM/EPFL

ware implementation of the system which has 15 cameras on a 3-layer and 3 cm diameter hemisphere can be seen in Figure 2.2a. In [18], high-resolution-44-camera system design for defense and security applications is presented. It is capable of recording omni-directional video in a  $360^{\circ} \times 100^{\circ}$  FOV at 9.5 fps with a resolution over 82.3MP (see Figure 2.2c). Another approach based on interconnected network of the cameras is proposed in [17], and the presented hardware is depicted in 2.2b.

Physical dimensions of the multiple camera systems can be reduced down to millimeter scale. Cogal and Leblebici developed a miniaturized omnidirectional camera system with 24 pinhole cameras [20], shown in Figure 2.2d. Cameras are placed on a 5 mm radius hemispherical case. Its FPGA implementation achieves 1 megapixel resolution at 25 fps.

#### 2.2 Distributed camera systems

One of the earliest examples of the smart camera system is CMUcam [21] which was proposed in 2001. It combines a low-cost CMOS image sensor at CIF resolution and a low-cost micro-controller. Since the processing capability is quite limited, it can only perform a basic color based blob tracking at 16.7 fps.

Another example of early smart cameras with MCU is Cyclops [22]. It consists of a CPLD for image capturing from a CIF-resolution camera and transfer it to the frame buffer in 64-KB external SRAM. Since the image resolution  $352 \times 288 = 99K$  is greater then the available memory, it reduces down the resolution to  $128 \times 128$  for the processing applications. Buffered frame is accessed by a 8-bit microcontroller to perform some vision algorithms, including moving object detection and hand posture recognition.

The Cyclops and CMUCam is used as the low-power tier of SensEye [23] system which employs multiple tier of cameras. For the high-level tiers it has a VGA resolution web-cam and PTZ (pan-tilt-zoom) camera at HD resolution with high-cost. The network activates the high-level tiers, if only low-level tiers detect an important activity.

The processing capability of WVSN nodes is increased with the development of more efficient MCUs. 32-bit ARM powered MeshEye [4] system is battery-operated and provides a low-

(a) CITRIC

(b) CMUcam-5

(c) Google clips

Figure 2.3 – Smart camera examples

resolution stereo vision, presented in 2007. In this system, a low-resolution stereo camera system observes the scene and determines the position, range and size of the moving objects. This information triggers a high resolution color camera module for further analysis.

Increasing CPU power and memory extend the capability, thus application range. Integrating an Intel XScale MCU which can operate up to 624 MHz, 16 MB Flash and 64 MB RAM in CITRIC [24] system enables image compression, target tracking and camera localization applications. Its power consumption is reported to be minimum 428mW at IDLE mode, and 970mW at high performance mode.

Combining the high performance MCUs and open source software tools provides a high flexibility in terms of the applications. Raspberry Pi (ARM 700 MHz) and MSP430 MCUs are used together in a solar powered wireless smart camera SWEETcam [25], and proposed for the surveillance of public spaces in 2014. It also benefits from the Linux operating system and OpenCV libraries which reduce the application development time significantly. But the power consumption is still around 500 mW.

In the recent years, commercial products targeting consumer electronics market have been appearing. A popular example is Google Clips [26] shown in Figure 2.3. It selects the best moments with a learning algorithm and store them as short video files. However, its battery enables up to only 3 hours operation.

Energy consumption could be reduced by custom hardware design at the expense of software flexibility. FPGAs are reconfigurable digital devices which allows parallelization of task. Thus, lower operating clock frequencies reduce power consumption. An early smart camera architecture with FPGA is presented in 2006 [27]. Inspiring from the human vision system, authors split the process into three layers: (1) attention and (2) focusing of eye sends the pertinent information, and it is (3) interpreted in brain. Since attention and focusing stages need parallelization, they are assigned to FPGA. On the other hand, since the data to be processed is reduced down, high level tasks are performed in PC.

SRAM FPGA is known as power efficient comparing with Flash FPGA. SENTIOF-CAM [28] is an example of wireless vision sensor node with SRAM FPGA, proposed in 2014. Authors implemented a low-complexity background subtraction, segmentation and bi-level video codec in FPGA. They employed the system in particle detection, meter reading and people counting applications. In these applications, processing power is measured as 670 mW.

Utilizing off-the-shelf processing devices such as MCUs and FPGAs provide high flexibility, however ASIC solutions and transistor level optimizations are needed in order to reach much power efficiency by sacrificing this flexibility. Focal-plane image processing is one of the most efficient methods to reduce the power consumption. An example image sensor which has focal-processing array, FLIP-Q, is presented in [29]. Inside of each sensor area, pixel level analog processing elements operating concurrently with photosensing were incorporated. Having analog processing elements reduce the accuracy, but they are more area and power efficient. Resolution of the sensor was  $176 \times 144$  fabricated in a 0.35  $\mu$ m technology. It is reported that power consumption was maximum 5.6 mW. Later this platform was integrated to a WVSN node, Wi-FLIP [30].

Fill factor of an image sensor is the ratio between the light sensitive area to its total area and affects the sensitivity [31]. Placing the processing elements inside the pixel area reduce the fill factor, and hence the sensitivity as well. In order to overcome this issue, sensor, processing and memory planes were integrated vertically in [32]. Moreover, the resulting data bandwidth limitations of this solution was eliminated by fully parallel connections with high density of through-silicon-vias. Benefiting from this approach, a 3D vision chip VISCUBE which has different vision tasks stacked was presented. It had nearly 100% fill factor and able to reach very high frame rates up to 1000 fps. However, power consumption of the processing tiers could vary from order of 10 mW to 100 mW.

Another efficient transistor level technique to reduce the power consumption was near-threshold computing [33]. By using this method, reducing the power consumption down to even sub-mW levels by using energy-efficient MCUs is possible as presented in [34], [35]. This smart camera architecture exploited a low power contrast-based imager at  $128 \times 64$  resolution and a quad-core ultra-low power processor (PULP) operates near-threshold. It also used content aware analog circuits to extract meaningful data from the sensor which sends the post-processed data to the processor. By this way, the sensor to processor bandwidth was reduced by 31 times.

Although near-threshold computing enables energy efficient integrated circuits, its reduction is also limited [36] and it is known that scaling down the transistor size does not bring a significant power advantage [37]. Therefore, future power reduction attempts are expected to be from different directions. A recent approach, Energy-Quality (EQ) Scalability was presented in 2017 [38]. It is based on the idea that, high quality tasks need high energy, and reducing the quality, where it is tolerable, can bring significant power reductions. This approach was applied on vision applications and an EQ scalable feature extraction accelerator EQSCALE

was implemented in [39]. EQSCALE is assumed to be the first feature extractor that operates in sub-mW range at VGA resolution and 30 fps.

In this chapter, we presented examples of multiple and wireless smart camera systems among many of them. It can be seen that, there is not indeed a single unique solution to the problem. Since there are different design concerns and challenges in terms of power, area, bandwidth and flexibility, solutions also diversify. In the next chapters, inspiring from the ideas that were presented in the state-of-the art systems, we will develop the smart camera architecture targeting at a good balance between the system requirements and limitations.

## **3** Architecture

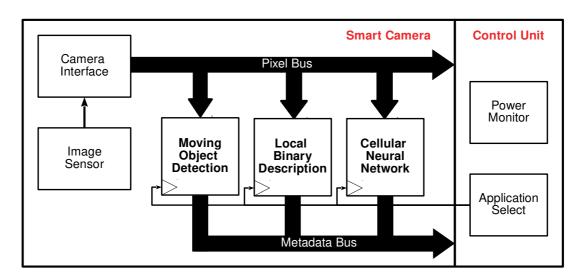

In this chapter, we present our smart camera architecture which is optimized in terms of resources and flexible enough to incorporate several processing modules with respect to the intended application. After giving an overview of the architecture, we will detail which functionalities that have been integrated as sub-modules into the proposed system.

#### 3.1 Overview

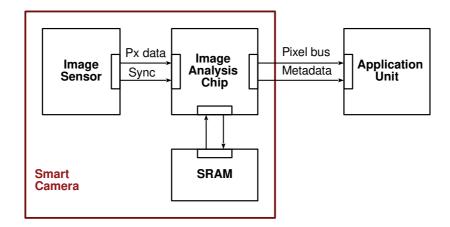

Our smart camera concept consists of three key components is shown in Figure 3.1. An image sensor captures the frame and sends the pixel information with the synchronization signals. In fact, the most common method is to save the frame into a memory (*i.e. frame buffer*), and process this pixel data by accessing from there. Instead of this, our image analysis chip directly receives the data form the sensor, and performs its operations on the fly, benefiting from pixel buffers to reduce the output latency. The processing blocks which performs local analysis does not wait the end of the frame. Therefore metadata of a frame is produced during its stream.

Figure 3.1 - Block diagram of the smart camera

Figure 3.2 – Image analysis chip of the smart camera

A closer look to the image analysis chip is shown in Figure 3.2. Firstly a camera interface compatible with the image sensor is needed to receive the pixel data and synchronization signals, and convert them into pixel color information and pixel row/column addresses. Many computer vision algorithms process the gray level intensity, not the color. Since the implemented block in this architecture also process the grayscale data, an RGB to grayscale conversion block is embedded into the camera interface block.

Processing blocks which are connected to the pixel bus are activated by the application unit. The activated block drives the metadata bus, while the others have high impedence outputs. It processes the pixel stream on-the-fly and generates metadata.

The produced metadata is received by an application unit at lower bandwidth than the pixel stream. Thus, the application unit can achieve at better performance by processing this reduced amount of data. Each processing block produces metadata at different energy levels. In power critical systems, a decision mechanism which take into account the power level of the system observed by power monitor is needed. A list of possible metadata is listed below:

- Location and size of the moving objects

- Keypoint positions and their descriptions

- Classification of the objects

- Disparity depth

- Polarimetry data

In this thesis, we show the implementation of three different application blocks, namely

moving object detection, local binary description and cellular neural network, in the following sections.

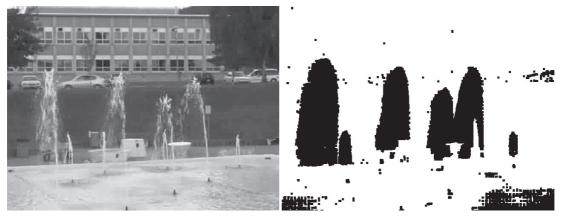

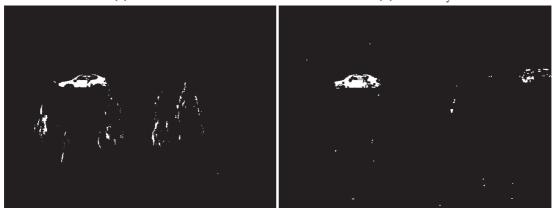

# 3.2 Moving Object Detection

Applying resource-hungry complex analysis for each pixel at the each frame generally prevents one to meet real-time and power requirements. In fact the amount of the data to be processed must be reduced in order to keep resource requirements as low as possible. Most of the cases, pixel information remains the same from frame to frame, and a small portion shows a difference. However, those changes may not represent salient information and could belong to the movements out of interest, such as fountain, water flow, clouds, shaking of the leaves or grasses in natural images. Therefore, retrieval of the most relevant pixels in the foreground that bare the most important information should be targeted. If such relevant pixels could be detected, the system would simply ignore the rest where there is no significant change and this would speed up the processing, satisfying real-time requirements. The goal is accordingly to detect salient changes and avoid to re-compute the pixel positions that are part of either background or noisy and uninformative changes. This problem is well studied concept under the moving object detection title. In this section, we first present an overview of the moving object detection techniques and then propose a hardware-oriented scheme aiming at memory and power efficiency with reasonable accuracy.

Moving object detection problem has been often approached with background subtraction techniques. Accordingly, several methods have been proposed in the literature targeting different efficiency components: memory, power, accuracy, speed, etc, or providing a good trade-off between those concerns. Robustness of the method is also an important challenge. It is an expectation that the algorithm should handle illumination changes and filter the non-salient motions. We will mention some of such techniques including the ones that are more relevant to our study.

One of the common pixel stream methods is running Gaussian average method [40]. For each pixel position, it fits a Gaussian probability density function (pdf) of the last *n* pixels. But in order to prevent re-computation of the pdf for each frame, a running average is calculated as given below:

$$\mu_t = \alpha I_t + (1 - \alpha) \mu_{t-1} \tag{3.1}$$

where  $I_t$  is current value of the pixel,  $\mu_t$  is the previous average, and  $\alpha$  is an empirical value can stand for learning rate.

A pixel location at each frame can be labeled as foreground, if it meets the following inequality:

$$|I_t - \mu_t| > k\sigma_t \tag{3.2}$$

15

In the running Gaussian average approach, the background model is updated even if the pixel marked as foreground. In order to prevent this updates, a selective update method is proposed:

$$\mu_t = M\mu_{t-1} + (1 - M)(\alpha I_t + (1 - \alpha)\mu_{t-1}$$

(3.3)

where *M* is 1 if the pixel belongs to a foreground object, otherwise it is 0.

Adaptive Mixture of Gaussians (MoG) [41] is interested in adaptive modeling of the background for real-time tracking of scenes with complex and non-static backgrounds. They accordingly model each pixel as a pixel process with K Gaussians (K being 3 to 5) with corresponding mean and variance parameters and update the mixture model with each new pixel value over time. The background model is described by the first most probable distributions and a new pixel accordingly assigned as background if the most fitting Gaussian distribution to that pixel is deemed to belong to background model, as foreground otherwise. Each distribution represented by its mean and variance as floating point numbers.

The work in [42] proposed an hardware implementation of the MoG method by simplifying the formulations using look-up-tables (LUTs) which results in an FPGA-based circuit outperforming its counterparts as well as an ASIC baseline for further research. It is implemented on FPGA and ASIC UMC-90 nm process, and achieved 60 fps at full-HD resolution with 33.2 pJ/pixel power performance.

$W_4$  (Who? When? Where? What?) is a widely used method in surveillance systems [43] In this method, background model is compound of minimum ( $\mu_{min}$ ), maximum ( $\mu_{max}$ ) and largest absolute difference ( $D_{max}$ ). A pixel at a position *i*, *j* is determined to be foreground if it satisfies one of the following inequalities:

$$|I(i,j) - \mu_{min}(i,j)| > D(i,j) \qquad \text{or} \qquad |I(i,j) - \mu_{max}(i,j)| > D(i,j)$$

(3.4)

There are also some methods which includes several methods at the same time. In [44], authors benefit from both frame difference and  $W_4$  methods. This two approach is implemented seperately and the outputs are combined with a logical OR operation.

One of the recent background subtraction algorithms for embedded vision is EBSCam [45]. This method is based on the suppression of the variation of the background mode. It provides a competitive accuracy with better hardware efficiency in terms of both area and speed. In this method, for each pixel location 90 bits need to be stored.

A memory-efficient and light-weight foreground detection method is presented in [46]. Although this method needs less memory for each pixel, it is robust against lighting variations and non-static background. Method selectively updates the background model with an automatically adaptive rate, thus can adapt to rapid changes. Pixels are not treated individually, and information about the neighbours is incorporated into decision making. Instead of building a mathematical model for each pixel location, this method observes the state changes being

Figure 3.3 - Moving object detection pipeline

between background and foreground in the pixel position and its neighbours. If the number of state changes exceeds a threshold, that pixel marked as a non-reliable pixel. For the foreground pixel decision, reliability of the pixel and its neighbours are taken into consideration.

Background subtraction produces a binary image shows the foreground pixels. This binary data can be processed by a connected component labeling block, in order to group the pixels which belongs the same object. Although there are many efficient solutions of the connected component labeling problem in software, their iterative process needs to access the binary image several times. Moreover, at least one binary frame must be stored in the memory. Thee Hoshen-Kopelman algorithm [47] applies two passes over the image. In the first pass, it assigns incremental numbers as temporary labels and finds the equivalent pixels. In the following second pass, it replaces each temporary label by the smallest label of its equivalence class.

More hardware friendly approaches are also presented in the literature. In [48], authors propose a real-time blob analysis methods by using only one single pass, and implement it on the FPGA. Before the operation, the pixels are compressed by a run length coding. A linked list based FPGA implementation is [49]. Another example of the single-pass methods is presented in [50] and [51]. This method requires less memory than the alternatives, and can reach high throughput.

Since our smart camera concept utilizes an external vision sensor chip, sensor level processing is not an option. Instead, we target to have a with a low complexity design by processing the pixel stream reducing the memory bandwidth and storage requirements. Therefore, similar to [46], we compute the number of switches between background and foreground for each pixel, to determine its reliability. Foreground detection takes into account the reliability information of the pixel and its neighbours. In addition to this, thanks to hardware centric approach and pixel processing on-the-fly, we reach high accuracy results with very low memory and power requirements. Moreover, we incorporate the background subtraction block with a morphological filtering and connected component labeling blocks, to give clean results ready to be processed.

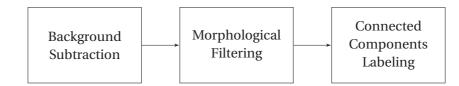

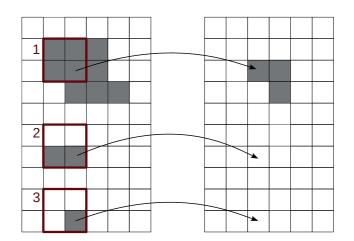

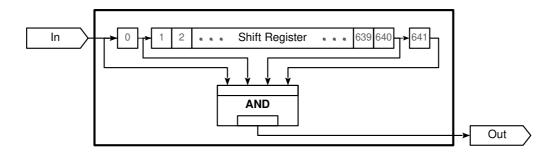

This moving object detection block is connected to the pixel bus, and when a new pixel is received, its data directly feed the processing pipeline. As presented in Figure 3.3, the moving object detection block constitutes of background subtraction, morphologic filtering MF and connected components labeling blocks. Background subtraction block creates a binary image from the difference of the current frame and the background model. This binary result directly feeds a shift register of the morphologic filter which removes the shapes of dimensions smaller

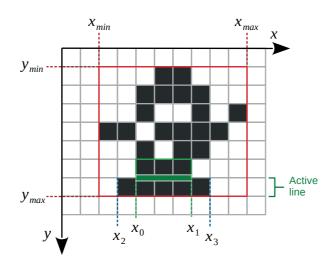

than  $2 \times 2$ . Non-filtered binary values are evaluated by the connected component labeling block. It determines if a pixel belongs to a previously found object or a new one and accordingly updates the results. The output of the moving object detection process gives the location of the objects and their boundary boxes.

This integrated method creates the metadata which is the positions and dimensions of the moving objects. In total, it requires 18 bits per pixel for background model, and 5 binary line buffers. Since it is based on the on-the-fly processing, the latency is minimum. As soon as a moving object is detected, its information is immediately sent to the metadata bus without waiting end of the frame. In the following subsections, we explain the methods in the pipeline in detail.

#### 3.2.1 Background Subtraction

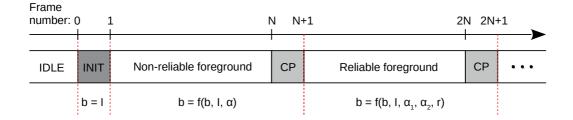

In the background subtraction block, two main operations are performed: (1) creating and updating the background model, (2) evaluation of the pixels as background or foreground. This two operations changes depending on the information level of the system. From the initialization signal, states of the frame can be illustrated in Figure 3.4. Normally, this hardware remains in IDLE state when the operation is not necessary, or lack of power. With a trigger signal, it switches to INIT state where the first captured frame is set as the background for fast adaptation:

$$\mu_t(i,j) = I_t(i,j) \tag{3.5}$$

where  $\mu_t(i, j)$  is background model for the pixel location *i*, *j*, and  $I_t(i, j)$  is gray level pixel intensity of the captured frame. After the first frame, absolute value of the difference of the

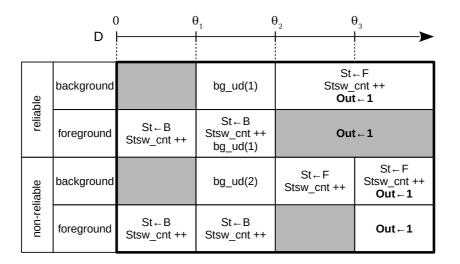

Figure 3.4 - Frame states for background subtraction block

intensity of a pixel position (*i*, *j*) and the value at the background model in the same pixel position is:

$$d = |I_t(i, j) - \mu_{t-1}(i, j)|$$

(3.6)

If the difference d is smaller than a threshold  $\theta_1$ , it means that there is not a significant change in the background model, and the background does not updated. It prevents unnecessary memory access and switches, thus power consumption is reduced down. Otherwise, it is updated by running Gaussian average:

$$\mu_t(i,j) = \begin{cases} \mu_{t-1}(i,j), & \text{if } d < \theta_1 \text{ or } d > \theta_2 \\ \alpha \mu_{t-1}(i,j) + (1 - \alpha I(i,j)), & \text{otherwise} \end{cases}$$

(3.7)

where  $\alpha$  is an ampirical pre-defined learning rate, and selected as  $2^{-N}$  for hardware efficiency. If this difference *d* exceeds a threshold  $\theta_2$ , status of the pixel is determined as foreground:

$$s = \begin{cases} 1, & \text{if } d > \theta_2 \\ 0, & \text{otherwise} \end{cases}$$

(3.8)

In this state, there is no reliability information. Therefore foreground output will always be 0. But this information is used to compute the number of the state changes of each pixel:

$$r_{c,t}(i,j) = \begin{cases} r_{c,t-1}+1, & \text{if } s_t(i,j) \oplus s_{t-1}(i,j) \\ r_{c,t-1}, & \text{otherwise} \end{cases}$$

(3.9)

where  $r_{c,t}(i, j)$  is a register which is incremented if there is a state change. A logical *XOR* operation applied on current and previous states gives the state change, and in this case state switch register is incremented by one.

When the frame counter reaches *N*, the system switches to checkpoint state and decides the reliability of the pixels. If the number of state switches exceeds the threshold  $\theta_r$ , then it is determined as it switches too much and does not give a reliable information:

$$r(i,j) = \begin{cases} 1, & \text{if } r_c(i,j) < \theta_r \\ 0, & \text{otherwise} \end{cases}$$

(3.10)

where r stands for reliability bit of the pixel. System resets the register which keeps the number of state switches  $r_c$ . The next N frames are evaluated according to this reliability information.

After processing the first checkpoint frame, having the reliability data of the pixels enable more accurate background model and foreground information. The evaluation operation is summarized in Figure 3.5. In this state, background update is a function of the difference d, and the reliability r.

$$\mu_{t} = \begin{cases} \mu_{t-1}, & \text{if } d < \theta_{1} \\ \alpha_{1}\mu_{t-1} + (1-\alpha_{1})\mu_{t-1}, & \text{if } d > \theta_{1} \text{ and } r = 1 \\ \alpha_{2}\mu_{t-1} + (1-\alpha_{2})\mu_{t-1}, & \text{if } d > \theta_{1} \text{ and } r = 0 \end{cases}$$

(3.11)

where  $\alpha_1$  and  $\alpha_2$  are update rates such that  $\alpha_1 > \alpha_2$ . By this way, small changes in reliable pixel positions are updated faster than the non-reliable pixel positions, because the confidence

Figure 3.5 - Advanced evaluation of the pixels

level of the coming pixel is higher.

For a reliable pixel position, if the difference exceeds the threshold  $\theta_2$ , state output is 1. However, for a non-reliable pixel position, it is already expected to oscillate background and foreground. Therefore, the system filters this change. In this case, in the non-reliable areas the output will be masked, even if there is a significant abnormal change. In order to cover this case, we define another threshold  $\theta_3$ , to detect the movements in non-reliable areas. This threshold is determined during the first non-reliable foreground operation, by storing the maximum difference for each pixel position. Output *s*<sub>out</sub> is given in the following equation:

$$s_{out} = r.(d > \theta_2) + \overline{r}.(d > \theta_3) \tag{3.12}$$

One of the main target of this method is keeping the memory allocation and access minimum. To reach this goal, we store 18-bit words for each pixel as shown in Figure 3.6. Most of the SRAMs in the market is designed as 9, 18 or 36 bit words, therefore, 18 bit selection suits well the available memories. The first 8 bits keep the background model of the pixel. This data is used to compute the difference *d* in the Equation 3.6 The next 5 bits stores the number of switching activities. Reliability and status occupy one bit each. The final 3 bits are dedicated to maximum difference for non-reliable pixels. Before each incoming pixel captured from the pixel bus, its information must be requested from the memory and be ready for the evaluation process. After the evaluation, pixel data on the memory may be updated. However, if the information stored in the memory location does not change, then it is not needed to update the information. The situations which does not require a memory write request is marked as gray boxes in Figure 3.6.

Sometimes a moving a foreground object appears in the scene but then it stops and keep its position for a long time. After a point, it is better to evaluate this pixel as a part of background.

| Background |  |  |  |  |  | 904 | activity |  | Reliability | Status | Maximum<br>Difference |  |  |

|------------|--|--|--|--|--|-----|----------|--|-------------|--------|-----------------------|--|--|

Figure 3.6 - Content of a memory row stores information of one pixel

Because, this moving object information is already produced and sent to the application unit. Re-computation of this area creates unnecessary signal switches without a useful information. Therefore, we update the background with a small update rate.

This background subtraction method brings several advantages in terms of energy consumption. We can formulate the total energy requirement of a general background subtraction operation based on the frame difference method as in the following:

$$E_{bs} = E_{op} + E_{cw} + E_{cr} + E_{bw} + E_{br}$$

(3.13)

where  $E_{cw}$  and  $E_{cr}$  are the energy consumption required to write and read the current frame, while  $E_{bw}$  and  $E_{br}$  are the ones to update/write and read the background model respectively and  $E_{op}$  is the energy used for the computation. In our case, since the pixel stream is evaluated on-the-fly, the energy consumption due to read and write operations, i.e.  $E_{cw}$  and  $E_{cr}$  are eliminated. Moreover,  $E_{bw}$  involves only when the background is updated. For most of the cases,  $E_{bw}$  does not contribute which also reduces the total energy consumption.

Another important advantage is reduced memory space. While the memory requirement per pixel in average more than 300 bits in [41], and more than 400 bits in [52]. In the work [46] which is also our starting point is needs to store 2 integer number in addition to pixel data. Our hardware oriented approximation lead us to achieve 18 bits per pixel and background data for each pixel can be stored in a single cell of 18-bit configurations of the SRAMs.

#### 3.2.2 Morphologic Filter