# Advances in the characterization of nanowire photovoltaic devices

## THÈSE N° 8884 (2018)

PRÉSENTÉE LE 2 NOVEMBRE 2018

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR LABORATOIRE DES MATÉRIAUX SEMICONDUCTEURS PROGRAMME DOCTORAL EN SCIENCE ET GÉNIE DES MATÉRIAUX

## ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

#### PAR

## **Dmitry MIKULIK**

acceptée sur proposition du jury:

Prof. P. Bowen, président du jury Prof. A. Fontcuberta i Morral, directrice de thèse Prof. P. McIntyre, rapporteur Dr E. Alarcón Lladó, rapporteuse Dr F.-J. Haug, rapporteur

To my lovely wife, Liza,

To my sweet daughter, Emilia,

And to my wonderful parents...

## Acknowledgements

Firstly, I would like to thank my advisor, Anna Fontcuberta i Morral, who believed in me 4 years ago and invited to work on the completely new topic for me – nanowire solar cells. You gave me an opportunity to return back to science after several years in the industry, for which I am immensely grateful. I appreciate all you time and ideas, motivation and expertise, you gave to me during these 4 years. The amazing atmosphere in the lab that I found from the beginning of my PhD is totally your merit.

I would like to thank Esther Alarcon Llado for giving me a lot of advice during my first year at EPFL. Your expertise in photovoltaics helped me a lot to start smoothly and give the first results very soon. Moreover, with your great support we made a fantastic collaboration on C-AFM analysis, which otherwise would not be possible.

Thanks to Paul McIntyre, for providing me an opportunity to join your team at Stanford University during 9 months in 2017. This internship was successful not only from the scientific point of view, but also gave me a great experience to work in one of the best universities in the world and to feel the energetic atmosphere of your group.

Thank to Franz-Jozef Haug and Christophe Ballif from PV lab at EPFL for your advices and help with the measurements and fabrication of solar cells. Working on new type of solar cells without support from PV lab would be much harder.

I acknowledge Paul Bowen for finding time and accepting to preside in my committee.

A big thanks to Pablo Romero-Gomez, whose arrival to LMSC certainly helped me to finalize my research and write a thesis. Your motivation and creativity are priceless for me.

This work was full of collaborations and I would like to thank all my collaborators - Andrew Meng and Kechao Tang from Stanford, Maria Ricci from Cambridge, Mikhail Mintairov from Ioffe institute, Josua Stuckelberger from PV lab at EPFL. Your knowledge in different areas of science helped a lot during my research.

Thanks to all former and current member of LMSC, including Jelena, Eleonora, Francesca, Federico, Alberto, Yannik, Gozde, Heidi, Martin, Luca, Mehdi, Wonjong, Lea, Jean-Baptiste, Akshay, Elias, Simon, Anna, Rajrupa, Monika and many others. It was a great time together. I will miss this friendship atmosphere!

A special acknowledge goes to the funding sources, supporting my research at EPFL – NanoTera and Swiss National Science Foundation. Thanks to CMi staff for being kind and supportive every time I made a mess in the cleanroom (especially to Zdenek and Patrick).

Finally, I would like to thank all my friends for helping to achieve perfect work-life balance during PhD.

Thanks to my parents, who convinced me to stay in the science at the beginning of my academic career. This would not have been possible without your great support.

## Acknowledgements

Last but most important, thanks to Liza, my lovely wife, and my sweet Emilia, who accompany me around the world and make life easy and fun. You are my biggest achievement in life.

Dmitry Mikulik

Lausanne, 8th of August 2018

## **Abstract**

III-V nanowires (NWs) have a great potential for solar energy applications due to their diameter-dependent optical properties, which may enhance absorption of light. In addition, core-shell radial p-i-n structures, in which the direction of light absorption is orthogonal to the carrier collection, can provide efficient carrier collection. The main goal of this thesis is the experimental study of the challenges of NW-based solar cells, related to materials and device fabrication.

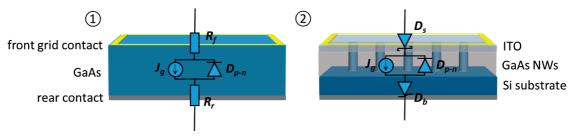

In the first part of the thesis, we present an analysis of where the electrical losses can be originated. By applying an equivalent circuit analysis approach, we classified them into three main groups: (i) the non-uniformity of NWs which may result in a reduction of the parallel resistance, (i) potential barriers originated at the different materials interfaces in the solar cell structure may result in an increase of the series resistance or addition of a second diode and (iii) surface recombination resulting in the reduction of the open-circuit voltage. In this thesis, we propose separate strategies to characterize and tackle these factors.

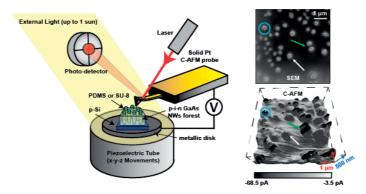

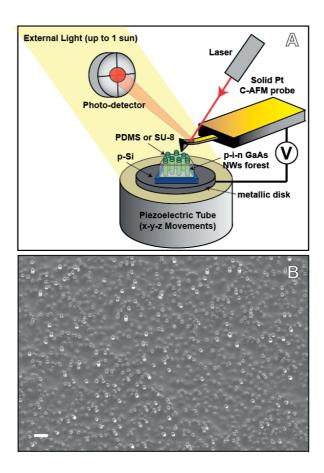

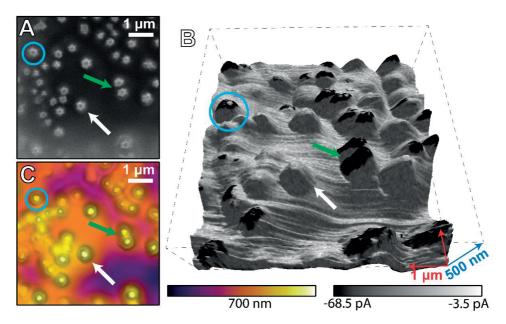

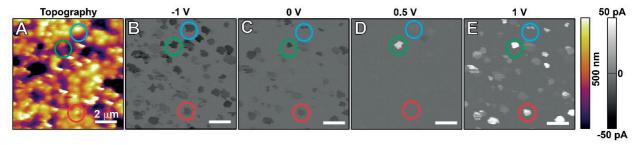

The electric scheme of a NW-based solar cell consists of an ensemble of p-n junctions connected in parallel. We show how conductive-probe atomic force microscopy, C-AFM, is an essential tool for the characterization and optimization of these parallel-connected NW devices. We demonstrate topography and current mapping of the NW arrays, combined with current-voltage (IV) measurements of the individual NW junctions from the ensemble. Our results provide discussion elements on some of the factors limiting the performance of a NW-based solar cell, such as uniformity and photosensitivity of the individual NW p-n junctions within the array, and thereby a path for their improvement.

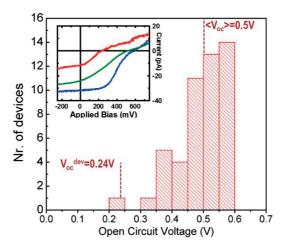

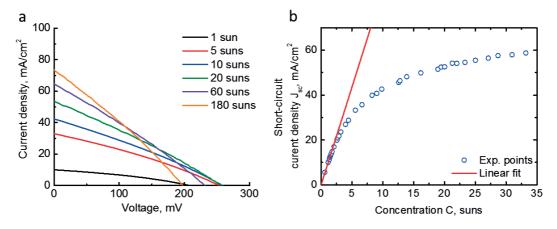

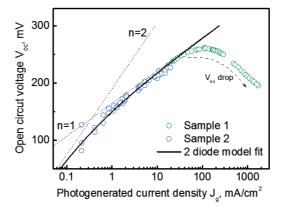

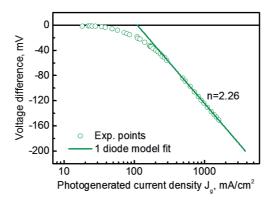

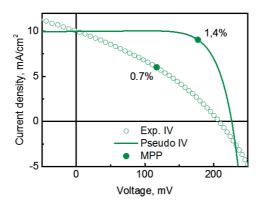

Besides parallel losses due to uniformity issues, barriers in the carrier collection through the various heterointerfaces composing the device is discussed. To analyze it, we illuminate GaAs NW-based solar cells at different levels of light intensity and extract IV characteristics. This analysis helps to separately study the NW p-n junction response and the series resistance. The high series resistance of the NW-ensemble device can be attributed to the following interfaces: 1) GaAs-ITO, forming a photoactive Schottky diode, which suppresses the p-n junction at high concentrations of light, and 2) Si-GaAs heterojunction, disturbing the flow of majority carriers.

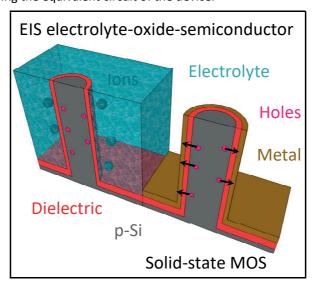

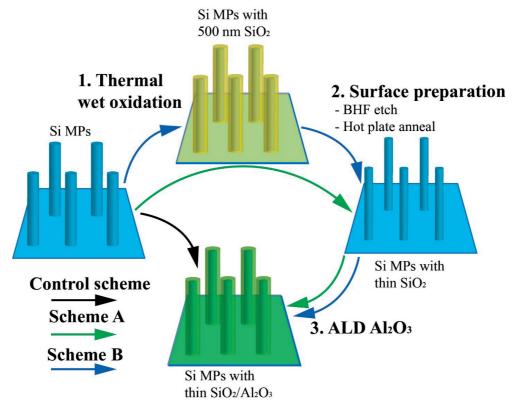

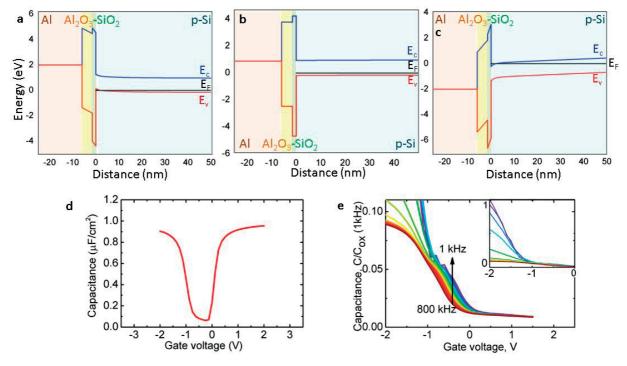

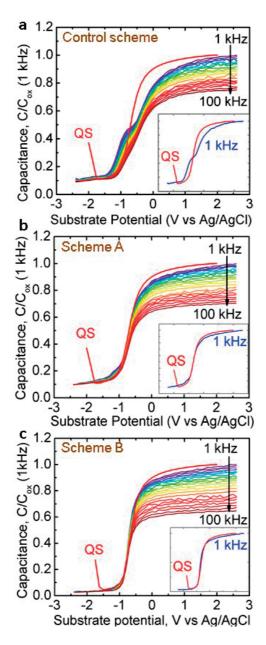

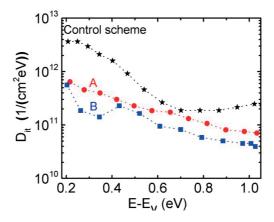

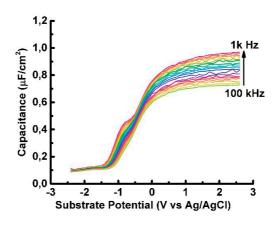

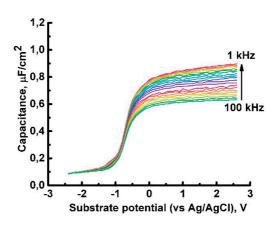

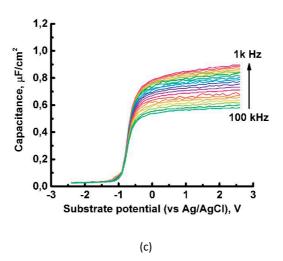

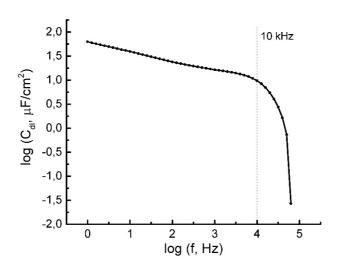

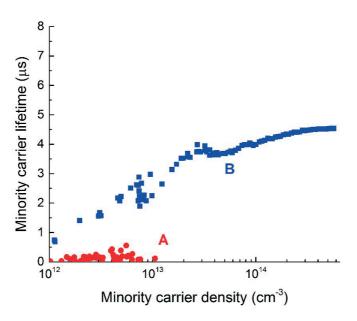

Finally, the characterization of surface passivation in high-aspect-ratio nano/micro structures is addressed by electrochemical impedance spectroscopy (EIS). The method is applied to Si micropillars, as a proof-of-concept prior to the application to III-V nanowires. We tested structures passivated by a dielectric layer. The effect of different surface treatments on the interface state density were quantified by the analysis of the capacitance-voltage and conductance-voltage characteristics. This method allows the electrical measurements on rough vertical surfaces, which would otherwise suffer from high gate leakage currents if tested using solid-state metal-insulator-semiconductor scheme.

The results and characterization methods, demonstrated in this work, contribute to the overall efforts of the scientific community on how to reveal the main engineering challenges in NW-based solar cells. It thus paves the way to approach the fundamental conversion efficiencies predicted by theory.

## Abstract

## Keywords

Nanowire, solar cells, III-V, integration of III-V on silicon, electrical losses, conductive atomic force microscopy, electrochemical impedance spectroscopy, surface recombination, surface passivation

## Résumé

Les nanofils (NFs) III-V ont un grand potentiel dans des applications dans le domaine de l'énergie solaire grâce à leurs propriétés optiques qui dépendent de leur diamètre, ce qui peut améliorer leur absorption de la lumière. De plus, des structures p-i-n radiales en géométrie noyau-enveloppe, dans lesquelles la direction de l'absorption de la lumière est orthogonale à celle de la collecte des porteurs de charge, peuvent fournir une collecte de porteurs efficace. Le but principal de cette thèse est l'étude expérimentale des défis des cellules solaires basées sur des nanofils portants sur les matériaux et la fabrication de dispositifs.

Dans la première partie de la thèse, nous présentons une analyse des sources de pertes électriques. En utilisant l'approche des circuits équivalents, nous les avons classés dans trois groupes : (i) la non-uniformité des NFs, qui peut causer une réduction de la résistance parallèle, (ii) les barrières de potentiel présentes aux différentes interfaces entre les matériaux dans la structure de la cellule solaire, qui peuvent causer une augmentation de la résistance en série ou l'ajout d'une seconde diode et (iii) les recombinaisons de surface, qui peuvent réduire la tension à circuit ouvert. Dans cette thèse, nous proposons différentes stratégies pour caractériser et traiter ces facteurs.

Le schéma électrique d'une cellule solaire à NFs consiste en un assemblage de jonctions p-n connectées en parallèle. Nous montrons comment la microscopie à force atomique avec sonde conductrice, C-AFM, est un outil essentiel pour la caractérisation et l'optimisation de ces dispositifs à connections parallèles. Nous montrons une cartographie de la topographie et du courant des grilles de NFs combinée avec des caractérisations courant-tension de jonctions de NFs individuels parmi ceux cartographiés. Nos résultats révèlent des éléments de discussion sur certains des facteurs limitants la performance de cellules solaires à NFs, tels que l'uniformité et la photosensibilité de jonctions p-n individuelles de NFs dans la grille et par conséquent une direction pour leur amélioration.

En plus des pertes dues aux problèmes d'uniformité, des obstacles à la collecte de porteurs au travers des différentes hétérointerfaces formant le dispositif sont discutés. Pour les analyser, nous illuminons les cellules solaires à NF de GaAs à différentes intensités et mesurons les propriétés courant-tension. Cette analyse permet d'étudier la jonction p-n du NF et la résistance en série séparément. La grande résistance en série des dispositifs avec grilles de NFs peut être attribuée aux interfaces suivantes : 1) GaAs-ITO, formant une diode Schottky photoactive qui supprime la jonction p-n à hautes concentrations de lumière, et 2) hétérojonction Si-GaAs, perturbant l'écoulement des porteurs majoritaires.

Finalement, la caractérisation de la passivation de surface dans les nano- et microstructures à grand ratio d'aspect est abordée par spectroscopie électrochimique à impédance. La méthode est appliquée à des micropiliers de Si comme preuve de concept avant d'être utilisée sur des NFs III-V. Nous avons testé des structures passivées par une couche diélectrique. Les effets de différents traitements de surface sur la densité des états d'interface ont été quantifiés par l'analyse des caractéristiques de capacité-tension et conductance-tension. Cette méthode permet des mesures électriques sur des surfaces verticales rugueuses qui endureraient dans d'autres cas de forts courants de perte s'il étaient testés dans un schéma métal-isolant-semiconducteur.

Les résultats et méthodes de caractérisations, démontrés dans cet ouvrage, contribuent à l'effort général de la communauté scientifique de déterminer les défis d'ingénierie principaux des cellules solaires à NFs. Cela trace le chemin pour approcher les rendements de conversion fondamentaux prédits théoriquement.

## Résumé

## Mots-clés

Nanofil, cellules solaires, III-V, intégration de III-V sur silicium, pertes électriques, microscopie à force atomique conductrice, spectroscopie d'impédance électrochimique, recombinaison de surface, passivation de surface

## Contents

| Acknov    | vledg  | ements                                                                          | V   |

|-----------|--------|---------------------------------------------------------------------------------|-----|

| Abstrac   | ct     |                                                                                 | /ii |

| Keywoı    | rds    | \                                                                               | /ii |

| Résum     | é      |                                                                                 | ix  |

| Mots-c    | lés    |                                                                                 | х   |

| Conten    | ıts    |                                                                                 | хi  |

| List of A | Abbre  | viationsx                                                                       | iii |

| List of F | Figure | ·sx                                                                             | iv  |

| List of 7 | Tables | 51                                                                              | .6  |

| List of E | Equat  | ions1                                                                           | .6  |

| Chapte    | r 1    | Introduction                                                                    | L7  |

| 1         | l.1    | Photovoltaics                                                                   | ١7  |

| 1         | 1.2    | Optical absorption in NW arrays1                                                | .8  |

| 1         | 1.3    | Multi-Junction and III-V on Si approaches                                       | 21  |

| 1         | L.4    | Radial p-n junction with NWs                                                    | 22  |

| 1         | L.5    | The main limiting factors in solar cell operation                               | 23  |

| 1         | L.6    | Objectives and outline of this Thesis                                           | 24  |

| Chapte    | er 2   | Parallel and series losses in NW-based solar cells                              | 27  |

| 2         | 2.1    | Growth of semiconductor nanowires                                               | 28  |

| 2         | 2.2    | Surface passivation                                                             | 31  |

| 2         | 2.3    | Post growth processes                                                           | 32  |

|           |        | 2.3.1 Polymer embedding                                                         | 32  |

|           |        | 2.3.2 Electrical contacts to NW based devices                                   | 3   |

| 2         | 2.4    | Standard electrical characterization methods of NW based solar cells structures | 34  |

|           |        | 2.4.1 Device current-voltage (I-V) curve characterization                       | }5  |

|           |        | 2.4.2 Single NW I-V curve characterization                                      | 36  |

## Contents

| Chapter 3    | Electrical characterization of parallel and series losses in NW based solar cells 39       |

|--------------|--------------------------------------------------------------------------------------------|

| 3.1          | Parallel losses characterization using Conductive-probe Atomic Force Microscopy (C-AFM) 39 |

|              | 3.1.1 Paper included in this section                                                       |

| 3.2          | Characterization of losses linked to series resistances using light concentration 57       |

|              | 3.2.1 Paper included in this chapter59                                                     |

| Chapter 4    | The use of Electrochemical Impedance Spectroscopy for surface states study71               |

| 4.1          | Paper included in this chapter                                                             |

| Chapter 5    | Conclusions and Outlook                                                                    |

| 5.1          | Future Outlook                                                                             |

| Appendix     | 91                                                                                         |

| Bibliograph  | y101                                                                                       |

| List of publ | ications                                                                                   |

| Resume       |                                                                                            |

## List of Abbreviations

**PV** photovoltaics

**SQ** Shockley-Queisser

**NWs** nanowires

ARC anti-reflective coating

MBE molecular beam epitaxy

**MOCVD** metal-organic chemical vapor deposition

ALD

VLS vapor-liquid-solid

SAG selective area growth

HAR high-aspect ratio

**C-AFM** conductive atomic force microscopy

EIS electrochemical impedance spectroscopy

IV current-voltage

CV capacitance-voltage

**SEM** scanning electron microscopy

EBIC electron beam induced current

**PDMS** polydimethylsiloxane

**TCO** transparent conductive oxide

MOS metal-oxide-semiconductor

## List of Figures

| Figure 1-1 Simulations of light absorption (a) and absorption cross-sectional area (b) in a 2.5 $\mu$ m standing GaAs nanowire that is fully embedded in SU-8 on a silicon substrate. Reprinted by permission from Macmillan Publishers Limited: Nature Photonics [22][COPYRIGHT] (2013)                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Figure 1-2</b> a) GaAs nanowire array absorption simulated by FDTD; b) Calculated total photocurrent given by the simulated absorbance and surface coverage as a function of pitch distance. Calculations performed by E. Alarcon-Lladó© 2016 IEEE [30] 21                                                                                |

| Figure 1-3 Different types of the NW geometry: (a) Radial junctions NW array; (b) Axial junctions NW array; (c) Substrate junctions NW array. Green and blue colors represent different type of doping                                                                                                                                       |

| Figure 1-4 The main limiting factors in solar cells24                                                                                                                                                                                                                                                                                        |

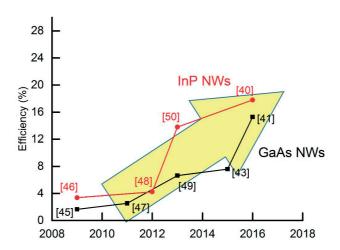

| Figure 1-5 Best III-V NW based solar cell efficiencies vs Time [40,41,43,45–50].25                                                                                                                                                                                                                                                           |

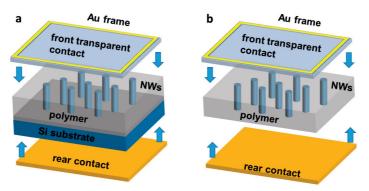

| <b>Figure 2-1</b> Two ways to obtain large area commercial NW solar cells: <b>(a)</b> rigid device on Si substrate; <b>(b)</b> flexible device utilizing NW-polymer composite27                                                                                                                                                              |

| Figure 2-2 Equivalent electrical scheme of the NW based solar cell                                                                                                                                                                                                                                                                           |

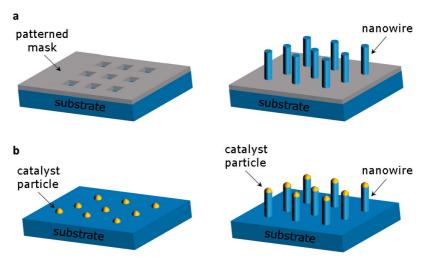

| Figure 2-3 Schematic illustration of SAG (a) and VLS (b) growth methods of semiconductor NWs                                                                                                                                                                                                                                                 |

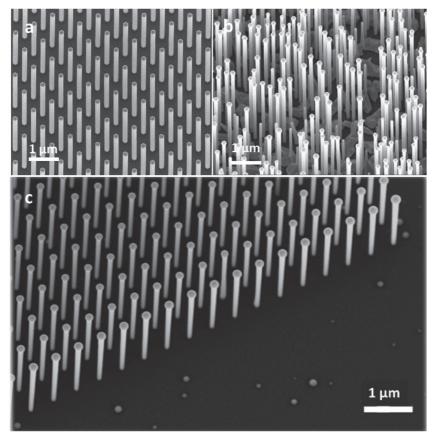

| Figure 2-4 SEM images showing the uniformity of GaAs NWs grown by SA-MOVPE on GaAs substrate (a), self-assembled Ga-catalysed VLS MBE on Si substrate (b) and Ga-catalysed VLS MBE on Si substrate with hole pattern (c) [image by Wonjong Kim] methods                                                                                      |

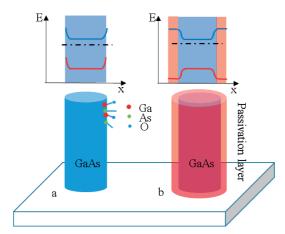

| <b>Figure 2-5</b> Position of the conduction (blue) and valence bands (red) across a NW diameter for: <b>(a)</b> un-passivated GaAs NW and <b>(b)</b> a GaAs NW passivated with a thin layer of AlGaAs. Below, the 3D drawing of the structures are shown. As-dangling bonds and GaOx are represented at the surface of the un-passivated NW |

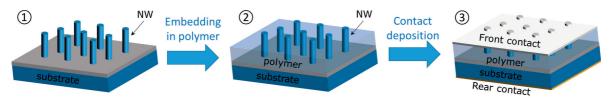

| Figure 2-6 Process flow of post-growth fabrication of NW based solar cell32                                                                                                                                                                                                                                                                  |

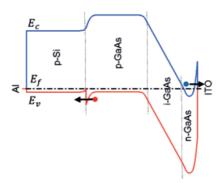

| <b>Figure 2-7</b> One-dimensional energy band diagram of the solar cell structure Al/p-Si/p-GaAs/i-GaAs/n-GaAs/ITO along the NW axis (in dark at equilibrium conditions). Electron (blue circle) and hole (red circle) flow is indicated34                                                                                                   |

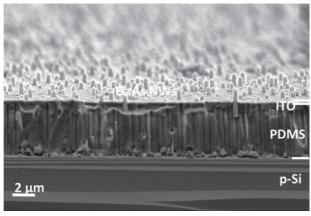

| Figure 2-8 Cross-sectional SEM image of GaAs NW based solar cell35                                                                                                                                                                                                                                                                           |

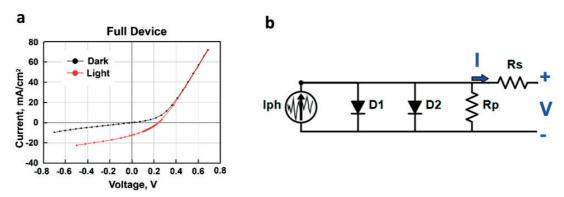

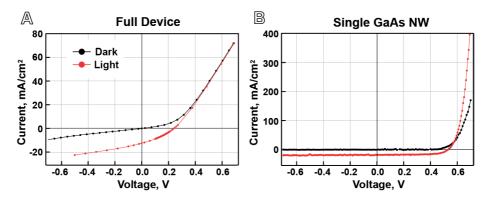

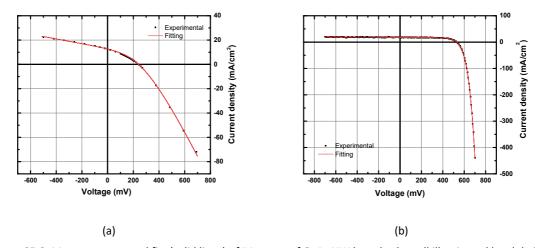

| Figure 2-9 (a) IV curve characterization (dark and light) of GaAs NW based solar cell [78]; (b) Double diode model equivalent scheme                                                                                                                                                                                                         |

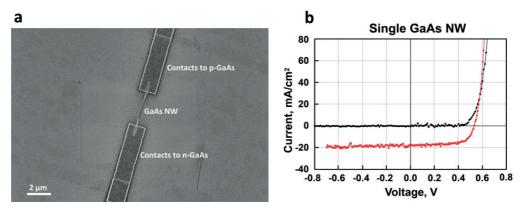

| <b>Figure 2-10 (a)</b> SEM image of single GaAs NW with 2 contacts scheme; <b>(b)</b> IV curve characterization of single GaAs NW [78]37                                                                                                                                                                                                     |

## Contents

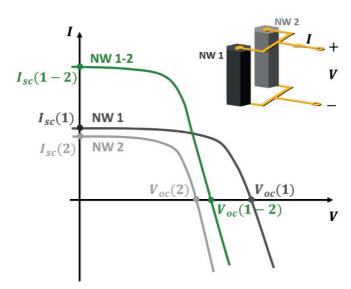

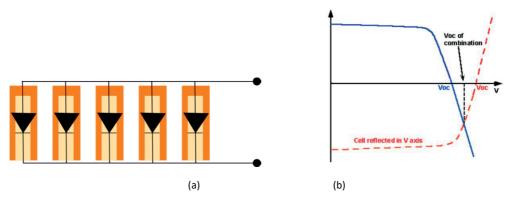

| Figure 3-1 Schematic illustration of the electrical device consisted of two NW p-n                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| junctions connected in parallel with corresponding I-V curves under the light. The green-                                                                                                                                    |

| coloured IV curve of the device shows the drop of $V_{oc}$ due to lowest performing NW 2.                                                                                                                                    |

| 40                                                                                                                                                                                                                           |

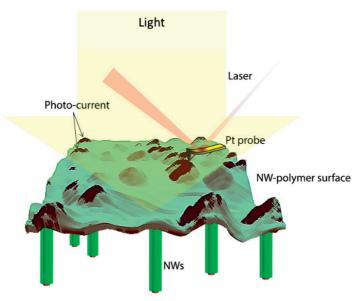

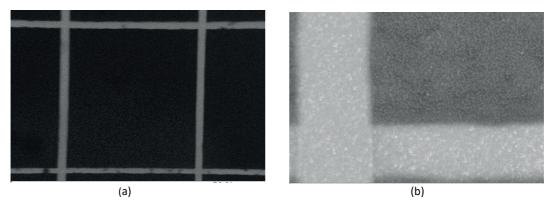

| <b>Figure 3-2</b> Conductive AFM analysis of NW solar structure. The surface is constructed by overlaying of the current map over 3D topography map. Dark spots represent photocurrent obtained under the light at zero bias |

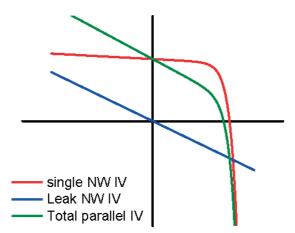

| <b>Figure 3-3</b> Illustrative light I-V curves of two single NWs p-n junctions – leaking and not - and combined device of two NWs connected in parallel42                                                                   |

| <b>Figure 3-4</b> A simplified scheme of the planar and NW-based solar cells together with its equivalent circuits: $\textcircled{1}$ - classic; $\textcircled{2}$ - with non-linear series effects57                        |

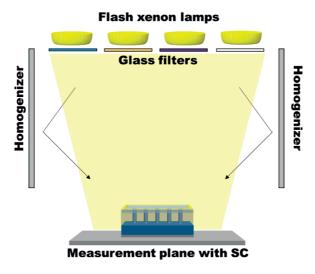

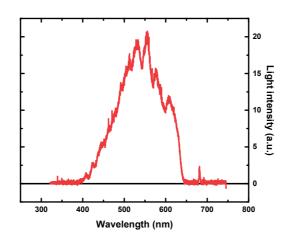

| Figure 3-5 Optical layout of flash illumination system                                                                                                                                                                       |

| <b>Figure 4-1</b> EIS and standard solid-state MOS characterization methods shown on HAR structures                                                                                                                          |

## Contents

| List of | Tables                                                                                                                                                                   |        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|         | <b>Table 1-1</b> Photovoltaic performance of III-V NW array devices. Pattern technical EBL – electron beam lithography, NIL – nano imprint lithography, PL – photolithog | raphy. |

|         | Table 2-1 Electrical losses in NW based solar cell due to fabrication issues35                                                                                           |        |

|         |                                                                                                                                                                          |        |

| List of | Equations                                                                                                                                                                |        |

|         | <b>Equation 1</b> - Short-circuit current and open-circuit voltage dependencies from concentration                                                                       | •      |

|         | Equation 2 - Open circuit voltage definition23                                                                                                                           |        |

## Chapter 1 Introduction

#### 1.1 Photovoltaics

Clean and renewable energy became increasingly necessary in the last decades, especially due to worldwide agreements such as the Kyoto Protocol (framework convention on climate change) [1]. The benefits of the renewable energy are obvious: less global warming [2], improved public health due to minimization of pollution, inexhaustibility of the energy, stable energy prices, reliability and resilience. Alongside other renewable technologies, conversion of solar light into electricity with photovoltaic (PV) technology is an attractive option for our future.

The photovoltaic effect was first observed by Edmond Becquerel in 1839 [3], while he was working with electrolytic cells, using platinum as both as anode and cathode. Measuring electric current between electrodes, he found its increase under the light compared to dark measurements. The practical use of this effect was only realized many decades later. In 1954, engineers of Bell Labs accidentally discovered photosensitivity of doped Si that led to the fabrication of first c-Si solar cells with efficiency of about 6% [4]. The era of solar cell development began. Modern solar cell systems can be adapted to different situations – from home use with small power needs, to large PV energy plants. Among other elements, the potential of this technology will rely on the availability of raw materials and on the cost for refining them, as the available quantities of raw materials on Earth for global PV capacities are limited [5]. Presently, many research groups in PV focus on optimizing both material consumption and conversion efficiency.

Conventionally, PV technologies have been divided into three generations, G [6]:

- G1 bulk, wafer based (e.g. c-Si, poly-c-Si)

- G2 thin film based (e.g. a-Si:H, μ-Si:H, CIGS, CdTe)

- G3 multi-junction, organic, dye-sensitized and nanostructure based

Today, the term of third generation, G3, has been generalized to next generation solar cells. Next generation photovoltaics aims at the increase of the efficiency at a lower cost or materials consumption. A large manifold of concepts are included in this next generation.

Nowadays, 90% of PV cell market is still accounted by the first generation Si based solar cells. Despite disadvantages of this technology such as the indirect energy band gap, silicon remains the most preferred material for PV. This is due to low cost, close to optimum value of the band gap and well-developed technology processing. Still, high-efficiency Si solar cells require very high quality, defect-free bulk material with large carrier mobilities and long minority carrier lifetimes that drastically increase manufacturing cost. With such requirements, the current record efficiency of 26.7% for a Si solar cell is almost approaching its theoretical limit [7]. However, this value is only relatively close to the Shockley-Queisser (SQ) limit of 33.7% for a single bandgap cell (optimum bandgap of 1.34 eV) [8]. Conversion efficiency in single-junction GaAs solar cells are closer to this limit, with an efficiency approaching 29% from Alta Devices [7]. One inconvenient of the GaAs technology is that the cost is much higher due to the scarcity and extraction costs of Ga.

In recent years, nano- and microstructures have been recurrently proposed in the absorber structure for next generation solar cells. As an example, the nanoscale texture of wafer surfaces decreases the reflectance of the surface allowing a better coupling of the incident light in the device [9–11]. Microstructuring of the surface can also enhance absorption of light by this principle and/or by changing the momentum of the incoming light through a grating coupler effect, thus reducing the effective thickness of the solar cell [12,13]. Furthermore, shortening of the minority carrier collection path reduces bulk recombination losses in nanostructure based p-n junctions [14].

The original way to increase efficiency of conventional single junction solar cells is implementing several p-n junctions composed of two or more semiconductor materials with different energy band gap. For example, epitaxially grown GaInP/GaAs/GaInAs/GaInAs multi-junction solar cells result in an efficiency above 45% under concentrating conditions [7]. Still, the fabrication process is technologically complicated and costly. One of the main challenges is the growth of the multilayer stack which requires multiple steps to reduce stress between layers with different lattice constants [15]. In addition, since the cells are being connected in series, the efficiency is dependent on the nature of the solar spectrum. The variation in the spectrum is relevant when using the same device in different latitudes, but also in different seasons and weather conditions [16]. Therefore, as an alternative to monolithic technology, wafer bonded and mechanically stacked configurations become more and more promising in multi-junction solar cell technology. Another strategy consists of merging different generations to build hybrid solar cells, such as a tandem device formed by a silicon bottom solar cell and a lead-halide perovskite device on top [17].

In summary, the main motivation of the ongoing research in PV is centered on improving the conversion efficiency of PV solar cells using novel approaches while reducing the use of the raw materials. Semiconductor nanowires (NWs) represent an extremely promising option for next generation solar cells. Due to its particular morphology and fabrication methods, NWs should also enable the fabrication of flexible or multiple junction solar cells. Next, main advantages of NWs for PV will be introduced, such as superior light absorption, band gap engineering and radial p-n junction configuration.

#### 1.2 Optical absorption in NW arrays

Several factors can prevent the full absorption of the incident light: parasitic absorption in the transparent and adjacent contacts, partial light reflection and finite thickness of the active material of the solar cell. The decrease thickness of the active material to reduce materials costs or increase carrier collection in the solar cell requires a new way to enhance absorption. In the last decade, the use of photonic principles and nanostructuring of materials has shown to be effective in increasing light collection in the active part of the device [18]. Nanophotonic light trapping can utilize arrays of nanoscale particles, wires or holes that enhance light absorption. Among all mentioned nanostructures, our focus here lies on NWs standing on a substrate.

Historically, the first experimental evidence of the advantages of using NWs in solar cells came from the demonstration of their anti-reflection properties [19]. Compared to the standard anti-reflective coating (ARC) strategy, an array of nanostructures provides an alternative approach. To be a broadband and angularly independent, ARC should consist of a multilayer stack with graded refractive index, which makes its fabrication complex and expensive. Nanostructuration is highly effective in both being thin and easily processed (e.g. black Si). The best Si nanostructures with nanocone shape maintain the absorption above 93% over a broad range of wavelengths and incident angle, compared to 64% for Si thin film [10].

The next step was to use nanostructures for light absorption as an active part of solar cell. For that, scientists utilized numerical simulations to discover new optical properties of nanostructured media.

Different rules than standard reflection, transmission and refraction laws, need to be applied for light propagation in structures of wavelength or subwavelength dimensions. In case of vertically oriented NWs, they can act both as a total reflection or leaky-mode waveguide, only the latter being efficient in coupling the incident light [20,21]. Thus, there is a photon energy dependent absorption due to the corresponding spectral dependence of these modes on the nanowire diameter and refractive index. The introduction of NWs in PV as an active material meant also a new geometrical concept of p-n junction formation. In addition to traditional planar (or axial in NW case) p-n junction, core-shell configuration can be realized. The pioneering idea of using semiconductor NW radial p-n junctions for solar cells was published in 2005 by the Atwater group [14]. In particular, they elucidated for the first time the advantages of radial p-n junctions compared to planar p-n junctions. The radial geometry of the p-n junction in a NW allows the orthogonalization of the light absorption and carrier collection and thus allows for independent optimization of light absorption and carrier collection.

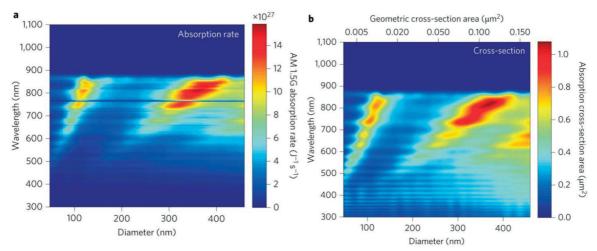

The light absorption efficiency of individual nanostructures can also be characterized by the so-called absorption cross-section. This value represents the ratio between the power absorbed in nanostructure and the nominal power flow per unit area for an incident plane-wave. A value of the absorption efficiency (cross-section area/geometrical area) above 1 indicates the existence of concentration effect. Krogstrup *et al.* showed enhancement of light absorption in single GaAs NW due to an effective light-concentrating property of the standing NW [22]. **Figure 1-1** shows simulations of light absorption and absorption cross-sectional area in a 2.5 µm standing GaAs nanowire that is fully embedded in SU-8 on a silicon substrate. Light absorption in the standing NW is enhanced by a factor of between 10 and 70 with respect to the equivalent thin film. As shown on **Figure 1-1a**, simulations of light absorption exhibit two main absorption enhancement branches. **Figure 1-1b** represents enhancement of absorption cross-section area compared to the geometrical cross-section area. A built-in light concentration up to 12 at photon energies slightly higher than the bandgap was found for a NW diameter of 380 nm.

**Figure 1-1** Simulations of light absorption (a) and absorption cross-sectional area (b) in a 2.5 μm standing GaAs nanowire that is fully embedded in SU-8 on a silicon substrate. Reprinted by permission from Macmillan Publishers Limited: Nature Photonics [22][COPYRIGHT] (2013)

In case of concentrated solar cells, in which focusing lenses are used to concentrate light. The concentration C has a direct influence on short-circuit current  $I_{sc}$  and  $V_{oc}$  through linear and logarithmic dependences, accordingly [23]:

$$I_{sc} = I_{sc}^{1}C$$

$$V_{oc} = V_{oc}^{1} + \frac{nkT}{a}\ln C$$

Equation 1 - Short-circuit current and open-circuit voltage dependencies from light concentration.

where  $I_{sc}^1$  and  $V_{oc}^1$  – short-circuit current and open-circuit voltage at 1 sun and n the ideality factor. Light concentration increases the carrier generation rate while leaving the equilibrium recombination rate unchanged. One should note here that the light-concentrating effect in NWs for photovoltaics application exhibits a more complicated nature. Recently, Mann  $et\ al.$  elucidated the principal difference between macroscopic light concentration and self-concentration in nano-photonics [24]. The absorption cross-section enhancement due to increased coupling of light in the nanowire may increase both generation and recombination rate. In this case, it should not play a role in increasing the  $V_{oc}$ . Mann  $et\ al.$  propose that  $V_{oc}$  may increase because of a reduction in the recombination rate by optimizing the light direction both in absorption and in emission (i.e. by reducing light absorption at oblique angles). By placing single NWs in array with the pitch in the order of the light wavelength, strong directive absorption enhancement at the band edge is observed due to the reduced symmetry of NW geometry (around 150 nm and 380 nm of NW diameter on **Figure 1-1**).

Light emission of the absorber into a solid angle larger than the incident light reduces the overall internal carrier concentration, thus limiting the maximum open-circuit voltage (radiative open-circuit voltage,  $V_{oc}^{rad}$ ) in the absence of non-radiative recombination. The effect of  $V_{oc}^{rad}$  increase due to the photonic effects in NWs was studied recently [25,26]. The explanation is similar to the theory developed by Yablonovitch *et al.* in which an efficient external luminescence is, counterintuitively, a necessity for approaching the SQ efficiency limit [27].

Overall, light absorption enhancement in NWs and its application on photovoltaics should be carefully studied and optimized in order to reach or surpass the SQ limit. Numerical simulations of single NW behavior under the light helps optimizing the nanowire dimensions in devices utilizing NWs as building blocks of nanoscale solar cells. For a realistic device, deterministic arrays of NWs should be fabricated to provide effective absorption of the sunlight over the whole area whilst minimizing materials utilization [28]. When the spacing between nanostructures is on the same scale as optical wavelengths (below 1  $\mu$ m), photonic crystal effects can play a role, bringing the potential to exceed the conventional ray optics absorption limit [29].

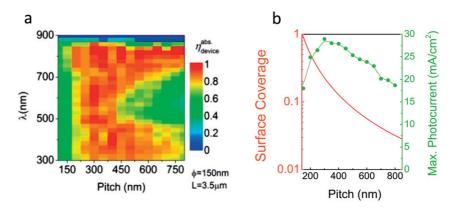

**Figure 1-2a** represents the results of numerical simulations of light absorption perpendicularly incident on an array of GaAs NWs with a diameter of 150 nm and 2 μm in length. The calculations were performed by Dr. Alarcon-Llado using Finite Difference Time Domain (FDTD) [30]. At the lowest pitch sizes, the NW array performs like a thin film under light illumination. By increasing the pitch, the absorption efficiency increases up to the highest values. Finally, as the spacing between the NWs is further increased, the array absorbs mostly on the low and high energy parts of the spectrum as it is the case single NWs. Based on FDTD simulations, maximum photocurrent vs pitch size can be calculated. **Figure 1-2b** shows surface coverage by NWs (orange line) and maximum photocurrent (green dots and line) vs pitch size on the same graph. At least 60% of maximum photocurrent can be achieved with only several percent of surface covered by NWs (at pitch size 800 nm). This calculation shows the potential in tandem design application with NW based solar cell on top, since a large portion of light will be able to transmit through the NW solar cell for the absorption in the bottom cell.

Figure 1-2 a) GaAs nanowire array absorption simulated by FDTD; b) Calculated total photocurrent given by the simulated absorbance and surface coverage as a function of pitch distance. Calculations performed by E. Alarcon-Lladó© 2016 IEEE [30]

## 1.3 Multi-Junction and III-V on Si approaches

In a semiconductor material photons with energy lower than the bandgap are not absorbed. In addition, the excess energy of high-energy photons above the bandgap is lost in thermalization. Considering the solar spectrum, AM 1.5, the bandgap 1.34 eV gives a maximum solar conversion efficiency of 33.7 % [8]. To increase this efficiency, one can stack together active layers with different band gaps. This minimizes both thermalization and transparency losses. The large band gap material is located on top of the solar cell, and small band gap material is used as a substrate, such as Si or Ge. Intermediate band gap materials can also be added to further increase the light absorption in the form of a triple or multiplejunction solar cell. Combining semiconductor materials with different band gaps into multi-junction solar cells leads to experimental solar conversion efficiencies beyond the theoretical SQ limit for one junction (38.8% for five-junction device under 1 sun [7]). This strategy is widely used in solar concentrating systems and other "niche" application such as solar panels in space, where fabrication cost, extremely high for such technology, is offset by the reduction in weight to efficiency ratio, which greatly reduces fuel related costs. For terrestrial applications, different combinations with low-cost perovskite materials have been intensively studied [31,32]. In case of NW technology, the perspectives of combining NW arrays and c-Si solar cell for tandem configuration were analyzed by Kandala et al [33]. Advantages of series connection compared to parallel connection of the sub-cells were depicted using detailed balance calculation. Later on, tandem technology using c-Si substrate with GaAs NWs on top was experimentally introduced by Yao et al [34]. In addition, theoretical conversion efficiency of almost 50% was calculated for multi terminal NW solar cell design with three different III-V material NW arrays grown on Si substrate [35]. The potential lower cost of fabrication different material NWs on cheap substrates compared to planar technology opens new avenues for the application of NWs in concentrating photovoltaics. However, the current experimental efficiencies for the tandem-junction design with NWs are still far below single p-n junction NW solar cell.

For a direct band gap semiconductor, such as GaAs, a few micrometers of active layer is enough for effective light absorption and a maximum conversion efficiency of 28.8% has been achieved by Kayes *et al* [36]. However, this achievement requires complexed and expensive technology in order to achieve perfect crystal quality in thin films. Moreover, expensive III-V substrates should be used for the epitaxial growth of device structures. NWs with high crystal quality can easily be obtained on cheaper substrates such as Si by standard epitaxial methods such as Molecular Beam Epitaxy (MBE) and Metal-Organic Chemical Vapor

Deposition (MOCVD) [37,38]. The possibility of combining III-V materials with Si thus opens up many new possibilities in multiple-junction solar cells [35].

To date the experimental efficiencies of NW-based solar cells are still far from the theoretical predictions. **Table 1-1** shows current best conversion efficiency values for III-V NW based solar cells. Taking in account results for planar solar cells, implementing multi-junction concept in NW geometry can significantly improve solar conversion efficiency. The tandem configuration for c-Si/GaAs NW solar cell is one of the first attempts in this direction.

| Material and       | Area (mm²) | Conversion | Open-       | Short-              | Fill   | Reference |

|--------------------|------------|------------|-------------|---------------------|--------|-----------|

| Pattern technology |            | efficiency | circuit     | circuit             | Factor |           |

|                    |            |            | voltage (V) | current<br>(mA/cm²) | (%)    |           |

| InGaAs (EBL)       | 0.81       | 7.1%       | 0.54        | 18.2                | 72.1   | [39]      |

| InP (NIL)          | 0.09       | 17.8%      | 0.765       | 29.3                | 79.4   | [40]      |

| GaAs (NIL)         | 1.08       | 15.3%      | 0.91        | 21.3                | 79.2   | [41]      |

| c-Si/GaAs NW       | 1          | 11.4%      | 0.956       | 20.6                | 57.8   | [34]      |

| Tandem (PL)        |            |            |             |                     |        |           |

**Table 1-1** Photovoltaic performance of III-V NW array devices. Pattern technology: EBL – electron beam lithography, NIL – nano imprint lithography, PL – photolithography.

## 1.4 Radial p-n junction with NWs

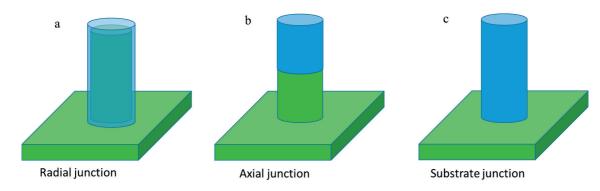

Conventional Si solar cells require thick Si layers to maximize light absorption. The charge carriers generated throughout the region must be transported by diffusion over the large distances to be collected efficiently. Different recombination processes might hinder collection. Ordered arrays of vertical NWs with radial junctions (like in **Figure 1-3a**) reduce the path for the photo-generated electrons-hole pairs to the electrodes, thereby improving charge collection. Still, one should note that NW solar cells can also be obtained using axial junctions or substrate junctions (see **Figure 1-3a-b**). In this case, charge carriers diffuse a longer path than in the radial configuration. As a consequence, surface passivation becomes key in order to obtain a good carrier collection [42].

**Figure 1-3** Different types of the NW geometry: (a) Radial junctions NW array; (b) Axial junctions NW array; (c) Substrate junctions NW array. Green and blue colors represent different type of doping.

**Figure 1-3** represents three different NW p-n junction geometries – substrate junction **(a)**, axial junction **(b)** and radial junction **(c)**. The arrays of NWs with radial junctions maintain all the advantages described above, including reduced reflection, extreme light trapping, radial charge separation, relaxed

interfacial strain, and single-crystalline synthesis on non-native substrates. Axial junctions lose the radial charge separation benefit but keep the remaining ones of radial junctions. Finally, substrate junctions lack the radial charge separation benefit and cannot be removed from the substrate to be tested as single-NW solar cells.

Still, both axial and radial p-n junction NW concepts are highly explored by different scientific groups. The ability to control doping and surface passivation in NWs is one of the key factor for the success of the devices. Simulations showed that NWs with axial junction configuration are more tolerant to doping variation than with radial configuration [43]. Low doping in the core of NW ("base" for radial junction) can lead to inversion of the carrier type caused by the shell doping. However, high doping of the core is not desirable due to reducing mobility and diffusion length. As a result, current records in NW solar cells all belong to axial configuration, which is more robust.

Surface recombination is another major concern for NW-base solar cells due to their high surface-to-volume ratio. Yu *et al* simulated the impact of surface recombination velocity on both axial and radial p-n junction NW arrays [42], and they concluded that the recombination rate at the surface for the same doping level is much higher in the axial configuration than in the radial case.

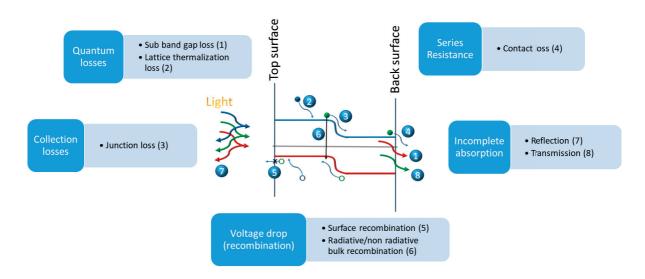

## 1.5 The main limiting factors in solar cell operation

The main limiting factors of energy conversion in solar cells were elucidated more than 50 years ago by Wolf et~al~[44]. They are the following: incomplete absorption, quantum loss (band gap), collection losses, voltage drop and dark saturation current, and resistive losses (from contacts). **Figure 1-4** schematically illustrates the main losses in solar cells directly on a schematic p-n junction band diagram. In short, when a photon is absorbed in the active region of solar cell, an electron in the valence band receives this energy and is excited to the conduction band. Afterwards, the electron and the hole created in the valence band after electron excitation are collected at the electrodes due to an internal electric field. However, several additional fundamental processes can occur. Process 1 and 2 correspond to sub-band gap absorption loss and loss of excess energy of high-energy photons to phonons. Junction loss (3) represents the energy loss caused by the voltage drop of the carriers from bandgap voltage to internal voltage of the junction. Non-optimized metal contacts lead to losses of carriers due to series resistance (4). Besides current loss (processes 3 and 4), voltage drop is observed due to recombination effects – surface and bulk recombination (5 and 6). It can be explained by direct dependence on the dark current  $I_{dark}$  and open circuit voltage  $V_{oc}$  as:

$$V_{oc} = \frac{kT}{q} \ln(\frac{I_{ph}}{I_{dark}} + 1)$$

Equation 2 - Open circuit voltage definition.

where k is the Boltzmann constant, T is the cell temperature, q is the electron charge and  $I_{ph}$  is the photocurrent. Dark current increases with the increase of recombination rate in solar cells. Finally, solar cell surfaces can reflect part of light, and light can transmit through the absorbing layer without absorption in case of thin film solar cells (7 and 8).

Figure 1-4 The main limiting factors in solar cells.

The introduction of nanostructures in PV devices may allow overcoming some of above-mentioned limitations but may increase other factors that are less relevant in bulk or thin film devices. Nanotexturization can significantly decrease the reflectance of the surface. The ability of nanostructures to enhance absorption of light results in reduced transmission losses due to thin absorbing layer, allowing one to use less material whilst retaining similar levels of absorption. Furthermore, short carrier path for electrons to be collected significantly eliminates bulk recombination losses in nanostructure based p-n junctions. Therefore, light trapping using nanostructures can enhances both the short-circuit current and the open circuit voltage of a solar cell. Worth noting, some of the main losses can be enhanced with the use of nanostructures. Large surface-to-volume ratio in 1D nanostructures makes the surface recombination overall much higher, increasing the importance of the surface passivation. Series resistance due to the not optimized interfaces with transparent front or the back contacts limits the fill factor of the devices.

## 1.6 Objectives and outline of this Thesis

Device characteristics of radial and axial NW p-n junction solar cells have been reported for various fabrication approaches like the bottom-up vapor-liquid-solid (VLS) and selective area growth (SAG) methods, top-down dry and wet etching methods, electrodeposition and others. **Figure 1-5** illustrates the increase in the best-reported conversion efficiencies based on III-V NW devices in the last few years.

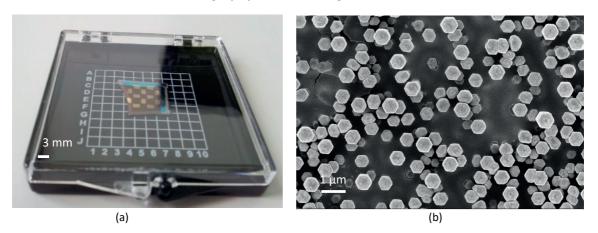

The still comparably low efficiencies for NW-based solar cells indicate many unresolved issues such as obtaining high quality shell formation, reducing surface and interfacial carrier recombination losses, and forming conformal transparent electrodes on the surface of NW with low contact resistance. All these fabrication issues should be carefully analysed to reveal the way to optimize the solar cell structure and increase the solar conversion efficiency up to or beyond planar solar cells, which goes beyond photonic design [45,46]. Another challenge is coming from the scaling NW technology for PV terrestrial applications. Increase in the area of the solar cell leads to the increase of potential losses through the imperfection of the solar cell structure. Garnett *et al.* have shown a scalable technology for Si NW solar cell, achieving areas up to 10 cm<sup>2</sup> [47]. However, III-V NW based solar cells are still much smaller (up to 1 mm<sup>2</sup>).

**Figure 1-5** Best III-V NW based solar cell efficiencies vs Time [40,41,43,48–53].

Classical electrical characterization of solar cells is not enough to reveal the weak points in NW solar cells due to radically different nature. The focus of this thesis is to provide advanced tools and strategies for the analysis of the losses and solutions in NW-based solar cells.

After this introduction, next **Chapter 2** is dedicated to the fabrication of NW based solar cells and classification of different losses in such devices. Starting from the overview of the growth processes, we investigate and reveal difficulties, coming from it, in post-growth steps and device accomplishment. All losses can be divided in two categories – parallel and series losses. At the end, we show that classic I-V characterization cannot univocally analyse these losses.

**Chapter 3** covers the developed characterization methods for the analysis of parallel and series losses in NW based solar cells. First, we introduce important issues with the uniformity in NW array and how conductive AFM (C-AFM) may be useful for its characterization. The second main loss we focus on is different interfaces in NW solar cells, where series resistance can be generated. We separate p-n junction electrical properties from general IV curve using advanced method with applying different intensities of light. The former is widely used in multi-junction solar cells to reveal any losses at the interfaces in solar cell structure.

Finally, in **chapter 4** surface recombination in NW solar cell is recognised as one of the main drawback due to enhanced surface-to-volume ratio. We present an electrochemical impedance spectroscopy (EIS) method that provides a way to obtain quantitative information on the interface states in high-aspect-ratio (HAR) structures.

In **chapter 5**, overview of the thesis and a brief comment on the future perspectives in NW application for PV industry is provided.

# Chapter 2 Parallel and series losses in NW-based solar cells

This chapter is dedicated to the fabrication of NW based solar cells and classification of different losses (which can be classified as series or parallel) in such a devices. Starting from the overview of the growth processes, we investigate and reveal difficulties, coming from it, in post-growth steps and device accomplishment.

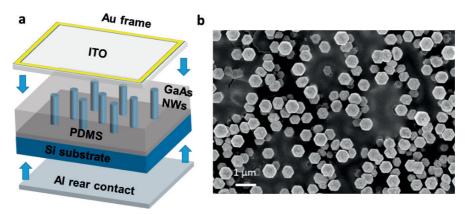

We start with highlighting several obvious requirements to increase the area of NW based solar cell technology and reduce the cost of fabrication, such as absence of e-beam lithography patterning, need for wafer-scale technology, and cheap or reusable substrates. Figure 2-1 shows two strategies for NW based solar cell commercialization – rigid solar cell on a cheap Si substrate and a NW-polymer solar cell peeled off from the substrate. For the first scheme, the bottom-up growth of NWs can be performed on p-doped silicon substrate with a dielectric layer acting as a mask. Large scale patterning can be done using, for example, soft imprint lithography [54]. Due to the reduced contact area between highly lattice-mismatched GaAs and Si, the strain is limited and therefore the formation of dislocations and misfits at the interface is suppressed [55]. Thus, NWs represent an opportunity to integrate GaAs on Si for different opto- and microelectronic applications [56]. The latter method requires peel-off step, which constitutes mechanical breakage of the NWs at the bottom, leaving the substrate reusable for the next growth [57]. Using this process, an expensive III-V substrate can be reused for multiple growth of NWs, reducing the total fabrication cost.

**Figure 2-1** Two ways to obtain large area commercial NW solar cells: **(a)** rigid device on Si substrate; **(b)** flexible device utilizing NW-polymer composite.

Scaling fabrication processes for terrestrial applications is one of the main challenges for the introduction of new device schemes in the PV industry. So far, the record efficiency of 17.8 % was obtained for an InP NW based solar cell with the area of only 0.09 mm<sup>2</sup> [40]. Other high performance NW devices have an area around 1 mm<sup>2</sup> or even less. One of the reasons for using reduced sizes is the geometrical and

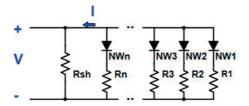

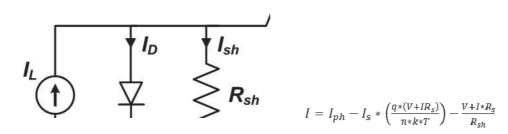

structural uniformity issues in NW arrays, which introduces electrical losses. Besides scaling, overall efficiency of the best NW devices is much lower than their thin film analogs [7]. Therefore, not only parallel losses due to uniformity issues, but also series losses that are generated through the solar cell structure, limit the potential breakthrough of NWs in the PV industry. Unambiguously, detailed analysis of losses should be done in order to improve NW based solar cell performance. The equivalent electrical scheme can be drawn in order to illustrate parallel and series losses in the NW based solar cell. Figure 2-2 shows simplified equivalent electrical scheme for NW based solar cell. Parallel connection of n diodes represents different electrical behavior of NWs in array in case of poor uniformity (NW1...NWn). Series losses can be defined by series resistances R1...Rn. Finally, shunt resistance Rsh is nothing else as a leakage path for electrical current past p-n junctions.

Figure 2-2 Equivalent electrical scheme of the NW based solar cell.

This chapter addresses the potential impact of the fabrication technology on introducing different losses in NW solar cells. We describe the fabrication steps of semiconductor NW based solar cells in details and how it effects on device properties. We start with the growth of NWs and surface passivation, following by post-growth processes, such as polymer embedding and the electrical contacts formation. At the end, applicability of IV electrical characterization method is analyzed in the case of NW based solar cells.

#### 2.1 Growth of semiconductor nanowires

In general, top-down and bottom-up are the two main paradigms in nanostructure fabrication. The first one dominates the modern microelectronics due to the perfect device definition and density, which have typically been the strengths of top-down fabrication. In recent years, advances in bottom-up fabrication processes have opened up the possibility of the integration III-V on Si for different optoelectronic applications. Despite the fact that top-down plasma etching of NWs into a wafer provides the highest uniformity, unresolved reproducibility of mechanical peel-off step (required for substrate re-use) reduces the prospect of this method for commercially available large-area III-V NW based solar cells. Therefore, we focus on the bottom-up growth processes, such as catalyst-free SAG and VLS growth methods by MOVPE and MBE. Below, different technologies to obtain arrays of vertical NWs on substrates are discussed in this context.

Catalyst-free SAG method requires a dielectric mask with openings, formed by a lithographic process and subsequent dry or wet etching. **Figure 2-3a** illustrates SAG method. NWs are epitaxially and locally grown in such holes due to selectivity [58]. Typical features of SAG in MOVPE is high V-III ratio (ratio between V and III group elements) and relatively high growth temperature (700 - 800 °C) [59]. MBE has very low growth rates, therefore, the vapor-solid process, such as SAG, is inexpedient in terms of time and cost of the process. However, the VLS method using Ga or Au droplet as a catalyst is well developed and highly used to grow different types of semiconductor NWs by MBE.

**Figure 2-3b** shows the VLS method in two steps. The initiation of the growth starts with the droplet formation, where the self-catalyzed method uses Ga droplet formation inside the holes of the pattern [60],

and the Au-catalyzed method needs annealing of the Au film above the liquid phase transition temperature to form Au droplets [61,62] or direct pre-deposition of Au nano particles [63]. Next, precursors in the form of vapor are transported to the substrate and absorbed by the droplets. Finally, due to supersaturation, the material precipitates at the liquid/solid interface. Thus, NW is growing along the direction of the largest surface free energy. MBE VLS method utilizes low V-III ratios (Ga-rich conditions) and relatively low temperatures.

Figure 2-3 Schematic illustration of SAG (a) and VLS (b) growth methods of semiconductor NWs.

The growth of perfect vertically aligned NW arrays is one of the key factors to develop high-efficiency NW based solar cell. The uniformity of NWs, both geometrical and functional, plays significant role in obtaining high efficiency due to the parallel electrical connection of NWs in the array, as shown on **Figure 2-2**. Each NW p-n junction is a diode, working as a single solar cell. Parallel connection of solar cells is known to be an option to connect solar cells in a solar module [64]. For solar cells connected in parallel, current is additive while voltage is the same. This configuration has high tolerance against complex irradiance conditions (for example, partial shading). However, if among the solar cells connected in parallel there is a cell with open-circuit voltage lower than the others, it will drag down the voltage on all the remaining solar cells. A similar case can be extrapolated on NW based solar cell with NWs connected in parallel in arrays. Therefore, high uniformity in the array is needed to get best performance. Here, we come to the first challenge in large area NW solar cell structures – the need of high uniformity of NWs.

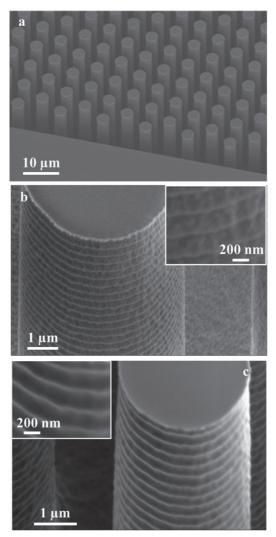

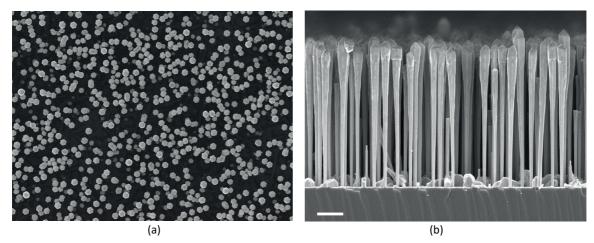

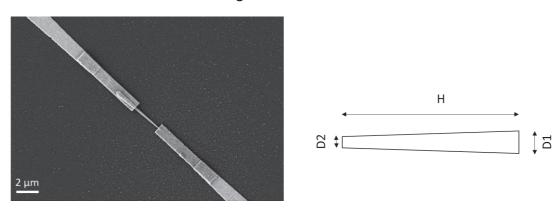

Figure 2-4a shows a scanning electron micrograph (SEM) of a GaAs NW array, grown by SAG MOVPE on a GaAs substrate. Perfect uniformity in NW length and diameter reduces the possible losses due to parallel connection of NWs in device structure. Figure 2-4b and Figure 2-4c show GaAs NWs obtained on a silicon substrate by Ga-catalyzed VLS growth by MBE, where Ga droplets exist on the top of the NWs. The difference between the last two images comes from the fact that there is no dielectric mask with predefined holes on Figure 2-4b in contrast to the sample from Figure 2-3c. In the absence of the patterned mask, NWs are grown in a self-organizing mode and thus have a wide variation in the diameter and length [65,66]. In addition, parasitic GaAs deposition between NWs is enhanced. These two cases show the importance of the dielectric mask with lithographically defined openings for uniform NW array. It is worth to note additional feature on Figure 2-4c such as tapering of NWs in case of small distance between them. Diameter variation in NW should be considered in order to optimize light absorption in arrays with small pitch. Moreover, radial p-n junction in tapered NWs can be non-uniform along the NW length.

The preparation and type of substrate prior to NW growth is key since in rigid NW based solar cells it is used as a back electrical contact (see **Figure 2-1a**). In case of GaAs NWs, native GaAs substrates and foreign Si substrates can be used. The crystalline orientation of the substrate plays a major role in determining the orientation of NWs compared to the substrate. GaAs (111) B and Si (111) wafers allow preferential vertical growth of NWs (perpendicular to the substrate). Besides the growth mechanism on native or foreign substrates and crystalline quality issues related with it, the carrier transport mechanism through the "substrate-NW" interface should be mentioned. In case of using Si as a foreign substrate to grow GaAs NW, a potential barrier between Si and GaAs can occur due to the band alignment characteristics between the two semiconductors. By changing doping levels in the substrate and the NWs, the width of the barrier can be minimized in order to promote carrier tunneling through the potential barrier and therefore reduce series resistance at the interface. We will come back to this question later. Finally, the obvious difference between Si and GaAs is the substrate cost. While Si is cheap and can be a part of the solar cell without increase in the cost, GaAs substrates should be removed and re-used in next growth for reducing the production cost of NW based solar cell.

**Figure 2-4** SEM images showing the uniformity of GaAs NWs grown by SA-MOVPE on GaAs substrate **(a)**, self-assembled Ga-catalysed VLS MBE on Si substrate **(b)** and Ga-catalysed VLS MBE on Si substrate with hole pattern **(c)** [image by Wonjong Kim] methods.

A conventional solar cell needs p-n junction in order to separate electron-hole pairs. As mentioned in **Chapter 1.4**, axial or radial geometries of junction can be implemented in NW concept. Depending on the growth method, epitaxial technique and geometry of p-n junction, different difficulties with optimal doping of n- and p-type of junction are exist. In VLS growth, the doping is incorporated through the droplet and

therefore less controllable compared to standard doping in vapor-solid growth such as SAG. Not taking in account the technological aspect of this question, the analysis and characterization of the p-n junction in NWs is the fundamental point in order to optimize the carrier transport inside NW p-n junction. The doping level can be measured through the single NW characterization or directly in the array by electron beam induced current (EBIC) method but it requires advanced techniques to prepare the sample for the measurements. In addition to doping concentration evaluation, the p-n junction diode behavior is the important parameter in the solar cell. The diode current is limited by the carrier recombination mechanism in the structure. Therefore, detailed diode analysis provides the main limiting factors in the p-n junction and opens the ways to improve the carrier transport through p-n junction.

## 2.2 Surface passivation

After the growth of NWs and formation p-n junction, the surface should be passivated. While the one-dimensional nature of NWs provides several advantages, such as enhanced light absorption, this particular morphology and reduced size results also in an increase in the surface-to-volume ratio. Consequently, any defects or energy states at the surface due to oxidation can disturb its functional properties. As shown on **Figure 2-5a**, electronic states at the surface can appear due to an abruptness of the periodical crystal lattice (e.g. dangling bonds) and the existence of a non-stoichiometric surface oxide. These states can act as non-radiative recombination centers and contribute to the trapping of charge carriers. As a consequence, pinning (bending) of the Fermi level at the surface occurs [67]. A pinned Fermi level can push the free carriers from surface to the bulk forming an undesirable depletion layer in NW. Overall, this results in a decrease in the figure of merit of devices such as a reduction of photo-generated power for solar cells.

**Figure 2-5** Position of the conduction (blue) and valence bands (red) across a NW diameter for: **(a)** un-passivated GaAs NW and **(b)** a GaAs NW passivated with a thin layer of AlGaAs. Below, the 3D drawing of the structures are shown. As-dangling bonds and GaOx are represented at the surface of the un-passivated NW.

One strategy to reduce the effect of surfaces in nanostructures consists of coating with a semiconductor with a lattice-matched material with a larger bandgap, as shown on **Figure 2-5b**. Coating results in the passivation of dangling bonds, while the higher bandgap allows charge carriers to remain in the core of the structure. Note that Fermi level pinning can occur at the surface of passivation layer (not shown on **Figure 2-5**); however, this region is not the part of the electrically relevant area of p-n junction. From the conceptual point of view, coating with a lattice-matched material should result in the suppression of surface states. Therefore, popular way to passivate GaAs NWs is to coat them radially with an AlGaAs layer inside the epitaxial reactor just after the growth. AlGaAs is lattice-matched with GaAs and exhibits a

higher bandgap. The band alignment of GaAs and AlGaAs semiconductors results in type I heterostructure. Capping with a highly doped layer also helps saturating the surface defect states [68,69]. In addition, to prevent further oxidation of Al in AlGaAs, which is highly probable in case of high Al concentration, application of a thin GaAs extra layer can be an option to complete the device structure. The potential losses with such a passivation scheme are related with a non-uniform Al content distribution (also called Al segregation), parasitic absorption in the capping layer and the presence of the potential barrier for majority carriers.

Another strategy focuses on passivation of III-V NWs with an amorphous and high bandgap dielectric, such as aluminum oxide,  $Al_2O_3$ , by atomic layer deposition (ALD). This material has shown encouraging results with other III-V NWs such as InAs and InAsSb [70]. In the case of III-V arsenide surfaces, the group III components often oxidize preferentially, producing As dangling bonds and As anti-site defects at the oxide/semiconductor interface [71]. To prevent it, pre-ALD dosing of trimethylaluminium, the standard molecular precursor for  $Al_2O_3$  deposition, can be used before starting deposition to both inhibit subsequent oxidation of the surface and selectively passivate As dangling bonds, as was successfully shown for InGaAs surfaces [72,73].

Efficient passivation of nanostructures by dielectric material by ALD has turned out to be challenging as a few interface states remain, with the consequent impact on the functional properties of the nanostructures. In this sense, there is the need for a deeper understanding of the passivation mechanism of nanostructures as well as defining fabrication procedures for finding optimal passivation layers for different semiconductors. This optimization can only be realized if the surface and interface states can be characterized in a proper manner. In **Chapter 4**, we provide a path for the characterization of surface and interface states in HAR semiconductor structures passivated with dielectric layer.

#### 2.3 Post growth processes

Several post growth processes are realized for the complete fabrication of the solar cell structure. These include planarization and mechanical support via embedding in transparent polymer, opening of the NW tips by polymer etching and electrical front and rear contact formation. All these steps should be optimized to minimize possible losses in solar cell. **Figure 2-6** represents the main post-growth steps in fabrication NW based solar cell.

Figure 2-6 Process flow of post-growth fabrication of NW based solar cell.

#### 2.3.1 Polymer embedding

Embedding of NWs into a flexible polymer film was first reported by Plass *et al.* [74]. An array of VLS-grown Si wires was suspended in a Polydimethylsiloxane (PDMS) film. Subsequently, a free standing PDMS film with NWs was created by mechanically peeling the film from the Si substrate. Since the first publication, there were very few reports on the performance of detached NW-polymer composites for solar cell applications due to difficulties in fabrication process. Spurgeon *et al.* [75] demonstrated that this approach could potentially lead to a solar cell without sacrificing solar energy conversion efficiency compared to substrate-supported NW solar cells. Here, we discuss the embedding of NWs in polymer film,

which acts as a supporting layer and reduces the surface roughness of NW array for conformal electrical contacts coating. Additional benefit of the polymer media comes from the ability to cool down the NW based solar cell in more effective way [76]. Embedding the NWs in polymer (such as BCB) increases the spectral emissivity over the whole thermal wavelength range due to better thermal IR absorption in polymer compared to bare NWs case.

To embed NWs in a polymer film, different insulating polymer materials can be used, such as BCB [43,52], PDMS [77,78] and SU-8 [22]. Two of them are discussed in this thesis – PDMS and SU-8. The requirements for integration polymer in NW based solar cells are transparency at visible wavelength range, electrical insulation and chemical compatibility with III-V NWs. The main advantage of PDMS is an opportunity to mechanically peel the NWs from the substrate, while maintaining a low refractive index and transparency. It opens up opportunities to fabricate flexible NW based devices and re-use expensive III-V substrates for NW growth. The standard PDMS embedding process includes several steps, such as PDMS mixture preparation, spin coating and baking. One key aspect that should be considered is the typically high density and aspect ratio of NWs in array. To prevent any mechanical breakage or bending of NWs during spin coating, the PDMS mixture must be diluted by Hexane or another appropriate component for decreasing viscosity. SU-8 resist can be spin coated without dilution at rather low spin rate to obtain thickness down to 1 µm. Comparing both polymers, PDMS is preferred in case of mechanical peeling of the NWs from the substrate, while SU-8 is preferred for rigid NW solar cell design with NWs below several microns.

Here, we highlight another potential issue for large area NW based solar cell, which is the mechanical damaging of NWs during polymer coating. Potentially, it can effect on a carrier transport through the solar cell structure by forming leakage paths. The probability to damage NWs highly depends on two parameters: viscosity of the polymer solution and hardness of the NWs. The first parameter can be tuned by choosing appropriate polymer and/or diluting it with special chemical components. The second parameter comes from geometrical parameters of NWs such as diameter, length and pitch size, as well as NW fabrication method. One can conclude that top-down etched NWs are naturally stronger than ones grown by the bottom-up approach. After spin coating and baking in the oven, the polymer film with NWs on the substrate is cross-linked and ready for the next fabrication steps.

One of the most complicated process steps related to the polymer is dry etching by plasma. To contact NWs with a top electrode, the tips of NWs should be exposed. The etching process requires careful time control and multi-step configuration to get a desirable polymer thickness slightly below the NW height. Imperfection in NW array leads to thickness variation in polymer film after opening the NW tips. This can affect the quality of the top electrical contacts and result in an increase series resistance. In addition, residuals of polymer on NW surface can lead to an additional parasitic contact resistance at the interface between NWs and the top electrical contact.

#### 2.3.2 Electrical contacts to NW based devices

To complete the solar cell, front and rear electrical contacts are needed. Typically, the rear electrical contact is opaque, made from metal alloys. Since the rigid NW solar cell stays on the substrate, the rear contact is provided through the doped substrate and metal film deposited on the back of the wafer. Another option is forming the rear contact on the top of the wafer out of the NW array area. Different metal contacts can be used for the NW device, depending on the substrate material. In the case of III-V substrates, Au alloys form ohmic contacts to GaAs after annealing at certain temperatures, such as

Pd/Ge/Au to n-GaAs and Pd/Ti/Au to p-GaAs. Si substrates as a back contact form ohmic contacts with Al (p-type) or Au and Pt (n-type). This process is well developed for Si technology.

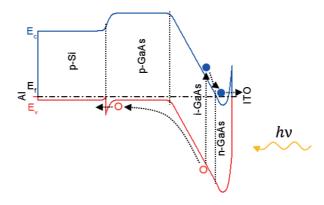

To illustrate the contact formation to GaAs p-n junction structure grown on Si, electronic band diagram in dark at equilibrium is shown on **Figure 2-7**. The software package Nextnano was used to simulate band alignment of the GaAs p-n junction and hetero interfaces [79]. Note that Al rear contact to p-doped Si substrate is considered as ohmic. Regarding additional losses due to rear contacts, we can highlight increased series resistance in the case of low-doped substrate, since carriers have to travel along the whole thickness of the substrate. One should also highlight the barrier at the valence band alignment at the interface between GaAs and Si. This results in a barrier (and added series resistance) for holes that have to diffuse through this interface. Tanabe *et al.* showed that to prevent barrier at the hetero interface, GaAs should be doped up to 5x10<sup>19</sup> cm<sup>-3</sup> concentration [80].

**Figure 2-7** One-dimensional energy band diagram of the solar cell structure Al/p-Si/p-GaAs/i-GaAs/n-GaAs/ITO along the NW axis (in dark at equilibrium conditions). Electron (blue circle) and hole (red circle) flow is indicated.