# Satisfiability-Based Methods for Digital Circuit Design, Debug, and Optimization

THÈSE Nº 8850 (2018)

PRÉSENTÉE LE 28 SEPTEMBRE 2018 À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS LABORATOIRE D'ARCHITECTURE DES PROCESSEURS PROGRAMME DOCTORAL EN INFORMATIQUE ET COMMUNICATIONS

## ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

## Andrew James BECKER

acceptée sur proposition du jury:

Prof. V. Kuncak, président du jury Prof. P. lenne, directeur de thèse Prof. Ph. Brisk, rapporteur Prof. W. Hu, rapporteur Dr B. Jobstmann, rapporteuse

To my family, whose guidance, support, and encouragement are the earth from which all my achievements grow.

# Résumé

Il est notoirement difficile de bien concevoir des circuits numériques. Cette difficulté découle en partie des nombreux degrés de liberté inhérents à la conception de circuits, et est généralement associée à la nécessité de satisfaire diverses contraintes.

Dans cette thèse, nous démontrons comment les formulations de problèmes de satisfaction peuvent être utilisées pour compléter une conception, ou pour trouver une architecture spécifique qui satisfait à certaines contraintes ; comment celles-ci peuvent être utilisées pour créer, déboguer et optimiser des conceptions ; et introduire un langage spécifique au domaine, bien adapté à la conception, au débogage et à l'optimisation assistées par la satisfaction.

Dans la première application, nous montrons comment des incertitudes explicites appelées "holes" peuvent à la fois être utilisées naturellement et favoriser la création de problèmes de satisfaction formels utiles à la conception de circuits. Nous développons également un langage DSL approprié pour rendre la conception avec des holes facile et efficace.

Nous montrons ensuite comment, en utilisant le même type de formulation de satisfaction, nous pouvons automatiquement instrumenter une conception buggy donnée pour remplacer les fragments de syntaxe suspects par des alternatives potentiellement correctes. Le solveur de satisfaction détermine alors s'il existe un ensemble possible de fragments alternatifs qui corrigent le bogue. Nous démontrons également que cette approche est raisonnablement évolutive, en partie parce qu'il y a moins besoin d'une spécification entièrement précise dans la formulation du problème de satisfaction.

Nous avançons ensuite au-delà du "hole-filling" et montrons comment une intégration étroite de l'élaboration du design avec des solveurs de satisfaction permet des approches totalement nouvelles. Nous utilisons cette intégration étroite pour créer les premières méthodes connues d'optimisation des circuits du modèle GLIFT (Gate-Level Information Flow Tracking) et pour faire des compromis de principe dans leur précision.

Enfin, en intégrant tous les travaux précédents, nous proposons un DSL plus puissant, spécifiquement conçu pour combler les lacunes du premier langage de "hole-filling". Ce langage, que nous appelons Nasadiya, permet des intégrations de satisfaction plus générales dans la conception et l'optimisation des circuits, et fournit une fonctionnalité de modélisation intégrée utile pour optimiser les propriétés extra-fonctionnelles comme le retard de chemin critique. Nous démontrons l'utilité de ces fonctions en implémentant un optimiseur automatique de puissance pour un type populaire d'additionneurs de préfixes parallèles.

Mots clefs : Satisfiabilité, SAT, QBF, débogage, optimisation, propriétés extra-fonctionnelles.

# Abstract

Designing digital circuits well is notoriously difficult. This difficulty stems in part from the very many degrees of freedom inherent in circuit design, typically coupled with the need to satisfy various constraints. In this thesis, we demonstrate how formulations of satisfiability problems can be used automatically to complete a design, or to find a specific design architecture that satisfies certain constraints; how these can be used to create, debug, and optimize designs; and introduce a domain-specific language particularly well-suited for satisfiability-assisted design, debug, and optimization.

In the first application, we show how explicit uncertainties called "holes" can both be natural to use and conducive to the creation of formal satisfiability problems useful for designing circuits. We further develop a Scala-hosted Domain Specific Language (DSL) with appropriate syntactic sugar to make design with holes easy and effective.

We then show how, utilizing the same kind of satisfiability formulation, we can automatically instrument a given buggy design to replace suspicious syntax fragments with potentially-correct alternatives. The satisfiability solver then determines if there is any possible set of alternative fragments which fix the bug. We also demonstrate that this approach is reasonably scalable, in part because there is less need for a fully-precise specification in the formulation of the satisfiability problem.

We then advance beyond mere hole-filling and show how a tight integration of design elaboration with satisfiability solvers allows totally new approaches. To point, we use this tight integration to create the first known methods to optimize Gate-Level Information Flow Tracking (GLIFT) model circuits and to make principled trade-offs in their precision.

Finally, integrating all the previous work, we propose a more powerful DSL specifically designed to address the shortcomings of the first "hole-filling" language. This language, which we call Nasadiya, affords more general integrations of satisfiability into circuit design and optimization, and provides built-in modeling functionality useful for optimizing extra-functional properties like critical path delay and circuit area. We demonstrate the utility of these features by implementing an automatic power optimizer for a popular type of parallel prefix adders.

Key words: Satisfiability, SAT, QBF, Debug, Optimization, Extra-Functional Properties.

# Contents

| Ab | ostra   | ct (Français)                                                       | i   |

|----|---------|---------------------------------------------------------------------|-----|

| Ab | ostra   | ct (English)                                                        | iii |

| Та | ble o   | f Contents                                                          | v   |

| Li | st of ] | Figures                                                             | vii |

| Li | st of ' | Tables                                                              | xi  |

| 1  | Intr    | oduction                                                            | 1   |

|    | 1.1     | Boolean Logic                                                       | 3   |

|    | 1.2     | Boolean Satisfiability                                              | 4   |

|    | 1.3     | 2QBF-SAT                                                            | 7   |

|    | 1.4     | Overview                                                            | 8   |

| 2  | Sati    | sfiability for Circuit Design Assistance                            | 11  |

|    | 2.1     | Motivational Example                                                | 12  |

|    | 2.2     | Related Work                                                        | 12  |

|    | 2.3     | Implementation                                                      | 14  |

|    |         | 2.3.1 Sketchilog                                                    | 16  |

|    |         | 2.3.2 The Rules of the Code                                         | 18  |

|    |         | 2.3.3 Hardware Sketching vs. Software Sketching                     | 19  |

|    |         | 2.3.4 The Limitations of SKETCHILOG                                 | 19  |

|    | 2.4     | Experiments                                                         | 20  |

|    |         | 2.4.1 Prefix Adders                                                 | 20  |

|    |         | 2.4.2 Sketching to Enable Design Re-Use                             | 21  |

|    |         | 2.4.3 Strength Reduction of a Constant Divider                      | 21  |

|    | 2.5     | Experimental Results                                                | 22  |

|    | 2.6     | Conclusions                                                         | 23  |

| 3  | A Sa    | tisfiability-Based Approach to Localizing and Correcting RTL Errors | 25  |

|    | 3.1     | Introduction                                                        | 26  |

|    | 3.2     | Related Work                                                        | 28  |

|    | 3.3     | "Fudging" Buggy RTL Circuits                                        | 30  |

#### Contents

| Bi | bliog | graphy 1                                                | 01       |

|----|-------|---------------------------------------------------------|----------|

| 6  | Con   | nclusion                                                | 97       |

|    | 5.4   | Conclusion                                              | 93       |

|    |       |                                                         | 91       |

|    |       | 5.3.2 Constraints                                       | 87       |

|    |       | 5.3.1 Design                                            | 84       |

|    | 5.3   | Case Study: Power-Efficient Parallel Prefix Adders      | 83       |

|    | 5.2   | Related Work                                            | 82       |

|    |       | 5.1.3 Virtualized Solver Access                         | 80       |

|    |       | 5.1.2 Arbitrary Constraint Specification                | 78       |

|    |       | •                                                       | 68       |

|    | 5.1   | Nasadiya                                                | 67       |

| 5  | Solv  | ver-Aided Circuit Design and Optimization with Nasadiya | 65       |

|    | 4.6   | Conclusions                                             | 64       |

|    | 4.5   |                                                         | 63       |

|    | 4 5   | 1 1                                                     | 59<br>62 |

|    |       | 1                                                       | 57       |

|    | 4.4   | 1                                                       | 56       |

|    |       |                                                         | 54       |

|    |       |                                                         | 51       |

|    | 4.3   | 1 1                                                     | 51       |

|    | 4.0   |                                                         | 48       |

|    | 4.2   | 1                                                       | 48       |

|    |       |                                                         | 47       |

|    |       |                                                         | 44       |

|    | 4.1   |                                                         | 44       |

| 4  |       |                                                         | 43       |

|    |       |                                                         |          |

|    | 3.7   | -                                                       | 42       |

|    | 3.6   |                                                         | 40       |

|    | 3.5   |                                                         | 38       |

|    | 0.1   |                                                         | 37       |

|    | 3.4   |                                                         | 37       |

|    |       |                                                         | 34       |

|    |       |                                                         | 34       |

|    |       |                                                         | 32       |

|    |       | 3.3.1 Common Error Library                              | 31       |

# List of Figures

| 1.1 | Truth table for the universal Boolean function NAND.                                 | 3  |

|-----|--------------------------------------------------------------------------------------|----|

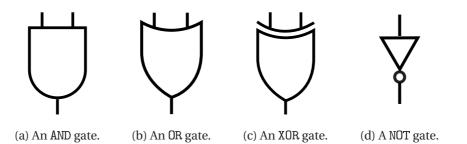

| 1.2 | Common Boolean logic gates                                                           | 3  |

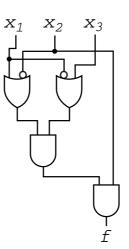

| 1.3 | An example schematic of Boolean logic gates.                                         | 4  |

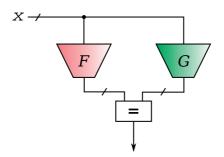

| 1.4 | An example miter circuit.                                                            | 6  |

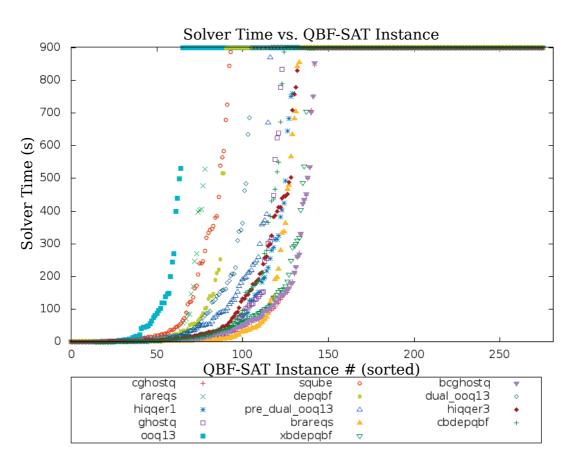

| 1.5 | A chart showing solver performance in a recent QBF-SAT solver competition            | 7  |

| 1.6 | An example of a 2QBF-SAT miter circuit.                                              | 8  |

| 2.1 | Visualizations of a sketch of a ADD/SUB unit and its solution.                       | 13 |

| 2.2 | A visualization of part of the Chisel type hierarchy.                                | 14 |

| 2.3 | A simple example Chisel module.                                                      | 15 |

| 2.4 | A visualization of the Chisel representation of a multiplexer.                       | 16 |

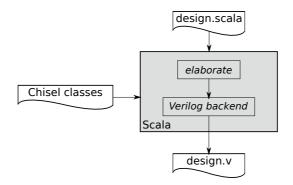

| 2.5 | The Chisel flow.                                                                     | 16 |

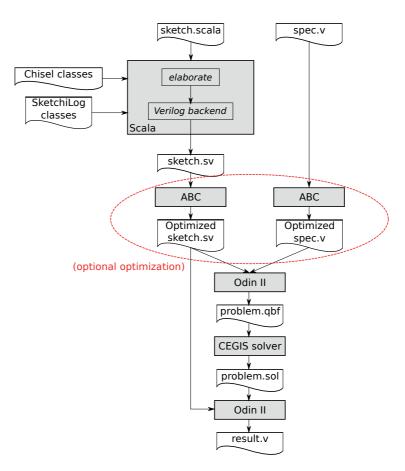

| 2.6 | The Sketchilog tool flow.                                                            | 17 |

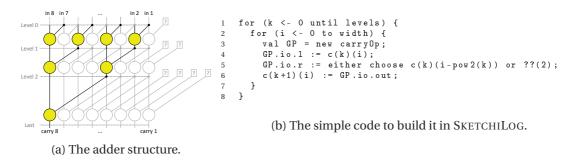

| 2.7 | A visualization of a partial sketch of an adder generator.                           | 20 |

| 2.8 | Visualization of a sketch of an IP interface adapter.                                | 21 |

| 2.9 | Visualization of a sketch of a strength-reduced constant divider                     | 22 |

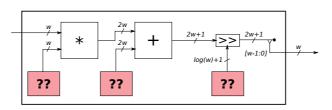

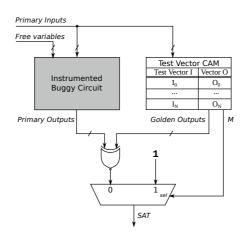

| 3.1 | The FUDGEFACTOR tool flow.                                                           | 27 |

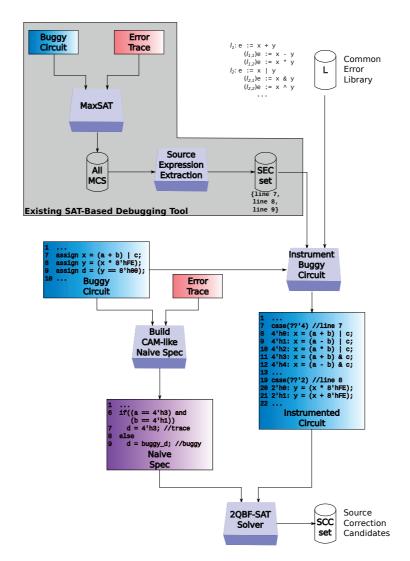

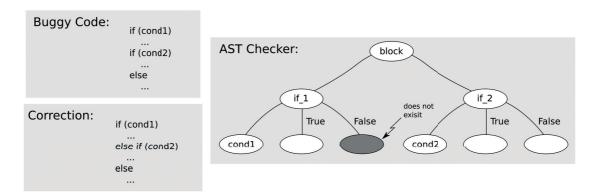

| 3.2 | A visualization of an error rule.                                                    | 32 |

| 3.3 | A more complex rule matching condition.                                              | 33 |

| 3.4 | A visualization of a miter constructed with test vectors.                            | 35 |

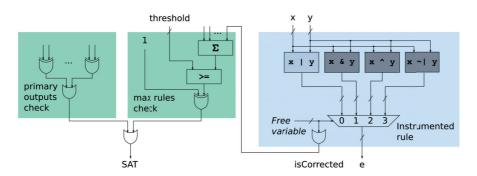

| 3.5 | A visualization of the 2QBF-SAT miter that helps to minimize source code inter-      |    |

|     | ventions.                                                                            | 36 |

| 3.6 | A simplified miter for a combinational syntax-guided synthesis problem               | 36 |

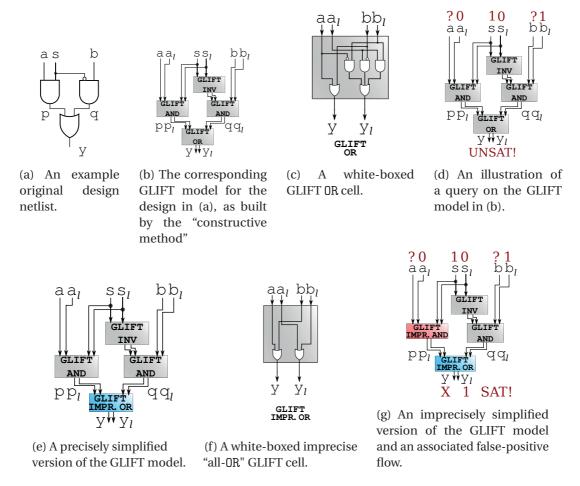

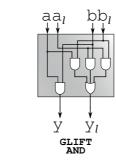

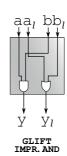

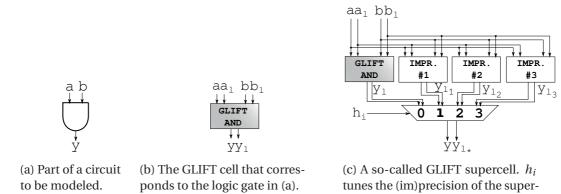

| 4.1 | An overview of GLIFT cells, models, and queries.                                     | 45 |

| 4.2 | Precise and imprecise GLIFT cells and truth tables.                                  | 47 |

| 4.3 | A visualization of GLIFT model construction and instrumentation.                     | 49 |

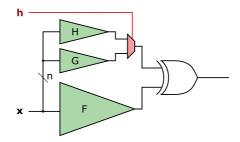

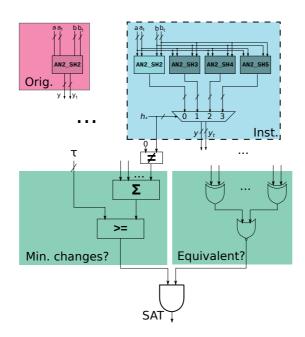

| 4.4 | A visualization of the 2QBF-SAT miter for precise GLIFT model simplification         | 50 |

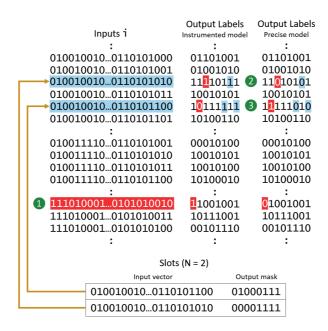

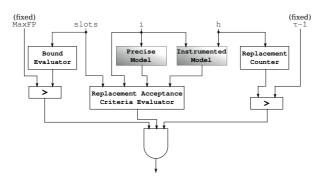

| 4.5 | A visualization of the acceptance criteria for the explicit imprecise simplification |    |

|     | method.                                                                              | 52 |

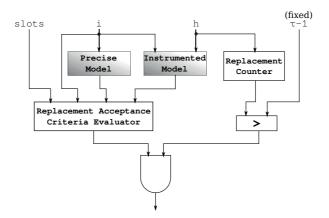

| 4.6 | A visualization of the 2QBF-SAT miter for the explicit imprecise simplification      |    |

|     | method.                                                                              | 52 |

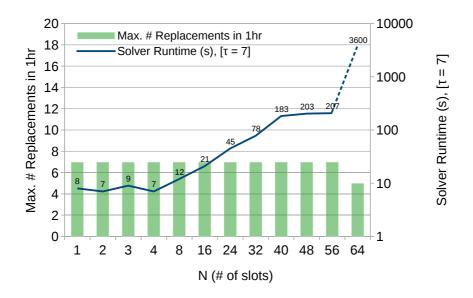

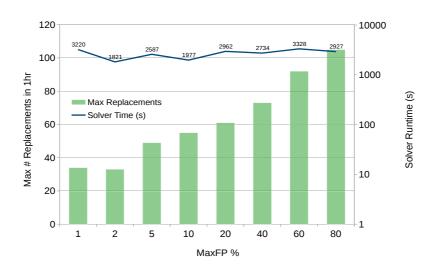

| 4.7 | A chart showing the solver time and effectiveness of the explicit method             | 54 |

#### List of Figures

| 4.8  | A visualization of the acceptance criteria for the patterns imprecise simplifica-       |    |

|------|-----------------------------------------------------------------------------------------|----|

|      | tion method                                                                             | 55 |

| 4.9  | A visualization of the 2QBF-SAT miter circuit for imprecise GLIFT model simpli-         |    |

|      | fication using the patterns method.                                                     | 56 |

| 4.10 | Pseudo-code for the solution space exploration algorithm used to find the best          |    |

|      | solution.                                                                               | 57 |

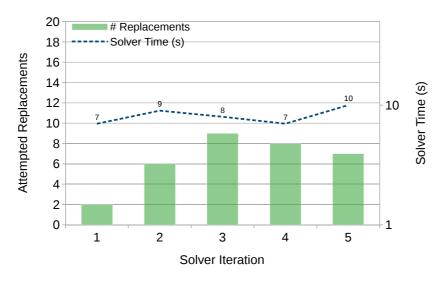

| 4.11 | A visualization of the solver progression for precise simplification of the $too_large$ |    |

|      | benchmark                                                                               | 58 |

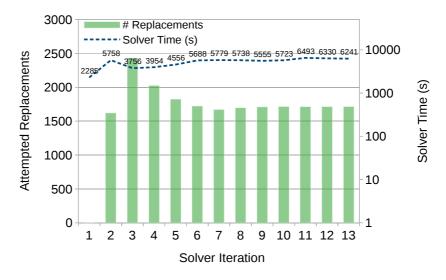

| 4.12 | A visualization of the solver progression for precise simplification of the C7552       |    |

|      | benchmark                                                                               | 59 |

| 4.13 | A visualization of solver performance and effectiveness of the patterns imprecise       |    |

|      | simplification method                                                                   | 60 |

| 4.14 | Benchmark results for the patterns imprecise simplification method.                     | 61 |

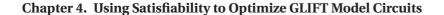

| 4.15 | A scatter plot showing area reduction vs. added false positive rate for the patterns    |    |

|      | imprecise simplification method.                                                        | 62 |

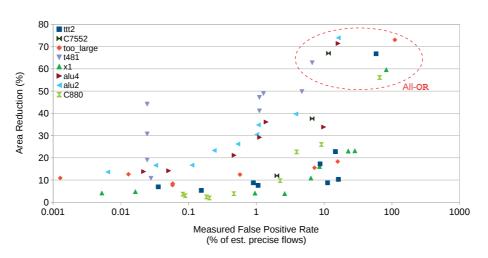

| 4.16 | A scatter plot showing measured added false positive rate vs. the MaxFP parameter.      | 62 |

|      |                                                                                         |    |

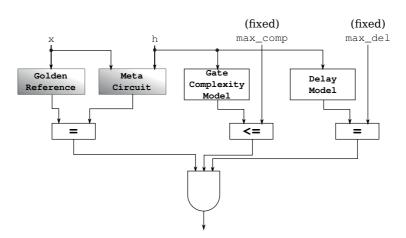

| 5.1  | An example 2QBF-SAT miter that can be easily built and solved in Nasadiya               | 66 |

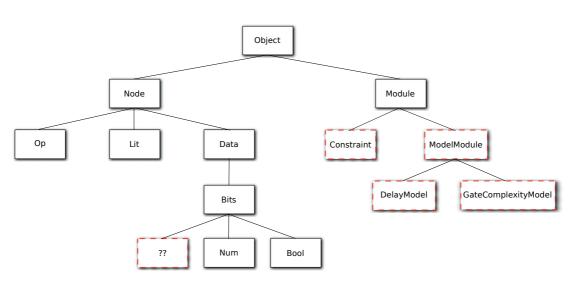

| 5.2  | Part of the Nasadiya object and class hierarchy.                                        | 67 |

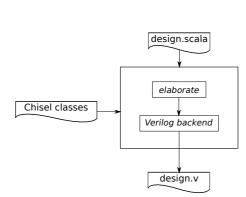

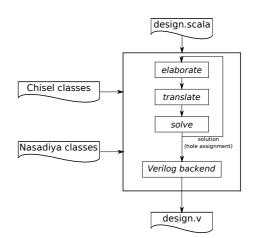

| 5.3  | A visualization of the high-level difference between the regular Chisel flow and        |    |

|      | the Nasadiya flow                                                                       | 69 |

| 5.4  | A simple toy example of a module and two possible implementations for which             |    |

|      | solver-aided design might be useful.                                                    | 70 |

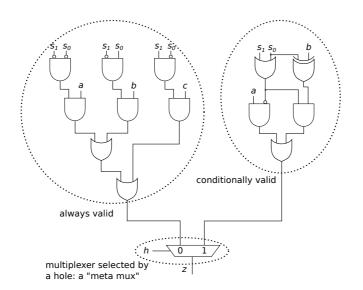

| 5.5  | An example "meta mux" construction.                                                     | 70 |

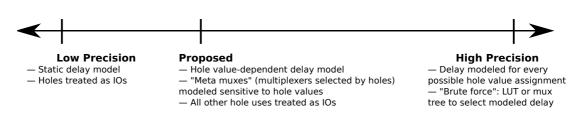

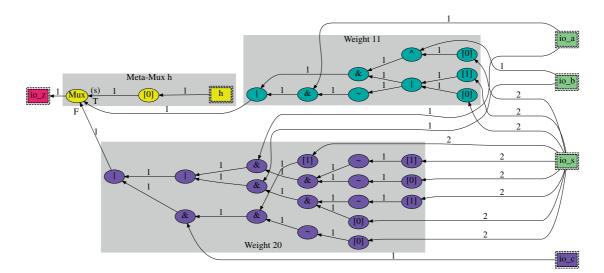

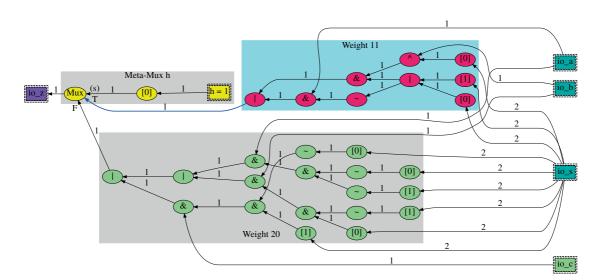

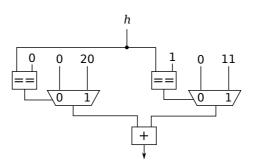

| 5.6  | A visualization of the trade-off space for hole-based circuit delay modeling            | 71 |

| 5.7  | Example code for extending delay modeling functionality.                                | 72 |

| 5.8  | Pseudo-code for the depth-first traversal function used to build delay models           | 74 |

| 5.9  | An overlay of an example gate complexity model on the original circuit                  | 77 |

| 5.10 | A visualization of an example gate complexity model.                                    | 78 |

| 5.11 | Another visualization of an example gate complexity model.                              | 79 |

| 5.12 | Pseudo-code for the depth-first traversal function used to build gate complexity        |    |

|      | models                                                                                  | 80 |

| 5.13 | An example showing an arbitrary constraint over a circuit and its models                | 81 |

| 5.14 | Another example constraint specification in Nasadiya.                                   | 81 |

| 5.15 | Example driver code for Nasadiya.                                                       | 82 |

| 5.16 | Generator code for a Ling adder amenable to solver-aided design and optimization.       | 85 |

| 5.17 | Generator code to build a sparse sum block for a Ling adder.                            | 86 |

| 5.18 | The constraint used to minimize modeled circuit power                                   | 87 |

| 5.19 | Driver code used to optimize the Ling adder                                             | 88 |

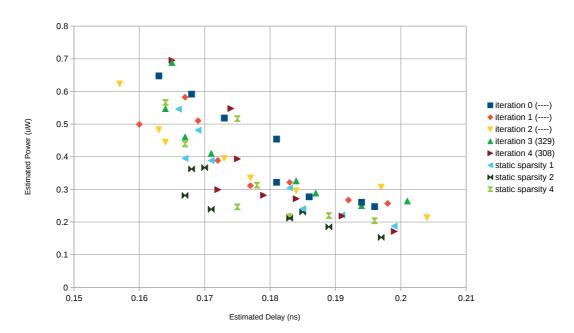

| 5.20 | A chart showing power vs. delay for all intermediate 8-bit adders.                      | 89 |

| 5.21 | A chart showing power vs. delay for all intermediate 16-bit adders                      | 89 |

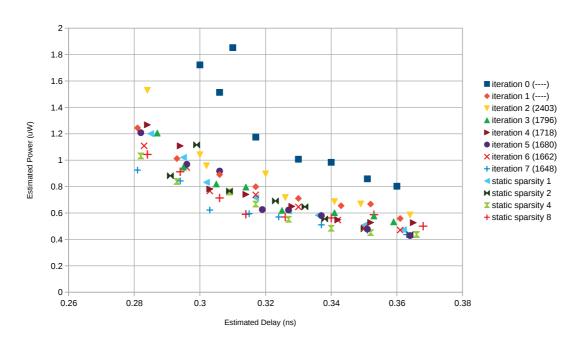

| 5.22 | A chart showing power vs. delay for all intermediate 32-bit adders                      | 90 |

#### List of Figures

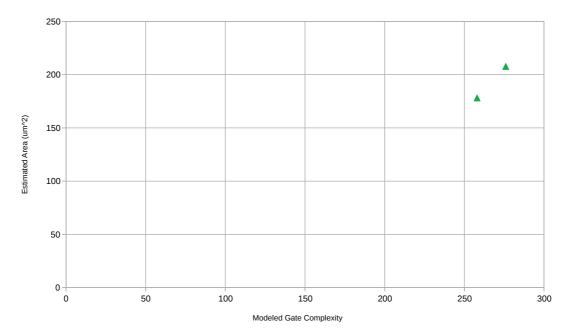

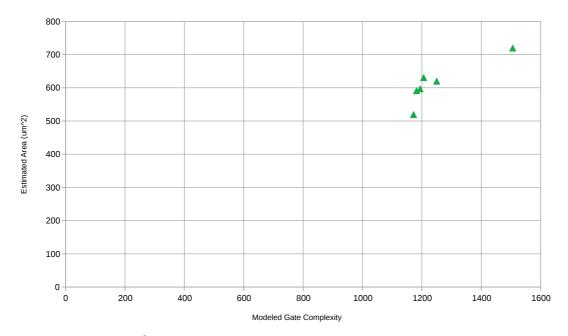

| 5.23 | A chart showing area vs. modeled gate complexity for all intermediate 8-bit adders. | 91 |

|------|-------------------------------------------------------------------------------------|----|

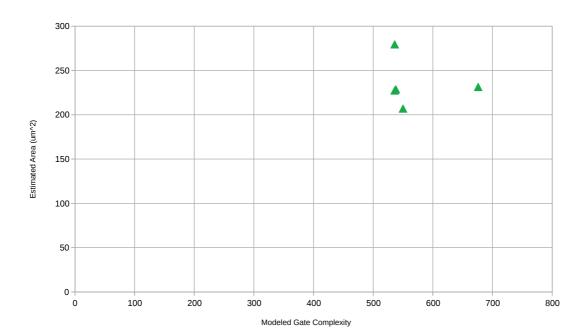

| 5.24 | A chart showing area vs. modeled gate complexity for all intermediate 16-bit        |    |

| i    | adders                                                                              | 92 |

| 5.25 | A chart showing area vs. modeled gate complexity for all intermediate 32-bit        |    |

| i    | adders                                                                              | 92 |

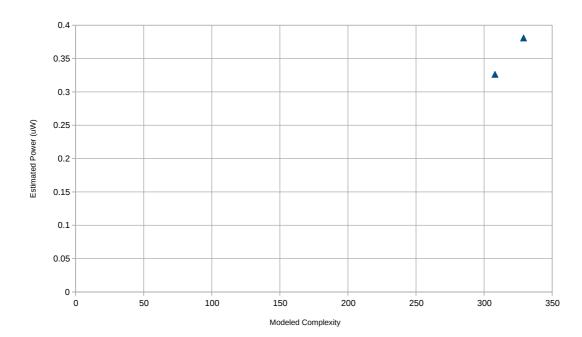

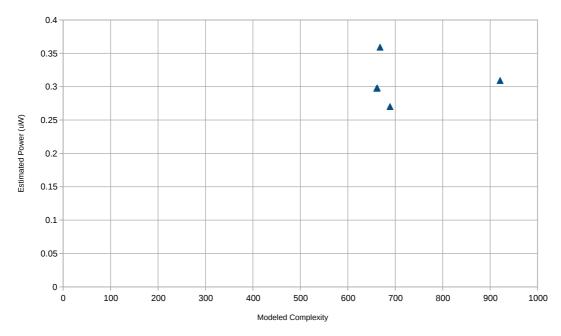

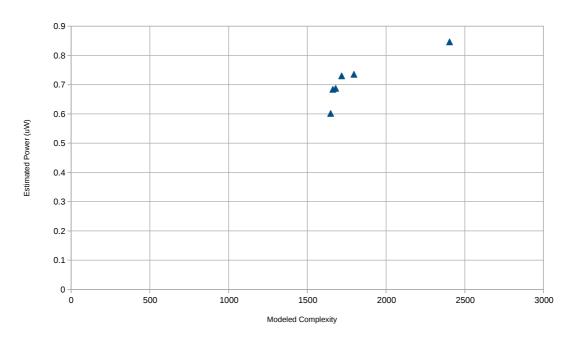

| 5.26 | A chart showing power vs. total modeled complexity for all intermediate 8-bit       |    |

| ä    | adders                                                                              | 94 |

| 5.27 | A chart showing power vs. total modeled complexity for all intermediate 16-bit      |    |

| i    | adders                                                                              | 94 |

| 5.28 | A chart showing power vs. total modeled complexity for all intermediate 32-bit      |    |

| i    | adders                                                                              | 95 |

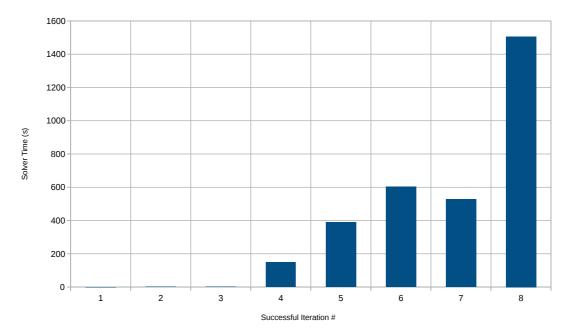

| 5.29 | A plot of solver time vs. iteration for the 32-bit adder experiment.                | 95 |

# List of Tables

| 2.1 | Experimental results for SKETCHILOG                                    | 23 |

|-----|------------------------------------------------------------------------|----|

| 3.1 | The common error library rules currently implemented in FUDGEFACTOR    | 31 |

| 3.2 | Experimental results for FUDGEFACTOR.                                  | 40 |

| 3.3 | Additional experimental data for FUDGEFACTOR.                          | 41 |

| 4.1 | Complexity of GLIFT models before and after simplification.            | 57 |

| 5.1 | The public, designer-facing interface for the Nasadiya object.         | 68 |

| 5.2 | A list of delay calculation nodes used to build abstract delay models. | 75 |

# **1** Introduction

In the span of only a few decades, computers and digital communications have exploded in both utility and complexity, and are now ubiquitous in nearly every aspect of the modern world. All these computers and digital communications systems are made possible by automated processes to etch transistors, wires, and other physical electronic components onto small pieces of silicon called "chips". As demand for these chips has grown, engineers have succeeded in making progressively smaller and more efficient features on those chips, driving further demand growth. Gordon Moore famously observed [Moore, 1965] that the apparent result is an approximate doubling of integrated circuit complexity approximately every eighteen months.

Although this "law" has been losing steam and appears to be nearing its end [Mack, 2011], it has held true for decades, and the results are truly fantastic: For a few hundred US dollars (or less), nearly any person can buy a smart phone—a hand-held computer—able to do far more computation far more quickly than is needed to control a lunar spacecraft. [Hall, 1996] This power has been unlocked by extreme miniaturization: Modern chips often boast *billions* of transistors.

Billions of transistors are great for software designers. Those transistors are used to make more cunning, faster implementations of the devices that execute software programs. Software programmers effectively have been getting a free lunch: Their programs have been getting faster without any need to modify their program code.

Unfortunately, those billions of transistors are a practical nightmare for hardware designers. In contrast to software design, where convenient abstractions of the executing machine make software cost-free to expand, update, and run faster on better computers, the relative paucity of convenient and scalable abstractions for hardware design makes every modification a major event. In the end, hardware design is entirely concerned with the placement, layout, routing, and timing of and between billions of actual physical components. Further, fabrication of a silicon chip is a time-consuming and expensive process [Maly, 1994], although the marginal cost of additional chip production is generally minimal. Combined, these factors mean that

#### **Chapter 1. Introduction**

increasing design complexity presents a serious financial and computational challenge to physical implementation. Making bigger circuits is not as simple as making bigger programs, and if a silicon chip has an error and needs to be updated, it can spell doom for the company's product.

Traditional approaches to managing this complexity revolve around raising the design's level of abstraction from the *Register Transfer Level* (RTL), where every logical component, memory element, and their connections is specified manually. So-called *High Level Synthesis* (HLS) approaches allow designers to write limited software programs and have them automatically transformed into RTL. While this has achieved some success, the best results are almost always obtained by hand; RTL design is here to stay.

In the face of multi-million dollar costs for design errors, increasing design complexity also makes debugging, or the process of reasoning about circuits to find and correct their errors, increasingly difficult and critical to project success [Foster, 2015]. Hardware designers are also becoming increasingly aware that their design errors can manifest in fiendishly subtle features of even functionally-correct implementations, and that so-called "side channels" can undermine the security of their designs [Lipp et al., 2018, Kocher et al., 2018, Becker et al., 2013]. For example, designs that require protection of a secret cryptographic key must be painstakingly designed and analyzed to ensure that non-functional properties of the design that may be visible to potential attackers (e.g., the power consumed by the chip during cryptographic operations, or the time spent computing those cryptographic operations) cannot reveal information that could be used to reconstruct that key material—even if the cryptographic operations are functionally correct and do not directly leak information about the key. Millions of dollars of corporate revenue relies on such side channel resistance [Markantonakis et al., 2009].

Further, because of the immutable and physically-constrained nature of fabricated circuit designs, hardware designers always want to find better, faster, smaller circuits that meet their requirements: Not only could better performance or lower power consumption differentiate their product from competitors', but a clever idea to reduce a circuit's area can directly increase profit margins by allowing more chips to be fabricated on a single wafer.

*Satisfiability* is a technique that can be used to automatically reason about surprisingly complex logical formulae—for example, formulae that define the behavior of some digital circuit. This thesis presents novel techniques based on satisfiability to help designers deal with each of these problems posed by increasing design complexity by enabling new forms of automated reasoning about those designs and their components. As many of these problems manifest in the level of the language used to design the circuits, we believe that applications and integrations of satisfiability into the language level is the right place to provide automated reasoning. However, before describing in detail how new integrations of satisfiability fit neatly into solving these problems, it is essential for the reader to understand some background knowledge.

| а | b | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Figure 1.1 – Truth table for the universal Boolean function NAND.

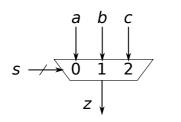

Figure 1.2 – Common Boolean logic gates. All gates except NOT have two inputs and one output; NOT has only one input.

### 1.1 Boolean Logic

While ubiquitous computing is only decades old, the foundations of electronic computation were laid nearly a century before the first stored-program electronic computer [Copeland, 2017]. George Boole first formalized the system of logic that bears his name in the early 19th century in his book "The Mathematical Analysis of Logic" and continued its development over the course of the following few years [Boole, 1847, 1854]. The logic system Boole developed, known as Boolean logic, underlies the implementation of every silicon chip of every computer that might be found in everything from so-called supercomputers to toaster ovens.

In Boolean algebra, values are either 1 or 0, also sometimes called true and false. Boolean functions, just like functions in conventional continuous real-valued algebra taught in grade school, compute a value by some operations on some input value(s). Unlike conventional algebra, those values are either true or false, and these functions can be completely specified in a *truth table* listing the truth value of the function for every possible input value.

For example, Fig. 1.1 shows the truth table for the so-called universal Boolean function NAND, which gets its name from the possibility of implementing any Boolean function using only the NAND function [Sheffer, 1913].

Boolean logic is not only the underpinning for the formalization of digital computation [Shannon, 1938], but also is very much at the core of the *implementation* of the digital circuits that power all modern computers. All silicon computer chips use etched transistors to implement so-called Boolean logic gates, or simple fixed-size Boolean logic functions, to realize the logical

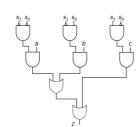

Figure 1.3 – An example schematic of Boolean logic gates for the function  $f(x_1, x_2, x_3) = (x_1 + \neg x_2) \cdot (\neg x_1 + x_3) \cdot x_2$ .

functionality the designers desire.

Fig. 1.2 shows some of the most common logic gates: from left to right, AND, OR, XOR, and NOT, which implement logical conjunction, disjunction, exclusive disjunction, and inversion, respectively. In plain terms, an AND gate computes 1 when both of its inputs are 1; an OR gate computes 1 when either or both of its inputs are 1; an XOR gate computes 1 when exactly one of its inputs is 1; and a NOT gate computes 1 when its single input is 0.

While logic gates are extensively used in this thesis in circuit schematics and design, Boolean logic functions are sometimes more naturally written with a more mathematical notation, where  $a \cdot b$  represents the conjunction of a and b (AND), a + b represents the disjunction of a and b (OR),  $a \oplus b$  represents the exclusive disjunction of a and b (XOR), and  $\neg a$ , represents inversion (NOT).

For example, the logic function  $f(x_1, x_2, x_3) = (x_1 + \neg x_2) \cdot (\neg x_1 + x_3) \cdot x_2$  describes the same function as the logic gate diagram in Fig. 1.3.

Unfortunately, the logic functions that fully describe most modern circuit designs are vastly more complicated than the one in Fig. 1.3. Modern circuit designs often have thousands of input variables and tens or hundreds of millions of logic gates. In the face of this kind of complexity, designers need help to reason about the behavior of their designs.

#### 1.2 Boolean Satisfiability

The Boolean satisfiability (SAT) problem is a well-known problem in computer science famous for being the first problem proven [Cook, 1971] to lie in a class of problems that are (widely believed to be) inherently difficult to solve, called NP-complete problems. It has also emerged in the past two decades as the premier encoding for many problems requiring reasoning about

Boolean logic.

Formally stated, Boolean SAT solvers determine if it is possible for a propositional formula  $\mathcal{P}$  to be true, as in the formula:

$$\exists \vec{x} : \mathscr{P}(\vec{x}). \tag{1.1}$$

In other words, given a logic function  $\mathscr{P}$  described as a set of clauses of Boolean logic statements, the problem is to determine if there is some input value that *satisfies* the function (i.e., when provided this input, the function  $\mathscr{P}$  computed 1). Typically, once a formula has been determined to be satisfiable, the *witness*, or the specific input value that satisfies  $\mathscr{P}$ , is trivial to report in addition to the confirmation of satisfiability.

For example, consider the formula for  ${\mathcal P}$  below.

$$\mathscr{P} = \prod_{i} P_i \tag{1.2}$$

If each  $P_i$  contains only literals, inversions, and disjunctions of the same, this kind of formula is said to be in *Conjunctive Normal Form* (CNF), because it is the conjunction (Boolean AND) of a set of clauses  $P_i$ . The formula is true if all of its clauses  $P_i$  are simultaneously true under some assignment to the variables in those clauses. This form of problem is notable because any logic function can be transformed into CNF by the Tseitin transformation [Tseitin, 1983], and because Boolean SAT solves problems provided in CNF.

For a concrete example, consider the set of clauses below.

$$P_{1} = (x_{1} + \neg x_{2})$$

$$P_{2} = (\neg x_{1} + x_{3})$$

$$P_{3} = x_{2}$$

(1.3)

These clauses together represent following function.

$$\mathcal{P} = P_1 \cdot P_2 \cdot P_3$$

$$\mathcal{P} = (x_1 + \neg x_2) \cdot (\neg x_1 + x_3) \cdot x_2$$

(1.4)

This formula—which happens to be the same formula described in the previous section—is satisfiable under the assignment  $(x_1, x_2, x_3) = 111$ , so a Boolean SAT solver given this problem would return an answer of SAT (i.e., satisfiable) and the witness 111.

Despite the inherent difficulty of solving NP-complete problems, certain algorithms for solving the Boolean SAT problem have been developed [Marques-Silva and Sakallah, 1999, Moskewicz et al., 2001] that often work quite well on modern hardware to find solutions even on large problem instances with millions of clauses. Thanks to techniques like conflict analysis and

Figure 1.4 – An example of a miter circuit used to check the functional equivalence of a circuit F and a "golden reference" circuit G. Once this circuit is translated to CNF, a SAT solver can determine if F and G are equivalent under all input conditions.

conflict-driven clause learning and backtracking, modern SAT solvers like MiniSAT [Eén and Sörensson, 2003] have made Boolean SAT an attractive encoding for problems that arise in a number of domains, and the premier tool for reasoning about Boolean logic circuits.

Most relevant to this thesis, computer-aided design tools that help designers create digital circuits mostly moved from *Binary Decision Diagram* (BDD) based algorithms [Y., 1959, Akers, 1978, Lai et al., 1992] to Boolean SAT based algorithms [Goldberg et al., 2001, Sapra et al., 2003] soon after the turn of the century in order to cope with increasing design complexity.

This is a prime indicator that Boolean SAT is an effective and scalable way to reason about circuits. For example, SAT-based combinational equivalence checking is a prime application of SAT widely used in CAD. This is done by constructing a special circuit, called a *miter*, that represents the SAT problem (this circuit will be transformed into CNF like in  $\mathcal{P}$  above). A miter is a circuit designed to produce exactly one output value. This value represents the satisfiability of the logical formula described by the miter function.

For combinational equivalence checking, the structure of this miter is shown in Fig. 1.4: it is composed of the circuit under test and a functional reference circuit, and computes 1 when an input assignment induces the circuit under test to compute a value that is not equal to that computed by the functional reference circuit. In other words, a buggy circuit (i.e., one that is not logically equivalent to the functional reference circuit) will result in a satisfiable SAT problem instance and any witness returned by the SAT solver is a counterexample, or error trace, that shows the input conditions for which equivalence fails.

The widespread application of Boolean SAT to many problems in CAD and its success has renewed interest in other applications of Boolean SAT to other problems in digital circuit design and also in other forms of satisfiability problems and their potential applications.

Figure 1.5 – A chart from the 2014 QBFEVAL gallery shows the sorted performance (i.e., solver time, on the vertical axis) of various QBF-SAT solvers for hundreds of instances (horizontal axis). The existence of so many solvers and the ingenuity that results from possible glory in a regular competition symbolizes the innovation in QBF-SAT solver heuristics over the past two decades.

## 1.3 2QBF-SAT

One of these other satisfiability problems is known as a QBF-SAT problem: A quantified Boolean formula satisfiability problem. Similar to Boolean SAT, these problems ask to find the truth of the following propositional formula  $\mathcal{Q}$ , with the use of additional quantifiers allowed, as represented by the formula below.

$$\exists \vec{h} \,\forall \vec{x} : \mathcal{Q}(\vec{h}, \vec{x}). \tag{1.5}$$

In other words, the problem is to find a concrete value for  $\vec{h}$  such that  $\mathcal{Q}$  is satisfied *for any value of*  $\vec{x}$ . In fact, this is a special sub-type of QBF-SAT problem, known as an exists-forall 2QBF-SAT problem, so named due to the sequence and number of quantifiers in its logical statement.

Just as with Boolean SAT, QBF-SAT solvers have seen dramatic practical performance improve-

Figure 1.6 – An example of a 2QBF-SAT miter circuit. It is similar to the Boolean SAT miter used in equivalence checking. Here, some sketch S, which functionally depends on some existentially-quantified "hole" values h, is constrained to be equivalent to the "golden reference" circuit G.

ments in the span of only a few years [Lonsing et al., 2016]. Figure 1.5 shows a chart borrowed from the QBFEVAL'14 QBF Gallery [Janota et al., 2014 (published 2016, Jordan and Seidl, 2014]. This chart, which shows the performance of various solvers on all the instances they were able to solve in a 900-second timeout for various benchmarks, symbolizes the innovation in QBF-SAT solver heuristics over the past two decades. Although this chart only provides a snapshot of the contemporary state of the art, the annual competitions (continuing to this day) trace their roots back to the beginning of the century, and continue to promote innovation in QBF-SAT solver technology.

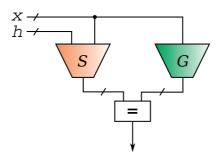

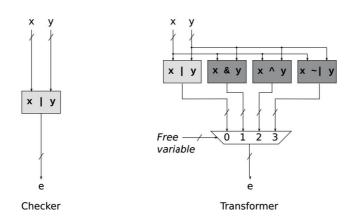

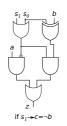

These kinds of satisfiability problems can also be represented as miters, like in Fig. 1.6. Note that this figure shows two distinct input vectors,  $\vec{h}$  and  $\vec{x}$ ; these represent the same existentiallyand universally-quantified variables in Eqn. 1.5 above. The miter circuit shown in Fig. 1.6 visualizes a simple 2QBF-SAT miter. Here we again have two circuits *S* and *G*, but now the functionality of *S* also depends on the existentially-quantified value  $\vec{h}$ . We call this kind of meta-circuit, where the exact functionality of the circuit is determined by some solverdetermined variables in  $\vec{h}$ , a "sketch". Once the 2QB-SAT solver finds a solution, the witness (or assignment to the  $\vec{h}$  variable) describes a circuit: the combinational logic circuit that results from the specialization of the problem instance  $\mathcal{Q}$  under a specific value for  $\vec{h}$ .

In this thesis, the existentially-quantified variable  $\tilde{h}$  is frequently referred to as a "hole". This terminology is not unique [Solar-Lezama et al., 2006], though it may seem odd upon first consideration. When a designer explicitly creates a circuit whose functionality depends on the value of a solver-determined variable, that "magic" variable is like a hole in the circuit: some vital but missing piece of information that is provided by the solver.

#### 1.4 Overview

This thesis explores how increased integration of satisfiability, particularly 2QBF-SAT, into the circuit design, debug, and optimization process can be useful to help designers better design,

analyze, and optimize complex circuits. After demonstrating a number of novel, useful, and reasonably scalable applications, we introduce a domain specific language well-suited not only to implementing those applications, but also to facilitating nearly arbitrary applications of 2QBF-SAT to circuit design or analysis.

Chapter 2 describes SKETCHILOG a language for circuit design with an integrated and transparent satisfiability solver. In SKETCHILOG designers provide two implementations of a desired circuit: a simple, but known-correct circuit (called the "golden reference" circuit), and a circuit with certain parts (e.g., values, logical functions) unspecified. These latter circuits, called "sketches", might be more complex but potentially better implementations of the same function in the golden reference circuit. To help the designer make a correct design, he or she is allowed to leave certain values or functions explicitly unspecified, and the satisfiability solver determines if there is a way to complete the sketch so that it is functionally identical to the golden reference circuit under all input conditions.

Chapter 3 describes FUDGEFACTOR a circuit debugging aid that uses a syntax-guided synthesis (SyGuS) approach and a satisfiability solver to localize trivial circuit design errors and provide semantically meaningful corrections. In FUDGEFACTOR the user provides a known-buggy design, at least one failing input vector that exposes the buggy functionality, and the correct response, along with some number of other correct responses to other input vectors. With this information, FUDGEFACTOR first finds suspect error locations using an existing error localization tool, then attempts to permute the design source code around those suspect locations, in order to provide potential alternative source code that *might* represent what the user actually wants and correct the error. A satisfiability problem is then constructed and solved to determine if the substitution of some or any of those alternatives corrects the bug in the known failing vector, and maintains correct functionality for other vectors. In this way, designers can automatically determine if a circuit bug is due to certain kinds of simple errors, without wasting time with a manual root-cause analysis. Further, a provided solution isn't just an opaque jumble of logic gates, but a meaningful, simple alteration directly to the source code.

Chapter 4 describes two satisfiability-based techniques to optimize GLIFT (gate-level information flow tracking) models of digital circuits. Circuits that need to keep certain information secret at all costs, like HSMs (Hardware Security Modules), or circuits that need to guarantee separation of data domains, like in HA (High Assurance) systems, are unfortunately very complex. Interactions between various components or sequences of actions can allow information to flow in undesirable ways need to be detected and avoided. Information flow tracking is a class of techniques that are used to analyze how information propagates throughout a system. Gate-level information flow tracking is especially relevant to the security of digital circuits, as it provides a precise way to model the flow of information through an actual implementation of a digital circuit. Unfortunately, these GLIFT models are very complex, and are often composed of many more gates than are contained in the circuit being modeled. By recognizing that the traditional mapping procedure used to produce GLIFT models ignores internal don't-care con-

#### **Chapter 1. Introduction**

ditions and there is often an opportunity for simplification, we first describe a 2QBF-SAT miter formulation and a solving procedure that can be used to find as many such simplifications as are possible without reducing the GLIFT model precision. We then describe another 2QBF-SAT miter formulation that can be used to go even further and make disciplined trade-offs in the precision and complexity of GLIFT models, allowing some imprecision at the expense of false positives under certain input conditions.

Finally, Chapter 5 introduces Nasadiya, a language for solver-aided hardware design and optimization. Nasadiya, like SKETCHILOG is based on Chisel, and embeds a 2QBF-SAT solver. However, Nasadiya provides much more flexible constraint specification, allowing design-based specification of constraints, and explicit solver access, which means the user specifies exactly how to apply the satisfiability solver to achieve his or her specific aims. The explicit solver access makes user-defined iterative solving procedures possible. Nasadiya also provides two simple but powerful and extensible modeling facilities, allowing models of extra-functional circuit properties like delay and area to be used inside constraints. Combined, these features make Nasadiya a powerful tool for automated reasoning about and design and generation of digital circuits. We finish with a case study, showing how Nasadiya can replicate automatically the kind of analysis and reasoning about adder circuits that would otherwise take man-months of engineer time.

# 2 Satisfiability for Circuit Design Assistance

For decades, digital circuit design has been done at the *Register Transfer Level (RTL)*, and this has been one of the key bottlenecks to productivity. One of the most glaring problems is that RTL design requires the designer to suffer through a tedium of minutae. Thus a number of researchers have repeatedly attempted to raise the design abstraction level [Camposano, 1990]. Progress in the area of *High-Level Synthesis (HLS)* has been less steady than originally anticipated, with various generations of tools reaching the market [Martin and Smith, 2009, Cong et al., 2011, Wang et al., 2014] and perhaps only in the last decade achieving some concrete commercial successes. Yet, RTL still offers a designer the most control, and skilled designers' analytical intuitions about structural circuit optimizations and trade-offs are usually superior to those achieved by high-level compilers.

We have extended a modern RTL design language, Chisel [Bachrach et al., 2012], and found inspiration from the software world [Solar-Lezama et al., 2006], to take a new approach: instead of abstracting away fundamental features of the architecture—as in High Level Synthesis—abstract only those details for which the designer has uncertainty, and let a satisfiability solver reason about the circuit to figure them out. We propose to allow designers construct their circuits in RTL as usual but leave *holes*, or explicit indeterminacies, in their designs, and accept the help of a satisfiability solver to complete their designs.

SKETCHILOG, the tool implemented by this author and introduced in the paper, "SketchiLog: Sketching Combinational Circuits" [Becker et al., 2014] by Andrew Becker, David Novo, and Paolo Ienne, reads a regular RTL "golden reference" specification of a desired functionality (typically a trivial un-optimized implementation) and an *incomplete* optimized implementation of the same functionality (a *sketch*). SKETCHILOG determines whether the holes can be filled (i.e., assigned specific, concrete values) so that the functionality of the sketch matches that of the specification under all inputs. If such a substitution exists, SKETCHILOG outputs fully functional Verilog of the completed and fully-verified solved sketch.

Although the domain of applicability is limited by a restriction to combinational circuits, this effectively relieves designers from responsibility for some of the most annoying details of

an architecture and entirely avoids a common source of maddening and time-consuming bugs. This represents a novel step forward toward using automation to increase designer productivity: rather than trying to hide details from the user and automatically implement the best guess at the user's desired architecture, leave the designer to control all the details of the architecture, but allow a satisfiability solver to reason about the circuit to fill in whatever the designer did not specify.

## 2.1 Motivational Example

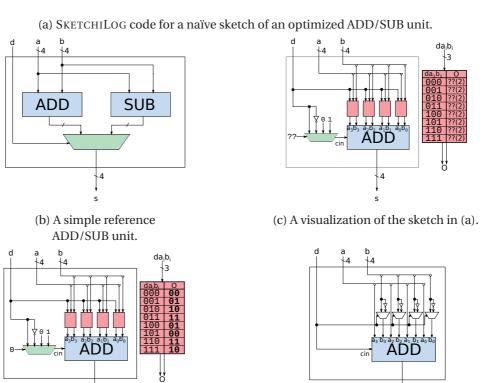

Any digital designer knows how to make an efficient two's-complement ADD/SUB unit. However, suppose for the sake of example that a designer does not remember *how exactly* to build the unit, but remembers that some voodoo with an adder's operands can implement a subtracter. Our designer might describe Fig. 2.1b as a reference and sketch Fig. 2.1c from fuzzy intuition—an adder, with inputs somehow permuted, can also implement a subtracter.

The core of this sketch can be expressed in SKETCHILOG as shown in Fig. 2.1a: a simple ripple-carry adder whose inputs are some undetermined function (a *black box* implemented with a look-up table of holes) of d and of the corresponding bits of the operands a and b. These holes correspond to the existentially-bound h bit vector in the QBF-SAT formula in Eqn. 1.5. SKETCHILOG solves the sketch and finds that the values shown in Fig. 2.1d for the holes in the look-up tables force the circuit to match to the reference design. Figure 2.1e shows what the solved sketch in Fig. 2.1d might look like after simple logic synthesis. Note that this logic synthesis is a very small and simple problem, where it can be sure the result will be high-quality; unlike large global logic restructuring, this is an area where traditional logic synthesis tools excel.

When a solution exists, correct hole values are always found and the resulting design is guaranteed to be functionally correct. If holes are not abused to give excessive architectural freedom, a given solution will usually be *very nearly as small and fast* as if the designer had no uncertainty at all. Our goal with SKETCHILOG is to provide useful and intuitive RTL language constructs which help designers focus on architectural intuition instead of nitty-gritty details, and yet can be encoded as a vector of unknown Boolean variables (holes).

## 2.2 Related Work

The idea of leaving the specific implementation of a program to a computer and, given a specification of the desired behavior, synthesizing an executable program has a long history [Manna and Waldinger, 1971, Pnueli and Rosner, 1989]. Full synthesis systems, like NuPRL [Constable et al., 1986] are based on deductive synthesis, where a designer specifies theorems about his or her desired application and guides an interactive process to create an executable proof.

da<sub>i</sub>b<sub>i</sub>

0

3

```

carries(0) := BB(io.d, 1);

for(i <- 0 until 4){

val fadd = new full_adder;

val unkn = io.d##io.a(i)##io.b(i);</pre>

2

3

4

val bb = BB(unkn, 2);

5

6

fadd.io.a := bb(0);

fadd.io.b := bb(1);

8

fadd.io.cin := carries(i);

sum_sigs(i) := fadd.io.s;

carries(i+1) := fadd.io.cout;

9

10

11

}

12

```

(d) A visualization of the solved sketch from (a).

4

(e) A more understandable representation of (d) that results from logic synthesis.

4

Figure 2.1 – A naïve sketch of an ADD/SUB unit. The solution (e) immediately reminds an inexperienced designer that the adder should be fed with signal a unmodified and with carry-in and b signals conditionally inverted upon the value of d.

Figure 2.2 – A visualization of part of the Chisel type hierarchy.

More frequently, though, such general pure synthesis techniques are not used for a variety of reasons. Instead, domain-specific tools use accessible high-level specifications to synthesize programs [George et al., 2013]. Recent work has also improved the utility of high-level synthesis tools, which use software-like input specifications to synthesize increasingly decent hardware implementations [Gupta et al., 2003, Nane et al., 2015]. However, these tools often produce sub-par implementations, and are not capable of discovering any fundamentally new architecture.

The mechanics behind SKETCHILOG lie along the same vein, and are very similar to those behind Sketch [Solar-Lezama et al., 2006]. Sketch is a software compiler that allows programmers to embed holes in software programs and with the aid of an additional functional reference program, constructs a 2QBF-SAT problem to find concrete values for those holes such that the solved program is functionally identical to the provided reference program. This allows the programmer to focus on the more general aspects of the architecture, while automating away most of the tedious task of handling corner cases or specifying exact constant values. All this is accomplished by constructing exactly the kind of 2QBF-SAT miter demonstrated in Fig. 1.6, and is conceptually broadly similar to the SKETCHILOG system we describe here, but developed specifically for software, and is unsuitable for circuit design.

#### 2.3 Implementation

Conceptually, SKETCHILOG translates both the sketch and the specification to pure Boolean functions  $\mathscr{S}$  and  $\mathscr{R}$ , respectively. Both functions take the same k-bit input vector x, but the sketched function also takes an additional m-bits parameter c, representing the m hole bits in the sketch. The problem reduces to a 2QBF-SAT satisfiability problem that can be solved by building the appropriate miter, as described in Sec. 1.3.

```

class Multiplexer extends Module {

1

2

var io = new Bundle {

val sel = Bits(INPUT, 1)

val in0 = Bits(INPUT, 1)

3

4

val in1 = Bits(INPUT, 1)

5

6

val o = Bits(OUTPUT, 1)

3

7

8

io.o := (~io.sel & io.in0) | (io.sel & io.in1)

9

10

11

// ... later instantiated:

12

13

val m = new Multiplexer;

```

Figure 2.3 – A simple example Chisel module.

In this case, the 2QBF-SAT problem instance is constructed to solve the following problem:

$\exists c \in \{0,1\}^m, \forall x \in \{0,1\}^k : \mathcal{R}(x) \Leftrightarrow \mathcal{S}(x,c).$

In other words, the object is to find an assignment for  $\vec{c}$  such that  $\mathscr{R}(x)$  and  $\mathscr{S}(x,c)$  are equivalent for all possible assignments to  $\vec{x}$ .

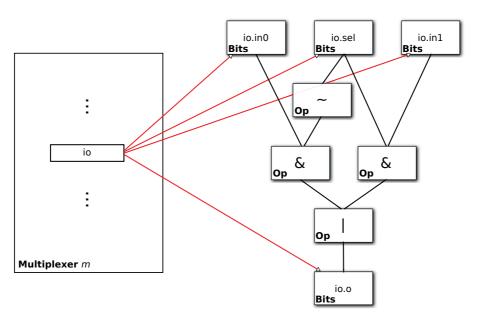

We chose the Scala-hosted Domain Specific Language (DSL) Chisel [Bachrach et al., 2012] as the base language upon which to implement our language features. Its use of Scala [Odersky et al., 2010] lends it easy extension and customization, and its scripting-like functionality makes sketching more intuitive and a better fit for circuit generators, which are very commonly used to describe the combinational components SKETCHILOG targets.

Chisel generates regular Verilog code and (solved) sketched designs can be used in standard EDA design flows. The language features added to Chisel could also be added directly to a VHDL or Verilog compiler, though this would likely require a much less intuitive syntax and deny the designer the very useful facilities that Chisel provides. For example, a designer uncertain about a logic function *can* but likely would *prefer not* to manually describe a look-up table filled with holes to be used in place of that function. Using Chisel allows us to provide the designer with simple syntactic constructs that takes care of the implementation and leaves the designer free to focus on the bigger picture.

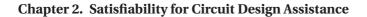

In Chisel, designs are represented as instances of the Module super-type, with a member i o that points to all circuit primary inputs and outputs. Figure 2.2 shows part of the Chisel class hierarchy.

These I/O signals are objects of the Node class sub-types, and are linked with objects of the Op class type. In Chisel, all designs are design generators: Chisel designs are Scala programs that instantiate Module objects with Node objects linked together by various Op objects.

Figure 2.4 shows a visualization of the example Chisel module in Figure 2.3. After the object graph is constructed in this *elaborate* phase, the Chisel library provides facilities to emit Verilog RTL from it. Figure 2.5 shows this two-phase process for compiling a Chisel design to Verilog.

Figure 2.4 – A visualization of an example Chisel object graph created with the instantiation of the Multiplexer module in Fig. 2.3.

Figure 2.5 – The complete tool flow required to turn a Chisel design into a Verilog design ready to be used by any standard EDA tool.

#### 2.3.1 SKETCHILOG

SKETCHILOG uses the same basic Chisel tool flow, but also adds a few new steps. The entire SKETCHILOG flow is described in Fig. 2.6. First, the designer creates his or her sketch in SKETCHILOG and names it sketch.scala, and creates a golden reference module whose functionality the sketch is designed to replicate exactly. Scala is invoked on the sketch, and a resulting "sketched Verilog" file sketch.sv is produced. This "sketched Verilog" file is identical to a regular Verilog file produced by Chisel, but crucially has special language support for specifying hole signals. All SKETCHILOG language constructs described below are compiled to Boolean logic referencing these special hole signals.

Next, optionally, the resulting sketch.sv and the designer-supplied golden reference module

Figure 2.6 – The complete tool flow required to turn a sketch (sketch.scala) and a golden reference module (spec.v) into a complete, solved result result.v ready to be used by any standard EDA tool.

spec.v are provided to the ABC [Brayton and Mishchenko, 2010] logic synthesis tool for simplification.

Once any desired simplifications are performed, both the sketched Verilog and the golden reference are provided to a custom-modified version of Odin II [Jamieson et al., 2010], which reads both the sketch and the golden reference, combines them into a miter, and writes the resulting circuit as problem.qbf, in a format understandable to the CEGIS 2QBF satisfiability solver [Solar Lezama, 2008].

The CEGIS solver is then invoked on this problem file. If a solution is found, it is written to problem.sol; if not, an error is produced and reported to the designer: there is no assignment to the holes that induces functional equivalence between the sketch and the golden reference. If a solution is successfully found, Odin II is again invoked, this time in a special mode that replaces hole signals in the sketched Verilog with the corresponding concrete values the solver found and wrote to problem.sol and writes the final resulting Verilog file to result.v.

#### 2.3.2 The Rules of the Code

On top of the standard Chisel features, we provide four intuitive constructs to support uncertainty in designs. Each construct can only be used to provide a value to Chisel data types (representing circuit elements) and never any regular Scala Int type (which are only useful to aid the construction of Chisel data types): the left-hand side of each expression below must be a Chisel data type.

$$x := ??(n);$$

This first construct, an uncertain constant (or *raw hole*) generator, serves as a substitute for a concrete signal value, and represents an n-bit constant signal whose value is undetermined. The value returned is a subclass of the Chisel Bits class, so it integrates seamlessly with regular Chisel code. This construct is the simplest both to understand and implement: SKETCHILOG infers an additional n-bits in the constructed satisfiability problem's existentially-quantified vector and will leave it to the satisfiability solver to find a concrete n-bit value that leads to a functionally correct design (if such a value exists).

All following constructs build upon this fundamental part of SKETCHILOG.

```

x := either choose signal1 or

signal2 or signal3;

```

This second construct, a selection operator, allows a designer to express an uncertain choice of signals in a design. SKETCHILOG automatically creates raw holes which represent constant values for the select inputs for newly-created multiplexers that choose one of the specified signals.

x := my\_array(2 \* ??(n) - 1);

This third construct, an undetermined index operator, allows a designer to express a partiallyconstrained index or bit in any indexed sequence data structure or Chisel signal type, respectively. It is more or less a further specialization of the second construct, selecting among the signals identified through every feasible index into my\_array (e.g., 1, 3, 5, etc.). Any out-ofbounds index is silently dropped from consideration—helping designers not to worry about edge cases. A *feasible set* associated with each hole is computed by static analysis of the index expression similar to classic bit-width analysis [Mahlke et al., 2001].

This powerful construct, an arbitrary logic function generator, constrains a signal x's value very loosely: only its dependencies and width are provided. Determination of exactly what

logic function to implement is left to SKETCHILOG. This adds  $2^{depends.width} * n$  bits to the existentially-quantified vector in the satisfiability problem. It must be used cautiously, however, as the number of hole bits grows exponentially with depends.width. Its misapplication with unreasonably large widths or number of dependencies dramatically affects scalability.

#### 2.3.3 Hardware Sketching vs. Software Sketching

Solar-Lezama et al. pioneered the sketching concept in a software context with a language called SKETCH [Solar-Lezama et al., 2006]. The same group toyed with the idea of sketching hardware [Raabe and Bodík, 2009], but to the best of this author's knowledge never moved beyond the drawing board. We build our hardware flow upon the CEGIS 2QBF-SAT satisfiability solver originally designed for software sketching. All other parts of our system are carefully tailored to the hardware design process and are either built from scratch, borrowed from other work with minor modifications (ABC), embraced and extended from other work (Chisel), or heavily modified from their original form (Odin II [Jamieson et al., 2010]).

The main difference (other than the domain of application) between software sketching as presented by Solar-Lezama et al. [Solar-Lezama et al., 2006] and our SKETCHILOG hardware design framework lays in the generation of the satisfiability problem. First, the software SKETCH framework needs to build the Boolean circuit models used to solve the satisfiability problem from an imperative C-like language by a sort of high-level synthesis. This inherits many difficulties from HLS; the generated models are often more complex than required, leading to increased solution times. In contrast, in our framework the Boolean circuit model is the actual sketch, which is directly constructed by the designer. As part of the model itself, our hole bit-widths are always known precisely while, in SKETCH, assumptions must be made to constrain the size of potential hole assignments. Second, software SKETCH allows the end user to reference a raw hole nearly anywhere in the code. Instead, we provide the set of constructs detailed in Section 2.3.2 to encapsulate holes and thus prevent the user from misusing them in ways that are possible in SKETCH. For example, software SKETCH code can contain a hole in place of a loop bound, resulting in potentially enormous models as the loop is unrolled. Such uncertainties in circuit structure cannot happen with SKETCHILOG.

#### 2.3.4 The Limitations of SKETCHILOG

SKETCHILOG is limited in scope, however, in two key regards. First, only combinational circuits are supported. This considerably restricts the domain of applicability, mostly to arithmetic or simple control structures (e.g., arbiters). Second, the empirical difficulty of solving 2QBF-SAT problems limits the feasible problem size, and solver performance is highly instance-specific. Minor changes in a designer's sketch might have a dramatic effect on solution time.

We believe these limitations do not fatally detract from the value of SKETCHILOG. While a limitation to combinational circuits seems severe, it still covers many use cases (especially for

Figure 2.7 – The core of a generator for a Kogge-Stone Adder. With SKETCHILOG, the designer focuses on the intuition of creating a binary tree of carryOp cells for each output and essentially ignores trivial but annoying boundary conditions.

datapath components), and simple pipelined circuits are functionally isomorphic to combinational models. This makes SKETCHILOG applicable to many arithmetic circuit generators, which are often some of the most tricky circuits to do well and get right.

Further, QBF-SAT solvers are an established and active area of research [Lonsing et al., 2016, Giunchiglia et al., 2001] and significant performance improvements are likely to follow in the near future. While many real-world sketches can already be solved, solver scalability will only improve.

## 2.4 Experiments

This section demonstrates our tool through simple but conceptually representative use-cases. For clarity, we have selected simple architectures which are described in any basic course in computer arithmetic, even if they are readily available in synthesis libraries—the purpose is to illustrate the simplicity of the approach and how SKETCHILOG could even benefit library writers themselves.

#### 2.4.1 Prefix Adders

The problem of adding two binary numbers as quickly as possible reduces to the problem of computing the carry signals  $C_i$  (represented in the form of a *generate* and *propagate* signal pair) for all bit positions i [Ercegovac and Lang, 2004, Parhami, 2010]. The computation of the carry signals can be posed in the form of a series of associative but non-commutative operations:

$$C_i = GP_i \star GP_{i-1} \star \dots \star GP_1 \star C_0 \tag{2.1}$$

The ripple-carry implementation is an easy reference for SKETCHILOG but it is faster to compute all carry signals independently: they can be computed fully in parallel as binary trees of **\*** operators, resulting in a *Kogge-Stone Adder* represented in Fig. 2.7. Even such a simple

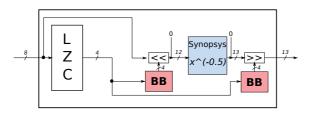

Figure 2.8 – Complex adaptation of an IP component. The intuition is that the shifters and leading zero counter (LZC) will help to scale the input into the component's domain and to correctly re-scale the output. The exact control logic is left to our tool.

structure requires careful attention to detail in the code: instantiating a complete binary tree is not possible for many i and ifwidth is not a power of two, the largest tree is itself incomplete. Fig. 2.7b shows the actual code needed in SKETCHILOG to generate the correct hardware, using two of our SKETCHILOG-specific Chisel syntax extensions. Note the design is not obfuscated by clumsy boundary tests: the designer simply says "connect regularly if you can, or else find a suitable constant".

# 2.4.2 Sketching to Enable Design Re-Use

Suppose a designer would like to use a library component like a Synopsys DesignWare [Synopsys, 2018b] inverse square-root unit. Unfortunately, that IP component requires the input to be in the range  $\left[\frac{1}{4},1\right)$ , a restriction not adapted to the domain required by the designer. The designer would rather create an adaptation interface than re-implement the unit from scratch. Elementary algebra suggests a variable shift at the input and output of the unit. Intuitively, there must be a correlation between the magnitude of the input and the scaling factors. Unfortunately, finding the exact relations is tricky and error prone. Instead, the designer can construct a general architecture with just his or her intuition (see Fig. 2.8) and these lines:

```

val pre_shift_amt = BB(zero_count, 4);

val post_shift_amt = BB(zero_count, 4);

```

These lines specify that the shift amounts depend *somehow* on the signal zero\_count and are 4 bits wide. When run with an extra sketched adjustment for the border cases against a trivial infinite-precision look-up table reference, SKETCHILOG finds the correct implementation— and automatically infers essential but trivial details, like that the input shift amount must be even to re-scale the output without loss of precision.

# 2.4.3 Strength Reduction of a Constant Divider

Our final example shows the case, common in arithmetic circuits, of finite precision operations implemented by simpler operators with so-called *magic numbers*. One well-known example

#### Chapter 2. Satisfiability for Circuit Design Assistance

Figure 2.9 – A sketch of a possible strength reduction for constant division with a near-powerof-two divisor. By using a full-precision multiplier and discarding some bits of the result, in many cases the solver can find assignments to the holes such that the imprecision of this approximation is not visible on the outputs.

is the inverse square-root approximation found in, among other places, the *Quake III* video game source code [Lomont, 2003].

In our example, a designer wants to devise an efficient implementation of a fixed-point constant division unit with a near-power-of-two divisor (e.g., 65,535). Figure 2.9 shows how this might be sketched. A simple right shift is a passable approximation, but is not exact. The designer's intuition is again simple: perhaps there are some integers x, y, and z (represented in the figure as holes), such that  $(i \cdot x + y) \gg z \equiv \frac{i}{65535}$ . In other words, maybe some unknown numbers define a simple affine approximation that, in the face of limited precision, is exact. Such values do exist in this case, and SKETCHILOG finds a correct design significantly smaller than a naïve DesignWare divider with a constant operand.

# 2.5 Experimental Results

We sketched the circuits described in Section 2.4. We also sketched a few other adders (a Brent-Kung and *hybrid* prefix adders, which lie between the Kogge-Stone and the Brent-Kung). RippleCarry is a non-sketched ripple-carry adder. Expanded\_InvSqrt is the Section 2.4.2 example; Raw\_InvSqrt is the IP used inside. DW\_Const\_Divider is a DesignWare divider with a constant divisor. We run SKETCHILOG both with and without a sketch pre-optimization pass, where the sketch circuit model is first run through simplifying logic transformations in ABC. Some statistics on these sketches and CEGIS solver runtimes for these problems are reported in Table 2.1.

In our experience, this pass often tends to *hurt* solver performance as often as it helps, but it's possible improved heuristics and different transformations that are exclusively beneficial to solver performance. In any case, the resultant "optimized" circuit's AIG depth and size are shown after ABC simplifies it with structural hashing and SAT sweeping. We did not resynthesize these circuits in, for example, Synopsys DesignCompiler [Synopsys, 2018a], because we are not concerned with super accurate results accounting for cell libraries, etc. Instead, we are more interested in the structural changes at the gate level, and ABC's integrated AIG depth reporting is more than adequate to give a sense of how the structural delay changes.

| Experiment       | Width | Hole<br>Bits | Unopt.<br>Time (s) | Opt.<br>Time (s) | AIG<br>Depth | AIG<br>Nodes |

|------------------|-------|--------------|--------------------|------------------|--------------|--------------|

| KoggeStone       | 16    | 427          | 3.732              | 3.799            | 12           | 229          |

| Hybrid_max1      | 16    | 509          | 1.681              | 1.450            | 12           | 217          |

| Hybrid_max2      | 16    | 368          | 0.697              | 0.901            | 13           | 196          |

| BrentKung        | 16    | 334          | 0.842              | 1.048            | 16           | 160          |

| RippleCarry      | 16    | 0            | n/a                | n/a              | 32           | 131          |

| KoggeStone       | 23    | 713          | 22.414             | 24.383           | 12           | 379          |

| Hybrid_max1      | 23    | 902          | 6.544              | 8.374            | 13           | 345          |

| Hybrid_max2      | 23    | 570          | 3.434              | 3.112            | 15           | 296          |

| BrentKung        | 23    | 522          | 2.884              | 3.339            | 18           | 237          |

| RippleCarry      | 23    | 0            | n/a                | n/a              | 46           | 187          |

| KoggeStone       | 32    | 992          | 93.620             | 85.064           | 14           | 545          |

| Hybrid_max1      | 32    | 1754         | 27.984             | 40.008           | 14           | 529          |

| Hybrid_max2      | 32    | 1166         | 19.772             | 19.871           | 15           | 488          |

| BrentKung        | 32    | 720          | 10.558             | 12.256           | 20           | 333          |

| RippleCarry      | 32    | 0            | n/a                | n/a              | 64           | 259          |

| Expanded_InvSqrt | 8/13  | 96           | 1.131              | 0.928            | 370          | 4093         |

| Raw_InvSqrt      | 8/12  | 0            | n/a                | n/a              | 371          | 4002         |

| ConstDivision    | 32    | 40           | 26.867             | 7.960            | 84           | 1152         |

| DW_Const_Divider | 32    | 0            | n/a                | n/a              | 255          | 2007         |

| ConstDivision    | 64    | 73           | 3373.790           | 333.083          | 164          | 4400         |

| DW_Const_Divider | 64    | 0            | n/a                | n/a              | 529          | 6291         |

Table 2.1 – Experimental results detailing instance bit-width, CEGIS solver runtime both with and without an optimization pass, total number of hole bits, and critical path delay (AIG depth) and area (AIG size) for the resulting completed design.

Our data show that for most experiments, the solver runtime is low enough to enable SKETCHILOG'S use as a real design aid. The adder experiments in particular show that our framework is scalable enough to be used as part of a standard design flow, at least for some important circuits. The inverse square-root example demonstrates that the described sketching constructs require very little overhead in the final solved circuit.

# 2.6 Conclusions

RTL design is here to stay—it may be complemented by higher level abstractions, but likely will not be supplanted.

We demonstrate here some first attempts at a new way to improve RTL design by allowing designers some explicit indeterminacy in designs. Despite the simplicity of our examples, the potential benefits of sketching circuits are clear: SKETCHILOG removes the burden of those small details which often cause errors, and are most annoying to get exactly right. It is this kind of precise reasoning at which satisfiability solvers truly excel.

Since a golden reference circuit is assumed to be available (of any quality—hence naturally simple to write and debug) and the 2QBF-SAT formulation ensures functional equivalence to this reference design, SKETCHILOG not only takes the dirty work from the designer but also

guarantees that the resulting design is correct. On the other hand, if *filling in the holes* and obtain a working circuit is impossible, SKETCHILOG immediately reports so.

Although in some domains, like digital arithmetic, the tool is already able to produce practical results, it remains ripe for further exploration, extension, and improvement. One example can be found in Chapter 5 of this thesis. Other future work might switch to other, potentially more powerful satisfiability solvers; increase the number of syntactic constructs to express design uncertainty without resorting to raw holes; attempt to use a sort of bounded model checking to handle sequential circuits, or more.

More broadly, designers might also be interested in other ways satisfiability solvers can be used to make their lives easier. For example, designers might have an existing design they wish to debug, or may not have any golden reference circuit with which to formally compare behavior. Happily, the next chapter discusses just such an application and provides a novel, practical solution to avoid the need for a golden reference circuit.

# **3** A Satisfiability-Based Approach to Localizing and Correcting RTL Errors

Functional verification is often a difficult part of the digital circuit design process, and occupies up to two thirds of the design cycle [Foster, 2015]. In general, there are at least two ways to reduce the time spent on this part of the design process: Either make it easier to develop functionally-correct circuits from the beginning, or improve circuit debug and verification tools. The previous chapter took the former approach; this chapter describes a technique for the latter approach.

To better understand why we take this approach, it helps to understand the broader context in which these tools are used. Formal verification tools typically return a counterexample when verification fails, and this counterexample is used in a subsequent debugging process (i.e., error localization and correction) to understand the bug and devise a fix. This is sometimes laborious and often relies heavily on designers' expertise and experience. Tools exist to help automate error localization and correction, but most (though not all) work on the subject has either suggested repairs at the netlist level [Chung and Hajj, 1992, Chung et al., 1994], or tried to map netlist repairs back to RTL source code (e.g., [Jobstmann et al., 2005, Staber et al., 2012]), which is not always possible and can lead to incomprehensible repair suggestions.