## Network-Compute Co-Design for Distributed In-Memory Computing

THÈSE Nº 8749 (2018)

PRÉSENTÉE LE 7 SEPTEMBRE 2018 À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS LABORATOIRE D'ARCHITECTURE DE SYSTÈMES PARALLÈLES PROGRAMME DOCTORAL EN INFORMATIQUE ET COMMUNICATIONS

## ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

## Alexandros DAGLIS

acceptée sur proposition du jury:

Prof. P. lenne, président du jury Prof. B. Falsafi, Prof. E. Bugnion, directeurs de thèse Prof. G. Sohi, rapporteur Dr P. Faraboschi, rapporteur Prof. J. Larus, rapporteur

Τῆς παιδείας ἔφη τὰς μὲν ῥίζας εἶναι πικράς, τὸν δὲ καρπὸν γλυκύν. — Αριστοτέλης

> The roots of education are bitter, but the fruit is sweet. — Aristotle

To my family

# Acknowledgements

My PhD journey has undoubtedly been the most challenging and, at the same time, most rewarding so far in my life. A journey that transformed me into a better person and taught me the true value of perseverance, team work, empathy, and patience. I would not have been able to reach the finish line if it weren't for the wonderful people around me; people who were always there to magnify the joy of the best moments; people who would always support and help me push through the hardest times. To all of these people, I owe my deepest gratitude. It is therefore apposite to start this thesis by thanking them.

First and foremost, I am grateful to my advisors, Babak and Ed. Babak has been a constant source of stimulation to keep pushing myself out of my comfort zone, a practice instrumental to my success. He taught me the importance of asking the right questions and taking a step back to look at the big picture. Babak's attention to detail and quest for perfection confirms that the "the path of virtues goes through toils". I am grateful for the great group culture Babak has inculcated in the PARSA group, which forms strong ties between students; I truly hope to succeed in achieving the same with my future research group. Finally, I can't help but blame Babak for spoiling me regarding coffee. He made sure that PARSA always had arguably the best espresso at (at least) EPFL. As a consequence, it has become a real challenge to find passable coffee outside the lab... On the bright side, if everything else fails, I've acquired sufficient knowledge about great espresso to become a half-decent barista.

It was a true honor to have Ed as a co-advisor. Thanks to Ed, I was involved in a great research project of much wider breadth than my initial research direction plans, which were limited to a narrower classic computer architecture scope. His astonishingly strong networking and systems background and his immense industry experience have been truly inspiring and have played a

#### Acknowledgements

key role in broadening my research horizons. I want to thank Ed for that, and for always being exceptionally empathetic, generous, and pragmatic.

Next, I would like to thank Jim Larus, Guri Sohi, Paolo Faraboschi, and Paolo Ienne for the honor of serving in my PhD thesis committee. Hadi Esmaeilzadeh and Abhishek Bhattacharjee have been selflessly offering me invaluable advice and support in academic matters. Boris Grot has been a very close collaborator and mentor, from whom I have learned a great lot. In several ways, he has been like a third advisor to me. Stanko Novakovic and Dmitrii Ustiugov have been close collaborators in most of the work I did as part of my thesis and other exciting research projects, but have also been great friends. Thank you for making my PhD journey more fruitful and exciting!

An integral part of academia is continuous learning and bequeathing that acquired knowledge through teaching. For my academic inclination I am greatly indebted to the great teachers I've had throughout my life. I have been fortunate enough to have had several great teachers, who constantly inspired me to pursue knowledge and excellence. I would like to explicitly thank two of them here. First, my Computer Architecture professor and mentor throughout my undergraduate studies at NTUA, Nectarios Koziris. In addition to giving me invaluable advice on how to start building a successful career early on, he is also an excellent teacher whose enthusiasm and positivity inspired my passion for Computer Architecture. Second, I would like to deeply thank Giorgos Despotidis. Being an excellent violin teacher was the least of his qualities; a man of exemplary kindness and dignity, with a deep love for his discipline, he has been a role model for me in several aspects. Maestro, may you rest in peace. You are deeply missed...

The next group of people that deserves my gratitude is the PARSA lab. The strong collaborative group culture was among the best experiences during this PhD. My daily interactions with my peers have been a great source of learning. First, I'd like to thank Javier Picorel, my office mate for many years, with whom we've been through a lot: occasions good and bad, funny and sad. His positivity and support helped me keep my sanity. We had a really good run; I often reminisce about all the jokes and fun times we shared. Next, I'd like to thank Mario Drumond and Arash Pourhabibi for being not only great colleagues, but also awesome friends and neighbors. They have been a lot of fun to hang out and argue with. I'm grateful to Sotiria Fytraki and the "fantastic

four"—Stavros Volos, Onur Kocberber, Cansu Kaynak, and Djordje Jevdjic—who were senior PhD students when I first joined PARSA. I bugged them a lot, but also learned *a lot* from them. I will always very fondly remember our PARSA ski trips together and the legendary Las Vegas excursion after ASPLOS 2014. Finally, I would like to thank Mark Sutherland—on whom befell the demanding task of replacing Javier as my office mate, Sid Gupta—also my gym buddy who made sure I never skipped leg day, Hussein Kassir—our official FPGA prototype-er, Nooshin Mirzadeh, and Zilu Tian.

I want to thank PARSA's administrative and technical staff, for always offering top-quality support above and beyond their duty. Stéphanie has always been extremely friendly and helpful with every minor or major headache related to bureaucracy, event organization, French translation, etc., making sure the rest of us can focus on our academic goals and duties. Rodolphe, our remarkable sysadmin, made sure all lab compute infrastructure was running like clockwork, and was always available and responsive in the most critical situations (e.g., dealing with the joys of a whole cluster going down on a Saturday night, just a few days before a deadline).

I've been fortunate to have an amazing group of people to spend my limited leisure time with in Lausanne: enjoying good beer, watching movies, attending the long-established Burger Nights, or, of course, having our infamous philosophical discussions of critical importance regarding what constitutes a computer or a root or whether infinite sentences are a thing (yes, this is as confusing as it sounds). I want to thank Manos, Eleni, Pavlos, Nathalie, and Christos for making Lausanne feel like home. Of course, nothing would have been the same without the jolly Greek and EPFL gang: Stefanos, Natassa, Iraklis, Vasilis, Panagiotis, Stella, Matt, Onur, Jean, Farah, Apostolis, Thodoris, Myrsini, Katerina, Loukia, Iliana.

I am very grateful for to my friends from the good old times back in Greece, who are now spread out all over the world. Our emotional proximity makes up for the petty inconvenience of physical distance; the memories of all the great times we've had together are lifelong companions and sources of joy. I want to thank all of of these cherished friends. My dear high-school friends, Orestis, Vilma, Andreas, and Thodoris. My childhood friends Xenofon and Vasilis. My close friends and once-upon-a-time neighbors, Nicholas and Despina (a.k.a. Cuervo, and also the closest I've had to a sister). The "tsouvlia" team from the Rosarte choir: Thanos, Sofia, Sofia

#### Acknowledgements

Jr., Miranda. The NTUA gang: Leonidas, Mary, Nikos, Ignatios, Ersi. Rea, for her friendship, wisdom, support, and invaluable advice over the past decade. I am looking forward to happy get-togethers around the globe for years to come!

Last but not least, I want to thank my family, from the bottom of my heart, for their endless love, support, and encouragement, during my PhD and my whole life. My parents, Ioannis and Anna, for eagerly offering me more than I could ever ask for; for bringing me up in a loving environment; for teaching me all things important: principles, ethics, justice, empathy, gratitude, honesty... and so much more. I could not have asked for better parents, and for that I am extremely fortunate and grateful. My dearest brothers, Thanasis and Dimitris, have been the best company to grow up with. I am very proud of you both and feel blessed to have you. My grandparents—Alexandros, Anthi, Thanasis, Vasiliki—for living a hard life to provide a better future for their children and grandchildren. My dear uncles, Stathis, Fotis, and Dimitris; my aunt Maria, who has been like second mother, and my cousins Eleni and Theofanis for their unconditional love. Finally, my very own person and partner in crime, Kyveli. You have been my safe haven, inspiration and joy for the past decade, and I am looking forward to spending a lifetime with you. I love you.

This thesis would not have been possible without numerous funding sources. I am thankful to Babak for making sure I never had to worry about funding. My PhD research has been partially supported by an EPFL Fellowship, a Microsoft Research Fellowship, the *EuroCloud* project of the 7th Framework Program of the European Commission, the *Workloads and Server Architecture for Green Datacenters* project of the Swiss National Science Foundation, the Nano-Tera *YINS* project, the *Scale-Out NUMA* project of the Microsoft-EPFL Joint Research Center, and the CHIST-ERA *DIVIDEND* project.

-0C/000

Lausanne, August 1, 2018

A. D.

# Abstract

The booming popularity of online services is rapidly raising the demands for modern datacenters. In order to cope with data deluge, growing user bases, and tight quality of service constraints, service providers deploy massive datacenters with tens to hundreds of thousands of servers, keeping petabytes of latency-critical data memory resident. Such data distribution and the multi-tiered nature of the software used by feature-rich services results in frequent inter-server communication and remote memory access over the network. Hence, networking takes center stage in datacenters.

In response to growing internal datacenter network traffic, networking technology is rapidly evolving. Lean user-level protocols, like RDMA, and high-performance fabrics have started making their appearance, dramatically reducing datacenter-wide network latency and offering unprecedented per-server bandwidth. At the same time, the end of Dennard scaling is grinding processor performance improvements to a halt. The net result is a growing mismatch between the per-server network and compute capabilities: it will soon be difficult for a server processor to utilize all of its available network bandwidth.

Restoring balance between network and compute capabilities requires tighter co-design of the two. The network interface (NI) is of particular interest, as it lies on the boundary of network and compute. In this thesis, we focus on the design of an NI for a lightweight RDMA-like protocol and its full integration with modern manycore server processors. The NI capabilities scale with both the increasing network bandwidth and the growing number of cores on modern server processors.

Leveraging our architecture's integrated NI logic, we introduce new functionality at the network endpoints that yields performance improvements for distributed systems. Such additions include

#### Abstract

new network operations with stronger semantics tailored to common application requirements and integrated logic for balancing network load across a modern processor's multiple cores. We make the case that exposing richer, end-to-end semantics to the NI is a unique enabler for optimizations that can reduce software complexity and remove significant load from the processor, contributing towards maintaining balance between the two valuable resources of network and compute. Overall, network-compute co-design is an approach that addresses challenges associated with the emerging technological mismatch of compute and networking capabilities, yielding significant performance improvements for distributed memory systems.

**Key words:** datacenters, servers, network interface, network protocol, integration, co-design, one-sided operations, RDMA, distributed memory, remote memory

# Zusammenfassung

Die wachsende Popularität von Online-Diensten erhöht die Nachfrage nach modernen Rechenzentren rasant. Um mit Datenflut, wachsenden Benutzerzahlen und strikten Servicequalität-Einschränkungen zurechtzukommen, stellen Service-Provider massive Rechenzentren mit zehntausenden bis hunderttausenden von Servern bereit, die Petabytes von latenzkritischen Datenspeichern resident halten. Eine solche Datenverteilung und die mehrstufige Natur der Software, die von funktionsreichen Diensten verwendet wird, führt zu einer häufigen Inter-Server-Kommunikation und einem Fernspeicherzugriff über das Netzwerk. Daher steht das Netzwerk in Rechenzentren im Mittelpunkt.

Als Reaktion auf den wachsenden internen Datenverkehr in Rechenzentren entwickelt sich die Netzwerktechnologie rasant. Leichte Benutzerebene Protokolle, wie RDMA, und High-Performance-Fabrics haben Einzug gehalten, wodurch die Rechenzentrum-weite Netzwerklatenz dramatisch reduziert und eine noch nie dagewesene Datenübertragungsrate pro Server geboten wird. Gleichzeitig bringt das Ende der Dennard-Skalierung die Prozessorleistungverbesserungen zum Stillstand. Das Endergebnis ist eine wachsende Diskrepanz zwischen den pro-Server Netzwerkfähigkeiten und Rechenfähigkeiten: Es wird für einen Server-Prozessor bald schwierig sein, die gesamte verfügbare Datenübertragungsrate des Netzwerks zu nutzen.

Die Wiederherstellung des Gleichgewichts zwischen Netzwerk- und Rechnerleistung erfordert ein engeres Co-Design der beiden. Die Netzwerkschnittstelle (NS) ist von besonderem Interesse, da sie auf der Grenze von Netzwerk und Rechner liegt. In dieser Arbeit konzentrieren wir uns auf das Design einer NS für ein leichtes RDMA-ähnliches Protokoll und dessen vollständige Integration in moderne Mehrkern-Server-Prozessoren. Die NS-Funktionen skalieren sowohl mit der steigenden Netzwerk-Datenübertragungsrate, als auch mit der wachsenden Kernanzahl

### Zusammenfassung

moderner Server-Prozessoren.

Den Vorteil der NS-Integration unserer Architektur ziehend, führen wir neue Funktionalität an den Netzwerkendpunkten ein, die für vertelte Systeme Leistungsverbesserungen bringt. Solche Ergänzungen beinhalten neue Netzwerkoperationen mit stärkerer Semantik, die auf allgemeine Anwendungsanforderungen zugeschnitten sind, sowie auch integrierte Logik zum Ausgleichen der Netzwerklast über die mehreren Kerne moderner Prozessoren. Wir zeigen, dass die Bereitstellung umfassenderer End-to-End-Semantiken für NS ein einzigartiger Ermöglicher für Optimierungen ist, der die Softwarekomplexität reduzieren kann und erhebliche Lasten aus dem Prozessor entfernen kann. Dadurch kann sich das Gleichgewicht zwischen den beiden wertvollen Ressourcen Netzwerk und Rechenleistung aufrechterhalten. Das Co-Design von Netzwerk-Computing ist ein Ansatz, der die Herausforderungen im Zusammenhang mit der sich abzeichnenden technologischen Diskrepanz zwischen Rechen- und Netzwerkfähigkeiten anspricht und zu erheblichen Verbesserungen der Rechenzentrumsleistung führt.

**Stichwörter:** Rechenzentren, Netzwerkschnittstelle, Netzwerkprotokoll, Integration, Co-Design, einseitige Operationen, RDMA, verteilter Speicher, Remotespeicher

# Contents

| Ac | know    | vledgements                           | i   |

|----|---------|---------------------------------------|-----|

| Al | ostrac  | et (English/Deutsch)                  | v   |

| Li | st of f | igures                                | XV  |

| Li | st of t | ables                                 | xix |

| 1  | Intr    | oduction                              | 1   |

|    | 1.1     | Forms of Inter-Server Communication   | 3   |

|    | 1.2     | Thesis Goals                          | 4   |

|    | 1.3     | Thesis Contributions                  | 5   |

|    | 1.4     | Thesis Organization                   | 7   |

|    |         | 1.4.1 Bibliographic Notes             | 8   |

| 2  | Арр     | lication and Technology Trends        | 9   |

|    | 2.1     | Datacenter Services                   | 9   |

|    | 2.2     | Server Architectures                  | 10  |

|    | 2.3     | RDMA and Lossless Fabrics             | 11  |

|    | 2.4     | Rack-Scale Computing                  | 12  |

|    | 2.5     | The Emerging Network–Compute Mismatch | 14  |

|    | 2.6     | One-Sided Operations Versus RPCs      | 15  |

### Contents

| I | ICC | ONIC A  | rchitecture Features                  | 19 |

|---|-----|---------|---------------------------------------|----|

| 3 | The | Scale-C | Out NUMA Architecture                 | 21 |

|   | 3.1 | Obstac  | eles to Fast Remote Memory            | 23 |

|   | 3.2 | Scale-  | Out NUMA Overview                     | 24 |

|   | 3.3 | Remot   | e Memory Controller                   | 26 |

|   |     | 3.3.1   | Hardware/Software Interface           | 26 |

|   |     | 3.3.2   | RMC Overview                          | 27 |

|   | 3.4 | Comm    | unication Protocol                    | 30 |

|   |     | 3.4.1   | Handling Packet Loss                  | 31 |

|   | 3.5 | Softwa  | are Support                           | 33 |

|   |     | 3.5.1   | Device Driver                         | 33 |

|   |     | 3.5.2   | Access Library                        | 34 |

|   |     | 3.5.3   | Synchronization Library               | 36 |

|   |     | 3.5.4   | Messaging over One-Sided Operations   | 36 |

|   | 3.6 | RMC I   | Microarchitecture                     | 38 |

|   |     | 3.6.1   | Shared SRAM Structures                | 41 |

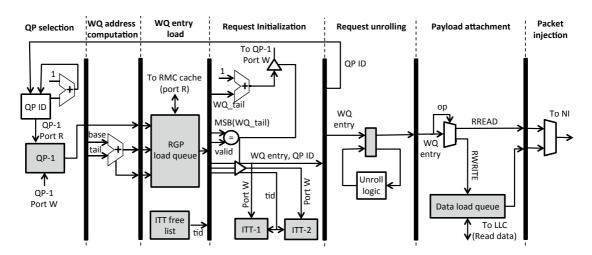

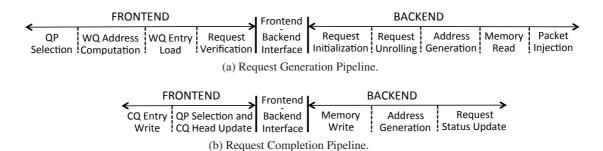

|   |     | 3.6.2   | Request Generation Pipeline           | 42 |

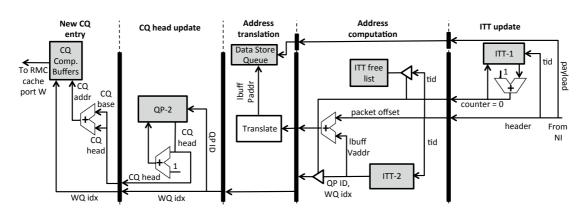

|   |     | 3.6.3   | Request Completion Pipeline           | 42 |

|   |     | 3.6.4   | Remote Request Processing Pipeline    | 44 |

|   |     | 3.6.5   | RMC Area and Power Estimation         | 45 |

|   | 3.7 | Chapte  | er Summary                            | 48 |

|   |     |         |                                       | 40 |

| 4 |     |         | mory Operations with Richer Semantics | 49 |

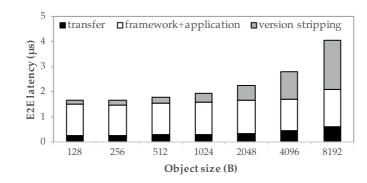

|   | 4.1 |         | c Remote Object Reads                 | 52 |

|   |     | 4.1.1   | In-Memory Object Stores               | 52 |

|   |     | 4.1.2   | Atomic One-Sided Operations           | 53 |

|   |     | 4.1.3   | Implications of Faster Networking     | 55 |

|   |     | 4.1.4   | The Case for SABRe                    | 56 |

|   | 4.2 | SABR    | e Design Space                        | 57 |

### Contents

|   |      | 4.2.1    | Destination-Side Concurrency Control            | 57  |

|---|------|----------|-------------------------------------------------|-----|

|   |      | 4.2.2    | Design Goals                                    | 59  |

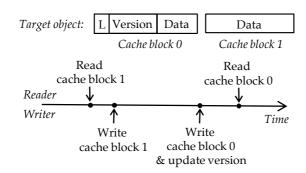

|   |      | 4.2.3    | Safely Overlapping Lock and Data Access         | 61  |

|   | 4.3  | LightS   | ABRe                                            | 62  |

|   |      | 4.3.1    | Address Range Snooping Implementation           | 63  |

|   |      | 4.3.2    | System Integration                              | 65  |

|   | 4.4  | LightS   | ABRe on Scale-Out NUMA                          | 68  |

|   |      | 4.4.1    | Integration with RRPP                           | 69  |

|   |      | 4.4.2    | Other Protocol and Hardware Modifications       | 70  |

|   | 4.5  | Chapte   | r Summary                                       | 71  |

| 5 | Inte | grated 7 | fail-aware Load Balancing                       | 73  |

|   | 5.1  | Theore   | tical Load Balancing Implications               | 76  |

|   | 5.2  | Load E   | Balancing in Practice                           | 79  |

|   | 5.3  | Toward   | ls Dynamic Load Balancing                       | 80  |

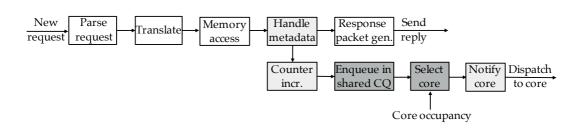

|   | 5.4  | Native   | Messaging                                       | 82  |

|   |      | 5.4.1    | Additional Benefits of Native Messaging         | 87  |

|   | 5.5  | Dynam    | ic Load Balancing Design                        | 88  |

|   | 5.6  | soNUN    | IA Extensions for Dynamic Load Balancing        | 89  |

|   | 5.7  | Chapte   | r Summary                                       | 91  |

|   |      |          |                                                 |     |

| Π | Im   | plemen   | tation and Evaluation of an ICONIC Architecture | 93  |

| 6 | Man  | ycore C  | Chip Design                                     | 95  |

|   | 6.1  | Key De   | esign Considerations                            | 98  |

|   |      | 6.1.1    | Application Requirements and Technology Trends  | 98  |

|   |      | 6.1.2    | QP-Based Interface for Remote Memory Access     | 99  |

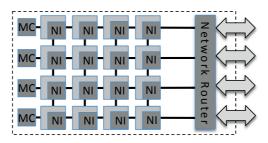

|   | 6.2  | Manyc    | ore Network Interfaces                          | 100 |

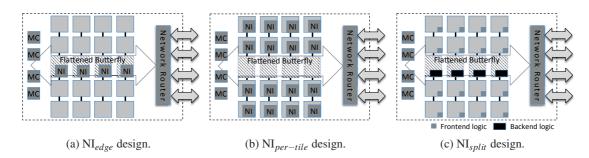

|   |      | 6.2.1    | Conventional Edge-Based NI                      | 101 |

|   |      | 6.2.2    | Per-Tile NI                                     | 104 |

|   |      |          |                                                 |     |

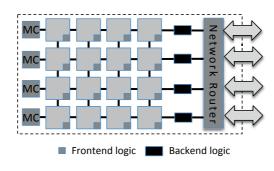

|   |       | 6.2.3  | Split NI                                       | 105 |

|---|-------|--------|------------------------------------------------|-----|

|   |       | 6.2.4  | NI Cache                                       | 105 |

|   | 6.3   | A Case | e Study with Scale-Out NUMA                    | 108 |

|   |       | 6.3.1  | soNUMA NI Scaling and Placement                | 108 |

|   |       | 6.3.2  | Other Design Issues                            | 110 |

|   | 6.4   | Metho  | dology                                         | 112 |

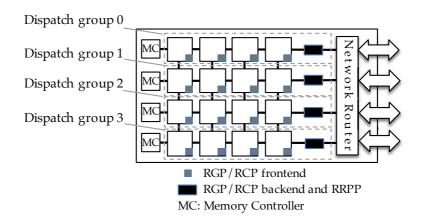

|   | 6.5   | Evalua | tion                                           | 114 |

|   |       | 6.5.1  | Latency Characterization                       | 114 |

|   |       | 6.5.2  | Bandwidth Characterization                     | 118 |

|   |       | 6.5.3  | Effect of Latency-Optimized Topology           | 120 |

|   | 6.6   | Chapte | r Summary                                      | 123 |

| 7 | Ligh  | tSABR  | e in Action                                    | 125 |

|   | 7.1   | Manyc  | ore NI Architecture Implications on LightSABRe | 125 |

|   | 7.2   | Metho  | dology                                         | 126 |

|   | 7.3   | Evalua | tion                                           | 129 |

|   |       | 7.3.1  | Latency and Throughput Characterization        | 129 |

|   |       | 7.3.2  | Conflict Sensitivity                           | 130 |

|   |       | 7.3.3  | FaRM Key-Value Store                           | 131 |

|   | 7.4   | Chapte | r Summary                                      | 134 |

| 8 | Tail- | Aware  | Balancing of µs-Scale RPCs                     | 135 |

|   | 8.1   | Manyc  | ore NI Design Implications                     | 135 |

|   |       | 8.1.1  | 4×4 Queuing System                             | 136 |

|   |       | 8.1.2  | 1×16 Queuing System                            | 137 |

|   | 8.2   | Metho  | dology                                         | 139 |

|   |       | 8.2.1  | Load Balancing                                 | 139 |

|   |       | 8.2.2  | Messaging                                      | 141 |

|   | 8.3   | Evalua | tion                                           | 142 |

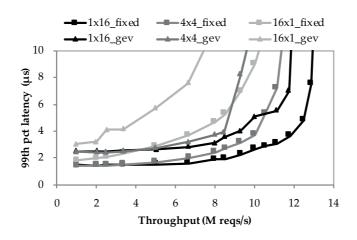

|   |       | 8.3.1  | Load Balancing: Hardware Queuing Systems       | 142 |

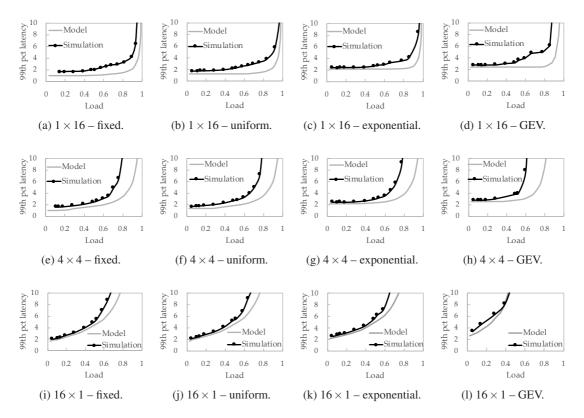

|     |      | 8.3.2    | Comparison to Queuing Model                | 143 |

|-----|------|----------|--------------------------------------------|-----|

|     |      | 8.3.3    | Hardware Versus Software Load Balancing    | 145 |

|     |      | 8.3.4    | Messaging Performance                      | 146 |

|     |      | 8.3.5    | Messaging Memory Requirements              | 147 |

|     | 8.4  | Chapte   | r Summary                                  | 149 |

|     |      |          |                                            |     |

| III | Re   | elated a | and Future Work                            | 151 |

| 9   | Rela | ted Wo   | rk                                         | 153 |

|     | 9.1  | soNUN    | IA and NI Integration                      | 153 |

|     |      | 9.1.1    | Partitioned Global Address Space           | 153 |

|     |      | 9.1.2    | Software Distributed Shared Memory         | 154 |

|     |      | 9.1.3    | Cache-Coherent NUMA                        | 154 |

|     |      | 9.1.4    | User-Level Messaging                       | 155 |

|     |      | 9.1.5    | Remote Memory Access                       | 156 |

|     |      | 9.1.6    | Coherent NI Integration                    | 157 |

|     | 9.2  | Hardwa   | are Support for Atomic Remote Object Reads | 158 |

|     |      | 9.2.1    | Hardware-Software Contract                 | 158 |

|     |      | 9.2.2    | Atomic Chunk Operations                    | 159 |

|     |      | 9.2.3    | Memory Subsystem Support                   | 159 |

|     |      | 9.2.4    | SABRe: One-Sided Operation or RPC?         | 160 |

|     |      | 9.2.5    | Destination-Side Concurrency Control       | 160 |

|     | 9.3  | Load B   | alancing                                   | 161 |

|     |      | 9.3.1    | Load Distribution and Imbalance            | 161 |

|     |      | 9.3.2    | Load Balancing Policies                    | 162 |

|     |      | 9.3.3    | Programmable NIs                           | 164 |

| 10  | Futu | re Rese  | arch Directions                            | 167 |

|     |      |          | are Heterogeneity in Datacenters           | 167 |

|     |      |          | ic Load Balancing Extensions               | 169 |

|     |      | 5        |                                            | -   |

xiii

| 10.2.1         | Advanced Load Balancing                             | 170 |

|----------------|-----------------------------------------------------|-----|

| 10.2.2         | Proactive Versus Reactive Load Balancing            | 171 |

| 10.2.3         | Scaling to CPUs with Hundreds of Cores              | 172 |

| 10.2.4         | Load Balancing Opportunities with PCIe-Attached NIs | 173 |

| 11 Conclusion  |                                                     | 175 |

| Bibliography   |                                                     | 177 |

| Curriculum Vit | ae                                                  | 201 |

# List of Figures

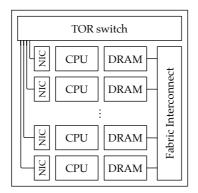

| 2.1  | Overview of a rack-scale computer.                                                   | 13 |

|------|--------------------------------------------------------------------------------------|----|

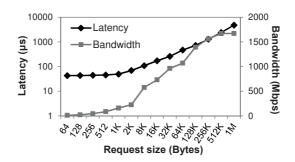

| 3.1  | Netpipe benchmark on a Calxeda microserver                                           | 23 |

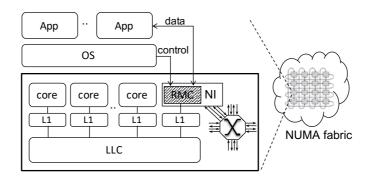

| 3.2  | soNUMA overview.                                                                     | 25 |

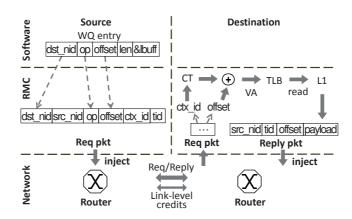

| 3.3  | QP interactions and memory access on the remote end for a remote read                | 27 |

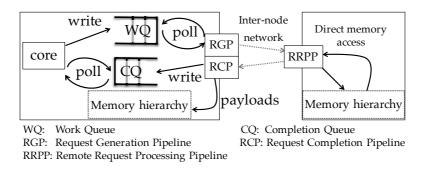

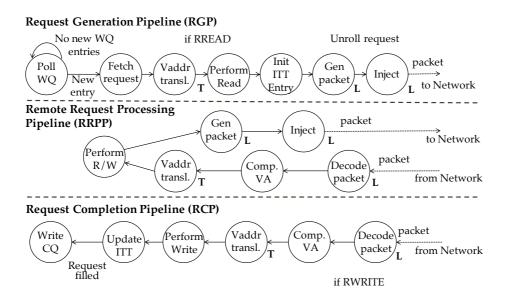

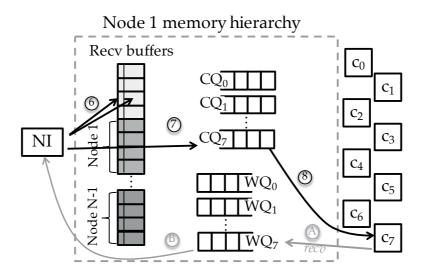

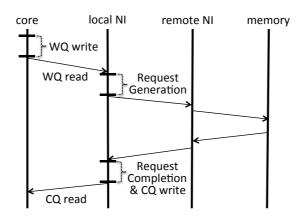

| 3.4  | Functionality of the RMC pipelines. The notation ' $L$ ' next to a stage indicates   |    |

|      | local processing in combinational logic; ' $T$ ' indicates a TLB access; the rest of |    |

|      | the states access memory via an MMU.                                                 | 28 |

| 3.5  | Communication protocol for a remote read.                                            | 31 |

| 3.6  | Computation of a PageRank superstep in soNUMA through a combination of               |    |

|      | remote memory accesses (via the asynchronous API) and local shared memory.           | 35 |

| 3.7  | Messaging emulation using one-sided operations.                                      | 37 |

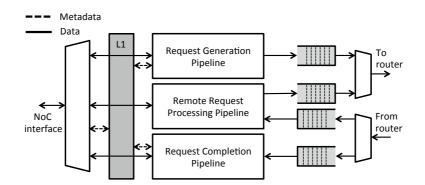

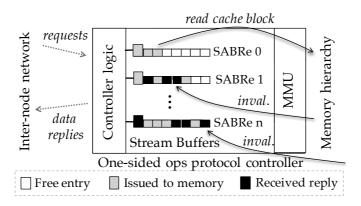

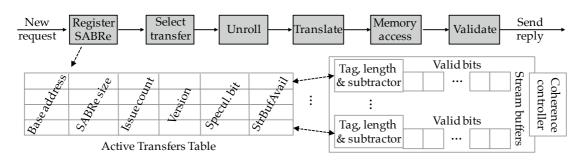

| 3.8  | RMC interface to the on-chip and off-chip network.                                   | 39 |

| 3.9  | The Request Generation Pipeline (RGP). SRAM structures appear shaded                 | 43 |

| 3.10 | The Request Completion Pipeline (RCP). SRAM structures appear shaded                 | 44 |

| 4.1  | End-to-end remote object read latency using the per-cache-line-version software      |    |

|      | atomicity check mechanism on FaRM over soNUMA                                        | 57 |

| 4.2  | Reader–Writer race example                                                           | 60 |

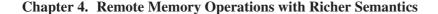

| 4.3  | LightSABRe: Leveraging stream buffers to safely overlap lock & data access.          | 64 |

| 4.4  | Block diagram of a LightSABRe-enhanced NI.                                           | 66 |

| 4.5  | soNUMA overview.                                                                     | 68 |

|      |                                                                                      |    |

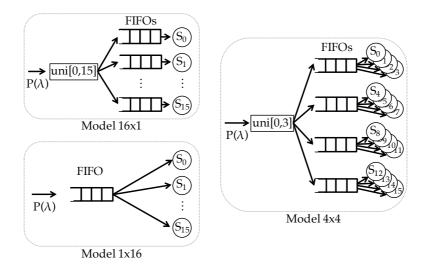

| 5.1  | Different queuing models for 16 serving units (CPU cores). $P(\lambda)$ stands for |     |

|------|------------------------------------------------------------------------------------|-----|

|      | Poisson arrival distribution.                                                      | 76  |

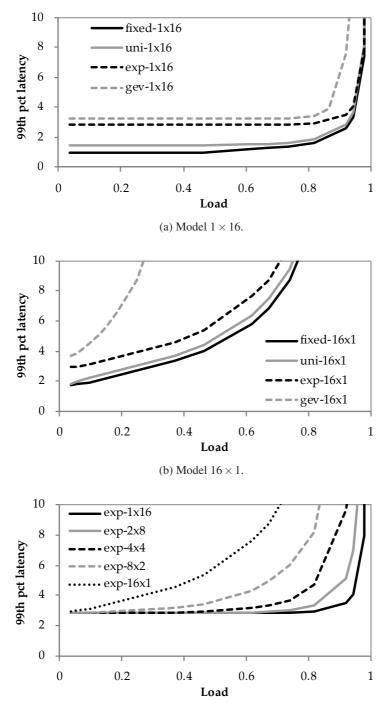

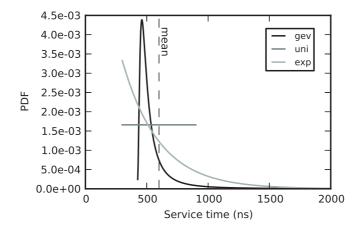

| 5.2  | Service time distributions.                                                        | 77  |

| 5.3  | Throughput vs. tail latency for different queuing systems and service time         |     |

|      | distributions.                                                                     | 78  |

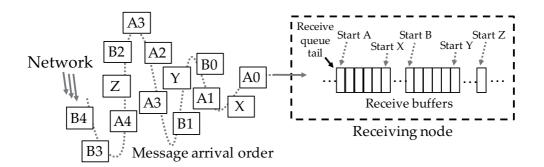

| 5.4  | Inter-packet interleavings of arriving multi-packet messages                       | 82  |

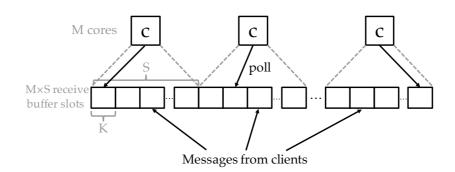

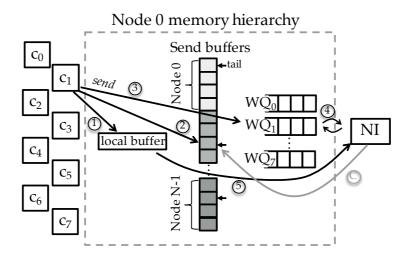

| 5.5  | Messaging illustration: Sender. Boxes marked as $c_i$ represent CPU cores          | 84  |

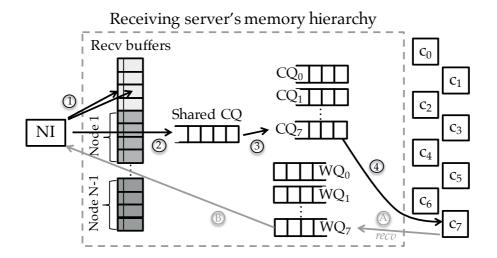

| 5.6  | Messaging illustration: Receiver. Boxes marked as $c_i$ represent CPU cores        | 85  |

| 5.7  | Messaging mechanism extensions for load balancing.                                 | 88  |

| 5.8  | Extensions of soNUMA's RRPP for load balancing support.                            | 90  |

| 6.1  | QP-based remote read.                                                              | 100 |

| 6.2  |                                                                                    | 100 |

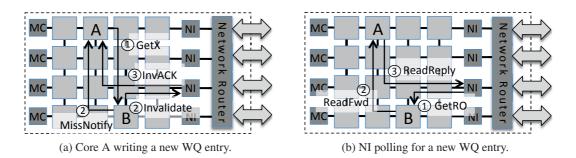

| 6.3  | Core and NI WQ interactions on an $NI_{edge}$ design                               | 101 |

|      | •                                                                                  |     |

| 6.4  | NI <sub>split</sub> design.                                                        | 105 |

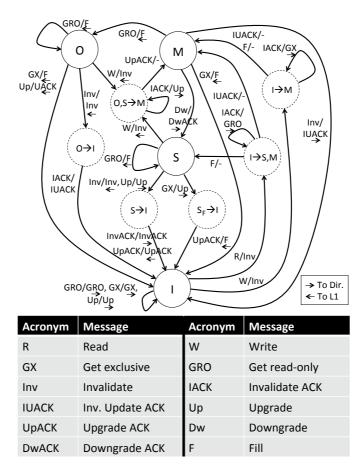

| 6.5  | NI cache coherence state diagram.                                                  | 107 |

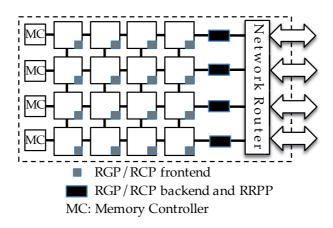

| 6.6  | Logical separation of soNUMA's RGP and RCP into a frontend and a backend.          | 109 |

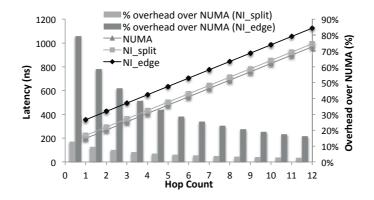

| 6.7  | Projection of the end-to-end latency of a cache-block remote read operation for    |     |

|      | multiple intra-rack network hops. Bars map to the right y-axis, lines to the left  | 116 |

| 6.0  | y-axis.                                                                            | 116 |

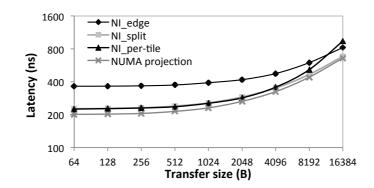

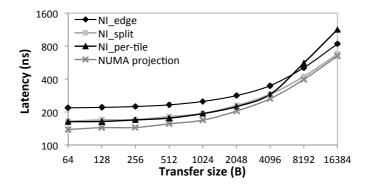

| 6.8  | End-to-end latency for synchronous remote reads.                                   | 117 |

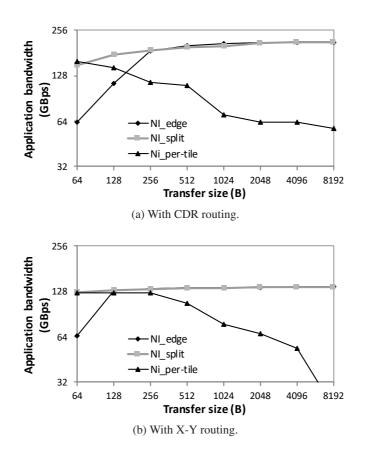

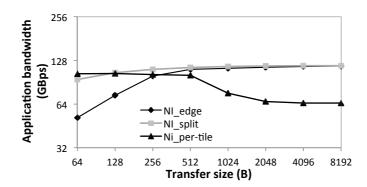

| 6.9  | Application bandwidth for asynchronous remote reads.                               | 119 |

| 6.10 | NI design space for NOC-Out-based manycore CMPs. Striped rectangles repre-         |     |

|      | sent LLC tiles.                                                                    | 120 |

|      | Latency for synchronous remote reads on NOC-Out.                                   | 122 |

| 6.12 | Application bandwidth for asynchronous remote reads on NOC-Out                     | 123 |

| 7.1  | Multicore chip layout based on NI <sub>split</sub> architecture                    | 126 |

| 7.2  | Microbenchmark with one-sided operations.                                          | 129 |

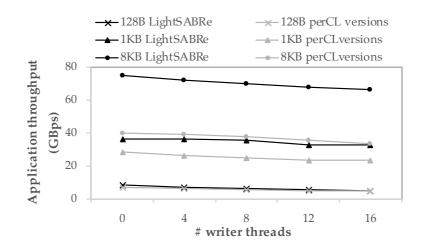

| 7.3  | Application throughput with increasing conflict rate.                              | 131 |

### List of Figures

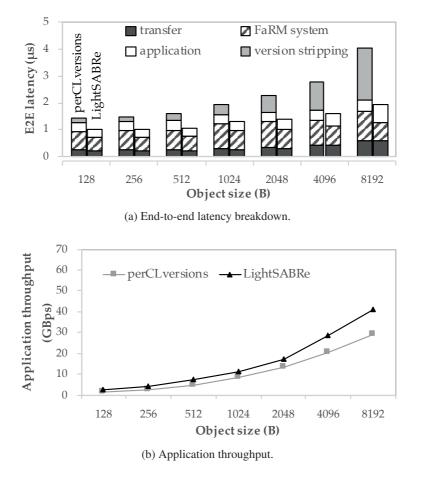

| 7.4 | FaRM KV store: baseline versus LightSABRe.                                              | 132 |

|-----|-----------------------------------------------------------------------------------------|-----|

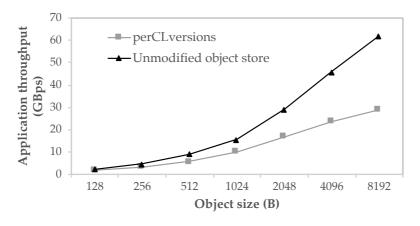

| 7.5 | FaRM local reads throughput comparison.                                                 | 134 |

| 8.1 | Message dispatch groups on a multicore chip                                             | 137 |

| 8.2 | Modeled service time distributions.                                                     | 140 |

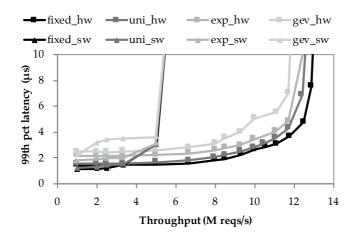

| 8.3 | Load balancing with three different queuing system implementations in hardware.         | 142 |

| 8.4 | Performance of three hardware load balancing implementations (1 $\times$ 16, 4 $\times$ |     |

|     | 4, $1 \times 16$ ) as compared to a theoretical queuing model, for four service time    |     |

|     | distributions: fixed, uniform, exponential, GEV. Tail latency shown as a multiple       |     |

|     | of the average service time S.                                                          | 144 |

| 8.5 | Load balancing performance of a $1 \times 16$ queuing system: Hardware vs. software     |     |

|     | implementation.                                                                         | 146 |

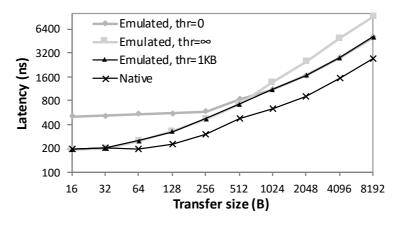

| 8.6 | Messaging latency.                                                                      | 147 |

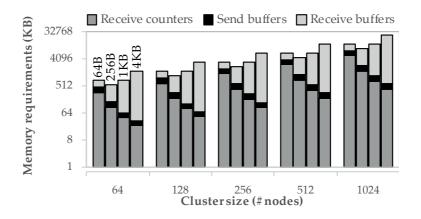

| 8.7 | Total memory footprint of messaging mechanism for different cluster and mes-            |     |

|     | sage sizes (64B, 256B, 1KB, 4KB)                                                        | 149 |

# List of Tables

| 3.1 | Estimated area and power for RMC SRAM structures                                    | 45  |

|-----|-------------------------------------------------------------------------------------|-----|

| 4.1 | Design space for one-sided atomic object reads.                                     | 58  |

| 5.1 | Throughput loss of different queuing systems at target 99th percentile tail latency |     |

|     | as compared to $1 \times 16$ , for different service time distributions             | 79  |

| 6.1 | Latency comparison of a QP-based model and a pure load/store interface              | 103 |

| 6.2 | System parameters for simulation on Flexus                                          | 112 |

| 6.3 | Zero-load latency breakdown of a single-block remote read                           | 115 |

| 6.4 | Zero-load latency breakdown of a single-block remote read (NOC-Out)                 | 121 |

| 7.1 | Flexus simulation parameters for LightSABRe on soNUMA                               | 127 |

| 8.1 | Estimation of buffering slots required for a peak target messaging throughput of    |     |

|     | 100Gbps, as a function of message size.                                             | 148 |

# **1** Introduction

Modern online services have gradually become an integral part of everyday life for billions of users. Web search, email, social networking, and e-commerce are a few examples of such popular massive-scale services. At the time of writing, Google claims 1 billion Gmail users and 1.5 billion search engine users, servicing over 3.5 billion search queries per day [42, 84]. Facebook has over 1.4 billion daily and 2.1 billion monthly active users [58], while massive-scale online retailers Amazon and Alibaba receive online orders corresponding to 3 and 12 million daily item shipments, respectively [172]. With every user constantly generating data and each user request probing data services handling petabytes of data, data access demands are growing dramatically. To cope with such data and userbase deluge, online service providers deploy several massive-scale datacenters, each populated with tens of thousands of servers.

In addition to the challenge of immense volume, online services have to be *interactive*, delivering seamless high-quality experience to all users; failing to do so may result in customer loss. Prior work has shown that users are sensitive to response latencies in the orders of hundreds of milliseconds [86, 131]. Experiences from real-life commercial settings corroborate this observation and highlight the dramatic impact of latency in company revenue: every 100ms of latency costs Amazon 1% in sales, while an extra 500ms in search page generation time drops traffic to Google by 20% [77]. It is therefore common for online service providers to set strict latency boundaries for servicing user requests as part of their service's quality metric, commonly

#### **Chapter 1. Introduction**

referred to as *Service Level Objectives* (SLO). To deal with such demands for low latency, it has become common practice for service providers to distribute the data across the memory of the datacenter's servers.

Keeping data memory resident removes the bottleneck of disk accesses, accelerating data access by up to five orders of magnitude (100ns versus 10ms). However, data distribution across thousands of servers unavoidably results in accesses to data residing in the memory of remote servers, thus requiring inter-server communication. Using commodity networking technology, servers and operating systems, communication delays can exceed  $100\mu s$  [149]; hence, accessing data in remote memory is  $1000 \times$  more expensive than accessing local memory ( $100\mu s$  versus 100ns). For the most challenging applications traversing large data structures that cannot be easily partitioned (e.g., graphs) or accessing many disparate pieces of data (e.g., key-value stores), distributed computation results in frequent inter-server communication, which may easily dominate the total time required to process a user request. Therefore, inter-server communication within the datacenter becomes a first-order performance concern.

The importance of communication has resulted in fast datacenter network infrastructure evolution. Advanced networking technologies such as high-performance lossless fabrics (e.g., InfiniBand) and Remote Direct Memory Access (RDMA) [124] that would typically only appear in High-Performance Computing environments have started penetrating the datacenter space as well, promising dramatic improvements in network bandwidth and latency. Modern fabrics continue improving network bandwidth, in contrast to silicon, whose seamless density scaling met an abrupt slowdown with the end of Dennard scaling. Datacenters already feature 10Gbps Ethernet, with 40Gbps already ramping up and 100Gbps just around the corner. InfiniBand, while still more expensive than Ethernet, already offers up to 300Gbps (InfiniBand EDR) and will soon double that (InfiniBand HDR) [81]. On the latency front, the evolution of optics and introduction of cut-through switches has enabled datacenter traversals in just a few tens of microseconds. Further down the line, advancements in silicon photonics foreshadow end-to-end optic communication, which could enable datacenter-wide communication in just a couple of microseconds, ultimately approaching fundamental bounds set by the speed of light. Overall, the dramatic improvement of

raw network performance capabilities lay the groundwork for large-scale distributed memory systems of unprecedented performance. However, reaping these network capabilities requires a major rethink of software, network protocols, and hardware architectures. In this thesis, we focus on protocol and architecture redesign for communication-intensive distributed memory systems.

### **1.1 Forms of Inter-Server Communication**

The majority of modern large-scale distributed memory systems, such as datacenters, is deployed in a scale-out fashion. The size of the system grows with the addition of more servers that tap into the system's network, and each server deploys its own OS instance managing its local resources (e.g., CPU, memory, storage). The most typical form of inter-server communication in such scale-out deployments is Remote Procedure Calls (RPCs), invoked over the network. RPCs are a very versatile form of inter-server communication, which has established them as the lingua franca of datacenters; all the internal services in modern datacenters communicate via RPCs. For instance, every user request for a Google service triggers more than 1000 RPCs within the datacenter [18, 91].

RDMA technology that has recently started appearing in the datacenter space, introduces an additional form of communication. As the name implies, RDMA—Remote Direct Memory Access—enables a server to directly read a remote server's memory. Unlike RPCs, this is a *one-sided operation*, i.e., it does not involve the remote end's CPU. One-sided operations come with simple memory access semantics and provide the opportunity to expose the aggregate memory resources of a scale-out deployment as a single global memory pool. The capability of direct access to a global memory pool brings back to scale-out architectures some of the features of scale-up architectures, without the drawbacks associated with the latter (e.g., cost, single-OS limitations, hurdles of verification and fault containment). Memory pooling enables faster access to remote data, lower memory overprovisioning requirements, and stronger resilience to load imbalance arising from skewed data popularity distributions [133, 136].

Despite their strengths, one-sided operations are semantically limited to simple remote memory

access. Hence, they cannot generally replace the versatile RPCs as the sole form of inter-server communication. Each of the two communication forms has its own merits and drawbacks, which we discuss in further detail in Section 2.6. We expect that future distributed systems will eventually deploy an appropriate combination of one-sided operations and RPCs, leveraging the strengths of each.

### **1.2 Thesis Goals**

The primary goal of this thesis is the drastic acceleration of inter-server communication in distributed memory environments. We aim to offer substantial improvements for both major communication models, one-sided operations and RPCs. To that end, we investigate the limits of inter-server communication latency and the impact of network evolution on the design of future server chips and the network stack itself, from the protocol layer down to hardware.

We start by focusing on one-sided operations and pursue a holistic system design to approach the lower latency bounds of remote memory access. We find that the evolution of networks has shifted the bottlenecks of inter-server communication from the physical network itself to the higher layers of the stack that comprises networking. Particularly, we identify conventional deep network stacks and the slow PCIe bus connecting the CPU to the Network Interface (NI) logic as the last major obstacles to low-latency inter-server communication. To overcome the first latency obstacle, we design a lightweight user-level and hardware-terminated protocol. In turn, the protocol's simplicity enables the design of a simple enough protocol controller that allows full on-chip of the NI logic, enabling rapid CPU-NI interaction. We show that NI integration not only accelerates existing forms of communication, but also opens up new opportunities for network-compute co-design that improves the efficiency of both one-sided- and RPC-based inter-server communication.

### Thesis statement:

Network interface integration and co-design with compute logic enables network endpoint operations with richer functionality and stronger semantics, resulting in significant performance improvements for distributed memory systems.

In this thesis, we advocate architectures leveraging Integration and CO-design of Network Interface and Compute logic (ICONIC architectures) as new building blocks capable of significantly boosting the performance of communication-intensive distributed memory systems.

### **1.3 Thesis Contributions**

This thesis introduces network-compute co-design and network interface integration as key design aspects to drastically improve the performance and versatility of communication-intensive distributed memory systems. We introduce basic design guidelines for an ICONIC architecture and demonstrate a number of new features such an architecture can deliver. We then implement a proof-of-concept instance of such an architecture and demonstrate its benefits.

First, we propose Scale-Out NUMA (soNUMA), a new architecture, programming model, and communication protocol that enables fast remote memory access by eliminating the last remaining major obstacles to low latency, namely the deep network stack and the slow interface between the CPU and the network. The heart of soNUMA is its on-chip integrated NI implementing soNUMA's protocol controller logic. The NI is not only integrated on chip, but also taps into its local CPU's coherence domain, which serves as a mechanism for rapid CPU-NI interaction. soNUMA is a representative of an ICONIC architecture—featuring an NI tightly coupled with compute logic—that serves as an appropriate baseline to demonstrate the new opportunities arising from network-compute integration and co-design.

Second, motivated by the vast semantic gap between one-sided operations and RPCs, we advocate the introduction of new one-sided primitives with richer semantics. As a concrete proposal of such a primitive, we identify an operation that is ubiquitously used by modern distributed object

#### **Chapter 1. Introduction**

stores, yet performed in a surprisingly inefficient manner in existing systems: atomic object reads from remote memory. We introduce *SABRe*, a new one-sided operation with the semantics of an *atomic remote object read*, and detail all the protocol and hardware additions required to support it. We demonstrate that the new SABRe operation yields significant performance gains and software simplification for distributed object stores.

Third, we show that the proximity of NI and compute logic in ICONIC architectures opens opportunities for dynamic load balancing mechanisms integrated as part of the NI logic. Such hardware support at the NI delivers significant throughput improvements under tight response time tail latency constraints for the most challenging, short-lived RPCs, where existing software solutions are unable to react to load imbalances in a timely manner. We show that such a dynamic load balancing solution outperforms pre-existing adaptive software-based or static hardwarebased load balancing mechanisms, by being the only solution that breaks the tradeoff between load imbalance resulting from static load distribution decisions and synchronization overheads of software-based load balancing practices.

Fourth, we address practical chip design challenges that arise when considering practical implementations of ICONIC architectures, which have to accommodate for the modern technological realities of growing CPU core counts and network bandwidth per server. We find that obvious approaches to scaling and integrating the NI in a manycore chip significantly hurt either latency or bandwidth. In contrast, careful splitting of NI functionality into core-NI interaction and data transfer, and independent scaling and placement of these two components enables an NI design that optimizes for both latency and bandwidth. Based on that insight, we propose NI<sub>split</sub>, a novel scalable NI design that outperforms alternative NI designs in both latency and bandwidth. Importantly, our NI design study demonstrates that the performance of remote memory accesss is primarily dictated by chip design choices rather than the hardware/software interface used to initiate remote data transfers. A specialized load-store interface for direct remote memory accesses is *neither necessary nor sufficient* for high performance. A less intrusive hardware/software interface based on a set of memory-mapped queues, when combined with proper chip and NI design, is equally competitive. Finally, we describe a concrete implementation of an ICONIC architecture based on the soNUMA protocol and our scalable chip design with  $NI_{split}$ , featuring our new SABRes primitive and our integrated dynamic load balancing mechanism. Our evaluation of the system demonstrates significant performance improvements, in terms of both latency and throughput, showcasing the strengths of tight NI integration and network-compute integration and co-design.

### **1.4 Thesis Organization**

This thesis is organized as follows. Chapter 2 provides background on key application and technology trends that necessitate a rethink in the way we design large-scale communicationintensive distributed memory systems, motivating a network-centric design approach. The rest of the thesis is organized in three parts:

- **Part I** introduces the key design principles of an ICONIC architecture, and a set of new features they offer. Chapter 3 presents the Scale-Out NUMA protocol and its specialized on-chip integrated NI. Chapter 4 propose SABRes, a new one-sided operation with rich semantics offering the capability reading objects from remote memory atomically. Chapter 5 introduces a novel dynamic load balancing mechanism of incoming network messages to CPU cores, integrated in the NI logic, demonstrating unique benefits of ICONIC architectures in RPCs handling.

- **Part II** is focused on the implementation and evaluation of an ICONIC architecture, based on the design presented in Part I. Chapter 6 introduces a novel chip design that addresses the practical challenges of scaling the performance of an on-chip integrated NI with the evolving capabilities of modern servers, in terms of CPU core counts and network bandwidth. Building on top of that chip design, Chapters 7 and 8 implement and evaluate the performance benefits of our proposed SABRes primitive and dynamic load balancing mechanism, respectively.

- Part III discusses related work (Chapter 9) and future research directions (Chapter 10).

Finally, Chapter 11 concludes the thesis.

### **1.4.1 Bibliographic Notes**

This thesis was conducted under the supervision of my advisors, Babak Falsafi and Edouard Bugnion. Portions of it are product of collaboration with three colleagues: Boris Grot, Stanko Novakovic, and Dmitrii Ustiugov. Chapter 3 is partially based on a conference paper published in the *Proceedings of the 19th International Conference on Architectural Support for Programming Languages and Operating Systems* (ASPLOS) in 2014 [134] and a patent granted by the US Patent & Trademark Office in 2017 [137]. Chapters 4 and 7 are based on a conference paper published in the *Proceedings of the 49th Annual IEEE/ACM International Symposium on Microarchitecture* (MICRO) in 2016 [40]. Finally, Chapter 6 is based on a conference paper published in the *Proceedings of the 42nd International Symposium on Computer Architecture* (ISCA) in 2015 [39].

# **2** Application and Technology Trends

Modern datacenters are evolving rapidly, being shaped by growing demands for online services. From a single server's design to the overall datacenter network architecture, the deployed platforms evolve in a scale-out fashion to meet the high volume demand at tight latency constraints. This chapter provides an overview of key software and hardware trends that highlight the role of networking in the datacenter, and motivate the need for tighter network-compute integration.

### 2.1 Datacenter Services

Today's massive web-scale services, such as web search, social networking, e-commerce or analytics, require tens of thousands of servers and petabytes of storage [175]. Increasingly, the trend has been toward deeper analysis and understanding of data in response to real-time queries. To minimize the latency, datacenter operators have shifted hot datasets from disk to DRAM, necessitating terabytes, if not petabytes, of DRAM distributed across a large number of servers.

Online services typically comprise several software layers, resulting in multi-tiered architectures. In the most basic model, datacenter traffic patterns are *north-south*, as every user request propagates through the different service tiers. As services are gradually offering richer features, inter-server communication patterns in the datacenter become *east-west*, which are more complex and unpredictable [168]. Typically, while the amount of north-south traffic is a function of incoming user requests, east-west traffic increases as a function of the rapidly increasing offered functionality per request, causing internal datacenter network bandwidth demands to double every 12–15 months [57, 157]. Every incoming user request triggers multiple software layer interactions, involving hundreds of servers. For instance, Amazon reports that the rendering of a single page typically requires access to over 150 internal services [48], while a single Google search query uses 1000 servers to retrieve an answer [46]. Latency considerations force Facebook to restrict the number of sequential data accesses to fewer than 150 per rendered web page [149].

Related work examining sources of network latency overhead in datacenters found that a typical deployment based on commodity technologies may incur over  $100\mu s$  in round-trip latency between a pair of servers [149]. According to the study, principal sources of latency overhead include the operating system stack, NIC, and intermediate network switches. While  $100\mu s$  may seem insignificant, communication time can end up dominating the overall latency of a user request, mainly for two reasons. First, every request results in long sequences of inter-server communication, as it goes through several internal datacenter service layers. Second many of these service layers mainly involve data retrieval with minimal computation per data item loaded (e.g., key-value stores). For example, read operations dominate key-value store traffic, and simply return the object in memory. With  $1000 \times$  difference in data access latency between local DRAM (100ns) and remote memory ( $100\mu s$ ), distributing the dataset, although necessary, incurs a dramatic performance overhead. In conclusion, inter-server communication is taking center stage as a major performance determinant of online services.

### 2.2 Server Architectures

Datacenters employ commodity technologies due to their favorable cost-performance characteristics. The end result is a *scale-out* architecture characterized by a large number of commodity servers connected via commodity networking equipment. Two architectural trends are emerging in scale-out designs.

First, System-on-Chips (SoC) provide high chip-level integration and are a major trend in servers.

Current server SoCs combine many processing cores, memory interfaces, and I/O to reduce cost and improve overall efficiency by eliminating extra system components. More recently, some SoCs went as far as integrating the network endpoints on the chip. For instance, Calxeda (now defunct) integrated the Ethernet controller on chip [44], a practice that Intel recently also started following with its Xeon D SoCs [13]. AppliedMicro's X-Gene2 server SoC [107] and Oracle's Sonoma [109] integrated an RDMA controller directly on chip. While the controller still communicates with the chip's memory hierarchy over DMA transfers, this is a clear effort to bridge the gap between the compute and the network.

Second, there is a growing trend for manycore server chips, motivated by the nature of online services, which operate on massive datasets, exhibiting little data locality and immense request-level parallelism. These characteristics result in CPU cores processing short-lived independent requests and spending most time waiting for data retrieval from memory [62, 91, 119]. The net result is that servers are gradually featuring more and more—potentially leaner—cores. Emerging server processors, such as Cavium's ThunderX series [110, 111], AppliedMicro's X-Gene 3 [115], Phytium's FT-2000/64 [112], Qualcomm's Centriq [113], and EZChip's TILE-Mx [56], already feature from several dozens to 100 ARM cores. Even the latest Intel and AMD x86 CPUs, which typically feature brawnier cores, are hitting the 30s range [114, 116]. For example, the latest Skylake Xeons offer up to 28 cores.

While both trends are beneficial for online services running on modern datacenters, they currently seem to evolve independently; it is, however, important to reconcile the manycore and network integration trends. Both are key to server efficiency, thus the two should be co-designed.

### 2.3 RDMA and Lossless Fabrics

RDMA [124] enables memory-to-memory data transfers across the network without processor involvement on the destination side. These direct data transfers from remote memory are also commonly referred to as *one-sided operations*. By exposing remote memory and reliable connections directly to user-level applications, RDMA eliminates all kernel overheads. Furthermore, one-sided remote memory operations are handled entirely by the adapter without interrupting the destination core. RDMA is supported on lossless fabrics such as InfiniBand [80] and Converged Ethernet [79] that scale to thousands of nodes and can offer remote memory read latency as low as a couple of  $\mu s$ .

Although historically associated with the High-Performance Computing market, RDMA is now making inroads into web-scale datacenters, such as Microsoft's and Google's [155]. Latency-sensitive key-value stores such as RAMCloud [138], Pilaf [127], FaRM [53, 54], HERD [89], and DrTM [171] use RDMA fabrics to achieve key-value lookups from remote memory at latencies as low as 5µs.

There are a number of limitations that are currently blocking the adoption of full datacenter-scale RDMA, such as the lack of integrated congestion management in the protocol and the difficulty of scaling lossless fabrics to networks of tens of thousands of nodes, a guarantee RDMA relies on to achieve high performance. The strong interest of massive online service providers, who also own the largest datacenters, in RDMA technology, is driving significant resources into research to address these challenges. However, it should be noted that even if these challenges remain unsolved, RDMA and RDMA-like solutions, such as the soNUMA architecture proposed in this thesis (Chapter 3), will remain highly relevant to datacenter architectures, as they can provide significant performance benefits. We discuss in the following section how such technologies can be leveraged to offer more powerful building blocks for datacenters.

### 2.4 Rack-Scale Computing

Rack-scale computing is a young field that recently started gaining traction from both industry and academia [5]. Rack-scale computing identifies the *rack* as an architectural block—instead of the typical *server* architectural block in today's datacenters—within which, all components are tightly integrated to deliver significant compute capacity at high efficiency in a contained scale.

Figure 2.1 represents a high-level view of such a rack-scale computer. In addition to the traditional

Figure 2.1 – Overview of a rack-scale computer.

Ethernet connections to a top-of-the-rack (TOR) switch for conventional networking with the outside world, all SoCs in the rack are directly attached to a secondary high-performance fabric interconnect. The key strength of rack-scale computers is that they offer high density of cores and memory that can rapidly communicate via integrated high-performance fabrics. In the near future, rack-scale computers will feature 1000s of cores and terabytes of memory in a rack form factor, with glueless fabrics offering high-bandwidth, low-latency interconnection. Such systems will be capable of replacing large-scale NUMA machines, as they will offer comparable performance at a fraction of the cost. Early examples of rack-scale systems are AMD SeaMicro [50], Boston Viridis [24], HP's The Machine [76], and Oracle's ExaLogic and ExaData [139]. The aggregate vast memory pool of a rack-scale computer can be seamlessly accessed using fast one-sided operations over the fabric, making these systems a great fit for computation on massive datasets that cannot be easily partitioned, hence remote memory access is unavoidable and frequent.

A rack-scale computer can offer enough resources to be used as a standalone solution for a family of medium-sized problems, or as even as a building block for future datacenters. For example, the RackOut architecture [136] demonstrates that organizing the datacenter as collection of rack-scale computers rather than a collection of servers can yield substantial utilization improvements under tight response time tail latency guarantees. Thus, even if systems with fully integrated networking and lightweight protocols will not outgrow current rack-scale solutions, they still represent excellent building blocks for future datacenter-scale deployments.

Our main focus on this thesis is on systems of contained scale, such as these rack-scale computers, where network-compute co-design and tighter integration will have the most dramatic impact. In such systems, inter-server communication performance is largely determined by the endpoints: the protocol executed on the CPU and network controller, and the flow of information between the CPU and the network controller. Furthermore, any software overhead added to the bare remote memory access latency imposed by the underlying hardware perceivably increases the end-to-end latency. We take a vertical system redesign approach to holistically tackle these major sources of inter-server communication overheads in rack-scale computers.

At datacenter scale, there are other factors that significantly affect inter-server communication performance, such as multi-hop topologies with several switches that add a measurable latency, oversubscribed network tiers, and long distances. However, these additional overheads of datacenter-scale communication will be gradually ameliorated. Rapid advancements in datacenter networking equipment (e.g., adoption of high-performance fabrics like InfiniBand) already offer datacenter-wide network roundtrips faster than  $20\mu s$  [28]. End-to-end optic networks at full datacenter scale are expected in the near future; such networks will allow datacenter traversals in a single  $\mu s$ , dictated by the speed of light. Thus, whether the performance of datacenter inter-server communication will converge with that of rack-scale computers, or rack-scale computers will emerge as building blocks in the datacenter space, we expect the contributions of this thesis to eventually be highly relevant even at datacenter scale.

# 2.5 The Emerging Network–Compute Mismatch

We are entering an era of intense technological turmoil, which, among others, will significantly affect the design of communication-intensive systems. Historically, compute logic has been dramatically faster than network communication and systems were designed around this basic assumption. However, technology advancements are bound to disrupt long-established balances. The slowdown of Moore's Law and the end of Dennard Scaling are leading to stagnating performance of general-purpose logic. At the same time, networks are evolving rapidly. On the

latency front, in-datacenter propagation delays approaching the fundamental limit imposed by the speed of light, enabling full datacenter traversals in just a couple of  $\mu s$ . On the bandwidth front, we continuous improvements that are expected to continue in the foreseeable future; the InfiniBand Trade Association's roadmap predicts a quadrupling of network bandwidth [81]. The net result is in the near future, balanced communication-intensive systems will have to be increasingly more frugal in the amount of computation spent per network message.

The emerging imbalance between CPU processing capacity and network capabilities has already started surfacing. To illustrate, at the time of writing, a high-end Mellanox InfiniBand NIC delivers 200Gb/s and 200M IOPS; this leaves even the highest-end server CPUs with fewer than 1000 cycles to complete a request associated with a single network packet. For example, the Xeon Platinum 8176 features 28 cores at 2.1GHz. In a 2-socket configuration, utilizing all the available network bandwidth using small messages would require spending as few as 600 CPU cycles per message. It is becoming increasingly more challenging to utilize the growing network bandwidth, especially with small messages. Therefore, any achieved reduction in computational resources spent per network message directly contributes towards building more balanced systems. In this thesis, we put actively put effort towards this direction. Network-compute integration and co-design opens a range of opportunities to alleviate the emerging network-compute imbalance.

# 2.6 One-Sided Operations Versus RPCs

Computation in distributed memory systems requires inter-server interaction, which generally takes one of two forms: either data is *pulled* from a remote server to a local server, or computation is *pushed* from the local server to the remote server, where it is executed on the target data. We refer to the former interaction form as *remote memory access* and to the latter as *Remote Procedure Call (RPC)*.

An RPC is inherently a *two-sided* operation: RPC-based inter-server interaction implies CPU involvement of both communicating servers. A remote memory access may of course be performed over an RPC, but can also be performed over a *one-sided* operation, i.e., an operation

that does not involve the CPU of the remote end. For most scale-out system deployments that rely on conventional network stacks such as TCP/IP, one-sided remote memory access is not possible. However, hardware-terminated protocols like InfiniBand not only offload the bulk of protocol processing to hardware, leaving a lean user-level protocol to be executed by the CPU, but also offer such operations. Such technology is commonly referred to as RDMA (Remote Direct Memory Access). An RDMA NIC has the capability of directly accessing application memory without CPU involvement at the remote end, offering the fastest path to remote memory. An additional benefit of one-sided operations over two-sided operations is tighter response latency distribution, as bypassing software interaction at the remote end removes a major source of unpredictability [161]. Hardware delivers more predictable latencies than software, resulting in tighter tails, as also demonstrated by Microsoft's Catapult project [28]. Several software frameworks have recently been built to leverage the strengths of these one-sided operations offered by RDMA technology [53, 54, 89, 127].

However, one-sided operations also have disadvantages, with first and foremost their lack of flexibility, because each operation is limited to reading/writing a single remote memory location. The requesting server has to specify exactly the remote memory location to be accessed. Such requirement is not trivial, as it involves software and use of data structures (e.g., FaRM's Hopscotch [53]) specially designed to facilitate location of remote data from the requesting side. Consequently, legacy software cannot make use of such operations without a major rewrite. Second, even with specially designed software, locating the target remote data can result in multiple roundtrips over the network. Adding an extra roundtrip voids the benefit of using a one-sided operation, as the overall remote data access time ultimately exceeds that of a conventional two-sided operation.

As a result, conventional wisdom dictates resorting to a two-sided operation (a.k.a. an RPC— Remote Procedure Call) to conduct any remote memory operation more complicated than a simple remote memory location read. To illustrate, even systems that are specifically designed to heavily rely on one-sided operations for fast remote memory reads (e.g., Pilaf [127] and Microsoft's FaRM [53]), resort to two-sided operations for writes. The reason for that design choice is that writes can trigger complex side-effects that can only be dealt with in software, such as data structure rebalances, memory allocation, etc. Of course, the flexibility of two-sided operations does not come for free; it involves CPU involvement at the remote end, which is a valuable resource (see Section 2.5): a message triggers some arbitrary code to be executed on a general-purpose CPU core. The involvement of software at the remote end also implies increased response latency and unpredictability.

Datacenter services still rely mostly on RPCs partially because of their great flexibility of RPCs and partially because they have been a well-established model for inter-server communication for decades; RDMA technology that enables one-sided operations started appearing in the datacenter space only recently. We expect that software layers that deliver very simple but latency-critical functionality, such as key-value stores, will gradually be restructured to leverage the low latency of one-sided operations. While the jury is still out as to when each of the two operation types is preferable, the community seems to be gradually reaching consensus that future systems using high-performance networking solutions should judiciously use both one- and two-sided operations, leveraging the merits of each [52]. Several recent well-engineered software stacks for distributed memory systems are a good example of that direction, as they combine the strengths of both operation types to maximize performance (e.g., [34, 171, 177]).

The net result is that any high-performance distributed memory architecture should offer support for rapid one-sided operations and efficient two-sided communication. In this thesis, we propose a new architecture with co-designed compute and network interface logic, aiming to significantly improve the performance and scalability of hardware-terminated protocols. We demonstrate that tightly integrated ICONIC architectures deliver superior performance, scalability, and flexibility for one-sided operations, and new opportunities for more efficient RPC invocations. Finally, in an attempt to bridge the semantic gap between one-sided operations and RPCs, we also investigate new one-operations with richer semantics and propose such a new primitive.

# **ICONIC Architecture Features Part I**

# **3** The Scale-Out NUMA Architecture

The rising demand for real-time online services has made it common practice for service providers to keep all data memory resident, distributed across millions of servers in a datacenter. While memory residency eliminates disk accesses, shrinking data access latency from 10s of milliseconds to 100s of nanoseconds, data distribution across machines results in frequent inter-server communication. As modern datacenters are built with commodity networking technology running on top of commodity servers and operating systems, inter-server communication delays can exceed  $100\mu s$  [149], a  $1000 \times$  overhead over the desired memory access latency.

The reasons for the high communication latency are well known and include deep network stacks, complex network interface cards (NIC), and slow chip-to-NIC interfaces [149, 63]. RDMA reduces end-to-end latency by enabling memory-to-memory data transfers over InfiniBand [80] and Converged Ethernet [79] fabrics. By exposing remote memory at user-level and offloading network processing to the adapter, RDMA enables remote memory read latencies in the range of a couple of  $\mu s$ ; however, that still represents a >10× latency increase over local DRAM.

To mitigate the performance gap between local and remote memory, we introduce Scale-Out NUMA (soNUMA): an architecture, programming model, and communication protocol for distributed, in-memory applications that reduces remote memory access latency to within a small factor ( $\sim$ 3–4x) of local memory. soNUMA leverages two simple ideas to minimize latency. The

#### **Chapter 3. The Scale-Out NUMA Architecture**

first is to use a stateless request/reply protocol running over a NUMA memory fabric to drastically reduce or eliminate the network stack, complex NIC, and switch gear delays. The second is to integrate the protocol controller into the node's local coherence hierarchy, thus avoiding state replication and data movement across the slow PCI Express (PCIe) interface.

soNUMA exposes the abstraction of a partitioned global virtual address space, which is useful for big-data applications with irregular data structures such as graphs. The programming model is inspired by RDMA [124], with application threads making explicit remote memory read and write requests with copy semantics. The model is supported by an architecturally-exposed hardware block, called the *remote memory controller* (RMC), that safely exposes the global address space to applications. The RMC is integrated into each node's coherence hierarchy, providing for a frictionless, low-latency interface between the processor, memory, and the interconnect fabric. This chapter describes the soNUMA architecture, programming model and protocol, with a particular focus on the RMC design.

Figure 3.1 – Netpipe benchmark on a Calxeda microserver.

# **3.1** Obstacles to Fast Remote Memory

As datasets grow, the trend is toward more sophisticated algorithms at ever-tightening latency bounds. While SoCs, glueless fabrics, and RDMA technologies help lower network latencies, the network delay per byte loaded remains high. Here, we discuss principal reasons behind the difficulty of further reducing the latency for in-memory applications in modern scale-out deployments.

**Deep network stacks are costly.** Distributed systems rely on networks to communicate. Unfortunately, today's deep network stacks require a significant amount of processing per network packet which factors considerably into end-to-end latency. Figure 3.1 shows the network performance between two directly-connected Calxeda EnergyCore ECX-1000 SoCs, measured using the standard netpipe benchmark [159]. The fabric and the integrated NICs provide 10Gbps worth of bandwidth. Despite the immediate proximity of the nodes, the integrated NICs and the lack of intermediate switches, we observe high latency (in excess of  $40\mu s$ ) for small packet sizes and poor bandwidth scalability (under 2 Gbps) with large packets. These bottlenecks exist due to the high processing requirements of TCP/IP and are aggravated by the limited performance offered by Calxeda's wimpy ARM Cortex-A9 cores.

**PCIe/DMA latencies limit performance.** I/O bypass architectures have successfully removed most sources of latency except the PCIe bus. Studies have shown that it takes 400–500ns to communicate short bursts over the PCIe bus [63], making such transfers  $7-8 \times$  more expensive,

in terms of latency, than local direct DRAM accesses. Furthermore, PCIe does not allow for the cache-coherent sharing of control structures between the system and the I/O device, leading to the need of replicating system state such as page tables into the device and system memory. In the latter case, the device memory serves as a cache, resulting in additional DMA transactions to access the state. SoC integration alone (e.g., integrated RDMA controller in X-Gene 2 and Oracle's Sonoma) does not eliminate these overheads, since IP blocks often use DMA internally to communicate with the main processor [20].

# 3.2 Scale-Out NUMA Overview

soNUMA is an architecture and programming model for low-latency distributed memory, designed to address each of the obstacles to low-latency described in Section 3.1. soNUMA goes after a scale-out model with physically distributed processing and memory: (i) it replaces deep network stacks with a lean user-level, hardware-terminated protocol; (ii) eschews system-wide coherence in favor of a global partitioned virtual address space accessible via RMDA-like remote memory operations with copy semantics; (iii) replaces transfers over the slow PCIe bus with fast cache-to-cache transfers; and (iv) is optimized for rack-scale deployments, where physical distance (i.e., propagation delays) is minuscule. In effect, our design goal is to borrow the desirable qualities of ccNUMA and RDMA without their respective drawbacks.

Figure 3.2 identifies the essential components of soNUMA. At a high level, soNUMA combines a lean memory fabric with an RDMA-like programming model in a rack-scale system. Applications access remote portions of the global virtual address space through remote memory operations. A new architecturally-exposed block, the *remote memory controller* (RMC), converts these operations into network transactions and directly performs the memory accesses. Applications directly communicate with the RMC, bypassing the operating system, which gets involved only in setting up the necessary in-memory control data structures.

Unlike traditional implementations of RDMA, which operate over PCIe, the RMC benefits from a tight integration into the processor's cache coherence hierarchy. In particular, the processor and

Figure 3.2 – soNUMA overview.

the RMC share all data structures via the cache hierarchy. The implementation of the RMC is further simplified by limiting the architectural support to one-sided remote memory read, write, and atomic operations, and by unrolling multi-line requests at the source RMC. As a result, the protocol can be implemented in a stateless manner by the destination node.