# Time-resolved Single-photon Detector Arrays for High Resolution Near-infrared Optical Tomography

THÈSE Nº 8815 (2018)

PRÉSENTÉE LE 31 AOÛT 2018 À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR LABORATOIRE D'ARCHITECTURE QUANTIQUE PROGRAMME DOCTORAL EN GÉNIE ÉLECTRIQUE

# ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

# Scott Anthony LINDNER

acceptée sur proposition du jury:

Prof. D. Atienza Alonso, président du jury Prof. E. Charbon, Prof. M. Wolf, directeurs de thèse Prof. A. Torricelli, rapporteur Prof. W. Uhring, rapporteur Prof. P. Seitz, rapporteur

# Acknowledgements

As I reflect on my time as a PhD student, there are many people I'm grateful to for making this all possible. I'd like to thank my two advisors Martin Wolf and Edoardo Charbon for giving me the chance to work on such a rewarding project and for their personal support when things went awry. I'd like to thank Martin for his scientific advice and for cultivating the friendly and collaborative environment at BORL which makes it a great place to come and work. I'm also very grateful to Edoardo, for fruitful scientific discussions, providing great opportunities to design chips and then encouraging us to pursue bold ideas.

I'd like to thank everyone in the team at BORL for their help along the way. Juan Mata Pavia, for meeting me at the airport over 5 years ago, providing guidance as I got to know the project, and karaoke nights in Selnau. I wish to thank Linda Ahnen for being a great office mate, runs along the limmat, and many chats over a cup of tea. Damien de Courten also shared an office with us and contributed to a friendly working environment, giving us many laughs over the years. Rashmi Hegde joined the project as a master student at a critical time and was a great help in turning Piccolo into a robust system. The Pioneer team at BORL, Sasha, Jinjing and Aldo, for their enthusiasm for the project and patience as I iron out the hardware. I'd like to thank Sasha in particular for assisting with the flash measurement with Piccolo. Iris Suter was always extremely helpful for administrative issues and has my gratitude. I'd also like to express thanks to all past and present members of neonatology at USZ who've contributed to my work, among them, Helene Isler, Daniel Ostojic, Dominik Wyser, Stefan Kleiser, Mark Adams, Nassim Nasseri, Raphael Zimmerman, Andreas Metz, Salvador Sanchez Majos, Felix Scholkmann, Simon Christen, Matthias Heinzmann, Flavia Wehrle, Manya Hendriks, Thi Dao Nguyen, Jean-Claude Fauchère, Dirk Bassler, Claudia Knöpfli and Tanja Karen.

Despite being based in Zurich, I worked for a lot of the time with colleagues from Edoardo's AQUA labs in Delft and then later in Neuchatel. Although I existed mainly as a voice through skype, whenever I worked with colleagues in these groups either online or when I visited, I found people eager to collaborate and who shared their knowledge freely. The Ocelot and Piccolo sensors were co-designed with Chao Zhang and Ivan Michel Antolovic. I'd like to

#### Acknowledgements

give a huge thanks to Chao Zhang, for his dedication, calm attitude under pressure, and for sharing his expertise of digital circuits. Michel's calm demeanor and attention to detail were massively appreciated and crucial to the success of the sensors. The 3D IC pixels were designed as part of the POLIS project, where I worked with Augusto Carimatto and Augusto Ximenes. Augusto Carimatto was a great collaborator in stressful situations and provided great company whilst watching football whenever I was in Delft. I'd like to thank August Ximenes for sharing his knowledge of IC design which helped improve the later designs of Piccolo and Ocelot. Esteban Venialgo, MJ Lee and Chockalingam Veerappan, with whom I never worked directly, deserve a special mention for sharing their extensive expertise. I always enjoyed these technical discussions, which improved my own work greatly. I'd like to thank Preethi Padmanaban for frequent discussions both inside and out of work, and for nights singing karaoke in Japan. Francesco Gramuglia wrote firmware for the Piccolo and Ocelot boards, which was a great help in bringing the system into the lab that much sooner. Claudio Bruschini and Brigitte Khan have also been a great help with organizational issues as I've come towards the end of my PhD. I'd also like to express thanks to all past and present members of AQUA who've contributed to my work, among them, Arin Ulku, Samuel Burri, Harald Homulle, Ting Gong, Kazuhiro Morimoto, Andrea Ruffino, Andrada Muntean, and Andrei Ardelean.

Finally, I would like to thank my family for the inspiration and support they've given me throughout the years. To my brother, Mark, whose determination and dedication is a daily motivator. To my mum, Doreen, for filling my head from a young age with stories of her travels and then cheering me on as I went on my own journey. And to my dad, Tony, for showing me the patience that only a lifetime of fishing can teach, and for instilling in me the strength to see things through to the end.

# Abstract

Oxygenation is an important marker in many clinical settings, e.g. diagnosing ischaemic brain injuries in preterm infants or determining treatment effectiveness in cancer patients. Despite significant efforts to determine the oxygenation state of the human tissue with conventional imaging modalities, e.g. positron emission tomography (PET) and magnetic resonance imaging (MRI), a method which is fit for continuous, routine use in clinics does not exist.

Near-infrared optical tomography (NIROT) is a compelling alternative which can be employed to measure tissue oxygenation. This method is based on the illumination and subsequent detection of the tissue response to light in the near-infrared (NIR) spectrum. NIROT is non-invasive and safe for continuous monitoring of patients. However, conventional NIROT systems have demonstrated a limited spatial resolution, in the 1-2 cm range, and prevented widespread clinical uptake. A major reason for this limited resolution is the low numbers of sources and detectors in conventional systems.

In an effort to improve the spatial resolution of NIROT, researchers have recently applied time-resolved cameras based on single-photon avalanche diodes (SPADs) to NIROT phantom measurements, achieving a resolution of 5 mm. Despite these promising results, conventional SPAD cameras are unsuitable for clinical measurements due to a slow image acquisition time.

In this thesis, time-resolved cameras were developed which have the potential to perform image acquisitions in NIROT measurements for a multi-source multi-wavelength system in a number of minutes. The main objective was to develop a large format,  $252 \times 144$  pixel, time-resolved SPAD camera capable of wide field measurements in a clinical setting.

Two new pixel circuits were developed in a backside-illuminated (BSI) 3D IC technology to increase the signal-to-noise ratio (SNR) and dynamic range (DR) in time-resolved measurements. The first circuit demonstrates, for the first time, a technique to increase the excess bias range, and thus the photon detection efficiency (PDE) and timing performance of conventional SPAD pixels. Coupled to an active recharge circuit, the pixel achieves a minimum dead time of 8 ns, and is thus suitable for high DR measurements. The second presents the first pixel circuit able

#### Acknowledgements

to interface with a SPAD via the anode or the cathode terminal, thus enabling the possibility of a general purpose time-correlated single-photon counting (TCSPC) die connecting to multiple application specific photodetector dies.

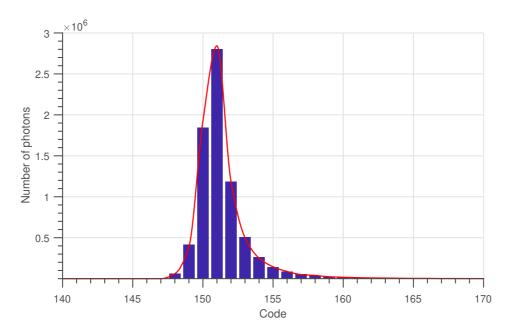

A new time-resolved SPAD sensor architecture is presented which employs a time-to-digital converter (TDC) sharing architecture to achieve both high PDE and high throughput parallel measurements. A  $32 \times 32$  sensor based on this architecture is produced in a 180nm CMOS technology. At the maximum throughput,  $10^6$  photons can be obtained for every pixel in the array in parallel in 4.6 seconds.

Finally, a wide-field,  $252 \times 144$  pixel time-resolved sensor is presented. To maintain a fast acquisition speed the architecture includes a per-pixel integrated histogramming readout. This enables the compression of the readout data by up to a factor of 14.9. To the best of the author's knowledge, this is the first implementation of integrated histogramming on a per-pixel basis for a full sensor array. This new sensor has game changing potential for NIROT, opening the door to high resolution wide-field clinical measurements.

Key words: Near-infrared spectroscopy (NIRS), near-infrared optical tomography (NIROT), optical tomography (OT), diffuse optical tomography (DOT), diffuse optical imaging (DOI), single-photon avalanche diode (SPAD), single-photon imaging, time-to-digital converter (TDC), time-correlated single-photon counting (TCSPC), integrated histogramming

# Zusammenfassung

Die Oxygenierung ist ein wichtiger Biomarker in vielen klinischen Situationen, insbesondere bei der Diagnose von ischämischen Hirnverletzungen bei Frühgeborenen oder der Bestimmung der Behandlungwirksamkeit bei Krebspatienten. Trotz erheblicher Anstrengungen, den Oxygenierungszustand des menschlichen Gewebes mit konventionellen bildgebenden Verfahren, wie z.B. der Positronen-Emissions-Tomographie (PET) und der Magnetresonanztomographie (MRT), zu messen, gibt es bisher keine Methode, die für den kontinuierlichen, routinemäßigen Einsatz in Kliniken geeignet ist.

Die optische Nah-Infrarot-Tomographie (NIROT) ist eine überzeugende Methode zur Messung der Gewebeoxygenierung. Sie basiert darauf, dass Gewebe mit nahinfrarotem (NIR) Licht beleuchtet und die Intensität des aus dem Gewebe wieder austretenden Lichtes gemessen wird. NIROT ist nichtinvasiv und harmlos sogar bei einer kontinuierlichen Überwachung von Patienten. Herkömmliche NIROT-Systeme verfügen jedoch nur über eine begrenzte räumliche Auflösung im Bereich von 1-2 cm, was eine weite Verbreitung in der klinischen Anwendung verhindert. Ein wesentlicher Grund für diese begrenzte Auflösung ist die geringe Anzahl von Quellen und Detektoren in herkömmlichen Systemen.

Um die räumliche Auflösung von NIROT zu verbessern, haben Forscher kürzlich zeitaufgelöste Kameras mit Single Photon Avalanche Dioden (SPADs) auf NIROT mit Phantommessungen untersucht und eine Ortsauflösung von 5 mm erreicht. Trotz dieser vielversprechenden Ergebnisse sind herkömmliche SPAD-Kameras aufgrund der langen Aaufnahmezeit nicht für klinische Messungen geeignet.

In dieser Arbeit wurden zeitaufgelöste Kameras entwickelt, die das Potenzial haben, diese Aufnahmzeit bei NIROT-Messungen inklusive Messungen bei mehreren Wellenlängen und Lichtquellenpositionen auf wenige Minuten zu reduzieren. Das Hauptziel war die Entwicklung einer großformatigen, zeitaufgelösten SPAD-Kamera mit 252 × 144 Pixeln, die in der Lage ist, hochauflösende Messungen im klinischen Umfeld durchzuführen.

Zwei neue Pixelschaltungen wurden in einer rückseitig beleuchteten (BSI) 3D-IC-Technologie entwickelt, um das Signal-Rausch-Verhältnis (SNR) und den Dynamikbereich (DR) bei zeitauf-

#### Acknowledgements

gelösten Messungen zu erhöhen. Die erste Schaltung demonstriert zum ersten Mal eine Technik zur Erhöhung der Sperrspannung und damit der Photonendetektionseffizienz (PDE) und der Zeitauflösung herkömmlicher SPAD-Pixel. Kombiniert mit einer aktiven Wiederaufladeschaltung erreicht das Pixel eine minimale Totzeit von 8 ns und ist somit für hohe DR-Messungen geeignet. Die zweite Schaltung stellt die erste Pixelschaltung dar, die über den Anoden oder Kathodenanschluss mit SPADs verbunden werden kann und somit einen universell einsetzbaren zeitkorrelierten Einzelphotonenzähler (TCSPC) Chip ermöglicht, der an mehrere anwendungsspezifische Photodetektorchips angeschlossen werden kann.

Es wird eine neue zeitaufgelöste SPAD-Kamera vorgestellt, die eine Architectur verwendet bei der Time-to-Digital Converter (TDC) gemeinsam verwendet werden, so dass sowohl eine hohe PDE- als auch parallele Messungen mit hohem Durchsatz erreicht werden. Ein darauf basierender 32 × 32 Pixel Sensor wurde in einer 180nm CMOS-Technologie hergestellt. Bei maximalem Durchsatz können für jedes Pixel des Chips 10<sup>6</sup> Photonen parallel in 4,6 Sekunden gewonnen werden.

Schließlich wird ein großer, zeitaufgelöster 252 × 144 Pixel Sensor vorgestellt. Um eine hohe Aufnahmegeschwindigkeit zu gewährleisten, verfügt die Architektur über eine integrierte Histogrammberechnung für jedes Pixel. Dies ermöglicht die Komprimierung der ausgelesenen Daten um bis zu einen Faktor von 14,9. Nach bestem Wissen des Autors ist dies die erste Implementierung einer integrierten Histogrammberechnung auf Pixelbasis für einen gesamten Sensorarray. Dieser neue Sensor eröffnet ein grosses Potential für NIROT, und wird zu hochauflösenden klinischen Messungen führen.

Stichwörter: Nah-Infrarot-Spektroskopie (NIRS), Nah-Infrarot-Tomographie (NIROT), optische Tomographie (OT), diffuse optische Tomographie (DOT), diffuse optische Bildgebung (DOI), Einzelphotonen-Avalanche-Photodioden-Detektoren (SPAD), Einzelphotonen-Bildgebung, Zeit-Digital-Wandler (ZDW), zeitkorrelierte Einzelphotonen-Zählung, integrierte Histogrammberechnung

# Contents

| Ac | knov                           | wledgements                                                  | i   |  |  |

|----|--------------------------------|--------------------------------------------------------------|-----|--|--|

| Ał | Abstract (English/Deutsch) iii |                                                              |     |  |  |

| Li | st of i                        | figures                                                      | xi  |  |  |

| Li | stof                           | tables                                                       | xv  |  |  |

| Li | stof                           | acronyms x                                                   | vii |  |  |

| 1  | Intr                           | oduction                                                     | 1   |  |  |

|    | 1.1                            | The Clinical Need for Oxygen Measurement                     | 1   |  |  |

|    | 1.2                            | Light Propagation in Tissue                                  | 4   |  |  |

|    | 1.3                            | Near-infrared Spectroscopy (NIRS)                            | 6   |  |  |

|    | 1.4                            | Near-infrared Optical Tomography (NIROT)                     | 8   |  |  |

|    | 1.5                            | Time-resolved Instrumentation                                | 9   |  |  |

|    | 1.6                            | Motivation and Aims of the Thesis                            | 10  |  |  |

|    | 1.7                            | Thesis Organization                                          | 12  |  |  |

|    | 1.8                            | Thesis Contributions                                         | 12  |  |  |

| 2  | Pixe                           | els for Improved SNR and Dynamic Range                       | 15  |  |  |

|    | 2.1                            | Single-photon avalanche diode (SPAD) Operation               | 15  |  |  |

|    | 2.2                            | SPAD Characteristics                                         | 17  |  |  |

|    | 2.3                            | System Level Metrics                                         | 21  |  |  |

|    |                                | 2.3.1 Photon detection efficiency (PDE)                      | 21  |  |  |

|    |                                | 2.3.2 Signal-to-noise ratio (SNR)                            | 21  |  |  |

|    |                                | 2.3.3 Dynamic range (DR)                                     | 22  |  |  |

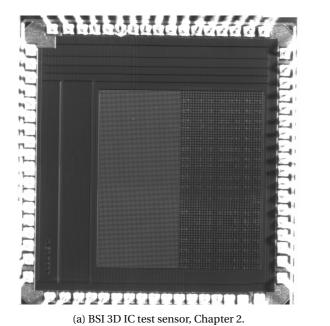

|    | 2.4                            | Stacked 3D BSI Image Sensors                                 | 23  |  |  |

|    | 2.5                            | A High-PDE Pixel with Cascoded Quenching and Active Recharge | 25  |  |  |

|    |                                | 2.5.1 SPAD Structure and 3D IC Technology                    | 26  |  |  |

#### Contents

|   |      | 2.5.2    | Pixel Design                                                      | 26 |

|---|------|----------|-------------------------------------------------------------------|----|

|   |      | 2.5.3    | Results and Discussion                                            | 29 |

|   | 2.6  | A Bidi   | rectional Pixel for 3D IC Technologies                            | 33 |

|   |      | 2.6.1    | Pixel Design                                                      | 34 |

|   |      | 2.6.2    |                                                                   | 35 |

|   | 2.7  | Concl    | usions                                                            | 35 |

|   |      |          |                                                                   |    |

| 3 | Eve  |          | ven Time-resolved SPAD Sensors                                    | 37 |

|   | 3.1  | Time-    | resolved SPAD Image Sensors                                       | 37 |

|   |      | 3.1.1    | TDC-per-pixel Sensor Architectures                                | 38 |

|   |      | 3.1.2    | TDC Sharing Architectures                                         | 39 |

|   |      | 3.1.3    | Overcoming the I/O Bandwidth Bottleneck                           | 42 |

|   | 3.2  | NIRO     | T Sensor Requirements                                             | 42 |

|   | 3.3  | Case S   | Study: Piccolo, A High-PDE Event-driven Time-resolved SPAD Sensor | 43 |

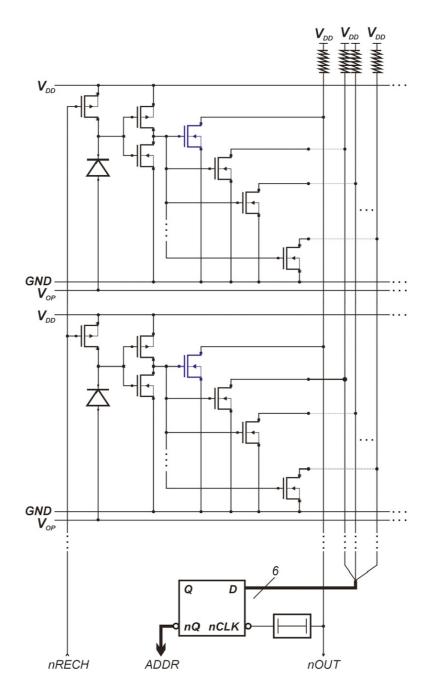

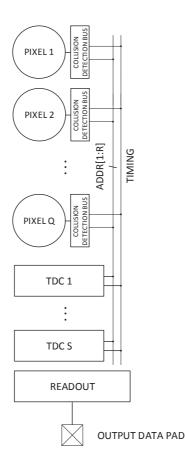

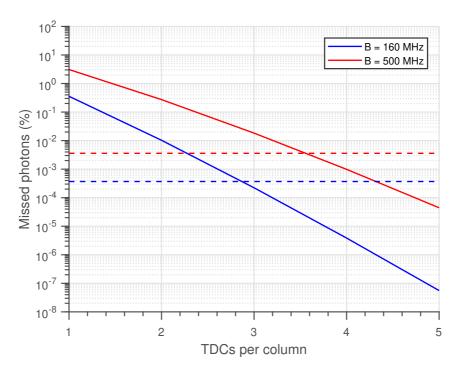

|   |      | 3.3.1    | Sizing the TDC Bank                                               | 43 |

|   |      | 3.3.2    | Photon Collision Analysis                                         | 47 |

|   | 3.4  | Concl    | usions                                                            | 50 |

| 4 | A 32 | 2 × 32 F | event-driven Time-resolved SPAD Sensor                            | 51 |

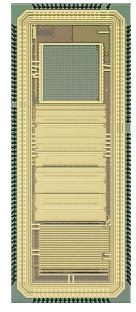

| - | 4.1  |          | lo Camera System                                                  | 53 |

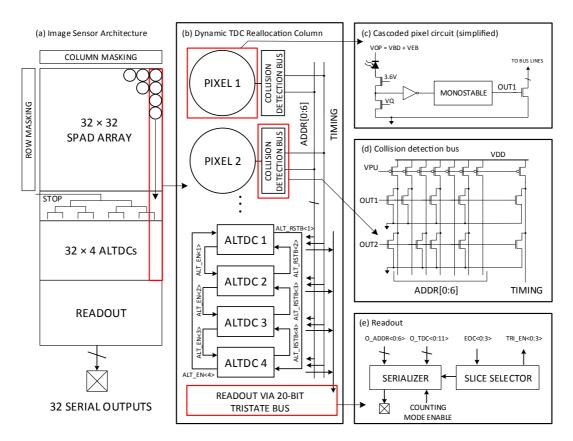

|   |      | 4.1.1    | Sensor Architecture                                               | 53 |

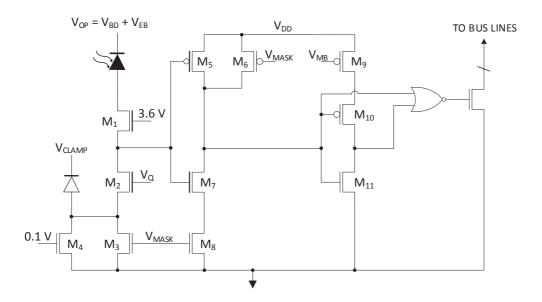

|   |      | 4.1.2    | The Pixel                                                         | 55 |

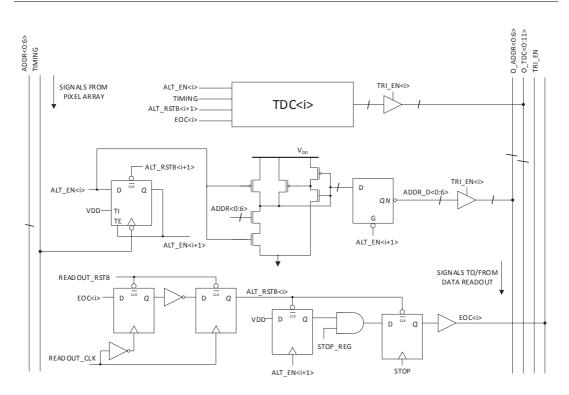

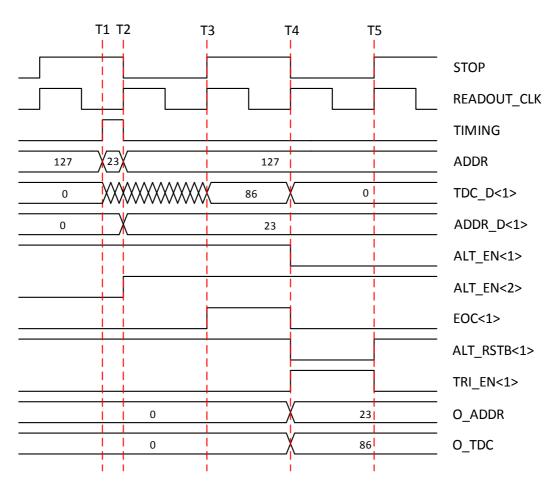

|   |      | 4.1.3    | Address Latch and Dynamic Reallocation                            | 57 |

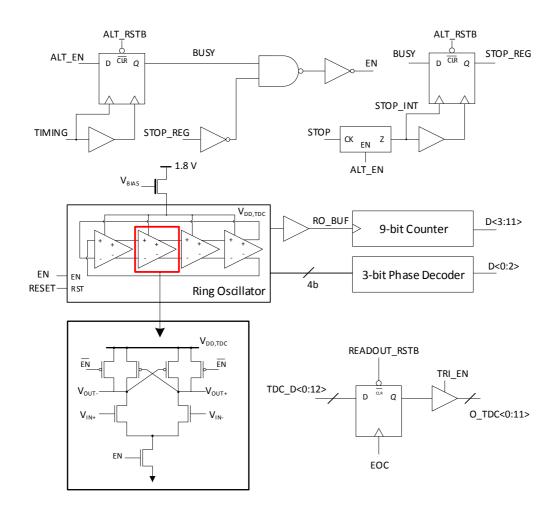

|   |      | 4.1.4    | The TDC                                                           | 60 |

|   |      |          | Complete Sensor                                                   | 64 |

|   | 4.0  |          | -                                                                 |    |

|   | 4.2  |          | ts                                                                | 65 |

|   |      | 4.2.1    | Light Emission Test                                               | 65 |

|   |      | 4.2.2    | Dark count rate (DCR)                                             | 66 |

|   |      | 4.2.3    | Afterpulsing                                                      | 67 |

|   |      | 4.2.4    | Photon detection probability (PDP)                                | 68 |

|   |      | 4.2.5    | TDC Characterisation                                              | 69 |

|   |      | 4.2.6    | Timing Response                                                   | 72 |

|   |      | 4.2.7    | Signal-to-noise ratio (SNR)                                       | 73 |

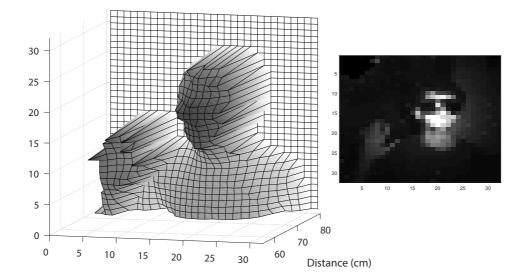

|   |      | 4.2.8    | Flash Ranging Measurement                                         | 74 |

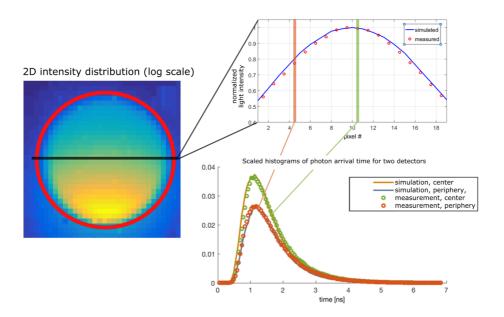

|   |      | 4.2.9    | Phantom Validation                                                | 75 |

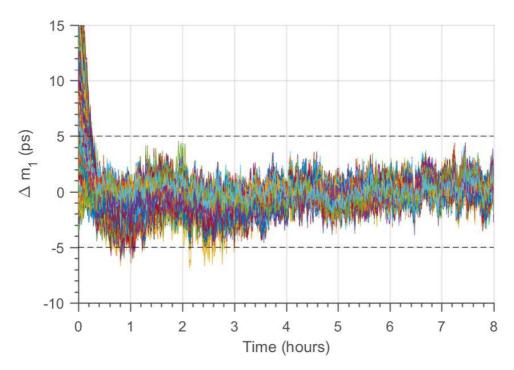

|   |      | 4.2.10   | Timing Stability                                                  | 76 |

### Contents

|    |                         | 4.2.11 Power Consumption                                        | 77  |  |

|----|-------------------------|-----------------------------------------------------------------|-----|--|

|    |                         | 4.2.12 State-of-the-art Comparison                              | 78  |  |

|    | 4.3                     | Conclusions                                                     | 78  |  |

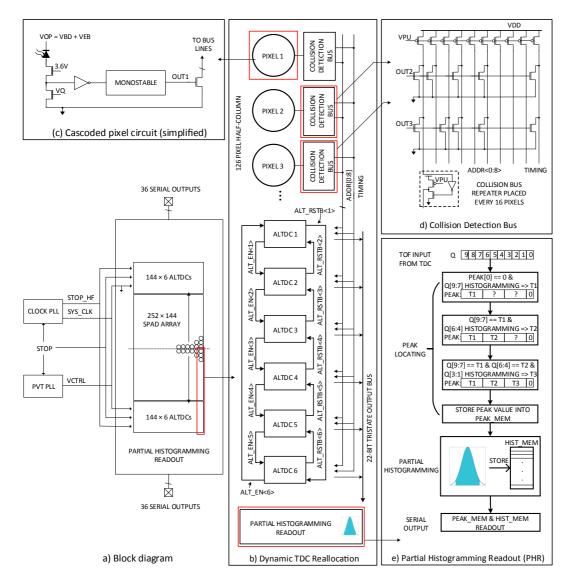

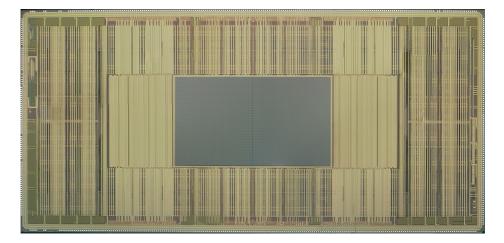

| 5  | A 25                    | 52 × 144 Event-driven High-throughput Time-resolved SPAD Sensor | 81  |  |

|    | 5.1                     | Large Format Time-resolved SPAD Sensors                         | 82  |  |

|    | 5.2                     | Sensor Architecture                                             | 83  |  |

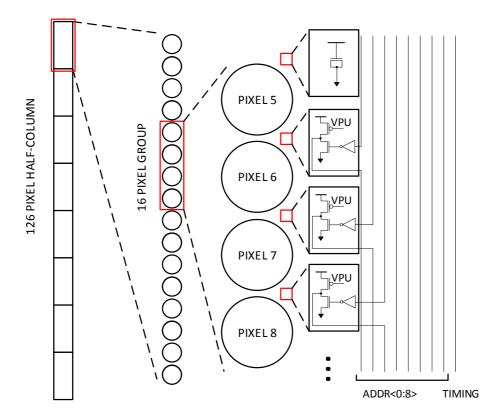

|    | 5.3                     | Scalable Collision Detection Bus                                | 85  |  |

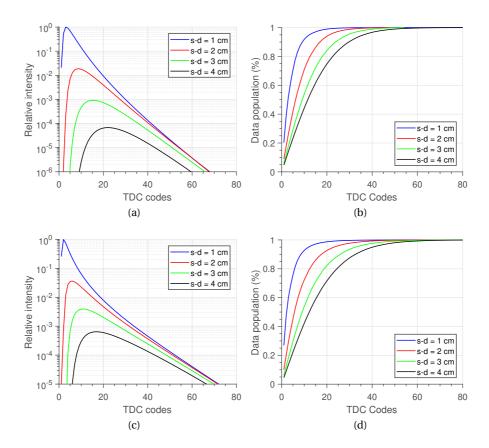

|    | 5.4                     | Partial Histogramming Readout                                   | 87  |  |

|    | 5.5                     | Dual-clock ring oscillator (RO) TDC                             | 91  |  |

|    | 5.6                     | Clock Generation                                                | 97  |  |

|    | 5.7                     | Results                                                         | 99  |  |

|    |                         | 5.7.1 TDC Nonlinearity                                          | 102 |  |

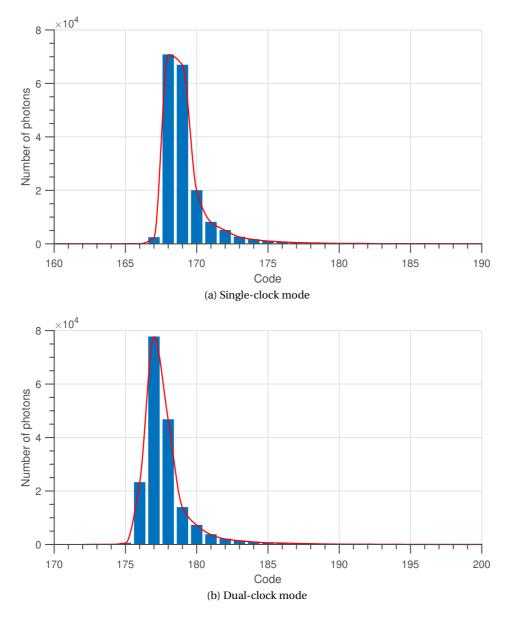

|    |                         | 5.7.2 Timing Response                                           | 103 |  |

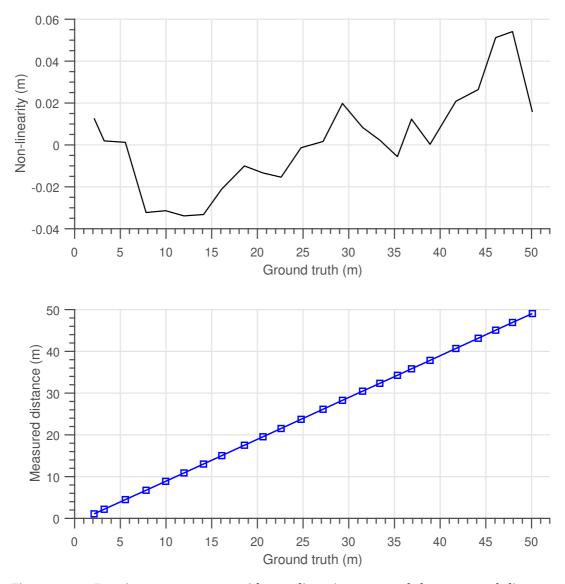

|    |                         | 5.7.3 Distance Linearity                                        | 104 |  |

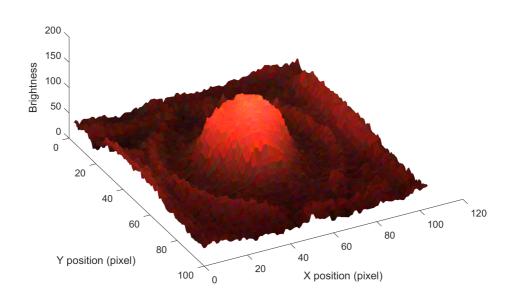

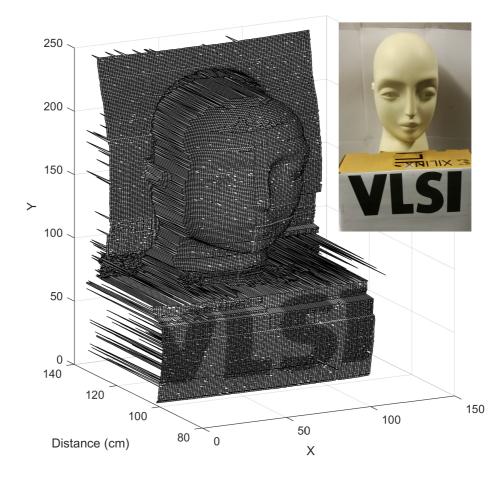

|    |                         | 5.7.4 Flash Image                                               | 105 |  |

|    |                         | 5.7.5 Power Consumption                                         | 107 |  |

|    |                         | 5.7.6 State-of-the-art Comparison                               | 108 |  |

|    | 5.8                     | Conclusions                                                     | 108 |  |

| 6  | Con                     | nclusions and Future Work                                       | 111 |  |

| Bi | bliog                   | graphy                                                          | 128 |  |

| Cł | Chip Gallery 1          |                                                                 |     |  |

| Li | List of Publications 13 |                                                                 |     |  |

| Сι | ırricu                  | ulum Vitae                                                      | 133 |  |

# List of Figures

| 1.1  | Uterine cervical cancer survival rates considering tumor hypoxia                    | 3  |

|------|-------------------------------------------------------------------------------------|----|

| 1.2  | Dependence of light intensity on source-detector separation in reflection mode      | 4  |

| 1.3  | Absorption spectra of molecules in human tissue                                     | 5  |

| 1.4  | NIRS measurement geometries                                                         | 7  |

|      |                                                                                     |    |

| 2.1  | SPAD front-end and cross section of CMOS SPAD                                       | 16 |

| 2.2  | Mean penetration depth in silicon as a function of wavelength, data taken from [1]. | 18 |

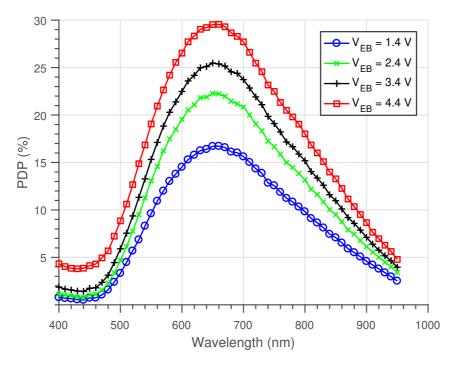

| 2.3  | Compression of PDP spectrum with increasing $V_{EB}$                                | 19 |

| 2.4  | Timing response of a SPAD with slow exponential tail                                | 20 |

| 2.5  | Cross section of 130nm BSI 3D IC CMOS technology                                    | 24 |

| 2.6  | Cross section of p-well/deep n-well BSI SPAD and 65/40 nm 3D IC CMOS tech-          |    |

|      | nology                                                                              | 26 |

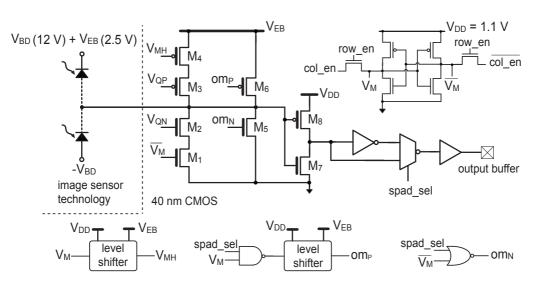

| 2.7  | Cascoded active recharge SPAD pixel schematic                                       | 27 |

| 2.8  | Hold-off and recharge time, delay generation                                        | 28 |

| 2.9  | Avalanche quenching and recharge simulation showing critical circuit voltages       | 29 |

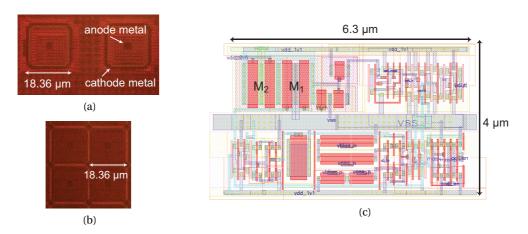

| 2.10 | Cascoded quenching and active recharge pixel micrograph                             | 30 |

| 2.11 | Dark count rate vs excess bias                                                      | 31 |

| 2.12 | Inter avalanche arrival time with 8 ns dead time                                    | 31 |

| 2.13 | PDP vs wavelength for varying excess bias                                           | 32 |

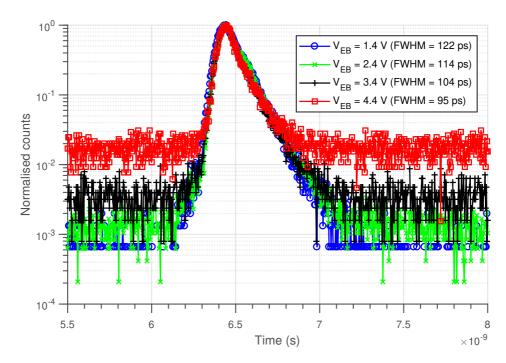

| 2.14 | Timing response for varying excess bias at 700 nm                                   | 33 |

| 2.15 | Bidirectional passive quenching circuit schematic                                   | 34 |

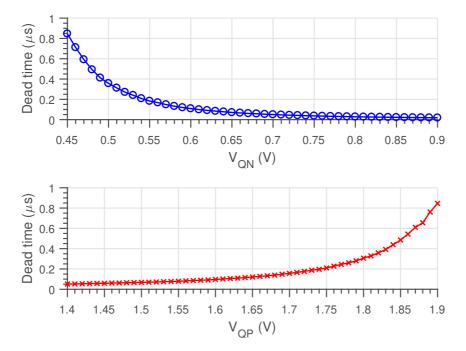

| 2.16 | SPAD dead time versus quenching voltage for anode and cathode biasing $\ldots$      | 36 |

| 0.1  |                                                                                     | 41 |

| 3.1  |                                                                                     | 41 |

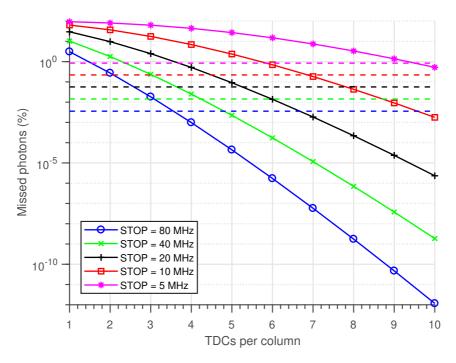

| 3.2  | 1 I                                                                                 | 44 |

| 3.3  |                                                                                     | 45 |

| 3.4  | Simulation of missed photons vs number of TDCs per column for GPIO case             |    |

|      | with varying laser frequency                                                        | 46 |

# List of Figures

| 3.5  | Simulation of missed photons vs number of TDCs per column for LVDS case                                |    |

|------|--------------------------------------------------------------------------------------------------------|----|

|      | with varying laser frequency                                                                           | 47 |

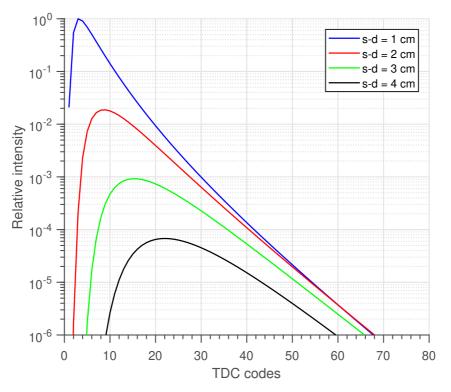

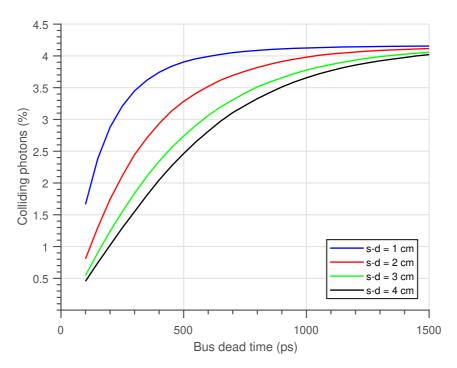

| 3.6  | NIROT TPSF of homogeneous media simulated with NIRFAST $\ldots$                                        | 48 |

| 3.7  | Simulation of colliding photons vs bus dead time                                                       | 49 |

| 4.1  | Piccolo camera system                                                                                  | 52 |

| 4.2  | Piccolo sensor architecture                                                                            | 54 |

| 4.3  | Cascoded passive quenching pixel schematic                                                             | 56 |

| 4.4  | Simplified ALTDC slice schematic                                                                       | 58 |

| 4.5  | ALTDC timing diagram                                                                                   | 59 |

| 4.6  | Piccolo ring oscillator TDC architecture                                                               | 62 |

| 4.7  | Piccolo TDC timing diagram.                                                                            | 63 |

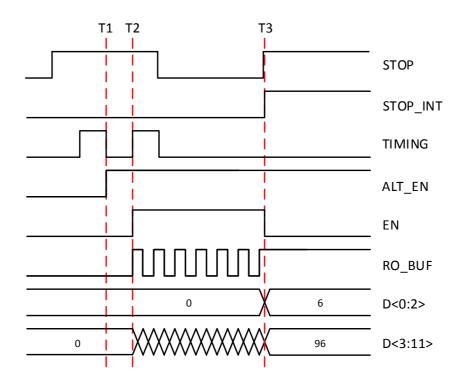

| 4.8  | Photomicrograph of Piccolo sensor                                                                      | 64 |

| 4.9  | Light emission test of p-i-n SPAD                                                                      | 65 |

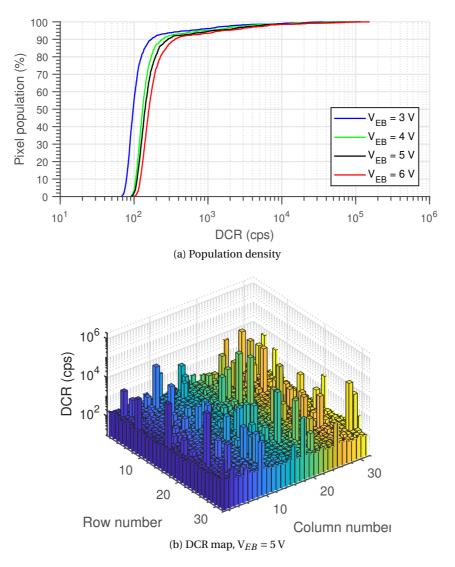

| 4.10 | DCR characterisation of Piccolo array                                                                  | 66 |

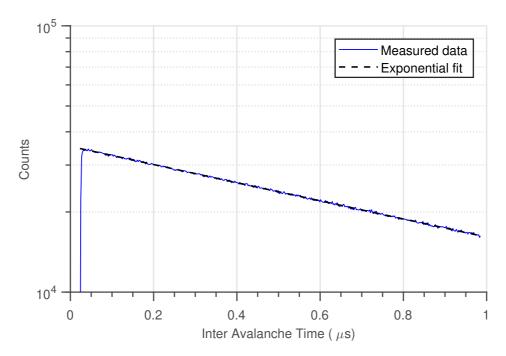

| 4.11 | Inter arrival times of photon detections with uncorrelated illumination and 50                         |    |

|      | ns dead time                                                                                           | 67 |

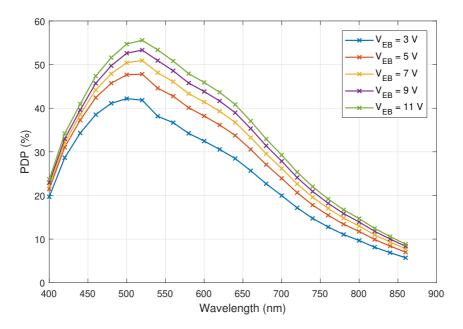

| 4.12 | PDP versus wavelength for excess bias voltages in the range 3-11 V                                     | 68 |

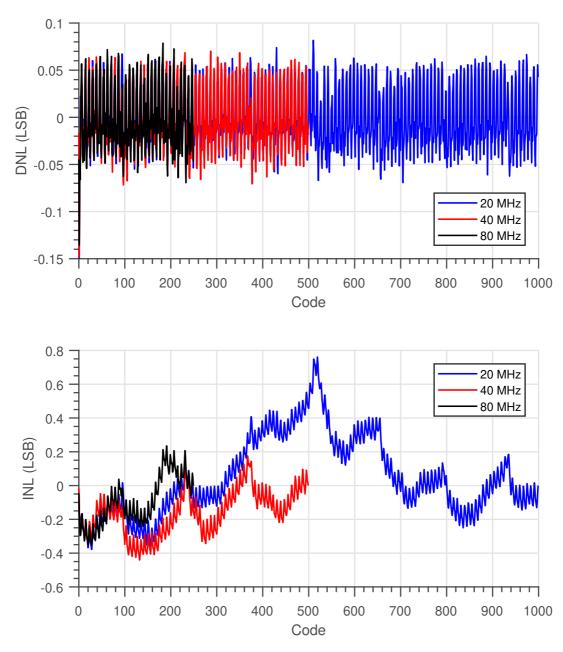

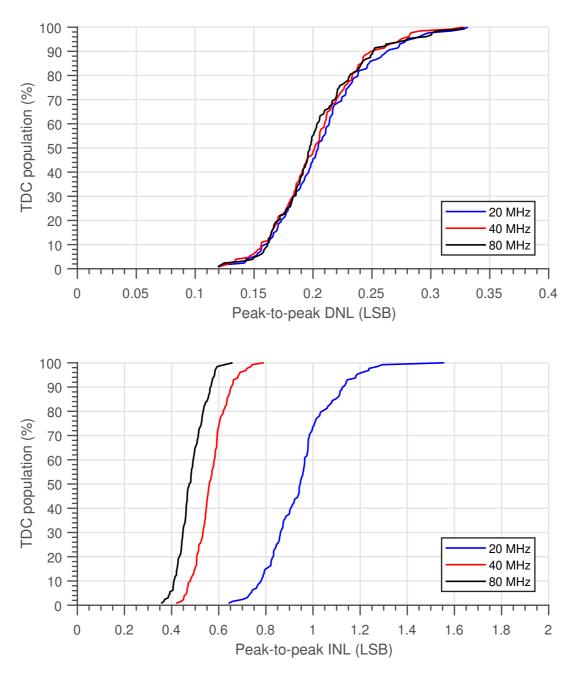

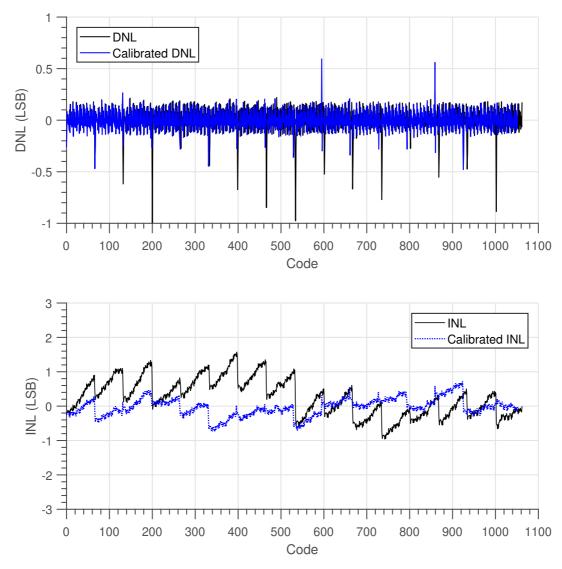

| 4.13 | Typical DNL and INL at STOP frequencies of 80, 40 and 20 MHz                                           | 70 |

| 4.14 | Peak-to-peak DNL and INL at STOP frequencies of 80, 40 and 20 MHz                                      | 71 |

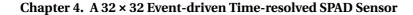

| 4.15 | Piccolo LSB variation                                                                                  | 72 |

| 4.16 | Timing response of Piccolo system at 700 nm                                                            | 73 |

| 4.17 | Computed relative SNR as a function of $V_{EB}$                                                        | 74 |

| 4.18 | $32 \times 32$ flash ranging measurement of a human $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 75 |

| 4.19 | $\ensuremath{\text{TPSFs}}$ of silicon phantom measurement compared to Monte Carlo (MC) simulation     | 76 |

| 4.20 | Timing stability of Piccolo system                                                                     | 77 |

| 5.1  | Ocelot architecture                                                                                    | 84 |

| 5.2  | Bus repeater distribution within the 126 pixel half-column                                             | 88 |

| 5.3  | TPSF of homogenous medium from NIRFAST forward simulation at varying                                   |    |

|      | source-detector (s-d) separations                                                                      | 89 |

| 5.4  | Ocelot partial histogramming readout block diagram                                                     | 91 |

| 5.5  | Code difference accumulated between two TDCs, with a fixed measurement                                 |    |

|      | period                                                                                                 | 92 |

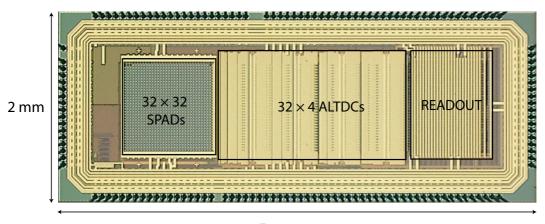

| 5.6  | Dual clock TDC schematic                                                                               | 93 |

| 5.7  | Dual clock TDC timing diagram                                                                          | 94 |

|      |                                                                                                        |    |

# List of Figures

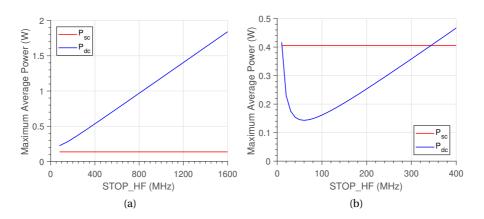

| 5.8  | Maximum average power consumption in the dual clock TDC for varying STOP_HF $$      |     |  |

|------|-------------------------------------------------------------------------------------|-----|--|

|      | frequencies                                                                         | 96  |  |

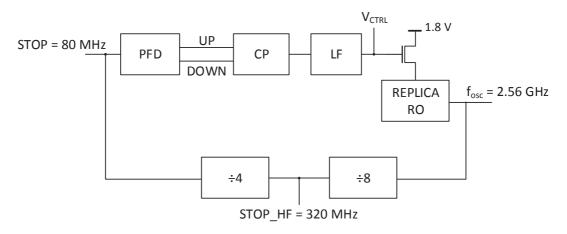

| 5.9  | Ideal clock generation for Ocelot sensor                                            | 97  |  |

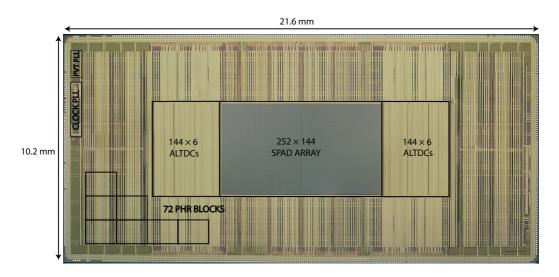

| 5.10 | Photomicrograph of Ocelot sensor                                                    | 100 |  |

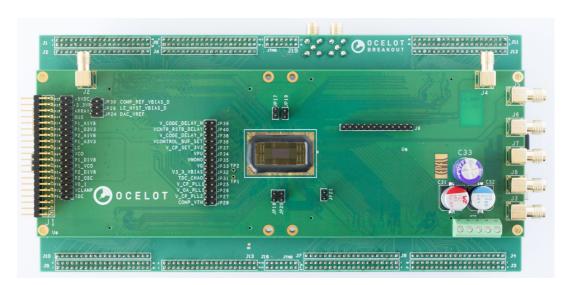

| 5.11 | Ocelot camera system                                                                | 101 |  |

| 5.12 | DNL and INL of dual-clock TDC                                                       | 102 |  |

| 5.13 | Ocelot timing response for one pixel and one TDC in TCSPC mode at 700 $\rm nm$ $$ . | 104 |  |

| 5.14 | 14 Ranging measurement with non-linearity and the measured distance at dis-         |     |  |

|      | tances up to 50 m                                                                   | 106 |  |

| 5.15 | Flash image of mannequin at 1 m distance with 2 mW laser                            | 107 |  |

# List of Tables

| 4.1 | Piccolo power consumption           | 78  |

|-----|-------------------------------------|-----|

| 4.2 | Piccolo state-of-the-art comparison | 79  |

| 5.1 | Ocelot power consumption            | 108 |

| 5.2 | Ocelot state-of-the-art comparison  | 109 |

# List of Acronyms

| ALTDC | address latch and time-to-digital converter |

|-------|---------------------------------------------|

| AOTF  | acousto-optical tunable filter              |

| BSI   | backside-illuminated                        |

| CCD   | charge-coupled device                       |

| CMOS  | complementary metal-oxide-semiconductor     |

| СР    | charge pump                                 |

| cps   | counts per second                           |

| CW    | continuous wave                             |

| DAC   | digital-to-analog converter                 |

| DCR   | dark count rate                             |

| DFF   | D-type Flip-Flop                            |

| DLL   | delay-locked loop                           |

| DNL   | differential nonlinearity                   |

| DOI   | diffuse optical imaging                     |

| DOT   | diffuse optical tomography                  |

| DR    | dynamic range                               |

| FD    | frequency domain                            |

| FLIM  | fluorescence lifetime imaging               |

| FOV   | field of view                               |

#### List of Tables

| FPGA              | field-programmable gate array       |

|-------------------|-------------------------------------|

| FSI               | frontside-illuminated               |

| FWHM              | full width at half maximum          |

| GPIO              | general purpose I/O                 |

| Hb                | hemoglobin                          |

| HBP               | hybrid bonding pad                  |

| HHb               | deoxygenated hemoglobin             |

| INL               | integral nonlinearity               |

| IRF               | instrument response function        |

| LET               | light emission test                 |

| LF                | loop filter                         |

| LiDAR             | light detection and ranging         |

| LSB               | least significant bit               |

| LVDS              | low-voltage differential signalling |

| MC                | Monte Carlo                         |

| MRI               | magnetic resonance imaging          |

| NIR               | near-infrared                       |

| NIROT             | near-infrared optical tomography    |

| NIRS              | near-infrared spectroscopy          |

| O <sub>2</sub> Hb | oxygenated hemoglobin               |

| ОТ                | optical tomography                  |

| РСВ               | printed circuit board               |

| PDE               | photon detection efficiency         |

| PDP               | photon detection probability        |

| PET               | positron emission tomography        |

| PFD               | phase-frequency detector            |

xviii

- **PHR** partial-histogramming readout

- PLL phase-locked loop

- **PMT** photomultiplier tube

- **PVT** process, voltage and temperature

- rms root mean square

- **RO** ring oscillator

- **RTE** radiative transfer equation

- **SiPM** silicon photomultiplier

- **SNR** signal-to-noise ratio

- **SPAD** single-photon avalanche diode

- **SRAM** static random access memory

- **TCSPC** time-correlated single-photon counting

- **TD** time domain

- TDC time-to-digital converter

- **ToF** time-of-flight

- **TPSF** time point-spread function

- VCO voltage-controlled oscillator

# **1** Introduction

Oxygen is crucial for our continued survival, yet methods for measuring its concentration in our bodies are severely lacking. This chapter begins by outlining the importance of oxygen and discusses some clinical applications where there is a pressing need for better imaging techniques. Near-infrared optical tomography (NIROT), a technique based on the propagation of light, has the potential to address this need. The state-of-the-art in NIROT methods and instrumentation is reviewed. The spatial resolution, and thus the clinical relevance, of existing systems is constrained by hardware. Thus, a motivation for developing new time-resolved hardware based on single-photon avalanche diodes (SPADs) is presented.

## 1.1 The Clinical Need for Oxygen Measurement

Oxygen is vital for human life. Every time we take a breath, oxygen is extracted from the air filling our lungs and then transported around our bodies via the hemoglobin in the blood. At the cellular level, oxygen is used to convert nutrients into adenosine triphosphate (ATP), which provides the energy we need to function in our daily lives, e.g. movement, cognition, etc. As well as its presence, the concentration and distribution of oxygen in the body are also of critical importance. An inadequate supply of oxygen to the body, hypoxia, can affect the whole body but also localised regions. This thesis focuses on two applications in particular.

Every year approximately 15 million babies worldwide are born prematurely, with a gestational age of less than 37 weeks [2]. For these infants, a lack of oxygen in the brain after birth can lead to severe complications such as hypoxic-ischaemic and haemorrhagic brain injuries. This can result in life altering disabilities, e.g. cerebral palsy and epilepsy, and in the worst cases, death [3]. A study of surviving extreme preterm infants (< 28 weeks gestation), who

#### **Chapter 1. Introduction**

account for approximately 5.2% of the premature births [2]), showed almost 50% of the cohort demonstrated significant cognitive delay [4] at school age. Although there are treatments which can be applied, the time window within which these treatments are effective is typically small. For example, hypothermia has been shown to attenuate brain damage, however, it must be administered within 6 hours [5]. Thus, there is a pressing need to identify those infants which require treatment as early as possible.

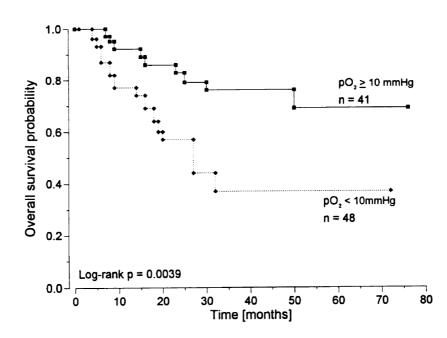

Another medical setting where hypoxia is important is in the prognosis and treatment of cancer. For cancer tumors, hypoxia is the result of an imbalance between the consumption and supply of oxygen. This can be caused by inadequate blood supply to the tumor and also an increased oxygen demand due to tumor growth. Tumor hypoxia has been shown to indicate a greater resistance to radiation [6] and chemo- [7] therapies. A 1996 study [8], Figure 1.1, investigated the effect of tumor oxygenation on treatment effectiveness and patient outcomes by sampling the partial oxygen pressure  $(pO_2)$  of advanced uterine cervical tumors at multiple points spaced 0.7 mm apart with a polarographic probe. The study showed that patients whose tumors had a median  $pO_2$  of less than 10 mmHg had a less than 40% 5-year survival rate. In contrast, patients whose tumors exhibited a median  $pO_2$  of greater than 10 mmHg had a 5-year survival rate of more than 70%. These results tell two stories. Firstly, oxygen is an important indicator for treatment effectiveness and prognosis for cancer patients. Secondly, the necessity of sampling many points over a cancer tumor indicates that heterogeneity is crucial. Thus an effective method for determining the oxygenation state in this setting must provide spatially resolved information of the entire tumor, rather than just a point value.

With the pressing need for quantification of oxygen within the human body, it should come as no surprise that a number of methods have already been investigated, e.g. polarographic probes [9] as used in [8], paramagnetic resonance imaging [10], magnetic resonance imaging [11], and PET [12, 13]. Of these, PET is generally regarded as the gold standard imaging method for *in vivo* oxygen quantification due to its high specificity and sensitivity enabled by hypoxia specific radiolabelled agents. However, the use of these radiotracers raises concerns about radiation exposure to patients. As such, measurements are generally restricted to two time points [14]. Furthermore, long measurement times, high costs and the requirement for an on-site cyclotron have limited the uptake of PET for oxygen measurements.

For the two applications already mentioned, monitoring cerebral oxygenation in neonates and tumor hypoxia, there remains a clear need for improved quantification of oxygenation in human tissue. Such a method must firstly be safe. Although PET has been applied for the measurement of glucose metabolism in term infants [15], the safety of the radiation dose is

Figure 1.1 – A 1996 study [8] demonstrated that the 5-year survival rate for uterine cervical cancer reduced from greater than 70% with a median  $pO_2 > 10$  mmHg to less than 40% with a  $pO_2 < 10$  mmHg, with  $pO_2$  sampled at multiple points with a polarographic probe. *Picture credit: M. Höckel, Copyright* ©1996, *American Association for Cancer Research.*

dependent on the administered radiotracer and measurement frequency. Thus, continuous monitoring is a concern as it is with tumor hypoxia monitoring [14]. Additionally, an effective oxygen monitoring method should have a high spatial resolution. This is important to localise regions of low oxygenation in the brain of preterm infants and also to detect oxygenation heterogeneities in cancer tumors. Finally, low cost is a crucial aspect for widespread uptake. Both of these applications would likely require screening of a large number of patients as well as continuous monitoring to monitor the treatment effectiveness.

Relatively new methods to measure the oxygenation state of biological tissue are near-infrared spectroscopy (NIRS) and near-infrared optical tomography (NIROT). In these methods, the biological tissue under study is illuminated with light in the NIR region of the spectrum, from 600-1000 nm. By detection of the light leaving the tissue via a suitable photodetector, the oxygenation state can be obtained by exploiting differences in the optical properties of the various substances in the tissue. Since this method employs only light, it is non-ionizing, completely safe and can be applied continuously. Furthermore, the hardware required to illuminate and detect light are inexpensive when compared to systems such as PET and MRI. Therefore, imaging methods based on this principle are highly promising for clinical settings.

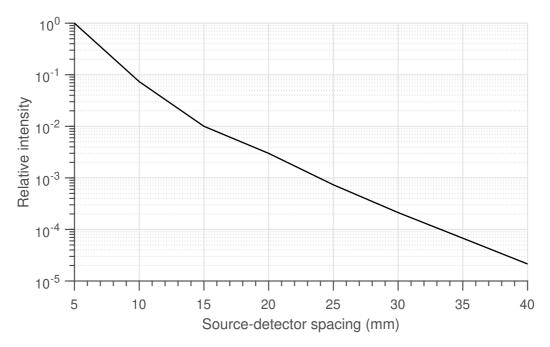

Figure 1.2 – NIRFAST [18] simulation of relative intensity in reflectance mode NIROT measurement as a function of source-detector separation. Simulation in 40 mm depth homogeneous medium with  $\mu_a = 0.01 \text{ mm}^{-1}$  and  $\mu'_s = 1 \text{ mm}^{-1}$ , i.e, typical properties of adult human tissue.

## 1.2 Light Propagation in Tissue

To better understand how NIROT works, we must first look at light propagation in tissue, which is largely dictated by two processes, scattering and absorption. Scattering is due to the interaction of photons with structures within the medium [16], e.g. cells, nuclei, organelles, [17] etc. This interaction alters the direction of the incident photons and can be expressed by the scattering coefficient,  $\mu_s$ , which gives the probability that a photon will be scattered per unit length. An alternative measure, the reduced scattering coefficient  $\mu'_s$ , gives the probability per unit length that a photon loses its initial direction. As photons scatter inside the medium, collisions with molecules can result in the incident photon being absorbed. The probability of absorption per unit length is given by the absorption coefficient,  $\mu_a$ . As a result of absorption, the light intensity detected at the surface of the medium decreases with an exponential dependence as the distance between the light source and detector, the source-detector (s-d) separation, is increased, Figure 1.2.

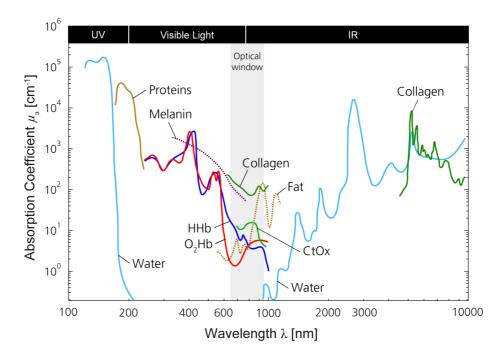

Figure 1.3 [19] shows the absorption spectra of many of the molecules found in human tissue over the wavelength range 100-10000 nm. Critical to the function of NIRS and NIROT, there exists an 'optical window' in human tissue between approximately 650 and 950 nm [19], at

Figure 1.3 – Absorption spectra of molecules in human tissue in the wavelength range 100-10000nm [19]. *Picture credit: F. Scholkmann, Copyright* ©2013 Elsevier Inc. All rights reserved.

which absorption and scattering is relatively low. In this window, light is able to penetrate several centimetres without being absorbed, allowing the study of relatively deep regions of tissue. The main absorbers in the optical window are oxygenated hemoglobin ( $O_2Hb$ ) and deoxygenated hemoglobin (HHb). Hemoglobin (Hb) is contained in the red blood cells which are mainly responsible for oxygen delivery from the lungs to the different parts of the body. Although there are molecules with a greater absorption coefficient between 650 and 950 nm, their low concentrations in human tissue mean that their contribution to total absorption is small, thus they are generally neglected in the calculation of oxygenation state.

The absorption spectra of the various molecules within the optical window are each unique and show a wavelength dependency. Therefore, measurements at multiple wavelengths can be performed to obtain the absorption contributions from individual molecules.

In human tissue, scattering is dominant in comparison to absorption,  $\mu'_s$  values 100 times greater than  $\mu_a$  are typical [20]. Light propagation in tissue then is a diffusive process, and any calculation of the oxygenation state must take into account the contributions to the detected signal from both absorption and scattering.

## **1.3 Near-infrared Spectroscopy (NIRS)**

NIRS was first demonstrated in 1977 by Frans Jöbsis [21], where the oxygenation status of both hemoglobin and cytochrome oxidase were measured. This initial discovery led to the development of a range of different instruments applied in settings such as breast tumor diagnosis [22], functional activation of the cerebral cortex in neonates [23] and muscle oxygenation monitoring [24].

The earliest measurements were carried out with continuous wave (CW) NIRS devices [25]. In this method, the tissue under study is illuminated with light at a constant intensity and the detector measures the attenuation in the light that exits. The simplicity of this technique means that it can be implemented with relatively unsophisticated hardware that is both inexpensive and can be made portable. Furthermore, CW instruments have a high time resolution, e.g. a sampling rate up to 100 Hz [25], which means that they can monitor rapidly changing physiological signals. This property has enabled, for example, measurements of muscle oxygenation in sport activities [26] and has led to the CW method being by far the most popular among NIRS techniques. Unfortunately, the CW method cannot determine the scattering properties of the tissue under study. As such, only relative changes in  $O_2$ Hb and HHb can be measured without applying more advanced measurement procedures or instrumentation [19].

To obtain information on the scattering properties of the tissue, the time duration required for the light to travel from the source to detector must be known [25]. There are two methods which can be applied for this purpose. Frequency domain (FD) NIRS devices obtain the time information by illuminating the tissue with frequency modulated light and the detector measures the amplitude and phase of the light that exits [27]. Time domain (TD) instruments on the other hand illuminate the tissue with very short pulses of light, typically on the order of tens of picoseconds, and the detector measures the dispersion in time of the exiting light [28]. Due to the speed of the response, the detected light is typically measured by singlephoton detectors coupled to time-correlated single-photon counting (TCSPC) hardware [29]. In TCSPC, the arrival time of individual photons are measured in relation to a reference signal, typically the electrical trigger from a pulsed light source. Photons are accumulated over many cycles to achieve a certain statistical precision. The data is then output in the form of a histogram, where the bins on the x-axis represent arrival time windows and the y-axis is the number of photons to arrive in that window, this histogram is termed the time point-spread function (TPSF). Of the two, FD instruments can be implemented with simpler, cheaper hardware, and provide better SNR and time resolution [30]. However, to provide

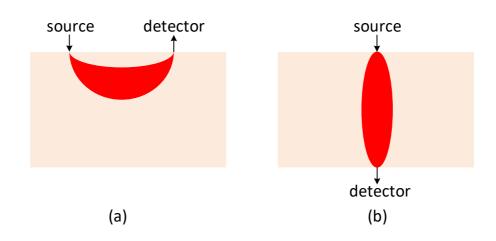

Figure 1.4 – Measurement geometry of NIRS in (a) reflectance and (b) transmission modes. The red region illustrates where the trajectories of most detected photons will be confined.

equivalent information to the TPSF in the TD method, an FD instrument must scan through a range of frequencies from 50 MHz to 1 GHz [31], thus increasing the system complexity and degrading the time resolution.

A crucial limitation of NIRS in comparison to established imaging methods such as MRI or PET is the depth penetration. NIRS instruments are typically employed with the source and detector in contact with the patient in either reflectance, Figure 1.4a), or transmission, Figure 1.4b), modes. In both of these figures, the region in which most of the photon trajectories are confined is illustrated in red, showing the diffuse nature of photon propagation. In reflection mode, due to the exponential decay of light intensity, Figure 1.2, a source-detector separation in the region of 1-4 cm is typically employed [32]. Since the source-detector spacing is proportional to the depth penetration in CW and single frequency FD methods, a source-detector separation of 4 cm translates to a depth penetration of approximately 2-3 cm. This can be increased by measuring the medium in transmission mode, where the source and detector are on opposite sides of the tissue under study. In this configuration a depth penetration of up to 6 cm can be achieved. In practice, transmission mode is applied in relatively few cases such as optical mammography [33] whilst the reflectance mode is highly versatile and applicable to a much larger number of situations.

In the TD method, the source-detector separation is not proportional to the depth penetration since the TPSF allows the discrimination between early and late photons. Thus, in principle the TD method can be used at very small source-detector separations to achieve up to 6 cm penetration depth [34]. In practice, these small source-detector separations can only be implemented by gating the detector on for small windows of time, [35], due to the large

#### **Chapter 1. Introduction**

dynamic range requirement. The power of the laser source can then be adjusted as the gate window is moved to encompass the entire TPSF, e.g. low power for the earliest window and increasing for late windows. Thus, the dynamic range required of the detector is reduced.

## 1.4 Near-infrared Optical Tomography (NIROT)

Whilst NIRS is a widely employed tool for measuring the oxygenation state of human tissue, resolving localized changes in oxygenation with millimetric accuracy requires a tomographic approach. This tomographic approach is termed NIROT here, but is also commonly referred to as diffuse optical tomography, or diffuse optical imaging. NIROT is enabled by multi-channel hardware, illuminating the tissue and sampling the diffuse light at different points on the tissue boundary. Due to the multi-source, multi-wavelength nature of the measurement system, NIROT has a lower time resolution in comparison to NIRS. To obtain 3D images of the oxygenation state, e.g. concentrations of O<sub>2</sub>Hb and HHb within the tissue volume, a two-step reconstruction [36] is performed. In the first step, a forward model for light propagation in the medium under study is defined. This forward model can be based on the radiative transfer equation (RTE) [37], the diffusion approximation, which is a simplified version of the RTE, or alternatively on numerical models such as the finite element method [18] and Monte Carlo methods [38]. The problem is then inverted, in what is known as the inverse problem, and measurements from the tissue boundary are used to reconstruct the absorption and scattering properties of the medium. An extensive coverage of image reconstruction in NIROT can be found in [36, 39, 40].

A major difference between NIROT and conventional imaging modalities such as MRI or PET, is that the image reconstruction problem is ill-posed due to the absorbing and scattering nature of tissue [41]. Furthermore, it is often underdetermined since there are more voxels to reconstruct than there is measurement information [42]. The ill-posed nature of the problem can be reduced by providing the image reconstruction with more information. This can mean including prior information of the tissue under study [39], employing TD instruments which provide the richest datasets, or increasing the number of sources and detectors [42].

The spatial resolution of NIROT systems can be divided into lateral and depth resolution. Due to photon migration in tissue, the lateral resolution in NIROT measurements degrades with depth penetration and decreased depth selectivity [32]. As such, a fair comparison of lateral resolution should be made at a fixed depth. Lateral resolution in NIROT reconstructions can be improved by reducing the ill-posed nature of the reconstruction, as stated previously.

Depth resolution can be improved by employing a time-domain instrument with a narrower instrument response function (IRF) although the influence of the IRF can be partially overcome with deconvolution algorithms [43, 44]. Thus, from a hardware perspective, it appears that a time-resolved system with a large number of narrow IRF detectors is the most promising instrumentation for achieving NIROT reconstructions with a high lateral and depth resolution.

## 1.5 Time-resolved Instrumentation

Early time-resolved systems employed photomultiplier tubes (PMTs) as photodetectors [45, 46, 47], whilst the time-resolved information was acquired with dedicated TCSPC hardware. Due to the size of the PMTs, light is coupled from the target to the photodetectors via a fibre bundle. This results in some loss of light as well as a small temporal dispersion of the TPSF [45]. Furthermore, this coupling of light into and out of the measurement subject makes scaling the system to large numbers of sources and detectors very difficult. For example, a PMT based system with 32 sources and 32 detectors coupled via fibres [45, 48] is already cumbersome. This low number of sources and detectors results in a spatial resolution in the 1-2 cm range in a NIROT application [49], limiting uptake in clinical settings. Furthermore, it is difficult to imagine scaling such a system to several hundreds of sources and detectors. Additional complexities of PMTs are the requirement of a high voltage, 3.2 kV in [45], cooling elements for temperature stability and high cost (> 5 k€ per unit) [50].

Recently, systems based on silicon photomultipliers (SiPMs) have been developed which overcome many of the shortcomings of PMTs [50, 51]. SiPMs are solid-state detectors where the outputs of many SPADs are summed together to form a macrocell. Thus, despite consisting of a large number of detectors, SiPMs typically have few macrocells, e.g. 4 × 4. However, their large photosensitive area, which can be several mm<sup>2</sup>, means that they can be placed on a small printed circuit board (PCB) and placed in direct contact with measurement subject. This avoids the complexity and losses associated with fibre coupling. Such detectors are available for a relatively low cost, e.g. < \$100 per unit, and do not require an extremely high voltage, as is the case with PMTs. Furthermore, TDCs are employed to acquire the time-resolved data, which can be purchased for less than \$1000 dollars per channel [51] in comparison to a TCSPC board at > 8 k€ per unit. The combination of SiPMs with TDCs represents a leap forward for time-resolved hardware. Despite these improvements, however, the application of discrete sensor probes attached to the measurement subject means that scaling up the system to a large number of sources and detectors would remain cumbersome.

#### **Chapter 1. Introduction**

An approach to NIROT which does not involve fibre coupling or probes based on discrete hardware acquires time-resolved data with a gated intensified charge-coupled device (CCD) camera [52, 53]. This method has the benefit of being able to acquire images over a wide field of view (FOV) with a large number of detectors, thus it can in principle be used for a high-resolution NIROT system. Gated operation implies that the measurement time is increased, since the complete TPSF must be acquired in several windows. On the other hand, the power can be increased or decreased depending on whether the window is early or late. There is thus, a delicate balance between the laser power and gate window length. A disadvantage of the gated CCD approach is the minimum length of the gate window with 300 [52] and 500 [53] ps, which is inferior to the state-of-the-art IRF of the SiPM at 130 ps [50], and 80-150 ps of the PMT [45].

A compelling alternative to gated CCD cameras, which still employ an array of detectors but exploit the TCSPC approach are image sensors based on CMOS SPAD. SPADs first came to prominence in the 1970s and 1980s, as researchers identified their potential for observing scientific phenomena on the picosecond scale [54]. As early as 1989, SPADs with full width at half maximum (FWHM) down to 20 ps [55] had been reported. Despite the speed of such devices, the hardware required to implement multi-channel systems was prohibitively bulky and expensive. A major breakthrough was made, with the demonstration of the first SPAD in CMOS [56]. Soon multi pixel SPAD arrays could be produced [57] and finally, SPAD arrays with integrated TDCs [58, 59], achieving a timing response FWHM in the range of 100-250 ps.

In [42] an early  $128 \times 128$  time-resolved SPAD camera [58] was applied in NIROT phantom experiments, demonstrating a spatial resolution of 5 mm. A number of other systems have been developed employing individual SPADs with TCSPC systems in both free-running and gated modes, a review of which can be found in [60]. Time-resolved cameras based on SPADs are a compelling prospect for two reasons. The possibility for a large number of detectors with a narrow timing resolution could lead to unprecedented spatial resolution in NIROT, whilst the future possibility to gate such a camera would lead to improve depth sensitivity.

## 1.6 Motivation and Aims of the Thesis

Oxygen is an extremely important clinical marker. For example, preterm infants commonly suffer from brain injuries caused by a lack of oxygen in the brain. The treatment window for such injuries is very small, typically just 6 hours. Similarly, hypoxia in cancer tumors is an indicator of increased resistance to radiation and chemo- therapies. The oxygenation state of tumors could lead the way to more effective treatments and accurate prognosis. Therefore, there is a stringent need for a safe, non-invasive, reliable and inexpensive method to measure the oxygenation state of the human body. Despite this need, no existing method is widely applied in clinics. In particular, the current gold standard, PET suffers from high costs, poor time resolution, as well as the use of ionizing radiation.

NIROT presents a promising alternative for measuring the oxygenation state of human tissue. It is safe, as it uses only non-ionizing radiation, can be employed for continuous monitoring and is relatively cheap in comparison to established imaging modalities, e.g. PET or MRI. However, the major obstacle preventing widespread uptake of NIROT in clinical applications is a limited spatial resolution. This is important, for example, to localise regions of the preterm brain with an oxygen deficit and to measure hypoxia heterogeneity across cancer tumors. To increase the spatial resolution of NIROT, the information available for the reconstruction should be maximised. Practically, this means employing a large number of time-resolved detectors in a multi-wavelength measurement.

Up to now, most TD NIROT systems have employed discrete photodetectors such as photomultiplier tubes with bulky TCSPC boards for the timing conversion [45, 46, 47]. Although more recent systems have been based on more compact and less costly SiPMs and TDCs, it remains difficult to scale systems based on discrete hardware to large numbers, e.g. > 500 detectors.

In this thesis we advocate the use of time-resolved image sensors based on SPAD arrays for NIROT. Thanks to SPAD integration in CMOS, a very large number of single-photon detectors is possible. The power of applying a time-resolved SPAD sensor to the NIROT application was demonstrated in [42], where a spatial resolution of 5 mm was achieved in a laboratory experiment. However, whilst these cameras are an exciting prospect for implementing a NIROT system with millimetric spatial resolution, the image acquisition time with existing sensors is prohibitively slow [42]. In clinical measurements a long acquisition time will result in motion artifacts and decreased patient comfort. The slow acquisition time is due to two issues, the low sensitivity of the image sensor and rate at which photons can be acquired, e.g. the sensor throughput. This thesis aims to address both of these issues and produce instruments which are suitable for high resolution clinical NIROT measurements.

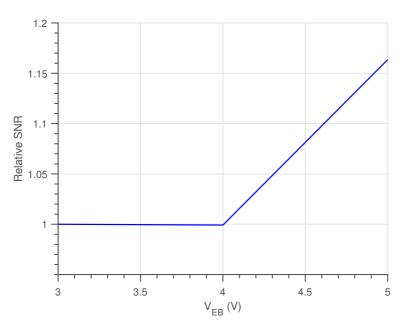

For a fast data acquisition, the sensitivity of the sensor, the SNR, should be maximised. Similarly, to handle the large range of intensities across the sensor as seen in Figure 1.2, a high dynamic range is required. The first aim of this thesis was to investigate new SPAD pixels for improved SNR and dynamic range.

A major factor in the slow acquisition speed of current time-resolved SPAD sensors is the low throughput of conventional circuit architectures. The second aim was to design and implement a  $32 \times 32$  time-resolved SPAD camera for reflection mode NIROT measurements which overcomes the low throughput of existing architectures.

A compelling prospect for NIROT is the possibility of capturing wide-field images without requiring any mechanical scanning of the detectors across the FOV. To enable this, the third aim was to develop a larger format,  $252 \times 144$  time-resolved SPAD camera which extends the architecture already developed whilst maintaining a fast data acquisition time.

## 1.7 Thesis Organization

In Chapter 2, a background to SPADs and the impact of design decisions on system performance is discussed. Two new SPAD pixel structures for improved SNR and dynamic range in time-resolved measurements are then presented. Chapter 3 begins with a review of timeresolved SPAD imagers and a discussion of the challenges involved in their design. A new architecture which is targeted at the NIROT application is presented. In Chapter 4, a  $32 \times 32$ pixel sensor based on this architecture is produced and measurement results reported. This architecture is extended in Chapter 5 to a  $252 \times 144$ -pixel format sensor, with circuit additions made to maintain a high event throughput. In Chapter 6, conclusions are drawn and an outlook presented for the future time-resolved SPAD sensors applied to NIROT.

# 1.8 Thesis Contributions

Due to the challenging optical environment in NIROT, pixels with high **SNR and DR** are required. In Chapter 2, two new pixels designs, produced in a BSI 3D IC technology, are presented. The first pixel employs a new quenching and recharge structure based on the cascode technique which can operate the SPAD at increased excess bias voltages, thus increasing the sensitivity and timing performance. Implemented using only transistors, the circuit is compact and remains compatible with active quenching and recharge schemes. To the best of the author's knowledge, this is the first quenching and recharge circuit which is capable of operating above the maximum voltage tolerance of a single transistor without the use of large polysilicon resistors. Implemented with an active recharge scheme, the pixel achieves the lowest afterpulsing at 8-ns for a BSI SPAD to date. The second pixel design exploits the

flexibility of 3D IC technologies, to demonstrate the first SPAD pixel which is capable of interfacing to a SPAD via the anode or cathode terminal. This opens the door to new 3D IC sensors which exploit a general purpose data processing tier which can be interfaced with different application specific photodetector tiers.

Chapter 3 presents a new sensor architecture for **high-PDE time-resolved SPAD imagers**. Motivated by the short acquisition time required by the NIROT application, a new architecture is proposed which overcomes the low fill factor and throughput of conventional TDC-inpixel architectures. By employing an event-driven bus and dynamic TDC reallocation, a small number of TDCs can be shared by a large number of pixels. A collision detection bus is included to detect events which are the result of coincident photons on the shared bus. Analysis of missed photons due to the shared architecture with dedicated GPIO and LVDS pads per column shows that it is easily scalable to higher bus activities. Analysis of collision rates with data from NIROT forward simulations showed less than 3.5% of colliding photons at maximum bus activity. Since the maximum bus activity, and therefore the number of shared TDCs required, is limited by the output data rate, the number of pixels in the array can be extended to large numbers without an impact on pixel fill factor or overall throughput.

In Chapter 4, a  $32 \times 32$ -pixel time-resolved sensor based on the architecture in Chapter 3 is presented. Produced in a 180 nm CMOS technology, the sensor includes a wide-spectral range SPAD for low DCR and high PDP. The cascoded quenching and recharge circuit developed in Chapter 2 is employed to increase PDE. Power consumption is minimised with the design of a ring oscillator (RO) based TDC. The manufactured sensor achieves an unprecedented 28% fill-factor in a pixel pitch of 28.5 $\mu$ m with a maximum throughput of 220 Mevents/second. At this event rate,  $10^6$  photons can be acquired for every pixel in the array in 4.6 seconds, thus it is highly relevant for a clinical NIROT setting.

With the main goal of the thesis being to develop a **high throughput wide-field time-resolved SPAD sensor**, the architecture in Chapter 3 is extended to a 252 × 144 pixel sensor in Chapter 5. A bus repeater scheme is implemented to make the collision detection bus scalable. This addition allows the column to be extended without adverse impact on the bus dead time, timing jitter or pixel PDE. A per-pixel integrated histogramming scheme was developed to increase the photon throughput and thus minimise the image acquisition time in NIROT clinical measurements. To the best of the author's knowledge this is the first integrated histogramming scheme implemented for a full array. Modifications were made to the RO based TDC from Chapter 4, to continue employing the low power RO based technique whilst remaining compatible with the integrated histogramming readout. A clock generation scheme was

#### **Chapter 1. Introduction**

developed to achieve operation with a large range of laser frequencies without impacting the system timing response. The manufactured sensor retains the unprecedented 28% fill factor and narrow 110 ps FWHM timing response of the sensor in Chapter 3, whilst the integrated histogramming scheme enables a compression factor of up to 14.9. This compression factor can be employed to reduce the power consumed by the I/O pads or to increase the image acquisition speed of the sensor. Therefore, the manufactured sensor is highly suitable for NIROT measurements, opening the door to high resolution clinical systems.

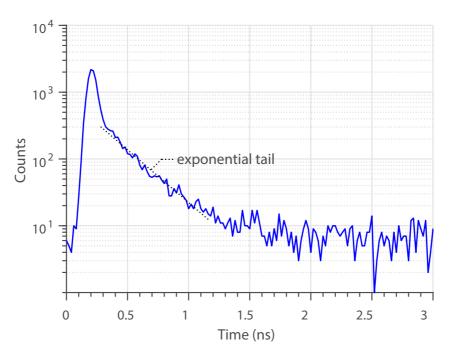

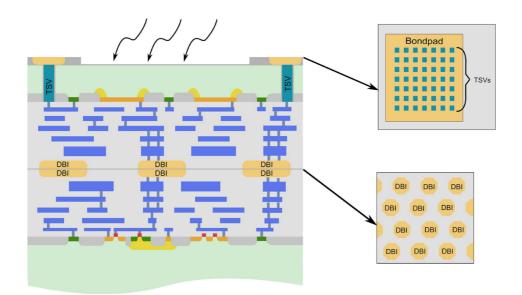

# 2 Pixels for Improved SNR and Dynamic Range

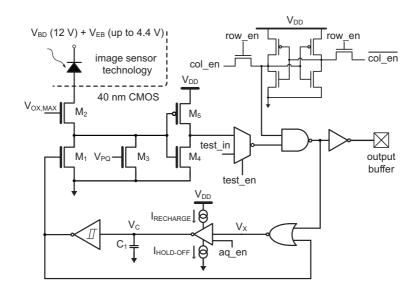

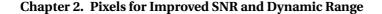

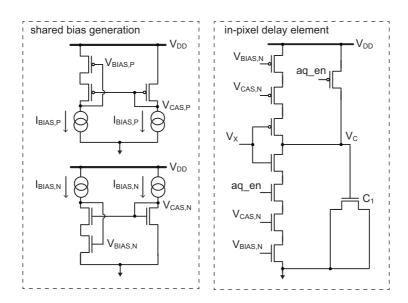

NIROT is an extremely challenging optical environment for time-resolved image sensors. Due to the requirement for multiple source positions, which then need to be measured at a number of different wavelengths, many individual acquisitions must be made for a single reconstructed image. Thus, it is critical that each acquisition be completed in a short time, a number of seconds if possible. A high SNR and dynamic range are critical to achieving this goal. This chapter begins with a section dedicated to SPAD operation before discussing the SPAD characteristics and system level metrics which impact the duration and quality of NIROT measurements. Two new pixel designs are then demonstrated which can improve the SNR and dynamic range in a NIROT measurement. Results from the cascoded active recharge pixel are published in, S. Lindner et al., "A High-PDE, Backside-Illuminated SPAD in 65/40-nm 3D IC CMOS Pixel With Cascoded Passive Quenching and Active Recharge," in *IEEE Electron Device Letters*, vol. 38, no. 11, pp. 1547-1550, Nov. 2017.

## 2.1 Single-photon avalanche diode (SPAD) Operation

A SPAD is a p-n junction which is reverse biased at a voltage  $V_{OP}$ . This is composed of the device breakdown voltage  $V_{BD}$ , which is determined by the device doping profiles and the excess bias voltage,  $V_{EB}$ , a parameter chosen by the user dependent on desired performance. When the reverse bias of a SPAD is set above its breakdown voltage the device is said to operate in Geiger-mode. When a photon arrives at or in close proximity to the depletion region, it can create an electron-hole pair, which with some probability can ignite a self-sustaining avalanche of mobile carriers via ionization of both holes and electrons. The region where 95% of the ionization occurs is termed the multiplication region. Once an avalanche has been initiated, the device would maintain this state until its destruction. For this reason,

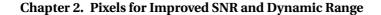

Figure 2.1 – (a) Simple SPAD front-end, (b) Cross section of CMOS SPAD. Structure reported in [62]

a SPAD may be connected in series with a ballast resistance, shown in Figure 2.1a. This resistance quenches the avalanche by reducing the current flowing to less than  $\approx 100\mu$ A [61] as the voltage across the SPAD decreases towards V<sub>BD</sub> due to the space charge dynamics in the depletion region. Below this current, the avalanche is no longer self-sustaining and the depletion region becomes free of carriers once again. The voltage across the SPAD can then be recharged to V<sub>OP</sub> through the ballast resistance.

The almost infinite optical gain implied by the creation of this avalanche of carriers means that SPADs are sensitive to the arrival of individual photons. Indeed, the output of the SPAD is connected to some discrimination electronics, which senses when the SPAD output voltage has passed a set threshold, this can be a comparator or as simple as a logic inverter, as depicted in Figure 2.1a. In this manner, a transition of the inverter output,  $V_{OUT}$ , from logic '1' to '0' signifies an avalanche event, or the arrival of at least a single photon. Therefore, SPADs are suitable for single-photon counting and TCSPC applications.

Whilst SPADs have been under investigation for a number of decades, it was only in 2003 that the first SPAD was fabricated in a CMOS technology [56]. An example of a SPAD is illustrated in Figure 2.1b. The depletion region and guard ring region, which ensures the electric field is highest in the multiplication region, are formed from layers already available in the CMOS process. Therefore, the performance of CMOS SPADs is typically inferior to those produced in custom processes, since the doping profiles are not been optimized. However, the possibility of integrating SPADs and CMOS electronics on the same silicon die is a great advantage, and enables the production of SPAD arrays with circuits for photon timing or counting. Due to this complex functionality, and the overhead for the SPAD, the pixel fill-factor, the area of the pixel which is sensitive to light, tends to be small.

## 2.2 SPAD Characteristics

To understand the challenges for developing pixels for a NIROT system it is instructive to first discuss the various characteristics of SPADs which will determine the performance. Particular attention is given to pixel design considerations. A more device physics oriented review can be found in [63].

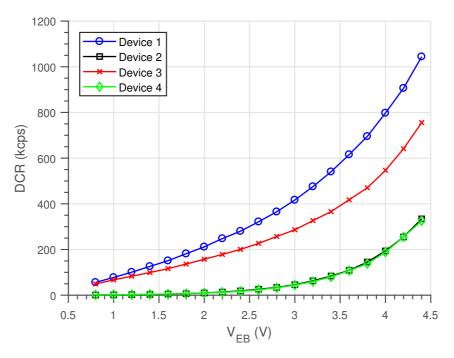

#### **Dark Count Rate**

Dark counts are the occurrence of uncorrelated avalanche events in the absence of any photons impinging on the active region. The frequency is given by the dark count rate (DCR), measured in counts per second (cps) or Hertz (Hz). Although there are many physical mechanisms which contribute to DCR [64], they can be said to be due to either tunneling or thermal generation. A major source of noise is band-to-band tunneling [65], which is moderately dependent on temperature and highly dependent on doping concentrations. Furthermore, a high dependence on the electric field strength in the depletion region means this noise is very sensitive to the SPAD excess bias,  $V_{EB}$ . As process nodes used to develop SPAD imagers have shrunk below 100nm, band-to-band tunneling noise has become dominant due to the heavy doping concentrations of the native implants. To improve the noise performance at these nodes, custom layers have been defined for SPAD production [66]. Thermally generated noise is highly dependent on the density of lattice defects or "traps", which capture and then release carriers after some time duration dependent on the implantation and annealing processes in fabrication [63]. The contribution due to this trap assisted noise is exponentially dependent on temperature.

#### **Photon Detection Probability**

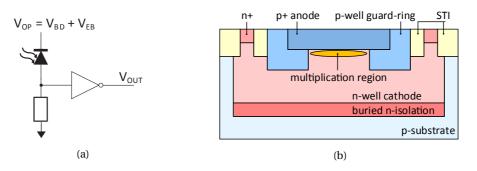

The photon detection probability (PDP) defines the likelihood of producing an avalanche for each photon incident on the active region of the SPAD. When a photon is incident on the detector, the depth at which it is absorbed and creates an electron-hole pair is dependent on the optical properties of the detection material. This dependency as a function of wavelength is given by the mean penetration depth, shown for silicon in Figure 2.2. Electron-hole pairs which are not created in the immediate vicinity of the multiplication region, e.g. too shallow or too deep in the silicon, will likely recombine before triggering an avalanche. As such, the peak PDP appears at the wavelength which has a mean penetration depth corresponding to the multiplication region depth. This is in the range of 400-560 nm in frontside-illuminated (FSI)

Chapter 2. Pixels for Improved SNR and Dynamic Range

Figure 2.2 – Mean penetration depth in silicon as a function of wavelength, data taken from [1].

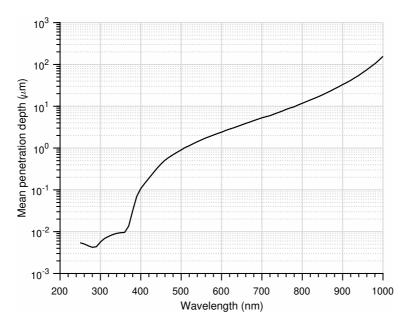

planar SPADs [67], corresponding to a multiplication region depth in the range of 100-1700 nm. Importantly, the electric field across the depletion region determines the ionization rate within the multiplication region. This means that the PDP of a SPAD can be improved by increasing the SPAD excess bias,  $V_{EB}$ . Practically, the excess bias cannot be increased indefinitely as PDP improvement diminishes at higher bias voltages and the DCR is also increased. This diminishing improvement does however mean that higher excess bias voltages can be employed to improve PDP uniformity in SPAD arrays [67]. This is illustrated in Figure 4.12, which shows that the gain in PDP as a result of increasing excess bias reduces as the voltage is increased and the PDP spectrum reaches the compression point.

#### **Timing Jitter**

One of the major benefits of SPADs is their timing response, characterized by a low timing uncertainty, or jitter, between a photon being absorbed and the output voltage of the SPAD reaching the comparison threshold of the discrimination circuitry. The SPAD has jitter because the build up and spread of each avalanche is dependent on the position [68] of the avalanche ignition and the statistics of the ionization process. The statistics of the avalanche process are responsible for the characteristic gaussian component of the timing response, usually expressed as the full width at half maximum (FWHM). Similar to the PDP, the timing jitter of a SPAD can be improved by increasing the ionization rate in the multiplication region by

Figure 2.3 – Compression of PDP spectrum with increasing  $V_{EB}$ .

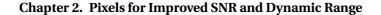

raising  $V_{EB}$ . Photons which are absorbed in the neutral region beneath the SPAD can also trigger avalanches but only after diffusing. Thus, the time to trigger the avalanche can take orders of magnitude longer than those photons which are absorbed in the depletion region. This mechanism is responsible for the slow exponential tail seen in the timing response, an example of which is given in Figure 2.4, where the tail has a time constant of 250 ps.

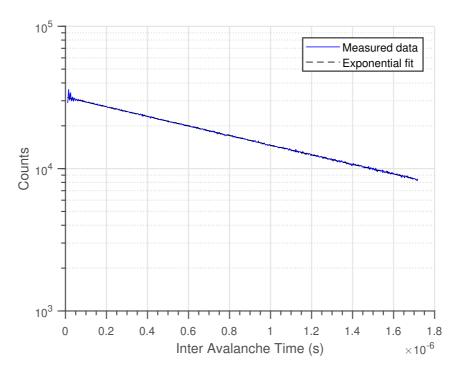

#### Afterpulsing

As well as being a major source of uncorrelated noise, as discussed in section 2.2, traps in the silicon lattice can also produce correlated noise in the form of afterpulsing. Carriers involved in the avalanche process can become captured by traps with an energy close to the energy bands of semiconductor. The release of these carriers can happen after a number of nanoseconds. If the SPAD excess bias has been sufficiently recharged by this point then the carrier release can trigger a second avalanche. Thus, the afterpulsing probability,  $P_{AP}$ , indicates the probability of an avalanche event resulting in a secondary avalanche via afterpulsing. Afterpulsing can be reduced by decreasing the number of carriers which flow during an avalanche or by minimising  $V_{EB}$ , and thus the probability of an avalanche, in the period that these secondary carriers will be released. These techniques are known as active quenching and active recharge, respectively.

Figure 2.4 – Timing response of a SPAD with slow exponential tail, highlighted. The time constant of the tail is 250 ps.

#### Crosstalk

Crosstalk is correlated noise which is the result of an initial avalanche resulting in one or more secondary avalanches in neighboring SPADs. It can be categorised as being electrical or optical.

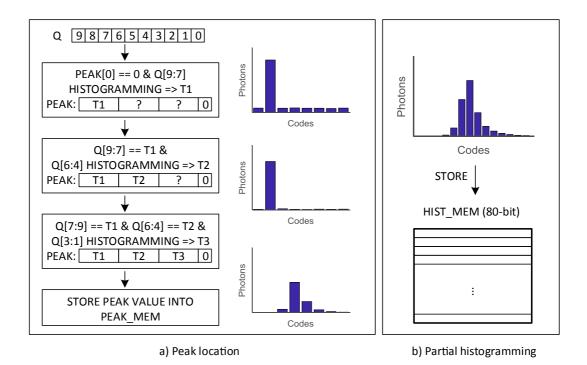

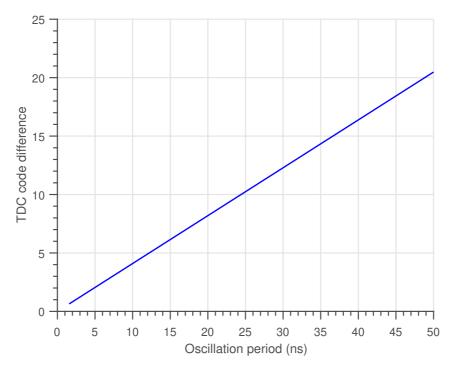

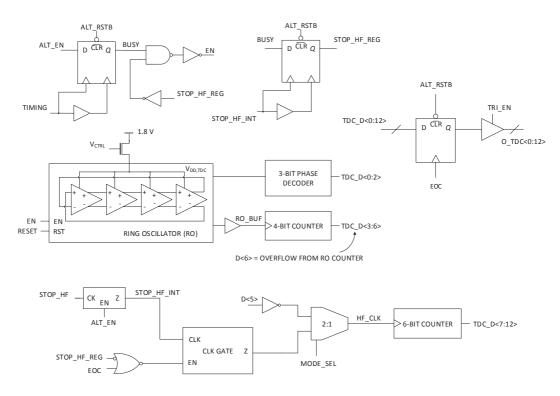

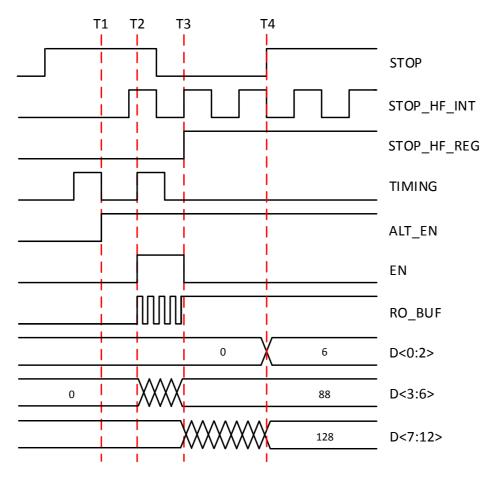

Electrical crosstalk can occur as the result of capacitive coupling from the anode or cathode terminals of neighboring devices. It can be reduced to a negligible level with careful layout of the sensor and PCB. As such, this effect is not widely reported in the literature.