# Learning-Based Hardware Design for Data Acquisition Systems

THÈSE Nº 8693 (2018)

PRÉSENTÉE LE 24 AOÛT 2018 À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR LABORATOIRE DE SYSTÈMES D'INFORMATION ET D'INFÉRENCE PROGRAMME DOCTORAL EN GÉNIE ÉLECTRIQUE

# ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

# Cosimo APRILE

acceptée sur proposition du jury:

Dr J.-M. Sallese, président du jury Prof. V. Cevher, Prof. Y. Leblebici, directeurs de thèse Prof. A. Emami, rapporteuse Dr C. Menolfi, rapporteur Prof. C. Dehollain, rapporteuse

Nullius in verba. — Epistle, Orace

To my mother, my brother and To the memory of my father

# Acknowledgements

This Ph.D thesis work has been supported by many people throughout these years. First and foremost, I would like to thank my advisors Prof. Yusuf Leblebici and Prof. Volkan Cevher for giving me the opportunity to pursue my doctoral degree at EPFL under their constant guidance. In particular, I would like to thank Prof. Leblebici for his endless support, kindness, patience and for giving me the motivation, enthusiasm and guidance. He was my advisor at the time of my Master thesis and I really thank him for giving me the opportunity to continue my studies in his lab, opening me the doors to improve drastically my personal and professional profile, working on many exciting projects. Before I started my Ph.D, he introduced me to Prof. Cevher who became my advisor during these years. I am very thankful to Prof. Cevher for many reasons. First of all, he constantly showed me the way to reach the top, giving me many fruitful advices and some times trying me, giving me challenges to push my motivation. Without his advices and his will for excellence, this work would not have been possible. I am also very thankful to Prof. Yusuf Leblebici and Prof. Volkan Cevher for allowing and enabling many collaborations during these years, in particular with IBM Zurich Research Laboratory and RFIC group and EPFL.

I am very grateful towards the members of my thesis committee: Prof. Azita Emami, Dr. Christian Menolfi, Prof. Jean-Michel Sallese and Prof. Catherine Dehollain for their useful comments, patience and time in reading this dissertation. Moreover, I am sincerely thankful to Prof. Catherine Dehollain and Dr. Thomas Toifl for the very fruitful collaboration established among our groups. This work would not have been possible without their outstanding project ideas and commitment.

I would like to thank Dr. Alain Vachoux for his timeless support on CAD tools and nice time spent together and Dr. Alexandre Schmid for his support with computing infrastructure.

My deepest gratitude goes to Dr. Luca Baldassarre for all his extraordinarily support. Luca has been one of the most important person during these years. In few words, Luca inspired me. He showed me how to work hard, being professional while still enjoying your life with many activities. I really appreciated all the brainstorming we had even after he left EPFL. And I can not forget all the times we challenged our-selfs in climbing gym and running, waiting for Elias to grow and climb with us...Luca, thank you and to your lovely family!

I am extremely grateful to Dr. Alessandro Cevrero who has been a constant guidance during these years. Thanks to his positive mood and determination we have managed to reach great results during the collaboration at IBM Zurich Research Laboratory. Thank you so much Ale, you are the man!

#### Acknowledgements

I can not forget to thank Dr. Jury Sandrini. I really thank him for being a great colleague and friend during our Ph.D. We shared great times, nice coffee breaks, climbs and my few skiing experiences. It has been a pleasure to share the office space with you!

I acknowledge Dr. Kiarash Gharibdoust for his friendship, guidance and assistance on circuit modeling. We were office mates for 2 amazing years. Thank you *doostam*!

I would like to express my gratitude to Prof. Mahsa Shoaran. Our constant discussions and brainstorming have been source of new ideas and solutions to problems.

Many thanks to Kerim Ture for the great collaboration we had during these years. I really enjoyed working together with a great engineer and kind person as you, Kerim!

I would like to thank all former and current members of LSM and lions@epfl laboratories. Especially, I am very thankful to Jonathan Narinx for his friendship and his positive behavior. I really appreciate his help on CAD tools and his constant support in the different phases of my last 2 years in the lab. I have been very lucky to find a true friend on top of a great colleague and engineer. Thank you, Jonny!

Thanks a lot to Arda Uran for his support and kindness. In these months I have been truly impressed by his preparation and positive attitude and I am sure Arda will reach great results during his research.

Thanks to Dr. Tugba Demirci for her constant support, especially during the tape-out periods. Thanks to Sylvain Hauser, for his kind support and nice time shared together during all these years. Thanks to Selman, Mustafa, Radisav, Nikola, Vladan, Clemens, Kadir, Giulia, Sebastian, Gulperi, Ayca, Firat, Can, Irem, Bilal, Wen-Yang, Duygu, Omer, Seniz and Kerem for the funny and joyful moments we shared. A special thank to Elmira Shahrabi and Reza Ranjandish (*navidinho*), for the constant support and friendship. Thanks to all the *lions* people, especially to Dr. Anastasios Kyrillidis (*Tasos*) for his friendship; the amazing Prof. Bah Bubacarr who supported me a lot during my first complicate year; Prof. Tran-Dinh Quoc for sharing his knowledge and kindness; Baran Gozcu for all the good times we spent together; Dr. Marwa El Halabi for her friendship, Alp Yurtsever, Ilija Bogunovic and Dr. Yen-Huan Li.

A special thank goes to Dr. Mariazel M. Lopez. Among all these years I really enjoyed our discussions and all the time spent together. Thank you so much for your unconditional support, encouragement and inspiration, zellina!

A great thank goes to Mattia D'Agostino, Matteo Cossale and Yari Ferrante. Even if we are far away from each other, we have managed to keep our great friendship. Life would have been more tough without you, guys.

Thanks to Dr. Enrica Montinaro who (likely) was my home-mate during my first 2 years of Ph.D. We had amazing times together in our villa. Thanks for your true friendship, Enri!

I am also thankful to the secretaries of LSM and lions@epfl laboratories, Melinda Mischler, Patricia Vonlanthen and Gosia Baltaian as well as the secretary of the doctoral program Vanessa Maier.

I would like to thanks my colleagues from IBM Zurich Research Laboratory for their useful technical discussion: Lukas Kull, Pier Andrea Francese, Christian Menolfi, Matthias Brandli, Gain Kim, Ilter Oezkaya and Marcel Kossel. I am also thankful to my colleague from TCL laboratory Andrea Bonetti and Prof. Andreas Burg.

Last but foremost, I am hugely indebted to my parents, my brother and my girlfriend. Ringrazio mia madre, per il suo supporto incondizionato, il suo infinito amore e per rappresentare la mia ancora. Mio padre, per avermi insegnato i giusti valori e per avermi spinto a superare i miei limiti e a vincere le mie paure.

Mio fratello Antonio, esempio di forza e determinazione, ispirazione di grinta e motivazione. Grazie a zia Lucia per il suo conforto e la sua meravigliosa presenza. Grazie a zio Gigi per avermi insegnato tanto e per tutto il supporto negli anni. Grazie a zia Ada e zio Tonino...

Grazie ad Andrea F. Re, per essere stato, da sempre, un amico fraterno. Grazie alla mia fidanzata Rachele, per essermi stata sempre presente, per avermi aiutato a superare i momenti piu difficili, per tutta la pazienza e l'incoraggiamento.

Lausanne, 24 August 2018

Cosimo Aprile

# Abstract

This multidisciplinary research project aims to investigate the optimized information extraction from signals or data volumes and to develop tailored hardware implementations that trade-off the complexity of data acquisition with that of data processing, conceptually allowing radically new device designs. The mathematical results in classical *Compressive Sampling* (CS) support the paradigm of *Analog-to-Information Conversion* (AIC) as a replacement for conventional ADC technologies. The AICs simultaneously perform data acquisition and compression, seeking to directly sample signals for achieving specific tasks as opposed to acquiring a full signal only at the Nyquist rate to throw most of it away via compression. Our contention is that in order for CS to live up its name, both theory and practice must leverage concepts from learning. This work demonstrates our contention in hardware prototypes, with key trade-offs, for two different fields of application as edge and big-data computing.

In the framework of edge-data computing, such as wearable and implantable ecosystems, the power budget is defined by the battery capacity, which generally limits the device performance and usability. This is more evident in very challenging field, such as medical monitoring, where high performance requirements are necessary for the device to process the information with high accuracy. Furthermore, in applications like implantable medical monitoring, the system performances have to merge the small area as well as the low-power requirements, in order to facilitate the implant bio-compatibility, avoiding the rejection from the human body. Based on our new mathematical foundations, we built different prototypes to get a neural signal acquisition chip that not only rigorously trades off its area, energy consumption, and the quality of its signal output, but also significantly outperforms the state-of-the-art in all aspects.

In the framework of big-data and high-performance computation, such as in high-end servers application, the RF circuits meant to transmit data from chip-to-chip or chip-to-memory are defined by low power requirements, since the heat generated by the integrated circuits is partially distributed by the chip package. Hence, the overall system power budget is defined by its affordable cooling capacity. For this reason, application specific architectures and innovative techniques are used for low-power implementation. In this work, we have developed a single-ended multi-lane receiver for high speed I/O link in servers application. The receiver operates at 7 Gbps by learning inter-symbol interference and electromagnetic coupling noise in chip-to-chip communication systems. A learning-based approach allows a versatile receiver circuit which not only copes with large channel attenuation but also implements novel

#### Abstract

crosstalk reduction techniques, to allow single-ended multiple lines transmission, without sacrificing its overall bandwidth for a given area within the interconnect's data-path.

#### Key words:

Implantable integrated circuit, area-efficient, low-power, compressive sensing, neural signals, learning-based digital signal processing, signal recovery, medical monitoring, adaptive compression. Far-end crosstalk, Decision-Feedback Equalizer, Inter-Symbol Interference, source-synchronous architecture, Continuous Time Linear Equalizer.

# Résumé

Ce projet de recherche multidisciplinaire vise à étudier l'extraction d'informations optimisée à partir de signaux ou de volumes de données et à développer des implémentations matérielles dédiées qui transforment la complexité de l'acquisition de données en traitement de données permettant de concevoir des dispositifs radicalement nouveaux. Les résultats mathématiques de l'*Acquisition comprimée (Compressive Sampling,* CS) classique prennent en charge le paradigme de la *Conversion analogique-à-information (Analog-to-Information Conversion,* AIC) en remplacement les technologies ADC classiques. Les AICs effectuent simultanément l'acquisition et la compression des données, en cherchant à échantillonner directement les signaux pour réaliser des tâches spécifiques, par opposition à l'acquisition d'un signal complet uniquement à la fréquence de Nyquist pour en éliminer la plus grande partie par compression. Notre thèse est que, pour que le CS suive son nom, la théorie et la pratique doivent tirer parti des concepts de l'apprentissage. Ce travail démontre notre prétention dans les prototypes de matériel, avec des compromis clés, pour deux domaines d'application différents comme le calcul de bord et de big-data.

Dans le cadre de l'informatique de bord, tel que les écosystèmes portables et implantables, le budget de puissance est défini par la capacité de la batterie, ce qui limite généralement les performances et la facilité d'utilisation de l'appareil. Ceci est plus évident dans les domaines très exigeants, tels que la surveillance médicale, où des exigences de haute performance sont nécessaires pour que l'appareil traite l'information avec une grande précision. En outre, dans des applications telles que la surveillance médicale implantable, les performances du système doivent résulter en une petite taille tout en répondant aux exigences de faible puissance, afin de faciliter la biocompatibilité de l'implant en évitant le rejet du corps humain. Sur la base de nos nouvelles bases mathématiques, nous avons construit différents prototypes pour obtenir une puce électronique d'acquisition de signaux neuronaux qui non seulement présentent des compromis rigoureux entre sa surface, sa consommation d'énergie et sa qualité de sa sortie de signal, mais qui surpasse également l'état de l'art.

Dans le cadre du calcul de données volumineuses et hautes performances, comme dans l'application des serveurs haut de gamme, les circuits RF destinés à transmettre des données de puce à puce ou de puce à mémoire sont définis par des exigences de faible consommation, car la chaleur générée par les circuits intégrés est partiellement distribuée par le package des puces. Par conséquent, le budget de puissance global du système est défini par sa capacité de refroidissement. Pour cette raison, des architectures spécifiques aux applications et des techniques innovantes sont utilisées pour une implémentation à faible consommation. Dans

#### Résumé

ce travail, nous avons développé un récepteur multi-voies à extrémité unique pour la liaison entrée/sortie à haute vitesse dans l'application des serveurs. Le récepteur fonctionne à 7 Gbps en apprenant l'interférence entre symboles et le bruit de couplage électromagnétique dans les systèmes de communication puce à puce. Une approche basée sur l'apprentissage permet au circuit récepteur polyvalent de, non seulement gérer l'atténuation des grands canaux, mais également mettre en œuvre de nouvelles techniques d'annulation de diaphonie pour permettre une transmission à plusieurs lignes sans sacrifier sa bande passante globale pour une zone donnée dans le chemin de données de l'interconnexion.

#### Mots clés :

Circuit intégré implantable, taille efficace, faible puissance, acquisition comprimée, signaux neuronaux, traitement de signal numérique basé sur l'apprentissage, reconstruction de signal, surveillance médicale, compression adaptative. Far-end crosstalk, égaliseur de décision-rétroaction, interférence inter-symbole, architecture source-synchrone, Continuous Time Linear Equalizer.

# Sommario

Questo progetto di ricerca multidisciplinare mira a studiare l'estrazione ottimizzata delle informazioni da segnali o volumi di dati e a sviluppare implementazioni hardware su misura, che compromettono la complessità dell'acquisizione dei dati con quella dell'elaborazione dei dati, consentendo concettualmente di progettare dispositivi radicalmente nuovi. I risultati matematici nel settore di Compressive Sampling (CS) supportano il nuovo paradigma della conversione da *Analogico a Information* (AIC) in sostituzione delle tecnologie ADC convenzionali. Le AIC eseguono simultaneamente l'acquisizione e la compressione dei dati, cercando di campionare direttamente i segnali per ottenere compiti specifici anziché acquisire un segnale completo alla frequenza di Nyquist, per poi buttarne via la maggior parte tramite la compressione. La nostra tesi è che, affinché l'approccio CS mantenga il suo nome, sia la teoria che la pratica devono sfruttare i concetti dell'apprendimento. In questo lavoro sono stati sviluppati diversi prototipi di hardware, con trade-offs chiave, implementati su due diversi campi di applicazione come edge e big-data computing.

Nell'ambito del edge-data computing, come sono le applicazioni wearable o impiantabili, il budget energetico è definito dalla capacità della batteria, che generalmente limita le prestazioni e l'usabilità del dispositivo. Ciò è più evidente in un settore molto impegnativo, come il monitoraggio medico, in cui sono necessari requisiti ad alte prestazioni del dispositivo per elaborare le informazioni con elevata precisione. Inoltre, in applicazioni come il monitoraggio medico in dispositivi impiantabili, le prestazioni del sistema devono essere raggiunte in un'area minima così come a bassa potenza, al fine di facilitare la biocompatibilità dell'impianto, evitando il rifiuto da parte del corpo. Sulla base delle nostre nuove basi matematiche, abbiamo costruito diversi prototipi per il chip di acquisizione del segnale neuronale, che non si limita a compattare e minimizzare la sua area, il consumo di energia e ottimizzare la qualità del segnale ricostruito, ma supera anche in modo significativo lo stato dell'arte in tutti aspetti.

Nell'ambito dei big-data e del calcolo ad alte prestazioni, come nelle applicazioni di server di fascia alta, i circuiti RF dedocato a trasmettere dati da chip a chip o da chip a memoria sono definiti da requisiti di bassa potenza, dal momento che il calore generato dai circuiti integrati è solo parzialmente dissipato dal package del chip. Quindi, il budget complessivo di energia del sistema è definito dalla sua capacità di raffreddamento. Per questo motivo, per l'implementazione a bassa potenza vengono utilizzate architetture specifiche dell'applicazione e tecniche innovative. In questo lavoro, abbiamo sviluppato un ricevitore a più linee, single-ended, per

#### Sommario

il collegamento I/O ad alta velocità per applicazioni server. Il ricevitore funziona a 7 Gbps riducendo l'interferenza inter-symbol e il rumore di accoppiamento elettromagnetico nei sistemi di comunicazione chip-to-chip. Un approccio basato sull'apprendimento consente un circuito ricevitore versatile che non solo abbatte l'importante attenuazione dovuta alla trasmissione nei canali, ma implementa anche nuove tecniche di riduzione del crosstalk, per consentire la trasmissione di linee multiple single-ended, senza sacrificare la larghezza di banda complessiva.

#### Parole chiave:

Circuiti integrati impiantabili, bassa potenza, area minima, compressive sensing, segnali neuronali, learning-based digital signal processing, ricostruzione dei segnali, monitoraggio medico, compressione adattiva. Far-end crosstalk, Decision-Feedback Equalizer, Inter-Symbol Interference, source-synchronous architecture, Continuous Time Linear Equalizer.

# Contents

| Ac                                     | Acknowledgements i |                                                                          |     |  |  |

|----------------------------------------|--------------------|--------------------------------------------------------------------------|-----|--|--|

| Abstract (English/Français/Italiano) v |                    |                                                                          |     |  |  |

| Li                                     | List of Figures xv |                                                                          |     |  |  |

| Li                                     | st of '            | Tables                                                                   | xxi |  |  |

| 1                                      | Intr               | oduction                                                                 | 1   |  |  |

|                                        | 1.1                | Mobile computing and autonomous sensing systems                          | 3   |  |  |

|                                        | 1.2                | High performance computing                                               | 5   |  |  |

|                                        | 1.3                | Thesis Goal                                                              | 6   |  |  |

|                                        | 1.4                | Organization and Thesis Overview                                         | 6   |  |  |

|                                        |                    | 1.4.1 Part One: Wireless Implantable Device for Medical Monitoring Brain | 6   |  |  |

|                                        |                    | 1.4.2 Part Two: Multi-lane Single-Ended High Speed I/O Receiver          | 8   |  |  |

|                                        |                    | 1.4.3 Last Part: Conclusion and Appendix                                 | 8   |  |  |

|                                        |                    |                                                                          |     |  |  |

| I                                      | Wir                | eless Implantable Device for Medical Monitoring Brain                    | 9   |  |  |

| 2                                      | Imp                | lantable ecosystem                                                       | 11  |  |  |

|                                        | 2.1                | Bio-compatible requirements of the implant                               | 12  |  |  |

|                                        | 2.2                | Neuronal bioelectricity and biocompatible electrodes                     | 13  |  |  |

|                                        |                    | 2.2.1 Macro and Micro-electrodes iEEG recording                          | 15  |  |  |

|                                        | 2.3                | Implantable System on Chip                                               | 15  |  |  |

|                                        |                    | 2.3.1 Wireless recording System-on-Chip                                  | 18  |  |  |

|                                        |                    | 2.3.2 Data telemetry                                                     | 18  |  |  |

|                                        |                    | 2.3.3 Power management                                                   | 18  |  |  |

| 3                                      | Dat                | a compression for autonomous sensing systems                             | 21  |  |  |

|                                        | 3.1                | Compressive Sensing                                                      | 21  |  |  |

|                                        |                    | 3.1.1 Signal Sparisity                                                   | 22  |  |  |

|                                        |                    | 3.1.2 Compressive Signal Measurements                                    | 24  |  |  |

|                                        |                    | 3.1.3 Signal Recovery                                                    | 25  |  |  |

|                                        | 3.2                | Structured Sparsity, Sampling and Recovery                               | 29  |  |  |

## Contents

|    |      | 3.2.1 Structured Sparsity                          | 30 |

|----|------|----------------------------------------------------|----|

|    |      | 3.2.2 Structured Sampling                          | 31 |

|    |      | 3.2.3 Structured Recovery                          | 31 |

|    | 3.3  | Learning Based Compressive Sampling                | 39 |

|    |      | 3.3.1 Optimal encoding                             | 40 |

|    |      | 3.3.2 LBCS performance evaluation                  | 40 |

|    | 3.4  | Summary                                            | 45 |

| 4  | LBC  | CS based hardware implementation and validation    | 47 |

|    | 4.1  | System level overview                              | 47 |

|    |      | 4.1.1 Analog to compressed data stream             | 47 |

|    |      | 4.1.2 Wireless Communication                       | 50 |

|    |      | 4.1.3 Implanted System Powering                    | 51 |

|    | 4.2  | Learning based sampling implementations            | 53 |

|    |      | 4.2.1 LBCS-Had Implementation                      | 54 |

|    |      | 4.2.2 LBCS-DCT implementation                      | 57 |

|    |      | 4.2.3 Optimal vs LBCS encoders                     | 61 |

|    | 4.3  | Single channel Adaptive LBCS-Had implementation    | 62 |

|    |      | 4.3.1 Adaptive LBCS                                | 62 |

|    |      | 4.3.2 Implantable Architecture                     | 64 |

|    |      | 4.3.3 Measurement results                          | 72 |

|    | 4.4  | Multichannel Adaptive LBCS-Had implementation      | 76 |

|    |      | 4.4.1 Multichannel Implantable Architecture        | 76 |

|    |      | 4.4.2 Multichannel Layout                          | 78 |

|    | 4.5  | Summary                                            | 78 |

| II | M1   | ılti-lane Single-Ended High Speed I/O Receiver     | 81 |

| 11 | IVIL | nu-tane single-Ended fingh speed 1/0 Receiver      | 01 |

| 5  | Hig  | h speed IOs ecosystem                              | 83 |

|    | 5.1  | System overview                                    | 84 |

|    |      | 5.1.1 Channel boards environment                   | 85 |

|    | 5.2  | Crosstalk cancellation state-of-art                | 88 |

| 6  | Syst | em level analysis for high speed RX                | 89 |

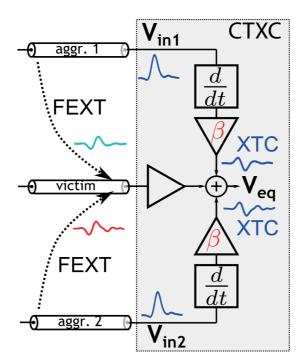

|    | 6.1  | Crosstalk cancellation considerations              | 89 |

|    | 6.2  | Boards characteristics                             | 91 |

|    |      | 6.2.1 Ch1 board                                    | 91 |

|    |      | 6.2.2 Ch2 board                                    | 91 |

|    | 6.3  | Mathematical formulation for ideally coupled lanes | 93 |

|    | 6.4  | System level simulations                           | 93 |

|    |      | 6.4.1 Ch1 board crosstalk reduction                | 94 |

|    |      | 6.4.2 Ch2 board crosstalk reduction                | 94 |

|    | 6.5  | Crosstalk cancellation over skewed lanes           | 98 |

| 7  | Hig                                                                                      | h speed re                                               | eceiver hardware implementation and validation | 103                                              |

|----|------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------|--------------------------------------------------|

|    | 7.1                                                                                      | Receiver                                                 | Architecture and Circuits                      | . 103                                            |

|    |                                                                                          | 7.1.1 Cl                                                 | lock generation                                | . 104                                            |

|    |                                                                                          | 7.1.2 C                                                  | TXC and CTLE                                   | . 104                                            |

|    |                                                                                          | 7.1.3 D                                                  | FE and DFXC                                    | . 106                                            |

|    | 7.2                                                                                      | Measure                                                  | ment Results                                   | . 107                                            |

|    |                                                                                          | 7.2.1 Cl                                                 | h1 measurement results                         | . 108                                            |

|    |                                                                                          | 7.2.2 Cl                                                 | h2 measurement results                         | . 110                                            |

|    | 7.3                                                                                      | Summar                                                   | y                                              | . 113                                            |

| II |                                                                                          | onclusio                                                 | ns                                             | 115                                              |

|    |                                                                                          |                                                          |                                                |                                                  |

| 8  | Con                                                                                      | clusion a                                                | nd future work                                 | 117                                              |

| 8  | <b>Con</b><br>8.1                                                                        |                                                          | <b>nd future work</b><br>Vork                  |                                                  |

| 0  | 8.1                                                                                      | Future W                                                 |                                                |                                                  |

| 0  | 8.1                                                                                      | Future W<br>endix: Da                                    | Vork                                           | . 118<br>119                                     |

| 0  | 8.1<br><b>App</b><br>A.1                                                                 | Future W<br>endix: Da<br>I001-P0                         | Vork                                           | . 118<br>119<br>. 119                            |

| 0  | 8.1<br><b>App</b><br>A.1                                                                 | Future W<br>endix: Da<br>1001-P0<br>Study 0              | Vork                                           | . 118<br>119<br>. 119<br>. 119                   |

| 0  | <ul><li>8.1</li><li>App</li><li>A.1</li><li>A.2</li><li>A.3</li></ul>                    | Future W<br>eendix: Da<br>I001-P0<br>Study 0<br>Experime | work                                           | . 118<br>119<br>. 119<br>. 119<br>. 119<br>. 119 |

| A  | <ul> <li>8.1</li> <li>App</li> <li>A.1</li> <li>A.2</li> <li>A.3</li> <li>A.4</li> </ul> | Future W<br>eendix: Da<br>I001-P0<br>Study 0<br>Experime | work                                           | . 118<br>119<br>. 119<br>. 119<br>. 119<br>. 119 |

| 1.1 | The first 7 nm node test chip wafer from IBM Research [3].                                                                                                                                                                                                                      | 2  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Big-data and instant data in the cloud era [4]                                                                                                                                                                                                                                  | 2  |

| 1.3 | Wireless implantable devices currently available in the medical market [5]                                                                                                                                                                                                      | 4  |

| 1.4 | The Watson supercomputer, based on IBM Power7 servers                                                                                                                                                                                                                           | 5  |

| 1.5 | Designed and tested prototypes in this thesis: (a) Learning-based CS hardware design in 180nm CMOS technology; (b) Multichannel LBCS-based neuronal sensing system; (c) high-speed, 8-lanes single-ended RX in 32nm SOI technology.                                             | 7  |

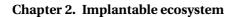

| 2.1 | European brain disorders costs in 2010, reprinted from [10]                                                                                                                                                                                                                     | 12 |

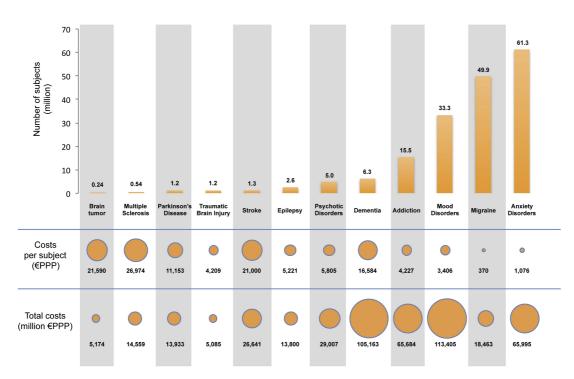

| 2.2 | Biocompatible electrodes, reprinted from [25].                                                                                                                                                                                                                                  | 14 |

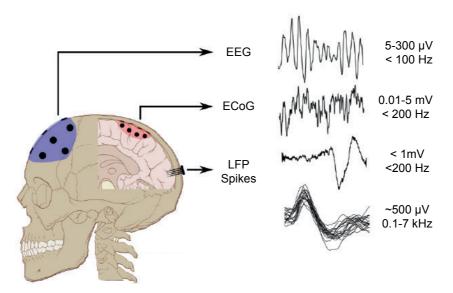

| 2.3 | Hybrid electrodes grid containing macro and microelectrode arrays (a) for iEEG signal recordings, reprinted from [21]. Signals recorded from micro and macro electrodes in (b), with an highlight on micro electrode 27 that records a seizure onset seconds before the macros. | 16 |

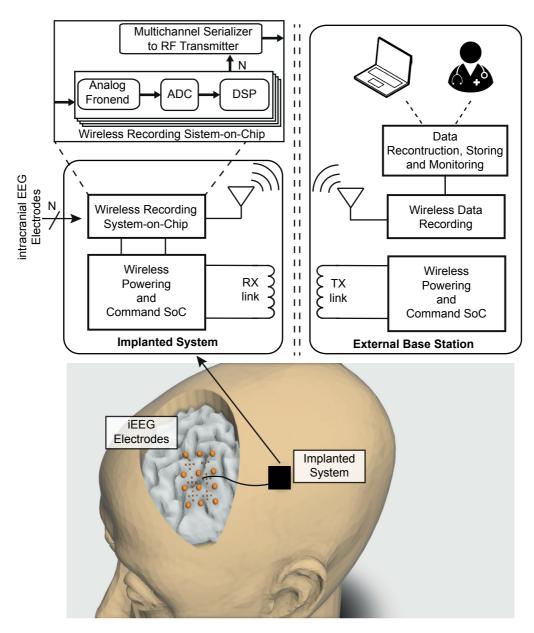

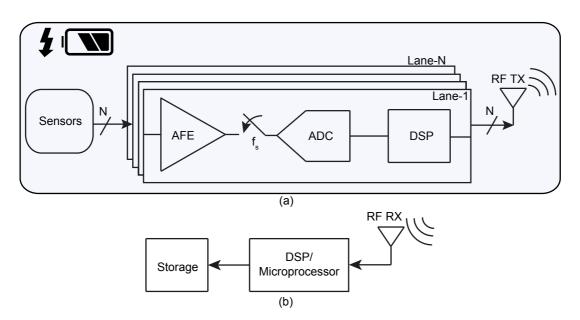

| 2.4 | Block diagram of the implantable integrated system (on the left side), wirelessly linked with an external base station (on the right), where the data is reconstructed for medical monitoring and stored. No battery is used in the implanted system.                           | 17 |

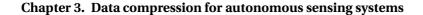

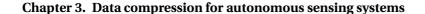

| 3.1 | Electrocardiography gives a time-sparse representation of the heart electrical activity.                                                                                                                                                                                        | 22 |

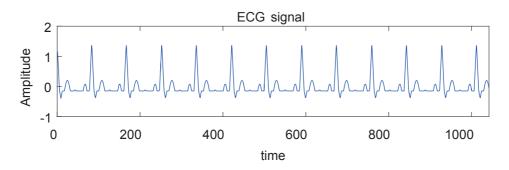

| 3.2 | A multi-tone sine in the non-sparse time domain (left) and its sparser represen-<br>tation in Fourier domain (right).                                                                                                                                                           | 23 |

| 3.3 | Electrocardiography signal on top with the threshold level; its sparser represen-<br>tation at the bottom.                                                                                                                                                                      | 24 |

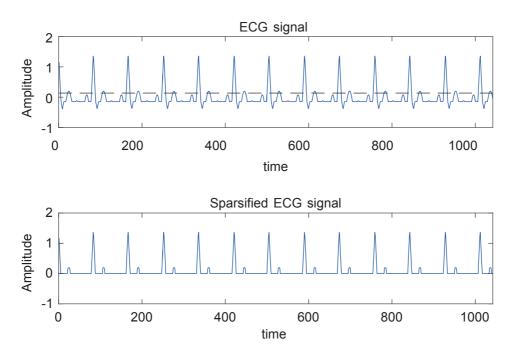

| 3.4 | Dimensionality reduction applying Compressive Sensing technique.                                                                                                                                                                                                                | 25 |

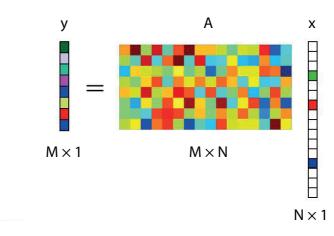

| 3.5 | Shape of the $\ell_p^2$ minimization for $p = 1$ and $p = 2$ , while the thick straight line represents all the solutions to $\mathbf{y} = \mathbf{A}\mathbf{x}$ .                                                                                                              | 27 |

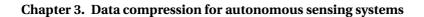

| 3.6 | Empirical performance of simple and structured sparsity recovery of natural images, reprinted from [61].                                                                                                                                                                        | 30 |

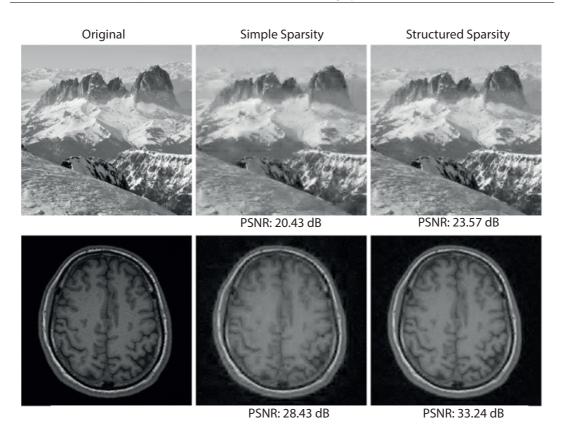

| 3.7   | (left) Coherence between the Hadamard and the Wavelet bases. The coherence decreases for higher frequencies (higher coefficients). (right) Probability func-                                                                                      |          |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|       | tions used for sampling the indices of the Fast Walsh-Hadamard Transform for 4x and 32x compression factors.                                                                                                                                      | 22       |

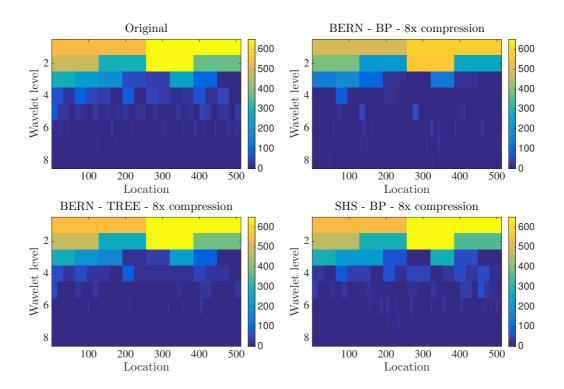

| 3.8   | Tree structure in one signal from iEEG.org dataset I001 P034 D01 (channel 6,                                                                                                                                                                      | 32       |

| 5.0   | first annotated seizure, first 1024 samples window) and in three reconstructions obtained via Bernoulli sampling (BERN) and structured Hadamard sampling                                                                                          |          |

|       | (SHS). The tree structure can be enforced via a specific tree regularizer or mostly                                                                                                                                                               |          |

|       | captured via structured sampling.                                                                                                                                                                                                                 | 33       |

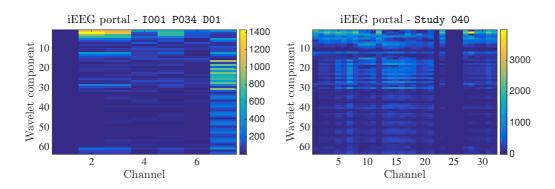

| 3.9   | First 64 Wavelet coefficients of the micro-electrode signals from two datasets<br>from the iEEG.org portal. (left) 7 channels from dataset I001 P034 D01. (right)<br>32 channels from dataset Study 040. The group structure is evident among the |          |

|       | correlated channels in both datasets, however, there remain outlier channels                                                                                                                                                                      |          |

|       | which do not abide to the group structure.                                                                                                                                                                                                        | 34       |

|       | Dataset 1                                                                                                                                                                                                                                         | 36       |

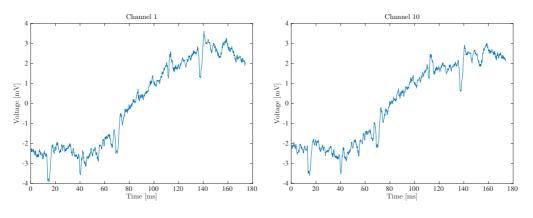

| 3.11  | Example of micro-electrode signals from iEEG.org dataset I001 P034 D01                                                                                                                                                                            |          |

|       | (first seizure, first 1024 samples window). Channel 1 is inactive, since it simply                                                                                                                                                                |          |

|       | jumps between $-1\mu V$ and $1\mu V$ . Channel 2 to 6 record normal activity, which is                                                                                                                                                            |          |

|       | not much correlated. Channel 7 exhibits strong AC components, possibly picked                                                                                                                                                                     | ~ -      |

| 0.10  | up from the power sources.                                                                                                                                                                                                                        | 37       |

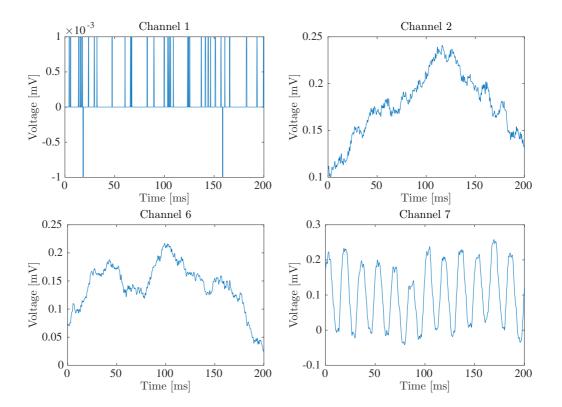

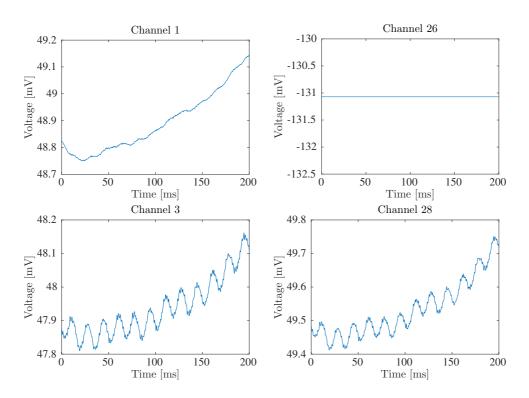

| 3.12  | Example of micro-electrode signals from iEEG.org dataset Study 040 (first                                                                                                                                                                         |          |

|       | seizure, first 1024 samples window). Channel 26 seems completely inactive, it                                                                                                                                                                     |          |

|       | sends a constant signal of approximately $-131 mV$ . Channels 3 and 28, among others are highly correlated. Channel 1 is an example of a channel which does                                                                                       |          |

|       | others, are highly correlated. Channel 1 is an example of a channel which does not exhibit the smaller oscillations of channels 3 and 28                                                                                                          | 38       |

| 2 1 2 |                                                                                                                                                                                                                                                   | 30       |

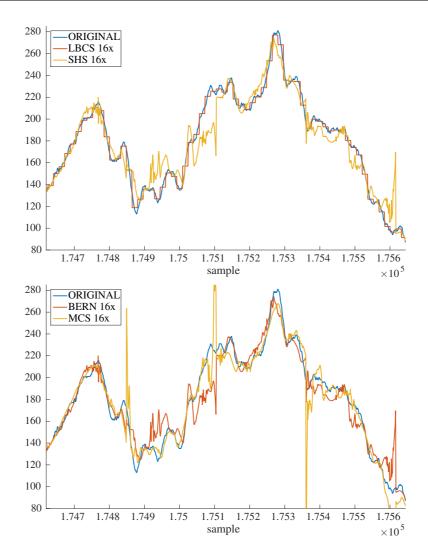

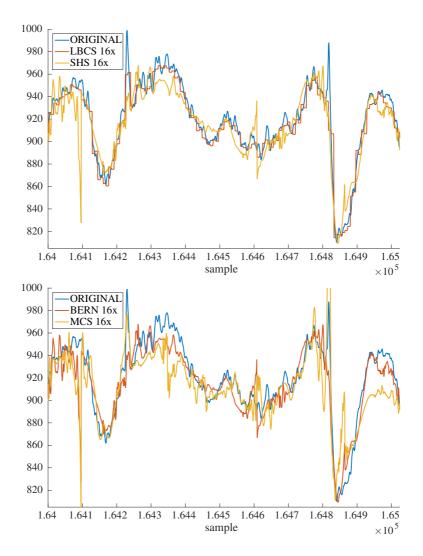

| 5.15  | I001-P034-D01 Reconstruction example for channel Grid28 on four windowsof length 256 each.                                                                                                                                                        | 41       |

| 2 1 4 | Study 040 Reconstruction example for channel LG50 on four windows of length                                                                                                                                                                       | 41       |

| 5.14  | 256 each.                                                                                                                                                                                                                                         | 43       |

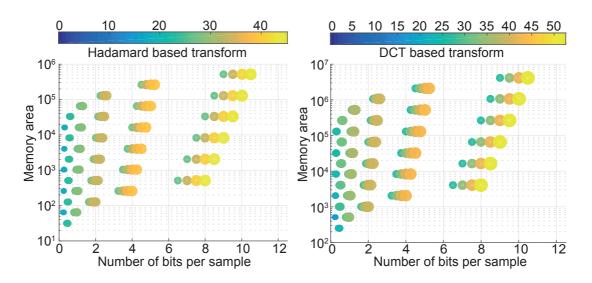

| 3 15  | Trade-off between bit-rate, memory size and reconstruction performance                                                                                                                                                                            | 45<br>45 |

| 5.15  | nade-on between bit-rate, memory size and reconstruction performance                                                                                                                                                                              | 43       |

| 4.1   | Typical wireless sensor system, with highlight in a battery-powered multiple                                                                                                                                                                      |          |

|       | lanes TX (a) and its RX counterpart (b).                                                                                                                                                                                                          | 48       |

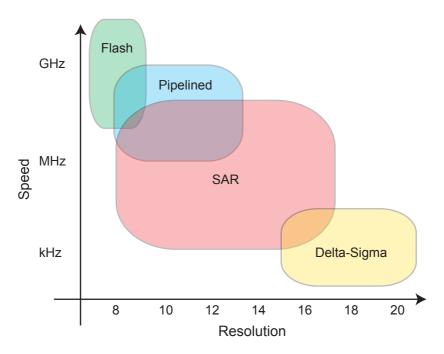

| 4.2   | Different ADC operating range, considering the sampling rate and the bit resolu-                                                                                                                                                                  |          |

|       | tion, adapted from [71].                                                                                                                                                                                                                          | 49       |

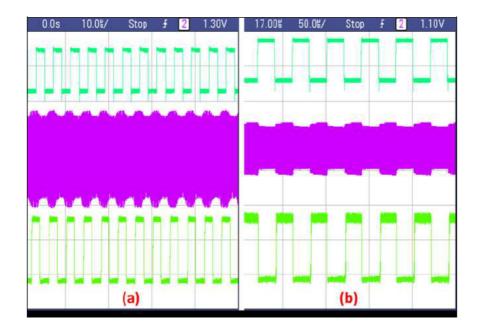

| 4.3   | Downlink data communication at (a) 500 kbit/s and (b) 50 kbit/s (waveforms from top to bottom;                                                                                                                                                    |          |

|       | turquoise: modulator input (5V/div), purple: demodulator input ((a)2V/div (b)5V/div), and green:                                                                                                                                                  |          |

|       | demodulator output (1V/div), respectively) [85]                                                                                                                                                                                                   | 52       |

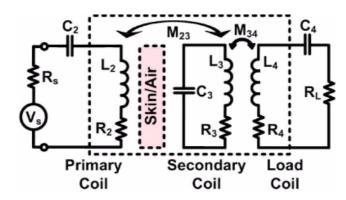

| 4.4   | Lumped circuit model of the 3-coil inductive link [88]                                                                                                                                                                                            | 53       |

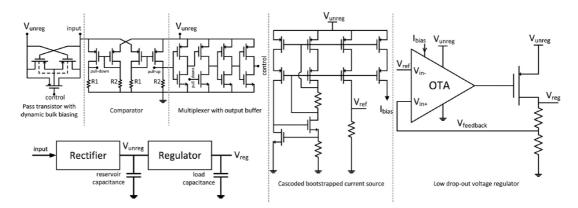

| 4.5   | (Left top) Half-wave active rectifier composed of a pass transistor, comparator, and a multiplexer;                                                                                                                                               |          |

|       | (right) the low drop-out voltage regulator with its cascoded bootstrapped current source; and (left                                                                                                                                               |          |

|       | bottom) connection of rectifier and the regulator. [89]                                                                                                                                                                                           | 53       |

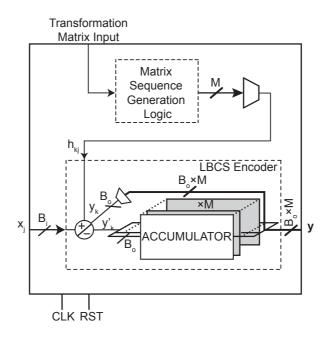

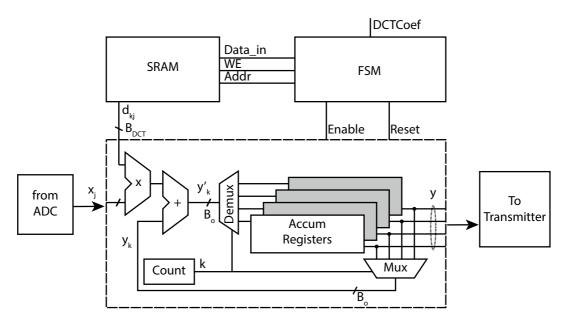

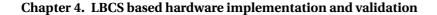

| 4.6  | One channel block diagram showing the LBCS encoder and the matrix sequence                                                          |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | generation logic.                                                                                                                   | 55  |

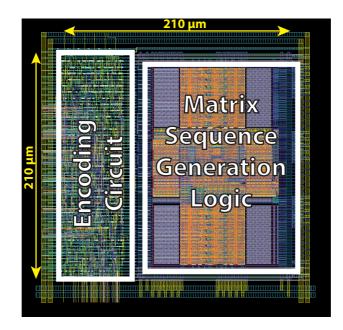

| 4.7  | Accumulator block diagram.                                                                                                          | 55  |

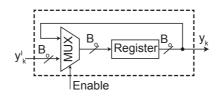

| 4.8  | One channel encoder layout showing the LBCS encoding circuit and the matrix sequence generation logic for $N = 256$ and $CR = 16$ . | 57  |

| 4.9  | One channel block diagram showing the LBCS encoder and the matrix sequence                                                          |     |

|      | generation logic.                                                                                                                   | 59  |

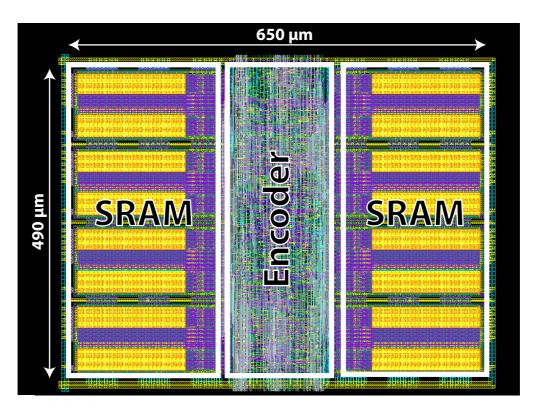

| 4.10 | One-channel DCT-LBCS encoder layout for $N = 256$ and $CR = 32$                                                                     | 60  |

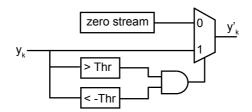

| 4.11 | Variable CR block diagram, defined by the threshold level (Thr).                                                                    | 64  |

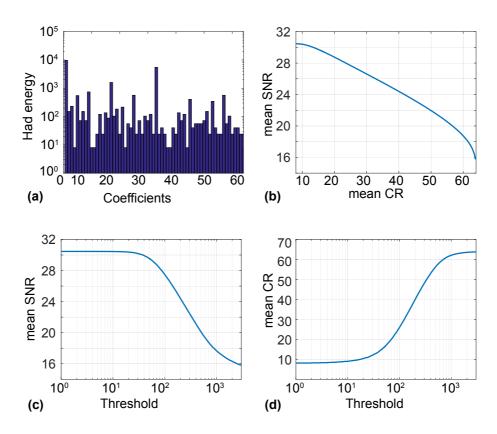

| 4.12 | SNR analysis for adaptive approach                                                                                                  | 65  |

| 4.13 | One channel block diagram showing the LBCS encoder and the matrix sequence                                                          |     |

|      | generation logic.                                                                                                                   | 66  |

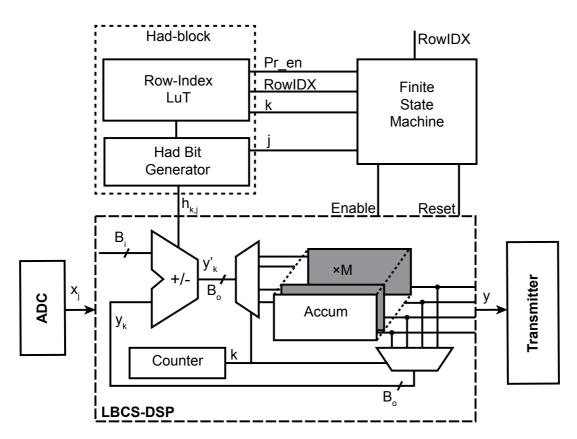

| 4.14 | Hadamard bit generator block diagram.                                                                                               | 67  |

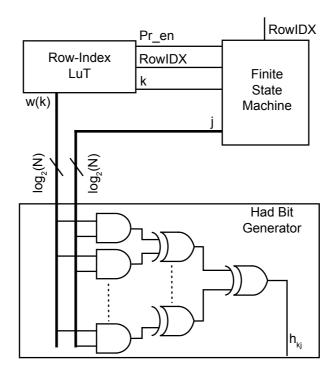

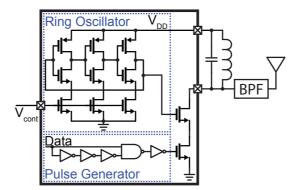

| 4.15 | Schematic of the LC cross-coupled voltage controlled oscillator [93]                                                                | 68  |

| 4.16 | Schematic of the IR-UWB transmitter [93]                                                                                            | 69  |

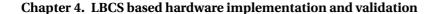

| 4.17 | Block diagram of the proposed implanted electronics for wireless power trans-                                                       |     |

|      | mission [93]                                                                                                                        | 70  |

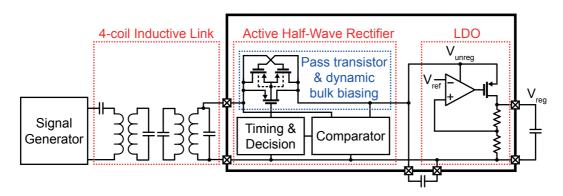

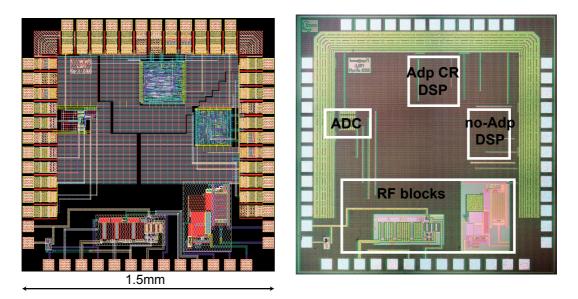

| 4.18 | Layout (on the left) and micrograph (on the right) of the tested chip                                                               | 71  |

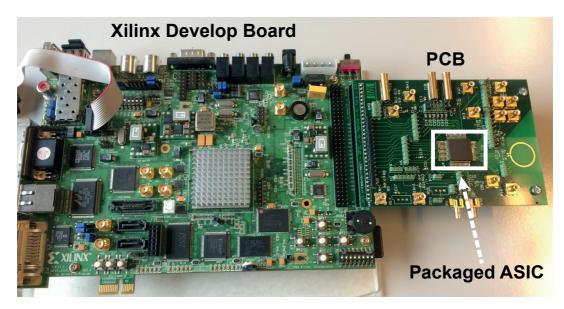

| 4.19 | Measurement setup, highlighting the FPGA and PCB link.                                                                              | 71  |

| 4.20 | Measured compressed values with low threshold (on the left) and high threshold                                                      |     |

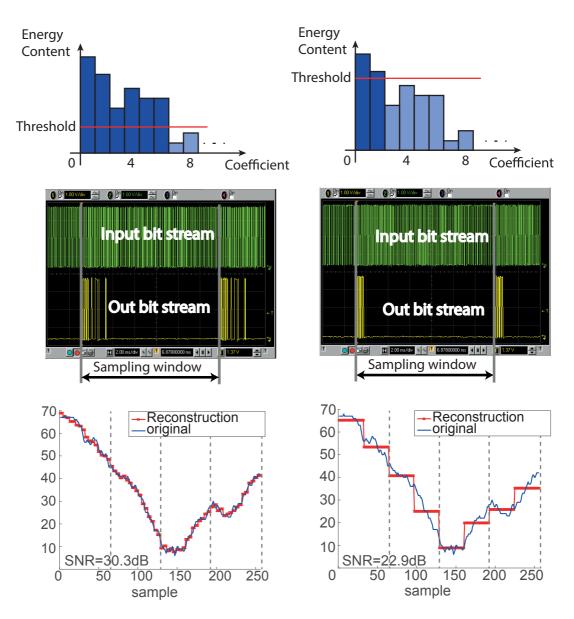

|      | (on the right).                                                                                                                     | 73  |

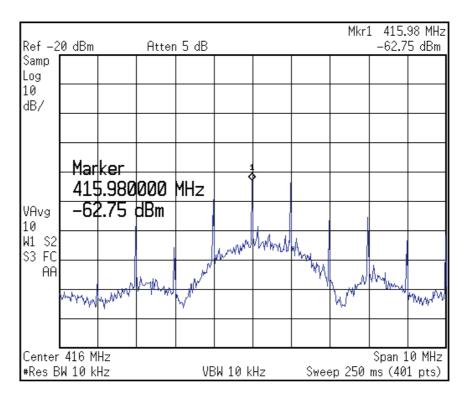

| 4.21 | Spectrum of the LC cross-coupled voltage controlled oscillator [93]                                                                 | 75  |

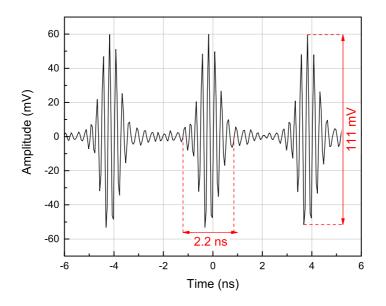

| 4.22 | Transient pulses of the IR-UWB transmitter at 250 Mpps [93]                                                                         | 76  |

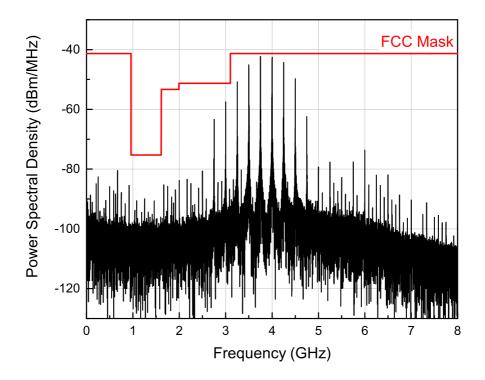

| 4.23 | Power spectral density of the IR-UWB transmitter [93]                                                                               | 77  |

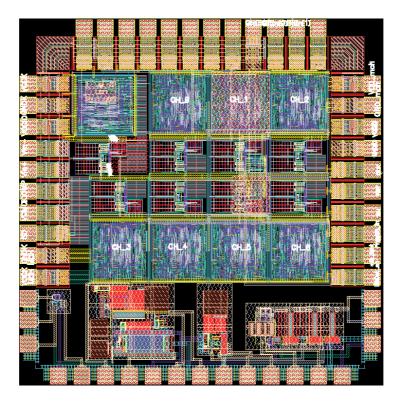

| 4.24 | Layout of the designed multichannel implementation.                                                                                 | 79  |

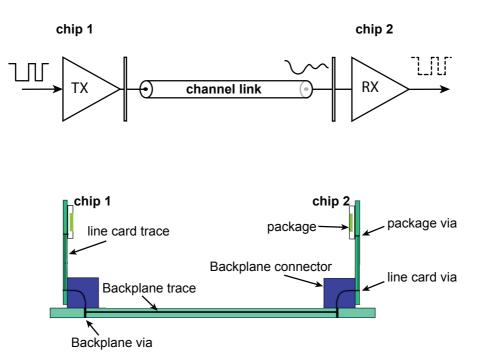

| 5.1  | Chip-to-chip backplane link, SE 4.8 Gb/s [100].                                                                                     | 84  |

| 5.2  | Pin data rate evolution across most common I/O standards [101]                                                                      | 85  |

| 5.3  | Chip-to-chip block diagram (top), depicting the transmitted signal before and                                                       |     |

|      | after the attenuation due to the channel link. Section of a typical backplane                                                       | 0.0 |

| - 4  | system, highlighting the signalling paths [100] (bottom)                                                                            | 86  |

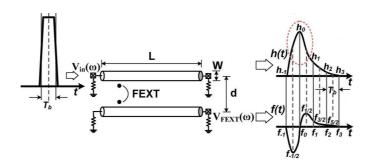

| 5.4  | ISI and crosstalk highlight in a multilane high speed I/O link [105]                                                                | 86  |

| 5.5  | Highlight of the pulse response and its derived crosstalk pulse response in a 2                                                     | 07  |

|      | lanes single ended I/O link, reprinted from [105]                                                                                   | 87  |

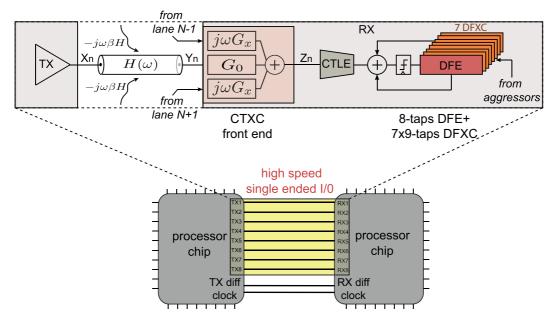

| 6.1  | Crosstalk cancellation using CTXC front-end on 3 lanes channel                                                                      | 90  |

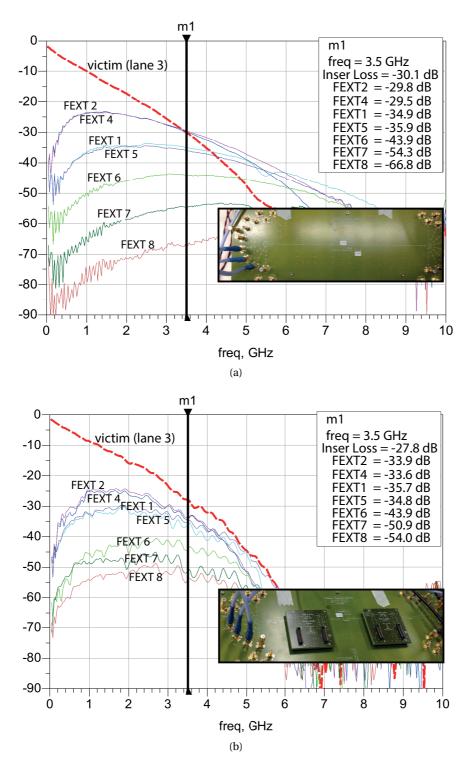

| 6.2  | Forward and FEXT frequency responses (magnitude) for the Ch1 (a) and Ch2 (b)                                                        |     |

|      | PCB board                                                                                                                           | 92  |

| 6.3  | Single-lane transceiver block diagram with crosstalk compensation scheme                                                            |     |

|      | combining CTXC on the front-end.                                                                                                    | 94  |

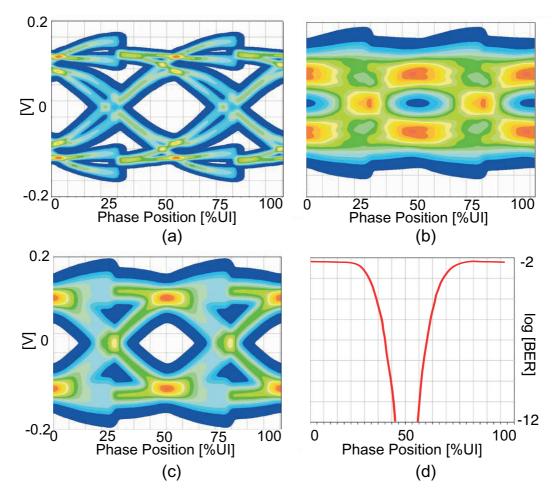

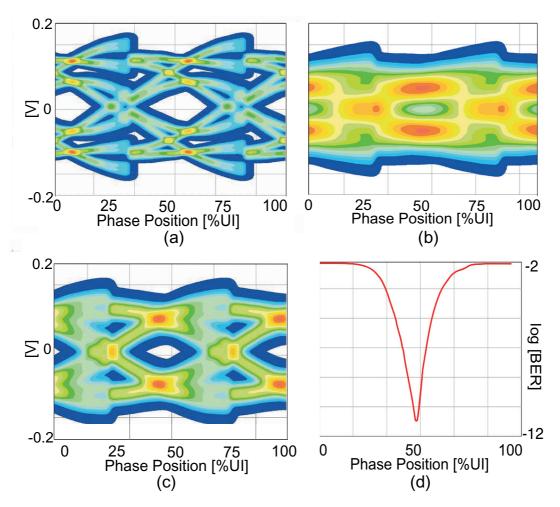

| 6.4  | Simulated RX data eye for Ch1 board, with all aggressors switched (a) off and on (b) without crosstalk compensation scheme (CTLE and DFE on, in both cases). (c) Data eye and (d) bathtub plot with optimally calibrated CTXC front-end. All aggressors are transmitting.      | 95  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

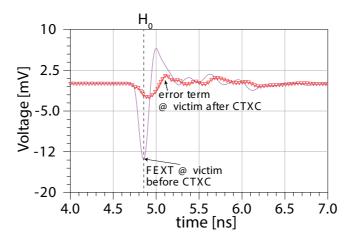

| 6.5  | FEXT pulse response from the aggressor to victim lane before and after CTXC.                                                                                                                                                                                                   | 95  |

| 6.6  | Simulated RX data eye for Ch2 board, with all aggressors switched off (a) and on (b) without crosstalk compensation (CTLE and DFE on, in both cases). (c) Data eye and (d) bathtub plot with optimally calibrated CTXC front-end with the two nearest aggressors transmitting. | 96  |

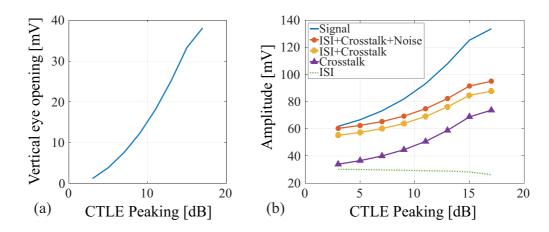

| 6.7  | Highlight of the vertical eye aperture (a) and <i>signal</i> , crosstalk and ISI (b) evolution for different CTLE peaking settings.                                                                                                                                            | 97  |

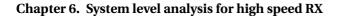

| 6.8  | Probability distribution function of the crosstalk pulse-response spanned over all postcursor taps without crosstalk cancellation (a), with only CTXC on (b), with CTXC off and DFXC on (c) and with both CTXC-DFXC activated (d)                                              | 100 |

| 6.9  | Skewed (a) and un-skewed (b) impulse responses at the TX side                                                                                                                                                                                                                  | 100 |

|      | Qualitative highlight of CTXC effects for un-skewed (a) and skewed (b) board                                                                                                                                                                                                   |     |

|      | lanes.                                                                                                                                                                                                                                                                         | 101 |

| 6.11 | Vertical eye aperture versus different lane skews at the RX side, with different number <i>n</i> of taps activated on the DFXC. The simulations are performed with Ch2 channel board.                                                                                          | 102 |

| 7.1  | 8-lane single-ended receiver architecture.                                                                                                                                                                                                                                     | 103 |

| 7.2  | CTXC stage with single-ended passive differentiator, variable gain amplifier and current summation. The two high pass RC differentiators are highlighted in the                                                                                                                |     |

|      | boxes                                                                                                                                                                                                                                                                          | 104 |

| 7.3  | Simulated AC response of main signal path VGA with maximum gain setting. $% \mathcal{A} = \mathcal{A} = \mathcal{A}$ .                                                                                                                                                         | 105 |

| 7.4  | CTLE stage with negative-C bandwidth enhancement. Reprinted from [121]. $\ .$                                                                                                                                                                                                  | 106 |

| 7.5  | Integrating DFE using SC feedback.                                                                                                                                                                                                                                             | 107 |

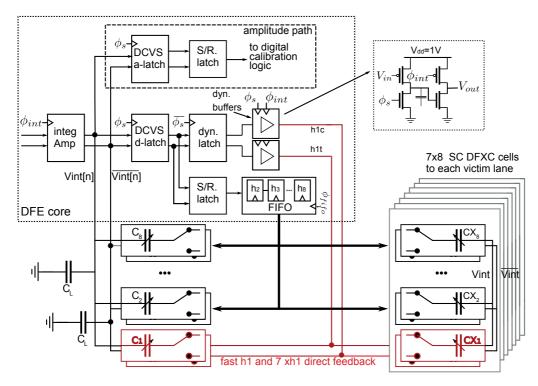

| 7.6  | DFE and DFXC core, with fast tap-1 feedback, including 8-tap DFE and 7×8 DFXC SC cells.                                                                                                                                                                                        | 108 |

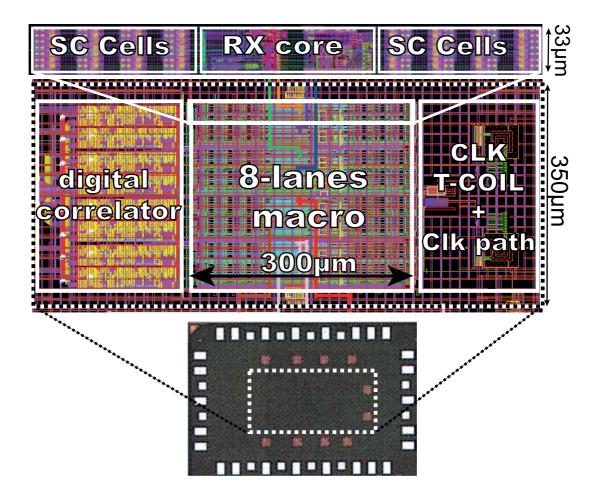

| 7.7  | Layout of RX macro (center), detail of the SC-DFE cells (on top) and the die micrograph (bottom).                                                                                                                                                                              | 109 |

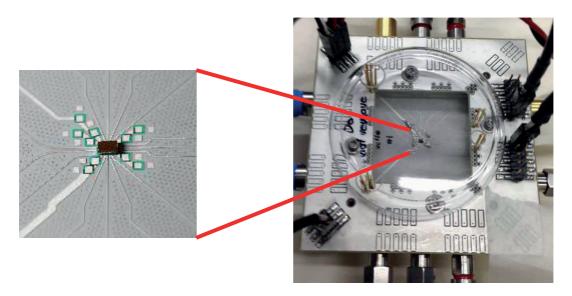

| 7.8  | On the left, the chip is flip-chip mounted on the LCP PCB. On the right, the LCP is packaged in a rigid metallic frame.                                                                                                                                                        | 110 |

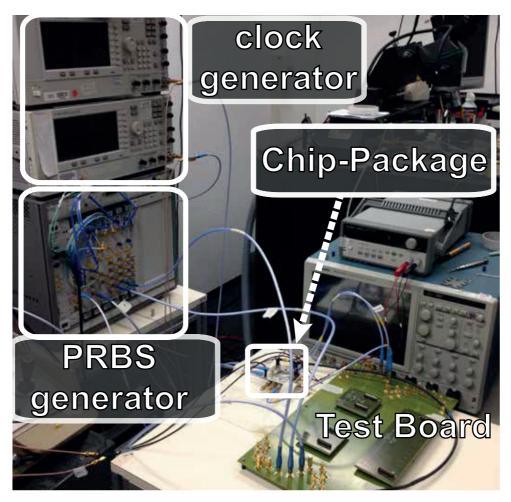

| 7.9  | Measurement setup: clock generators on top left, PARBERT for PRBS generation<br>on bottom left, test board Ch2 on bottom right and the RX in the middle                                                                                                                        | 111 |

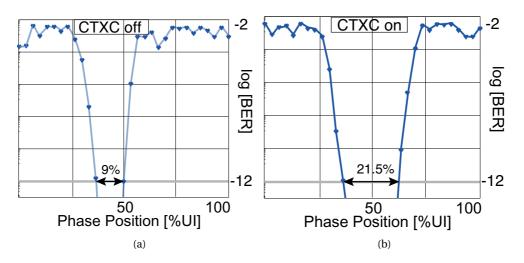

| 7.10 | Measured bathtub plots for Ch1 board with CTXC switched off (a) and switched                                                                                                                                                                                                   |     |

|      |                                                                                                                                                                                                                                                                                | 112 |

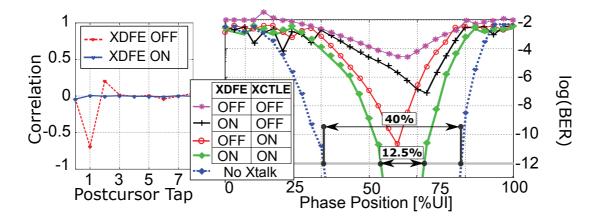

| 7.11 | Board-Ch2: measured correlation with postcursor taps with and without DFXC, on the left; measured bathtub plots, on the right.                                                                                                                                                 | 112 |

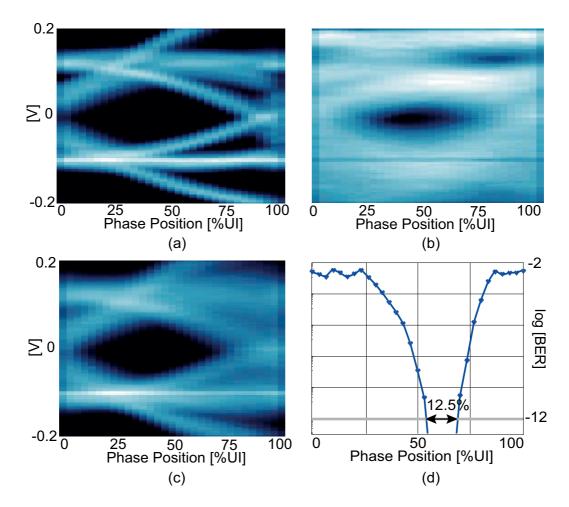

| 7.12 Received eye diagrams with silent aggressors (top-left), crosstalk cancellation off |     |

|------------------------------------------------------------------------------------------|-----|

| (top-right), crosstalk cancellation activated (bottom-left) with related bathtub         |     |

| plot (bottom-right)                                                                      | 113 |

# List of Tables

| 1.1 | Power budget for different applications                                                        | 3   |

|-----|------------------------------------------------------------------------------------------------|-----|

| 2.1 | Neuronal signals characteristics.                                                              | 15  |

| 3.1 | iEEG.org portal dataset I001 P034 D01. Mean SNR over channels 2-6                              | 36  |

| 3.2 | iEEG.org portal dataset I001 P034 D01. Mean SNR over channels 2-6                              | 36  |

| 3.3 | iEEG.org portal dataset Study 040. Mean SNR over all channels                                  | 39  |

| 3.4 | I001-P034-D01 N = 256, $B_i$ = 10 $\hdots$                                                     | 42  |

| 3.5 | Study 040 N = 256, $B_i = 10$                                                                  | 42  |

| 3.6 | Reconstruction performance (in dB) N = 32 - $B_i = 10$                                         | 42  |

| 3.7 | Performance (dB) N = 256, $B_i$ = 10, $B_{DCT}$ = 8                                            | 44  |

| 4.1 | Comparison With Published Work                                                                 | 58  |

| 4.2 | Comparison With Published Work                                                                 | 61  |

| 4.3 | Recovery performance comparison with published work (N = 256, B_i = 10) $\ldots$               | 74  |

| 4.4 | Recovery performance summary for this work (N = 64, B <sub>i</sub> = 8) $\ldots \ldots \ldots$ | 74  |

| 4.5 | Compression hardware comparison with published work                                            | 74  |

| 6.1 | Crosstalk boards key parameters                                                                | 91  |

| 6.2 | Crosstalk Cancellation Performances                                                            | 98  |

| 7.1 | RX power distribution                                                                          | 114 |

| 7.2 | Comparison of 8 lanes × 7 Gb/s RX macro with prior art                                         | 114 |

# **1** Introduction

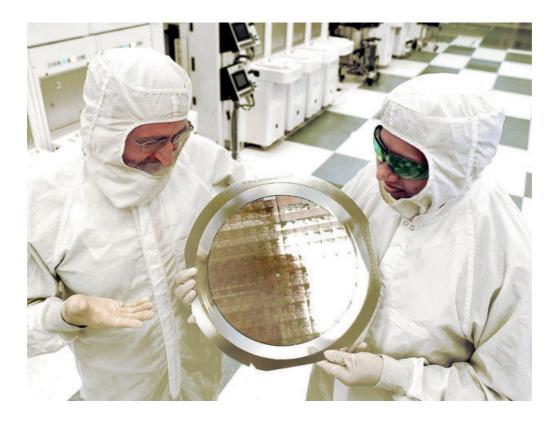

Since the advent of *Integrated Circuits* (ICs) in 1958 [1], the semiconductor manufacturing technology has improved constantly, to follow the need for integrating more complex functions into a single chip. In the last few decades, there has been a revolution in the information technology, in which *Very Large Scale Integration* (VLSI) technology has been the key to develop systems capable to address different challenges for many applications, spanning from telecommunications to imaging, high-speed transceivers, home automation, environmental and medical monitoring etc. The continuous technology scaling, known as Moore's law [2], where the transistor physical size has been halved every two years, has been the feedstock for the continuous innovation in the system performances. Indeed, this trend predicted by Moore resulted into more complex system-on-chip architectures, with naturally increase of the system's bandwidth. Recently, IBM Research in collaboration with GlobalFoundries and Samsung, has successfully made the first 7 nm node test chips at wafer scale, shown in Fig. 1.1. Such new manufacturing technique has the potential to host 20 billion working transistors packed into a chip of a fingernail's size.

Although the miniaturization law has been followed rigidly for half a century, the prediction of the 2015 *International Technology Roadmap for Semiconductors* (ITRS) [4], reports that the transistor could stop shrinking in the next few years. The report forecasts that, after 2021, it will be no longer economically viable for companies to continue the traditional effort in transistor miniaturization, sacrificing the chip speed gains for energy savings. However, the manufacturing technology will move towards other ways to increase chip density, turning the chip design to the vertical geometry, allowing multiple layers of circuitry, one on top of the other, namely allowing 3D microprocessor structures.

Moreover, system scaling is challenged with the limits on area, power and interconnect bandwidth. Since the advent of cloud computing, there are mainly two kinds of data generation: the *big-data*, requiring heavy computation and memory resources, and *instant data*, which are produced by always-on low power devices, as depicted in Fig. 1.2. In such framework, the industry is currently facing a new trend, named *More Moore* (MM), in which added value to devices is enabled by integrating optimized solutions that do not scale following the Moore's

Figure 1.1 – The first 7 nm node test chip wafer from IBM Research [3].

Figure 1.2 – Big-data and instant data in the cloud era [4].

| Application              | Sensors                         | Wireless<br>Interfaces                 | Power<br>Consumption | Battery<br>Lifetime |

|--------------------------|---------------------------------|----------------------------------------|----------------------|---------------------|

| Pacemaker                | Pacing leads                    | Inductive link                         | $10 \mu \mathrm{W}$  | Several Years       |

| Human body<br>monitoring | ECG, heart rate,<br>Temperature | 900 MHz ISM                            | 1-8 mW               | Several Hours       |

| Smart Phone              | Multiple sensors                | Bluetooth, WiFi,<br>GSM,<br>HSDPA, LTE | 1 W                  | Few Hours           |

Table 1.1 – Power budget for different applications.

law. MM technologies allow applications that go from mobile computing, *autonomous sensing and monitoring systems* (targeting reduced energy and area costs) to the *high performance computing*, requiring more performance and operating frequency.

In this work, we are concerned with optimized information extraction from signals or data volumes. We therefore develop mathematical theory, computational methods and their hard-ware implementations, for information recovery from highly incomplete data. Our approach trades-off the complexity of data acquisition with that of data processing, conceptually allowing radically new device designs. Our contention is that both theory and practice must leverage concepts from learning processes, in order to validate the merging between mathematical algorithms and circuit design. This work has been demonstrated in two new hardware prototypes with key trade-offs, in the More Moore technologies.

# 1.1 Mobile computing and autonomous sensing systems

In mobile applications the power budget is defined by the battery limits, which, unfortunately, does not improve from one node to the following one, as the amount of logic gates does in the IC. Table 1.1 gives an overview of different battery power budget used in some of the current electronic devices used for general daily life applications.

Among all the autonomous sensing applications, one of the most critical and challenging field is medical monitoring, in which various biological signals have to be processed with a relatively high accuracy, in order to extract reliable medical information for disease diagnosis or therapy. The implantable medical sector is nowadays a highly consolidated market, which is mainly dominated by few companies (e.g., Medtronic, St. Jude Medical and Boston Scientific). According to a research report [6], the implantable medical market forecast expects to grow from an evaluation of US\$ 32.3 Billion in 2015 to US\$ 49.8 Billion by the end of 2024.

In the last few decades, new health-oriented devices and wireless technologies have been

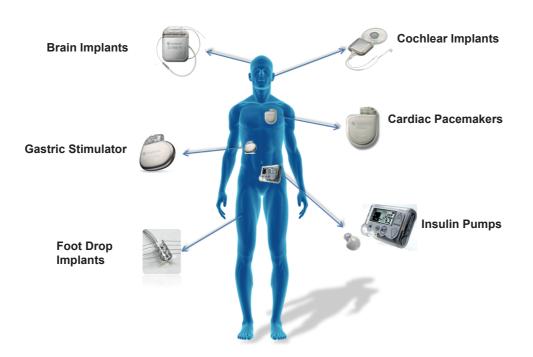

Figure 1.3 - Wireless implantable devices currently available in the medical market [5].

proposed, spanning from low-power implants that harvest energy from the body, to wireless sensors for in-house medical monitoring. In particular, implantable medical devices, including pacemakers, cardiac defibrillators, insulin pumps, and neurostimulators (shown in Fig. 1.3), feature wireless communication, enabling remote personal health monitoring, and facilitate the treatment procedures provided by health care systems.

Usually, the implant, also named *sensor*, is characterised by limited energy resources, due to the limits on the battery. The power consumption by the wireless *Transmitter* (TX) unit, in the sensor node, is usually higher than the required power by all the other blocks in the signal acquisition system of the implanted chip. For this reason, some data treatment on the sensor node is crucial to reduce the amount of data sent by the *Radio Frequency* (RF) TX, while keeping a relatively high information content, enabled after a tailored signal reconstruction, at the receiver node. Data compression becomes then crucial to reduce data telemetry power costs, without losing any critical information of the signal. To address this challenge, a new mathematical approach named *Compressive Sensing* [7] or *Compressed Sensing* [8] (CS) has been exploited in many applications, spanning from remote controlling to imaging systems. In a nutshell, CS allows to sample less the signal of interest than dictated by the Shannon-Nyquist theorem, while the recovered signal performance is still robust. Such mechanism is possible because, in natural signals, the information content is often much lower than the raw signal data content.

Overall, CS reduces the costs on the sensor node, allowing less linear samples than standard systems. However, the receiver has to deal with fewer data and requires to perform non-linear

Figure 1.4 - The Watson supercomputer, based on IBM Power7 servers.

operation to get the reconstructed signal. This means that the receiver will present some data latency and high energy costs. In this thesis, we propose hardware implementations of different CS-based approaches, capable to boost the performance of autonomous sensing systems, both on the area and power. Finally, an adaptive learning-based CS approach, named LBCS, allows a linear sampling and linear recovery, resulting in a real-time high signal reconstruction quality up to  $64 \times$  compression rate, as quantitatively demonstrated on different datasets.

# 1.2 High performance computing

High performance computing is needed to perform massive-scale and complex computing, at server nodes. Such technology targets are energy efficiency, real-time responsiveness and huge demand for processing power. As examples, the IBM Power Systems, shown in Fig. 1.4, are servers designed for critical applications and massive workloads needed for advanced machine learning, deep learning, advanced analytics and high performance computing.

The data processing capability of such big data computational infrastructures are highly dependent on how fast is the system to perform the operations. In such framework, high speed *transceivers* (TRX) play a crucial role connecting short range chip-to-chip or chip-to-memory, to allow high performance big data treatment. High speed TRX capability has continuously grown following the IC technology trend. However, the channel board in which the signal propagates has not improved accordingly, resulting in an intricate path in which the data gets deteriorated. The electrical link through PCB or backplane channels is characterised by the related signal losses, due to natural low pass filter characteristic of the board. In these interconnects, the need of complex equalization grows as the channel loss increases, resulting in a reduction in energy efficiency of the channel link. An increased bandwidth per pin ratio is allowed by single-ended signaling architectures, which doubles the performance with respect to the differential implementation. However, as the operating frequency of the system increases, the electromagnetic coupling between the PCB traces, named *crosstalk* (XTK or xtalk), becomes a significant noise source in single-ended parallel links. The combination of high speed signal processing algorithms with technological challenge in the circuit implementation, due to transistor scaling, becomes crucial, in order to reduce the signal degradation due to the aforementioned noise sources. Moreover, the challenge is enhanced by the stringent power constraints, so to meet the high performance requirements related to the application.

In this work, we propose a low power, multi-lane single-ended RX for high loss sourcesynchronous links. In such system, a learning-based approach allows us to effectively cancel insertion loss and electromagnetic coupling noise in hardware and increase communication speed without sacrificing its overall bandwidth for a given area within the interconnect's datapath. Moreover, the receiver macro can be adapted to different board channels, presenting high insertion losses and intricate crosstalk patterns.

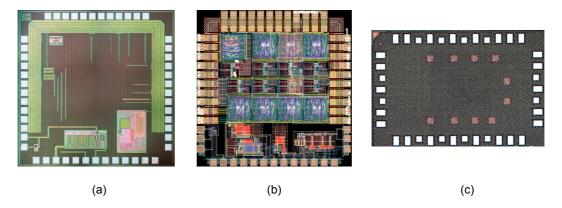

## 1.3 Thesis Goal

The More Moore technologies depict an indispensable and stronger trade-off in the main chip's requirements, that is the device area, power and operating frequency. The goal of this work is to improve the system performance boosting the information we have from the signal and/or environment in which the device is exploited. In this thesis we developed different learning-based approaches specifically tailored to the applications, defining new architectures, efficient circuit implementations and silicon prototypes of integrated signal processing algorithms. Fig. 1.5 depicts the die micrograph of the prototypes that have been designed, fabricated and tested in the frame of this work. In particular, Fig. 1.5 (a) shows the adaptive learning-based chip used for autonomous sensing systems, while Fig. 1.5 (b), depicts the chip micrograph of the 8-lanes receiver for high performance computing applications. Overall, particular emphasis is given to the efficient design and implementation of adaptive architectures, in order to cope with the multiple scenarios in which the proposed systems are used.

### 1.4 Organization and Thesis Overview

### 1.4.1 Part One: Wireless Implantable Device for Medical Monitoring Brain

Chapter 2 - Implantable ecosystem

Figure 1.5 – Designed and tested prototypes in this thesis: (a) Learning-based CS hardware design in 180nm CMOS technology; (b) Multichannel LBCS-based neuronal sensing system; (c) high-speed, 8-lanes single-ended RX in 32nm SOI technology.

In Chapter 2, we give an overview of the implantable ecosystem, discussing the general requirements of the implant. This will be followed by a discussion on neuronal bioelectricity and biocompatible electrodes. Afterwards, this chapter presents the basic information needed about the overall implantable system on chip.

#### Chapter 3 - Data compression for autonomous sensing systems

Chapter 3 describes the data compression algorithms developed during this work. We describe the main concepts of compressive sensing, which is then followed by a discussion on structureaware sparsity, sampling and recovery methods. The final part of the chapter focuses on the Learning-based compressive sampling, describing the main advantages of this method. For all the CS-based methods described in this work, a performance evaluation is given, based on iEEG human datasets (defined in the Appendix).

### Chapter 4 - LBCS based hardware implementation and validation

In Chapter 4, we describe the different hardware prototypes based on the LBCS algorithm. In particular, we show LBCS implementation applying different measurement schemes, analysing the pros and cons of each one. Then, we show the global system on chip for a single channel implementation, where we adopt an adaptive LBCS compression technique. Afterwards, we give the silicon electrical measurements of the single channel implementation. In the last part of the chapter is then discussed a multichannel implementation that, at the time of writing, is under fabrication process.

# 1.4.2 Part Two: Multi-lane Single-Ended High Speed I/O Receiver

### Chapter 5 - High speed I/Os ecosystem

Chapter 5 describes the high speed Input/Output link interconnection. This Chapter gives a general system level overview, discussing the channel board environment and the signal loss caused by attenuation in high frequency wired link. The state-of-art reduction of crosstalk in serial link high speed link is then described in the last part of the chapter.

## Chapter 6 - System level analysis for high speed receiver

In Chapter 6, we describe the system level analysis of the high speed link, motivating our crosstalk cancellation technique on the receiver side only. We give the boards characteristics before describing the crosstalk mathematical formulation for ideally coupled lanes. In the last part of the chapter we discuss the system level simulations, followed by the analysis of crosstalk cancellation over skewed lanes.

## Chapter 7 - High speed receiver hardware implementation and validation

Chapter 7 describes the receiver architecture and gives the circuit design of its main components. The validation of the overall receiver design is given by the measurement results over two single-ended channel boards, presenting high insertion loss and crosstalk.

## 1.4.3 Last Part: Conclusion and Appendix

The conclusion of the work is presented in Chapter 8. The main results and the contributions of this work are summarized in this chapter, and a perspective on future works is given.

# Wireless Implantable Device for Part I Medical Monitoring Brain

# 2 Implantable ecosystem

Among all the autonomous sensing system applications, one of the most critical and challenging field is the medical monitoring, in which biological signals have to be processed with a relatively high accuracy, in order to treat reliable medical informations.

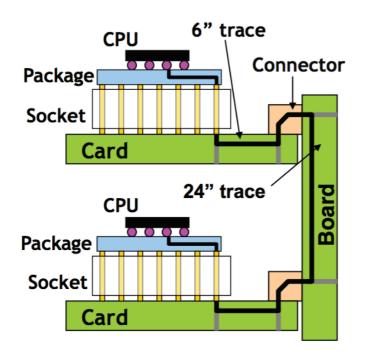

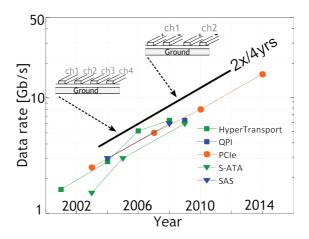

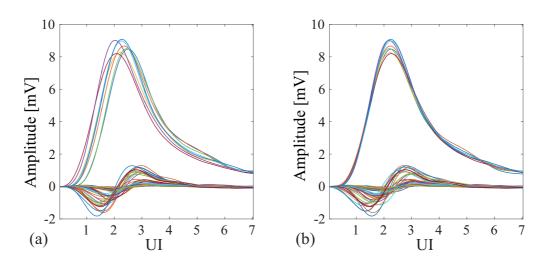

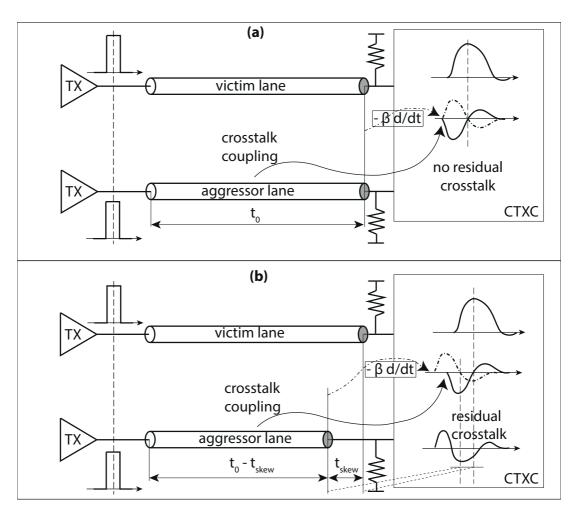

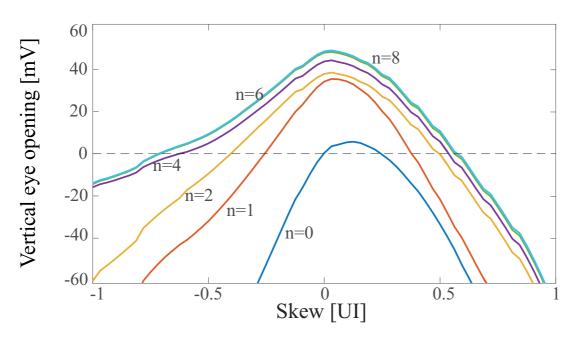

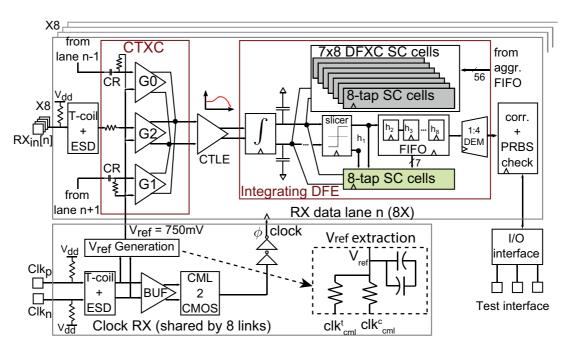

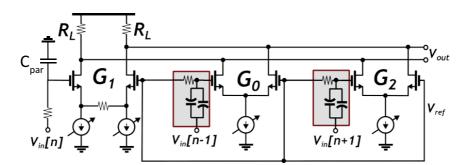

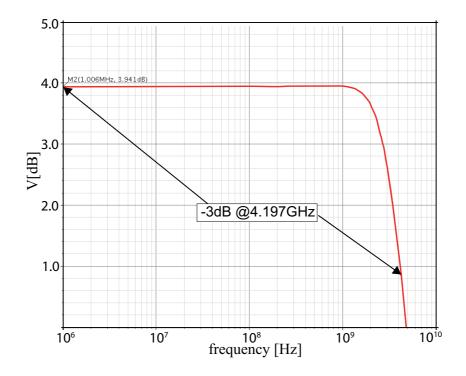

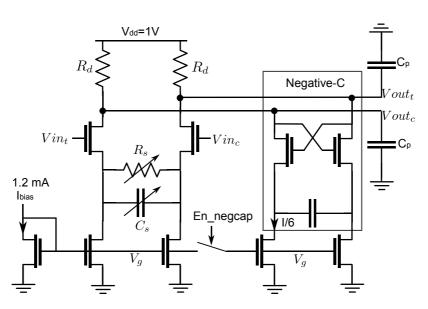

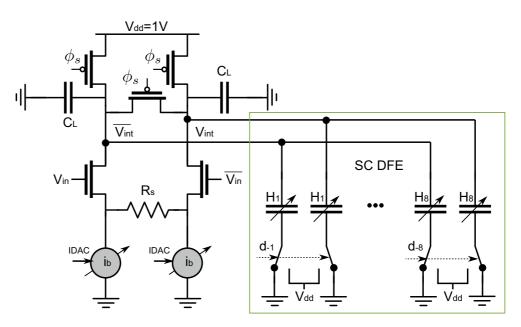

A research study developed in all the high-income countries have evinced that brain disorders are the major health problem [9]. Di Luca et al. [10] estimate that brain disorders cost to the EU economy around 900 billion US\$, with 179 million people afflicted in 2010. Fig. 2.1 shows the cost distribution of the main brain diseases in Europe [10], in 2010. A tentative comparison is given with other major human disorders, such as around 200 billion US\$ [11] for cardiovascular diseases and from 150 to 250 billion US\$ [9, 10], giving the global picture of how important is the brain health as social and economic burden in Europe and the rest of the world.