### Multi-Tone Signaling and ADC-Based Digital Receiver for High-Speed Wireline Serial Links

### THÈSE Nº 8747 (2018)

PRÉSENTÉE LE 18 JUILLET 2018

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR

LABORATOIRE DE SYSTÈMES MICROÉLECTRONIQUES

PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

Gain KIM

acceptée sur proposition du jury:

Prof. G. De Micheli, président du jury Prof. Y. Leblebici, directeur de thèse Dr T. Toifl, rapporteur Prof. H.-M. Bae, rapporteur Prof. A. Burg, rapporteur

|  |  | To my parents |

|--|--|---------------|

|  |  |               |

|  |  |               |

|  |  |               |

|  |  |               |

|  |  |               |

## Acknowledgements

First of all, I would like to express my most profound gratitude to my supervisor, Prof. Yusuf Leblebici for giving me an opportunity to work in LSM as his Ph.D. student. He always encouraged me to explore new ideas, gave me complete freedom to work on whichever topic I am interested in, and showed me the right direction to go whenever I needed his advice. I can never thank him enough for his trust in me and his unlimited support.

I would like to thank Dr. Thomas Toifl for providing me such an excellent research environment at the IBM Research Laboratory in Zurich. He was always available to help and to have a discussion when needed. Without his technical input to DMT RX project, a successful tape-out and measurements would not have been possible.

I must thank colleagues at IBM ZRL: Matthias Braendli for his invaluable help in DSP physical design, Danny Luu, Christian Menolfi, Pier-Andrea Francese, Thomas Morf, Lukas Kull and Marcel Kossel for sharing their technical knowledge and for their invaluable help during the measurement in the lab, Alessandro Cevrero, Ilter Ozkaya, Riduan Khaddam-Aljameh, and Irem Boybat for their friendship during my stay at IBM ZRL.

I also thank my thesis committee and jury president for their valuable time for reviews and discussions: Prof. Hyeon-Min Bae, Dr. Thomas Toifl, Prof. Yusuf Leblebici, Prof. Andreas Burg, and Prof. Giovanni De Micheli.

I am thankful to Dr. Alain Vachoux and Dr. Alexandre Schmid for their support during my stay at LSM. I also thank my current and past colleagues in LSM: Ayca, Firat, Arda, Duygu, Mustafa, Cosimo, Jonathan, Jury, Bilal, Selman, Lizeth, Behnoush, Sylvain, Seniz, Elmira, Kerem, Gulperi, Sebastian, Tugba, Clemens, Vladan, Omer, Kadir, Mahsa and Armin for being the best colleagues. I have to thank Can and Wen-Yang for being my best office mates. Special thanks to Navid (Reza) Ranjandish and Raffaele Capoccia for sharing an uncountable number of dinners with me at Holycow and Burrito Brothers. I thank Kiarash Gharibdoust for his immense input on publications and for sharing his technical experience and knowledge with me, and of course, for his friendship. I also thank my students Thierry Barailler, Chen Cao, and Chirag Ranawat for their contributions in my work.

I must thank Lorenz Schmid, Yassir Benkhedda, and Dion Tzamarias for their unchanging friendship from our undergraduate study.

I would like to thank my Korean friends who had so much of funny time with me in Lausanne: Yonghoon Yoon, Kyonghwan Jin, Joowon Lim, Hokwon Kim, Youngjoo Seo, Boram Choi, Jeonghyeok Im, Bomi Lee, Doohyun Kim, Kyungtaek Cho, Mintae Chung, Woojin Lee, Byungyeon Cho, Yeonji Oh, Sohyeong Kim, Myeongseop Song, Oh-hyeon Choung, Yangsun

### Acknowledgements

Hwang, Sukho Song, and Sungyeon Hong for sharing unforgettable moments with me. I also thank my friends in Zurich: Juneseung Lee, Jihye Suh, and Somi Yoo for sharing precious moments with me during my stay in Zurich. I am thankful to Dr. Kwangjin Lee and his wife for inviting me to their home with hospitality every time I visit South Korea. I thank my dear friends from schooltime, Hyungmin Rho, Sangwoo Shim, and Miso Huh for their endless friendship.

And I thank my aunt Joanna Kim and uncle Peter Sebestyen for their endless love and their encouragement. I also thank my grandparents Samdo Lee, Young-Ok Kim, and Seokjong Kim for their inexpressible and infinite love. I express my deepest gratitude to my mother Jonghee Kim, my father Dowon Kim, and my sister Nayoung Kim for their unconditional and unlimited love, for being beside me whenever I needed, for their endless support, and for always being on my side. Finally, I would like to thank my lovely Hyesung for being the most important person in my life for the rest of our long journey.

Lausanne, 9 July 2018

Gain Kim

### **Abstract**

The exponential growth of Internet traffic and related demands for higher communication speed pushes processor-to-processor and processor-to-memory interconnects to provide further higher data-rate. Often time, processor-to-memory interconnects' speed is limited by reflections due to their multi-drop bus (MDB) channel nature, and processor-to-processor interconnects' speed is limited by inter-symbol interference due to the slowly-decaying channel pulse response and the operating speed and/or power efficiency of the equalization circuits. For the data-rate to continue its exponential growth, more complex modulation and equalization techniques should be employed in the transmitter (TX) and receiver (RX) circuits, given the power and silicon area budget.

This thesis presents a signaling scheme designed to overcome equalization challenges related to reflection-limited interfaces such as MDB interfaces. By shaping the spectrum of the transmitted signal appropriately to the channel's frequency characteristics, the proposed signaling enables minimization of energy-loss due to reflections. While the data-rate of conventional non-return-to-zero (NRZ) signaling over MDB is limited by its first notch frequency unless power-hungry decision-feedback equalizer (DFE) is employed, the proposed signaling scheme allows overcoming such limitation by simple encoding and decoding.

Analog multi-tone (AMT) signaling with single-sideband (SSB) radio-frequency (RF)-bands for efficient bandwidth usage is proposed for lossy point-to-point interfaces. The mutuallyorthogonal RF sub-bands feature self-equalization throughout the propagation through the communication medium and down-conversion at the RX, without necessitating the presence of conventional equalizers. To enable communication with higher modulation order for more efficient bandwidth utilization, an analog-to-digital converter (ADC)-based discrete multi-tone (DMT) RX is designed and implemented. Thanks to the high bandwidth efficiency of approximately 5.33 bits/Hz (including the cyclic prefix of DMT symbol) using 64-level quadrature amplitude modulation (64-QAM), the implemented RX undergoes less channel attenuation as compared to its 4-level pulse amplitude modulation (PAM-4) counterpart given target communication speed through the same channel. Moreover, the inherently parallel RX architecture of DMT signaling allows the RX digital signal processing (DSP) elements to be designed in semi-custom style without stringent timing constraints. Finally, a PAM-4 RX based on ADC with fully-digital equalization is presented. With register-transfer level (RTL) modeling of the designed digital equalizer, the results demonstrate the feasibility of frequency-domain equalization of the time-domain signal using Fourier transform and its inversion. The proposed frequency-domain equalization technique removes the necessity

of symbol-by-symbol feedback loop in DSP that is present in DFE, relaxing critical timing constraints in DSP synthesis.

The focus of this thesis is on the study of spectral characteristics of transmitted/received data and frequency-domain solution for equalization by multi-channel (carrier) and/or ADC-based digital signal processing. The spectrum shaping signaling targeting MDB interfaces is demonstrated by architectural modeling and general-purpose digital-to-analog converter (DAC)-based experiment. The SSB-AMT signaling with self-equalization characteristics is demonstrated by architectural modeling and general-purpose DAC and ADC with a high oversampling ratio for emulating analog signaling. The DMT transceiver (TRX) for ultra-high-speed wireline serial link system is demonstrated using DAC as DMT TX and fabricated RX chip in GlobalFoundries 14 nm FinFET low-power plus (LPP) process technology.

**Keywords:** Serial link, wireline transceiver, wireline receiver, ADC, analog-to-digital converter, ADC-based serial link, multi-drop bus, spectrum shaping, PAM-4, 4-PAM, discrete multi-tone, DMT, analog multi-tone, AMT, Fourier transform.

### Résumé

La croissance exponentièlle du trafic Internet et les demandes connexes pour une vitesse de communication plus élevée poussent les interconnexions processeur-à-processeur et processeur-à-mémoire vers un débit de données plus élevé. Souvent, les interconnexions processeur-mémoire sont limitées par des réflexions dues à leur nature de canal de bus multipoint, et les interconnexions processeur-processeur sont limitées par l'interférence inter-symboles due à la réponse d'impulsion de canal à décroissance lente et la vitesse de fonctionnement et/ou l'efficacité énergétique des circuits d'égalisation. Pour que le débit de données continue sa croissance exponentielle, une modulation et une égalisation plus complexes doivent être utilisées dans les circuits émetteur et récepteur, compte tenu du budget de la puissance et de la surface de silicium.

Cette thèse présente un schéma de signalisation conçu pour surmonter les interfaces limitées par la réflexion telles que les interfaces bus multipoint. En faisant correspondre de manière appropriée le spectre du signal transmis aux caractéristiques de fréquence du canal, la signalisation proposée permet de minimiser la perte d'énergie due aux réflexions. Alors que le débit de données de la signalisation non-retour à zéro classique sur le bus multipoint est limité par sa première fréquence d'entailleur, sauf si un égaliseur à rétroaction décisionnelle gourmand en énergie est utilisé, le schéma de signalisation proposé permet de surmonter cette limitation par simples encodage et décodage.

La signalisation à plusieurs tonalités analogiques avec des bandes à fréquence radio à bande latérale unique pour une utilisation efficace de la bande passante est proposée pour les interfaces point à point avec perte. Les sous-bandes fréquence radio mutuellement orthogonales présentent une auto-égalisation tout au long de la propagation à travers le canal et une conversion vers le bas au niveau du récepteur, sans nécessiter la présence d'égaliseurs classiques. Afin de permettre une communication avec un ordre de modulation plus élevé pour une meilleure utilisation de la bande passante, un récepteur multitone discret basé sur un convertisseur analogique-numérique (CAN) est conçu et implémenté. Grâce à l'efficacité de bande passante élevée d'environ 5,33 bits/Hz (préfixe cyclique inclu) utilisant une modulation d'amplitude en quadrature de 64 niveaux, le récepteur implémenté subit moins d'atténuation du canal que sa modulation d'impulsions d'amplitude de 4 niveaux (MIA-4) contrepartie pour la même vitesse de communication par le même canal. De plus, l'architecture réceptrice intrinsèquement parallèle de la signalisation discrète multitone permet aux éléments de traitement du signal numérique du récepteur d'être conçus dans un style placé et routé automatiquement sans contraintes de synchronisation strictes. Enfin, un récepteur MIA-4 basé sur CAN avec égalisa-

#### Résumé

tion entièrement numérique est conçu. Avec la modélisation du niveau de transfert de registre (RTL) de l'égaliseur numérique conçu, les résultats montrent la faisabilité de l'égalisation dans le domaine fréquentiel du signal dans le domaine temporel en utilisant la transformée de Fourier et son inversion. La technique d'égalisation du domaine fréquentiel proposée supprime la nécessité d'une boucle de rétroaction symbole par symbole dans le processeur de signal numérique qui est présente dans l'égaliseur à rétroaction décisionnelle, relâchant les contraintes de synchronisation dans la synthèse du processeur du signal numérique.

L'objectif de cette thèse est l'étude des caractéristiques spectrales des données transmises/reçues et de la solution de domaine fréquentiel pour l'égalisation par traitement de signal numérique multicanal (porteuse) et/ou CAN. Le schéma de signalisation proposé ciblant les interfaces de bus multipoint est illustré par une modélisation architecturale et une expérience à base de convertisseur numérique-analogique (DAC) à usage général. La signalisation de plusieurs tonalités analogiques à bande latérale unique avec des caractéristiques d'autoégalisation est démontrée par modélisation architecturale et l'experimentation basée sur le CDA et CAN à usage général avec suréchantillonnage pour l'émulation de la signalisation analogique. L'émetteur-récepteur multitone discret pour le système de liaison série filaire à ultra-haute vitesse est démontré en utilisant le CDA comme émetteur multitone discret et la puce RX fabriquée par la technologie de processus FinFET LPP de 14 nm de GlobalFoundries.

**Mots clés :** Lien série, émetteur-récepteur filaire, récepteur filaire, CAN, Convertisseur analogiquenumérique, Lien série basé sur CAN, bus multi-tap, mise en forme du spectre, multi-ton discrète, multi-ton analogique, Transformée de Fourier.

# Contents

| Ac | cknov | wledge   | ments                                                         | 1   |

|----|-------|----------|---------------------------------------------------------------|-----|

| Ał | ostra | ct (Eng  | lish/Français)                                                | vii |

| Li | st of | figures  |                                                               | xii |

| Li | st of | tables   |                                                               | xv  |

| 1  | Intr  | oducti   | on                                                            | 1   |

|    | 1.1   | Wired    | Interfaces and Standards                                      | 2   |

|    | 1.2   | Backg    | ground and Prior-Arts                                         | 5   |

|    |       | 1.2.1    | Point-to-Point Interconnect                                   | 5   |

|    |       | 1.2.2    | Multi-Drop Link                                               | 8   |

|    | 1.3   | Contr    | ibutions and Thesis Organization                              | 9   |

| 2  | Dig   | ital Spe | ectrum Shaping Signaling                                      | 13  |

|    | 2.1   | NRZ S    | Signaling for Multi-Drop Interfaces                           | 13  |

|    | 2.2   | Digita   | ll Spectrum Shaping Signaling for ISI and Crosstalk Reduction | 15  |

|    |       | 2.2.1    | ISI/Crosstalk Reduction Scheme                                | 15  |

|    |       | 2.2.2    | Hardware Architecture Example                                 | 19  |

|    |       | 2.2.3    | Simulation Results                                            | 21  |

|    |       | 2.2.4    | Supplementary Experimental Results                            | 23  |

|    | 2.3   | ICI Re   | eduction for Digital Spectrum Shaping Signaling               | 25  |

|    |       | 2.3.1    | ICI Reduction Mechanism                                       | 26  |

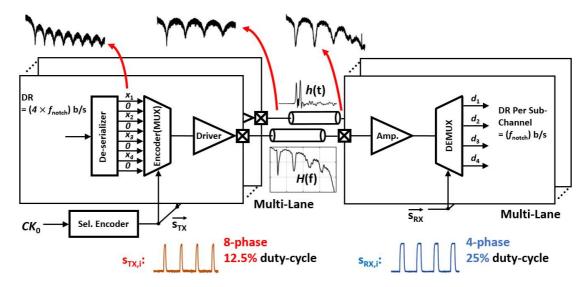

|    |       | 2.3.2    | TRX Architecture Example                                      | 29  |

|    |       | 2.3.3    | Simulation Results                                            | 30  |

|    | 2.4   | Concl    | usion                                                         | 33  |

| 3  | Sing  | gle-Sid  | eband Analog Multi-Tone Signaling                             | 35  |

|    | 3.1   | Single   | e-Sideband RF                                                 | 35  |

|    | 3.2   | Single   | e-Sideband Selection                                          | 37  |

|    | 3.3   | Propo    | osed TRX Architecture                                         | 40  |

|    |       | 3.3.1    | Transmitter                                                   | 40  |

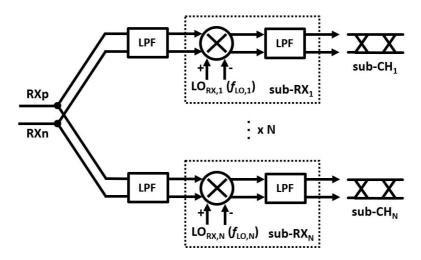

|    |       | 3.3.2    | Receiver                                                      | 43  |

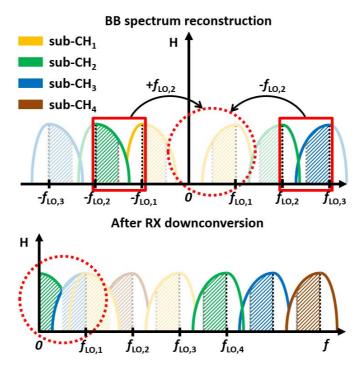

|    |       | 3.3.3    | Design Considerations and Main Limitations                    | 47  |

### **Contents**

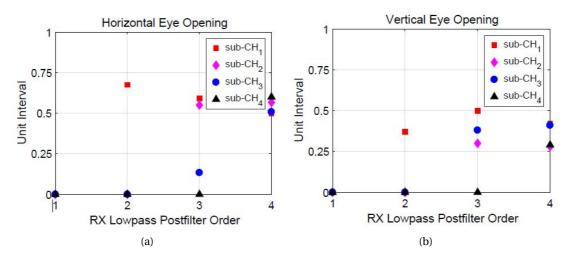

|    | 3.4                | Simulation Results                                                  | 47  |  |  |

|----|--------------------|---------------------------------------------------------------------|-----|--|--|

|    |                    | 3.4.1 With High-order RX Lowpass Postfilter (4 <sup>th</sup> order) |     |  |  |

|    |                    | 3.4.2 With Low-order RX Lowpass Postfilter (2 <sup>nd</sup> order)  | 49  |  |  |

|    | 3.5                | Supplementary Experimental Results                                  | 50  |  |  |

|    | 3.6                | Conclusion                                                          | 55  |  |  |

| 4  | ADO                | C-Based Wireline Receiver With Discrete Multi-Tone Signaling        | 57  |  |  |

|    | 4.1                | Introduction                                                        | 57  |  |  |

|    | 4.2                | Transmitter Architecture                                            | 60  |  |  |

|    | 4.3                | Receiver Architecture                                               | 62  |  |  |

|    | 4.4                | Measurement Results                                                 | 69  |  |  |

|    | 4.5                | Conclusion                                                          | 82  |  |  |

| 5  | ADO                | C-Based Fully-Digital PAM-4 Receiver                                | 85  |  |  |

|    | 5.1                | High-Speed Wireline Receiver Basics (Revisited)                     | 85  |  |  |

|    | 5.2                | Parallel Implementation of Digital Receiver                         | 86  |  |  |

|    |                    | 5.2.1 Signal Processing for Digital Equalization                    | 87  |  |  |

|    |                    | 5.2.2 DSP Implementation                                            | 88  |  |  |

|    | 5.3                | Simulation and Implementation                                       | 90  |  |  |

|    | 5.4                | Conclusion                                                          | 92  |  |  |

| 6  | Con                | nclusion                                                            | 93  |  |  |

|    | 6.1                | Achievements                                                        | 93  |  |  |

|    | 6.2                | Future Works                                                        | 94  |  |  |

| Bi | bliog              | graphy                                                              | 102 |  |  |

| Li | List of Acronyms   |                                                                     |     |  |  |

| Cı | Curriculum Vitae 1 |                                                                     |     |  |  |

# **List of Figures**

| 1.1  | type (b) due to connected mobile devices from 2016 to 2021 [1]                                          | 2  |

|------|---------------------------------------------------------------------------------------------------------|----|

| 1.2  | Lane data-rate of various serial link standards                                                         | 3  |

| 2.1  | Measured example multi-drop bus: (a) through and FEXT frequency responses,                              |    |

|      | (b) pulse response with 200-ps pulse-width                                                              | 14 |

| 2.2  | Crosstalk from an aggressor lane to a victim lane                                                       | 14 |

| 2.3  | Eye diagram of received 5 Gb/s single-ended NRZ signal with a CTLE followed by                          |    |

|      | a 10-tap DFE, (a) without FEXT cancellation and (b) with 1-tap XFFE+1-tap XDFE.                         | 14 |

| 2.4  | Overall system architecture of the proposed TRX                                                         | 15 |

| 2.5  | The time domain flow of the spectrum shaping signaling transmitter                                      | 16 |

| 2.6  | Power spectrums of signals (a) for the proposed TRX and (b) for the conventional                        |    |

|      | NRZ TRX, shown with the reference multi-drop channel frequency response. $$ .                           | 16 |

| 2.7  | (a) Effective pulse response and its pre/post-cursors of a modulated 2.5 Gb/s                           |    |

|      | each and (b) the ICI pre/post-cursors                                                                   | 17 |

| 2.8  | MDB FEXT frequency response and power spectrum envelopes for (a) $2 \times 2.5$                         |    |

|      | Gb/s modulated signals and (b) 5 Gb/s NRZ                                                               | 18 |

| 2.9  | FEXT and through response for, (a) 2-sub-channel 2.5 Gb/s each modulated                                |    |

|      |                                                                                                         | 18 |

| 2.10 | Effective pulse responses of sub-channels with ISI, ICI and FEXT for valid time-                        |    |

|      | division sampling windows on the receiver side for (a) $x_1$ and (b) $x_2$                              | 19 |

| 2.11 | Proposed (a) transmitter architecture and (b) receiver architecture                                     | 20 |

| 2.12 | Block diagram of clock vector generator                                                                 | 21 |

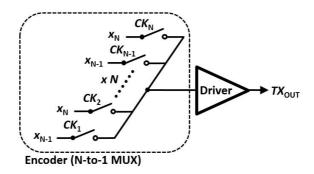

| 2.13 | Encoding MUX and its data-path and control signals                                                      | 21 |

| 2.14 | Eye diagrams (a) on the TX output and (b) on the receiver front-end with the                            |    |

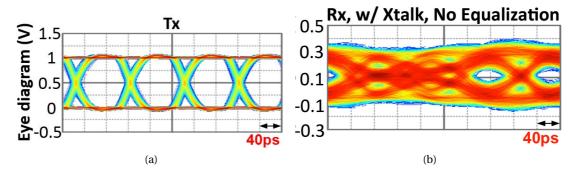

|      | FEXT, for a $2 \times 2.5$ Gb/s proposed TRX                                                            | 22 |

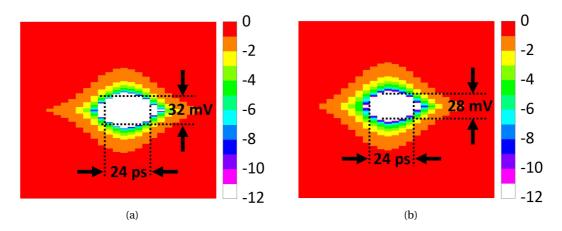

| 2.15 | BER eye diagram for (a) $x_1$ sub-channel and (b) $x_2$ sub-channel, taking the effect                  |    |

|      | of some important deterministic jitter sources into account                                             | 22 |

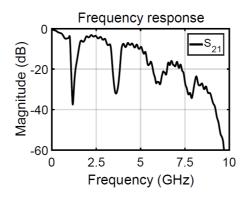

| 2.16 | MDB channel frequency response used for the measurement                                                 | 23 |

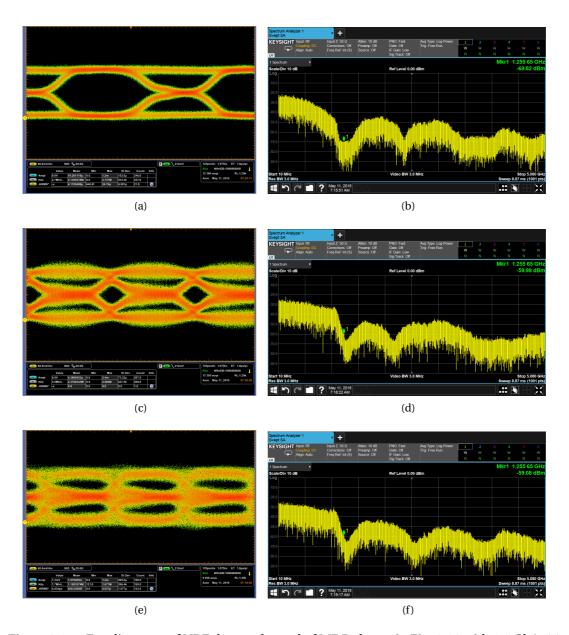

| 2.17 | Eye diagrams of NRZ data at the end of MDB shown in Fig. 2.16 with 1.2 Gb/s                             |    |

|      | (a), $2.2\mathrm{Gb/s}$ (c), $2.6\mathrm{Gb/s}$ (e) and their corresponding spectrum (b), (d), and (f), |    |

|      | respectively                                                                                            | 24 |

### **List of Figures**

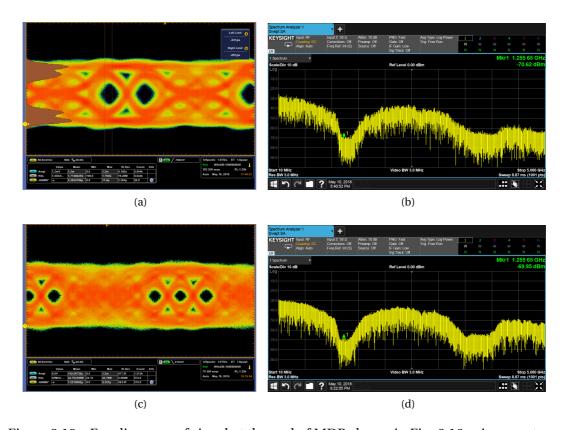

| 2.18 | Eye diagrams of signal at the end of MDB shown in Fig. 2.16 using spectrum shaping signaling with $2\times1.3$ Gb/s (a), $3\times1.2$ Gb/s (c) and their corresponding spectrum (b) and (d), respectively | 25 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

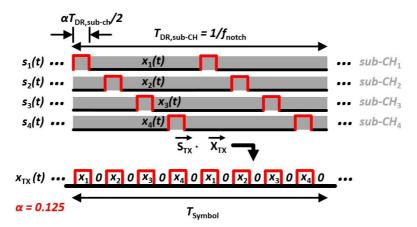

| 2 10 | Time-domain signal flow of the proposed signaling scheme by introducing guard                                                                                                                             | 23 |

| 2.13 | interval                                                                                                                                                                                                  | 26 |

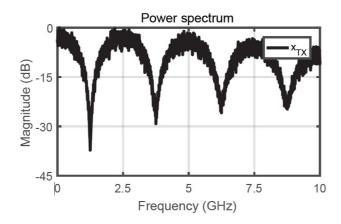

| 2 20 | Magnitude of the power spectrum of $x_{\text{TX}}(t)$                                                                                                                                                     | 26 |

|      | TDM-based serial data TRX architecture employing the proposed signaling                                                                                                                                   | 20 |

| 2,21 | scheme, with the maximum number of sub-channel being 4                                                                                                                                                    | 27 |

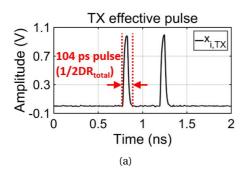

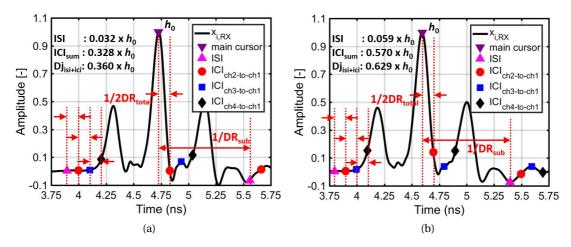

| 2.22 | Effective transmitted pulse (a) and the effective pulse response (b) with 4 sub-                                                                                                                          | 21 |

|      | channels and $DR_{\text{total}} = 4.8 \text{ Gb/s.}$                                                                                                                                                      | 28 |

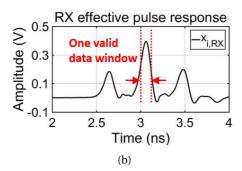

| 2.23 | Effective pulse responses and their main cursor, ISI, and ICI cursors (a) for the                                                                                                                         |    |

|      | proposed signaling scheme and (b) for the signaling proposed in Chapter 2.2.1.                                                                                                                            | 28 |

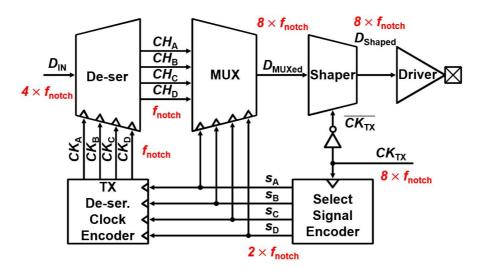

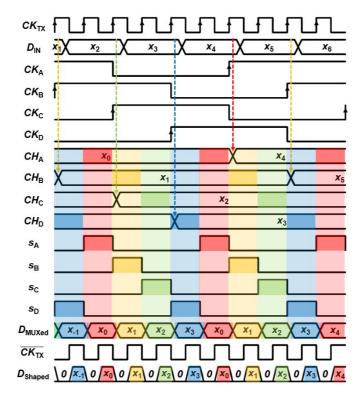

| 2.24 | TX block diagram for the proposed signaling scheme                                                                                                                                                        | 30 |

| 2.25 | Data flow at the TX internal nodes                                                                                                                                                                        | 31 |

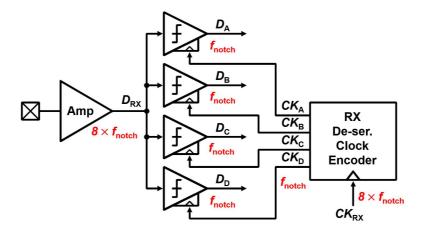

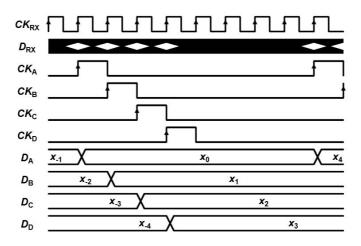

| 2.26 | RX block diagram for the proposed signaling scheme.                                                                                                                                                       | 31 |

| 2.27 | Waveform of RX nodes                                                                                                                                                                                      | 32 |

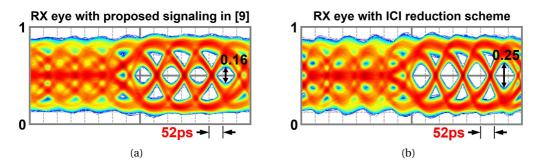

| 2.28 | Received eye diagrams of 4-channel 4.8Gb/s data stream with the system in [60]                                                                                                                            |    |

|      | and (b) that with the proposed scheme                                                                                                                                                                     | 32 |

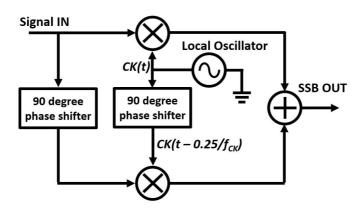

| 3.1  | Block diagram of a phase-discrimination circuit                                                                                                                                                           | 36 |

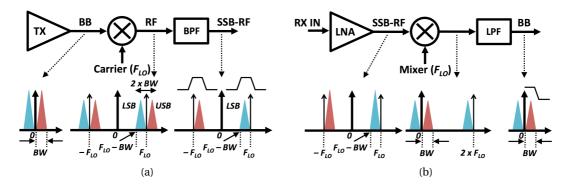

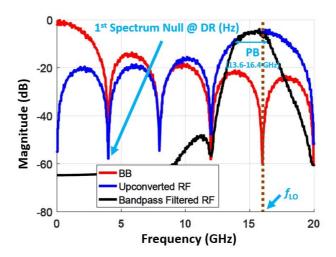

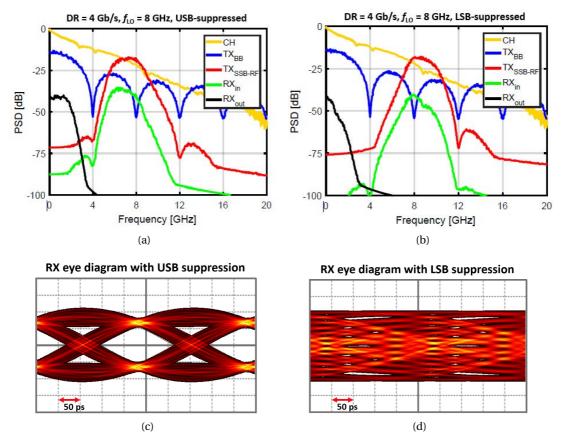

| 3.3  | Power spectrums of the 4 Gb/s data stream along the transmitter building blocks.                                                                                                                          | 37 |

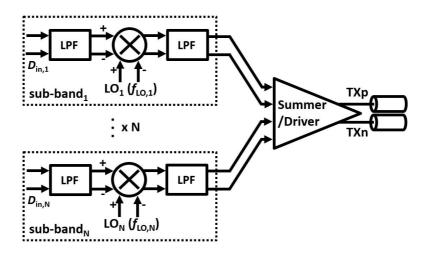

| 3.8  | AMT/SSB TX architecture                                                                                                                                                                                   | 41 |

| 3.10 | Frequency planning with four sub-channels                                                                                                                                                                 | 42 |

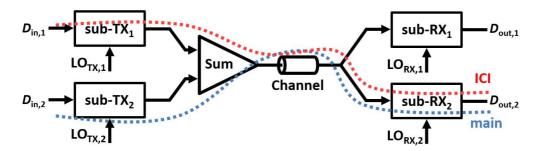

| 3.11 | ICI mechanism of sub-channel 1 to sub-channel 2                                                                                                                                                           | 42 |

| 3.12 | AMT/SSB RX architecture                                                                                                                                                                                   | 43 |

| 3.13 | BB spectrum reconstruction mechanism when downconverted, for sub-channel                                                                                                                                  |    |

|      | i=2                                                                                                                                                                                                       | 44 |

| 3.14 | Effect of low-pass prefilter on downconversion, for sub-channel $i=2.\dots$                                                                                                                               | 45 |

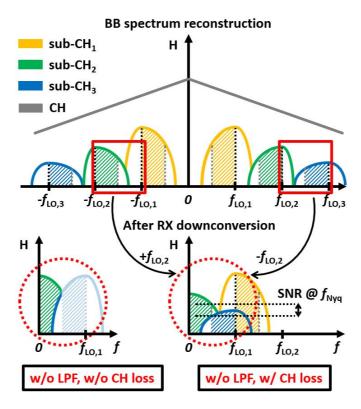

| 3.15 | Effect of channel insertion loss on downconversion, for sub-channel $i=2$                                                                                                                                 | 46 |

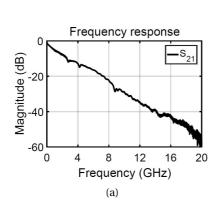

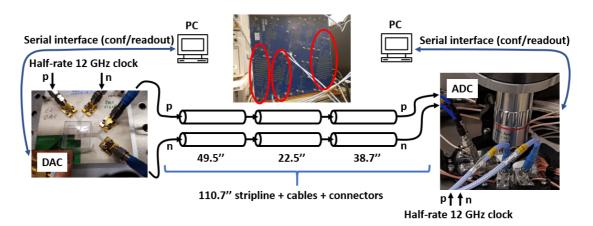

| 3.23 | Experiment setup with oversampling DAC and ADC, and series-connected                                                                                                                                      |    |

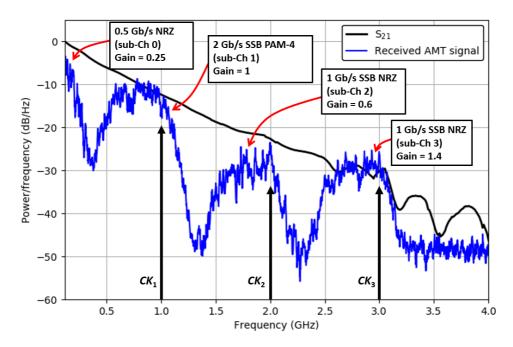

|      | striplines to maximize attenuation for DAC/ADC-based experiment                                                                                                                                           | 53 |

| 3.24 | Channel $S_{21}$ frequency response and the measured spectrum of the received 4.5                                                                                                                         |    |

|      | Gb/s 4-channel digitally-emulated AMT signal                                                                                                                                                              | 54 |

| 3.25 | Portion of waveform of AMT signal at the RX front-end sampled by 24-times                                                                                                                                 |    |

|      | oversampling 10-bit ADC                                                                                                                                                                                   | 54 |

| 3.26 | Reconstructed eye diagrams from oversampled RX AMT signal of which spec-                                                                                                                                  |    |

|      | trum is shown in Fig. 3.24                                                                                                                                                                                | 55 |

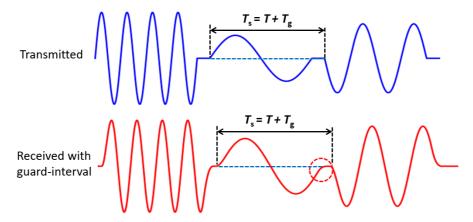

| 4.1  | Transmitted 3 consecutive DMT symbols (a) and the received symbols with ISI                                                                                                                               |    |

|      | (red circle)                                                                                                                                                                                              | 58 |

| 4.2  | Transmitted 3 consecutive DMT symbols (a) and the received symbols with                                                                                                                                   |    |

|      | guard-interval                                                                                                                                                                                            | 58 |

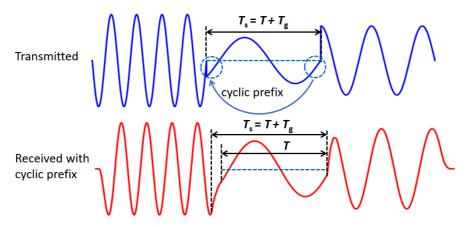

| 4.3  | Transmitted 3 consecutive DMT symbols (a) and the received symbols with                                                                                                           |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | cyclic prefix                                                                                                                                                                     | 59 |

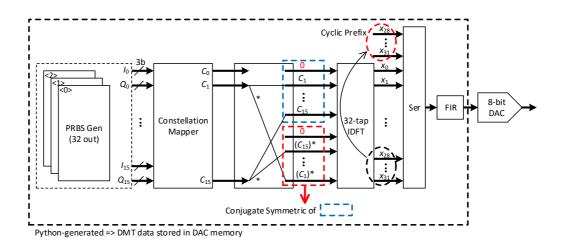

| 4.4  | DMT TX block diagram                                                                                                                                                              | 61 |

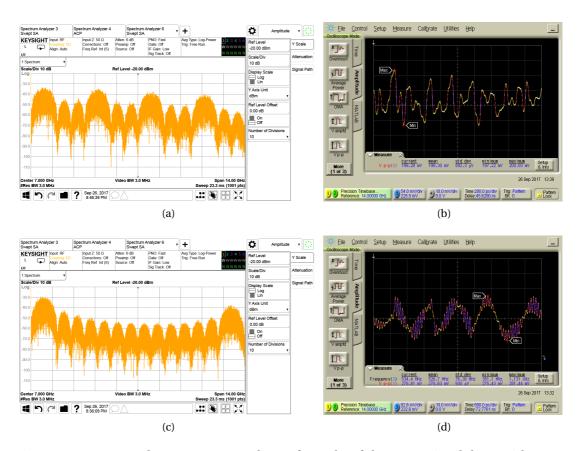

| 4.5  | Measured spectrum (a) and waveform (b) of the transmitted data (without TX                                                                                                        |    |

|      | FIR) at 28 GS/s conversion rate for DMT symbols with 1/5/9/13 <sup>th</sup> activated                                                                                             |    |

|      | sub-channels, and spectrum (c) and waveform (d) with $1^{st}$ and $15^{th}$ activated                                                                                             |    |

|      | sub-channels                                                                                                                                                                      | 61 |

| 4.6  | Constellation diagrams of the 1 <sup>st</sup> (a) and the 14 <sup>th</sup> (b) sub-channels, with red dots representing pre-FIR constellation and blue-dots representing post-FIR |    |

|      | constellation                                                                                                                                                                     | 63 |

| 4.7  | Implemented DMT RX block diagram                                                                                                                                                  | 63 |

| 4.8  | A DSP clock synthesizer block diagram (a), multiply-by-4 circuit detail (b), and                                                                                                  |    |

|      | divide-by-3 circuit detail (c).                                                                                                                                                   | 65 |

| 4.9  | Input layer details                                                                                                                                                               | 66 |

| 4.10 | A 32-tap DFT architecture based on two Winograd 16-tap DFTs                                                                                                                       | 67 |

| 4.11 | Illustration of frequency-domain equalization                                                                                                                                     | 70 |

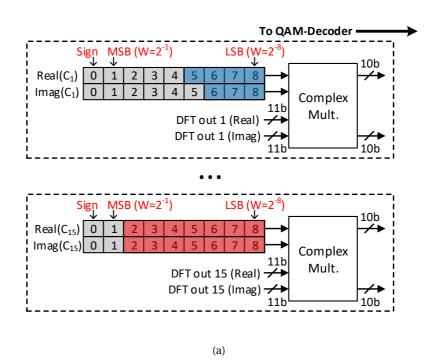

| 4.12 | The FDE architecture without per-sub-channel coefficient gain adjustment (a)                                                                                                      |    |

|      | and with per-sub-channel coefficient gain adjustment (b)                                                                                                                          | 71 |

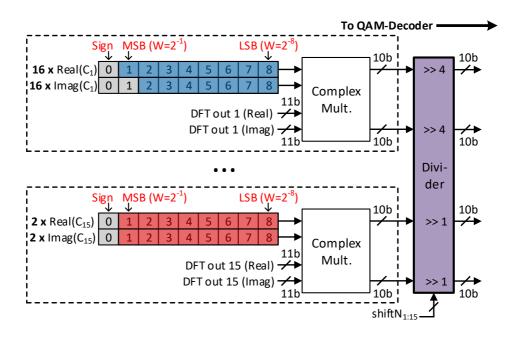

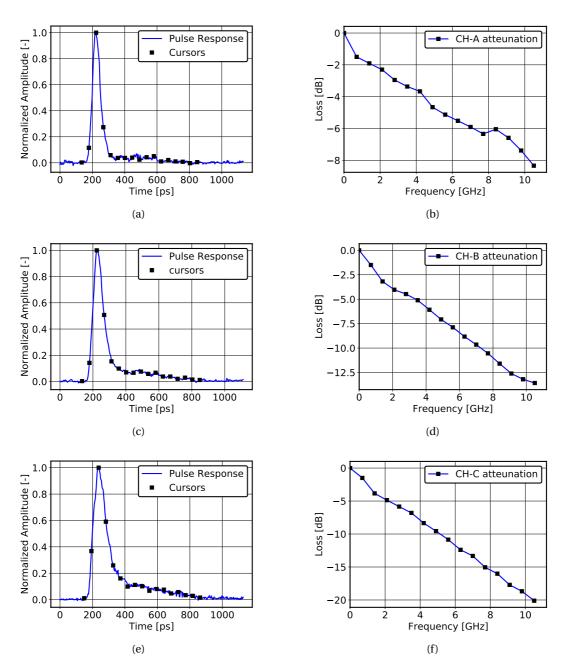

| 4.13 | Measurement setup (a) and DMT RX die with direct probing (b)                                                                                                                      | 72 |

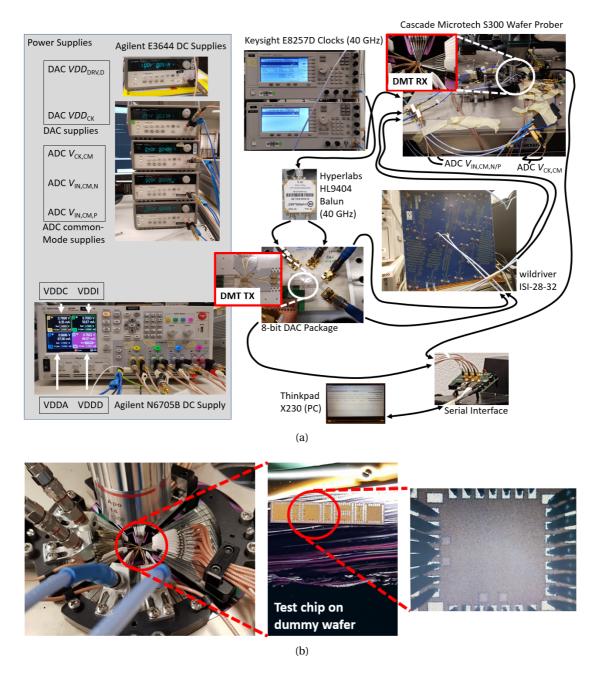

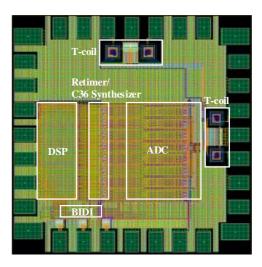

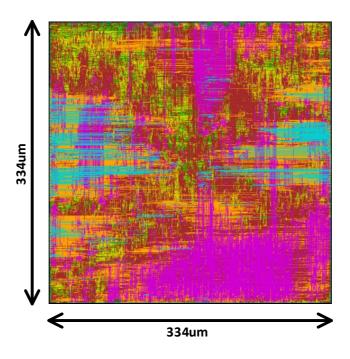

| 4.14 | Die photo of the DMT RX chip (left) and the top-level layout view (right)                                                                                                         | 73 |

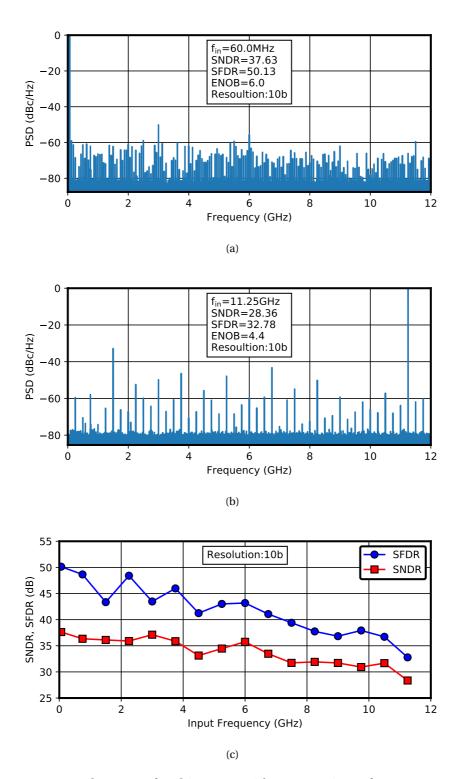

| 4.16 | Measured spectra of 10-bit output with 0.06 GHz input frequency (a) and 11.25 GHz input frequency (b), and SNDR/spurious-free dynamic range (SFDR) from                           |    |

|      | near-DC to near-Nyquist frequency.                                                                                                                                                | 75 |

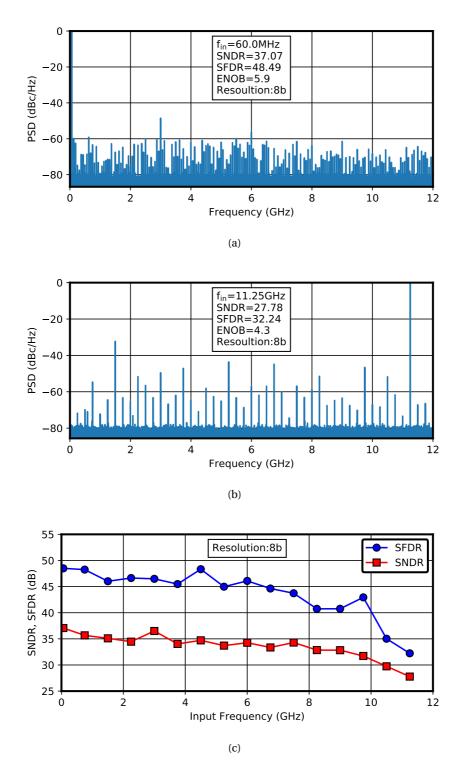

| 4.17 | Measured spectra of 8-bit output with 2-LSB rejection with 0.06 GHz input                                                                                                         |    |

|      | frequency (a) and 11.25 GHz input frequency (b), and SNDR/SFDR from near-                                                                                                         |    |

|      | DC to Nyquist frequency.                                                                                                                                                          | 76 |

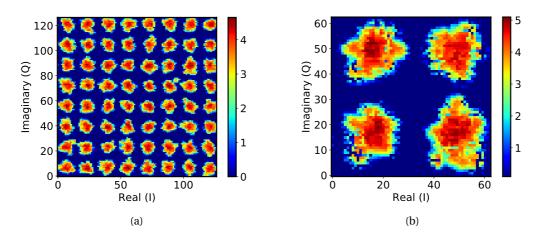

| 4.18 | Constellation diagram of all-64-QAM 15-sub-channels 56 Gbps data-rate over                                                                                                        |    |

|      | CH-C with full-scan (a) and locally focused scan (b)                                                                                                                              | 77 |

| 4.19 | Bathtub curves of all-64-QAM 15-sub-channels, 56 Gbps data-rate over CH-C                                                                                                         |    |

|      | with horizontal cross-section (a) and vertical cross-section (b)                                                                                                                  | 77 |

| 4.20 | Effective 22.4 GBaud/s pulse response with TX FIR filter, for channel-A (a) and                                                                                                   |    |

|      | for channel-B (b)                                                                                                                                                                 | 78 |

| 4.21 | Constellation diagrams of all-64-QAM 15-sub-channels 56 Gbps data-rate over                                                                                                       |    |

|      | CH-B with full-scan (a) and locally focused scan (b) with exponentially-increasing                                                                                                |    |

|      | gain of 0.34 dB/sub-channel from the 1 <sup>st</sup> sub-channel to the 15 <sup>th</sup> sub-channel.                                                                             |    |

|      | The full-scan and locally focused scan without frequency-dependent gain are                                                                                                       |    |

|      | shown in (c) and (d) respectively. The same FIR filter and channel (CH-B) are                                                                                                     |    |

|      | applied in both cases                                                                                                                                                             | 79 |

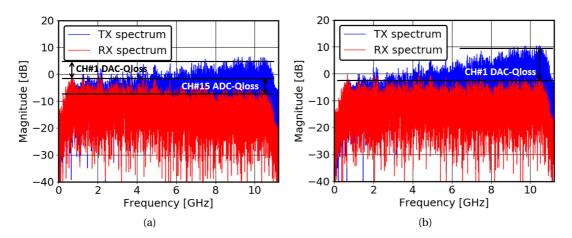

| 4.22 | TX (blue) and RX (red) spectrum with (a) and without (b) exponentially-increasing                                                                                                 |    |

|      | gain of 0.34 dB/sub-channel, where the TX $1^{st}$ sub-channel power is normalized                                                                                                |    |

|      | to RX $1^{st}$ sub-channel power. Qloss: SNR loss induced by data conversion                                                                                                      | 80 |

### **List of Figures**

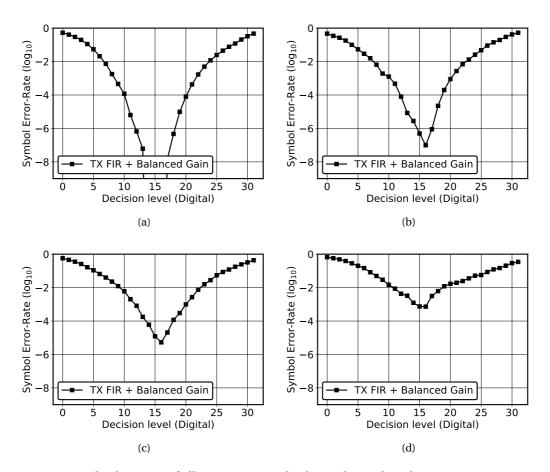

| 4.23 | Bathtub curves of all-64-QAM 15-sub-channels 56 Gbps data-rate over CH-B. Horizontal cross-section and vertical cross-section with gain balancing ((a) and     |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | (b), respectively) and without gain balancing ((c) and (d), respectively)                                                                                      | 81 |

| 4.24 | Constellation diagrams of all-64-QAM 15-sub-channels 56 Gbps data-rate over CH-A with full-scan (a) and locally focused scan (b) with exponentially-increasing |    |

|      | gain of 1.03/sub-channel from the $1^{st}$ sub-channel to the $15^{th}$ sub-channel                                                                            | 82 |

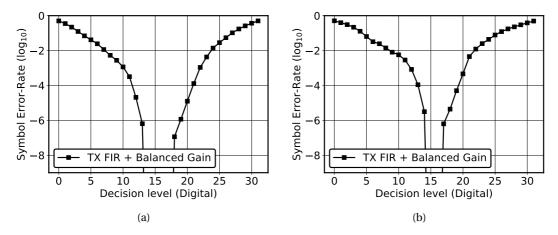

| 4.25 | Bathtub curves of all-64-QAM 15-sub-channels 56 Gbps data-rate over CH-A:                                                                                      |    |

|      | horizontal cross-section (a) and vertical cross-section (b)                                                                                                    | 82 |

| 4.26 | Bathtub curve of 14×64-QAM and 1×16-QAM sub-channels 58.77 Gb/s data-rate                                                                                      |    |

|      | over CH-A (black markers. and that of $13\times64$ -QAM and $2\times16$ -QAM sub-channels                                                                      |    |

|      | 57.33 Gb/s data-rate over CH-B (red markers), both with 24 GS/s data conversion                                                                                |    |

|      | rate                                                                                                                                                           | 83 |

| 4.27 | Bathtub curve of 14×64-QAM and 1×16-QAM sub-channels 58.77 Gb/s data-rate                                                                                      |    |

|      | over CH-A (black markers. and that of 13×64-QAM and 2×16-QAM sub-channels                                                                                      |    |

|      | 57.33 Gb/s data-rate over CH-B (red markers), both with 24 GS/s data conversion                                                                                |    |

|      | rate, with continuous equalization coefficient update                                                                                                          | 83 |

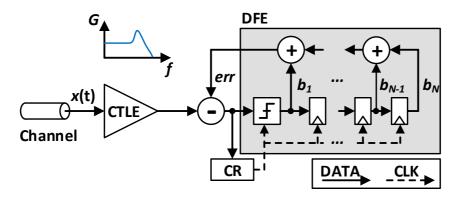

| 5.2  | Simplified receiver equalizer architecture consisting of CTLE, DFE and CR                                                                                      | 86 |

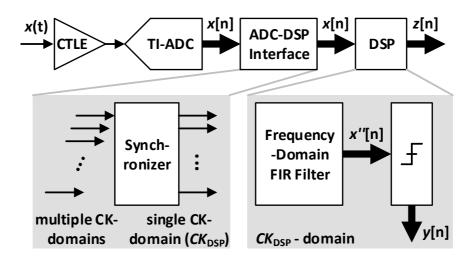

| 5.3  | The parallel digital receiver's architecture overview                                                                                                          | 87 |

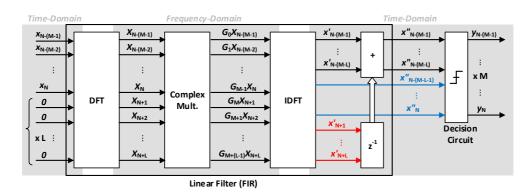

| 5.4  | Receiver DSP system overview and data flow                                                                                                                     | 88 |

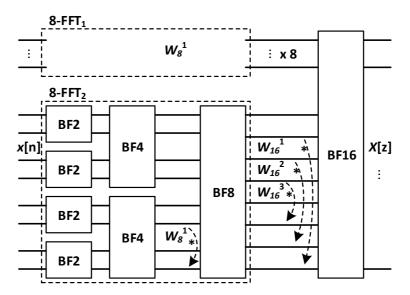

| 5.5  | A 16-tap real-input DFT core's outline. The BF2,4,8,16 are butterfly units and                                                                                 |    |

|      | $W_8 = e^{-i2\pi/8}, W_{16} = e^{-i2\pi/16}$                                                                                                                   | 89 |

| 5.8  | The layout of the DSP. The I/O pins are placed arbitrarily                                                                                                     | 92 |

## **List of Tables**

| 2.1 | Worst-case contributions of each deterministic jitter sources in percentage to |    |

|-----|--------------------------------------------------------------------------------|----|

|     | the main pulse response.                                                       | 19 |

| 2.2 | Performance Comparison With Other Relevant Works                               | 25 |

| 2.3 | Contribution of each deterministic jitter sources in percentage to the main    |    |

|     | cursor                                                                         | 29 |

| 2.4 | Comparison with other relevant works                                           | 33 |

| 3.1 | Lowpass filters' specifications.                                               | 48 |

| 3.2 | Comparison With Other Relevant Works                                           | 53 |

| 4.1 | Number of real multipliers and adders in some Winograd small DFTs for complex  |    |

|     | data with length of power-of-2                                                 | 68 |

| 4.2 | Comparison with state-of-the-art ADC-based RXs                                 | 84 |

## **1** Introduction

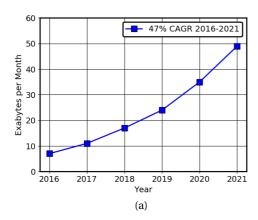

A fast increase in the number of electronic devices connected each other everywhere around the world lead ever-higher global Internet protocol (IP) traffic, meeting the era of Internet-of-things (IoT) and big-data. Moreover, the volume of the multimedia contents that are transmitted/received by individual electronic devices exponentially increases throughout the years [1]. For instance, a pixel-resolution of commonly-used consumer digital displays such as monitors, or televisions has been evolving from  $1024 \times 768$  in 2002 to  $3840 \times 2160$  in 2018, which mutually increases the resolution of the digital videos and photos to be displayed. Also, the number of worldwide smartphone users was increased from 1.57 billion in 2014 to 1.86 billion in 2015, and it is predicted to reach 2.87 billion in 2020, while per-smartphone monthly data traffic increases by 25-40 % annually [2]. Including smartphones, home-electronics, and other IoT devices, the total number of connected consumer-electronic devices is predicted to exceed 11 billion by 2021 [1]. As a result, the global mobile data traffic is expected to reach 49 Exabyte (EB) (or  $49 \times 10^9$  Gigabyte) per month by 2021 [1] where its compound annual growth rate (CAGR) is shown in Fig. 1.1(a).

Such exponential growth of data traffic necessitates enhancement of not only wireless radio frequency (RF) communication bandwidth between the cellular device and the base station or other electronic devices, but also data-rates among wired networking infrastructures. Fig. 1.1(b) highlights the growing network traffic more specifically [1]. Among various subsegments, a significant portion of Internet traffic is due to the mobile video streaming, of which traffic is expected to grow by 54 percent every year between 2016 and 2021 on average, while the overall mobile data traffic is expected to grow by 47 percent each year. This makes the data centers to be the heart of the Internet network, where the multimedia contents and other types of files are stored. A data center includes numbers of racks of servers that are containing processors, data storage units, memories, network switches, routers, that are connected with electrical/optical cables. The server board includes various wireline transceiver (TRX) units for communication with other modules over electrical channels with different communication standards.

As the power consumption of IT/network infrastructures is becoming increasingly crucial

Figure 1.1 – The expected compound data traffic growth (a) and the growth by specific data type (b) due to connected mobile devices from 2016 to 2021 [1].

while satisfying expanding bandwidth demands, pushing the limits of wireline TRXs for chip-to-chip links and chip-to-memory links in terms of data-rate, silicon area, and energy efficiency is crucial. While the aggregate input/output (I/O) data-rate can be increased by placing more I/O pins per component, the increased power consumption, additional interconnect material cost, and larger die/package area raise as an issue. Thus, higher per-pin data-rate with enhanced energy efficiency is must for keeping the aggregate power and material cost unchanged or decreased, while providing a higher total data bandwidth.

### 1.1 Wired Interfaces and Standards

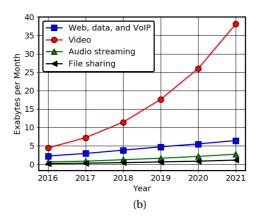

The wired communication systems' characteristics differ from one application to another, e.g., controller-storage interconnect, controller-memory interconnect, and processor-to-processor interconnect. Data rate evolution of some widely-used wireline standards over last two decades is shown in Fig. 1.2. It can be seen that lane data-rate has been successfully following the approximately  $\times 2$  speed enhancement with every generation. The data rates of point-to-point interconnect standards such as peripheral component interconnect express (PCIe), common electrical I/O (CEI), graphics double-data-rate synchronous random-access memory (GDDR SDRAM) remain faster than those of multi-drop interconnect standards such as DDR SDRAM by as much as close to  $\times 8$ .

While having relatively low per-pin data transfer rate, DDR SDRAM still exhibits as high module data-rate as 25.6 GBytes/s with a massively-parallel data bus in case of fourth generation DDR SDRAM (DDR4) dual in-line memory module (DIMM). A similar strategy has been applied in case of high-bandwidth memory (HBM) of which first- and second-generations have been adopted as joint electron device engineering council (JEDEC) standard in October 2013 and January 2016, respectively. The 2<sup>nd</sup> generation HBM (HBM2) exhibits only 2 GT/s but can

Figure 1.2 – Lane data-rate of various serial link standards.

reach as high as 256 GB/s of package bandwidth using 1024-bit-wide memory bus. Main memories such as DDR SDRAM and HBM are typical examples of serial interfaces transferring high bandwidth with relatively low per-pin data-rate using a wide parallel bus. Their massively-parallel bus characteristics requires high lane efficiency, hence single-ended signaling scheme is employed for memory I/Os.

For data center networking applications, optical internetworking forum (OIF) has defined CEI as serializer-deserializer (SerDes) interfaces for the industry since 2006, ranging its defined data-rate from 3.125 Gb/s to 56 Gb/s over multiple generations. It defines standards for various channel reaches, e.g., 10 mm ultra-short-reach (USR) traces for multi-chip modules (MCM), very-short-reach (VSR) traces for on-board module-to-module interconnects, midreach (MR) traces for processor-to-processor communications on server board, and long-reach (LR) backplane interconnects. While differential signaling is used for all sub-categories, modulation schemes may differ from one application to the other due to the different channel characteristics.

As a standard for high-speed computer expansion bus, PCIe standard was defined in 2003 by industries including Intel, Dell, HP, and IBM. PCIe can easily be found in most computer systems' motherboards, of which physical slots generally come with groups of lanes, e.g., ×4, ×8, ×16. Each lane supports data transfer rate from 2.5 GT/s (version 1.0) to 32 GT/s (version 5.0). After considering the redundancy introduced by line-coding such as 8b/10b code for version 1.0/2.0 and 128b/130b for version 3.0/4.0, its per-lane data-rate reaches 1969 MB/s/direction at the latest standard. While each lane is composed of two differential links for transmission/reception, multiple PCIe lanes can be aggregated to extend the bandwidth. Low-speed peripherals, e.g, Wi-Fi card, can use a link with one PCIe lane, while bandwidth-intensive applications such as multi-graphics processing unit (GPU) cards systems can use as many as four lots of 16 PCIe lanes.

The universal serial bus (USB) is an industry standard for personal computer (PC)-peripheral devices communication and power supply. The standard was designed by industries including

### Chapter 1. Introduction

Compaq, IBM, Intel, Microsoft, DEC, NEC, and Nortel in January 1996, and is maintained by the USB implementation forum. While its first standard supports data-rate of as low as 187.5 kB/s (1.5 Mb/s), it currently supports data-rate of as high as 2.5 GB/s (20 Gb/s), using differential signaling. Links employing USB standard are widely used for mass storage, extension cables, audio streaming and power supply.

The IEEE p802.3bj specifies 100 Gb/s Ethernet standard ( $4 \times 25$  Gb/s differential links) for data transmission over electrical links such as twinaxial copper cable and backplane. It allows the use of forward error-correction (FEC) to relax the raw bit error rate (BER) at the cost of coding overhead and additional latency. As FEC coding, Reed-Solomon (RS) codes are widely used in storage systems and data transmission. For example, in IEEE 802.3bj standard, RS (n=528, k=514, m=10, t=7) FEC was designed for 25 Gb/s non-return to zero (NRZ) signaling and RS (n=544, k=514, m=10, t=15) FEC was designed for 25 Gb/s 4-level pulse-amplitude modulation (PAM-4), which can also be used for links with 50 Gb/s/lane. The RS (n=544, k=514, m=10, t=15) FEC relaxes raw BER requirement to as low as  $3 \times 10^{-4}$  for output BER of  $10^{-12}$  [3].

While circuit innovations and equalization techniques as well as process technology enhancement have been pushing the per-lane (or per-pin) data-rate, power/thermal density would have been increased if energy efficiency had not been improved. Moreover, faster data stream occupies larger frequency bandwidth, which makes the signal gets more attenuated and more distorted due to the frequency-dependent channel attenuation and phase distortion, especially with low-cost and/or long-reach cables. The bandwidth- and attenuation-related issues with faster data-rate for lossy channels brought multi-level modulation schemes such as PAM-4 to the stage. While multi-level signaling enables data communication with narrower bandwidth as compared to 2-level signaling (PAM-2, or NRZ) and relaxes timing constraints, it makes the equalization circuits to be more complicated, more area consuming and more power hungry.

Complementary metal oxide semiconductor (CMOS) device fabrication process technology has been aggressively scaled-down over past decades from gate length of 10 um in 1971 down to 32nm. However, the gate length shrinkage no-longer follows the number appears in the process node designation from 28nm node. Standard 2-dimensional planar CMOS technology node had been shrunk down to 20nm with Taiwan Semiconductor Manufacturing Company (TSMC), and 3-dimensional process technology such as FinFET has been rising from 22nm node down to 7nm, and even further down to 5 nm, driven by industries such as TSMC, GlobalFoundries, Samsung, and Intel. Most of today's state-of-the-art field-programmable gate arrays (FPGA), mobile systems-on-chip (SoC), GPU, central processing unit (CPU) are manufactured in FinFET technology [4, 5, 6, 7, 8, 9]. Unlike in planar CMOS, FinFET process does not allow transistor design with continuous gate length choices, but only discrete lengths based on fin-count. Combined with ever-reducing supply voltage, intrinsic metal-oxide semiconductor field-effect transistor (MOSFET) gain over node shrinkage, and a discrete gate length of FinFET, process technology becomes more and more digital-friendly but analog-unfriendly. Following the trend of die-shrinkage and speed/power enhancement of microprocessors and

SoCs, analog circuits have to be fit together with digital circuits on the same die, including analog-to-digital converters (ADC), phase-locked loops (PLL), amplifiers, radio-frequency TRXs, and SerDes. Thanks to the intrinsic speed/power enhancement occupying smaller die area with process technology advancement, analog PLL and SerDes can operate faster with enhanced power efficiency as compared to implementation with older process technologies.

A fast enhancement of low-power, high-speed and mid-resolution ADC's performance in advanced process nodes (including planar CMOS, silicon-on-insulator, FinFET) enabled ADC-based interface design [10, 11, 12, 13]. This triggered increased interests in designing digital equalizers replacing many analog equalizers traditionally implemented as analog circuits. In order to keep the serial link performance improvement in every aspect, e.g., data-rate, energy efficiency, silicon area efficiency, numbers of prior researches have been conducted and reported. In the following sub-chapter, circuits, signaling, signal processing and architectural innovations for improving point-to-point links and multi-drop links are briefly reviewed.

### 1.2 Background and Prior-Arts

#### 1.2.1 Point-to-Point Interconnect

Point-to-point interconnects are widely used from short-reach electrical links such as chip-to-chip communication to long-haul optical links such as digital television and telecommunication network. Thanks to the high bandwidth and low cost, CMOS circuits are widely used for high-speed interconnect systems. Focusing more on electrical links, the transmission line (channel) exhibits low-pass filter-like behavior in its frequency response, due to the skin effect, dielectric loss, and such. Having all the effects causing a loss in channel frequency response, the resulting loss from one end of a channel to the other end is called insertion loss. As point-to-point links are mostly terminated with matched impedance, reflection is generally not pronounced. Moreover, differential signaling is typically used for high-speed links (e.g.,  $\geq$  10 GHz), providing higher input dynamic range and higher signal-to-noise ratio (SNR).

The insertion loss causes frequency-selective delay/attenuation for a wideband signal that passes through the channel. The low-pass filter nature of the channel makes the pulse-response of the system slow and long, resulting in inter-symbol interference (ISI). Since signals passing through a channel can be modeled as a convolution of the incoming waveform with channel's impulse response, tail post-cursors of past pulse responses at particular time slots can accumulate and can be superimposed on top of the main cursor of current pulse response, resulting in decision error. The same mechanism can be applied with precursors. Transmitter (TX) and/or receiver (RX) circuits in wireline serial link systems in general incorporate circuits that partially cancel-out these effects of the channels' characteristics.

Equalizer on the TX side can be used to pre-distort signal to be transmitted so that the predistorting filter's transfer function and the channel transfer function ideally compensate for each other. As the channel is generally low-pass filter-like, high-frequency pre-emphasis or low-frequency de-emphasis schemes are employed as TX equalizer. Implemented as digital finite impulse response (FIR) filter or analog feed-forward equalizer (FFE), such TX pre-/deemphasis filters have an effect to shorten the channel's effective pulse response, reducing the effects of pre-cursors and/or of post-cursors, hence reduced ISI. While the frequency response of pre- and de-emphasis filters are similar given a channel to equalize, their effect on the system differs. By pre-emphasizing TX signal's high-frequency components, the overall transmitted power is increased, resulting in stronger crosstalk power and higher TX power consumption, while de-emphasis reduces the TX output power resulting in lower signal-tonoise ratio at the RX front-end. TX prototypes with 1 pre-emphasis tap are demonstrated in [14, 15, 16] and 2 pre-emphasis taps are demonstrated in [17, 18, 19, 20]. More than 2 preemphasis taps are employed in [21, 22, 23, 24, 25] in order to fully or partially equalize a channel with high-loss, or output driver's bandwidth loss on the TX side. Often time, implementation of TX FFE is easier than implementing it on the RX side since the symbols used for FFE taps' output values are true-digital symbols if implemented on the TX side. However, it is challenging to implement TX FFE with long memory since it will require a high-resolution digital-to-analog converter (DAC) running at symbol-rate, and also due to the limited driver's output amplitude. Hence, in many high-speed serial links for lossy channels employ RX equalizer as well.

RX equalizer is composed of a continuous-time linear equalizer (CTLE) for high-frequency peaking, a linear FFE for pre-/post-cursor cancellation, a decision-feedback equalizer (DFE) for post-cursor cancellation. A CTLE-only RX equalizer demonstrated its equalization capability in [26, 27] when the channel is very smooth without reflection, or when the channel is ultra-short-reach channel with only a small amount of loss at Nyquist. In many designs, equalizer consisting of a CTLE followed by a DFE is chosen when pre-cursors are negligible [28, 29, 30, 31, 32]. To accommodate different types of channels, [28] employs CTLE providing 4–10 dB variable high-frequency peaking followed by a 2-tap DFE with automatic threshold tracking and sign-sign least mean square (LMS) adaptation engine. An RX data-path incorporating CTLE with variable peaking from 0 to 8.8 dB followed by a 2-tap DFE for 30 dB loss compensation is shown in [29], and [30] demonstrates equalization of 20 dB loss channel with 30 Gb/s data-rate under one pJ/b energy efficiency using a CTLE followed by a 1-tap DFE. In [31], RX equalizer consisting of a CTLE and a 1-tap DFE is realized for 21 Gb/s data-rate for channel loss of 14.9 dB at Nyquist, employing low-frequency and high-frequency equalization gain balancing adaptation method. A low-power RX data-path is demonstrated in [32] with an energy efficiency of 0.23 pJ/b at 25 Gb/s data-rate for 24 dB loss channel at Nyquist. It uses a one-stage CTLE followed by half-rate/quarter-rate current-steering 2-tap DFE.

As data-rate raises ever-higher, closing DFE's feedback loop becomes problematic even with advanced process node. In order to address this, loop-unrolling (also called speculation or look-ahead) technique has been applied to ultra-high-speed DFEs, relaxing the critical-path timing [33, 34, 23, 35, 36, 37, 38, 39, 40]. Each tap-speculating requires  $2^N$  look-ahead cases implemented by current sources and multiplexers (MUX), where N is the number of signaling levels, e.g., N = 2 for NRZ and N = 4 for PAM-4, and the number of look-ahead paths increases

exponentially with the basis N. Hence, loop-unrolling with more than two DFE taps becomes impractical due to an exponential growth of the area and resulting power consumption, especially with PAM-4 which would require 16-paths with only two-tap loop-unrolling. Some RX designs feature 2-tap speculation [34, 33, 39] with two-decision look-ahead.

As the loss at Nyquist increases with the data-rate increase when the transmission medium (channel) remains the same, equalization becomes more and more challenging. To reduce the loss at Nyquist, multi-level pulse-amplitude modulation schemes such as PAM-4 have been used for high-speed data communications. However, PAM-4 is said to be intrinsically three times more sensitive to ISI given same peak-to-peak amplitude, and the TX output driver may suffer from linearity issue [41], and the TX/RX equalizer's complexity becomes more complex than that of NRZ. Nevertheless, the fact that PAM-4 halves the bandwidth by half as compared to NRZ spectrum hence reducing insertion loss and crosstalk power lead many TRX designs supporting PAM-4. For the cases where using PAM-4 can give at least 9.5 dB less insertion loss when compared to the cases using NRZ signaling, prototypes employing PAM-4 signaling effectively demonstrated its feasibility for  $\geq$  25 Gb/s [42, 43, 35], for  $\geq$  56 Gb/s [33, 44, 45, 46, 35, 47], and for 112 Gb/s [24, 25].

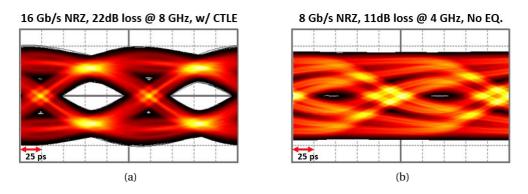

Taking advantage of recent advancement of ADC performance, ADC-based receivers are highly featured. In [48], ADC-based quarter-rate digital 8-tap FFE followed by 8-tap DFE based on 4-tap loop-unrolling and a look-up table (LUT)-based architecture, without analog equalizer has been demonstrated for NRZ RX. Based on a 5-bit 16 GS/s quarter-rate flash ADC, it demonstrated 3.5 pJ/b of energy efficiency at 16 Gb/s data-rate for equalizing 20 dB attenuation at Nyquist. Similar work in [49] including clock and data recovery (CDR) circuit and with added digital gain control function to the FFE shown in [48] demonstrated 25 Gb/s data-rate to equalize 40 dB loss at Nyquist with 8-tap FFE and 8-tap DFE. An NRZ RX with 6-bit 10.3125 GS/s 2-way time-interleaved flash ADC followed by digital 5-tap DFE together with 4-tap TX FFE is presented in [50]. This design incorporates a three-stage peaking amplifier to partially compensate for high-frequency channel attenuation before ADC. In [51], a 10 Gb/s NRZ RX based on 6-bit asynchronous successive approximation register (SAR) ADC embedding 3-tap analog FFE, followed by 3-tap DFE is present. By separating the RX input voltage range into reliable-'0' and reliable-'1' regions, the RX disables part of its equalizer to save power whenever the decisions are in the reliable region resulting in power saving. With the help of two-stage CTLE at the analog front-end (AFE), [52] demonstrated 8-bit 28 GS/s 32way TI-SAR ADC-based RX for 56 Gb/s data-rate with 31 dB attenuation at Nyquist achieving BER of  $10^{-8}$  dissipating 370 mW, where power consumption of digital signal processor (DSP) is not included in the reported number. Another ultra-high-speed ADC-based RX can be found in [53], based on reconfigurable ADC. Having three-stage CTLE followed by a VGA as AFE, the ADC can be configured as either 7-bit mode or 3-bit mode depending on the required equalization effort. It demonstrated that for channels that are easy to equalize, CTLE could practically perform all the required equalization letting the DSP to be bypassed, resulting in significant power saving. [54] presents a 64 Gb/s PAM-4 TRX with both TX/RX equalization, where RX employs a reconfigurable 4-way TI 6-bit flash ADC. For an easy channel, the ADC

can be configured as a 2-bit sampler if CTLE can equalize that channel, while for channels that require RX equalization in addition to TX FFE, ADC can be configured to a 6-bit mode for DSP equalization. However, the DSP is not implemented in [54], but the RX DSP equalization is performed in PC with recorded ADC output data.

### 1.2.2 Multi-Drop Link

Unlike the smoothly-decaying frequency response shape in point-to-point interconnects, multi-drop interconnects exhibits considerable notches in their frequency response [55]. This is because there are multiple possible electrical paths when modules or chips are connected to a bus for communicating between a TX and one of the RXs, which is known as multipath distortion in wireless communications. In time-domain, signals that are arriving at the selected RX after traveling around different paths can cause destructive superposition at certain frequencies depending on the physical feature of the multi-electrical-paths. Due to the destructive superposition, the energy of the received signal has been significantly reduced as compared to the transmitted energy, that is translated into spectrum notches in frequency-domain. A typical example of multi-drop bus (MDB) is dynamic random access memory (DRAM) interface as main system memory, where multiple DIMMs are connected to a controller without matched impedance. Also, the interface between NAND-flash memory controller and stacked NAND dies is MDB. Often time, such reflections exhibit long-tail post-cursors in the pulse response, necessitating DFE to effectively cancel them out if the first reflective frequency comes below the Nyquist frequency of the transmitted signal. However, even without speaking about being power hungry, implementing such equalization is challenging since CMOS memory process technologies for DRAM manufacturing only offers low-cost and slow devices.

To overcome the technology-limited DRAM interface performance, various efforts have been investigated. In [56], analog multi-tone (AMT) signaling is employed to allocate the transmit power avoiding channel notches efficiently. By transmitting 2.5 Gb/s NRZ at baseband with 5 Gb/s quadrature phase-shift keying (QPSK)-modulated RF band, the prototype in [56] demonstrated 7.5 Gb/s data transmission over MDB that exhibits the first notch at 2.5 GHz with 40 dB loss. With the same signaling scheme, the prototype shown in [57] demonstrated 9 Gb/s per lane data-rate for the same type of channel with four parallel data bus with source synchronous clocking. Measurement results in [57] proved the far-end crosstalk reduction capability of the AMT signaling for dense MDB interconnects. [58] proposed baseband + RF-bands signaling similar to [56, 57] with higher RF-bands' constellation order. While the proposed TX in [58] can efficiently transmit energy in terms of power, the proposed signaling scheme requires a 4-bit DAC and ADC per sub-band, respectively for TX and RX. Moreover, if the first notch in channel frequency response is located at a lower frequency, AMT becomes impractical with an increased number of sub-channels that are required for communicating at a fixed aggregated data-rate. Above-mentioned works all use differential signaling, which is not preferred in DRAM interfaces due to its pin-inefficiency. Phase-difference modulation

scheme that modulates each clock edge by data information is proposed in [59]. While being able to be configured as a single-ended mode for 7.8 Gb/s/pin data-rate, the prototype in [59] demonstrated 2 pJ/b energy efficiency for data transmission over 2-drop MDB.

### 1.3 Contributions and Thesis Organization

In high-speed wireline TRX systems, among different equalization circuits, time-domain equalizers such as FFE and DFE analyze wireline TRX response in time-domain and apply equalization in time-domain. Frequency-domain equalizer such as CTLE views channel response in frequency-domain and applies equalization in the same domain. Moreover, most of the widely-researched signaling schemes are time-domain signaling such as NRZ/PAM-4. Particularly in MDB interfaces, communicating with time-domain signaling (NRZ/PAM-N at baseband) combined with frequency-domain signaling (QPSK/16-level quadrature-amplitude modulation (16-QAM) or 256-QAM at RF-bands) were explored by analyzing channel in frequency-domain point of view. This thesis contributes to two wireline TRX sub-domains with different approaches: point-to-point link and MDB interfaces.

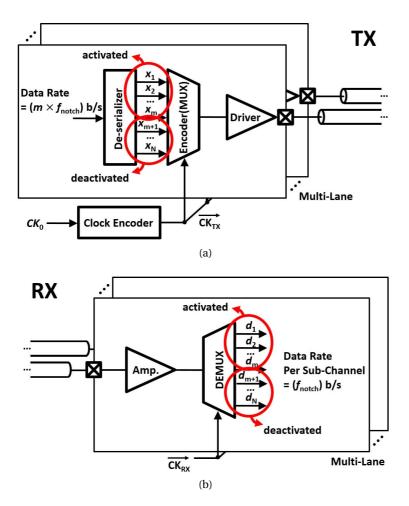

- For MDB interfaces, instead of analyzing the system and applying signal processing in the same domain (either in time-domain or frequency-domain), this thesis analyzes the MDB TRX system in frequency-domain and propose a time-domain signaling scheme. By doing so, the proposed signaling scheme demonstrates greater bandwidth improvement compared to conventional time-domain equalization-based systems, with greater architectural simplicity as compared to systems employing frequency-domain signaling. A TX employing the proposed signaling scheme is demonstrated by measurement using programmable DAC with MDB board.

- For point-to-point interconnect with a highly lossy channel, this thesis proposes AMT signaling of which each frequency-domain sub-channel spectrum is single-sideband (SSB). The proposed scheme uses the channel's frequency response inversion property by up/down-conversion by analog mixers in TX/RX respectively. By doing so, the RX does not require any of FFE/CTLE/DFE for receiving at data-rate that is much greater than it would be possible without the presence of equalizers with time-domain signaling. Moreover, since the proposed signaling divides aggregate data-rate into using multiple frequency-domain sub-bands, the TRX's data-path can operate at sub-band-rate with relaxed timing. The proposed TRX is demonstrated by system-level measurement using oversampling DAC and ADC as TX and RX respectively, where up/down-conversions and filtering are performed in PC with oversampling to mimic analog behavior.

- For ultra-high-speed point-to-point link, e.g., 56 Gb/s, discrete multi-tone (DMT) (or called orthogonal frequency division multiplexing (OFDM) in wireless communications fields) modulation is employed. The RX is implemented in fully-digital circuits

following ADC without any analog equalizer in AFE. Unlike time-domain signaling that necessitates symbol-by-symbol feedback using DFE, OFDM enables parallel circuit implementation allowing the RX circuit to benefit from nanosecond-order critical path delay. A prototype RX chip including ADC and fully-synthesized digital RX is implemented in 14 nm FinFET process technology and demonstrated less than 3 pJ/b RX energy consumption at 56 Gb/s data-rate with BER  $\leq 10^{-6}$  for channel exhibiting 18 dB loss at 14 GHz. This is the fastest reported DMT RX implemented in FinFET process with lowest energy-per-bit for electrical links.

• Another ADC-based RX for PAM-4 is proposed. Instead of time-domain symbol-by-symbol equalization, the proposed RX transforms a collection of consecutive time-domain received symbols into frequency-domain by Fourier transform and apply frequency-domain equalization. The frequency-domain-equalized symbols are then transformed-back into time-domain to reconstruct original time-domain PAM-4 data. Since time-domain circular convolution is equivalent to frequency-domain symbol-by-symbol multiplication in frequency-domain, the proposed method relaxes feedback equalizer's critical path with the help of domain-transformations and technique to make circular convolution equivalent to linear convolution. The proposed RX has demonstrated its feasibility to lossy wireline interfaces with 25 dB loss at 14 GHz channel by architectural modeling with register-transfer-level (RTL)-modeled RX.

The remaining parts of the thesis are organized as follows.

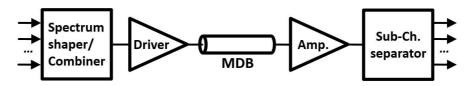

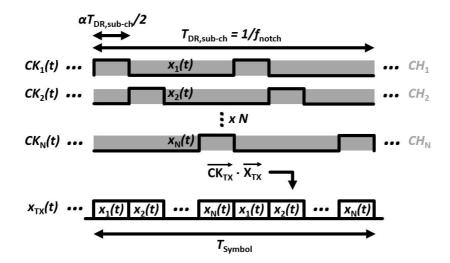

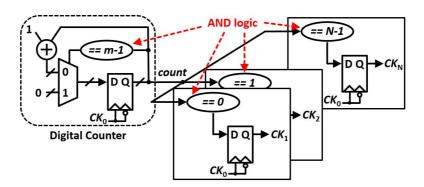

Chapter 2: Digital Spectrum Shaping Signaling In this chapter, a simple digital encoding scheme that shapes the transmitted signal's spectrum to mitigate energy loss caused by MDB frequency-domain notches is presented. The limitations of using NRZ signaling for MDB interfaces are analyzed, then the concept of digital spectrum shaping signaling is proposed. While the signaling scheme is proposed based on frequency-domain analysis, its time-domain behavior in reducing ISI/crosstalk is then analyzed. Then, a potential circuit implementation example is shown, followed by simulation results with measured MDB channel S-parameter. Measurement results using programmable DAC as TX for the proposed scheme are presented, and an enhanced modulation scheme is then introduced with pulse-response analysis, TX/RX design example, and simulation results, followed by a conclusion.

Chapter 3: Single-Sideband Analog Multi-Tone Signaling This chapter presents AMT signaling TRX architecture with SSB sub-channels for communication through lossy channels. Lossy-channel's self-equalization mechanism with RF up/down-conversion of upper-sideband-suppressed RF signal is analyzed. The proposed AMT/SSB TRX architecture is then shown with inter-channel-interference (ICI) analysis for RF sub-channels. Practical design considerations are discussed, then simulation results with measured S-parameter of example channel are shown. To demonstrate the feasibility of the proposed system, measurement results with oversampling DAC/ADC-based example system with digital pre-/post-processing in PC are presented followed by a conclusion.

**Chapter 4: ADC-Based Wireline Receiver With Discrete Multi-Tone Signaling** This chapter presents fully-digital ADC-based wireline RX with DMT modulation. While an 8-bit DAC is used as DMT TX with programmable data memory block, a TX architecture considered for generating equivalent DMT test sequence is presented. Then, the RX implementation details and measurement results under various conditions are shown. The full TRX system performance is compared with previous works followed by a conclusion.

**Chapter 5: ADC-Based Fully-Digital PAM-4 Receiver** This chapter presents a fully-digital ADC-based PAM-4 RX without the presence of analog front-end. It starts by reviewing basic high-speed wireline TRX architecture. Then, a frequency-domain equalization technique of the time-domain signal is presented. Simulation results and DSP implementation results are then shown, followed by a conclusion.

## 2 Digital Spectrum Shaping Signaling

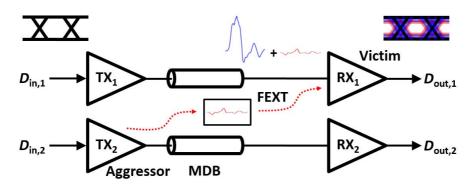

<sup>1</sup> This chapter presents a spectrum shaping signaling scheme and the corresponding transceiver architecture. The proposed signaling scheme can considerably reduce ISI and far-end crosstalk (FEXT) in MDB interfaces. The proposed TRX architecture features digital-style implementation rather than analog-based approach, which can provide a versatile and power-efficient silicon implementation. Moreover, the noise induced by FEXT can be greatly reduced by employing the proposed digital spectrum shaping signaling, and the TRX can customize to the communication channel by simple configuration while the aggregate data-rate is unchanged.

### 2.1 NRZ Signaling for Multi-Drop Interfaces

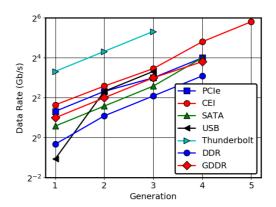

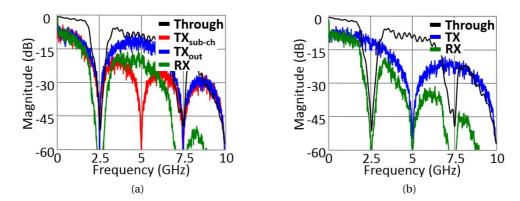

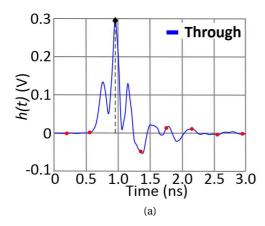

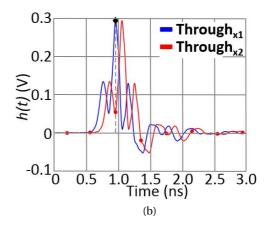

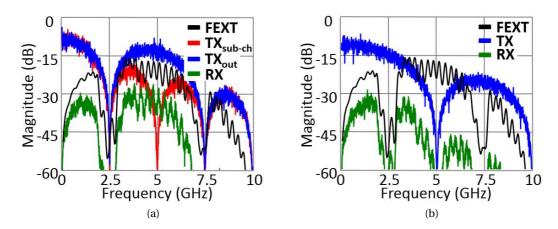

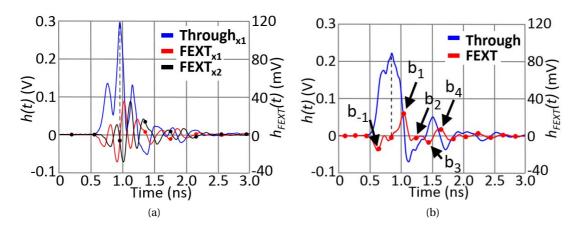

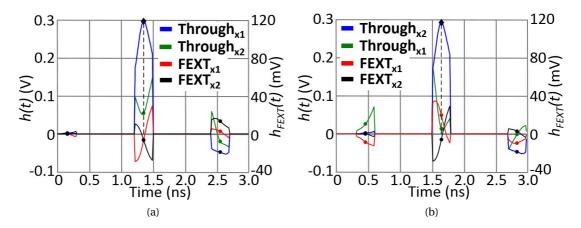

A multi-drop channel has its frequency notches at all odd multiples of  $f_{\rm notch}$  where  $f_{\rm notch}$  is the first notch frequency of a given multi-drop channel [62]. Fig. 2.1(a) shows measured through and FEXT frequency responses of an example 12-inch FR-4 MDB, with  $f_{\rm notch} = 2.5$  GHz [56]. The multi-path reflections cause long post-cursors on the pulse response as shown in Fig. 2.1(b), resulting in significant ISI. This example channel exhibits 45 dB attenuation at  $f_{\rm notch}$  due to the disruptive superposition of the main and reflected signals at RX front-end, making the RX difficult to equalize the channel.

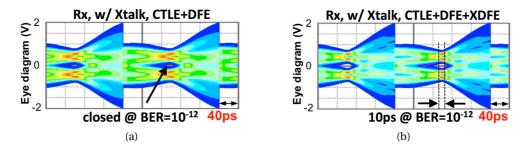

The nulls of the power spectrum of a random NRZ stream are located at  $n/T_{\rm b}$  where n is an integer number and  $T_{\rm b}$  is one-bit pulse duration [63]. Transmitting NRZ data stream over a channel that bears a notch around the Nyquist frequency necessitates complex equalizer including DFE with many number of taps to cancel out the reflected signals [56]. Although the MDB shown in Fig. 2.1(a) exhibits only 4 dB insertion loss at Nyquist for 5 Gb/s data-rate, the received eye diagram is closed due to the reflections.

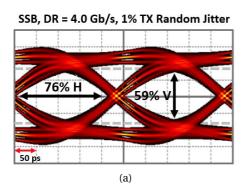

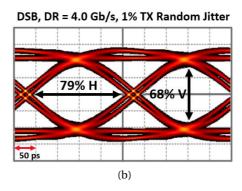

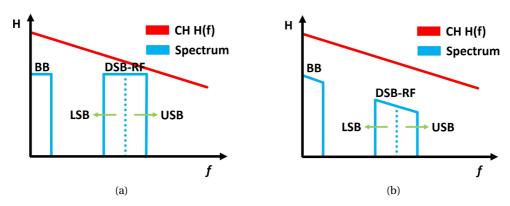

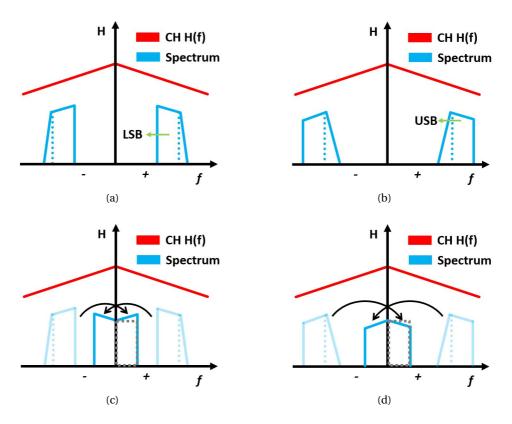

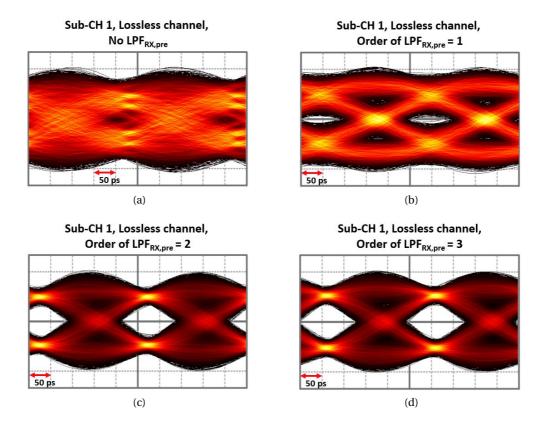

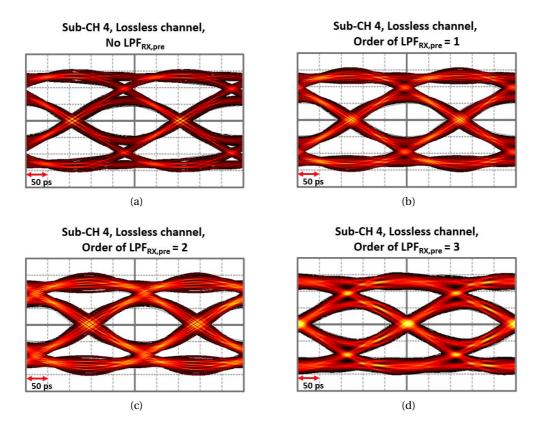

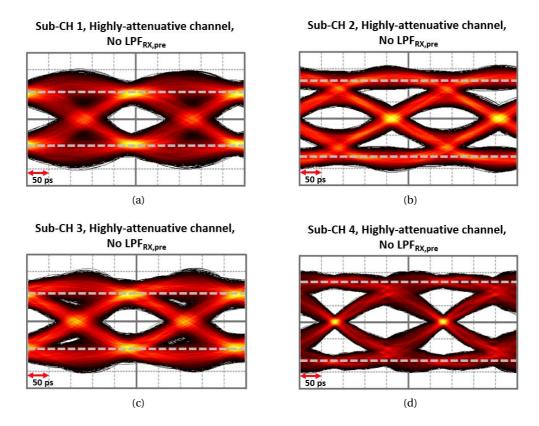

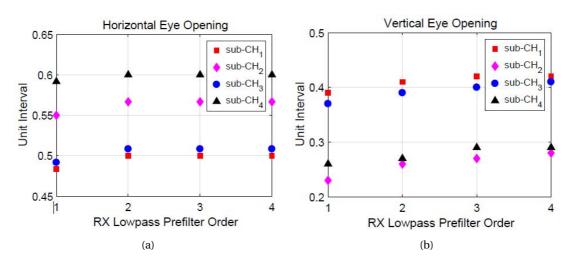

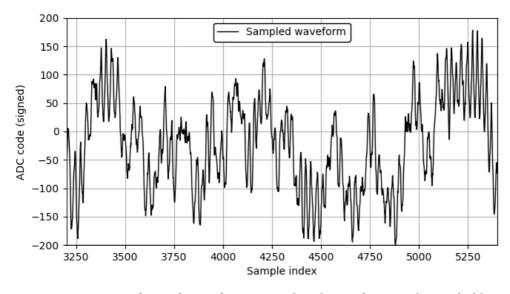

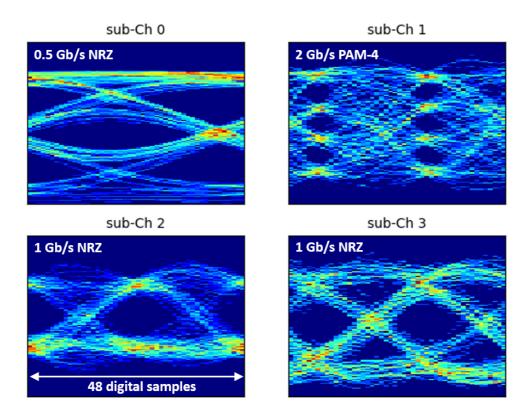

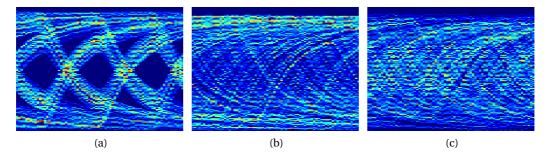

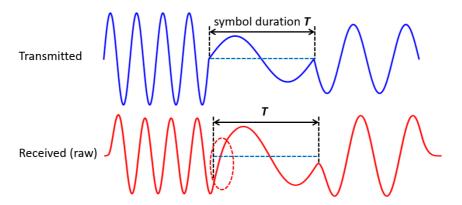

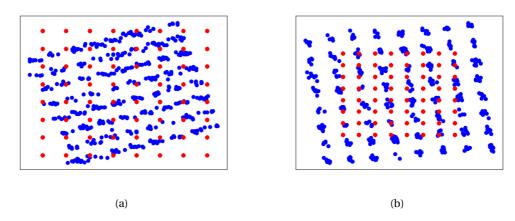

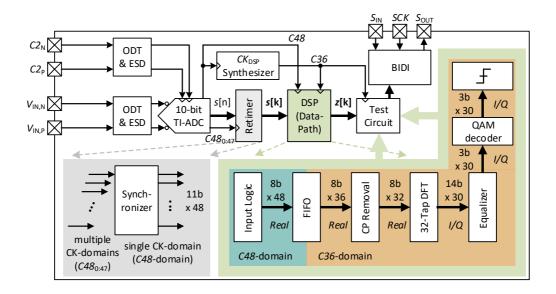

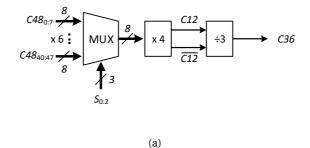

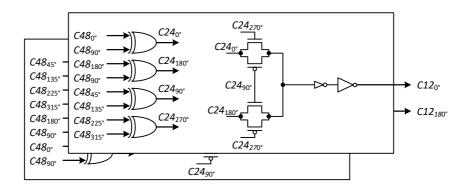

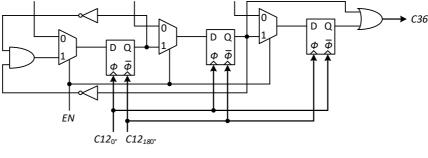

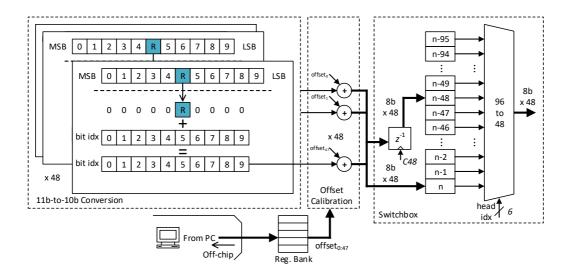

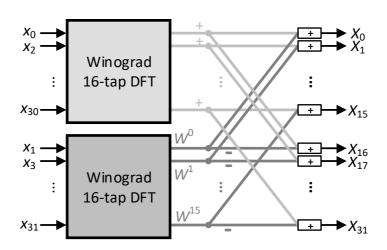

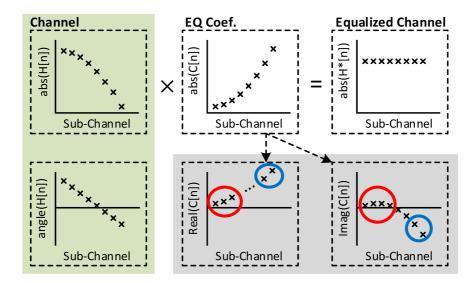

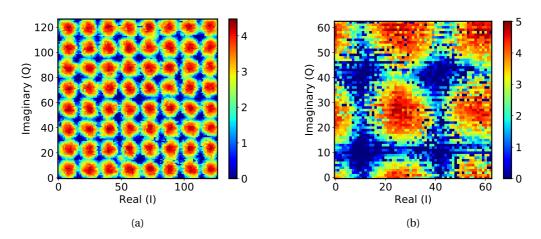

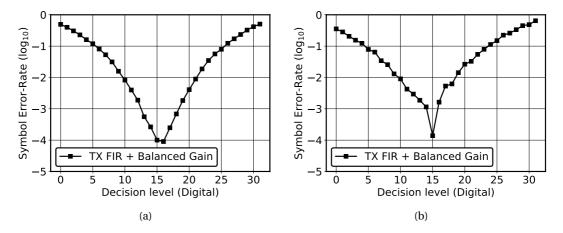

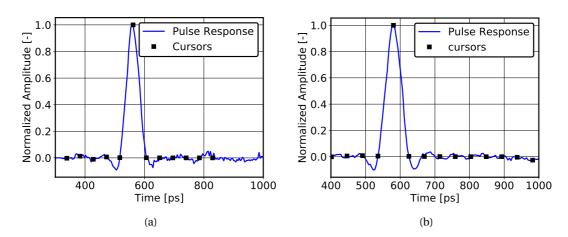

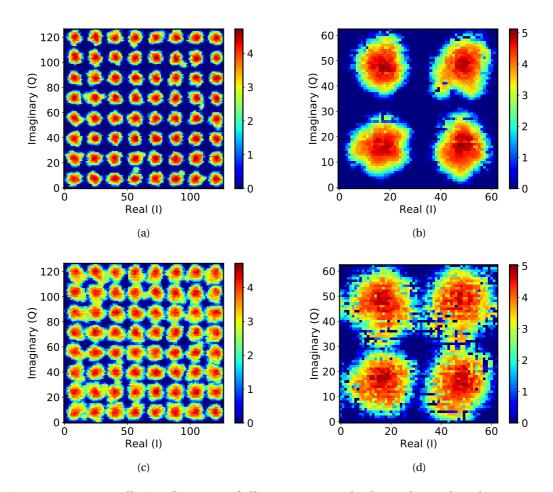

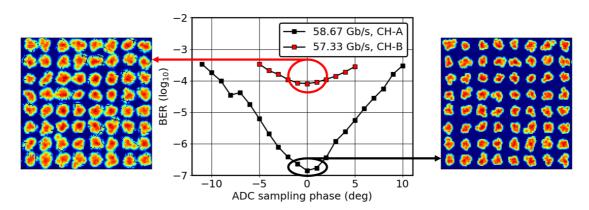

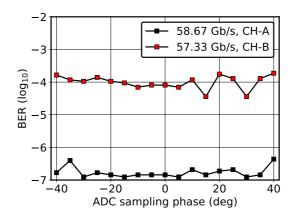

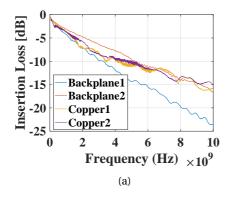

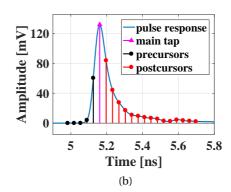

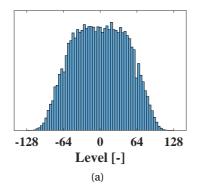

<sup>&</sup>lt;sup>1</sup>The contents of this chapter is based on: G. Kim, K. Gharibdoust, A. Tajalli, and Y. Leblebici, "A digital spectrum shaping signaling serial-data transceiver with crosstalk and ISI reduction property in multi-drop interfaces,", *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 63, no. 12, pp. 1126–1130, Dec. 2016 (©IEEE) [60] and G. Kim, C. Cao, K. Gharibdoust, A. Tajalli, and Y. Leblebici, "A time-division multiplexing signaling scheme for inter-symbol/channel interference reduction in low-power multi-drop memory links,", *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 64, no. 12, pp. 1387–1391, Dec. 2017 (©IEEE) [61].