# High voltage metal oxide thin film transistors to drive arrays of dielectric elastomer actuators

THÈSE Nº 8738 (2018)

PRÉSENTÉE LE 13 JUILLET 2018 À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR LABORATOIRE DES MICROSYSTÈMES SOUPLES PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

## ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

## Alexis Pierre Henri MARETTE

acceptée sur proposition du jury:

Prof. L. G. Villanueva Torrijo, président du jury Prof. H. Shea, Dr D. Briand, directeurs de thèse Prof. S. Seelecke, rapporteur Dr F. Zanella, rapporteur Prof. E. Charbon, rapporteur

Chacun ramasse à terre un caillou, et le jette dans le feu. Ce caillou s'appelle dès lors : Anaon. — Anatole Le Braz

A la mémoire de mon grand-père, André Marette.

# Acknowledgements

I would like to express my most sincere gratitude to Prof. Herbert Shea who gave me the opportunity to work on this challenging topic in his laboratory. Thank you for your availability, and your multiple suggestions for improvement. I learned a lot from them.

I am deeply thankful to Dr. Danick Briand for having followed my progress in the last four years with dedication. His scientific inputs and discussion were precious and helped a lot. Thank you for having shared with me your experience and your energy.

I am grateful to the members of my PhD jury, Prof. Guillermo Villanueva, Prof. Edoardo Charbon, Prof. Stefan Seelecke and Dr. Frederic Zanella for having accepted to read and evaluate this thesis.

Special thanks to Nadine Besse, Christine de Saint-Aubin, Giorgio Mattana, Alexandre Poulin, Samuel Rosset, Sam Schlatter, Xiaobin Ji, Dan Courtney, Matthias Imboden, Alessio Mancinelli and Peter van der Waal whose help and collaboration were critical for the success this project. I have a big thought also for Rubaiyet Haque, Etienne Lemaire and Seun Araromi, my office mates in the last 4 years, who had to bear my apocalyptic disorder. They were always supporting and I had with them very interesting and enthusiastic discussions. I also acknowledge Mathilde Rieu (Ecole des Mines de Saint Etienne), Pierre Mettraux (EPFL-MHMC), Gizem Nogay (EPFL-PVLAB), Olha Sereda (CSEM Neuchâtel), Ivan Marozau (CSEM Neuchâtel), and the CMi staff in Lausanne for their help and support for fabrication and material characterization. I owe a big favor to Aymeric Schafflützel and Olexandr Gudozhnik, who designed and improved Bertha that has since then characterized so many devices, part of which are included in this thesis. I also want to thank Daniel Ruedin for teaching me the basics of labview, which proved to be very useful for the rest of my project.

To current and previous lab members, Juan Zarate, Anna Kamolwat, Andres Vasquez-Quintero, Francisco Molina-Lopez, David McCoul, Bekir Aksoy, Ulas Adiyan, Saleem Khan, Ronan Hinchet, Vito Cacucciolo, Marianna Fighera, Edouard Leroy, Martin Lubej, Ryan van Dommelen, Francesca Sorba, Jules Heldens, Simon Dandavino, Jun Shintake, Luc Maffli, Subha Chakraborty, Malick Camara, Teru Akiyama, Joanna Bitterli, Silvia Demuru and Anthony Ruch, to James, Keyvan, Olivier and Julien, to Myriam Poliero who has been so amazing and patient at helping me with administrative tasks, to the structural mechanics team, I cannot express how grateful I am to have made LMTS, Microcity, EPFL such a great place to work in, in the last four years.

#### Acknowledgements

I am also indebted to my friends, whose encouragements have been critical to advance. In particular, I would like to thank my old friend Antoine. Our encounters in Paris are like a long lost island I like always to rediscover with my children eyes. I would like to thank Vincent, whose generosity and craziness have been a compass since I entered engineer school. Also, special thanks to the (ex-)Grenoblois, Cédric, Mathieu, Matt, Lucie, Nicolas, Benjamin, Bastien, Antoine, Laetitia, Alex, Ambre, Guillaume, Marine, and Christian. I would like to thank my fellow Rock Affinity members and partners for their friendship and the dances we shared, which have been a breath of fresh air every Wednesday for the last four years.

I acknowledge also the Lakeshore speakers, the Toastmaster club of Neuchâtel and their presidents Kathrin, Helene and Caroline for having accepted me as a member and helped me to improve my public speaking skills.

To my family, especially my mother, Véronique, and my father, Pierre, thank you for your love, your support, your generosity, your curiosity and for trying to understand what I have been working on in the last 4 years. I would like to thank my brother Grégoire, for corrupting my writing sessions with music and concerts - Mahler helped a lot to start writing this thesis. I am also grateful to Constance, whose willpower and obstacle-crushing enthusiasm have been inspiring every day to achieve my goals.

Finally, I would like to thank my girlfriend, Alyssia, for her unconditional and unlimited support, for having always been positive and patient. Thank you for having brought your gentleness into my life in this last year. It has played a huge role in this achievement. I am also grateful to her family for having been encouraging during the preparation of this manuscript.

A vous tous, merci!

Neuchâtel, June 21, 2018

Alexis

# Abstract

This thesis advances the field of high-voltage thin film transistors (HVTFTs) and dielectric elastomer actuators (DEAs) by demonstrating a strategy for low-voltage addressing of an array of high voltage soft actuators suspended on a flexible substrate.

First, I present the first HVTFTs operating at 1 kV drain-source voltage, switching with an on-off ratio of 20 at 80 V gate-source voltage. The HVTFTs can operate at high voltage thanks to geometrical features increasing the breakdown voltage: a thick gate dielectric composed of a bilayer of alumina (100 nm) and Parylene-C (1  $\mu$ m), a long semiconducting channel (500  $\mu$ m), and a 150  $\mu$ m long non-gated region between the drain and the gate electrode called the offset gate. The use of an amorphous oxide semiconductor (AOS), zinc tin oxide (ZTO), enables a high on-currents of 0.1 mA. The ZTO was synthesized by a sol-gel process after spin-coating on a flexible polyimide substrate, previously passivated with alumina. I optimized the HVTFT switching properties by doping the ZTO layer with yttrium (5%). It improved the on-off ratio up to 1000 at 500 V operation voltage by decreasing the leakage current down to 100 nA.

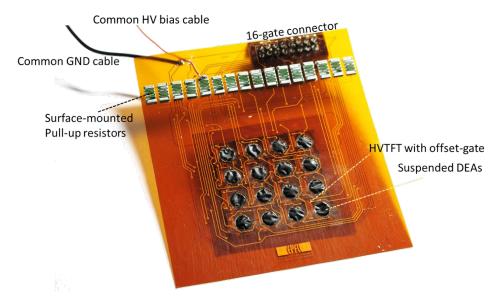

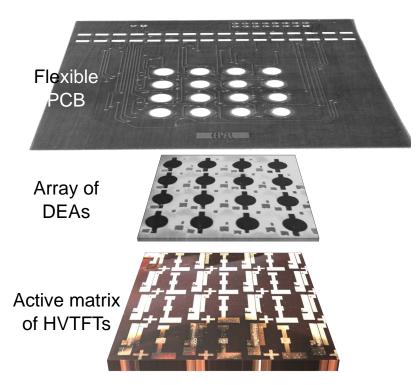

Then, I show the first integration of HVTFTs with DEAs. My ZTO HVTFTs switch DEAs on and off with only 30 V gate voltage under a bias voltage of 1.4 kV. The system time response in 50 ms. The demonstrator is a 4x4 array of diaphragm DEAs. A layer of 4x4 DEAs is suspended over a layer of 4x4 HVTFTs built on flexible polyimide. The DEAs and the HVTFTs were interconnected thanks to a flexible PCB in a resistive load inverter circuit architecture. A flexible 3D printed chamber was constantly biasing the DEA diaphragms with a back-pressure. The DEAs were made of PDMS and the active region is defined by overlapping carbon-PDMS electrodes. The device operates down to a 5 mm radius of curvature.

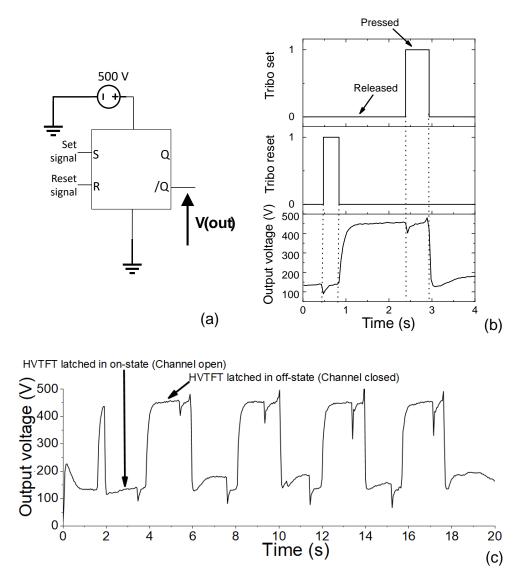

Finally, I demonstrate latching of the HVTFT and the DEA by using triboelectric sensors. Under a constant 500 V circuit bias, the control of the HVTFT gate with triboelectric generators enabled 4s latching of the inverter output voltage at 470 V for the off-state and at 120 V for the on-state. The latching of the DEAs with the HVTFT circuit finally proves that this approach can lead to a bistable control of DEAs.

This PhD thesis results show that my HVTFTs are versatile components usable not only to

#### Abstract

address DEAs but also to interface low voltage sensors with high voltage actuators.

**Keywords:** thin film transistors, high voltage, amorphous oxide semiconductor, zinc tin oxide, dielectric elastomer actuators, haptic display, triboelectric generator, electromechanical latching.

# Résumé

Les travaux défendus dans cette thèse impactent deux thématiques de recherche : Celles des transistors à films fins de haute tension (HVTFTs) et des actionneurs à élastomère diélectrique (DEAs). J'y présente une stratégie pour contrôler des matrices d'actionneurs souples à haute-tension sur substrat flexible.

Dans un premier temps, je démontre les premiers HVTFTs opérationnels à une tension drainsource de 1 kV. Le rapport de courant on-off est de 20 et la commutation s'effectue sur un intervalle de 80 V à la grille. Quelques optimisations géométriques ont été effectuées, lesdites optimisations entrainant une augmentation de la tension de claquage du HVTFT : J'ai utilisé un diélectrique de grille épais, composé d'une double-couche d'alumine (100 nm) et de Parylène-C (1  $\mu$ m). Le canal semiconducteur est long, sa taille est de 500  $\mu$ m et l'électrode de grille a été décalée de 150  $\mu$ m par rapport au drain. Cette modification est appelée grille en décalage ou offset gate selon la terminologie anglaise. L'utilisation d'un semiconducteur en oxyde amorphe (AOS), l'oxyde de zinc étain (ZTO) comme canal de transistor procure un courant de canal de 0.1 mA à l'état on. Le ZTO a été synthétisé par un procédé sol-gel sur un substrat en polyimide préalablement passivé à l'alumine. J'ai optimisé ce semiconducteur en le dopant avec de l'yttrium (5%). Le rapport on-off s'est amélioré et est monté à 1000 pour une tension d'opération de 500 V et ce, grâce à une diminution des courants de fuite du transistor à 100 nA.

Dans un deuxième temps, je présente la première intégration de HVTFTs avec des DEAs. Mes transistors en ZTO parviennent à commuter les DEAs sur un intervalle de 30 V de tension de grille, sous une alimentation générale de 1.4 kV. Le temps de réponse du système est de 50 ms. Mon démonstrateur est une matrice 4x4 membranes DEAs suspendue au-dessus d'un substrat de 4x4 HVTFTs sur polyimide. Un PCB flexible connecte HVTFTs et DEAs dans une configuration électronique d'inverseur résistif. Une chambre flexible imprimée 3D, permet la mise sous pression constante des membranes actives. Celles-ci sont faites en PDMS et leur région active est définie par deux électrodes étirables en silicone carboné. Le dispositif fonctionne jusque un rayon de courbure minimal de 5 mm.

Dans un dernier temps, je démontre le verrouillage de l'état du HVTFT et du DEA en utilisant

#### Abstract

des capteurs triboélectriques. Sous une alimentation constante de 500 V, on peut contrôler la tension de grille des HVTFTs via les dispositifs triboélectriques et verrouiller pendant quatre secondes la tension de sortie de l'inverseur à 470 V lorsque le transistor est bloquant, et à 120 V quand ce dernier est passant. Leur verrouillage par l'intermédiaire du HVTFT et des capteurs triboélectriques démontre que cette approche mène à un contrôle bistable des DEAs.

Les résultats de ma thèse de doctorat montrent que ces HVTFTs sont des composants polyvalents utilisables non seulement pour contrôler des matrices d'actionneurs, mais aussi pour permettre d'interfacer ces derniers avec des capteurs basse tension.

**Mots clefs :** Transistors film fin, haute tension, semiconducteur en oxyde amorphe, oxyde de zinc étain, actionneur à élastomère diélectrique, écran haptique, générateur triboélectrique, verrouillage électromécanique.

# Contents

| A  | Acknowledgements |                                                                             |    |

|----|------------------|-----------------------------------------------------------------------------|----|

| A  | Abstract         |                                                                             |    |

| R  | Résumé           |                                                                             |    |

| Li | st of            | Figures                                                                     | xi |

| Li | st of            | Tables                                                                      | xv |

| 1  | Intr             | oduction                                                                    | 1  |

|    | 1.1              | Background and motivation                                                   | 1  |

|    | 1.2              | Thesis objectives                                                           | 3  |

|    | 1.3              | Thesis outline and contribution                                             | 3  |

|    | 1.4              | Impact of this thesis                                                       | 5  |

| 2  | Die              | lectric elastomer actuators                                                 | 7  |

|    | 2.1              | Definition and properties of the DEA                                        | 8  |

|    |                  | 2.1.1 Basic structure and definition                                        | 8  |

|    |                  | 2.1.2 DEAs, high strain, compliance and high speed actuators                | 9  |

|    |                  | 2.1.3 Operation modes                                                       | 10 |

|    | 2.2              | Working principle                                                           | 12 |

|    |                  | 2.2.1 Dielectric elastomer actuation                                        | 12 |

|    |                  | 2.2.2 Actuation of DEAs under a low strain                                  | 13 |

|    |                  | 2.2.3 Failure mechanisms                                                    | 14 |

|    | 2.3              | Materials for DEAs                                                          | 15 |

|    |                  | 2.3.1 Elastomer membrane                                                    | 15 |

|    |                  | 2.3.2 Stretchable electrodes                                                | 15 |

|    | 2.4              | Example of DEA applications requiring integrated addressing                 | 17 |

|    |                  | 2.4.1 Haptic displays                                                       | 17 |

|    |                  | 2.4.2 Soft robots                                                           | 18 |

|    | 2.5              | Reducing the operation voltage of DEAs vs addressing high voltage DEAs with |    |

|    |                  | low-voltage switches                                                        | 20 |

#### Contents

| 3 | Hig               | h volta | ge thin film transistors: fundamentals and technologies               | 21              |

|---|-------------------|---------|-----------------------------------------------------------------------|-----------------|

|   | 3.1               | Intro   | duction to TFT technology                                             | 22              |

|   |                   | 3.1.1   | MOSFETs and TFTs                                                      | 22              |

|   |                   | 3.1.2   | TFT channel technologies                                              | 23              |

|   | 3.2               | TFTs    | working principle                                                     | 25              |

|   |                   | 3.2.1   | TFT characteristics                                                   | 25              |

|   |                   | 3.2.2   | Quantifying TFT performance                                           | 26              |

|   | 3.3               | High    | voltage thin film transistors                                         | 27              |

|   |                   | 3.3.1   | Introduction to the HVTFTs                                            | 27              |

|   |                   | 3.3.2   | HVTFTs state-of-the-art                                               | 28              |

|   | 3.4               | High    | electric field effects and failure modes for HVTFTs                   | 35              |

|   |                   | 3.4.1   | Dielectric breakdown                                                  | 35              |

|   |                   | 3.4.2   | Channel failure and high electric field effects                       | 35              |

|   |                   | 3.4.3   | Failure mechanisms of the different high voltage thin-film transistor |                 |

|   |                   |         | (HVTFT) technologies                                                  | 39              |

| 4 | Com               |         |                                                                       | 40              |

| 4 | <b>Con</b><br>4.1 | -       | nd design of a HVTFT to drive DEAs                                    | <b>43</b><br>44 |

|   | 4.1               | -       | Circuit to drive a DEA with a HVTFT                                   | 44<br>44        |

|   |                   |         |                                                                       | 44<br>45        |

|   |                   |         | Achieving DEA actuation with minimal voltage variation                |                 |

|   | 4.0               |         | HVTFT requirements                                                    | 47<br>52        |

|   | 4.2               | -       | n of the amorphous oxide semiconductor channel                        | 52              |

|   |                   | 4.2.1   | Introduction on amorphous oxide semiconductors                        | 52              |

|   |                   | 4.2.2   | Zinc oxide based alloys                                               | 53              |

|   |                   | 4.2.3   | Description of the sol-gel process of AOS                             | 56              |

|   | 4.0               |         | In this work: Zinc tin oxide                                          | 57              |

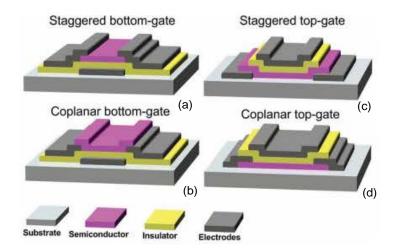

|   | 4.3               |         | IVTFT architecture                                                    | 58              |

|   |                   |         | Electrodes architecture                                               | 58              |

|   |                   | 4.3.2   | Substrate                                                             | 59              |

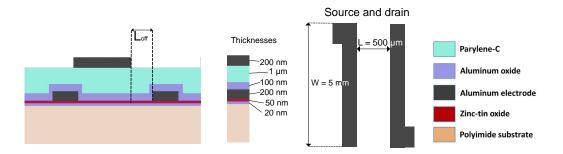

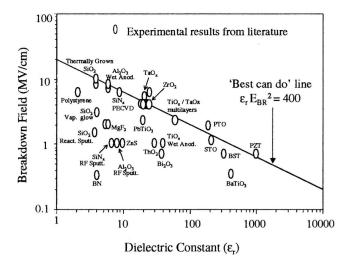

|   |                   |         | Dielectric                                                            | 60              |

|   |                   | 4.3.4   | Electrodes                                                            | 62              |

| 5 | Fab               | ricatio | n, characterization and optimization of ZTO HVTFTs                    | 65              |

|   | 5.1               | Valida  | ation of amorphous zinc tin oxide synthesis                           | 67              |

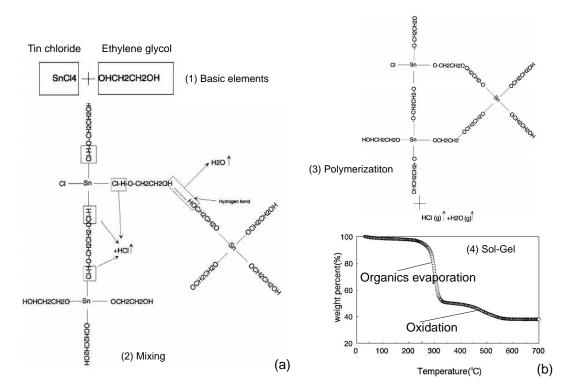

|   |                   | 5.1.1   | Characterization of the sol-gel reaction by TGA and DSC               | 67              |

|   |                   | 5.1.2   | Characterization of the zinc tin oxide chemical composition by XPS    | 68              |

|   |                   | 5.1.3   | Validation of amorphicity by XRD analysis                             | 71              |

|   |                   | 5.1.4   | Discussion                                                            | 71              |

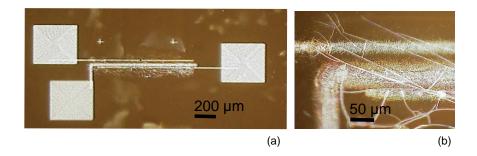

|   | 5.2               | HVTF    | T process flow                                                        | 73              |

|   |                   | 5.2.1   | Substrate and alumina coating                                         | 73              |

|   |                   | 5.2.2   | Semiconductor deposition                                              | 74              |

|   |                   | 5.2.3   | Dielectric deposition                                                 | 74              |

|   |                   | 5.2.4   | Electrodes deposition                                                 | 74              |

|   |      | 5.2.5  | Post-annealing bake                                                       | 74  |

|---|------|--------|---------------------------------------------------------------------------|-----|

|   | 5.3  | Trans  | istor electrical characteristics: Results and discussion                  | 75  |

|   |      | 5.3.1  | Characterization setup                                                    | 75  |

|   |      | 5.3.2  | Analysis methodology                                                      | 78  |

|   |      | 5.3.3  | HVTFT characteristics                                                     | 79  |

|   |      | 5.3.4  | Discussion                                                                | 84  |

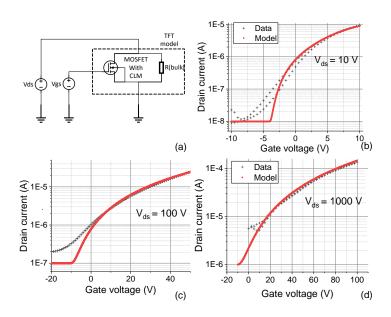

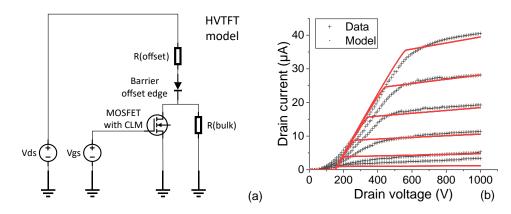

|   | 5.4  | Mode   | ling the HVTFT                                                            | 85  |

|   |      | 5.4.1  | LT-spice model for the HVTFT                                              | 85  |

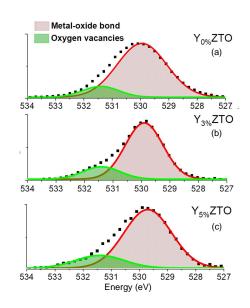

|   | 5.5  | Optin  | nization of ZTO by yttrium doping                                         | 88  |

|   |      | 5.5.1  | Adding Yttrium in the ZTO semiconductor                                   | 88  |

|   |      | 5.5.2  | Synthesis                                                                 | 88  |

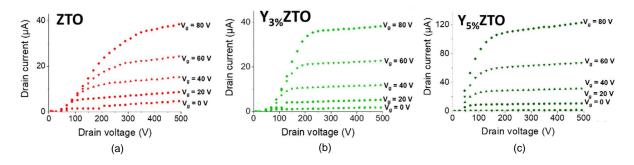

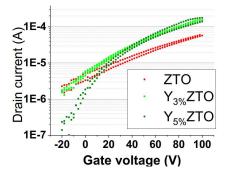

|   |      | 5.5.3  | Fabrication and electrical characterization of ZTO and YZTO HVTFTs        | 89  |

|   | 5.6  | Persp  | ectives: Fully inkjet printed HVTFTs                                      | 91  |

| 6 | Inte | gratio | n of HVTFTs with DEAs                                                     | 93  |

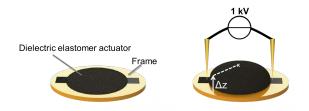

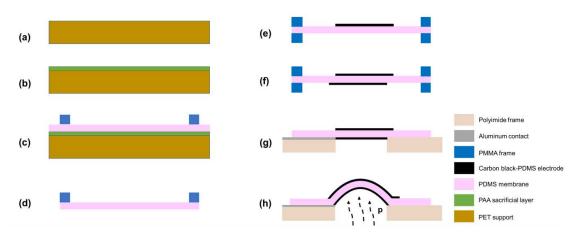

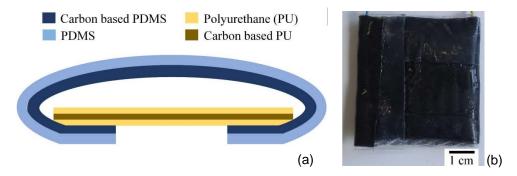

|   | 6.1  | DEA c  | lesign and fabrication                                                    | 95  |

|   |      | 6.1.1  | Operation                                                                 | 95  |

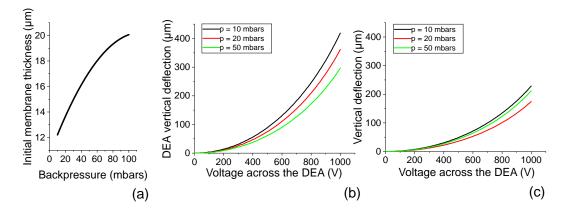

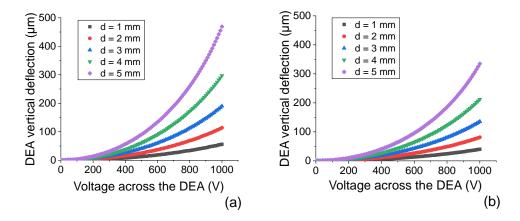

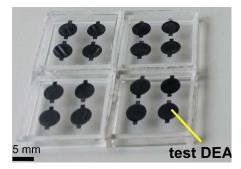

|   |      | 6.1.2  | Design                                                                    | 96  |

|   |      | 6.1.3  | Fabrication                                                               | 98  |

|   |      | 6.1.4  | Characterization                                                          | 99  |

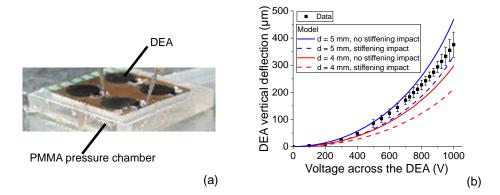

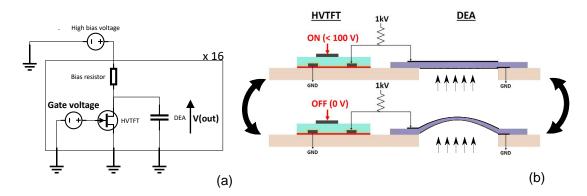

|   | 6.2  | Circui | it design to address DEAs with HVTFTs                                     | 101 |

|   |      | 6.2.1  | Circuit architecture                                                      | 101 |

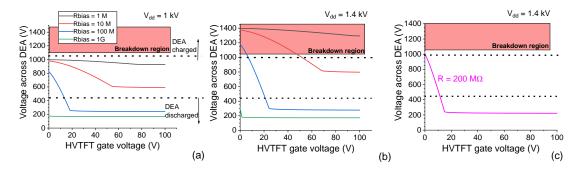

|   |      | 6.2.2  | Choice of bias resistor                                                   | 101 |

|   | 6.3  | Proof  | of concept design, fabrication and characterization                       | 104 |

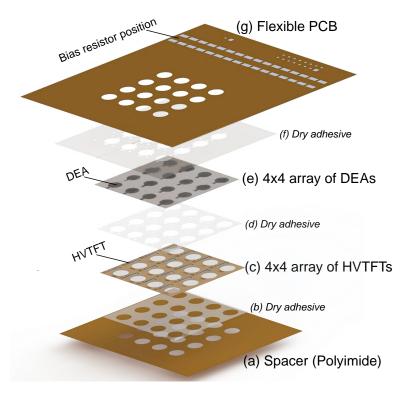

|   |      | 6.3.1  | Design                                                                    | 104 |

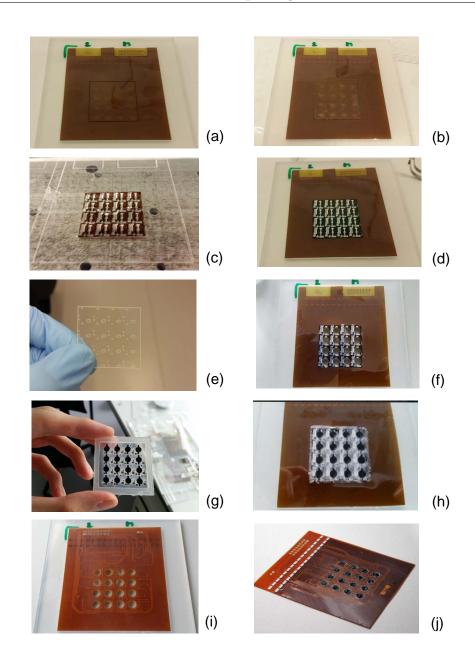

|   |      | 6.3.2  | Process                                                                   | 104 |

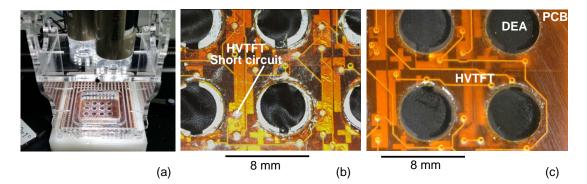

|   |      | 6.3.3  | Challenges                                                                | 106 |

|   |      | 6.3.4  | Deflection response to the gate voltage                                   | 107 |

|   |      | 6.3.5  | Operation under bending                                                   | 108 |

| 7 | Swit | tching | and logic in DEAs thanks to HVTFTs and triboelectric sensors              | 111 |

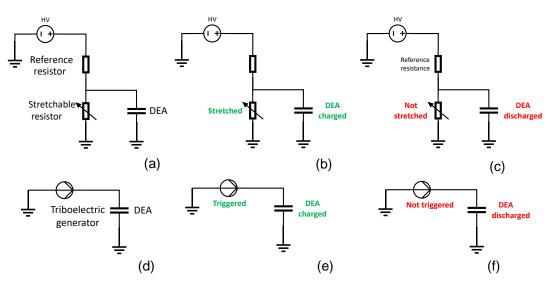

|   | 7.1  | Introd | luction on switching DEAs with triboelectric sensors                      |     |

|   |      | 7.1.1  | Switching DEAs with sensors directly connected to the actuator $\ldots$ . | 112 |

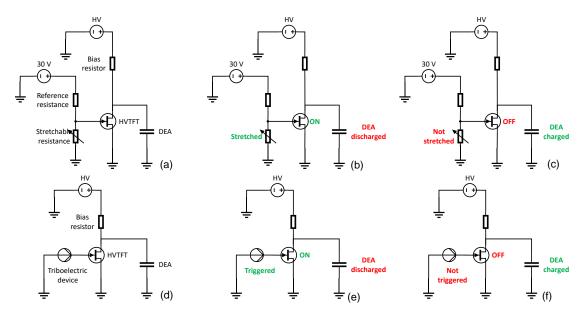

|   |      | 7.1.2  | Switching DEAs with intermediate HVTFTs amplifying the sensor signal      | 113 |

|   |      | 7.1.3  | Introduction to triboelectric sensors                                     | 114 |

|   | 7.2  | Ampli  | ifying the signal of a triboelectric device with a HVTFT to drive a DEA   | 116 |

|   |      | 7.2.1  | Working principle                                                         | 116 |

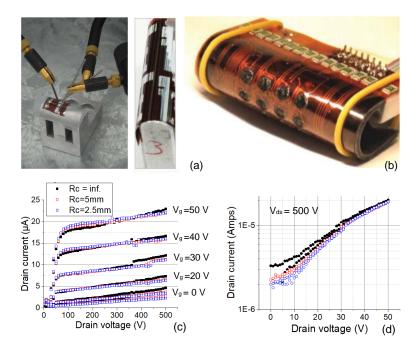

|   |      | 7.2.2  | Devices                                                                   | 116 |

|   |      | 7.2.3  | Results                                                                   | 117 |

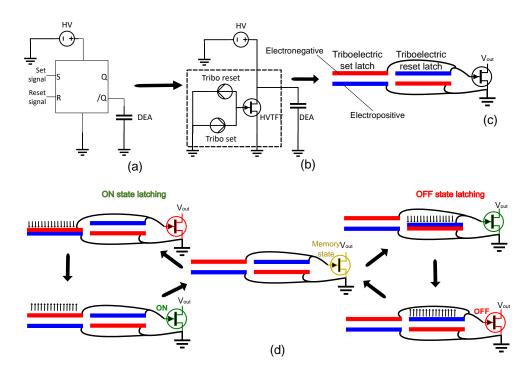

|   | 7.3  | A high | n voltage flip-flop gate to drive DEAs                                    | 120 |

|   |      | 7.3.1  | Working principle                                                         | 120 |

|   |      | 7.3.2  | Devices                                                                   | 122 |

|   |      | 7.3.3  | Results                                                                   | 122 |

#### Contents

| 8  | Con                   | nclusion                                                 | 127 |  |

|----|-----------------------|----------------------------------------------------------|-----|--|

|    | 8.1                   | Summary                                                  | 127 |  |

|    |                       | 8.1.1 Zinc tin oxide HVTFTs operating at 1 kV            | 128 |  |

|    |                       | 8.1.2 Addressing a matrix of DEAs with integrated HVTFTs | 129 |  |

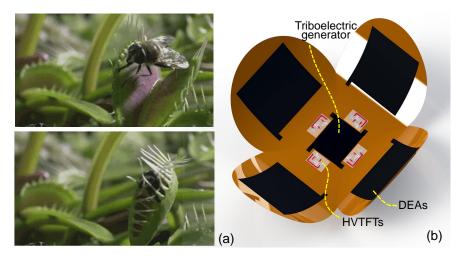

|    |                       | 8.1.3 Triboelectric control of the HVTFT channel         | 130 |  |

|    | 8.2                   | Perspectives                                             | 131 |  |

|    | 8.3                   | Concluding remarks                                       | 132 |  |

| Bi | bliog                 | graphy                                                   | 133 |  |

| Li | List of Abbreviations |                                                          |     |  |

| Li | List of Publications  |                                                          |     |  |

| Cı | Curriculum Vitae 1    |                                                          |     |  |

# List of Figures

| 1.1  | Size of high voltage optocouplers vs size of TFTs                               | 2  |

|------|---------------------------------------------------------------------------------|----|

| 1.2  | The first dielectric elastomer actuator (DEA)-HVTFT machine: a haptic display   |    |

|      | demonstrator                                                                    | 3  |

| 2.1  | Working principle of a DEA                                                      | 8  |

| 2.2  | DEAs: High strain, high speed, compliant actuators.                             | 9  |

| 2.3  | Examples of actuation modes of DEAs operating in surface expansion mode         | 11 |

| 2.4  | DEA devices operating in compression mode                                       | 11 |

| 2.5  | Voltage-stretch characteristics of DEAs                                         | 12 |

| 2.6  | Examples of haptic display made of 1000 of DEAs                                 | 17 |

| 2.7  | DEA based soft robots                                                           | 18 |

| 2.8  | Stiffening impact increase with DEAs miniaturization                            | 20 |

| 3.1  | Comparison between the MOSFET and the TFT cross-sections                        | 23 |

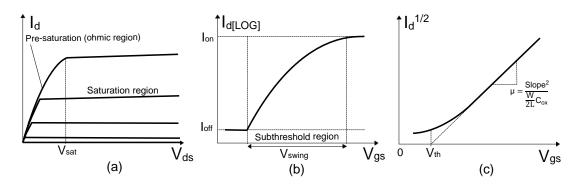

| 3.2  | TFT output and transfer characteristics description                             | 26 |

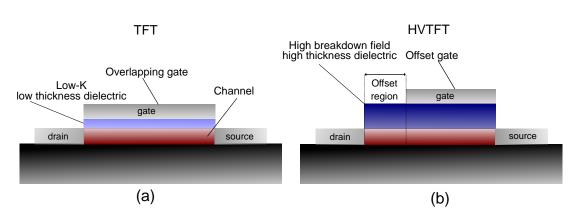

| 3.3  | Comparison between a TFT and a HVTFT                                            | 28 |

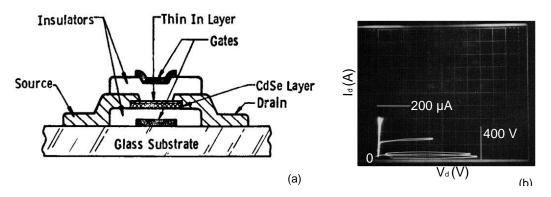

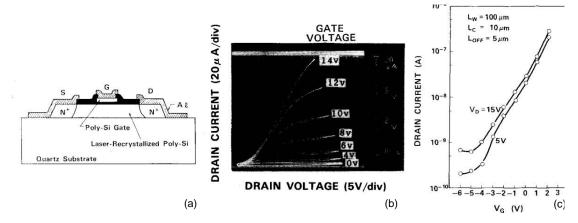

| 3.4  | CdSe HVTFT                                                                      | 30 |

| 3.5  | Poly-Si HVTFT                                                                   | 30 |

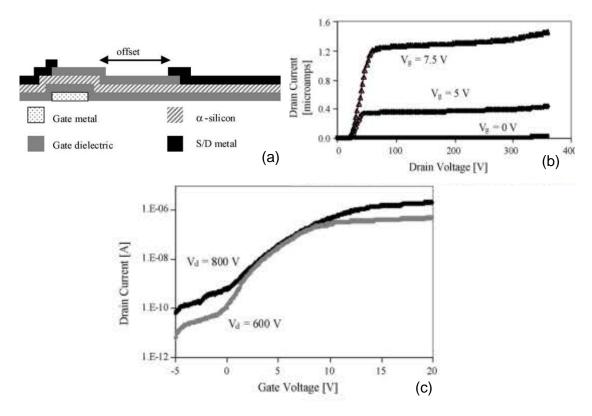

| 3.6  | a-Si HVTFT                                                                      | 31 |

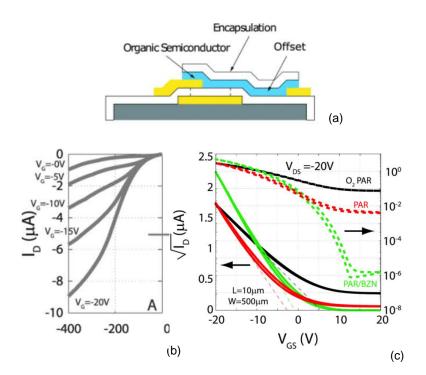

| 3.7  | Organic HVTFT                                                                   | 32 |

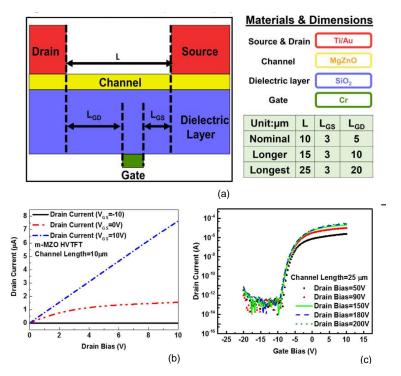

| 3.8  | Amorphous oxide semiconductors HVTFT                                            | 34 |

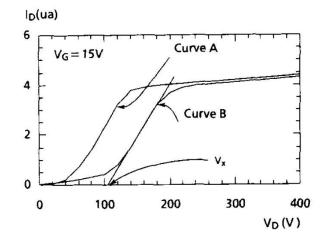

| 3.9  | Channel length modulation and punchthrough effect                               | 36 |

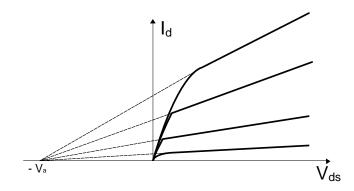

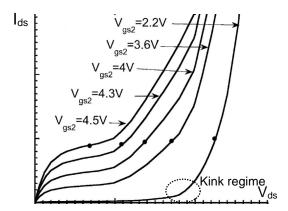

| 3.10 | Kink effect                                                                     | 36 |

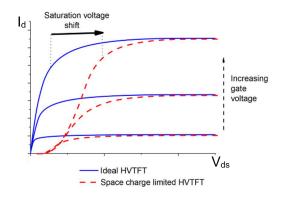

| 3.11 | Space-charge limited current and its effect on saturation voltage               | 37 |

| 3.12 | Potential barrier induced by the gate offset edge                               | 38 |

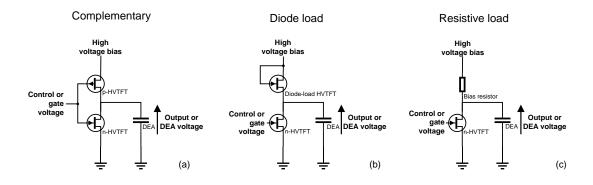

| 4.1  | Three inverter architectures                                                    | 44 |

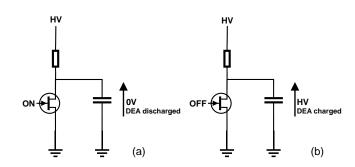

| 4.2  | Operation principle of a resistive loaded inverter driving a DEA                | 45 |

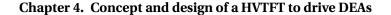

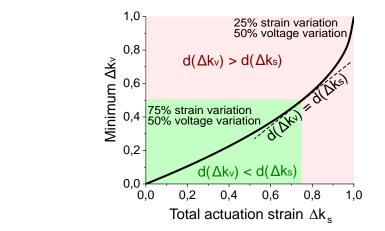

| 4.3  | Output voltage variation optimization for 80% normalized actuation strain $\$ . | 46 |

| 4.4  | Minimal variation of voltage required as a function of actuation strain         | 46 |

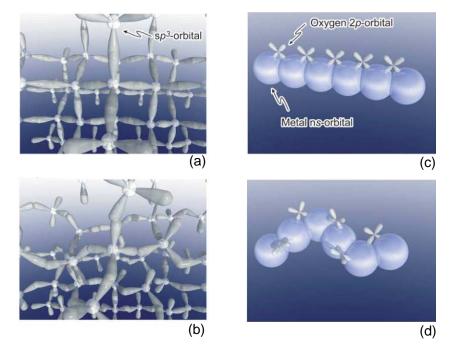

| 4.5  | Schematics of silicon and metal oxide orbitals                                  | 53 |

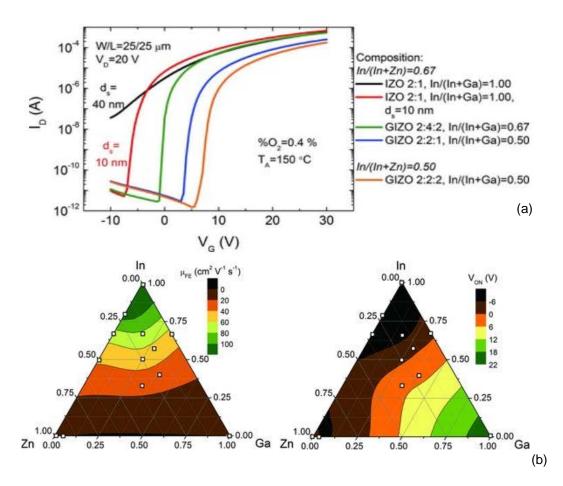

| 4.6  | effect of cation tuning on IGZO TFTs                                            | 54 |

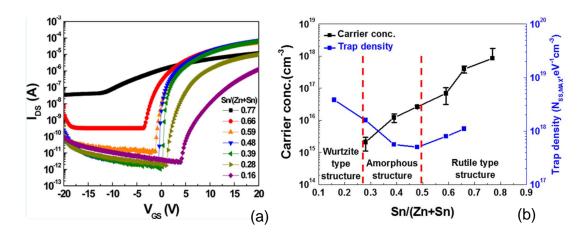

| 4.7  | effect of cation tuning on ZTO TFTs                                             | 55 |

| 4.8  | Description of the sol-gel process                                              | 57 |

|      |                                                                                 |    |

### List of Figures

| 4.9  | Cross-section of the HVTFT design                                                 | 58       |

|------|-----------------------------------------------------------------------------------|----------|

| 4.10 | The four gate-electrode architectures                                             | 58       |

| 4.11 | Theoritical limit for dielectric constant and breakdown field                     | 61       |

| 5.1  | Thermogravimetric analysis and differencial scanning calorimetry of chloride      |          |

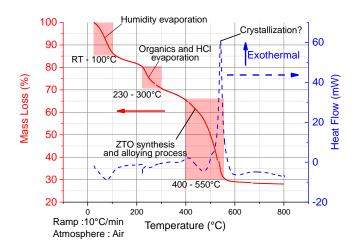

|      | based ZTO                                                                         | 68       |

| 5.2  | Surface and bulk XPS spectra of ZTO for compositional analysis before and after   |          |

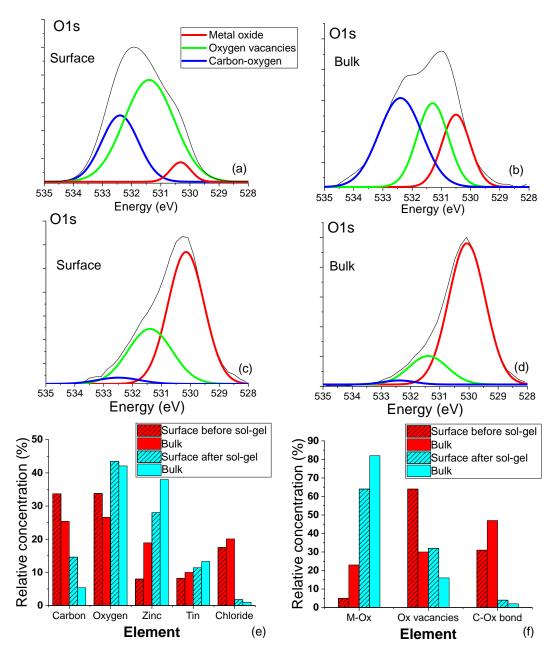

|      | sol-gel                                                                           | 69       |

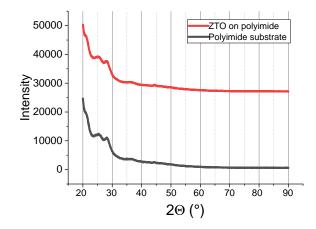

| 5.3  | X-ray diffraction spectrum of ZTO                                                 | 71       |

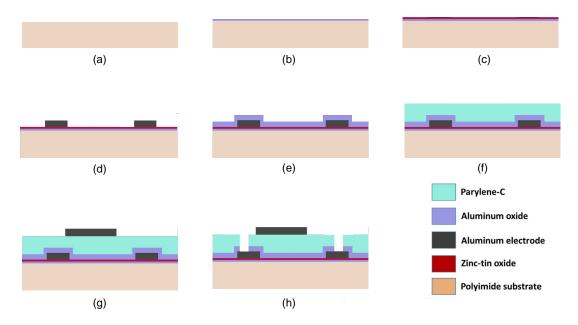

| 5.4  | HVTFT process flow                                                                | 73       |

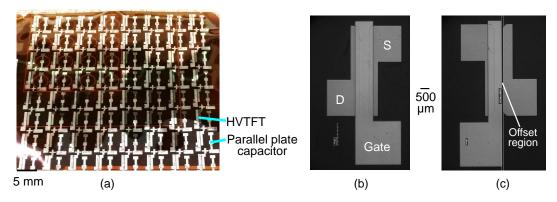

| 5.5  | Picture of the fabricated HVTFTs                                                  | 75       |

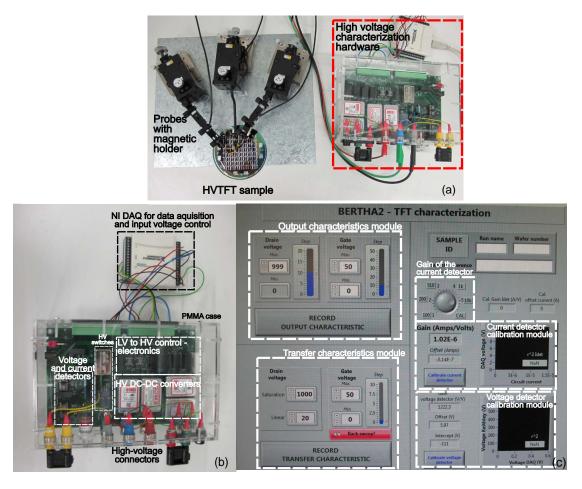

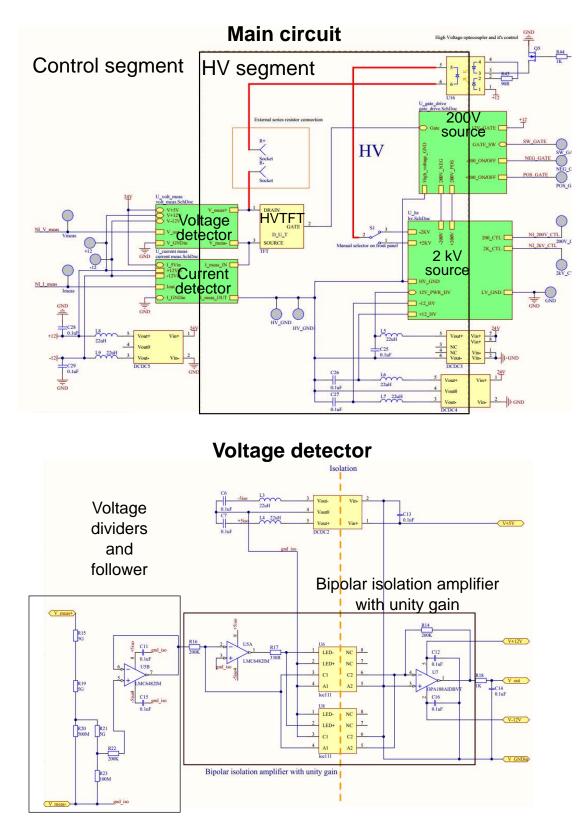

| 5.6  | High-voltage electrical characterization setup                                    | 76       |

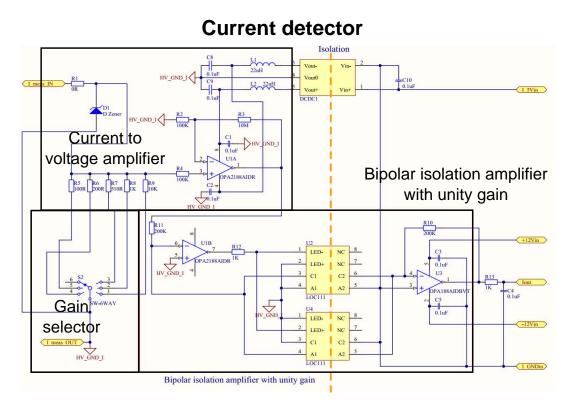

| 5.7  | Circuit of the high-voltage electrical characterization setup (1)                 | 77       |

| 5.8  | Circuit of the high-voltage electrical characterization setup (2)                 | 78       |

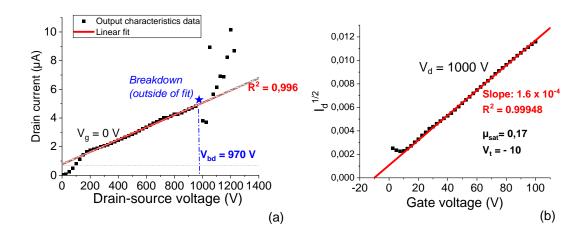

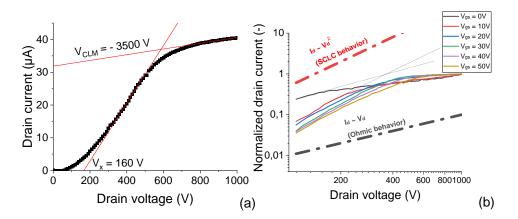

| 5.9  | Analysis methodology for breakdown voltage, mobility and threshold voltage .      | 79       |

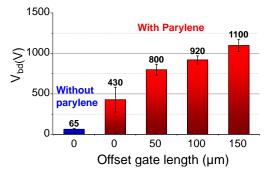

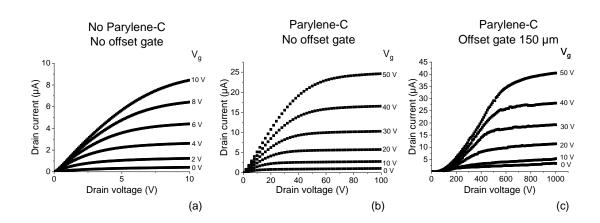

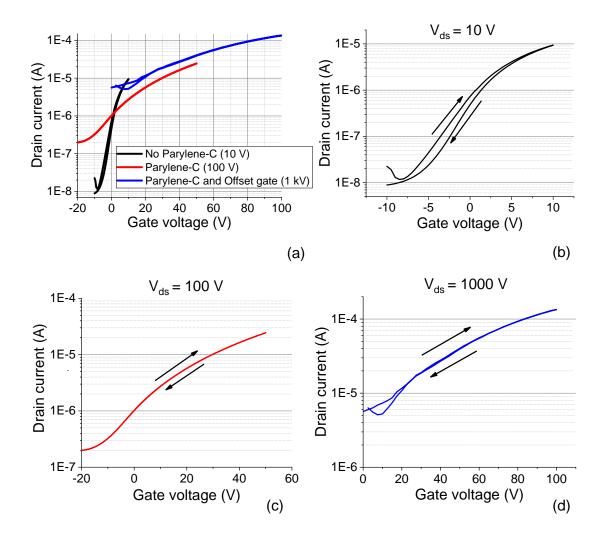

| 5.10 | Characterization of the breakdown voltage as a function of the offset gate length | 80       |

| 5.11 | Output characteristics of ZTO TFTs                                                | 81       |

| 5.12 | Transfer characteristics of ZTO TFTs                                              | 82       |

| 5.13 | Characterization of channel length modulation, potential barrier and space-       |          |

|      | charge limited current in ZTO HVTFT                                               | 83       |

| 5.14 | Modeling of saturation transfer characteristics of ZTO TFTs                       | 86       |

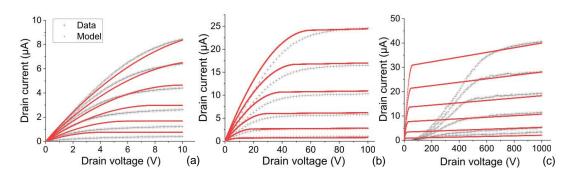

| 5.15 | Modeling of output characteristics of ZTO TFTs                                    | 87       |

| 5.16 | Modeling of output characteristics of ZTO HVTFTs                                  | 87       |

| 5.17 | XPS of YZTO HVTFTs                                                                | 89       |

| 5.18 | Output characteristics of YZTO HVTFTs                                             | 90       |

| 5.19 | Transfer characteristics of YZTO HVTFTs                                           | 90       |

| 5.20 | Fully printed HVTFT mock-up                                                       | 91       |

| 0.1  |                                                                                   | ~ ~      |

| 6.1  | Integration of DEAs with HVTFTs exploded view                                     | 94       |

| 6.2  | Deflection of a DEA constrained in a frame                                        | 95       |

| 6.3  | Analytical modeling of DEA actuation with varying membrane thickness to reach     | 07       |

| 6.4  | maximum actuation                                                                 | 97<br>07 |

| 6.4  | Diameter influence over DEA deflection                                            | 97       |

| 6.5  | Process-flow to fabricate deflection DEAs                                         | 98       |

| 6.6  | DEA fabricated on polyimide foil                                                  | 99       |

| 6.7  |                                                                                   | 100      |

| 6.8  | Circuit and operation principle of a DEA based haptic display addressed by HVTFTs | 101      |

| 6.9  | LTspice modeling of DEA switching characteristics with a HVTFT for different      |          |

|      | bias resistor                                                                     | 102      |

| 6.10 | Haptic display proof of concept exploded view                                     | 104      |

| 6.11 | Demonstrator assembly step by step                                                | 105      |

| 6.12 | Alignment considerations for integration                                          | 106      |

### List of Figures

| 6.13 | Characterization of DEA deflection controlled by HVTFTs gate voltage             | 107 |

|------|----------------------------------------------------------------------------------|-----|

| 6.14 | Static bending of HVTFTs                                                         | 108 |

|      |                                                                                  |     |

| 7.1  | Resistive and triboelectric sensor operation on a DEA                            | 112 |

| 7.2  | Resistive and triboelectric sensor of a DEA with an intermediate HVTFT $\ldots$  | 114 |

| 7.3  | Bending triboelectric device driving the gate of the HVTFT                       | 116 |

| 7.4  | Triboelectric arm and finger band                                                | 117 |

| 7.5  | Triboelectric control of the gate signal of a HVTFT operating at 600 V.          | 118 |

| 7.6  | Triboelectric control of the gate signal of a HVTFT connected to a 1 kV DEA      | 119 |

| 7.7  | Working principle of a high voltage flip-flop based on two triboelectric devices |     |

|      | and a HVTFT                                                                      | 121 |

| 7.8  | Cross-section and picture of a triboelectric pad                                 | 122 |

| 7.9  | Triboelectric bistable latching of a HVTFT.                                      | 123 |

|      |                                                                                  |     |

| 8.1  | Artificial flytrap concept.                                                      | 131 |

# List of Tables

| 3.1 | Comparison between the c-Si MOSFET and the TFT                                    | 22  |

|-----|-----------------------------------------------------------------------------------|-----|

| 3.2 | Comparison between amorphous silicon poly-silicon, organic and metal oxide        |     |

|     | TFT technologies(adapted from [1,2])                                              | 23  |

| 3.3 | Differences between TFTs and HVTFTs                                               | 27  |

| 3.4 | Review of HVTFTs, classified by channel materials.                                | 29  |

| 3.5 | Failure mechanisms per HVTFT channel technology                                   | 39  |

| 3.6 | Comparison between the different channel technologies to fabricate a perfor-      |     |

|     | mant HVTFT                                                                        | 41  |

| 4.1 | Requirements for a resistive load inverter based on a pull-up bias resistor, a    |     |

|     | control HVTFT and a DEA.                                                          | 47  |

| 4.2 | Minimal requirement on the on-off current ratio as a function of the bias voltage |     |

|     | and the saturation voltage of the HVTFT                                           | 49  |

| 4.3 | Requirements on the on current as a function of the DEA capacitance and the       |     |

|     | saturation voltage of the HVTFT.                                                  | 51  |

| 4.4 | Standard ZTO and IGZO TFT technologies vs table of requirements for the HVTFT     | 52  |

| 4.5 | Comparison between dielectric materials typically used for ZTO TFTs and com-      |     |

|     | parison between the different processes used to deposit them (adapted from [3–5]  | 60  |

| 5.1 | Comparison of the HVTFTs experimental results for ZTO TFT with no Parylene-C      |     |

|     | and no offset gate, ZTO TFTs with Parylene-C and no offset gate and ZTO HVTFTs    | 82  |

| 5.2 | TFT model inputs                                                                  | 85  |

| 5.3 | Table comparing HVTFTs with requirements                                          | 92  |

| 6.1 | Analytical model parameters to determine DEA initial membrane thickness and       |     |

|     | active area diameter                                                              | 96  |

| 6.2 | Comparison between the fabricated demonstrator parameters with the require-       |     |

|     | ments.                                                                            | 110 |

| 7.1 | Comparison between dielectric elastomer switches and triboelectric sensors to     |     |

|     |                                                                                   | 113 |

| 7.2 | Logic states of a set-reset flip-flop                                             | 120 |

# **1** Introduction

## 1.1 Background and motivation

An actuator is a device generating a mechanical response to an electrical stimulus. To operate systems made of large arrays of actuators such as haptic displays or projectors, integrated drive electronics such as transistors are required to independently control each actuator. This thesis focuses on the development and integration of transistors to address high-voltage soft actuators: dielectric elastomer actuators (DEAs).

DEAs are soft actuators [6] with a unique combination of properties [7,8]: They actuate fast (< 1 ms time response [9]), are compliant, can achieve high actuation strain (> 100 % [10]) and consume almost no power compared e.g. to electromagnetic actuators. These appealing properties have recently made DEAs an active field of research [6,11]. DEAs have been applied to several fields including optics, cell biology, energy harvesting and grippers [7, 8, 12, 13]. Several of these applications such as active microfluidic valves [14] or haptics displays [15] require the independent actuation of 10s to 100s DEAs. As an example, a Braille display requires the independent out-of-plane actuation of 6 dots or taxels (tactile pixels) to be able to form every letter of the Braille alphabet. A refreshable Braille text on an A4 page requires the independent actuation of > 1000 DEAs [16].

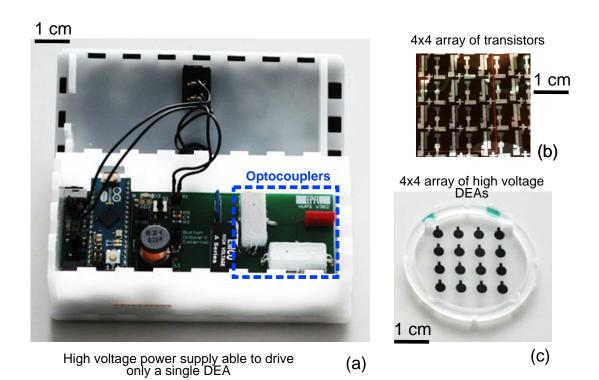

DEAs typically reach their maximum actuation strain at a drive voltage of several kVs. As a consequence, the circuit required to address a matrix of DEAs has to include power transistors or optocouplers, bulky components preventing any possible integration. Figure 1.1a shows the picture of a high-voltage power supply used to drive and switch on and off a single DEA. We would need 16 similar boxes to switch a matrix of 16 independent DEAs as represented in Figure 1.1c. This solution is unacceptable if we aim at achieving a compact or a wearable device made of DEAs.

The thin-film transistor (TFT) is an interesting compact candidate for addressing actuators. TFTs belong to the family of field effect transistors and were invented by Paul K. Weimer in

#### **Chapter 1. Introduction**

1962 [17]. TFTs differ from metal oxide semiconductor field effect transistors (MOSFETs) because their semiconductor is independent from the substrate. The conduction in a TFT occurs indeed in a thin-film semiconductor deposited on an insulator. Originally processed on glass, TFTs are processed today on flexible polymers to address flexible and stretchable sensors [18–20]. Despite being less performant than the standard MOSFET, the TFT was successfully used as a switching elements to address organic light emitting diodes (OLEDs) or liquid crystal display (LCD) matrices [1,21,22]. In term of size, a TFT enables a more compact integration of switches than bulky optocouplers and power MOSFETs. However, prior to this thesis, no TFT was reported operating at 1 kV or more.

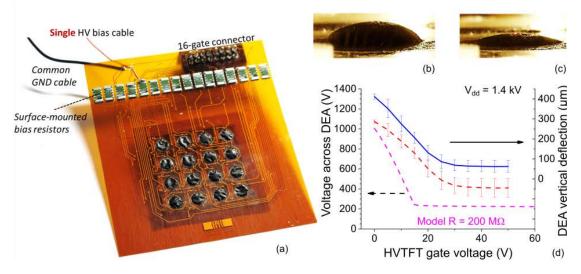

Figure 1.1 – Picture showing (a) a high voltage control box enabling the addressing of 1 single DEA [23].(b) A matrix of 16 compact high voltage thin film transistors used to drive DEAs. Each transistor replaces an optocoupler circuit (taken from the experimental batch that will be presented in the next chapters). (c) An array of 16 DEAs towards a haptic display.

In this thesis, we designed a high voltage thin-film transistors (HVTFTs) matching the high voltage required to drive DEAs. We integrated and demonstrated these HVTFTs with a matrix of DEAs. We also demonstrated that our HVTFTs were able to amplify and treat a sensor signal to drive a DEA. Figure 1.1b shows HVTFTs on foil that we fabricated in the frame of this thesis. Every transistor is more compact than the optocouplers shown in Figure 1.1a and can be integrated and control one DEA such as the ones shown in Figure 1.1c.

### 1.2 Thesis objectives

This PhD project has been funded by Fond National Suisse de la Recherche Scientifique (FNSNF) grants (Nos. 200020-153122 and 200020-165993). The HVTFTs developed in this thesis respect the following basic requirements:

- The HVTFTs should be able to drive DEAs.

- The HVTFT should be designed, fabricated and demonstrated at a voltage higher than 500 V with a control voltage lower than 100 V, while having a time response enabling operation of DEAs at a frequency higher than 10 Hz.

- A HVTFT matrix should be integrated with an array of 4x4 DEAs.

- The HVTFT should operate under flexure.

## 1.3 Thesis outline and contribution

In the PhD framework, we designed a HVTFT suitable for DEA addressing and sensor interfacing. This work shows the feasibility of low-voltage addressing of DEAs by removing the need for bulky, rigid and unpractical switches. First, we demonstrated and characterized a 1 kV HVTFT made of amorphous oxide semiconductor (AOS) materials. Then, we showed that DEAs operating at 1 kV can be switched by these integrated HVTFT with a control voltage of 30 V. We built a haptic display demonstrator as a proof of concept (Figure 1.2).

Figure 1.2 – The first DEA-HVTFT machine: a haptic display demonstrator. The 4x4 DEA matrix is addressed by a 4x4 HVTFTs matrix a single high voltage power supply and 16 low-voltage command lines [24].

Finally, we demonstrated a high-voltage flip-flop made of a HVTFT and triboelectric generators to drive a DEA. By demonstrating a novel high-voltage, flexible and compact transistor to address high voltage actuators, this work opens up additional perspectives of research projects (DEAs self-switching and automation, understanding the physics behind HVTFT and printing HVTFTs...), and a path towards novel practical applications for DEAs (Compact Braille displays, articulated soft locomotion robots...).

#### State of the Art

The first two chapters of this thesis cover the fundamentals of HVTFTs and provide an introduction to DEAs and their applications.

**Chapter 2** introduces the field of DEAs, summarizes the underlying actuation principles and presents several applications of DEAs where HVTFTs addressing is a critical addition.

**Chapter 3** summarizes the working principle of TFTs. It presents the typical semiconductor channel technologies available for TFTs. We report state-of-the-art HVTFTs technologies and we show that metal oxide HVTFT technology is the most promising to achieve high performance HVTFTs.

#### High-voltage thin film transistors design and characterization

**Chapter 4** presents the design requirements and defines a concept for our HVTFT. The HVTFT constraints are defined relatively to its integration with the DEA in a resistive load inverter configuration. We select an AOS semiconductor, zinc tin oxide as the channel semiconductor to achieve high performance, tunable devices. To operate at high voltage, a gate dielectric composed of a bilayer of alumina and Parylene-C and an offset gate geometry are chosen. We conclude this chapter by describing the entire HVTFT architecture.

**Chapter 5** presents the fabrication and demonstration of zinc tin oxide (ZTO) HVTFTs. The process developed to design HVTFTs is described. Then, the semiconductor synthesis, has been extensively studied with various material characterization methods including thermogravimetric analysis (TGA) coupled with differencial scanning calorimetry (DSC), X-ray photoelectron spectroscopy (XPS) and X-ray diffraction (XRD). Then, we discuss the HVTFTs electrical characteristics. The fabricated HVTFTs can operate up to 1 kV, have an on-off ratio of 20, high 100  $\mu$ A on-current and no charge hysteresis. We present and discuss a LT-Spice circuit model for the HVTFT. Afterwards, we show an optimization for the HVTFTs by yttrium doping. The drain-source leakage current drop from an order of magnitude to 100 nA. We conclude this chapter by presenting a route for optimization of the zinc tin oxide (ZTO) semiconducting properties by yttrium doping.

#### Integration of HVTFTs to address dielectric elastomer actuator arrays

**Chapter 6** describes the integration of HVTFTs with a matrix of out-of-plane DEAs similar to a haptic display. First we show the design and the fabrication of DEA diaphragms for out-of-plane actuation. The DEAs operate at a maximum voltage of 1 kV. Afterwards, we demonstrate and characterize the first integration of an array of DEAs with HVTFTs. The DEA actuate under a circuit bias of 1.4 kV and a gate voltage swing of 30 V. We conclude this chapter by demonstrating the device operation under static bending down to 5 mm radius of curvature.

#### Sensors and flip-flop made of HVTFTs and triboelectric sensors to drive DEAs

**Chapter 7** presents how the HVTFTs can be used as intermediate components to amplify and treat a low-voltage sensing signal to a DEA. We present how the use of triboelectric generators (TrEGs) can bias the HVTFT gate, and thus generate the 30 V gate voltage signal required to switch a 1 kV DEA on and off. We show the control of HVTFT drain-source current with a bending TrEG and we demonstrate actuation of DEA with this methodology. Then we demonstrate a high-voltage flip-flop made of two triboelectric sensors and one HVTFT: We demonstrate the bistable latching of the HVTFT and of the DEA by triggering the two parallel triboelectric sensors. This last chapter opens a path towards fully automated and integrated DEAs.

## 1.4 Impact of this thesis

This thesis advances the field of HVTFTs by introducing the first zinc tin oxide HVTFT operating at 1 kV. It also shows the first practical application of HVTFTs at a bias voltage > 500 V.

This thesis also advances the field of DEAs by showing the first compact addressing of a 4x4 DEA matrix with an active array of 4x4 HVTFT. The low voltage required to switch the DEAs, 30 V, is more than 30 times lower than the driving voltage of the DEAs (1 kV).

Finally this thesis advances the field of DEA systems and automation by demonstrating that triboelectric sensors be used to modulate the HVTFT gate voltage to control the DEA actuation. The HVTFT makes possible the transfer of the triboelectric signal to the DEA actuation signal. Also, the combination between triboelectric sensors and HVTFTs can lead to logic gates able to drive DEAs.

# 2 Dielectric elastomer actuators

#### Summary

In this chapter, we describe the dielectric elastomer actuator (DEA), an electrostatic actuator converting an applied electric field into a mechanical strain.

We start by defining the DEA and its properties. We illustrate the DEA appealing properties, compliance, high strain and high speed with practical examples. Then, we describe the DEA operation modes, in-plane expansion and out-of-plane compression.

Afterwards, we present the working principle of the DEA actuation. We discuss how the DEA actuation stress and strain relate to the applied voltage. Then, we briefly discuss typical failure mechanisms of DEAs.

After that, we describe typical elastomer membrane materials. We compare the specific advantages of polydimethylsiloxane (PDMS) membranes and VHB acrylic membrane. Then we discuss the different conductors usable to fabricate the stretchable electrodes of DEAs.

Finally, we discuss two examples of applications exploiting DEAs devices, which require addressing: haptic displays and soft robots. Haptic displays require the individual addressing of 100s of DEAs and more than 1000 in the particular case of Braille displays [16]. In the case of soft robots, individual controls of multiple actuators would enable soft locomotion with articulated arms and soft grippers with multiple degrees of freedom. These two examples show how the implementation of integrated high-voltage transistors is necessary to achieve compact complex DEA machines.

## 2.1 Definition and properties of the DEA

In this section, we present the concept of DEAs. The DEA is first defined. Then, its qualities (compliance, speed, high strain and low power consumption) are described with concrete examples.

#### 2.1.1 Basic structure and definition

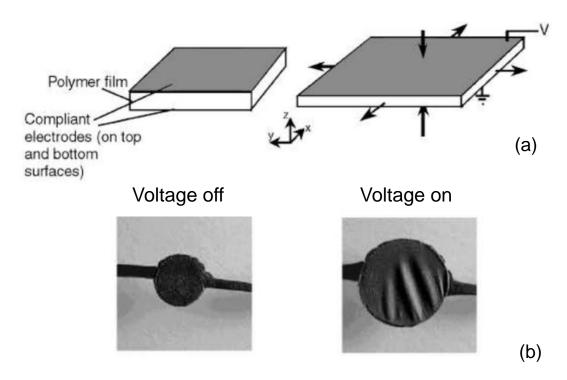

A DEA is a soft actuator composed of a dielectric elastomer straining under the application of a high voltage, typically several kVs [6, 11]. A DEA includes three main structural elements, one dielectric elastomer membrane with a thickness typically in the order of tens of  $\mu$ m and two stretchable electrodes. Each electrode is respectively patterned on the top and the bottom surface of the membrane. The active area is the region were both electrodes overlap. The application of a voltage leads to charge accumulation in the active region, which creates an electric field leading to an electrostatic pressure exerted by the electrodes. The membrane responds by compressing out-of-plane inducing in-plane expansion because of elastomer incompressibility (see Figure 2.1).

Figure 2.1 - (a) Description of a DEA structure and of its actuation principle. (b) Top view picture of the in-plane expansion of a DEA under a voltage bias. When a voltage is applied across a dielectric elastomer, the charges accumulating in the active region induce a compressive stress leading to in-plane expansion of the actuator (Adapted from [25]).

#### 2.1.2 DEAs, high strain, compliance and high speed actuators

DEAs have a lot of interesting properties, among which the ability to actuate at high strain and high speed with compliant structures.

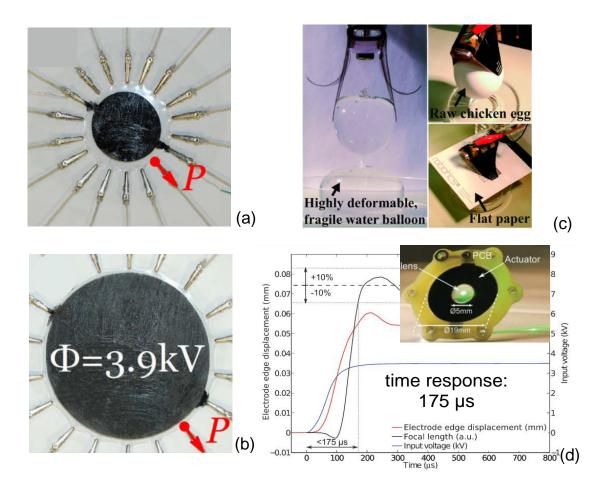

DEAs are able of very high strain. Figure 2.2a and b show the example of a DEA straining inplane by 488 % [26] under the application of 3.9 kV. In order to achieve a very high deformation, the DEA had to be prestretched with a dead load of 25.5 g to avoid electromechanical instability (see section 2.2 for the detailed mechanism and the working principle of DEAs actuation). The highest strain achieved by DEAs with an acrylic elastomer membrane has been reported to be 1692 % area strain [27]. It consisted in a bubble DEA that was prestretched with a backpressure of 18 mbar. The highest strain reported for silicone based DEA in the order of 80% linear strain [28].

Figure 2.2 – Picture of a DEA (a) idle and (b) actuated with an in-plane actuation area strain of 488 % under the application of 3.9 kV (adapted from [26]). (c) DEA based gripper. The compliance of the DEA enables it to adapt and grab a wide variety of surfaces(adapted from [29]). (d) A DEA tubable lense and its transient characteristics showing an actuation response time of 175  $\mu$ s (adapted from [9])

A key quality of DEAs is also their speed. It is highly dependent on the dielectric elastomer membrane material. Silicone membrane DEAs are the fastest polymer-based actuators. The time response for such devices has been reported to be less than 200 µs. Figure 2.3d presents the transient characteristics of an active lens made of DEAs [9]. The actuator time response has been reported to be 175 µs and to be able to operate at 4.7 kHz. A similar device made with acrylic DEAs can operate only up to a few Hz. The higher time response are due to the losses induced by the viscoelasticity of the acrylic elastomer.

DEAs are also compliant structures because they are made of stretchable polymers of low Young's moduli, typically in the order of 1 MPa. They can be suspended on both rigid or flexible frames depending on the application. The DEA compliance makes the actuator practical for applications related to flexible grippers [29–31], as the actuator can cover and adapt to a variety of shapes of an object more efficiently than rigid grippers. In the case of the DEA gripper, presented in Figure 2.2d, the actuation was combined with electro-adhesion to generate sufficient force to grip objects.

#### 2.1.3 Operation modes

DEAs can operate either in surface expansion or in thickness compression mode. Actuators used in surface expansion mode can generate large actuation strain and actuators in thickness compression mode can generate high forces.

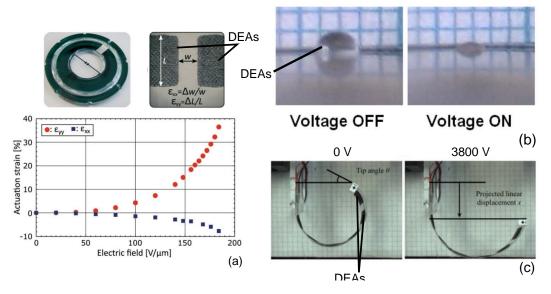

Figure 2.3 describes different applications achievable with surface expansion actuation of the DEA. Different motions can be achieved with the constraints applied on the DEA active region. When the active region can move freely without constraints (see Figure 2.3a), we are in planar expansion mode. Prestretching the membrane along a single axis leads to uniaxial strain deformation when the DEA actuates. This operation mode has been used e.g. for biological cell-stretcher [12, 28]. Figure 2.3a shows a cell-stretcher made of two parallel in-plane DEAs actuating simultaneously and the strain-voltage characteristics of the device [12]. They have been prestretched mostly along the x-direction to lead to an uniaxial actuation along the y-direction. When the actuators actuate, they strain the gap in-between e.g. in order to strain cells on top of it.

Constraining the active region of the DEA in a rigid frame prevents the DEA of moving in plane, which leads to vertical deflection of the actuator. The actuators are then operating in buckling or vertical deflection mode. Bubble DEAs were demonstrated using this principle [15, 16, 24, 27, 32, 33]. Figure 2.3b) shows a DEA deflecting more than 500 µm out-of plane with a bias voltage of 2500 V [32].

Constraining a uniaxially prestretched DEA on a flexible frame leads to the bending of the entire structure. The actuators are then operating mode and are called dielectric elastomer minimal energy structures (DEMES). This structure is used in soft robotics for grippers [29–31] and walking robots [34]. A variety of other operation modes such as zipping [35] and springroll

DEAs [36] are also achievable.

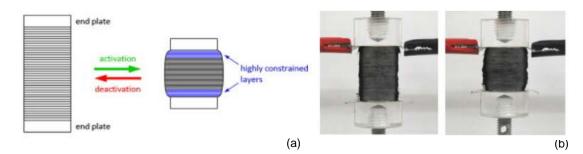

The compression mode of DEAs is used in structures requiring a high-force DEAs. The problem of operation mode is the small out-of-plane displacement it generates. To increase the vertical displacement, DEAs can be stacked as shown Figure 2.4 [36–38].

Figure 2.4a and b shows the picture of DEA with stacked architectures used to lift weights when contracting [37]. These DEA are made of 400 layers of 1.6 cm diameter acrylic circular DEAs stacked together. The DEA could lift a 2 kg weight and block a 20 N force while weighing only 4 g and contracted 10 %. Stacked structures were used eg for microfludic valves [39] and haptic display [38] applications.

Figure 2.3 – Picture and actuation characteristics of DEAs operating in surface expansion mode. (a) Actuator operating in planar expansion used for cell-stretching. The uniaxial prestretch orientates the strain direction as shown in the strain electric field characteristics. (adapted from [12]) (b) Out-of plane actuator operating like a taxel with transparent electrodes (adapted from [32]). (c) Bending actuator operating for gripping. (adapted from [30])

Figure 2.4 – Picture and actuation of DEA devices operating in compression mode. Stacked DEA (a) working principle and (b) pictures of actuation. (adapted from [37]).

#### 2.2 Working principle

#### 2.2.1 Dielectric elastomer actuation

As we already mentioned, the DEA membrane is typically made of acrylic or silicone elastomers. These materials are hyper-elastic polymers. We call  $\lambda_{DEA}$ , the in-plane stretch of the DEA membrane. The stress-strain relationship of the membrane is increasing non linearly until saturation when approaching a stretch value  $\lambda_{DEA} = \lambda_{lim}$ , where the polymer stiffens and no further extension is possible [10, 40]. The stress-strain relationship of hyperelastic materials can be approximated such as the Neo-hookean model, good for small deformation (stretch < 1.2) of hyperelastic materials, or the Gent model [41], which additionally takes into consideration the limit stretch of the hyperelastic membrane.

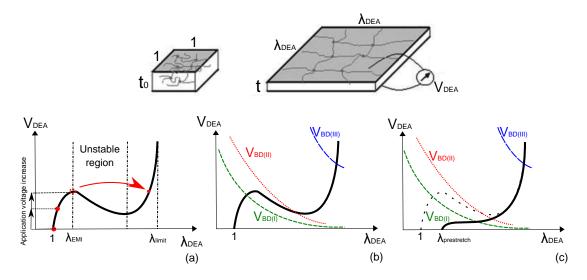

Figure 2.5 – (a) Voltage-stretch characteristics of a DEA without initial prestretch. Three regions in the curves can be identified: First, the monotonous increase of the stretch with applied voltage until a critical stretch  $\lambda_{EMI}$ . Then the DEA "snaps-through" and the stretch increases until a new stable value, where the increase of voltage leads again to a monotonous increase of the stretch until the limit stretch defined by the elastomer material  $\lambda_{limit}$  or the DEA breakdown field. (b) Dielectric breakdown curves of three different types of elastomer materials are superimposed with previous plot. Type I elastomers, break down after low electromechanical stretch (typically less than 1.1). Type II elastomers break down, when the DEA snap through and the type III survives the snap through and break down at very high stretch voltage characteristics of a DEA. The electromechanical instability region disappears and the stretch increases monotonously with the actuation voltage, enabling actuation at very high stretch values for type II and type III materials (adapted from [40])

As the compressive electrostatic stress  $\sigma_z$  can be connected to the stretch of the dielectric elastomer [6, 40], it is possible to plot the relationship between the stretch of the DEA and the

voltage applied across the DEA.  $\sigma_z$  can be expressed as a function of the applied electric field E or voltage V by Maxwell's equation [11]:

$$\sigma_z(\lambda) = \varepsilon_m \varepsilon_0 \cdot E^2 = \frac{\varepsilon_m \varepsilon_0}{t_m^2} \cdot V_{DEA}^2$$

(2.1)

Where  $\varepsilon_m$  is the relative permittivity of dielectric elastomer,  $t_m$  is the membrane thickness and  $\varepsilon_0$  is the vacuum permittivity constant.

Figure 2.5b adds up to the stretch voltage relationship of the previous graph the breakdown curves for three different types of elastomers. To calculate the strain-breakdown voltage relation, we have to first consider that an elastomer is incompressible, which means that the product of the stretch along every direction of space is equal to 1:

$$\lambda_x \lambda_y \lambda_z = 1 \tag{2.2}$$

In case of equibiaxial actuation strain:

$$\lambda_z = \frac{1}{\lambda_x \lambda_y} = \frac{1}{\lambda^2}$$

(2.3)

where  $\lambda$  is the lateral stretch. The breakdown voltage can be expressed as a function of the compressive stretch  $\lambda_z$  and the initial thickness of the DEA membrane:

$$V_{bd} = E_{bd} t = E_{bd} t_0 \lambda_z = \frac{E_{bd} t_0}{\lambda^2}$$

(2.4)

For the type I the DEA breaks down at  $\lambda < \lambda_{EMI}$ . The type II breaks down as soon as the stretch becomes equal to  $\lambda EMI$ . The type III breaks down in the region beyond the second stable point  $\lambda_{DEA} > \lambda_{giant}$ . This last type leads to the highest stretches and is responsible for the giant actuation reported [10, 27].

The key to very high and continuous actuation of DEAs is the removal of the electromechanical instability phenomenon. The solution is either to prestretch it [40] or to densify the polymer with interpenetrated polymer networks [42]. As shown in Figure 2.5c, the bump in the stretch-voltage characteristics disappear and the voltage stretch function increases monotonously, meaning that continuous actuation until dielectric breakdown is possible.

#### 2.2.2 Actuation of DEAs under a low strain

In this PhD thesis, the DEAs are all operating at low strain (< 20 %). In this strain range, the stress-strain relationship of the DEA can be considered as linear [6] if we neglect the stiffening impact of the DEA electrodes [43]. For a Young's modulus  $Y_m$  the compressive strain  $s_z$  can

therefore be expressed as, based on Equation 2.1 [6]:

$$s_z = -\frac{\varepsilon_m \varepsilon_0}{Y_m t_m^2} \cdot V_{DEA}^2 \tag{2.5}$$

#### 2.2.3 Failure mechanisms

DEAs have three major failure mechanisms, the dielectric breakdown, the material rupture and the loss of mechanical tension [44]. Dielectric breakdown occurs when the electric field across the dielectric membrane reaches the dielectric strength or breakdown field of the membrane (see before and Figure 2.5b). Electronic charges bypass the membrane and a current is created through the membrane, irreversibly destroying it. The loss of mechanical tension occurs when the reaction force from the passive area of the membrane cannot accommodate for the in-plane expansion of the active area. The membrane relaxes and locally buckles, and no in-plane expansion happens anymore.

### 2.3 Materials for DEAs

In this section, common materials used to fabricate DEAs are presented. First, we describe typical materials for the elastomer membrane and then, we discuss conductive stretchable electrodes for the DEA active area.

#### 2.3.1 Elastomer membrane

For maximizing in-plane strain, dielectric elastomer membranes need ideally to have a high breakdown field and a low Young's modulus in the order of 1 MPa or lower according to Equation 2.5. Beyond some marginal cases [15, 45], most DEAs are made in acrylic and in silicone elastomers.

Acrylic elastomers are usually made in Very High Bond (VHB), a commercial adhesive from  $3M^{TM}$ . VHB is a very interesting material as its combination of low Young's modulus and high breakdown strength makes it capable of the highest strain reported for DEAs up to date (up to 1690% area strain [27]). However, VHB has several drawbacks. VHB being a commercial product only available in pre-fabricated thin films, the thickness of one VHB membrane cannot be directly tuned. In addition, VHB is very viscoelastic leading to higher actuation time-constant [9]. The creep of a VHB membrane induces progressive relaxation of the pre-stretch preventing any long-term usage of acrylic DEA [46, 47].

These main limitation are the causes of the increase of popularity of silicone elastomers as membranes for DEAs. Silicone membranes lead to actuators with less actuation strain (up to 80% [28]) than VHB, but are excellent at solving the limitations of VHB DEAs. PDMS can be fabricated from commercial solutions and membranes thickness can be accurately tuned, while processing it, thus enabling calibration of the maximum DEA operation voltage [48]. PDMS has a very low viscoelasticiy and the absence of creep removes tension loss under prestretch and after actuation, enabling long-term usage for millions of cycles [49]at a very high frequency > 1kHz [9], making silicone DEAs applicable for vibrational applications. PDMS can either be selected from commercial pre-fabricated membrane (eg [50]) or in solution form, combining two elements, the silicone solution and its cross-linker (eg [51]). From a solution-form PDMS, membranes can be fabricated by blade-casting [48, 52], spray-coating [53], spincoating [54], stamping [43] to achieve thicknesses varying from 100s of nm to 100s of µm.

#### 2.3.2 Stretchable electrodes

In order to actuate, DEAs require stretchable (at least 10 %) electrodes able to adhere well on the elastomer membrane with limited stiffening impact. Also, to avoid the DEA response time to be limited by its charging time constant, the RC time constant combining the resistance of the DEA stretchable electrode and the capacitance of the actuator has to be low. Typically, the values of the capacitance of DEAs is between 10 pA and 1 nA, which means that the electrodes

should induce a resistance lower than 1 M $\Omega$  to enable at worst a RC time constant of 1 ms. Most conductive stretchable electrodes available for DEAs have been reviewed in [55, 56]. Several works report electrode materials such as hydrogels [57], ionogels [58] but most of the actuators are either metal based or carbon based. Metal based electrodes have very low sheet resistance but highly impact DEA actuation by stiffening [55] and, as thin film of continuous material, crack at very low strain [56]. To avoid this, metallic stretchable electrodes can be obtained from thin film pattering on corrugated membranes [55], nanolayer ion implantation [33], and nanowires [59]. As an example, 10 nm implanted gold electrodes in 30 µm PDMS membranes have been demonstrated [33] for a sheet resistance between 100  $\Omega$  and 1 k $\Omega$  per square. The implantation of gold electrodes multiplies the Young's modulus of the membrane from 1.5 to 5, decreasing thus the actuation performance [33]. Silver nanowire electrodes can achieve 16  $\Omega$  per square [60].

Carbon based material are the most used to fabricate dielectric elastomer actuators electrodes. Various forms of carbon electrode DEAs have been reported such as carbon powder [49,55], carbon grease [49, 55], carbon loaded PDMS [52, 55], graphene [61] and carbon nanotubes [62]. Carbon nanotube electrodes can lead to very conductive thin films and very thin membranes can be achieved without a negative impact on the DEA speed. Carbon nanotube in polymer nanolayers enabled a resistance of  $0.1 \,\mathrm{k}\Omega$  per square [55]. The main advantage of carbon grease and powders DEAs is the minimal stiffening impact on the elastomeric membrane. Carbon powder is difficult to handle as it is very sensitive to static electric fields, and is challenging to manipulate except if encapsulated in an additional silicone film [55]. However, as they are in powder and grease form the electrodes are subject to abrasion after several cycles, making these materials unpractical to design long-term devices. Carbon loaded PDMS solves the problem of abrasion, as the carbon black particles are encapsulated in a crosslinked PDMS matrix. The dispersion, in solution form can be deposited on the membrane by various means such as pad-printing [52], blade-casting [63], screen-printing [64], spray-coating [65] and the thickness obtained by these methods is often in the order of 1 or  $2 \mu m$ . Carbon grease, powder and elastomer have sheet resistances in the order of  $10s \, k\Omega$  per square.

# 2.4 Example of DEA applications requiring integrated addressing

Among the DEA applications, several require more the control of 10s to 1000s actuators to operate. Up to now these applications have required bulky external circuits to operate. To achieve compact devices an integrated high voltage switch driving the DEA is a critical building block that has been missing up to now.

In this section, we present two examples of such applications, haptic displays and soft robots, that would take advantage of integrated high-voltage control addressing.

## 2.4.1 Haptic displays

A haptic display is a display composed of 10s to 1000s of tactile pixels, often refered as taxels. Each taxel is an actuator providing a tactile information to a user. It can be a dynamic information such as a vibration (e.g. provided by a piezoelectric actuator) or a a static bump such as a Braille dot (e.g. provided by an out-of-plane actuator at mechanical equilibrium).

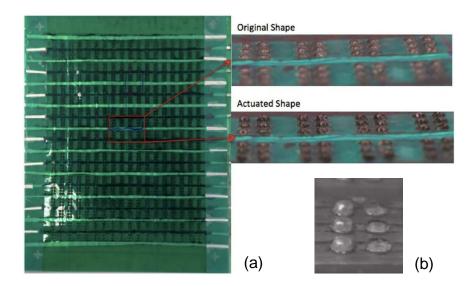

Figure 2.6 – (a)Haptic display made of more than 1000 DEAs. (b)Picture of an "l" in the Braille alphabet a DEA based haptic display. Each dot requires independent addressing so that every group of 6 dot can form every letter of the Braille alphabet.(Adapted from [15, 16])

Active braille sheets, in particular, can be an interesting application of out-of-plane DEA. A Braille display requires a refreshing rate < 100 ms, a force > 150 mN at a vertical displacement > 250  $\mu$ m and its taxels have to operate after 10<sup>7</sup> cycles [66]. A DEA-based braille display can take advantage of the actuator's high refreshing rate, the flexibility, the high cycle lifetime and vertical displacement > 100  $\mu$ m.

Figure 2.6 reports a braille display based on DEA and bistable electroactive polymer technology [15] reported in 2014. The actuation of one dot generates a displacement >  $500 \,\mu$ m. It includes

324 Braille cells, i.e. 1944 actuators requiring individual driving, motivating thus the need of integrated high voltage switches instead of bulky external addressing.

The low-force generated by in-plane expansion of such devices (< 1 mN) has classically been a problem for DEA base haptic displays. In this case, the problem is overcome by using thermally bistable electroactive polymers as the dielectric elastomer material [15, 16]. Other work report the use of liquid [32, 67] or rigid coupling [68, 69]. Alternatively, stacked DEAs can be used [37] or DEAs with bias mechanisms consisting in springs to amplify the force [70].

Up to date, one of the biggest challenge that has not been addressed is the requirement of "a high-voltage active matrix control circuitry which is currently unavailable" (sic [15]). Prior to this thesis, no work had been published demonstrating successful addressing of dielectric elastomer actuators haptic displays with active integrated controls.

# 2.4.2 Soft robots

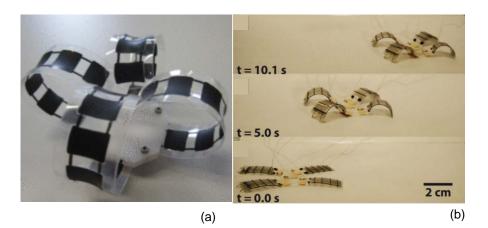

A soft robot is made of soft structural or functional elements [71]. Figure 2.7 shows different soft robots applications made of DEA that could take advantages of the implementation of high voltage thin-film transistors (HVTFTs).

Figure 2.7a shows four soft grippers made of four DEA segments [30]. When a high voltage is applied to this gripper every segment opens simultaneously. By controlling independently each segment, we would be able fabricate flexible, lightweight, compact articulated grippers with multiple degrees of freedom. For this, the integration compact flexible high voltage switches is required at every independent segment.

Another advantage of DEAs in soft robotics compared to other soft actuators comes from their very high speed, enabling very fast displacement. As an example, an inchworm robot made of DEAs has recently been demonstrated to be able to move at a speed of 1 body-length per

second [34]. Figure 2.7b shows a four legged robots [34] fabricated using the same principle as the grippers described by [31]. The robot has 5 layer stacked structure to amplify the force 1 DEA can generate. Compared to an inchworm robot actuator, composed of a single arm crawling, multi-legged robots have higher directional control and could combine several modes of displacement (walking, crawling, etc...). Integrating HVTFTs with this technology would enable to make all actuators independent from one another and integrate directly the power supply on the body of the robot with compact microcontrollers, moving forward towards untethered soft robots. Also adding thin film transistors on the leg of the soft robot could enable articulated motion by separating the DEAs in several segments, similarly to [30]. Adding HVTFTs could also enable the integration of smart sensors able to detect collision or self-switching the walking motion in a closed-loop, towards autonomous robots.

These two examples motivate the need for integrated HVTFTs. Compact addressing of several actuators in a soft robots with integrated flexible switches has not been demonstrated yet and would be a breakthrough for soft robotics.

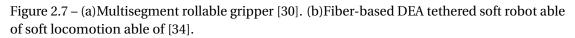

# 2.5 Reducing the operation voltage of DEAs vs addressing high voltage DEAs with low-voltage switches

Up to this point, we have seen the qualities, the working principle, the materials of DEAs and applications requiring addressing. From Equation 2.1, we have seen that the reduction of the membrane thickness reduces the voltage required to actuate a DEA. Intuitively, it would therefore be practical to reduce the voltage of DEAs down to several volts and address them with performant flexible low-voltage thin-film transistor (TFT) or with miniaturized silicon-chips integrated on flexible substrates as shown in [72] rather than designing HVTFTs. However, shrinking down DEAs comes at the cost of the DEA force and displacement [73]. In particular, shrinking down the membrane of the DEA means increasing the stiffening impact of the electrodes on the DEA, limiting thus the actuation strain [43, 52]. Figure 2.8 shows the effect of shrinking down of DEA with 2  $\mu$ m electrodes on the actuation strain, highlighting how the stiffening impact limits the actuation stretch. When the DEA has a membrane above 50  $\mu$ m the drop in actuation stretch is negligible. For 5  $\mu$ m thick membranes, the actuation strain drops by 50 %. Shrinking down the electrodes have recently been demonstrated to avoid stiffening impact [74], with a DEA having a maximum actuation strain of 7% at 150 V but at the cost of an electrode resistance higher than 20 M $\Omega$  per square.

Figure 2.8 – (a) Lateral stretch vs voltage for different membrane thickness under constant thickness 2  $\mu$ m electrodes. (b)Normalized lateral strain evolution vs the membrane thickness with 2  $\mu$ m electrodes. The dashed curves represent devices for which we would neglect the stiffening impact (Adapted from [73]).

By designing a high-voltage TFT, we can keep processing DEAs operating higher than 500 V, while switching them with a voltage lower than 100 V, a voltage that can be controlled with compact commercial components that can be integrated on foil.

# **3** High voltage thin film transistors: fundamentals and technologies

# Summary

This chapter covers fundamentals of thin-film transistors (TFTs) and high voltage thin-film transistors (HVTFTs) for operation above 100 V.

First, we introduce the TFT technology as an alternative technology to crystalline silicon (c-Si) metal oxide semiconductor field effect transistor (MOSFET) to be processed on insulated flexible substrate. We compare the four main semiconducting channel technologies that can be used for TFTs, amorphous silicon (a-Si), polycristalline silicon (poly-Si), organic polymers and metal oxides (MOxs). The latter, MOxs is the only one having demonstrated at the same time TFTs with high mobility (up to 100 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> [75]), good uniformity over a large area and stability under mechanical stress.

Afterwards, we present the working principle of TFTs and figures of merit to determine if a TFT behaves as a good switch: the threshold voltage, the gate voltage swing, the on-off current ratio and the on-current.

Then, based on these figures of merit, we classify and compare the HVTFTs reported up to date. From this classification, we identify a trade-off between performance and high voltage operation. The highest on-off ratio and on-current are achieved for the TFTs with the lowest operation voltage typically below 400 V. Only a-Si HVTFTs were reported operating above 500 V, specifically at 800 V [76].

Finally we report the failure mechanisms in HVTFTs and identify the ones that are specific to a channel technology. Kink effect makes poly-Si HVTFTs complicated to use for applications above 400 V. Channel length modulation and space charge limited current (SCLC) in organic HVTFTs lead to transistor failure above 500 V. Only a-Si and MOx technologies appear to be viable for applications > 500 V. However the limitation in on-current, typically in the  $\mu$ A range, for a-Si make us select MOx as the channel semiconductor for the HVTFTs of this thesis.

# 3.1 Introduction to TFT technology

A field effect transistor (FET) is a component with three terminals, a source, a drain and a gate. When a potential is applied at the drain or the source and at the gate, the current flow between the source and the drain is modulated. Therefore, a FET can act as a switch. A FET can operate as a p-type device or an n-type device, depending on the channel's majority carriers. The respective charge transport carriers of n-type and p-type devices are electrons and holes.

In this section, we first describe the TFT technology, a particular case of FET. Then, we describe the different TFTs channel technologies and compare them.

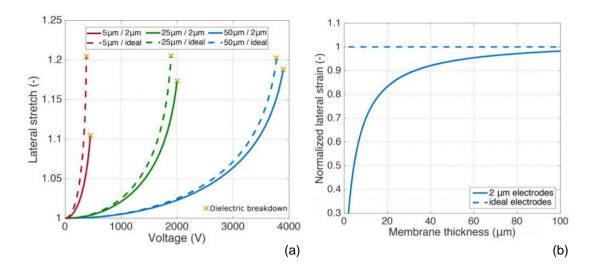

# 3.1.1 MOSFETs and TFTs

Today, the most widely used FET is the MOSFET. Table 3.1 and Figure 3.1 show the main differences between MOSFET and TFTs.

|                      | MOSFET                                            | TFT                                              |

|----------------------|---------------------------------------------------|--------------------------------------------------|

| Channel technologies | c-Si                                              | Mainly poly-Si, a-Si, organic, MOx               |

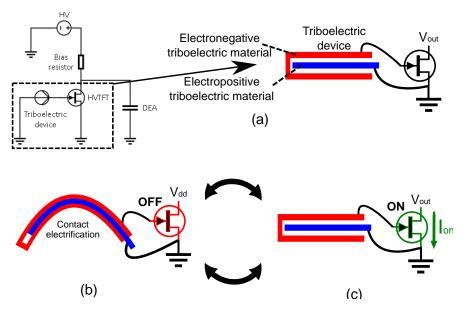

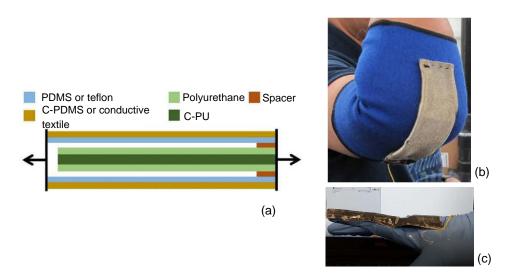

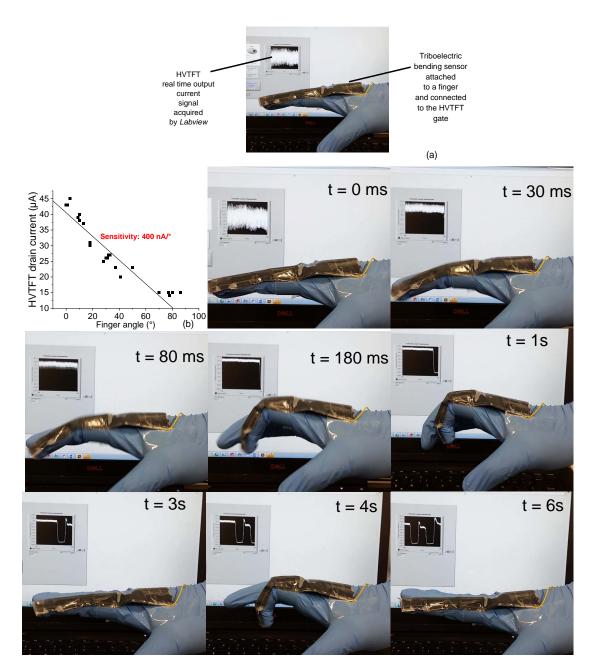

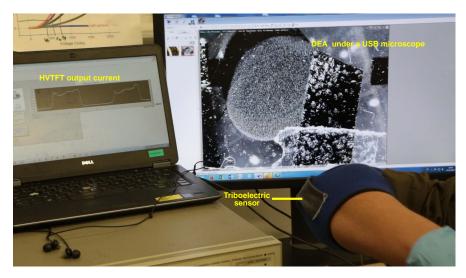

| Conduction mode      | Inversion                                         | Accumulation                                     |