# Self-Heating Aware Design of ICs in Deep Sub-Micron FDSOI and Bulk Technologies

#### THÈSE N° 8690 (2018)

PRÉSENTÉE LE 6 JUILLET 2018

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR LABORATOIRE DE SYSTÈMES MICROÉLECTRONIQUES PROGRAMME DOCTORAL EN GÉNIE ÉLECTRIQUE

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

Can BALTACI

acceptée sur proposition du jury:

Prof. A. P. Burg, président du jury Prof. Y. Leblebici, Dr T. Toifl, directeurs de thèse Prof. V. F. Pavlidis, rapporteur Dr T. Ernst, rapporteur Prof. C. Dehollain, rapporteuse

## Acknowledgements

First and foremost, I would like to express my sincere gratitude to Prof. Yusuf Leblebici for giving me the opportunity to spend more than six years in an excellent academic atmosphere. His contributions to me are countless, not only as a supervisor but also as a person, he is an example in every respect.

I would also like to thank Dr. Thomas Toifl for sharing his valuable experience as my co-advisor and the thesis committee members Prof. Andreas P. Burg, Prof. Vasilis F. Pavlidis, Dr. Thomas Ernst and Prof. Catherine Dehollain for their contribution and insightful comments. I would like to thank Dr. Alain Vachoux, Dr. Alexandre Schmid, Tuğba Demirci and Slyvain Hauser for their technical support in LSM. I must also thank Samsung Flash Memory Team for the two-month I spent with them; it was a precious learning experience.

Thanks to Buğra, Kerem Kapucu and Kerem Seyid, I had amazing time outside work. The lunch breaks and the random events we had after work were priceless. I am also thankful to my friends Ahmet, Cenk, Çağlar, Erhan and Fatih. I would like to thank many Turkish people in Switzerland, Cem-Handan, Meriç-Nariye, Başak-İsmail, Ece and Dilan for their friendship.

I am thankful to my students Krishna Pradeep, Mustafa Beşirli, Nicolas Claude Frigerio and Cloé Sophie Liberté Roy for their contributions in my work. I also thank all the current and former LSM members: Mustafa, Selman, Şeniz, İrem, Cosimo, Jonathan, Navid, Elmira, Behnoush, Jury, Gain, Clemens, İlter, Alessandro, Kiarash, Armin, Vladan, Nicola, Radisav, Ömer, Gözen, Kadir, Duygu, Firat, Ayça for being the best colleagues.

Most importantly, I am what I am thanks to my parents Olcay and Eray. I am grateful to them for their endless support, patience and love.

Finally, I would like to thank Elsa. Without her, none of these would be possible.

Can Baltacı Lausanne, May 2018

### **Abstract**

Bulk CMOS technologies left the semiconductor market to the novel device geometries such as FDSOI and FinFET below 30 nm, mainly due to their insufficient electrical characteristics arising from different physical limitations. These innovative solutions enabled the ongoing device scaling to continue. However, the threshold voltage and the power supply values did not shrink with the device sizes, which caused an excessive amount of heat generation in very small dimensions. With the high thermal resistivity materials used in FDSOI and FinFET, the generated heat cannot leave the device easily, which is not the case in bulk. With all of these, modern geometries brought a major problem, which is the self-heating.

Due to self-heating effects (SHE), the temperature of a device rises significantly compared to its surroundings. Having very large local temperature brings important reliability issues. Moreover, the electrical behaviour of a device also changes dramatically when its temperature is very large. These facts bring the need of considering SHE and the temperature of each device separately. Nevertheless, in many of today's CAD tools, a single global temperature is applied to all of the devices. Even if some advanced simulation options are used, estimating the temperature of a device is not a simple task as it depends on many parameters.

The focus of this thesis is to show the significance of SHE in the design of ICs and provide self-heating aware design guidelines. In order to achieve this, different circuit implementations are studied by considering the SHE. The study consists of two main parts, which are the reliability of the high-speed digital circuits and the performance of analog blocks where noise is critical. Moreover, detailed device-level electro-thermal simulations are performed to explain the self-heating phenomena more in detail and to perform a comparison between bulk and FDSOI.

The digital part of the self-heating study is performed on two very high-speed full-custom 64-bit Kogge-Stone adders in 40 nm and 28 nm technologies. Thermal simulations are performed on these blocks to compare SHE in bulk and FDSOI geometries. The comparison of two implementations also provides the increasing significance of SHE with scaling. Extensive heating analyses are performed to find the most critical devices that are the primary heat generators. Design guidelines and solutions are proposed to flatten the temperature profiles in precharged and static logic implementations and to decrease the probability of electromigration.

The analog study of the work focuses on the thermal noise performance of LNAs and SHE on the flicker noise. Since thermal noise of a device linearly depends on the temperature, it is directly affected by SHE. To show the amount of SHE on the noise figure, three common gate cascode LNAs operating at 2 GHz with different device lengths are implemented in 28 nm FDSOI. The measurements show that the self-heating effects are clearly observed on the noise figure and the performance of the blocks deviate importantly from the simulations. Moreover, the self-heating effects are significantly more in short channel devices due to their large heat density. Similar experiments are also performed on different test structures in FDSOI at lower frequencies to observe SHE on flicker noise. The experiments show that flicker noise degrades at larger temperatures and more in short channel implementations.

Keywords: Self-Heating Effects, FDSOI, bulk, high speed digital, 64-bit adders, reliability, integrated inductors, low noise amplifiers, thermal noise, flicker noise

### Résumé

Les technologies CMOS bulk ont laissé le marché des semi-conducteurs aux nouvelles géométries de dispositifs telles que FDSOI et FinFET en dessous de 30 nm, principalement en raison de leurs caractéristiques électriques insuffisantes résultant de différentes limitations physiques. Ces solutions innovantes ont permis la poursuite de la mise à l'échelle des dispositifs. Cependant, la tension de seuil et les valeurs d'alimentation n'ont pas rétréci avec la taille des dispositifs, ce qui a provoqué une génération excessive de chaleur dans de très petites dimensions. Avec les matériaux à haute résistivité thermique utilisés dans FDSOI et FinFET, la chaleur générée ne peut pas quitter le dispositif facilement, ce qui n'est pas le cas en bulk. A cause de tout cela, les géométries modernes ont apporté un problème majeur : l'auto-échauffement.

En raison des effets d'auto-échauffement, la température d'un dispositif augmente considérablement par rapport à son environnement. Avoir de très grandes températures locales apporte d'importants problèmes de fiabilité. De plus, le comportement électrique d'un dispositif change également de façon spectaculaire lorsque sa température est très élevée. Ces faits apportent le besoin de considérer les effets d'auto-échauffement et la température de chaque dispositif séparément. Néanmoins, dans la plupart des outils de CAO actuels, une seule température globale est appliquée à tous les dispositifs. Même si certaines options de simulation avancées sont utilisées, l'estimation de la température d'un dispositif n'est pas une tâche simple car elle dépend de nombreux paramètres.

L'objectif de cette thèse est de montrer l'importance des effets d'auto-échauffement dans la conception des circtuis intégrés et de fournir des directives de conception prenant en compte l'auto-échauffement. Pour ce faire, différentes implémentations de circuits sont étudiées en considérant les effets d'auto-échauffement. L'étude se compose de deux parties principales, à savoir la fiabilité des circuits numériques haute vitesse et la performance des blocs analogiques où le bruit est critique. De plus, des simulations électrothermiques détaillées au niveau du dispositif sont effectuées pour expliquer plus en détail les phénomènes d'auto-échauffement et pour effectuer une comparaison entre le FDSOI et le bulk.

La partie numérique de l'étude d'auto-échauffement est réalisée sur deux additionneurs

#### Résumé

Kogge-Stone 64 bits à très haute vitesse, entièrement personnalisés, dans des technologies 40 nm et 28 nm. Des simulations thermiques sont réalisées sur ces blocs pour comparer les effets d'auto-échauffement dans les géométries bulk et FDSOI. La comparaison de deux implémentations fournit également l'importance croissante des effets d'auto-échauffement avec la mise à l'échelle. Des analyses d'échauffement approfondies sont effectuées pour trouver les dispositifs les plus critiques qui sont les principaux générateurs de chaleur. Des lignes directrices et des solutions de conception sont proposées pour aplatir les profils de température dans les implémentations logiques préchargées et statiques, et pour diminuer la probabilité d'électromigration.

L'étude analogique du travail se concentre sur la performance de bruit thermique des LNAs et des effets d'auto-échauffement sur le bruit de scintillation. Puisque le bruit thermique d'un dispositif dépend linéairement de la température, il est directement affecté par des effets d'auto-échauffement. Pour montrer la quantité des effets d'auto-échauffement sur la figure de bruit, trois LNAs de cascode à grille commune fonctionnant à 2 GHz avec des longueurs de dispositifs différentes sont implémentés en FDSOI 28 nm. Les mesures montrent que les effets d'auto-échauffement sont clairement observés sur le chiffre de bruit et que les performances des blocs s'écartent fortement des simulations. De plus, les effets d'auto-échauffement sont significativement plus importants dans les dispositifs à canaux courts en raison de leur grande densité de chaleur. Des expériences similaires sont également effectuées sur différentes structures de test en FDSOI à des fréquences plus basses pour observer les effets d'auto-échauffement sur le bruit de scintillation. Les expériences montrent que le bruit de scintillation se dégrade à des températures plus élevées et encore plus dans des implémentations à canaux courts.

Mots clés : Effets auto-échauffants, FDSOI, bulk, numérique haute vitesse, additionneurs 64 bits, fiabilité, inductances intégrées, amplificateurs à faible bruit, bruit thermique et bruit de scintillation

## Contents

| A  | knov    | vledgements                                              | i    |

|----|---------|----------------------------------------------------------|------|

| Al | ostra   | et (English/Français)                                    | iii  |

| Ta | ıble o  | f Contents                                               | ix   |

| Li | st of ] | Figures                                                  | хi   |

| Li | st of   | Гables                                                   | xvii |

| 1  | Intr    | oduction                                                 | 1    |

|    | 1.1     | Operation at a Different Temperature                     | 1    |

|    |         | 1.1.1 Heating or Self-Heating?                           | 2    |

|    |         | 1.1.2 Observing Self-Heating Effects                     | 3    |

|    |         | 1.1.3 Why a Single Device?                               | 5    |

|    |         | 1.1.4 Self-Heating Related Issues                        | 6    |

|    |         | 1.1.5 Scope of This Work                                 | 7    |

|    | 1.2     | State of the Art                                         | 7    |

|    | 1.3     | Key Contributions of This Thesis                         | 10   |

|    | 1.4     | Thesis Outline                                           | 11   |

| 2  | Dev     | ice Level Analysis of Self-Heating                       | 13   |

|    | 2.1     | Introduction                                             | 13   |

|    | 2.2     | Theoretical Background and Related Work                  | 14   |

|    |         | 2.2.1 Block Level Thermal Simulations                    | 14   |

|    |         | 2.2.2 Device Level Thermal Simulations                   | 15   |

|    | 2.3     | Details of Our Device Level Simulations                  | 17   |

|    | 2.4     | Comparison of FDSOI and Bulk                             | 19   |

|    |         | 2.4.1 Physical Structure and Thermal Boundary Conditions | 19   |

|    |         | 2.4.2 Results and Discussions                            | 21   |

|    | 2.5     | Experiments on FDSOI                                     | 25   |

|    |         | 2.5.1 Effect of Drain Voltage                            | 25   |

|    |         | 2.5.2 Effect of Gate Voltage                             | 27   |

|    |         | 2.5.3 Effect of Gate Length                              | 29   |

|    |         | 2.5.4 Effect of BOX Thickness                            | 31   |

#### **Contents**

|   |             | 2.5.5 Effect of Drain and Source Contact Thermal Resistance  | 31  |

|---|-------------|--------------------------------------------------------------|-----|

|   | 2.6         | Conclusion                                                   | 32  |

| 3 | The         | rmal Aware Design of High Performance Digital Circuits       | 33  |

| • | 3.1         | Introduction                                                 | 33  |

|   | 3.2         | Method for Block Level Thermal Simulations                   | 35  |

|   | o. <b>_</b> | 3.2.1 Creation of Heat Maps                                  | 36  |

|   |             | 3.2.2 Thermal Model                                          | 37  |

|   |             | 3.2.3 Creation of Temperature Maps                           | 39  |

|   | 3.3         | Design of 64-bit Parallel Prefix Adders for Thermal Analysis | 39  |

|   | 5.5         | 3.3.1 Architecture                                           | 40  |

|   |             | 3.3.2 Performance                                            | 45  |

|   | 3.4         | Comparison of Bulk and FDSOI in 40 nm and 28 nm Nodes        | 47  |

|   | 3.4         | 3.4.1 Heating                                                | 47  |

|   |             |                                                              | 51  |

|   |             | 3.4.2 Temperature                                            |     |

|   | 2.5         | 3.4.3 Simulation Time                                        | 64  |

|   | 3.5         | Circuit Level Analysis of Hot-Spots                          | 65  |

|   |             | 3.5.1 Heat Density of Individual Devices                     | 65  |

|   |             | 3.5.2 Self-Heating of Devices with Different Functions       | 67  |

|   | 3.6         | Conclusion                                                   | 72  |

| 4 | Self        | -Heating Effects on the Noise Performance of FDSOI MOSFETs   | 73  |

|   | 4.1         | Introduction                                                 | 73  |

|   | 4.2         | Thermal Noise                                                | 74  |

|   |             | 4.2.1 Theoretical Background and Related Work                | 75  |

|   |             | 4.2.2 Thermal Noise Considering Self-Heating                 | 76  |

|   | 4.3         | Flicker Noise                                                | 82  |

|   |             | 4.3.1 Theoretical Background and Related Work                | 82  |

|   |             | 4.3.2 Flicker Noise Considering Self-Heating                 | 84  |

|   | 4.4         | Conclusion                                                   | 85  |

| 5 | Self        | -<br>Heating Aware Design of LNAs with Short Channel Devices | 87  |

|   | 5.1         | Integrated Inductor Design                                   | 87  |

|   |             | 5.1.1 Undesired Effects                                      | 88  |

|   |             | 5.1.2 Lumped Model of an Integrated Inductor                 | 89  |

|   |             | 5.1.3 Parametric Cell (pCell) for Integrated Inductors       | 94  |

|   | 5.2         | Common Gate Cascode LNA                                      | 99  |

|   | 0.2         | 5.2.1 Design Parameters                                      | 99  |

|   |             |                                                              | 110 |

|   | 5.3         | -                                                            | 115 |

|   | 5.5         |                                                              | 117 |

|   |             |                                                              |     |

|   | E 4         |                                                              | 120 |

|   | 5.4         | CONCIUSION                                                   | 120 |

| Contents | 5 |

|----------|---|

|          |   |

| 6  | Flic   | ker No | ise Measurements         | 121 |

|----|--------|--------|--------------------------|-----|

|    | 6.1    | Test B | locks                    | 121 |

|    |        | 6.1.1  | Practical Considerations | 123 |

|    |        | 6.1.2  | Input Referred Noise     | 126 |

|    | 6.2    | Meası  | urement Results          | 128 |

|    |        | 6.2.1  | Measurement Procedure    | 130 |

|    |        | 6.2.2  | Results of Experiment-A  | 136 |

|    |        | 6.2.3  | Results of Experiment-B  | 139 |

|    | 6.3    | Concl  | usion                    | 142 |

| 7  | Con    | clusio | n                        | 143 |

| Bi | bliog  | graphy |                          | 156 |

| Cu | ırricı | ulum V | Titae Titae              |     |

# List of Figures

| 1.1  | Independent of the activity of any other devices and the ambient temperature,       |    |

|------|-------------------------------------------------------------------------------------|----|

|      | the characteristics of M0 changes while passing from the state shown on (a) to      |    |

|      | the one shown on (b) due to its self-heating. The influence of self-heating effects |    |

|      | depends on the temperature difference $T_1 - T_0$                                   | 3  |

| 1.2  | Performance and reliability issues created by self-heating effects. Black lines     |    |

|      | encircle the items that are the focus of this work                                  | 6  |

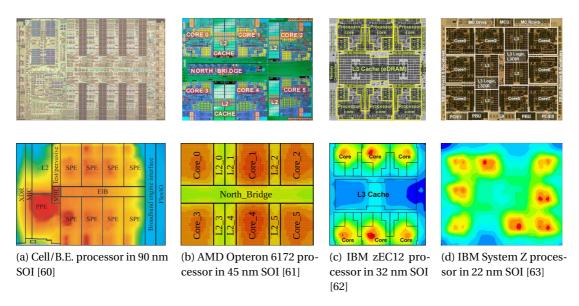

| 1.3  | Block level thermal simulations performed on different processors in SOI tech-      |    |

|      | nologies                                                                            | 8  |

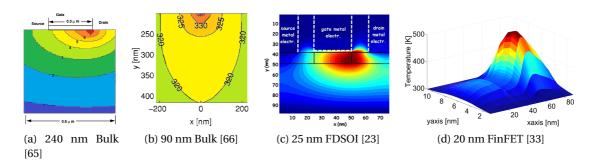

| 1.4  | Device level electro-thermal simulations performed in different technology          |    |

|      | nodes and geometries                                                                | 9  |

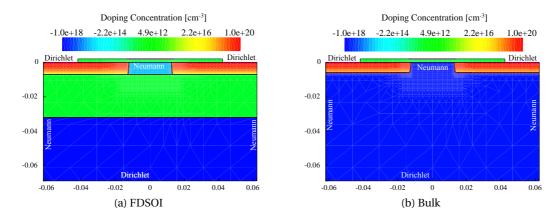

| 2.1  | Doping profiles of (a) the FDSOI and (b) the bulk device structures. The positive   |    |

|      | doping values are used to denote n-type doping, and negative values for the         |    |

|      | p-type doping                                                                       | 20 |

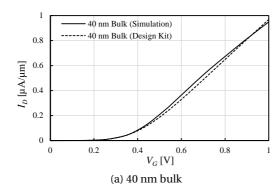

| 2.2  | Comparison of simulated 40 nm bulk and 28 nm FDSOI MOSFETs and the design           |    |

|      | kit models in terms of their $I_D$ - $V_G$ characteristics                          | 21 |

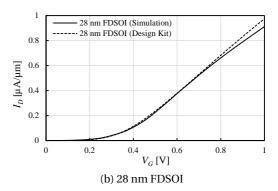

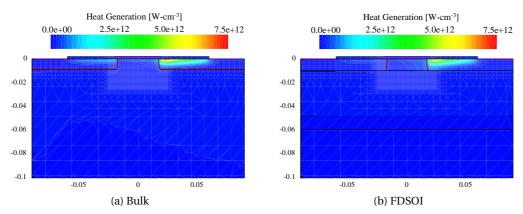

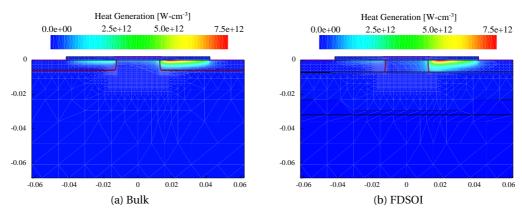

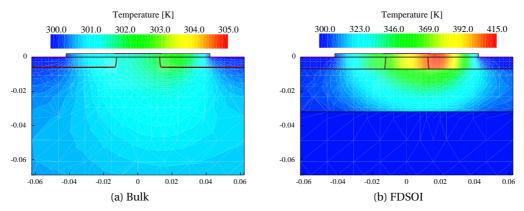

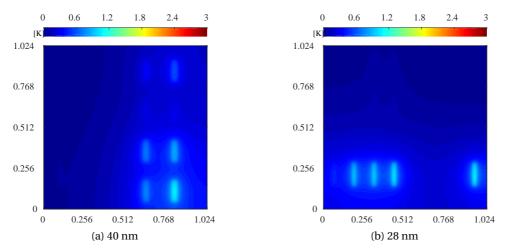

| 2.3  | Spatial heat generation profile of 40 nm (a) bulk and (b) FDSOI devices             | 22 |

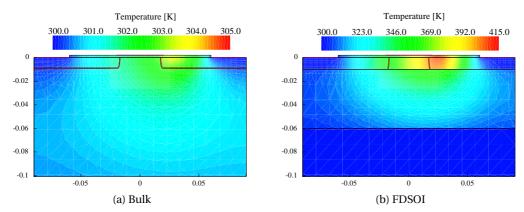

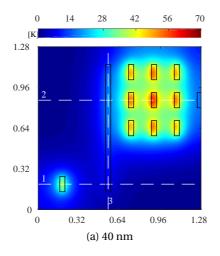

| 2.4  | Spatial temperature profile of 40 nm (a) bulk and (b) FDSOI devices                 | 22 |

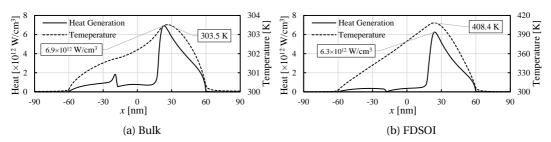

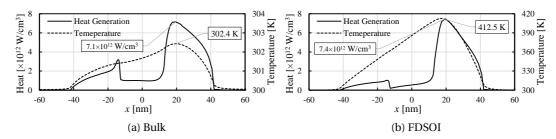

| 2.5  | Heat generation and temperature profiles of 40 nm (a) bulk and (b) FDSOI at $y =$   |    |

|      | -1 nm                                                                               | 22 |

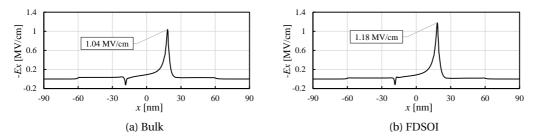

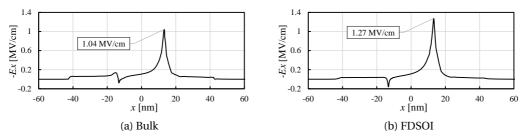

| 2.6  | Lateral electric field in 40 nm (a) bulk and (b) FDSOI MOSFETs at $y=-1$ nm         | 22 |

| 2.7  | Spatial heat generation profile of 28 nm (a) bulk and (b) FDSOI devices             | 23 |

| 2.8  | Spatial temperature profile of 28 nm (a) bulk and (b) FDSOI devices                 | 23 |

| 2.9  | Heat generation and temperature profiles of 28 nm (a) bulk and (b) FDSOI at $y =$   |    |

|      | -1 nm                                                                               | 23 |

| 2.10 | Lateral electric field in 28 nm (a) bulk and (b) FDSOI MOSFETs at $y = -1$ nm       | 23 |

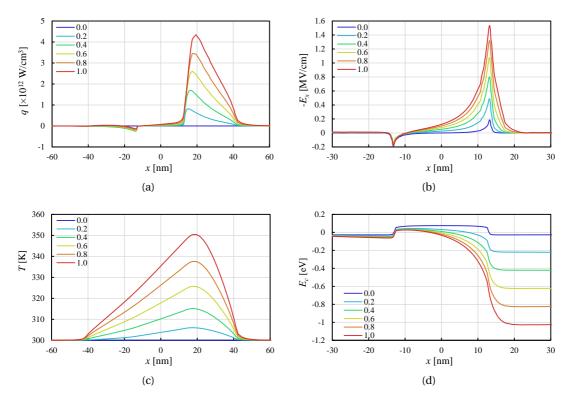

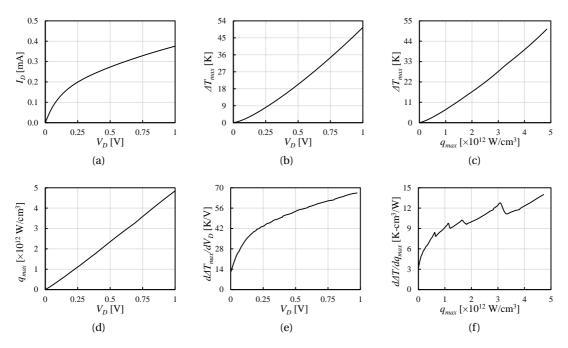

| 2.11 | (a) heat generation, (b) lateral component of the electric field, (c) temperature   |    |

|      | and (d) conduction band energy inside the channel for different values of $V_D$     |    |

|      | while $V_G$ is constant at 0.6 V                                                    | 26 |

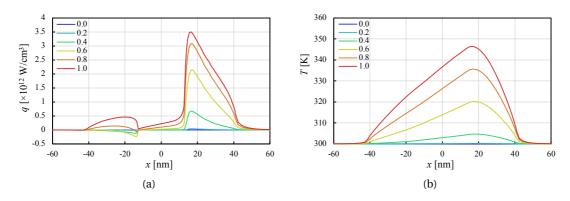

| 2.12 | Simulation results for $V_D$ swept from 0 V to 1 V while $V_G$ = 0.6 V              | 26 |

| 2.13 | (a) heat generation and (b) temperature inside the channel for different values     |    |

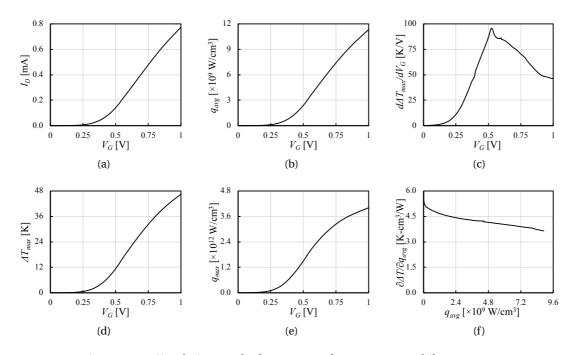

|      | of $V_G$ while $V_D$ is constant at 0.5 V                                           | 28 |

| 2.14 | Simulation results for $V_G$ swept from 0 V to 1 V while $V_D$ = 0.5 V              | 28 |

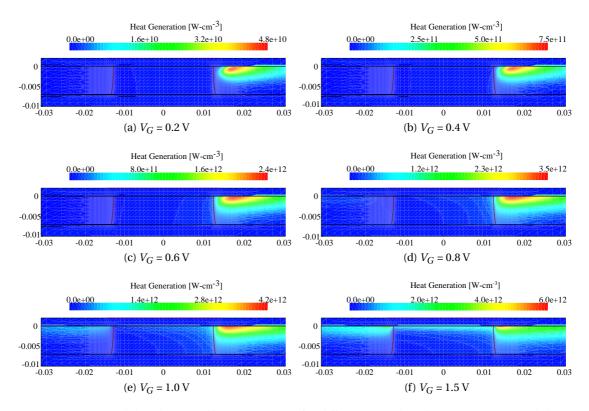

#### **List of Figures**

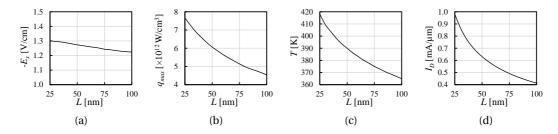

| 2.15 | Spatial distribution of heat generation for different $V_G$ values from 0.2 V to 1.5 V while $V_D$ is kept constant at 0.5 V                                                                                                                                                  | 29 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.16 | (a) Maximum lateral electric field, (b) maximum heat generation, (c) maximum temperature and (d) full bias drain current with respect to gate length for the 28                                                                                                               |    |

|      | nm FDSOI technology                                                                                                                                                                                                                                                           | 30 |

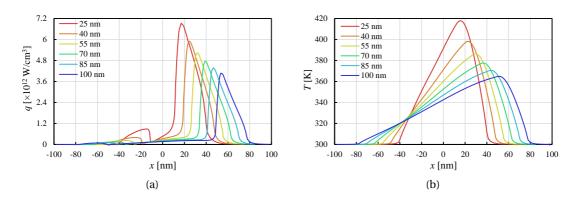

| 2.17 | (a) Heat generation and (b) temperature inside the channel for different the gate length values in 28 nm FDSOI technology.                                                                                                                                                    | 30 |

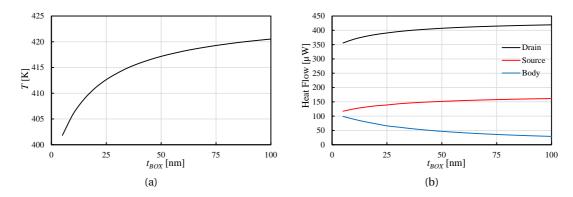

| 2.18 | (a) Temperature and (b) heat flow with respect to BOX thickness                                                                                                                                                                                                               | 31 |

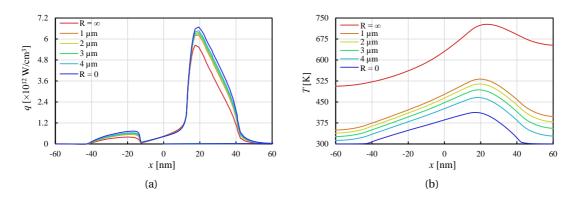

| 2.19 | (a) Heat generation and (b) temperature inside the channel for different thermal boundary conditions for drain and source                                                                                                                                                     | 32 |

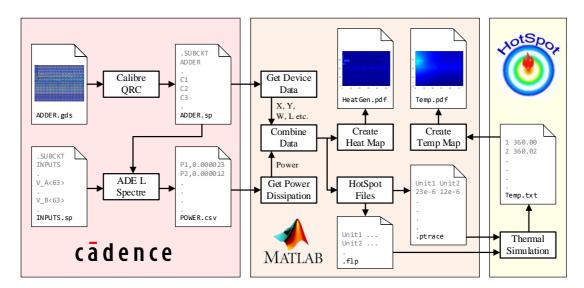

| 3.1  | Thermal analysis flow and data exchange between the used tools                                                                                                                                                                                                                | 35 |

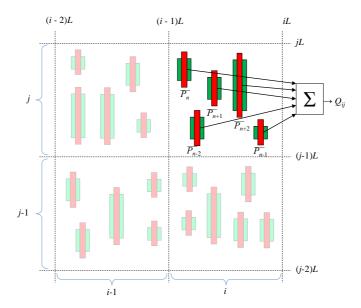

| 3.2  | Summation of the independent heat sources located in the same square                                                                                                                                                                                                          | 37 |

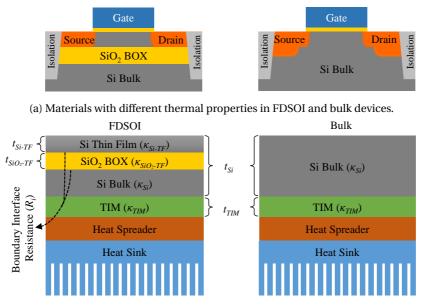

| 3.3  | Thermal models of FDSOI (left) and bulk (right)                                                                                                                                                                                                                               | 38 |

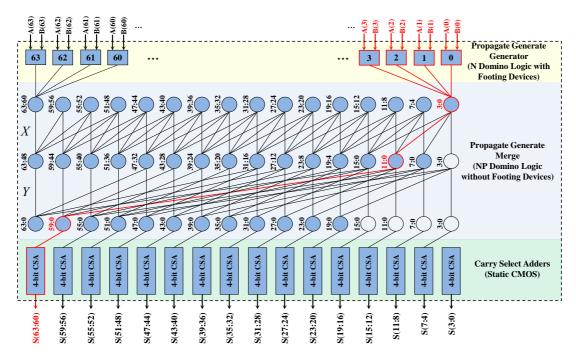

| 3.4  | The architectural block diagram of the implemented 64-bit Kogge-Stone parallel prefix adders with the radix-4 and sparsity-4 options. The input/output nodes, signal names and the hardware blocks on the critical path are indicated with red                                |    |

|      | colour                                                                                                                                                                                                                                                                        | 40 |

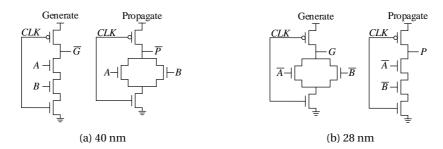

| 3.5  | Schematics of N-domino logic PG-Generator gates in (a) 40 nm and (b) 28 nm. The devices at the bottom are the clocked footing devices [1]                                                                                                                                     | 41 |

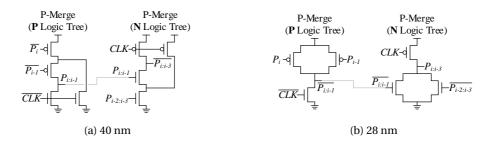

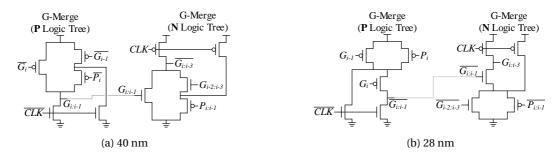

| 3.6  | Schematics of NP-domino logic P-Merge gates used in (a) 40 nm and (b) 28 nm.                                                                                                                                                                                                  | 43 |

| 3.7  | Schematics of NP-domino logic G-Merge gates used in (a) 40 nm and (b) $28 \text{ nm}$ .                                                                                                                                                                                       | 43 |

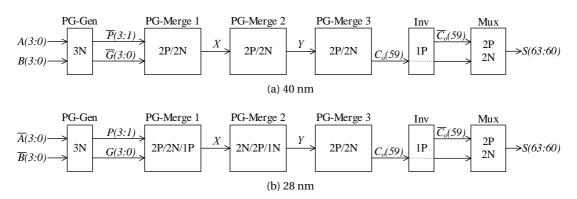

| 3.8  | The number and type of the devices on the critical path of (a) the 40 nm and (b) the 28 nm adder.                                                                                                                                                                             | 43 |

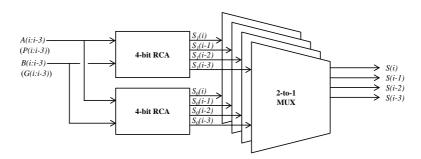

| 3.9  | The block diagram of the 4-bit CSA. The $S_1(i)$ and $S_0(i)$ signals at the outputs of the two 4-bit ripple carry adders are the sum signals which are generated for the                                                                                                     |    |

|      | two cases where $C_i$ is equal to 1 and 0 respectively                                                                                                                                                                                                                        | 45 |

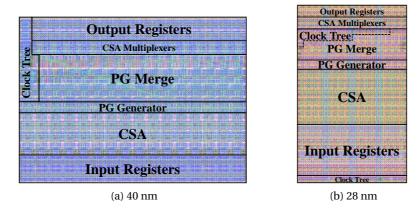

| 3.10 | The layouts and floorplans of the implemented 64-bit adders in (a) 40 nm and (b) 28 nm. Thermal simulations are performed on these areas                                                                                                                                      | 45 |

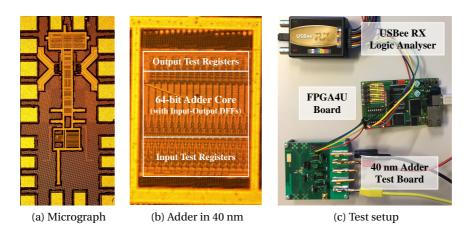

| 3.11 | (a) The die micrograph, (b) zoomed micrograph and (c) the test setup of the implemented 64-bit adder in 40 nm. Thermal simulations are performed on the                                                                                                                       |    |

|      | 64-bit adder core block                                                                                                                                                                                                                                                       | 46 |

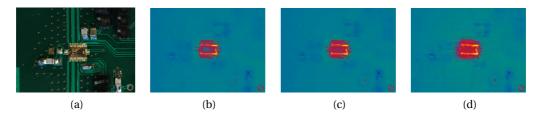

| 3.12 | Thermal images of the 40 nm adder taken during tests. (a) the visible image of the board where the thermal images are taken, (b) thermal image just before the addition begins, (c) thermal image just after the addition begins and (d) 20 seconds after the addition begins | 47 |

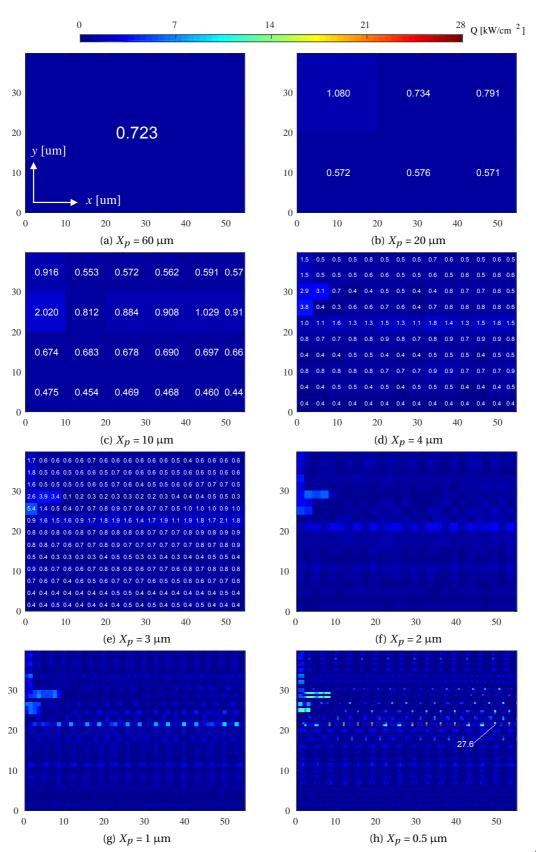

| 3.13 | Heat maps of the 40 nm adder for different pitch values. Heat density unit is $W/cm^2$                                                                                                                                                                                        | 48 |

| 3.14 | Heat maps of the 28 nm adder for different pitch values. Heat density unit is $W/cm^2$                                                                                                                                                                                        | 49 |

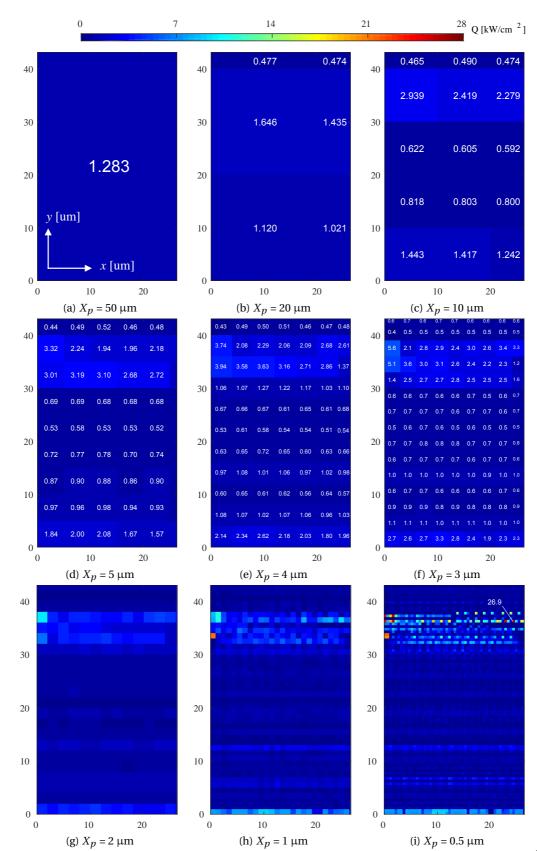

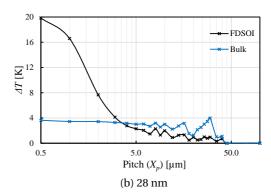

| 3.15          | Maximum and minimum heat density curves for heat maps with different resolu-<br>tions. Maximum heat density saturates as the pitch value becomes comparable |    |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|               | to the minimum length of the specified technology, whereas the minimum heat                                                                                 |    |

|               | density drops to 0 W/cm <sup>2</sup> as resolution increases                                                                                                | 50 |

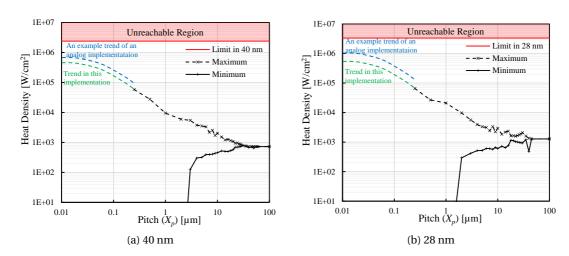

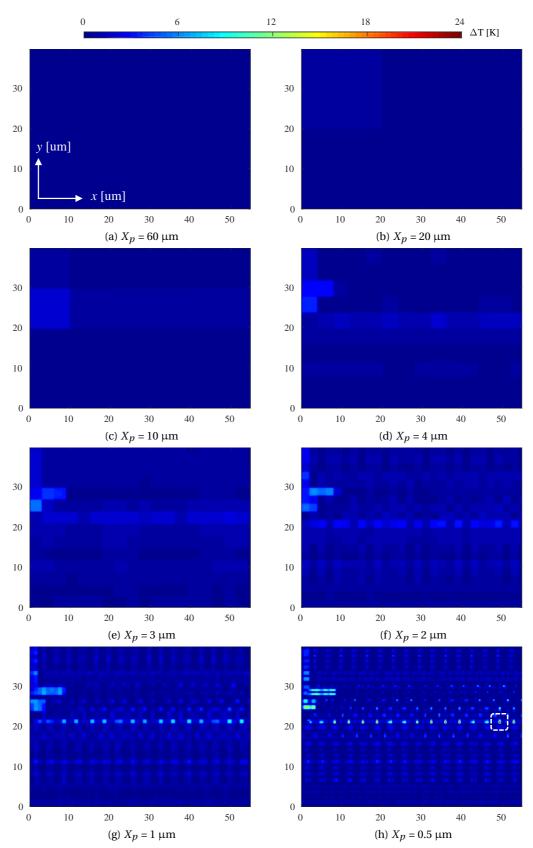

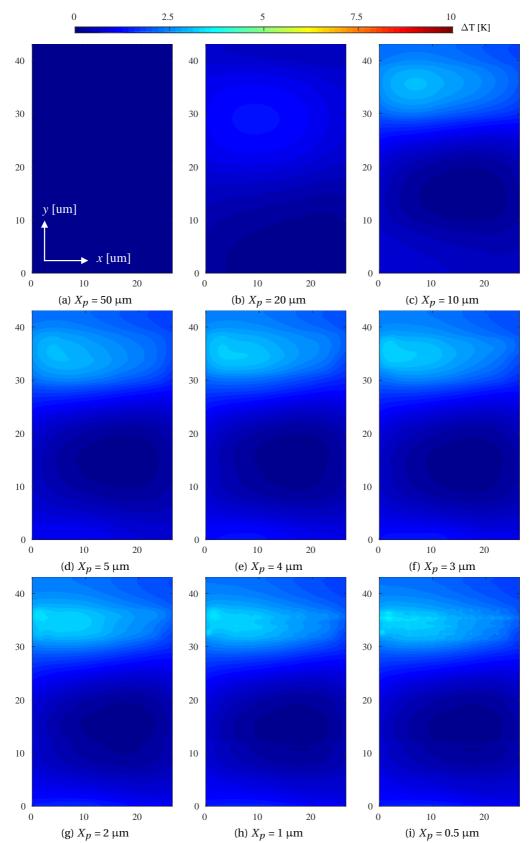

| 3.16          | Temperature maps of the 40 nm adder in bulk geometry for different pitch values.                                                                            |    |

|               | Temperature maps of the 40 nm adder in FDSOI geometry for different pitch                                                                                   |    |

| 0.1.          | values.                                                                                                                                                     | 53 |

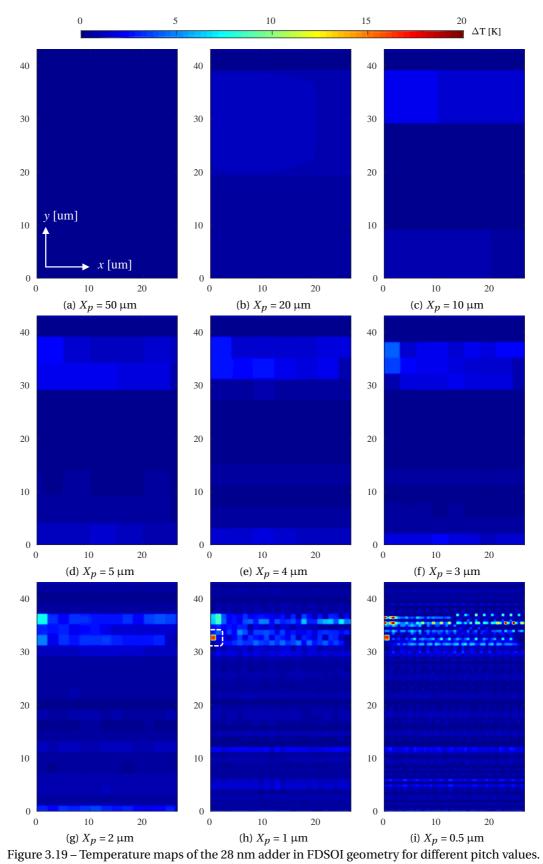

| 3.18          | Temperature maps of the 28 nm adder in bulk geometry for different pitch values.                                                                            |    |

|               | Temperature maps of the 28 nm adder in FDSOI geometry for different pitch                                                                                   |    |

| 0.10          | values.                                                                                                                                                     | 55 |

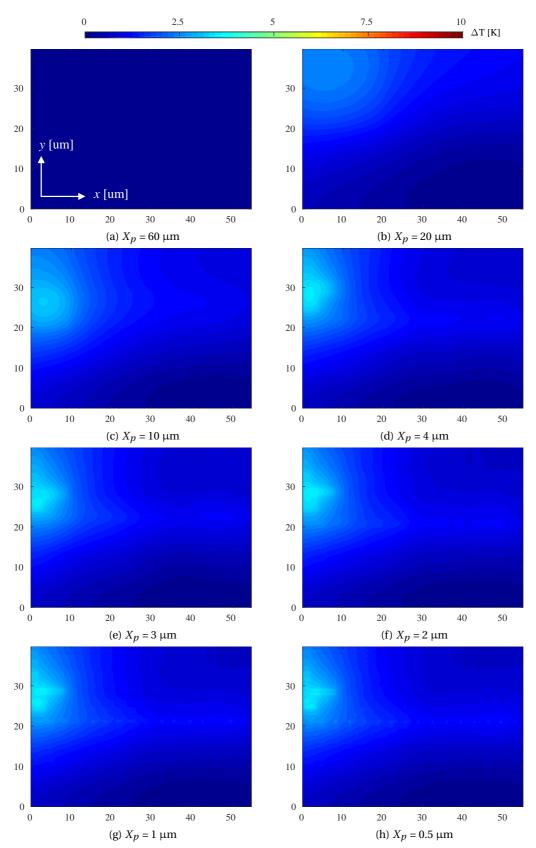

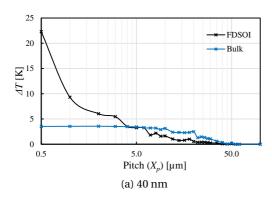

| 3.20          | Maximum and minimum temperature values for all temperature maps with                                                                                        |    |

| o. <b>_</b> o | heating inputs of different resolutions.                                                                                                                    | 56 |

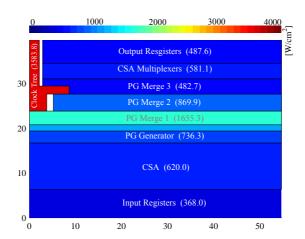

| 3.21          | Heat map of different blocks in 40 nm with their individual heating ( <i>x</i> and <i>y</i> in                                                              |    |

|               | μm)                                                                                                                                                         | 57 |

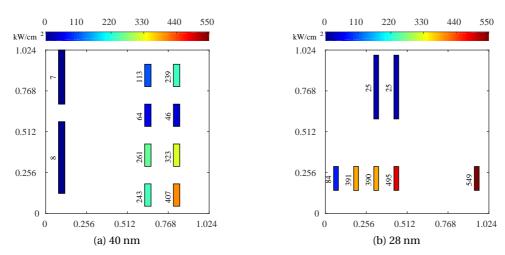

| 3.22          | Heat maps of (a) 40 nm and (b) 28 nm technologies focused on the hot-spots                                                                                  | 60 |

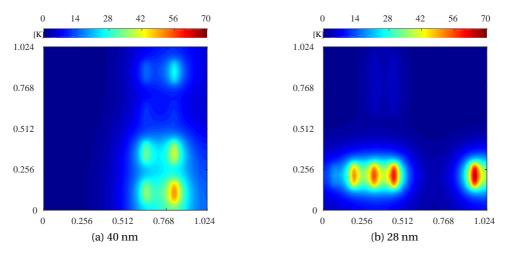

|               | Temperature maps of (a) 40 nm and (b) 28 nm FDSOI technologies focused on                                                                                   |    |

|               | the hot-spots.                                                                                                                                              | 60 |

| 3.24          | Temperature maps of (a) 40 nm and (b) 28 nm bulk technologies focused on the                                                                                |    |

|               | hot-spots.                                                                                                                                                  | 60 |

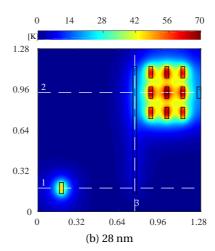

| 3.25          | Heat maps of (a) 40 nm and (b) 28 nm for observing extreme case temperature                                                                                 |    |

|               | profiles                                                                                                                                                    | 63 |

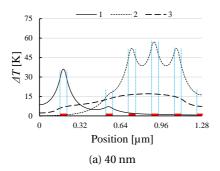

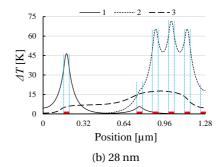

| 3.26          | Temperature profiles of (a) 40 nm and (b) 28 nm due to the heating inputs of                                                                                |    |

|               | Figure 3.25                                                                                                                                                 | 63 |

| 3.27          | Temperature profiles along the cut-lines (Figure 3.26) taken at the centre of the                                                                           |    |

|               | devices. The red thick lines show the location of the devices on Figure 3.26                                                                                | 63 |

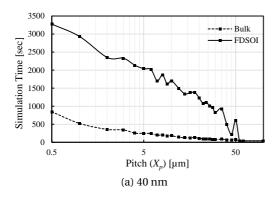

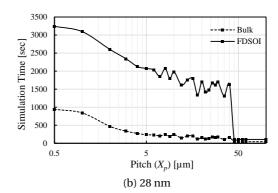

| 3.28          | Simulation time of bulk and FDSOI with respect to pitch. In this analysis the                                                                               |    |

|               | resolution of the heating input is swept while the resolution of the thermal                                                                                |    |

|               | simulation is fixed at 2048 $\times$ 2048                                                                                                                   | 64 |

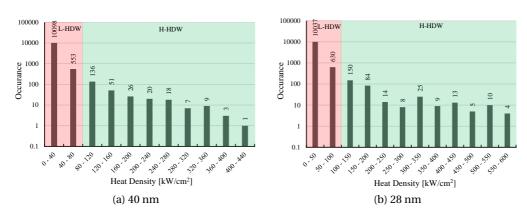

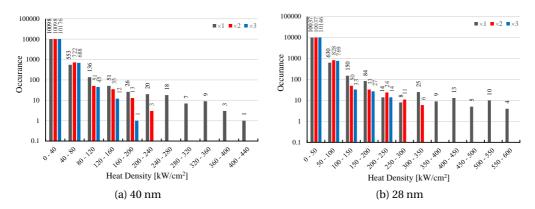

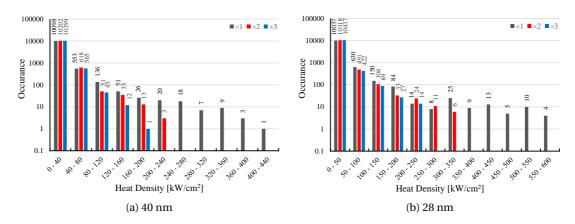

| 3.29          | Heat density distribution of the transistors in the 64-bit adder circuits                                                                                   | 66 |

| 3.30          | The heat density distribution after increasing the width of the high heat density                                                                           |    |

|               | devices by a factor of 2 and 3                                                                                                                              | 66 |

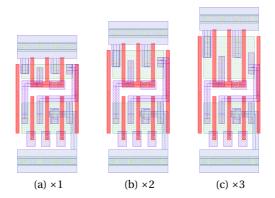

| 3.31          | Standard cell of a <i>Generate-Merge</i> gate with different size pre-charge devices                                                                        | 67 |

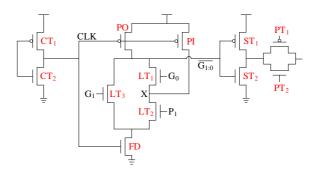

| 3.32          | The schematic that illustrates the devices belonging to different groups. The                                                                               |    |

|               | logic gate in the centre corresponds to the domino logic implementation of                                                                                  |    |

|               | Generate-Merge function with N-type logic tree                                                                                                              | 68 |

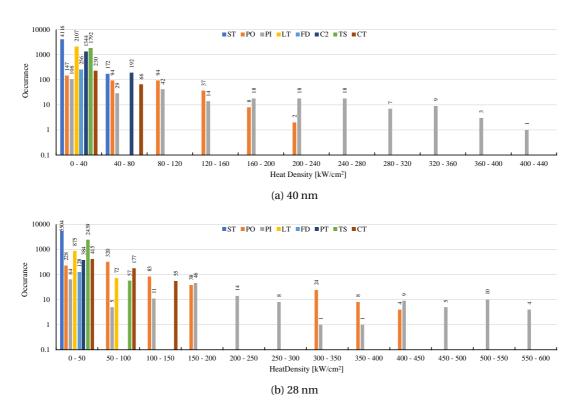

| 3.33          | Distribution of heat density for different group of devices in the 64-bit adders                                                                            |    |

|               | implemented in (a) 40 nm and (b) 28 nm                                                                                                                      | 69 |

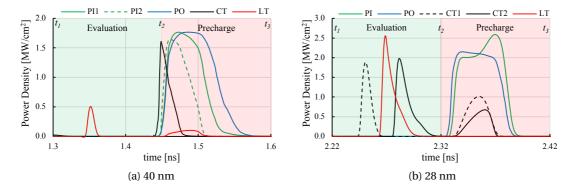

| 3.34          | Time domain power dissipation density waveforms of devices from different                                                                                   |    |

|               | groups                                                                                                                                                      | 70 |

| 3.35          | The heat density distribution after increasing the width of the PI and PO devices                                                                           |    |

|               | by a factor of 2 and 3                                                                                                                                      | 71 |

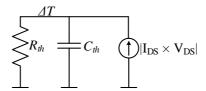

| 4.1 | The thermal model that provides the temperature rise of each device due to their self-heating [2]                                                                                                                                                                                                                                                                               | 74       |

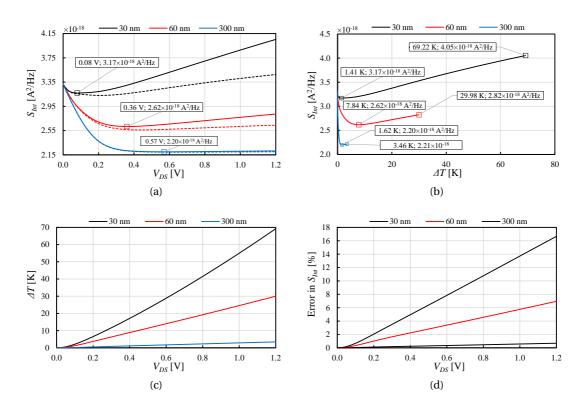

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

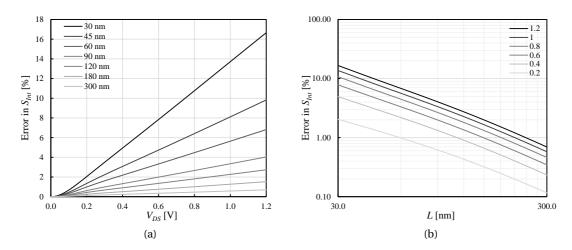

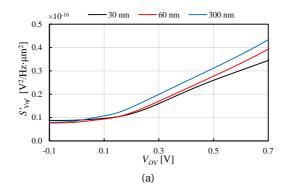

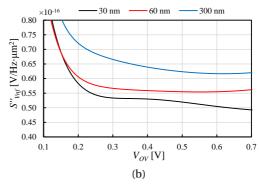

| 4.2 | Thermal noise current and temperature of 30 nm, 60 nm and 300 nm nMOS devices as $V_{DS}$ is changed. The continuous curves correspond to the case where self-heating effects are considered and the dashed curves correspond to the case where there are irreary decreases and the continuous curves correspond to the case where the continuous curves are irreary decreases. | 77       |

| 4.3 | where they are ignored                                                                                                                                                                                                                                                                                                                                                          | 77<br>78 |

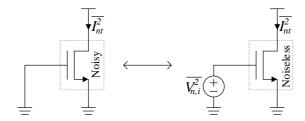

| 4.4 | Model of the noisy device with a fictitious input referred noise voltage source $\overline{V_{n_i}^2}$                                                                                                                                                                                                                                                                          |          |

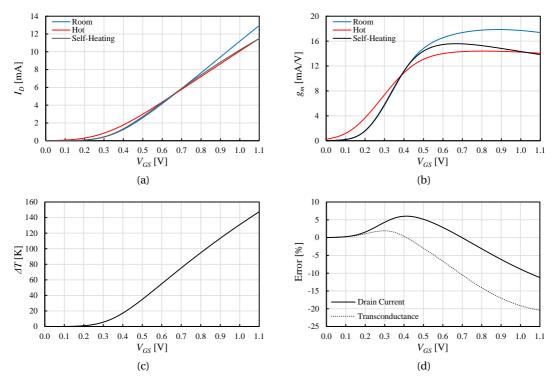

| 4.5 | (a) drain current, (b) transconductance, (c) temperature rise due to self-heating, (d) the calculation error in drain current and transconductance when self-                                                                                                                                                                                                                   | 13       |

| 4.6 | heating effects are not considered                                                                                                                                                                                                                                                                                                                                              | 80       |

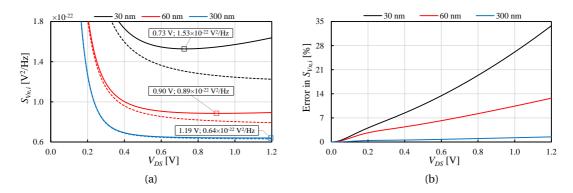

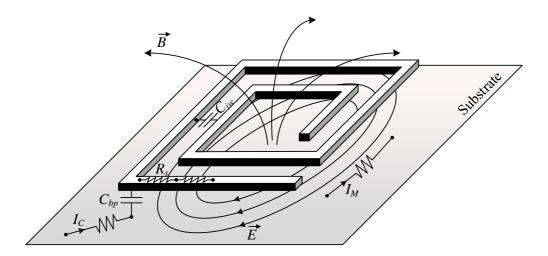

| 4.7 | heating effects are ignored. The devices are biased with $V_G$ = 0.6 V (a) Flicker noise voltage normalized with respect to effective device area and (b)                                                                                                                                                                                                                       | 81       |

| 4.7 |                                                                                                                                                                                                                                                                                                                                                                                 | 83       |

| 4.8 | (a) flicker noise voltage at the gate at 20 MHz according to (4.8) and (b) its calculation error when self-heating effects are ignored. The devices are biased                                                                                                                                                                                                                  |          |

|     |                                                                                                                                                                                                                                                                                                                                                                                 | 85       |

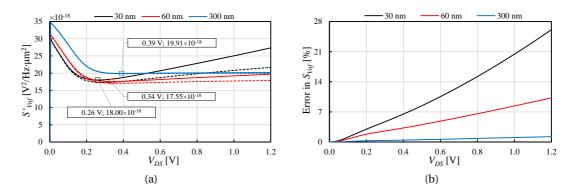

| 5.1 | Loss mechanisms of an integrated inductor                                                                                                                                                                                                                                                                                                                                       | 88       |

| 5.2 | Simple lumped models of an integrated inductor for different cases: (a) ideal, (b) first order lumped model where only the winding series resistance is taken into account, (c) more detailed model where other high frequency losses are                                                                                                                                       |          |

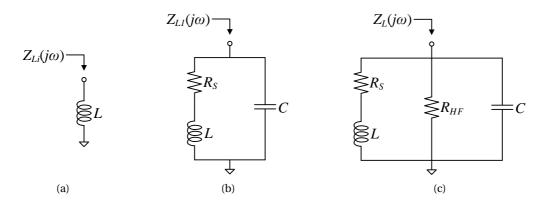

|     |                                                                                                                                                                                                                                                                                                                                                                                 | 90       |

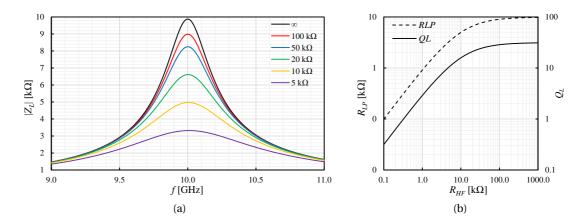

| 5.3 | Parallel <i>RLC</i> representations of the models on (a) Figure 5.2b and (b) Figure 5.2c                                                                                                                                                                                                                                                                                        | 91       |

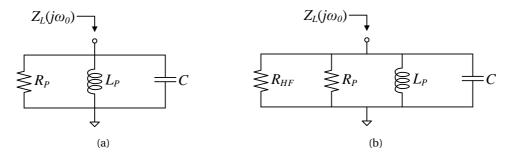

| 5.4 | Behaviours of $ Z_{L1} $ , $R_P$ and $Q_S$ with respect to the inductor series resistance $R_S$ for $f_0 = 10$ GHz, $L = 5$ nH and $C = 50.7$ fF                                                                                                                                                                                                                                | 92       |

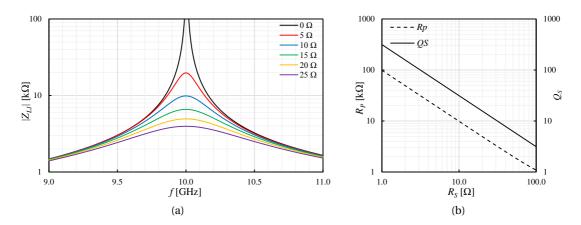

| 5.5 | •                                                                                                                                                                                                                                                                                                                                                                               | -        |

|     |                                                                                                                                                                                                                                                                                                                                                                                 | 93       |

| 5.6 | Layout screen-shots and cross-section views of the (a) two-stacked and (b)                                                                                                                                                                                                                                                                                                      |          |

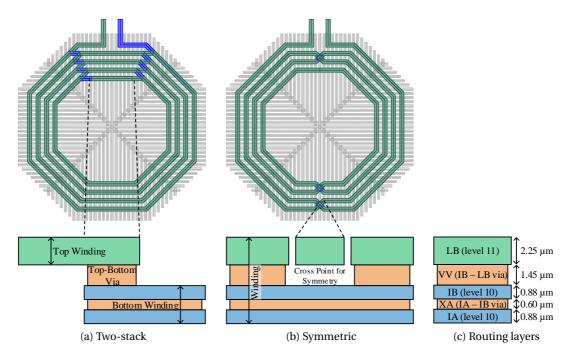

|     | symmetric inductor pCells synthesized in 28 nm FDSOI technology                                                                                                                                                                                                                                                                                                                 | 95       |

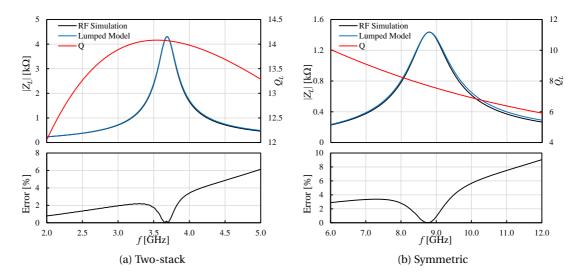

| 5.7 | Comparison of the behaviours of the RF simulation results and lumped model                                                                                                                                                                                                                                                                                                      | 07       |

| E 0 | of (a) a two-stack and (b) a symmetric integrated inductor                                                                                                                                                                                                                                                                                                                      | 97       |

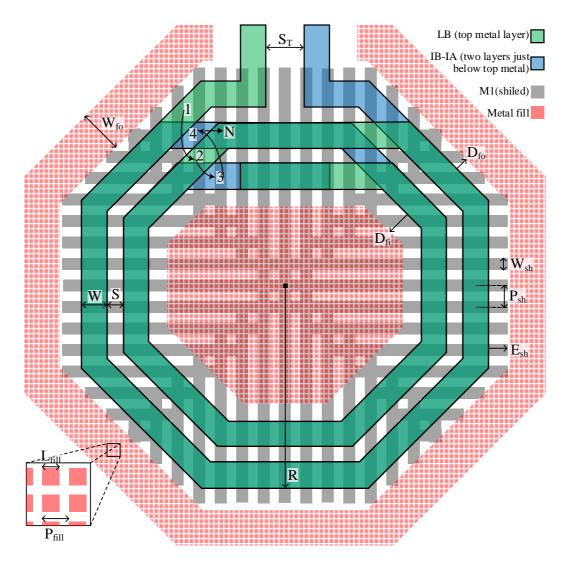

| 5.8 | Example of the integrated stacked inductor drawing and its adjustable parameters.<br>Behaviours of the inductor parameters as (a) the shield pitch of the inductor                                                                                                                                                                                                              | 90       |

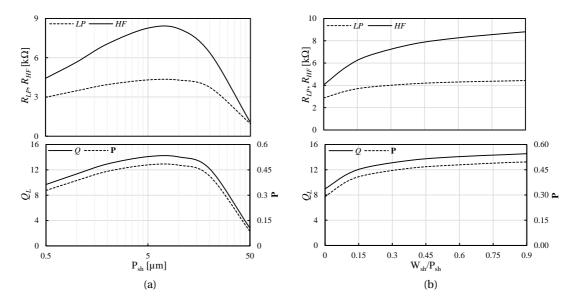

| 5.9 | •                                                                                                                                                                                                                                                                                                                                                                               |          |

|     | was changed while shield-width/shield-nitch ratio was kent constant at W-L/P-L                                                                                                                                                                                                                                                                                                  |          |

|     | was changed while shield-width/shield-pitch ratio was kept constant at $W_{sh}/P_{sh}$ = 0.6, (b) shield width was changed while shield pitch was kept constant at                                                                                                                                                                                                              |          |

|     | = 0.6, (b) shield width was changed while shield pitch was kept constant at                                                                                                                                                                                                                                                                                                     | 99       |

| 5.11 | Small-signal AC model used for finding the impedance seen from the source of a            |     |

|------|-------------------------------------------------------------------------------------------|-----|

|      | MOSFET while the drain is connected to an arbitrary impedance                             | 100 |

| 5.12 | Total input impedance (dashed lines) and equivalent parallel resistance (contin-          |     |

|      | uous lines) of three different LNAs with different gate lengths 30 nm, 45 nm and          |     |

|      | 180 nm (a) while looking into the source of M1 (b) seen from the PCB. $$                  | 104 |

| 5.13 | Tuning the input impedance by considering the off-chip parasitics: wirebonding            |     |

|      | inductance, $L_{wb}$ and parasitic capacitance of the PCB, $C_{PCB}$                      | 104 |

| 5.14 | Small-signal AC model used for finding the impedance seen from the drain of a             |     |

|      | MOSFET while the source is connected to an arbitrary impedance. $\ \ldots \ \ldots$       | 105 |

| 5.15 | Small-signal AC model of the common gate cascade LNA at $f_0$                             | 107 |

| 5.16 | Small-signal AC model of the common gate cascade LNA at $f_0$ with the indepen-           |     |

|      | dent noise sources                                                                        | 108 |

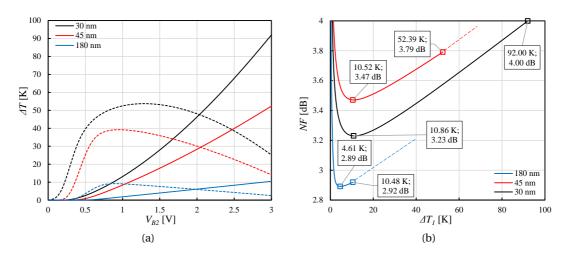

| 5.17 | Noise figure under different $V_{B2}$ levels when the supply voltage is set to 3 V        |     |

|      | for three different the common gate cascode LNA implementations with gate                 |     |

|      | lengths of (a) 30 nm, (a) 45 nm, (a) 180 nm. Continuous lines correspond to               |     |

|      | the case where self-heating effects are included and dashed lines are for the             |     |

|      | case where self-heating effects are excluded. (d) the calculation error when              |     |

|      | self-heating effects are not included                                                     | 112 |

| 5.18 | (a) temperature rise of M1 (continuous) and M2 (dashed) as $V_{B2}$ changes, (b)          |     |

|      | noise figure vs temperature rise of M1                                                    | 113 |

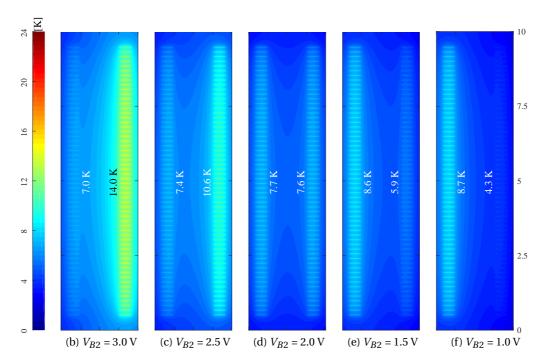

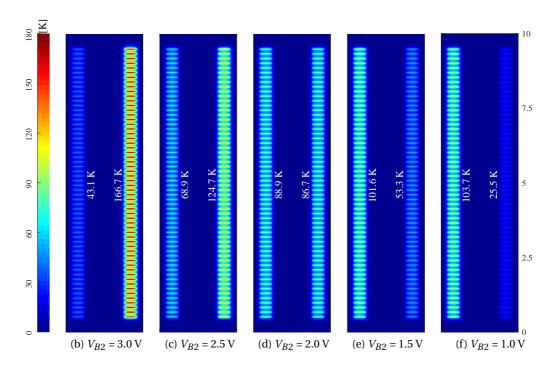

| 5.19 | $\Delta T$ profile of the common gate cascode LNA with $L = 30$ nm for the bulk thermal   |     |

|      | properties under different bias conditions provided by $V_{B2}$ while $V_{DD}$ = 3 V. The |     |

|      | observable devices are M2 and M1 from left to right. The spatial unit is $\mu m$          | 114 |

| 5.20 | $\Delta T$ profile of the common gate cascode LNA with $L = 30$ nm for the FDSOI          |     |

|      | thermal properties under different bias conditions provided by $V_{B2}$ while $V_{DD}$ =  |     |

|      | 3 V. The observable devices are M2 and M1 from left to right. The spatial unit is         |     |

|      | μm                                                                                        | 115 |

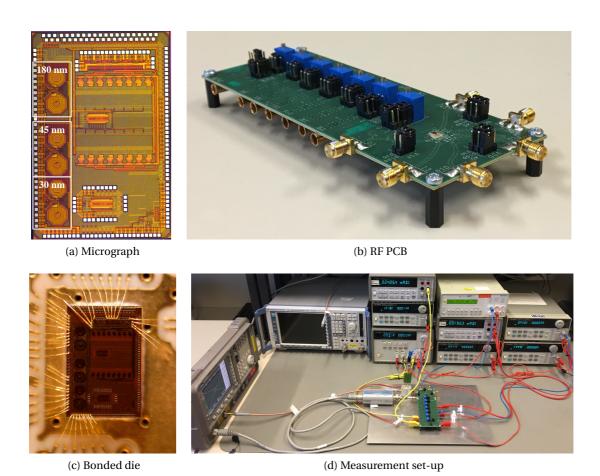

| 5.21 | (a) micrograph of the taped-out die where the three LNA implementations are               |     |

|      | indicated with the channel length values, (b) RF test board, (c) bonded die and           |     |

|      | (d) the measurement set-up.                                                               | 116 |

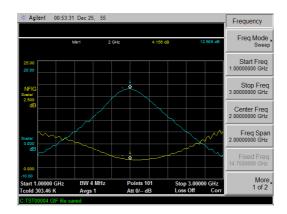

| 5.22 | Screen-shot of the N8975A screen, where the noise figure and gain of the 45 nm            |     |

|      | LNA can be seen for the 1 GHz - 3 GHz band                                                | 117 |

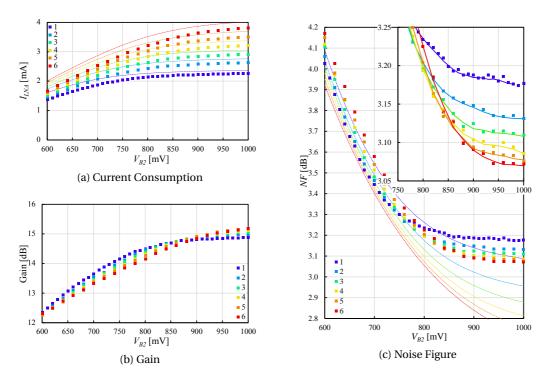

| 5.23 | Measurement results of (a) current consumption, (b) gain and (c) noise figure at          |     |

|      | 2 GHz of the LNA implemented with $L = 180$ nm                                            | 118 |

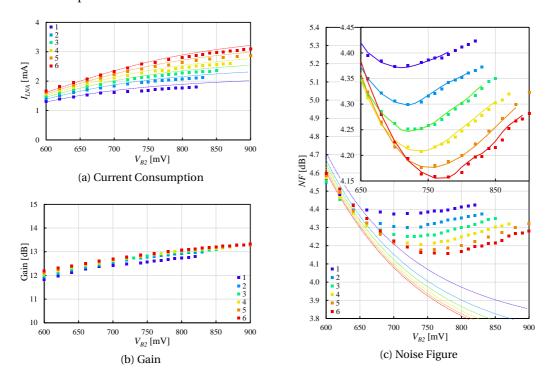

| 5.24 | Measurement results of (a) current consumption, (b) gain and (c) noise figure at          |     |

|      | 2 GHz of the LNA implemented with $L = 45$ nm                                             | 118 |

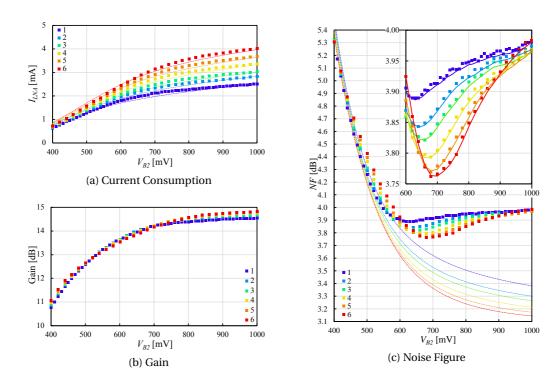

| 5.25 | Measurement results of (a) current consumption, (b) gain and (c) noise figure at          |     |

|      | 2 GHz of the LNA implemented with $L = 30$ nm                                             | 119 |

|      | *                                                                                         |     |

| 6.1  | Main parts of the two test structures for observing the flicker noise of a sin-           |     |

|      | gle MOSFET (M1). (a) experiment-A: common source and (b) experiment-B:                    |     |

|      | common source with a cascode device                                                       | 122 |

#### **List of Figures**

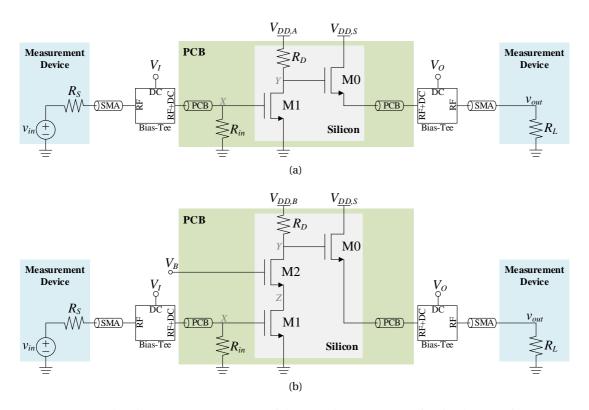

| 6.2  | Simple schematic representation of the complete test system for the designs of                                  |     |

|------|-----------------------------------------------------------------------------------------------------------------|-----|

|      | Figure 6.1                                                                                                      | 124 |

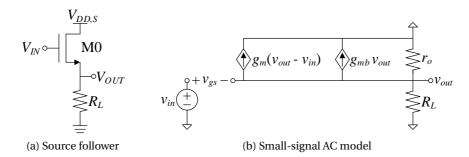

| 6.3  | (a) simple schematic of source follower and (b) its small-signal AC model                                       | 125 |

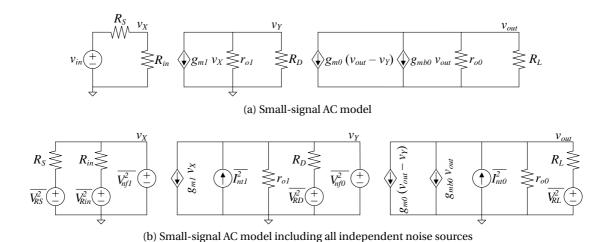

| 6.4  | Small signal AC models of the complete system of experiment-A                                                   | 127 |

| 6.5  | Small signal AC models of the complete system of experiment-B                                                   | 127 |

| 6.6  | (a) Micrograph of the taped-out die, (b) bonded die: gold wire-bonding is used                                  |     |

|      | for better electrical conductivity, (c) RF test board and (d) the measurement                                   |     |

|      | set-up. Many power supplies and multi-meters were necessary to provide the                                      |     |

|      | bias and supply voltages ( $V_I$ , $V_O$ , $V_B$ , $V_{DD,A}$ , $V_{DD,B}$ , $V_{DD,S}$ ) and measure different |     |

|      | currents for each data point.                                                                                   | 129 |

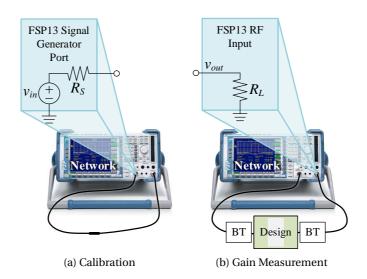

| 6.7  | Configurations of FSP for different steps of the gain measurement. Bias-tees are                                |     |

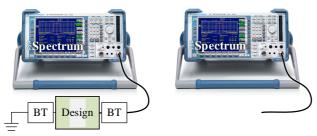

|      | indicated with BT                                                                                               | 131 |

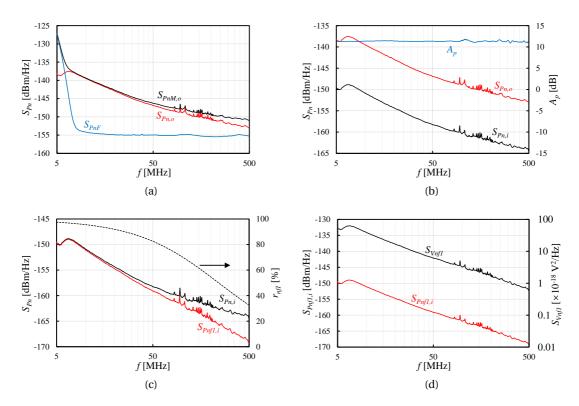

| 6.8  | Configurations of FSP for different steps of the noise measurement                                              | 132 |

| 6.9  | Noise power spectral densities at different stages of the set-up for obtaining the                              |     |

|      | flicker noise voltage of M1 from the measured noise power                                                       | 133 |

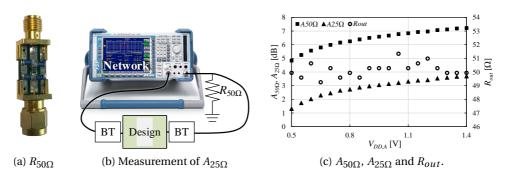

| 6.10 | (a) external SMA 50 $\Omega$ feed-through termination, (b) configuration of FSP for tun-                        |     |

|      | ing the output resistance to 50 $\Omega$ and (c) measured gain and output impedance                             |     |

|      | values                                                                                                          | 135 |

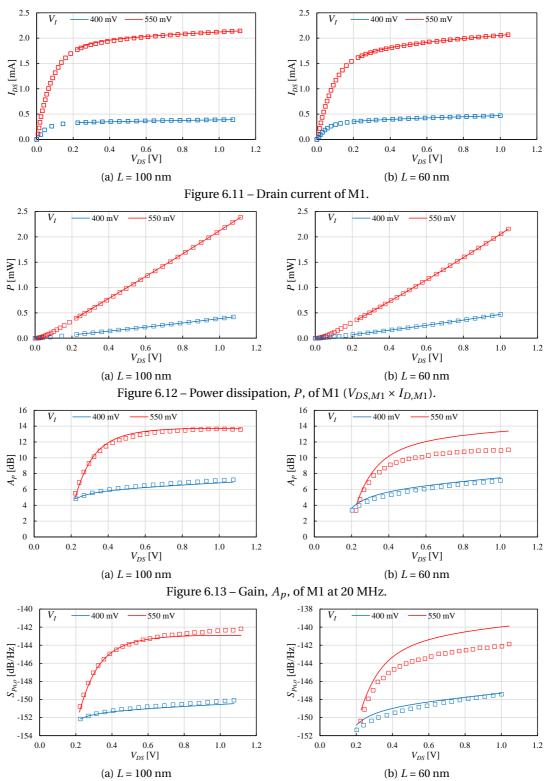

|      | Drain current of M1                                                                                             | 137 |

|      | Power dissipation, $P$ , of M1 ( $V_{DS,M1} \times I_{D,M1}$ )                                                  | 137 |

|      | Gain, $A_p$ , of M1 at 20 MHz                                                                                   | 137 |

|      | Output noise power spectral density, $S_{Pn,o}$ , of M1 at 20 MHz                                               | 137 |

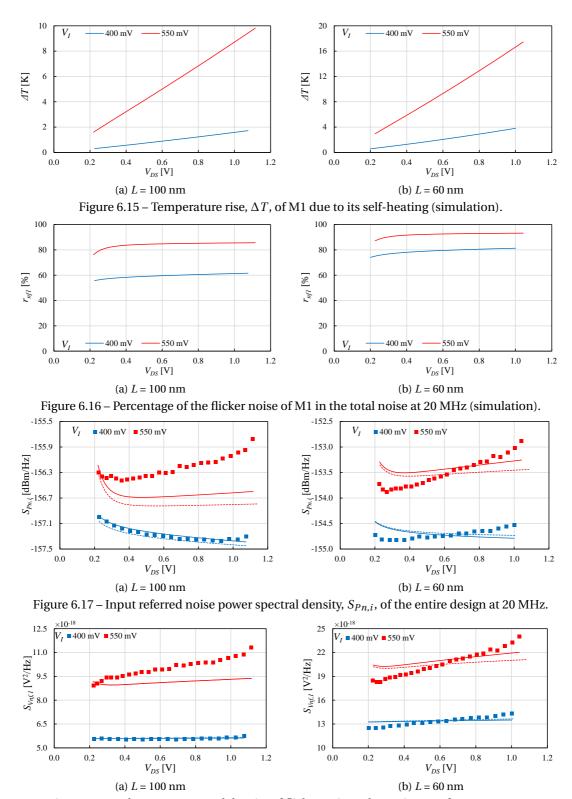

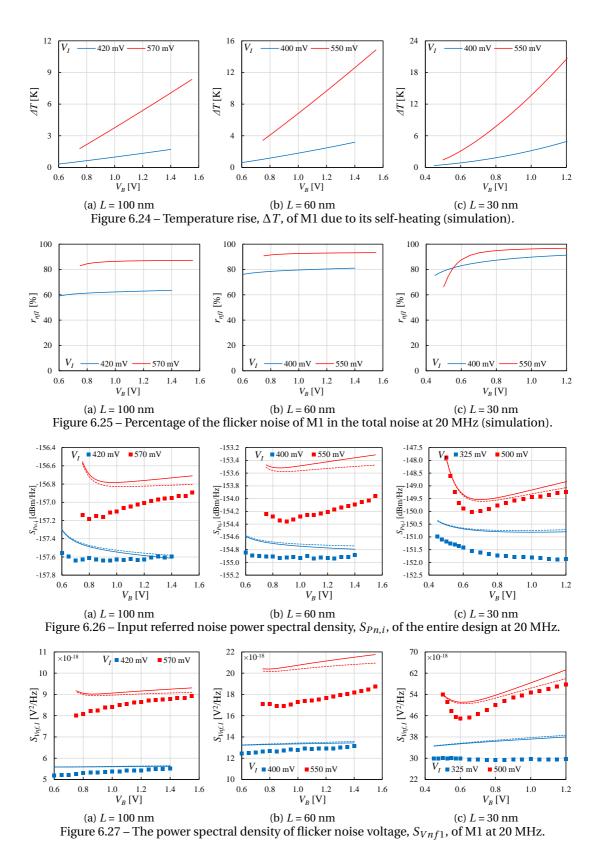

|      | Temperature rise, $\Delta T$ , of M1 due to its self-heating (simulation)                                       | 138 |

|      | Percentage of the flicker noise of M1 in the total noise at 20 MHz (simulation)                                 | 138 |

|      | Input referred noise power spectral density, $S_{Pn,i}$ , of the entire design at 20 MHz.                       |     |

|      | The power spectral density of flicker noise voltage, $S_{Vnf1}$ , of M1 at 20 MHz                               | 138 |

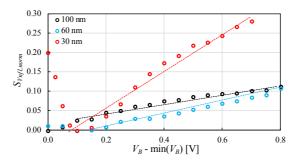

| 6.19 | Normalized flicker noise voltage power spectral densities of the 100 nm length                                  |     |

|      | and the 60 nm length devices for high heating case. The values of the horizontal                                |     |

|      | axis are shifted by the smallest $V_{DS}$ value in the measurement set                                          | 139 |

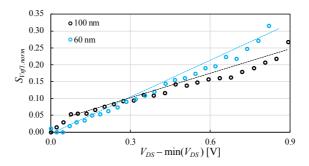

|      | Drain current of M1                                                                                             | 140 |

|      | Power dissipation, $P$ , of M1 ( $V_{DS,M1} \times I_{D,M1}$ )                                                  | 140 |

|      | Gain, $A_p$ , of M1 at 20 MHz                                                                                   | 140 |

|      | Output noise power spectral density, $S_{Pn,o}$ , of M1 at 20 MHz                                               | 140 |

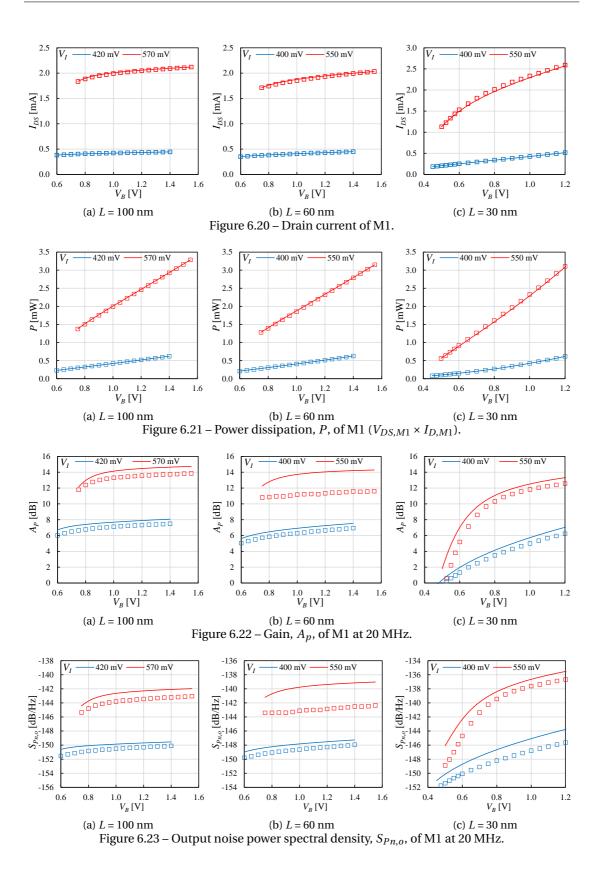

|      | Temperature rise, $\Delta T$ , of M1 due to its self-heating (simulation)                                       | 141 |

|      | Percentage of the flicker noise of M1 in the total noise at 20 MHz (simulation)                                 | 141 |

|      | Input referred noise power spectral density, $S_{Pn,i}$ , of the entire design at 20 MHz.                       |     |

|      | The power spectral density of flicker noise voltage, $S_{Vnf1}$ , of M1 at 20 MHz                               | 141 |

| 6.28 | Normalized flicker noise voltage power spectral densities of the 100 nm, 60 nm                                  |     |

|      | and 30 nm length devices for high heating case. The values of the horizontal axis                               |     |

|      | are shifted by the smallest $V_B$ value in the measurement set                                                  | 142 |

## **List of Tables**

| 2.1 | Duality between electrical and thermal circuits at steady state                             | 15  |

|-----|---------------------------------------------------------------------------------------------|-----|

| 2.2 | Parameters of the bulk and the FDSOI devices of Figure 2.1                                  | 20  |

| 3.1 | Thermal properties of FDSOI and bulk in 40 nm and 28 nm technologies                        | 38  |

| 3.2 | Comparison of the implemented adders in 40 nm and 28 nm technologies                        | 45  |

| 3.3 | Comparison of the published 64-bit adders. <sup>†</sup> The adder in [3] is a 32-bit imple- |     |

|     | mentation                                                                                   | 46  |

| 3.4 | Parameters of the devices on Figure 3.25                                                    | 62  |

| 3.5 | Maximum and mean heat density values and the number of devices from differ-                 |     |

|     | ent device groups in 40 nm                                                                  | 69  |

| 3.6 | Maximum and mean heat density values and the number of devices from differ-                 |     |

|     | ent device groups in 28 nm                                                                  | 70  |

| 3.7 | Change of thermal parameters in scaling from 40 nm to 28 nm                                 | 72  |

| 4.1 | Parameters for the devices with short, medium and long channels                             | 77  |

| 5.1 | Adjustable parameters and their explanations of the designed inductor pCells                |     |

|     | that are shown on Figure 5.8. Important note: all dimensions are shrinked by 0.9            |     |

|     | in fabrication                                                                              | 96  |

| 5.2 | Extracted lumped circuit parameters of the two-stack and symmetric integrated               |     |

|     | inductors                                                                                   | 96  |

| 5.3 | Input resistance values of LNAs with different gate lengths and their contributors          |     |

|     | from different parts of the circuit at $f_0$                                                | 104 |

| 5.4 | Design parameters of three different common gate cascode LNAs implemented                   |     |

|     | in 28 nm FDSOI technology                                                                   | 111 |

| 5.5 | The measured $I_{REF}$ and the applied $V_{B1}$ values for each experiment. The units       |     |

|     | of $I_{REF}$ and $V_{B1}$ are $\mu A$ and $mV$ respectively                                 | 117 |

| 6.1 | Properties and bias voltages of different samples used in experiment-A and                  |     |

|     | experiment-B                                                                                | 129 |

### **1** Introduction

Starting from the early 1960s, the integrated circuit technology has maintained a continuous advancement throughout its 60-year history. The number of devices per unit area in an IC was doubled every two years as predicted by G. E. Moore [4] primarily thanks to device scaling. With device scaling, the area of a single MOSFET was roughly halved from one technology node to the next one. Having more and smaller devices in integrated circuits enabled the designers to implement more complex systems with higher throughput, thanks to the increased clock frequency. As from mid-1990s, traditional device scaling started to encounter physical limitations such as velocity saturation, mobility degradation, sub-threshold and gate leakage, punch through, increased parasitics and so on. Innovative solutions like pocket and halo implantation, shallow trench isolation (STI), usage of high-k materials as gate dielectric enabled the ongoing device scaling to continue. However, the power density started to increase from one technology to another by breaking the Dennard scaling, which states that as the transistors are reduced in size, their power density stays constant [5]. Approaching to the late 2000s, bulk CMOS technology reached its limits and alternative device geometries such as Fully Depleted Silicon on Insulator (FDSOI) and FinFET devices took its place. The new device geometries improved the electrical characteristics of the devices; however, they brought the necessity to use thermally poor materials around them. While enabling the device scaling to go on, all of these novelties brought another formidable problem of excessive heating and operation at elevated temperatures.

#### 1.1 Operation at a Different Temperature

Many of the physical parameters of solid-state devices depend on temperature. In general, increasing the temperature changes these parameters in the undesired direction. The operation of semiconductors materials and solid-state devices at different temperatures have been investigated for a long time. One can find well established and experimentally proven accurate models in the literature  $[6, 7, 8, 9]^1$ . To observe a change in the temperature of a solid-state

<sup>&</sup>lt;sup>1</sup>In this report, we do not provide a detailed explanation of the physics of temperature dependent properties unless it is necessary to clarify a point, since it is not the main scope of this work.

device (a system in general), it has to interact with heat. Generally speaking, the temperature of an enclosed system increases only in two separate cases or with the combination of two. First, the temperature of a system increases if there is a positive heat flow into this system and no heat sources or absorbers are located in the same enclosed volume. In case this is an electronic system such as an IC, an example of this case can be placing it inside a heater without connecting any power supplies. Second, the temperature of a system also increases if a heat source that is located in this system generates heat that is greater than zero and no heat passes through the boundaries of this system. Returning back to the same IC, connecting it to a power supply and placing it to a thermal insulator test environment can be an example for this case. While the first case is not mandatory in many cases, the second one is an inevitable result of the desired operation of an IC. In this work, we skip the first case and focus on the second one, where the elevated temperature of an electronic system is due to the heating resulting from its operation.

#### 1.1.1 Heating or Self-Heating?

**Heating**<sup>2</sup> in electronic systems is the process where the kinetic energy of charge carriers is transferred to the body of the conductor through different scattering mechanisms. An IC can be composed of millions of transistors. According to the processed data, each transistor might conduct different amount of current where some of them might not be conducting any current at all. Depending on their activity, each conducting transistor contribute differently to the overall heating of the IC. Because of the overall heating of all transistors, the temperature values at different points of the IC would take values that are larger than the state where the IC is not connected to a power supply. Due to the temperature dependence of transistors' different parameters, their electrical characteristics are directly or indirectly affected depending on their temperature. In advanced technologies, the temperature at different points in the ICs might reach to extremely large values (more than 100 C), which might bring significant reliability and performance issues. This brings the problem of heating in IC design where the source is the combination of *all* constitutive transistors.

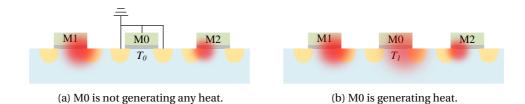

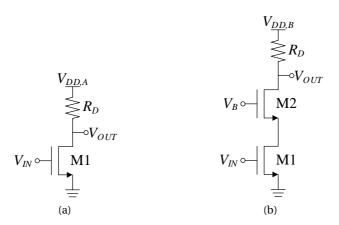

When we focus on a *single* transistor in an IC, its temperature would take a value depending on the total heating of the other transistors and the heat generated by itself. Under the same operating conditions where all the other devices generate the same amount of heat, the temperature of a transistor in its conducting state would be greater than its non-conducting state. The temperature difference between these two cases results from the **Self-Heating** of this transistor (Figure 1.1). Self-heating would bring an additional effect on the operation of a transistor on top of the heating effects of the other devices. Formally, we define **Self-Heating Effects (SHE)** as the combination of all the modifications in the physical properties of a transistor due to the elevation of its temperature arising from the heating that is only originating from its own electrical activity. In this work, our goal is to focus on the self-heating rather than the total heating of ICs or operation of ICs at high temperature environments.

<sup>&</sup>lt;sup>2</sup>Also called **Joule heating**, **Ohmic heating** or **resistive heating**

Figure 1.1 – Independent of the activity of any other devices and the ambient temperature, the characteristics of M0 changes while passing from the state shown on (a) to the one shown on (b) due to its self-heating. The influence of self-heating effects depends on the temperature difference  $T_1 - T_0$ .

#### 1.1.2 Observing Self-Heating Effects

The definition of self-heating effects contains two states where the transistor is electrically inactive and active. To observe the amount of self-heating effects, one should perform the necessary measurements on a transistor in these two states and report the values of each parameter for both cases. The difference of a parameter in two states would give information about how much that parameter is affected from self-heating effects. More formally, self-heating effects bring an additional shift in a parameter with a coefficient of

$$k_p = \frac{p|_{SH} - p|_{NO}}{p|_{NO}} \tag{1.1}$$

where  $p|_{NO}$  is the value of a parameter with *no* self-heating effects and  $p|_{SH}$  is its value when self-heating effects are present<sup>3</sup>. To illustrate the situation, let us assume we are interested in the self-heating effects on the transconductance of a transistor under a certain gate and drain bias. In this case, p in (1.1) is replaced by the transconductance,  $g_m$ . Hence, the value of transconductance under self-heating effects is

$$g_m|_{SH} = (1 + k_{g_m})g_m|_{NO}.$$

(1.2)

From a temperature point of view,  $g_m|_{NO}$  is the transconductance value at  $T_0$ ,  $g_m|_{SH}$  is the transconductance value at  $T_1$  and  $T_1 - T_0$  is the temperature rise due to self-heating.  $g_m|_{SH}$  can be simply observed by applying the desired bias levels with power supplies and performing the related measurements. When it comes to measure  $g_m|_{NO}$ , we cannot simply *switch* the self-heating effects *off* and repeat the same experiment while the desired voltage levels are still being applied by the external sources. The self-heating is naturally there and it cannot be removed without removing the external power. However, by switching off the power supplies, we cannot bring the device to necessary bias conditions in which we are interested. Nevertheless, the temperature of the device with no self-heating,  $T_0$ , can be measured simply by applying no power. Therefore, the temperature of the transistor can be externally pushed to  $T_0$  during its desired operation via heat sinks. In this case, the measured transconductance

<sup>&</sup>lt;sup>3</sup>In the following chapters,  $k_p$  in (1.1) is also referred as the **Error** for quantifying the miscalculation when self-heating effects are not considered.

would give the value of the sought  $g_m|_{NO}$ .

The amount of self-heating effects can be theoretically reported by applying the previously explained methods. Nevertheless, there are additional practical issues in measuring the temperature. In commercially available advanced technologies, the channel length of a transistor can be as small as 10 nm by 2018. Moreover, the transistors are buried under many interconnect and dielectric layers. These facts create issues for performing an accurate temperature measurement of a transistor. By removing the back end of line (BEOL) and some of the front end of line (FEOL) layers, the transistor can be revealed. However, this modification would change the temperature of the transistor due to the modified thermal geometry by removing different layers. Even if this does not bring a significant change, one should make sure that the measurement technique does not disturb the temperature of a nanometer scale region. In addition to these, it is reported in many sources and shown in our work that the temperature of a transistor shows very large variations in its volume. For example, the temperature difference between the drain and the source of a device might be some tens of Kelvins [10, 11]. This means that the temperature in a short channel device might change by more than 5 K in one nanometer distance. Consequently, measuring a single temperature value and assuming that it is the temperature of the entire transistor is not sufficient. Considering these, bringing the device temperature down to  $T_0$  would also be practically impossible. Even if the average temperature of a device can be set to  $T_0$  with a cooling system, there would still be a non-uniform temperature profile in the device due to its non-uniform heating and different heat diffusion paths.

Because of the mentioned difficulties and mainly because the self-heating cannot be practically removed, measuring the self-heating effects is a complicated task. Yet, there has been different studies on observing self-heating effects experimentally. One of the most common methods is the pulsed I-V technique [12]. The idea is to apply a sharp voltage or current pulse and to perform a measurement immediately after. This way, the temperature shift due to self-heating can be prevented to an extent. This depends on how fast the measurement setup can obtain a proper data point and the thermal time constant of the measured device. Different authors reported two distinct behaviours between the pulsed and the DC measurements [13, 14, 15, 16, 17] for SOI and FinFET devices. However, the amount of self-heating is still questionable at the instant where the first measurement data is sampled. Especially in nanometer scale devices, the hot-spot is extremely small. This decreases the thermal time constant significantly and the level of self-heating at the measurement moment becomes more questionable.

There has been also many attempts to gather information about the self-heating effects by performing device level simulations [10, 11, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30, 31]. The authors tried to estimate the temperature rise due to self-heating effects. Different sources reported different temperature values depending on the used techniques. The advantage of simulations is to have the chance to create the scenario where self-heating effects are disabled. However, one needs to consider detailed mathematical models for all physical

phenomena which are actively taking part under the applied conditions (size of the geometry, ambient temperature, boundary conditions, applied voltage levels, material type etc.). As the dimensions get smaller (less than the mean free paths of quantized energy particles such as phonons and electrons or comparable with the lattice constant of the conducting medium), it becomes necessary to consider the quantum effects, which contain very complex mathematical models. For this reason, very detailed simulations might take very long times to converge and the results might still be questionable. Today, there is still an ongoing research on performing more accurate electro-thermal simulations.

#### 1.1.3 Why a Single Device?

One might naturally wonder if the contribution of a single device out of millions is important to investigate or how much the temperature of an IC increases by only one device. It is true that turning a single device on and off would not have a big impact on the overall system if the entire chip is considered. However, the focus in the self-heating study is not the influence of a single device on the entire chip. The critical question is how much the operation of a device is influenced due to its own heating, excluding the heating of the other transistors.

The self-heating related problems became more an issue especially after the introduction of the modern MOSFET device geometries like FDSOI and FinFET, and new dielectric materials [10]. Previously, it was reported that the peak temperature of the FDSOI devices is located close to the drain end of the device [19, 24] and the maximum temperature value in FDSOI FETs is found to be much higher than the one in the conventional bulk MOSFETs [32]. The higher maximum temperature of the FDSOI and FinFET structures is mainly due to the thermal behaviour of its constitutive materials. SiO2 is one of these materials which is used on the sides of the channel for isolation [26, 33, 34]. The thermal conductivity of the SiO<sub>2</sub> isolation layer is two orders of magnitude lower than the thermal conductivity of the bulk Si. Moreover, in these structures, the channel is no longer a part of the bulk; it is rather a thin layer of Si. The thermal conductivity of the Si thin film, where the devices are generating heat, is one order of magnitude less than the thermal conductivity of bulk Si [24]. Additionally, the boundary between Si and SiO<sub>2</sub> creates a temperature jump, hence a finite interface thermal resistance, [35, 36], which is equal to the thermal resistance of a SiO<sub>2</sub> layer with a thickness of 20 nm [18]. Due to the mentioned facts, the dissipated power in FDSOI devices does not find a high conductance diffusion path. Because of this, in FDSOI and FinFET technologies, the generated heat turns into temperature in nanometer scale local spots with much smaller dimensions than the ones in bulk technologies. For this reason, contrary to the traditional bulk CMOS technologies where temperature is assumed a global variable, it is necessary to consider the self-heating effects and the temperatures of each device separately to obtain reliable results and better yield.

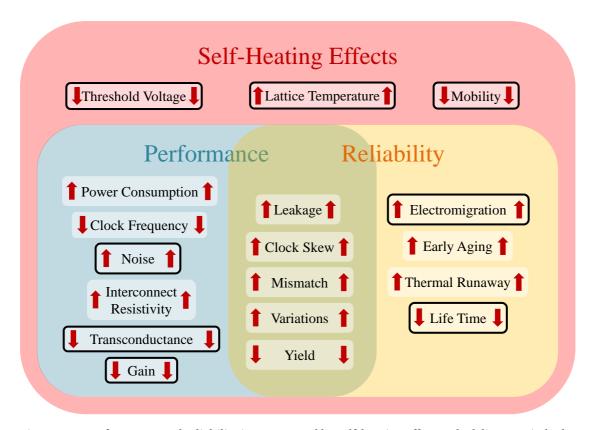

Figure 1.2 – Performance and reliability issues created by self-heating effects. Black lines encircle the items that are the focus of this work.

#### 1.1.4 Self-Heating Related Issues

As it has already been explained, the primary outcome of the self-heating is the increased temperature of the device. Two most well known device parameters that are directly affected by the increased temperature are the mobility and the threshold voltage. Mobility decreases at elevated temperatures mainly due to increased phonon scattering rate. Threshold voltage also decreases with temperature due to the temperature dependence of the flatband voltage [37]. These modifications in the main device parameters create threats in the performance and the reliability of ICs (Figure 1.2).

Due to the decreased mobility, the speed of the devices, consequently the maximum clock frequency decreases. Lower threshold voltage increases the sub-threshold current significantly due to its negative exponential dependence on the threshold voltage [38]. Larger sub-threshold current means leakage. Due to increased leakage, the power consumption also increases [39, 40]. Higher power consumption brings higher temperature and this might result in thermal runaway where the die fails due to the uncontrolled increase in the temperature. Although thermal runaway does not happen, the chip might settle down to a higher temperature, which would degrade the performance as well as the reliability of the chip [41, 42]. Electromigration phenomena is another reliability problem related to temperature where the

metal interconnects are broken due to diffusion or flow of atoms under very high current densities at high temperatures [43, 44]. The difference between the heating values of devices might create an uneven temperature profile. This results in different behaviours of the devices with the same properties and temperature dependent variations throughout the die. If these temperature variations are observed on some devices where matching is important, mismatch issues like larger offset voltage might occur. Nonhomogeneous temperature distribution also results in different conductance values of the interconnect lines due to the temperature dependence of the metal resistivity [45, 46, 47]. Consequently, the delay times of balanced interconnects might differ, which might cause serious clock skew issues [48, 49]. Larger average electron kinetic energy increases the noise, which results in lower SNR and dynamic range. All of the mentioned problems show that having a reliable and high performance chip is not possible without considering the self-heating effects and the thermal behaviour of a design.

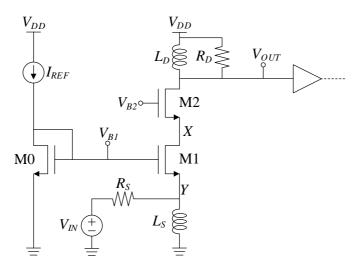

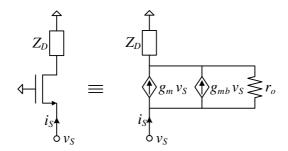

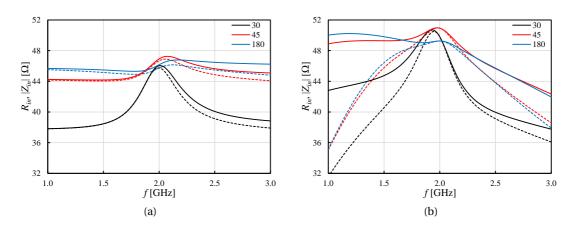

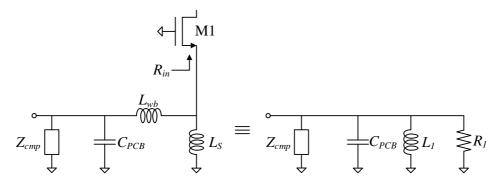

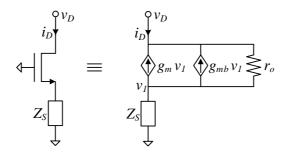

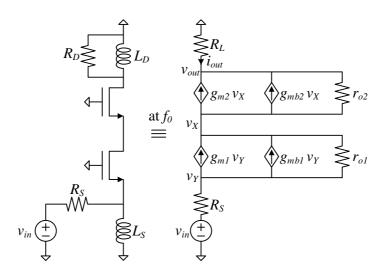

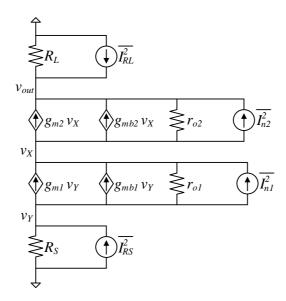

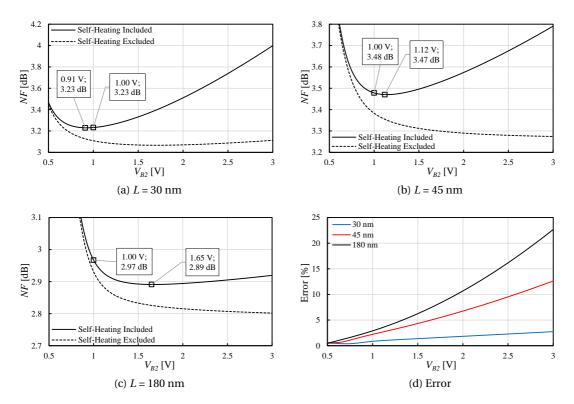

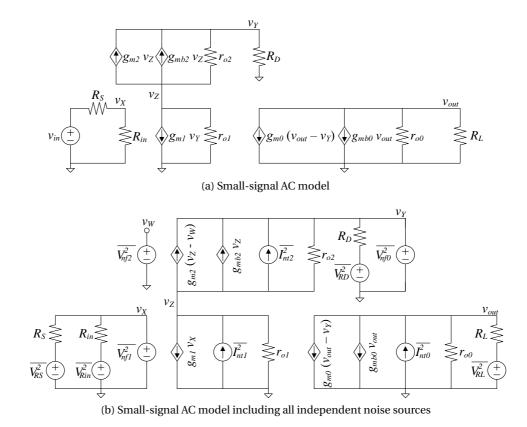

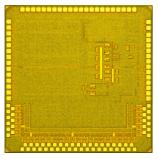

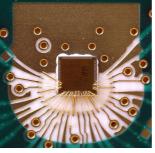

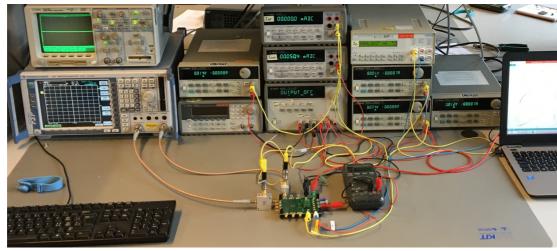

#### 1.1.5 Scope of This Work