# Bridging the gap between dataplanes and commodity operating systems

THÈSE Nº 8673 (2018)

PRÉSENTÉE LE 1<sup>ER</sup> JUIN 2018 À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS LABORATOIRE DES SYSTÈMES DE CENTRES DE CALCUL PROGRAMME DOCTORAL EN INFORMATIQUE ET COMMUNICATIONS

# ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

# **Georgios PREKAS**

acceptée sur proposition du jury:

Prof. W. Zwaenepoel, président du jury Prof. E. Bugnion, directeur de thèse Prof. A. Belay, rapporteur Prof. R. Stutsman, rapporteur Prof. J. Larus, rapporteur

# Acknowledgements

First, I would like to thank my advisor, Edouard Bugnion. Ed has great technical knowledge and a profound understanding of computer systems. I was extremely lucky that I had the opportunity to work with him, understand how he thinks, how he approaches and solves problems. Most importantly, I am grateful that I had the chance to learn from him. He helped me see the big picture of problems and be more systematic when solving them. With his support and guidance, I improved not only my technical skills but also my interpersonal skills.

I would also like to thank the members of my thesis committee, Adam Belay, James Larus, Ryan Stutsman, and Willy Zwaenepoel both for finding the time to serve in it, as well as for their constructive comments.

I am also fortunate for my collaborations with many people on our various research efforts: Adam Belay, Adrien Ghosn, Ana Klimovic, Christos Kozyrakis, Marios Kogias, Mia Primorac, and Samuel Grossman. Without them, most of this research would not have been possible.

Special thanks to all the members of my lab and our neighboring lab: Adrien, Bogdan, David, Dmitrii, Jonas, Maggy, Marios, Mia, Sahand, Sam, Stanko, and Stuart. Their diverse set of interests made life at work always more interesting. I would like to thank all the people who have given me feedback on my research on numerous occasions including, Alex, Manos, and Matt.

I would like also to thank all my friends, both in Greece and in Switzerland. The first for encouraging me to go abroad for my PhD and the second for making life in Switzerland entertaining.

Of course, I would like to thank my family, especially my parents, who have always supported me during many years of studies. Their support has been invaluable for me and has significantly contributed to allowing me to reach this point in my life.

Last but certainly not least, I would like to thank Joëlle. In the past two years, Joëlle has had to endure my irregular work schedule and was constantly helping me to find the balance between life and work.

This research has been supported by a Google Graduate Research Fellowship.

Lausanne, 15 May 2018

# Abstract

The conventional wisdom is that aggressive networking requirements, such as high packet rates for small messages and  $\mu$ s-scale tail latency, are best addressed outside the kernel, in a user-level networking stack. In particular, dataplanes borrow design elements from network middleboxes to run tasks to completion in tight loops. In its basic form, the dataplane design leverages sweeping simplifications such as the elimination of any resource management and any task scheduling to improve throughput and lower latency. As a result, dataplanes perform best when the request rate is predictable (since there is no resource management) and the service time of each task has a low execution time and a low dispersion. On the other hand, they exhibit poor energy proportionality and workload consolidation, and suffer from head-of-line blocking.

This thesis proposes the introduction of resource management to dataplanes. Current dataplanes decrease latency by constantly polling for incoming network packets. This approach trades energy usage for latency. We argue that it is possible to introduce a control plane, which manages the resources in the most optimal way in terms of power usage without affecting the performance of the dataplane.

Additionally, this thesis proposes the introduction of scheduling to dataplanes. Current designs operate in a strict FIFO and run-to-completion manner. This method is effective only when the incoming request requires a minimal amount of processing in the order of a few microseconds. When the processing time of requests is (a) longer or (b) follows a distribution with higher dispersion, the transient load imbalances and head-of-line blocking deteriorate the performance of the dataplane. We claim that it is possible to introduce a scheduler to dataplanes, which routes requests to the appropriate core and effectively reduce the tail latency of the system while at the same time support a wider range of workloads.

**Keywords**: web-scale application, datacenter, scale-out, virtualization, networking, operating system, energy proportionality, resource management, scheduling, work stealing, work conservation, head-of-line blocking, dataplane

# Résumé

Dans le milieu académique, il est communément accepté qu'afin de satisfaire des exigences élevées en termes de performance des réseaux, telles que de hauts débits pour des messages courts, ou une latence (tail-latency) à l'échelle de quelques microseconds, le stack réseau du noyau (kernel) doit être remplacé par des implémentations plus efficaces et spécialisées, au niveau utilisateur. En particulier, les dataplanes empruntent des éléments de design aux midd-leboxes réseaux et exécutent les tâches suivant un modèle « run-to-completion ». Dans leur forme la plus simple, les dataplanes reposent sur des simplifications telles que l'élimination de toutes gestions des ressources et de tout « scheduling » (ordonnancement) de tâches. Ces simplifications permettent de réduire la logique des dataplanes à une boucle d'exécution courte, et d'ainsi améliorer le débit tout en réduisant les latences. Cependant, ces simplifications radicales ne fonctionnent vraiment que lorsque les taux de requêtes sont prévisibles (dû au manque de gestion des ressources) et lorsque les temps d'exécution individuels des requêtes sont courts et homogènes. D'autre part, les dataplanes ont en général une mauvaise gestion des ressources (workload consolidation) et sont sujets au « head-of-line blocking ».

Cette thèse propose de réintroduire une forme de gestion des ressources dans les dataplanes. Les implémentations actuelles reposent sur un « polling » constant afin de traiter au plus vite les paquets entrants et de réduire les temps de latence. Cette approche sacrifie la consommation énergétique au profit de meilleures performances. Nous soutenons qu'il est possible d'introduire un « control plane », responsable de la gestion optimale de la consommation d'énergie, sans pour autant impacter les performances du dataplane.

De plus, cette thèse propose d'ajouter une forme de scheduling aux dataplanes. Les implémentations existantes reposent sur un modèle "FIFO" et traitent, entièrement, tour-à-tour chaque paquet (run-to-completion). Cette méthode n'est efficace que lorsque les requêtes entrantes correspondent à des temps d'exécution faibles, de l'ordre de quelques micro-seconds. Lorsque les temps d'exécution sont (a) plus longs ou (b) suivent une distribution avec une dispersion plus élevée, les déséquilibres sporadiques en terme de charge de travail, ainsi que les éventuelles situations de head-of-line blocking, détériorent les performances des dataplanes. Nous affirmons qu'il est possible d'introduire un « scheduler » dans les dataplanes, responsable de la répartition des tâches parmi les différents cœurs du processeur, et d'ainsi réduire la tail-latency du système tout en supportant des charges de travail hétérogènes.

**Mots clefs** : application à l'échelle du Web, centre de données, scale-out, virtualisation, réseaux, système d'exploitation, proportionnalité énergétique, gestion des ressources, scheduling, work stealing, conservation du travail/workload conservation, head-of-line blocking, dataplane

# Contents

| Ac | Acknowledgements |                                                                           |     |  |  |

|----|------------------|---------------------------------------------------------------------------|-----|--|--|

| Ał | ostra            | ct (English/Français)                                                     | iii |  |  |

| Li | List of figures  |                                                                           |     |  |  |

| Li | List of tables   |                                                                           |     |  |  |

| 1  | Intr             | oduction                                                                  | 1   |  |  |

|    | 1.1              | Web-scale applications                                                    | 1   |  |  |

|    |                  | 1.1.1 The tail at scale                                                   | 2   |  |  |

|    |                  | 1.1.2 Microsecond computing                                               | 3   |  |  |

|    |                  | 1.1.3 Energy-proportional computing                                       | 4   |  |  |

|    | 1.2              | Resource management for web-scale applications                            | 4   |  |  |

|    | 1.3              | Microsecond-scale scheduling for web-scale applications                   | 5   |  |  |

|    | 1.4              | Thesis Statement                                                          | 6   |  |  |

|    | 1.5              | Thesis Contributions                                                      | 7   |  |  |

|    |                  | 1.5.1 Resource management control plane for dataplane operating systems . | 7   |  |  |

|    |                  | 1.5.2 Work conserving scheduler for dataplane operating systems           | 8   |  |  |

|    | 1.6              | Thesis Roadmap                                                            | 9   |  |  |

|    | 1.7              | Bibliographic Notes                                                       | 9   |  |  |

| 2  | Dat              | aplane OS and resource management                                         | 11  |  |  |

|    | 2.1              | Introduction                                                              | 11  |  |  |

|    | 2.2              | Background and Motivation                                                 | 14  |  |  |

|    |                  | 2.2.1 Challenges for Datacenter Applications                              | 15  |  |  |

|    |                  | 2.2.2 The Hardware – OS Mismatch                                          | 15  |  |  |

|    |                  | 2.2.3 Alternative Approaches                                              | 16  |  |  |

|    | 2.3              | IX Design Approach                                                        | 17  |  |  |

|    | 2.4              | IX Implementation                                                         | 20  |  |  |

|    |                  | 2.4.1 Overview                                                            | 20  |  |  |

|    |                  | 2.4.2 The IX Dataplane                                                    | 22  |  |  |

|    |                  | 2.4.3 Dataplane API and Operation                                         | 23  |  |  |

|    |                  | 2.4.4 Multi-core Scalability                                              | 25  |  |  |

|    |                  | 2.4.5 Flow group migration                                                | 26  |  |  |

| Cı | ırricı          | ulum Vitae                                              | 97 |  |  |  |

|----|-----------------|---------------------------------------------------------|----|--|--|--|

| Bi | Bibliography 85 |                                                         |    |  |  |  |

|    | 4.2             | Future work                                             | 82 |  |  |  |

|    | 4.1             | What we did                                             | 81 |  |  |  |

| 4  | Con             | nclusion                                                | 81 |  |  |  |

|    | 3.9             | Conclusion                                              | 79 |  |  |  |

|    | 3.8             | Related Work                                            | 78 |  |  |  |

|    | 3.7             | Discussion: the impact of SLO on systems                | 77 |  |  |  |

|    |                 | 3.6.3 A real application: Silo running TPC-C            | 73 |  |  |  |

|    |                 | 3.6.2 Overheads of ZYGOS on tiny tasks: memcached       | 73 |  |  |  |

|    |                 | 3.6.1 Synthetic micro-benchmarks                        | 68 |  |  |  |

|    | 3.6             | Evaluation                                              | 68 |  |  |  |

|    | 3.5             | Implementation                                          | 67 |  |  |  |

|    |                 | 3.4.5 Inter-processor Interrupts                        | 66 |  |  |  |

|    |                 | 3.4.4 Eliminating Head-of-Line Blocking                 | 65 |  |  |  |

|    |                 | 3.4.3 Ordering semantics in multi-threaded applications | 65 |  |  |  |

|    |                 | 3.4.2 ZYGOS High-level Design                           | 63 |  |  |  |

|    |                 | 3.4.1 Requirements                                      | 62 |  |  |  |

|    | 3.4             | Design                                                  | 62 |  |  |  |

|    |                 | 3.3.4 Baseline results                                  | 61 |  |  |  |

|    |                 | 3.3.3 Evaluated Systems                                 | 61 |  |  |  |

|    |                 | 3.3.2 Experimental Environment                          | 60 |  |  |  |

|    |                 | 3.3.1 Approach and metrics                              | 60 |  |  |  |

|    | 3.3             | Experimental Methodology                                | 58 |  |  |  |

|    |                 | 3.2.3 Just enough queuing theory                        | 55 |  |  |  |

|    |                 | 3.2.2 Kernel bypass and sweeping simplifications        | 55 |  |  |  |

|    |                 | 3.2.1 Scaling remote procedure calls                    | 54 |  |  |  |

|    | 3.2             | Background                                              | 54 |  |  |  |

|    | 3.1             | Introduction                                            | 51 |  |  |  |

| 3  | Sch             | eduling for dataplane OS                                | 51 |  |  |  |

|    | 2.9             | Conclusion                                              | 49 |  |  |  |

|    | 2.8             | Related Work                                            | 48 |  |  |  |

|    | 2.7             | Discussion                                              | 45 |  |  |  |

|    | 2.6             | Evaluation                                              | 39 |  |  |  |

|    | 0.0             | 2.5.3 Pareto-Optimal Static Configurations              | 36 |  |  |  |

|    |                 | 2.5.2 Dataplane performance                             | 30 |  |  |  |

|    |                 | 2.5.1 Experimental Methodology                          | 28 |  |  |  |

|    | 2.5             | Evaluation of the dataplane                             | 28 |  |  |  |

|    |                 | 2.4.7 Security Model                                    | 27 |  |  |  |

|    |                 | 2.4.6 The IXCP Control Loop                             | 26 |  |  |  |

|    |                 |                                                         |    |  |  |  |

# List of Figures

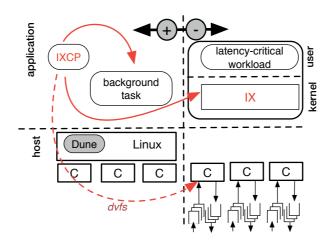

| 1.1  | Dynamic resource controls with IX for a workload consolidation scenario with<br>a latency-sensitive application (e.g., memcached) and a background batch task<br>(e.g., analytics). The controller, ixcp, partitions cores among the applications |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | and adjusts the processor's DVFS settings.                                                                                                                                                                                                        | 5  |

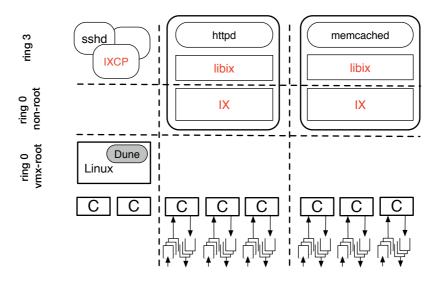

| 2.1  | Protection and separation of control and data plane in IX                                                                                                                                                                                         | 19 |

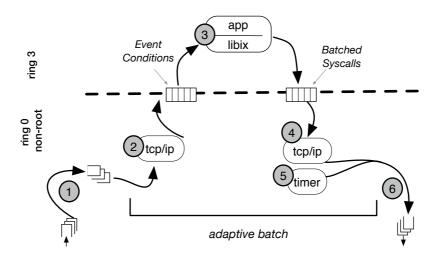

| 2.2  | Interleaving of protocol processing and application execution in the $\ensuremath{\mbox{\tiny IX}}$ dataplane.                                                                                                                                    | 21 |

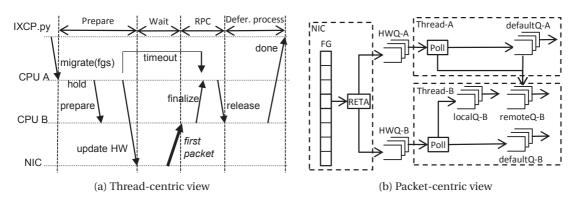

| 2.3  | Flow-group Migration Algorithm                                                                                                                                                                                                                    | 26 |

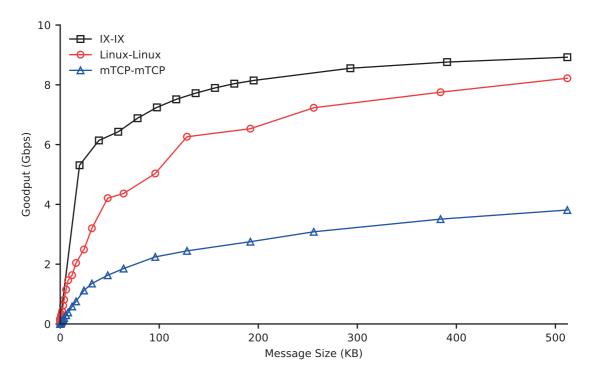

| 2.4  | NetPIPE performance for varying message sizes and system software configura-                                                                                                                                                                      |    |

|      | tions                                                                                                                                                                                                                                             | 29 |

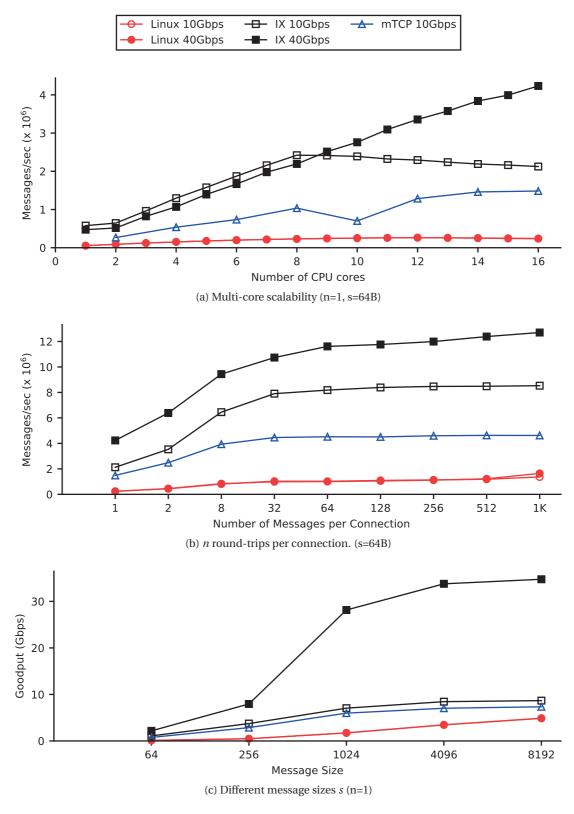

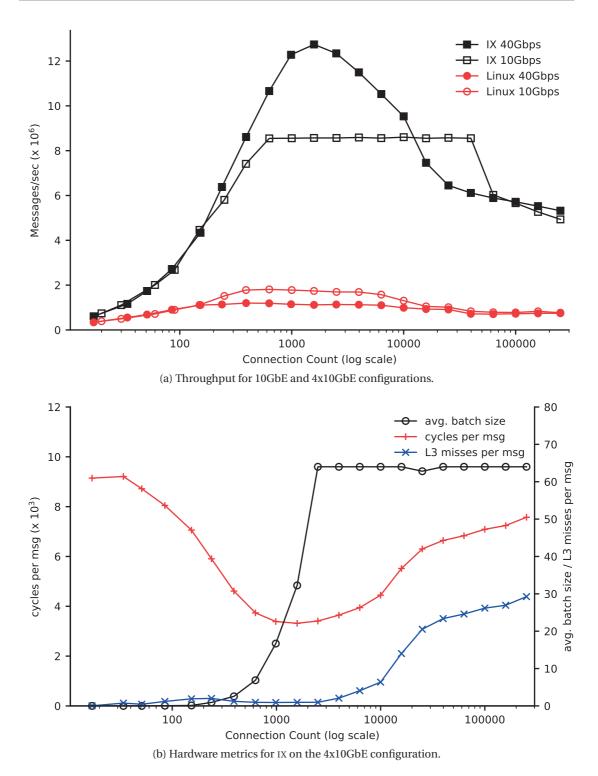

| 2.5  | Multi-core scalability and high connection churn for 10GbE and 4x10GbE setups.                                                                                                                                                                    |    |

|      | In (a), half steps indicate hyperthreads.                                                                                                                                                                                                         | 31 |

| 2.6  |                                                                                                                                                                                                                                                   | 32 |

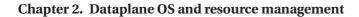

| 2.7  | Average and 99 <sup>th</sup> percentile latency as a function of throughput for the ETC and                                                                                                                                                       |    |

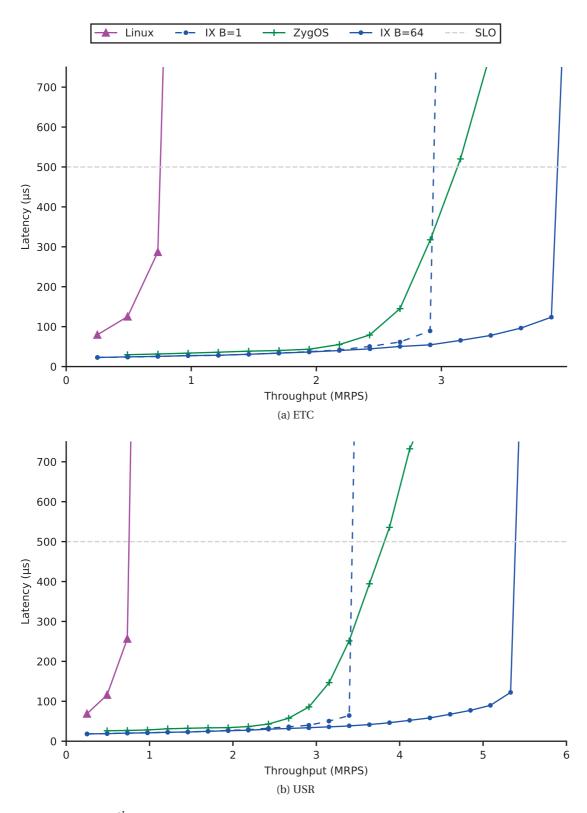

|      | USR memcached workloads                                                                                                                                                                                                                           | 34 |

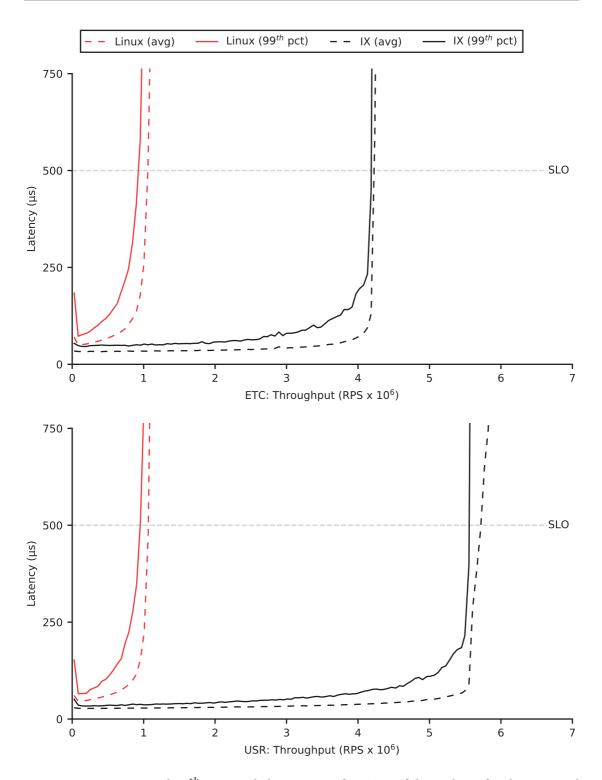

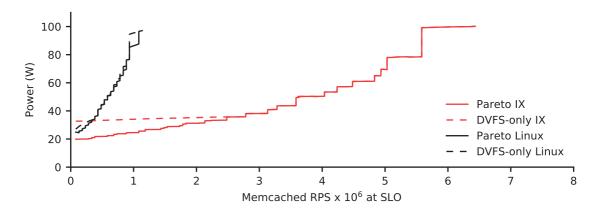

| 2.8  | Pareto efficiency for energy proportionality and workload consolidation for                                                                                                                                                                       |    |

|      | IX. The Pareto efficiency is in red while the various static configurations are                                                                                                                                                                   | 27 |

| 2.0  | color-coded according to their distinctive characteristics                                                                                                                                                                                        | 37 |

| 2.9  | sidering only DVFS adjustments, and the full Pareto frontier considering core                                                                                                                                                                     |    |

|      |                                                                                                                                                                                                                                                   | 37 |

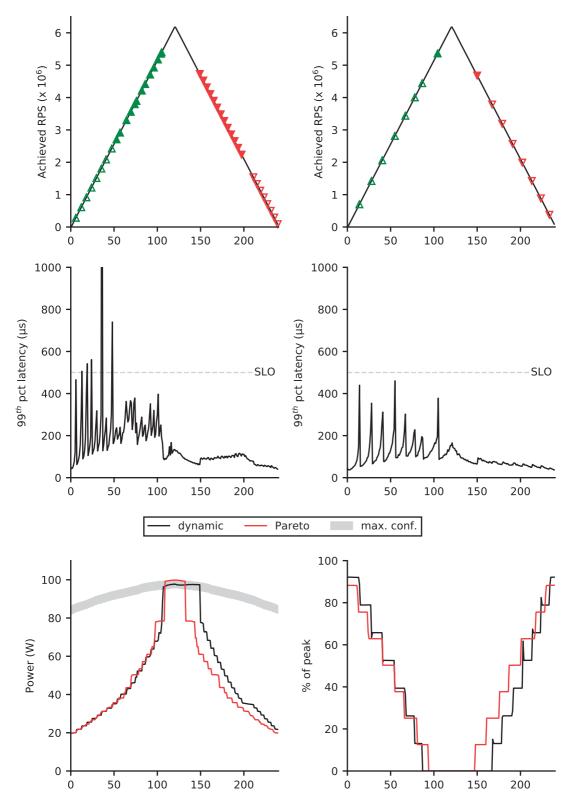

| 2 10 | Energy proportionality (left) and workload consolidation (right) for the <i>slope</i>                                                                                                                                                             | 51 |

| 2.10 |                                                                                                                                                                                                                                                   | 40 |

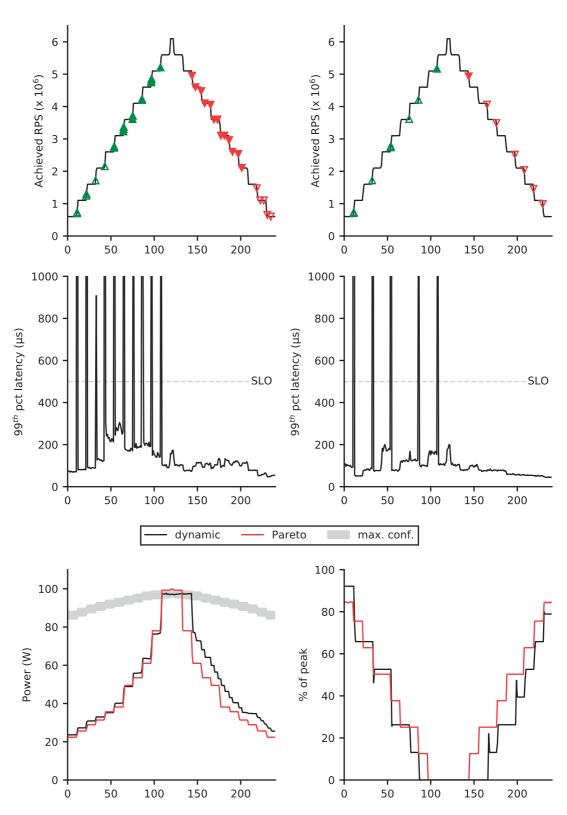

| 2.11 | Energy proportionality (left) and workload consolidation (right) for the <i>step</i> pattern                                                                                                                                                      |    |

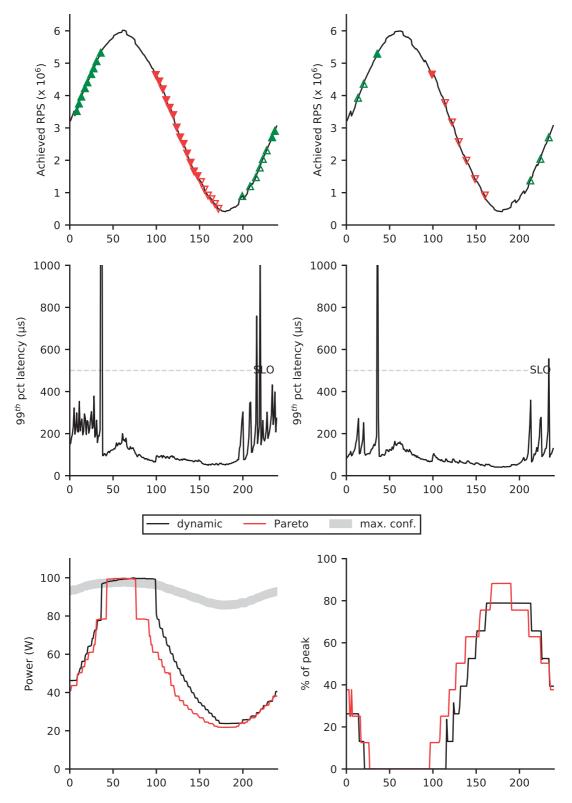

|      | Energy proportionality (left) and workload consolidation (right) for the <i>sin+noise</i>                                                                                                                                                         |    |

|      |                                                                                                                                                                                                                                                   | 42 |

| 2.13 | $99^{th}$ percentile latency as a function of throughput for USR workload from                                                                                                                                                                    |    |

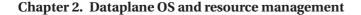

|      | Fig. 2.7b, for different values of the batch bound <i>B</i>                                                                                                                                                                                       | 46 |

| 3.1  |                                                                                                                                                                                                                                                   | 55 |

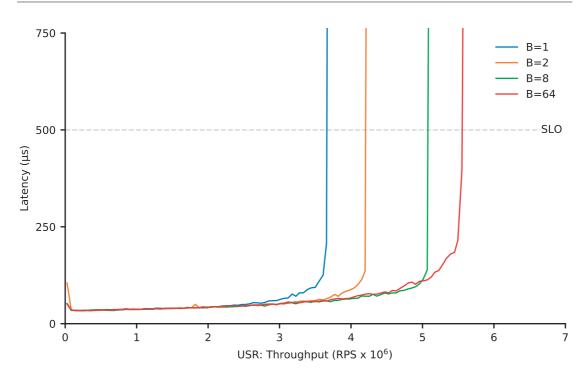

| 3.2  | Simulation results for the 99 <sup>th</sup> percentile tail latency for four service time distri-                                                                                                                                                 |    |

|      | butions with $\overline{S} = 1$                                                                                                                                                                                                                   | 56 |

## List of Figures

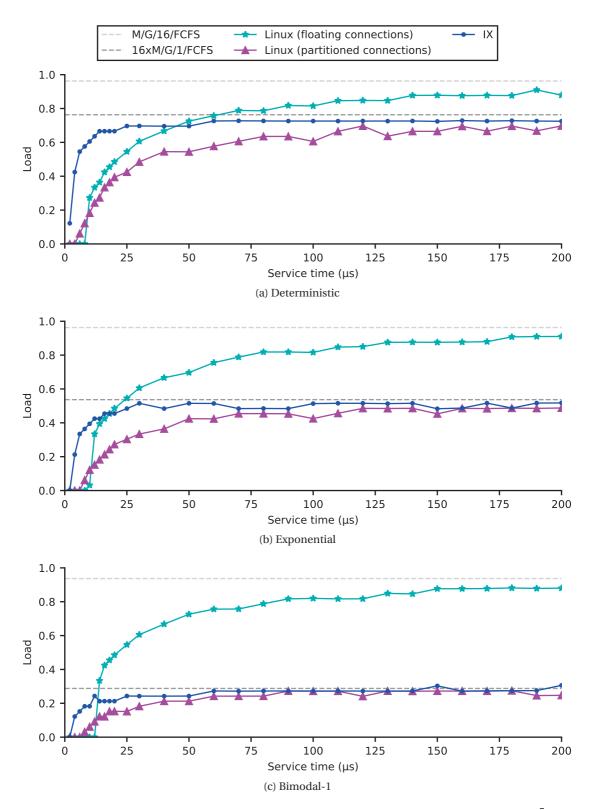

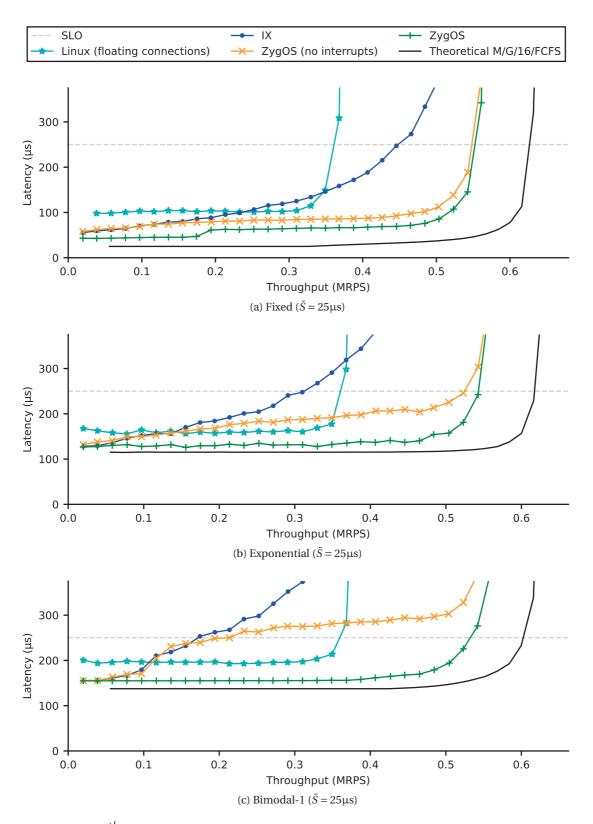

| 3.3  | Maximum load that meets the SLO as a function of the mean service time $\bar{S}$ . The                                                                       |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | SLO is set at $\leq (10 \times \overline{S})$ at the 99 <sup>th</sup> percentile. The grey lines correspond to the                                           |    |

|      | ideal upper bounds determined by the centralized-FCFS and partitioned-FCFS                                                                                   |    |

|      |                                                                                                                                                              | 59 |

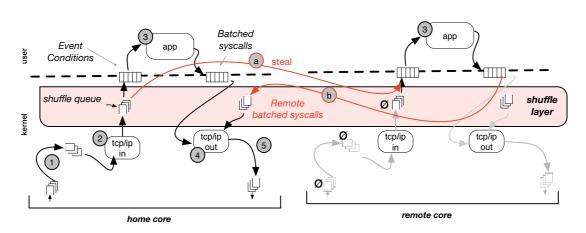

| 3.4  | Dataflow in the ZYGOS operating system. Steps $(1) - (6)$ correspond to the normal execution on the home core. Steps $(a)$ - $(b)$ occur during stealing and |    |

|      | involve the home and remote cores.                                                                                                                           | 62 |

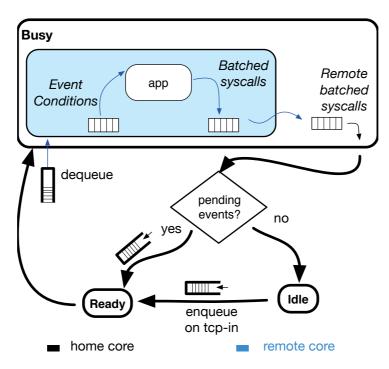

| 3.5  | Connection state machine transitions for the general case where an event is                                                                                  |    |

|      | executed on a remote core (in blue). The connection is present in the shuffle                                                                                |    |

|      | queue exactly once when it is in the "ready" state, and never otherwise                                                                                      | 66 |

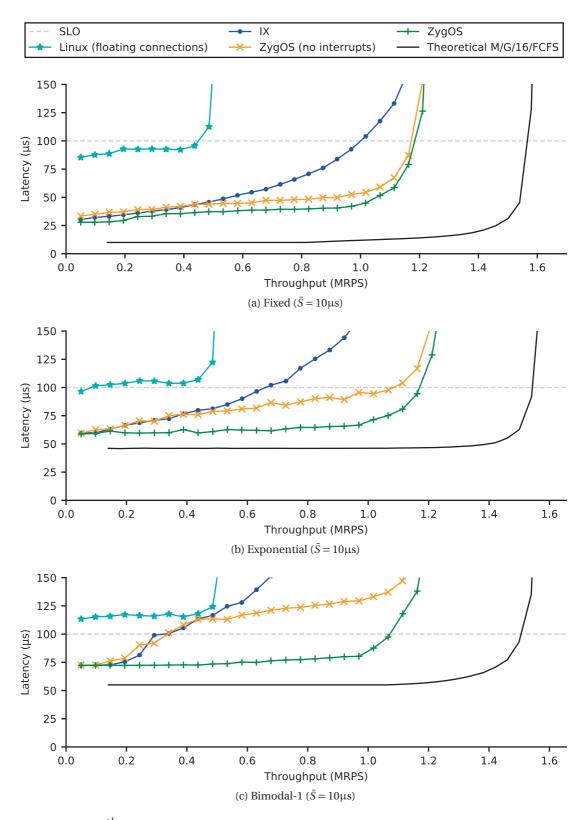

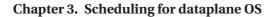

| 3.6  | 99 <sup>th</sup> percentile tail latency according to throughput for three distributions with                                                                |    |

|      | 10µs mean task granularity. The horizontal line corresponds to the SLO of $\leq 10 \times \overline{S}$ .                                                    | 69 |

| 3.7  | 99 <sup>th</sup> percentile tail latency according to throughput for three distributions with                                                                |    |

|      | 25µs mean task granularity. The horizontal line corresponds to the SLO of $\leq$ 10 × $\bar{S}.$                                                             | 70 |

| 3.8  | Maximum load that meets the SLO of the 99 <sup>th</sup> percentile $\leq 10 \times \overline{S}$ . The grey lines                                            |    |

|      | correspond to the ideal upper bounds of the two theoretical, zero-overheads,                                                                                 |    |

|      | models (centralized-FCFS and partitioned-FCFS).                                                                                                              | 71 |

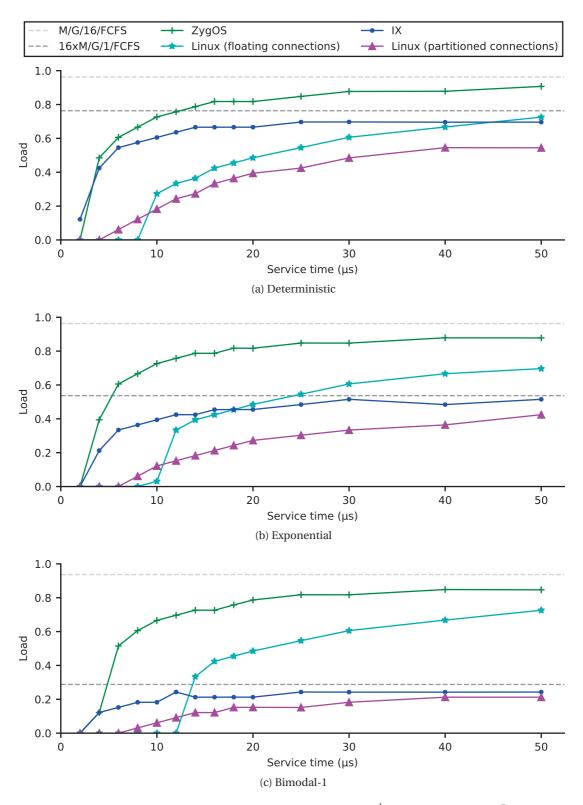

| 3.9  | Normalized rate of stealing vs. throughput for exponential service time with                                                                                 |    |

|      | mean 25 μs                                                                                                                                                   | 72 |

| 3.10 | 99 <sup>th</sup> percentile tail latency vs. throughput for two memcached workloads for                                                                      |    |

|      | Linux, IX and, ZYGOS.                                                                                                                                        | 74 |

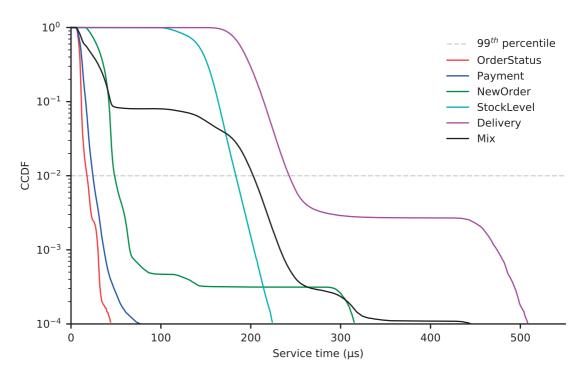

| 3.11 | Complementary CDF of task execution time for Silo running the TPC-C bench-                                                                                   |    |

|      | mark under Linux.                                                                                                                                            | 75 |

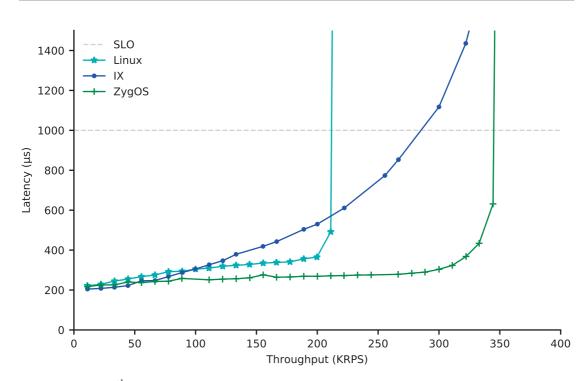

| 3.12 | 99 <sup>th</sup> percentile end-to-end latency vs. throughput for Silo running the TPC-C                                                                     |    |

|      | benchmark                                                                                                                                                    | 76 |

| 3.13 | Comparison of IX (batch size 1 and 64) and ZYGOS for a deterministic service                                                                                 |    |

|      | time of 10 µs and 2 different SLOs                                                                                                                           | 78 |

|      |                                                                                                                                                              |    |

# List of Tables

| 2.1 | Lines of code (in thousands).                                                             | 23 |

|-----|-------------------------------------------------------------------------------------------|----|

| 2.2 | The IX dataplane system call and event condition API                                      | 23 |

| 2.3 | Unloaded latency and maximum RPS for a given service-level agreement for the              |    |

|     | memcached workloads ETC and USR.                                                          | 36 |

| 2.4 | Energy Proportionality and Consolidation gains.                                           | 43 |

| 2.5 | Breakdown of flow group migration measured during the six benchmarks                      | 45 |

| 3.1 | Maximum throughput under the SLO of 1000 $\ensuremath{\mu s}$ and respective latencies at |    |

|     | approximately 50%, 75%, and 90% of that load for each Silo running the TPC-C              |    |

|     | benchmark. The number in the parentheses is the ratio of the 99 <sup>th</sup> percentile  |    |

|     | end-to-end latency to Silo's $99^{th}$ percentile service time (203µs)                    | 76 |

# **1** Introduction

## 1.1 Web-scale applications

Contemporary computer applications operate on a datacenter-scale [6]. Web search, social networking, e-commerce platforms, and ad serving are examples of applications that fall in this category. In order to support this massive scale, these applications are designed, implemented, and deployed as datacenter-wide distributed applications. Researchers have identified three major problems for the next generation of web-scale applications:

- Tail latency. User studies at Amazon, Bing, and Google have shown that even a minor increase of end-user latency in the orders of a couple of milliseconds negatively affects revenue [78, 118]. End-user latency depends in part on the internal deployment of these applications. It turns out that some of them are internally organized as a set of micro-services, which communicate in various high fan-in / fan-out patterns. The nature of this type of communication reveals the importance of tail latency [25].

- **Microsecond computing.** Datacenter operators deploy such latency-critical applications in memory in order to avoid the increased latency of accessing secondary storage. In-memory applications operate in the order of microseconds, which means that most of the commodity operating systems abstractions and mechanisms, such as schedulers, threads, and interrupt driven I/O are currently inadequate in terms of performance [8].

- Energy proportional computing. Another important aspect of datacenter-scale latency critical applications is resource efficiency. Most datacenter operators run their equipment at a deliberately low CPU utilization [7, 27, 4, 111] in order to accommodate for user requests spikes and respect the service level objectives. Of course, this practice leads to higher capital expenses. At the same time, datacenter operators face higher operational expenses, because modern CPUs do not exhibit a proportional energy-load relationship, by default. It is an elaborate task to configure the CPU so that it is more energy proportional [7].

#### **Chapter 1. Introduction**

Researchers and datacenter operators have been increasingly interested over the last few years in network dataplanes. Network dataplanes replace the traditional networking stack of commodity operating systems with a specialized and optimized stack. The goal is to provide stricter guarantees for the tail latency and at the same time support serving requests which require a couple of microseconds each. Dataplanes take advantage of the fact that existing networking stacks that are integrated in the operating systems are evolving very slowly for reasons of backward compatibility and complexity, which renders them unsuitable for modern workloads and/or hardware [121].

This thesis extends dataplanes in two ways: energy efficiency and work scheduling. The energy efficiency improvements rely on the introduction of an external control plane agent, which observes key latency metrics of the dataplane and takes coarse-grain decision in the order of milliseconds. The work scheduling improvements rely on the design and implementation of a low overhead work stealing mechanism, which is able to operate in the order of microseconds. This mechanism provides work conservation and reduces head-of-line blocking. Both mechanisms increase the potential impact of dataplanes and simplify their adoption as an architecture for serving low-latency microsecond-scale workloads with energy efficiency.

The following subsections summarize the three key issues for the next generation of web-scale applications: §1.1.1 summarizes the tail at scale problem as described by Dean et al. [25], §1.1.2 summarizes the microsecond scale computing problem as described by Barroso et al. [8], and §1.1.3 summarizes the energy proportionality computing problem as described by Barroso et al. [7].

#### 1.1.1 The tail at scale

The tail at scale problem describes the complexity of taming the tail of the latency distribution for interactive datacenter-scale applications. The basic assumption is that variability unavoidably exists in computer systems. Shared resources, daemons, global resource sharing, maintenance activities, queueing, power limits, garbage collection, and energy management can all contribute to variability.

The first class of actions to mitigate variability include differentiating service classes, keeping low-level queues short, reducing head-of-line blocking by splitting long requests into a series of short ones, managing and synchronizing background activities. Despite these efforts, variability in latency cannot be completely eliminated. Moreover, fanning out a request from a root to a number of leaf servers, which is necessary in order to scale an application, amplifies the latency variability of the root request.

The solution to the tail at scale problem takes advantages of the fact that systems are usually already designed with fault-tolerance in mind, thus most of the data and services are replicated. Hedged requests and tied requests rely on issuing the same request multiple times; when the fastest response arrives, the remaining requests are cancelled. These techniques lower tail

latency because the source of latency is often not inherent in the request itself but rather due to other forms of interference and because factors that cause variability do not tend to affect multiple nodes at the same time.

In this thesis, we will discuss dataplanes, which have the potential to help with the tail at scale problem because they are designed primarily to reduce latency and jitter, thus also reducing tail latency. Moreover, they reduce the end-to-end latency of network communication, which reduces the cost of implementing the techniques mentioned above, such as the tied requests.

#### 1.1.2 Microsecond computing

Existing hardware and software mechanisms are designed to mitigate latencies in the order of nanoseconds or milliseconds. Hardware techniques, such as prefetching, out-of-order execution, and branch prediction, can hide nanosecond-scale latencies. On the other hand, software is capable of dealing with millisecond latencies incurred by standard I/O devices, for example.

The emergence of new low-latency I/O, such as datacenter networking, raw flash devices, and non-volatile memory, makes microsecond operations much more common than before, as all these new I/O have (or are expected to have) latencies in the order of microseconds. Moreover, in-memory systems (such as RAMCloud [99]) also have latencies in the same range.

In order to utilize the full potential of this new hardware, system designers need to rethink the software stack. An RDMA operation can have a latency of 2  $\mu$ s but will take more than 50  $\mu$ s if it is used with a feature-filled RPC stack or even TCP/IP. The same behavior will be observed if a raw flash device is used with the standard storage subsystem of any operating system.

Another important aspect when dealing with microsecond-scale computing is the absolute need to reduce overheads, such as interrupts, data copies, and context switches. It is obvious that when the service time is short, an overhead of a few microseconds can lead to a reduction of the overall system efficiency.

Finally, it is worth noting that the system design for datacenter-scale computing systems must solve the microsecond computing challenge while at the same time optimize for high utilization in order to reduce the total cost of ownership of the equipment.

As the most interesting new datacenter technologies start to operate at that time scale, dataplanes become increasingly crucial as a component that can deal with these technologies. Dataplanes have been designed from the ground up in order to provide a microsecondoptimized system stack. Their layers and abstractions are tailored to the new workloads and their time scales. In this thesis, we will demonstrate how dataplanes can deal with a wide range of microsecond computations and at the same time remain resource efficient.

#### 1.1.3 Energy-proportional computing

A major effort in system design for datacenters is the case for energy-proportional computing. Energy efficiency has always been a major driver in the mobile and embedded computing areas where it maximized the battery life of devices. Lately, it is gaining significance also in general-purpose computing, because thermal constraints limit further CPU performance improvements.

Additionally, energy management is a key issue for datacenters because of cost and environmental reasons. Servers in datacenters cannot be completely turned off because each server holds a part of the datacenter's replicated data. Moreover, servers operate most of the time at between 10 and 50 percent of their maximum utilization [7, 27, 4, 111]. This behavior is by design so that servers can meet throughput and latency service level objectives even in the presence of load spikes and unexpected software or hardware events. Unfortunately, this range of utilization corresponds to the lowest energy-efficiency region of the server; essentially, a server still consumes about half of its full power when doing virtually no work.

CPU hardware improvements may improve this situation by widening the dynamic power range of the CPU. At the same time, software is responsible to use the hardware in the most energy-efficient way.

A naive implementation of a dataplane suffers from poor energy-proportionality because of constantly polling for network packets even at low load. In this thesis, we will demonstrate the design and implementation of a control agent to monitor load and adjust the resource allocation to the dataplane in the most energy efficient way.

## 1.2 Resource management for web-scale applications

It is obvious that managing and minimizing energy consumption is necessary to sustain a datacenter-scale application [7]. Datacenter operators prefer to run fully utilized servers in order to minimize their capital expenses. In addition, they would rather improve the proportionality of load vs. power to cut down on operational expenses. There are two goals towards this direction: (a) *energy proportionality*, which minimizes the energy consumed to deliver a workload and (b) *workload consolidation*, which raises server utilization and minimizes the number of servers needed for a set of workloads.

As we have seen before, a parallel trend in datacenter application is the effort to guarantee strict microscale-scale response latencies. This is necessary in order to support the large fan-out patterns that exist in modern datacenter applications, which are deployed as a set of microservices. Such latency-sensitive services are challenging to run in the presence of concurrent tasks on the same server, thus preventing workload consolidation. Additionally, these services must be able to respond to load spikes, so datacenter operators deploy them on

Figure 1.1 – Dynamic resource controls with IX for a workload consolidation scenario with a latency-sensitive application (e.g., memcached) and a background batch task (e.g., analytics). The controller, ixcp, partitions cores among the applications and adjusts the processor's DVFS settings.

dedicated servers running at low utilization. We can understand that it is difficult to combine the need for minimizing energy consumption and the trend for microsecond-scale computing.

To understand the challenges for resource management for latency-critical services, we performed a broad set of experiments under various configurations, such as core allocations, CPU frequency, use of hyperthreads, and existence of background tasks. Based on the results of these experiments and the Pareto methodology, we derived optimal strategies for achieving energy proportionality and/or workload consolidation. We integrate those strategies in IX, a state-of-the-art dataplane operating system that optimizes both throughput and latency for latency-critical workloads [13].

Fig. 1.1 illustrates our approach: the dynamic controller (ixcp) adjusts the number of cores allocated to a latency-sensitive application running on top of IX and the DVFS settings for these cores. The remaining cores can be placed in idle modes to reduce power consumption or can be safely used to run background tasks.

In §2.4.5 and §2.4.6, we introduce the design and the implementation of the control plane for IX. We present the methodology and the results of the exhaustive analysis of the configurations in §2.5.3. And, finally, in §2.6, we present the evaluation of the control plane.

# 1.3 Microsecond-scale scheduling for web-scale applications

Conventional operating system abstractions and mechanisms, such as schedulers, threads, and interrupt driven I/O, are not suitable for microsecond-scale microservices for performance reasons [8]. This observation led many researchers and engineers to develop solutions that bypass the operating system in order to achieve maximum performance [13, 103, 77, 57, 84, 59].

#### **Chapter 1. Introduction**

Most of these kernel-bypass approaches abandon the complicated schedulers [19] in favor for a much simpler execution model that involves polling, run-to-completion, and synchronization-free, flow-consistent mapping of requests to cores e.g., via RSS [90], or similar hardware mechanism.

The performance of this dataplane model relies on the elimination of system overheads that traditional operating systems face because of their complicated abstractions and layers. When the service time of the application is comparable to these overheads (e.g., for key-value stores), then the dataplane model improves throughput substantially (by up to  $6 \times [13]$ ). The limitations of this model appear for different applications or workloads where the service time is (a) either higher or (b) follows a distribution with high dispersion. In these cases, the lack of a proper scheduling mechanism reduces (and in some cases completely eliminates) the performance benefit of dataplanes vs. conventional operating systems.

The theoretical justification is well understood: (a) single-queue, multiple-processor models deliver lower tail latency than parallel single-queue, single-processor models and (b) FCFS delivers the best tail latency for low-dispersion tasks while processor sharing delivers superior results in high dispersion service time distributions [143]. Traditional operating systems follow more closely the first paradigm, while dataplanes adhere to the second one. Unfortunately, this leads to two inefficiencies: (a) the dataplane is not a work conserving scheduler, i.e., a core may be idle while there are pending requests, and (b) it suffers from head-of-line blocking, i.e., a request may be blocked until the previous tasks complete execution.

In chapter 3, we present ZYGOS, a new approach to system software optimized for µs-scale, in-memory computing. ZYGOS implements a work-conserving scheduler free of any head-of-line blocking. While the design decisions voluntarily deviate from dataplane principles, ZYGOS retains the bulk of their performance advantages.

#### 1.4 Thesis Statement

The "dataplane operating system" approach bypasses general-purpose operating systems and rely on sweeping simplifications such as the use of polling, run-to-completion, coherency-free execution, and in general the elimination of all forms of scheduling to increase throughput and/or reduce tail latency in a narrow set of conditions. These sweeping simplifications come with multiple hidden tradeoffs, such as loss of energy proportionality or head of line blocking, which limit their current applicability to a narrow set of workloads that consist of extremely small tasks with low dispersion of task service time.

This thesis demonstrates that energy management, resource allocation and request scheduling can be reintroduced within dataplane operating systems in order to eliminate these hidden tradeoffs. Energy proportionality (and workload consolidation) require a sophisticated control plane that interacts with the dataplane. Scheduling and elimination of head-of-line blocking require the design and implementation, within the dataplane, of a work-conserving scheduler suitable for microsecond-scale network tasks.

## **1.5 Thesis Contributions**

This thesis makes the following key contributions:

#### 1.5.1 Resource management control plane for dataplane operating systems

- We design and develop an external agent (control plane) which manages CPU resources (cores and frequency) while running a dataplane operating system. Certain metrics are exported in real time from the dataplane to the control plane. Then, the control plane aggregates the metrics and employs a control loop to make decisions regarding the CPU frequency and the number of dedicated CPU cores for the dataplane. The operator can configure the control plane in two modes: (a) maximum power efficiency and (b) maximum work consolidation. Under the maximum power efficiency mode, the control plane will use the minimum number of CPU cores and the minimum CPU frequency as required by the real time load of the dataplane without violating a defined service level objective (SLO). Under the maximum work consolidation mode, the control plane will schedule a configured background process to execute on as few cores as possible without violating the SLO of the dataplane.

- We develop techniques for fine-grain resource management for latency-critical workloads. This includes mechanisms for detection of load changes in sub-second timescales and for rebalancing flow-groups between cores without causing packet drops or reordered deliveries. In our experiments, this mechanism completes in less than 2 ms 95% of the time, and in at most 3.5 ms.

- We provide a methodology that uses the Pareto frontier of a set of static configurations to derive resource allocation policies. We derive two policies for memcached that respect the SLO constraints of a latency-critical in-memory key-value store. These policies lead to 42%–51% energy savings for a variety of load patterns, and enable workload consolidation with background jobs executing at 31%–44% of their peak throughput on a standalone machine. These gains are close to the Pareto-optimal bounds for the server used, within 91% and 81%–92% respectively.

- We demonstrate that precise and fine-grain control of cores, hyperthreads, and DVFS has a huge impact on both energy proportionality and workload consolidation, especially when load is highly variable. DVFS is a necessary but insufficient mechanism to control latency-critical applications that rely on polling.

#### 1.5.2 Work conserving scheduler for dataplane operating systems

- We design and implement a scheduler for a dataplane operating system. Originally, each CPU core of a dataplane process requests independently from the other cores in order to minimize contention and cache-coherence traffic. This operation model resembles the *nxM/G/1* queueing model, which is inferior to the *M/G/n* model according to queueing theory. Based on this theoretical observation, we designed a work stealing system where idle CPU cores steal connections from busy CPU cores. Additionally, we addressed the head-of-line blocking problem, which happens when a short network request follows a long network request. To mitigate this situation, we used inter-processor interrupts to notify a busy CPU core that it must perform a minimal amount of network processing in order to allow idle cores to steal requests from its queue.

- We design a new system (ZYGOS), which leverages many conventional operating system building blocks such as the use of symmetric multiprocessing networking stacks, alternate use of polling and interrupts, inter-processor interrupts (IPI), and task stealing with the overall goal of delivering a work-conserving schedule. ZYGOS is architected into three distinct layers: (a) a lower networking layer, which runs in strict isolation on each core, (b) a middle *shuffle layer* which allows idle cores to aggressively steal pending events, and (c) an upper execution layer, which exposes a commutative API to applications for scalability [22]. The shuffle layer eliminates head-of-line-blocking while also offering strong ordering semantics of events associated with the same connection.

- We implement ZYGOS, which includes an idle loop logic designed to aggressively identify task stealing opportunities throughout the operating system and down to the NIC hardware queues. Our implementation leverages hardware virtualization and the Dune framework [11] and handles IPIs in an exit-less manner similar to ELI [42].

- We develop a methodology using microbenchmarks with synthetic service times to identify system overheads as a function of task duration and distribution. This methodology allows us to identify both design limitations and implementation overheads. We apply this approach to Linux for event-driven execution models (using both partitioned and floating connections among threads), IX and ZYGOS and show that all converge as the task granularity increases, but at noticeably different rates, to distinct, well-understood models. For an SLO of 10× the mean service time at the 99<sup>th</sup> percentile, ZYGOS achieves 75% of the maximum possible theoretical load for 10µs tasks, and 88% of the equivalent load for 25µs tasks (§3.6.1).

- We compare ZyGOS to IX, a state-of-the-art dataplane with strict run-to-completion that partitions flows onto cores [13]. While ZyGOS's scheduler introduces some necessary buffering, communication and synchronization (which are measurable for extremely small tasks), it eliminates head-of-line blocking and clearly outperforms IX for tasks ≥10µs (§3.6.1). IX does outperform ZyGOS for workloads with very small task durations

such as memcached. The difference is primarily due to IX's adaptive bounded batching, which is not currently supported in ZYGOS. (§3.6.2)

• Last but not least, we evaluate the benefits of ZYGOS for an in-memory, transactional database running the TPC-C workload. Our setup uses Silo [130], a state-of-the-art, in-memory transactional database prototype. As Silo is only a library, we added clien-t/server support to Silo, ported it to Linux, IX, and ZYGOS, and benchmarked it using an open-loop load generator for an SLO of 1000µs at the 99<sup>th</sup> percentile tail latency. ZYGOS can deliver a 1.63× speedup over Linux and a 1.26× speedup over IX. The speedup over Linux is explained by the use of many dataplane implementation principles in ZYGOS. The speedup over IX is explained by ZYGOS's work-conserving scheduler, which rebalances tasks to deliver consistently low tail latency nearly up to the point of saturation (§3.6.3).

## 1.6 Thesis Roadmap

This thesis is organized as follows:

- Chapter 2 presents the design, implementation, and evaluation of the IX dataplane operating system. Additionally, it includes a study of the impact of various power management features of a modern CPU to the performance of a dataplane operating system in terms of throughput and latency. Finally, it introduces the resource management control plane for the IX dataplane operating system.

- Chapter 3 includes a detailed analysis of the throughput and latency performance of various queueing models and various service time distributions. Additionally, it introduces a methodology to identify system overheads as a function of task duration for different systems. Finally, it describes the design and implementation of ZYGOS, which extends the IX dataplane operating system with a work conserving scheduler.

- Chapter 4 concludes the thesis and presents future directions.

## 1.7 Bibliographic Notes

Portions of this thesis are based on the work I have previously published with my advisor and my colleagues. Chapter 2 is based on a journal article published in the ACM Transactions on Computer Systems (TOCS) in 2017 [13]; the article itself is based on a conference paper published in the Proceedings of the 11th Symposium on Operating System Design and Implementation (OSDI) in 2014 [12] and a conference paper published in the Proceedings of the 2015 ACM Symposium on Cloud Computing (SOCC) in 2015 [107]. Chapter 3 is based on a conference paper published in the Proceedings of the 26th ACM Symposium on Operating Systems Principles (SOSP) in 2016 [106].

#### **Chapter 1. Introduction**

It is important to note that from chapter 2 the contribution of this thesis is the Pareto analysis, and the design, implementation, and evaluation of the control plane. From chapter 3 this thesis' contribution does not include §3.2.3.

# 2 Dataplane OS and resource management

The conventional wisdom is that aggressive networking requirements, such as high packet rates for small messages and  $\mu$ s-scale tail latency, are best addressed outside the kernel, in a user-level networking stack. We present IX, a dataplane operating system that provides high I/O performance and high resource efficiency while maintaining the protection and isolation benefits of existing kernels.

IX uses hardware virtualization to separate management and scheduling functions of the kernel (control plane) from network processing (dataplane). The dataplane architecture builds upon a native, zero-copy API and optimizes for both bandwidth and latency by dedicating hardware threads and networking queues to dataplane instances, processing bounded batches of packets to completion, and by eliminating coherence traffic and multi-core synchronization. The control plane dynamically adjusts core allocations and voltage/frequency settings to meet service-level objectives.

We demonstrate that IX outperforms Linux and a user-space network stack significantly in both throughput and end-to-end latency. Moreover, IX improves the throughput of a widely deployed, key-value store by up to  $6.1 \times$  and reduces tail latency by more than  $1.9 \times$ . With three varying load patterns, the control plane saves 42%–51% of processor energy, and it allows background jobs to run at 31%–44% of their standalone throughput.

# 2.1 Introduction

Datacenter applications have evolved with the advent of web-scale services. User-facing, largescale applications such as search, social networking, and e-commerce now rely extensively on high fan-out patterns between low-latency services. Such services exhibit low per-request service times (a handful of  $\mu$ s for a key-value store), have strict service-level objectives (SLO, e.g. < 500 $\mu$ s at the 99<sup>th</sup> percentile), and must sustain massive request rates for short messages with high client fan-in connection counts and churn [3, 25, 98]. The conventional wisdom is that there is a basic mismatch between these requirements and existing networking stacks in commodity operating systems. To address the performance concern, some systems bypass the kernel and implement the networking stack in user-space [57, 59, 84, 125, 128]. While kernel bypass eliminates privilege level crossing overheads, on its own it does not eliminate the difficult tradeoffs between high packet rates and low latency (see §2.5.2). Moreover, user-level networking suffers from lack of protection. Application bugs and crashes can corrupt the networking stack and impact other workloads. Other systems go a step further by also replacing TCP/IP with RDMA in order to offload network processing to specialized adapters [31, 58, 91, 99]. However, such adapters must be present at both ends of the connection and can only be used within the datacenter.

Such latency-critical services are also challenging to run in a shared infrastructure environment. They are particularly sensitive to resource allocation and frequency settings, and they suffer frequent tail latency violations when common power management or consolidation approaches are used [71, 74]. As a result, operators typically deploy them on dedicated servers running in polling mode, forgoing opportunities for workload consolidation and reduced power consumption at below-peak utilization levels. Since these services are deployed on thousands of servers in large-scale datacenters, this deployment practice represents a huge waster in resource use.

Ideally, we want these services to achieve *energy proportionality*, so that their energy consumption scales with observed load [7, 79]. Hardware enhancements, primarily in dynamic voltage/frequency scaling (DVFS) and idle modes in modern processors [62, 114] provide a foundation for energy proportionality. Moreover, we want these services to allow for *workload consolidation*, so that any spare resources during periods of low load can be used by workloads such as background analytics in order to raise server utilization [136, 135]. The two goals map to distinct economic objectives: energy proportionality reduces operational expenses (*opex*), whereas workload consolidation reduces capital expenses (*capex*). Since capital costs often dominate the datacenter's total cost of ownership (*TCO*), consolidation is highly desirable. Nevertheless, it is not always possible, e.g., when one application consumes the entirety of a given resource, e.g., memory. In such cases, energy proportionality is a necessity.

We propose IX, an operating system designed to break the 4-way tradeoff between high throughput, low latency, strong protection, and resource efficiency. Its architecture builds upon lessons from high performance middleboxes, such as firewalls, load-balancers, and software routers [29, 66]. IX separates the control plane, which is responsible for system configuration and coarse-grain resource provisioning between applications, from the dataplanes, which run the networking stack and application logic. IX leverages Dune and virtualization hardware to run the dataplane kernel and the application at distinct protection levels and to isolate the control plane from the dataplane [11]. In our implementation, the control plane leverages mechanisms of the full Linux kernel to dynamically reallocate resources, and the dataplanes run as protected, library-based operating systems on dedicated hardware threads.

The IX dataplane allows for networking stacks that optimize for both bandwidth and latency. It is designed around a native, zero-copy API that supports processing of bounded batches of packets to completion. Each dataplane executes all network processing stages for a batch of packets in the dataplane kernel, followed by the associated application processing in user mode. This approach amortizes API overheads and improves both instruction and data locality. We set the batch size adaptively based on load. The IX dataplane also optimizes for multi-core scalability. The network adapters (NICs) perform flow-consistent hashing of incoming traffic to distinct queues. Each dataplane instance exclusively controls a set of these queues and runs the networking stack and a single application without the need for synchronization or coherence traffic during common case operation. The IX API departs from the POSIX API, and its design is guided by the commutativity rule [22]. However, the libix user-level library includes an event-based API similar to the popular libevent library [108], providing compatibility with a wide range of existing applications.

The core of the IX control plane is a dynamic controller that adjusts the number of cores allocated to a latency-sensitive application running on top of IX and the DVFS settings for these cores. The remaining cores can be placed in idle modes to reduce power consumption or can be safely used to run background tasks. The controller builds upon two key mechanisms. The first mechanism detects backlog and increases in queuing delays that exceed the allowable upper bound for the specific latency-critical application. It monitors CPU utilization and signals required adjustments in resource allocation. The second mechanism, implemented in coordination with the dataplane, quickly migrates both network and application processing between cores transparently and without dropping or reordering packets.

To evaluate the dataplane, we compare IX with a TCP/IP dataplane against Linux 4.8 and mTCP, a state-of-the-art user-level TCP/IP stack [57]. On a 10GbE experiment using short messages, IX outperforms Linux and mTCP by up to  $6.3 \times$  and  $1.8 \times$  respectively for throughput. IX further scales to a 4x10GbE configuration using a single multi-core socket. The unloaded uni-directional latency for two IX servers is  $5.8 \mu$ s, which is  $2.7 \times$  better than between standard Linux kernels and an order of magnitude better than mTCP, as both trade-off latency for throughput. Our evaluation with memcached, a widely deployed key-value store, shows that IX improves upon Linux by up to  $6.1 \times$  in terms of throughput at a given  $99^{th}$  percentile latency bound, as it can reduce kernel time, due essentially to network processing, from ~ 80% with Linux to 60% with IX.

Before evaluating the control plane, we performed an exhaustive analysis of static configurations for a latency-critical service (memcached [89]) running on a modern server to gain a principled understanding of the challenges for resource management in the presence of latency-critical services. We explored up to 224 possible settings for core allocation, use of hyperthreads, DVFS frequencies, and Turbo Boost. While our experiments use a single application, the implications have broad applicability because memcached has aggressive latency requirements, short service times, and a large number of independent clients that are common among many latency-critical applications. Our experiments reveal that there is an inherent tradeoff for any given static configuration between the maximum throughput and the overall efficiency when operating below peak load. Furthermore, the experiments reveal a Pareto-optimal frontier in the efficiency of static configurations at any given load level, which allows for close to linear improvements in energy-proportionality and workload consolidation factors.

We then evaluated our control plane with two control policies that optimize for energy proportionality and workload consolidation, respectively. A policy determines how resources (cores, hyperthreads, and DVFS settings) are adjusted to reduce underutilization or to restore violated SLO. The two policies are derived from the exhaustive analysis of the 224 static configurations. For the platform studied (a Xeon E5-2665), we conclude that: for *best energy proportionality*, (i) we start with the lowest clock rate and allocate additional cores to the latency-critical task as its load grows, using at first only one hyperthread per core; (ii) we enable the second hyperthread only when all cores are in use; and finally (iii) we increase the clock rate for the cores running the latency-critical task. For *best consolidation*, (i) we start at the nominal clock rate and add cores with both hyperthreads enabled as load increases; and (ii) finally enable Turbo Boost as a last resort.

IX demonstrates that, by revisiting networking APIs and taking advantage of modern NICs and multi-core chips, we can design systems that achieve high throughput, low latency, robust protection, and resource efficiency. It also shows that, by separating the small subset of performance-critical I/O functions from the rest of the kernel, we can architect radically different I/O systems and achieve large performance gains, while retaining compatibility with the huge set of APIs and services provided by a modern OS like Linux. Finally, we also demonstrate that latency-sensitive applications can be deployed efficiently through dynamic resource allocation policies that target a specific tail latency.

This chapter contains the research contributions of two conference papers that focus on the dataplane [12] and the control plane [107], respectively. The evaluation results presented in this chapter have been reproduced with IX v.1.0, which is available in open-source [55]. A corresponding technical report provides detailed instructions to reproduce all the results of this chapter [105].

The rest of the chapter is organized as follows. §2.2 motivates the need for a new OS architecture. §2.3 and §2.4 present the design principles and implementation of IX. §2.5 presents the quantitative evaluation. §2.7 and §2.8 discuss open issues and related work. We conclude in §2.9.

# 2.2 Background and Motivation

Our work focuses on improving operating systems for applications with aggressive networking requirements running on multi-core servers.

#### 2.2.1 Challenges for Datacenter Applications

Large-scale, datacenter applications pose unique challenges to system software and their networking stacks:

**Microsecond tail latency** To enable rich interactions between a large number of services without impacting the overall latency experienced by the user, it is essential to reduce the latency for some service requests to a few tens of  $\mu$ s [5, 115]. Because each user request often involves hundreds of servers, we must also consider the long tail of the latency distributions of RPC requests across the datacenter [25]. Although tail-tolerance is actually an end-to-end challenge, the system software stack plays a significant role in exacerbating the problem [71]. Overall, each service node must ideally provide tight bounds on the 99<sup>th</sup> percentile request latency.

**High packet rates** The requests and, often times, the replies between the various services that comprise a datacenter application are quite small. In Facebook's memcached service, for example, the vast majority of requests use keys shorter than 50 bytes and involve values shorter than 500 bytes [3], and each node can scale to serve millions of requests per second [98].

The high packet rate must also be sustainable under a large number of concurrent connections and high connection churn [43]. If the system software cannot handle large connection counts, there can be significant implications for applications. The large connection count between application and memcached servers at Facebook made it impractical to use TCP sockets between these two tiers, resulting in deployments that use UDP datagrams for get operations and an aggregation proxy for put operations [98].

**Protections** Since multiple services commonly share servers in both public and private datacenters [25, 49, 119], there is need for isolation between applications. The use of kernel-based or hypervisor-based networking stacks largely addresses the problem. A trusted network stack can firewall applications, enforce access control lists (ACLs), and implement limiters and other policies based on bandwidth metering.

**Resource efficiency** The load of datacenter applications varies significantly due to diurnal patterns and spikes in user traffic. Ideally, each service node will use the fewest resources (cores, memory, or IOPS) needed to satisfy packet rate and tail latency requirements at any point. Unfortunately, classic operating system schedulers are ill-matched to ensure tail control [71, 74]. Novel dynamic resource management mechanisms and policies are required to improve energy proportionality and workload consolidation in the presence of latency-sensitive applications [79, 80, 73].

#### 2.2.2 The Hardware – OS Mismatch

The wealth of hardware resources in modern servers should allow for low latency and high packet rates for datacenter applications. A typical server includes one or two processor sockets,

each with eight or more multithreaded cores and multiple, high-speed channels to DRAM and PCIe devices. Solid-state drives and PCIe-based Flash storage are also increasingly popular. For networking, 10 GbE NICs and switches are widely deployed in datacenters, with 40 GbE and 100 GbE technologies right around the corner. The combination of tens of hardware threads and 10 GbE NICs should allow for rates of 15M packets/sec with minimum sized packets. We should also achieve 10–20µs round-trip latencies given 3µs latency across a pair of 10 GbE NICs, one to five switch crossings with cut-through latencies of a few hundred ns each, and propagation delays of 500ns for 100 meters of distance within a datacenter.

Unfortunately, commodity operating systems have been designed under very different hardware assumptions. Kernel schedulers, networking APIs, and network stacks are based on an assumption of multiple applications sharing a single processing core and packet inter-arrival times being many times higher than the latency of interrupts and system calls. As a result, such operating systems trade off both latency and throughput in favor of fine-grain resource scheduling. Interrupt coalescing (used to reduce processing overheads), queuing latency due to device driver processing intervals, the use of intermediate buffering, and CPU scheduling delays frequently add up to several hundred µs of latency to remote requests. The overheads of buffering and synchronization needed to support flexible, fine-grain scheduling of applications to cores increases CPU and memory system overheads, which limits throughput. As requests between service tiers of datacenter applications often consist of small packets, common NIC hardware optimizations, such as TCP segmentation and receive side coalescing, have a marginal impact on packet rate.

#### 2.2.3 Alternative Approaches

Since the network stacks within commodity kernels cannot take advantage of the abundance of hardware resources, a number of alternative approaches have been suggested. Each alternative addresses a subset, but not all of the requirements for datacenter applications.

**User-space networking stacks** Systems such as OpenOnload [125], mTCP [57], and Sandstorm [84] run the entire networking stack in user-space in order to eliminate kernel crossing overheads and optimize packet processing without incurring the complexity of kernel modifications. However, there are still tradeoffs between packet rate and latency. For instance, mTCP uses dedicated threads for the TCP stack, which communicate at relatively coarse granularity with application threads. This aggressive batching amortizes switching overheads at the expense of higher latency (see §2.5). It also complicates resource sharing as the network stack must use a large number of hardware threads regardless of the actual load. More importantly, security tradeoffs emerge when networking is lifted into the user-space and application bugs can corrupt the networking stack. For example, an attacker may be able to transmit raw packets (a capability that normally requires root privileges) to exploit weaknesses in network protocols and impact other services [14]. It is difficult to enforce any security or metering policies beyond what is directly supported by the NIC hardware. Alternatives to TCP In addition to kernel bypass, some low-latency object stores rely on RDMA to offload protocol processing on dedicated Infiniband host channel adapters [31, 58, 91, 99]. RDMA can reduce latency, but requires that specialized adapters be present at both ends of the connection. Using commodity Ethernet networking, Facebook's memcached deployment uses UDP to avoid connection scalability limitations [98]. Even though UDP is running in the kernel, reliable communication and congestion management are entrusted to applications.

**Alternatives to POSIX API** MegaPipe replaces the POSIX API with lightweight sockets implemented with in-memory command rings [45]. This reduces some software overheads and increases packet rates, but retains all other challenges of using an existing, kernel-based networking stack.

**OS enhancements** Tuning kernel-based stacks provides incremental benefits with superior ease of deployment. Linux SO\_REUSEPORT allows multi-threaded applications to accept incoming connections in parallel. Affinity-accept reduces overheads by ensuring all processing for a network flow is affinitized to the same core [102]. Recent Linux Kernels support a busy polling driver mode that trades increased CPU utilization for reduced latency [52], but it is not yet compatible with epoll. When microsecond latencies are irrelevant, properly tuned stacks can maintain millions of open connections [141].

## 2.3 IX Design Approach

The first two requirements in §2.2.1 — microsecond latency and high packet rates — are not unique to datacenter applications. These requirements have been addressed in the design of middleboxes such as firewalls, load-balancers, and software routers [29, 66] by integrating the networking stack and the application into a single *dataplane*. The two remaining requirements — protection and resource efficiency — are not addressed in middleboxes because they are single-purpose systems, not exposed directly to users.

Many middlebox dataplanes adopt design principles that differ from traditional OSes. First, they *run each packet to completion*. All network protocol and application processing for a packet is done before moving on to the next packet, and application logic is typically intermingled with the networking stack without any isolation. By contrast, a commodity OS decouples protocol processing from the application itself in order to provide scheduling and flow control flexibility. For example, the kernel relies on device and soft interrupts to context switch from applications to protocol processing. Similarly, the kernel's network stack will generate TCP ACKs and slide its receive window even when the application is not consuming data, up to an extent. Second, middlebox dataplanes optimize for *synchronization-free operation* in order to scale well on many cores. Network flows are distributed into distinct queues via flow-consistent hashing and common case packet processing requires no synchronization or coherence traffic between cores. By contrast, commodity OSes tend to rely heavily on coherence traffic and are structured to make frequent use of locks and other forms of synchronization.

IX extends the dataplane architecture to support untrusted, general-purpose applications and satisfy all requirements in §2.2.1. Its design is based on the following key principles:

**Separation and protection of control and data plane** IX separates the control function of the kernel, responsible for resource configuration, provisioning, scheduling, and monitoring, from the dataplane, which runs the networking stack and application logic. Like a conventional OS, the control plane multiplexes and schedules resources among dataplanes, but in a coarse-grained manner in space and time. Entire cores are dedicated to dataplanes, memory is allocated at large page granularity, and NIC queues are assigned to dataplane cores. The control plane is also responsible for elastically adjusting the allocation of resources between dataplanes.

The separation of control and data plane also allows us to consider radically different I/O APIs, while permitting other OS functionality, such as file system support, to be passed through to the control plane for compatibility. Similar to the Exokernel [35], each dataplane runs a single application in a single address space. However, we use modern virtualization hardware to provide three-way isolation between the control plane, the dataplane, and untrusted user code [11]. Dataplanes have capabilities similar to guest OSes in virtualized systems. They manage their own address translations, on top of the address space provided by the control plane, and can protect the networking stack from untrusted application logic through the use of privilege rings. Moreover, dataplanes are given direct pass-through access to NIC queues through memory mapped I/O.

**Run to completion with adaptive batching** IX dataplanes run to completion all stages needed to receive and transmit a packet, interleaving protocol processing (kernel mode) and application logic (user mode) at well-defined transition points. Hence, there is no need for intermediate buffering between protocol stages or between application logic and the networking stack. Unlike previous work that applied a similar approach to eliminate receive livelocks during congestion periods [92], IX uses run to completion during all load conditions. Thus, we are able to use polling and avoid interrupt overhead in the common case by dedicating cores to the dataplane. We still rely on interrupts as a mechanism to regain control, for example, if application logic is slow to respond. Run to completion improves both message throughput and latency because successive stages tend to access many of the same data, leading to better data cache locality.

The IX dataplane also makes extensive use of batching. Previous systems applied batching at the system call boundary [45, 124] and at the network API and hardware queue level [57]. We apply batching in every stage of the network stack, including but not limited to system calls and queues. Moreover, we use batching *adaptively* as follows: (i) we never wait to batch requests and batching only occurs in the presence of congestion; (ii) we set an upper bound on the number of batched packets. Using batching only on congestion allows us to minimize the impact on latency, while bounding the batch size prevents the live set from exceeding cache capacities and avoids transmit queue starvation. Batching improves packet