# An Energy Efficient Power Converter for Zero Power Wearable Devices

### THÈSE N° 8341 (2018)

PRÉSENTÉE LE 12 JANVIER 2018

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR

LABORATOIRE D'ÉLECTRONIQUE ET TRAITEMENT DU SIGNAL

PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

#### PAR

#### Milad ATAEI ASHTIANI

acceptée sur proposition du jury:

Prof. J. Brugger, président du jury Prof. P.-A. Farine, Dr A. Boegli, directeurs de thèse Dr S. Tanner, rapporteur Dr K. Imfeld, rapporteur Dr J.-M. Sallese, rapporteur

ای برادر تو بهان اندیشه ای ما بقی تو استخوان و ریشه ای مولانا - مولانا

Oh brother, you are nothing but your thoughts

The rest of you is merely skin and bones

-Rumi 1207-1273, translated by B. Gooch

To my beloved mother, Mahrokh, and my beloved father, Abolfazl

### Acknowledgment

In the first place, I am grateful to my God who has given me all the blessings that I have.

I have to express my gratitude to the individuals without whom this work would not have been possible. I would first like to express my sincere gratitude to my advisor Prof. Pierre-Andre Farine. His kindness, motivation, and support make me confident work on my Ph.D. and to overcome the obstacle that I have faced during my studies. I always acknowledge his effort to provide the best condition in the ESPLAB group to work. I am sincerely thankful to my co-advisor Dr. Alexis Boegli who gave me his trust and support when I needed them the most. His practical and engineering foresight in solving academic issues were truly helpful for my Ph.D thesis. The results achieved in this work are deeply indebted to this vision of his. I should thank him for the freedom that he gave me in my research and his help in time management of the project as well.

I am grateful to the members of my thesis committee, Prof. Juergen Brugger, Dr. Steve Tanner, Dr. Kilian Imfeld, and Dr. Jean-Michel Sallese, to take time out from their busy schedule to read this manuscript and provide me with feedback. I appreciate the time and effort that emeritus Prof. Urs Graf spent to review a section of this work and provide me his valuable comments.

A special thanks goes to my colleagues and friends, Christian Robert, Saeed Ghamari, Hugo Franca, and Reza Ghanaatian, who helped me in the different stages of this work to solve difficult problems. I have to acknowledge Denis Pravica, Erica Debels, Severin Sidler, and Andreas Roovers, students or interns in our group, who contributed to the memory data recording measurements at the application level and the analog front-end design.

The presented work was carried out in the frame of an interdisciplinary project collaborating with different EPFL and ETHZ laboratories and university hospitals. The project was evaluated by the Swiss National Science Foundation and funded by Nano-Tera with Swiss Confederation financing. The collaboration in this project with the other Ph.D. students and scientists was exciting and instructive to me. I should thank Moritz Thielen, Elham Barzegaran, Dennis Majoe, and Christopher Borsa for the helpful discussions. A special thanks goes to Dr. Danick Briand who introduced the project and EPSLAB to me at the beginning.

I feel indebted to my professors during my studies in Iran. I am grateful to Prof. Nabavi, Dr. Mehrshahi, Prof. Vahid Ahmadi, Dr. Eshghi, Dr. Saniei, Dr. Fotowat-Ahmady, and Dr. Atarodi. They shaped my academic career and knowledge in electrical engineering. Most of my Ph.D. research depended on what I learned from them.

So many great friends and colleagues have supported me and helped me through the all these years I have been in Switzerland. Inevitably I will forget to name some, but among the others, I am genuinely grateful to Miguel, Vasili, Vincenzo, Patrick, Sanket, Babak, Mitko, Pradyumna, Urs, Youssef, Vincent, Jérémy, Elham, Leila, Rava, Endrit, Kiarash, Omid, Navid, Dordaneh, Parisa, Jean-Philippe, Ali, Rubaiyet, Martin, Flavien, Sara, and Cyril. I sincerely appreciate Mrs. Joelle Banjac for the all the support and administrative help she provided me during my time at EPFL. I should thank Aleksandar and Siavash for their friendship and their support and help especially when I just arrived at EPFL. I deeply appreciate Saeed, Christelle, Mohssen, Abbas, and Ali Dabirian for their truly wonderful friendship and all the best memories that they have made for me during these years.

I am truly grateful to my brother Mehrad, my sister Ghazaleh, and my brother-in-law Sasha who are my best friends as well. Their unflagging support keeps me happy and gives me the strength to work and live far from them. I am thankful to my other family members, especially my grandmothers who always believe in me. I acknowledge two persons to whom I am most grateful in my life: my mother Mahrokh Zakikhani and my father Abolfazl Ataei Ashtiani. I cannot describe with words my gratitude for their unconditional love, support, and all they have done for me throughout my entire life.

### **Abstract**

Early diagnosis of Alzheimer's and epilepsy requires monitoring a subject's development of symptoms through electroencephalography (EEG) signals over long periods. Wearable devices enable convenient monitoring of biosignals, unlike complex and costly hospital equipment. The key to achieving a fit and forgettable wearable device is to increase its operating cycle and decrease its size and weight. Instead of batteries, which limit the life cycle of electronic devices and set their form factor, ambient energy can be employed as an alternative energy source. Body heat and environmental light can power wearable devices through energy-scavenging technologies. The energy available to harvest is limited, and therefore the harvester transducers should be tailored according to on the application and the sensor placement. This leaves a wide variety of transducers with an extensive range of impedances and voltages.

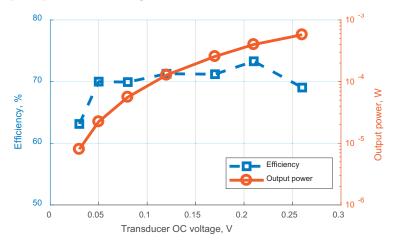

To realize an autonomous wearable device, the power converter energy harvester, which is responsible for transferring the transducer's low-voltage energy and providing it as a high-potential-energy source, has to be very efficient and maintain its efficiency despite potential transducer replacement or variations in environmental conditions. This thesis presents a detailed design of an efficient integrated power converter for use in an autonomous wearable device. The design is based on the examination of both power losses and power transfer in the power converter. The efficiency bound of the converter is derived from the specifications of its transducer. The inflexible converter parameters are optimized and fixed with regard to the worst-case efficiency scenario. The tuning ranges for the reconfigurable parameters are extracted to keep the converter efficient with variations in the transducer specifications. With the efficient design and the manual tuning of the reconfigurable parameters, the converter can work optimally with different types of transducers, and keeps its efficiency in the converter demonstrate an efficiency of higher than 50%

viii Abstract

and 70% with two different transducers having an open-circuit voltage as low as 20 mV and 100 mV, respectively.

The power converter should be able to reconfigure itself without manual tunings to keep its efficiency despite changes in the harvesters' specifications. The second portion of this dissertation addresses this issue with a proposed design methodology to implement a control section. The control section adjusts the converter's reconfigurable parameters by examining the power transfer and loss and through concurrent closed loops. The reconfigurable parameters here are the converter's switching durations. The concurrent loops working together raise a serious concern regarding stability. The system is designed and analyzed in the time domain with the state-space averaging (SSA) model to address the stability issue. The ultra-lowpower control section obtained from the SSA model estimates the power and loss with a reasonable accuracy, and adjusts the timings in a stable manner. The entire control section consumes only 30 nW dynamic power at 10 kHz. The control section tunes the converter's speed or its working frequency depending on the available power. The frequency clocks the entire architecture, which is designed asynchronously; therefore, the power consumption of the system depends on the power available from the transducer. Low-power circuits and techniques are introduced and employed in the sub-circuits to realize the ultra-low-power converter. The system is implemented using 0.18 µm CMOS technology. For an input as low as 7 mV, the converter is not only functional but also has an efficiency of more than 40%. The efficiency can reach 70% with an input voltage of 50 mV. The system operates in a range of just a few of millivolts to half a volt with ample efficiencies. It can work at an optimal point with different transducers and environmental conditions. This work does not focus on the cold start, and it is assumed that the output energy storage has some initial charge during start-up. The prior-art has addressed the low-voltage start-up issue using different methods.

**Keywords**: Analog design, application specific, autonomous system, chopper, CMOS, DC-DC converter, digital control oscillator, dynamic loss, efficiency, energy harvester, energy scavenging, frequency tuning, inductor-based, integrated circuit, low-power, low-voltage, medical device, mixed-signal, phase tuning, photovoltaic cell, power converter, power electronics, power transfer, reconfigurable, solar cell, state space, static loss, thermoelectric generator, ultra-low-power, ultra-low-voltage, wearable device, zero-power

### Résumé

Le diagnostic précoce de la maladie d'Alzheimer et de l'épilepsie nécessite une surveillance sur de longues périodes du développement des symptômes par électroencéphalographie (EEG). L'utilisation de dispositifs de mesures portables permet la surveillance de signaux biologiques en libérant le patient d'une hospitalisation et de l'utilisation d'équipements complexes et coûteux. Les clés du succès sont l'augmentation des cycles d'opération, la miniaturisation et la diminution du poids. Au lieu de batteries, qui limitent la durée de vie et influencent grandement la taille du dispositif, l'énergie ambiante peut être utilisée comme source. Grâce aux technologies de récupération d'énergie, il est envisageable d'utiliser la chaleur corporelle et la lumière ambiante pour alimenter de tels dispositifs. L'énergie à disposition étant limitée, sa production doit être adaptée au positionnement des capteurs et à l'application visée. Le choix des générateurs d'énergie est tel qu'il débouche sur une grande gamme d'impédances et de tensions différentes.

Pour réaliser un dispositif portable autonome, il faut un convertisseur de puissance chargé de transformer l'énergie produite à basse tension par un générateur en une source d'énergie utilisable par une électronique. Ce convertisseur de puissance doit être efficace et en mesure de maintenir son efficacité pour différents types de générateurs et pour des variations de conditions environnementales. Cette thèse présente la conception d'un tel convertisseur intégré. Cette conception se base sur l'examen des pertes et de l'efficacité du transfert de puissance. La limite d'efficacité est dérivée des spécifications du générateur. Les paramètres du convertisseur sont optimisés et fixés en fonction du scénario d'efficacité le plus défavorable. Les plages de régulation du convertisseur ont été définies de manière à en assurer la plus haute efficacité. En optimisant l'efficacité et l'utilisation de paramètres de configuration externes, le convertisseur peut fonctionner de manière optimale avec différents types de générateurs tout en maintenant son efficacité même en présence de basses tensions. Les mesures du convertisseur montrent que des efficacités supérieures à 50%

x Résumé

et 70% sont obtenues avec deux générateurs différents dont la tension en circuit ouvert sont respectivement de  $20~\mathrm{mV}$  et  $100~\mathrm{mV}$ .

Pour maintenir son efficacité malgré le changement de spécifications des générateurs, un convertisseur de puissance doit pouvoir s'auto configurer, c'est-à-dire ne pas avoir recours à des réglages externes. La deuxième partie de cette thèse traite de cette question en proposant une méthodologie de conception visant à mettre en œuvre une régulation automatique. Cette régulation ajuste les paramètres reconfigurables en surveillant le transfert et la perte de puissance au travers de boucles concurrentes de contrôle. Les paramètres réglables sont les durées de commutation. Les boucles de contrôles concurrentes posent. Pour répondre à cette préoccupation, le système est conçu et analysé dans le domaine temporel avec un modèle de movennes d'espace-état (state-space averaging SSA). La régulation obtenue grâce à ce modèle (SSA) fonctionne à très faible consommation en estimant la puissance et les pertes avec une précision raisonnable et ajuste le diagramme temporel d'une manière stable. Le circuit de régulation obtenu ne consomme que 30 nW à 10 kHz. Il régule la vitesse du convertisseur, c'est-à-dire sa fréquence de travail en fonction de la puissance disponible. Celle-ci cadence toute l'architecture qui fonctionne de manière asynchrone. La consommation du système dépend donc de la puissance disponible fournie par le générateur. Des circuits faible consommation et des techniques particulières sont introduits et utilisés dans les sous-circuits afin d'atteindre une consommation ultra-basse. Le système a été implémenté en utilisant une technologie CMOS à 0.18 µm. Avec une tension d'entrée de seulement 7 mV, le convertisseur est fonctionnel avec un rendement de plus de 40%. Le rendement peut atteindre 70% avec une tension d'entrée de 50 mV. Le circuit fonctionne à partir de quelques millivolts jusqu'à un demi-volt. Il adapte son fonctionnement de façon optimal pour différents générateurs et pour des conditions environnementales qui varient. Pour démarrer, le circuit a besoin d'une charge initiale à la sortie. L'art antérieur abordant déjà la problématique du « démarrage à froid », ce travail n'en traite pas.

Mots-clés: Conception analogique, application spécifique, système autonome, découpage, CMOS, convertisseur DC-DC, oscillateur numérique, pertes dynamiques, rendement, récupérateur d'énergie, récupération d'énergie, accord de fréquence, à base d'inductance, circuit intégré, basse consommation, faible tension, dispositif médical, signal mixte, accord de phase, cellule photovoltaïque, convertisseur de puissance, électronique de puissance, transfert de puissance, reconfigurable, cellule solaire, espace-état, pertes statiques, générateur thermoélectrique, ultra-basse puissance, ultra-basse tension, dispositif portable, zéro puissance, zero-power

## Contents

| $\mathbf{Ac}$          | know                   | ledgment                                                          | v    |

|------------------------|------------------------|-------------------------------------------------------------------|------|

| $\mathbf{A}\mathbf{b}$ | strac                  | t                                                                 | vii  |

| Ré                     | sumé                   |                                                                   | ix   |

| Co                     | ntent                  | S                                                                 | xi   |

| Lis                    | t of f                 | igures                                                            | xv   |

| Lis                    | t of t                 | ables                                                             | xix  |

| 1 I                    | $\operatorname{ntrod}$ | $\operatorname{uction}$                                           | 1    |

|                        | 1.1                    | Thesis goal                                                       | 4    |

| <b>2</b> I             | esign                  | ning a zero-power wearable medical device                         | 9    |

|                        | 2.1                    | A wearable device for early diagnosis of Alzheimer's and epilepsy | y 10 |

|                        | 2.2                    | Analog front-end                                                  | 14   |

|                        |                        | 2.2.1 EEG amplifier                                               | 17   |

|                        |                        | 2.2.1.1 OTA design                                                | 19   |

|                        |                        | 2.2.2 ADC design                                                  | 21   |

|                        |                        | 2.2.2.1 Sampling Switches                                         | 23   |

|                        |                        | 2.2.2.2 Comparator and buffer                                     | 24   |

|                        |                        | 2.2.2.3 Capacitor bank                                            | 24   |

|                        |                        | 2.2.3 Characterization of the analog front-end                    | 24   |

|                        | 2.3                    | Low-voltage power conversion for energy harvesters                | 26   |

|                        |                        | 2.3.1 Fully integrated switched capacitor power converters        | 28   |

xii Contents

|   |         | 2.3.2 Low-voltage inductor-based power converters              | 30 |

|---|---------|----------------------------------------------------------------|----|

|   | 2.4     | Conclusion                                                     | 33 |

| 3 | Integra | ated power converter design for low-voltage harvesters         | 35 |

|   | 3.1     | Efficient low-voltage power conversion: Overview               | 35 |

|   | 3.2     | Efficient power converter design                               | 37 |

|   |         | 3.2.1 Power transfer and power loss in a low-voltage converter | -  |

|   |         | 3.2.2 Loss optimization                                        | 42 |

|   |         | 3.2.3 Power transfer optimization                              | 45 |

|   |         | 3.2.4 Switch sizing optimization                               | 47 |

|   | 3.3     | Circuit design for the system specifications                   | 48 |

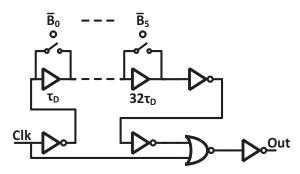

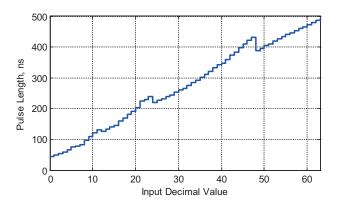

|   |         | 3.3.1 $t_2$ pulse generator design                             | 49 |

|   |         | 3.3.2 $t_I$ pulse generator                                    | 52 |

|   |         | 3.3.3 Deadtime delay generator                                 | 53 |

|   |         | 3.3.4 Power switch implementation                              | 54 |

|   | 3.4     | Measurement results and discussion                             | 55 |

|   | 3.5     | Conclusion                                                     | 62 |

| 4 | Self-re | configurable efficient power converter                         | 63 |

|   | 4.1     | Self-reconfiguration of energy harvester converters: Overview  | 64 |

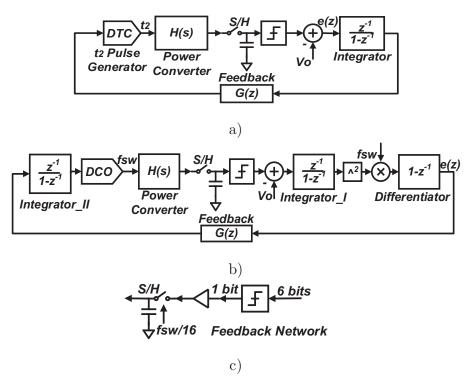

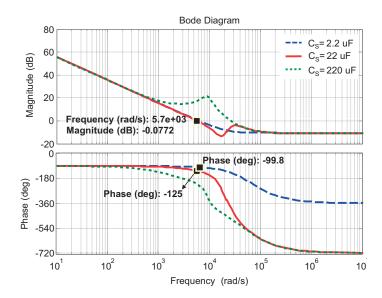

|   | 4.2     | Control system modeling and design                             | 66 |

|   |         | 4.2.1 <i>t</i> <sub>2</sub> control loop                       | 69 |

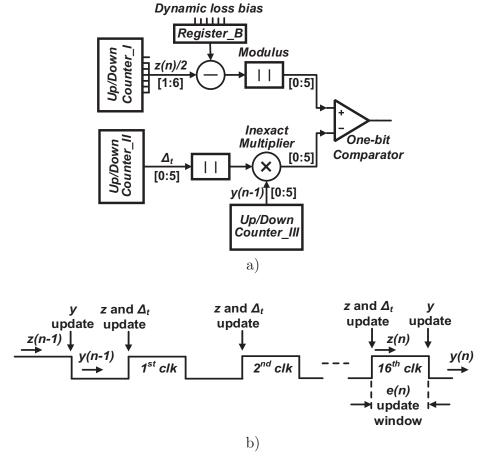

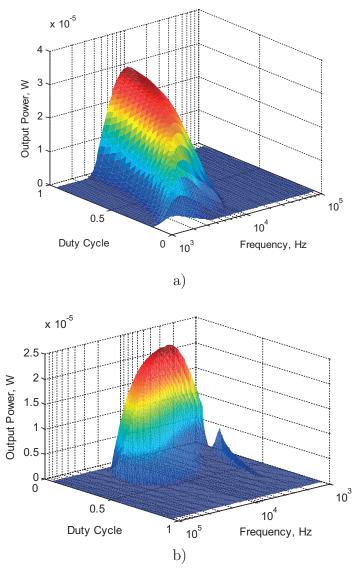

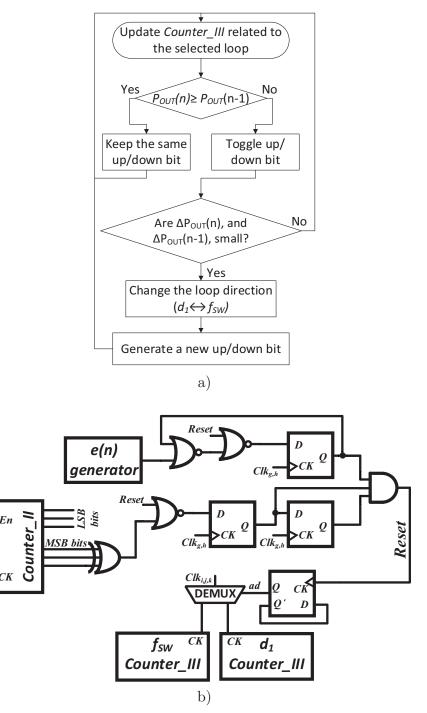

|   |         | 4.2.2 $f_{SW}$ and $d_1$ control loops                         | 71 |

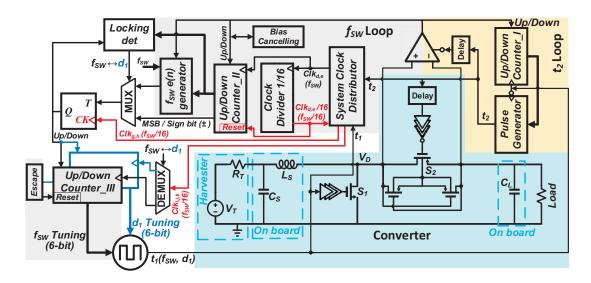

|   | 4.3     | System implementation                                          | 72 |

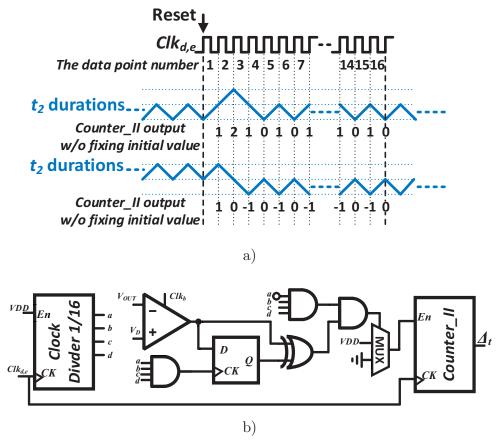

|   |         | 4.3.1 Implementation of the $t_2$ loop                         | 73 |

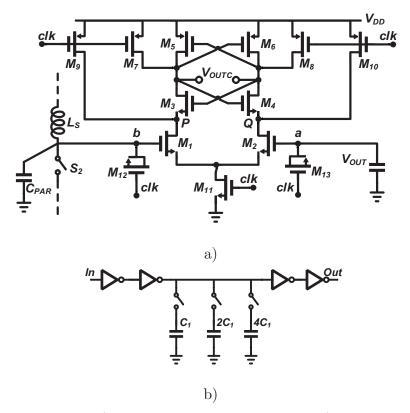

|   |         | 4.3.2 Latch comparator                                         | 74 |

|   |         | 4.3.2.1 Charge injection in the comparator                     | 74 |

|   |         | 4.3.2.2 Comparator offset                                      | 76 |

|   |         | 4.3.2.3 Comparator noises                                      | 77 |

|   |         | 4.3.3 Implementation of the $f_{SW}$ and $d_1$ loops           | 78 |

xiii Contents

|           | 4.3.3.1 Low-complexity fsw loop                                 | 79  |

|-----------|-----------------------------------------------------------------|-----|

|           | 4.3.3.2 Moderate-complexity $f_{SW}$ loop                       | 80  |

|           | 4.3.4 System convergence to the maximum efficiency              | 88  |

|           | 4.3.5 Digitally controlled oscillator                           | 93  |

|           | 4.3.6 Control system clock design                               | 97  |

| 4.4       | Measurement results                                             | 100 |

|           | 4.4.1 Chip I characterizations and discussions                  | 102 |

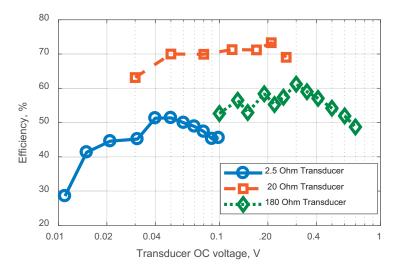

|           | 4.4.2 <i>Chip II</i> characterizations and discussions          | 105 |

| 4.5       | Conclusion                                                      | 115 |

| 5 Conclu  | usion and future directions                                     | 117 |

| 5.1       | Conclusion and summary                                          | 117 |

| 5.2       | Future directions                                               | 119 |

| A Appen   | dix                                                             | 121 |

| A.1       | Calculating the input-referred noise of the dynamic comparator. | 121 |

| B Appen   | dix                                                             | 123 |

| B.1       | Error signal approximation in the frequency loop without any mu | -   |

| List of A | cronyms                                                         |     |

|           |                                                                 |     |

|           | ıphy                                                            |     |

| Curriculi | um vitae                                                        | 141 |

# List of figures

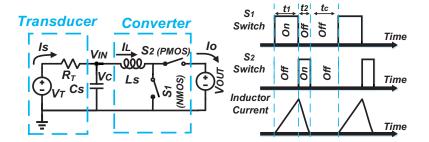

| Figure 3-1: a) General architecture of a converter [65, 70, 72] and b) its basic schematic, and timing diagram                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

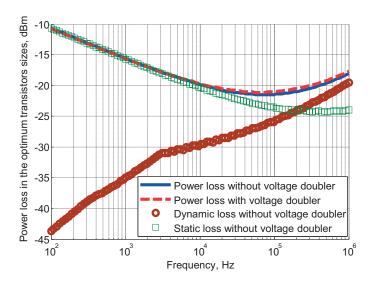

| Figure 3-2: Optimum power loss for optimized switch sizes versus frequency.                                                                                                   |

| 44                                                                                                                                                                            |

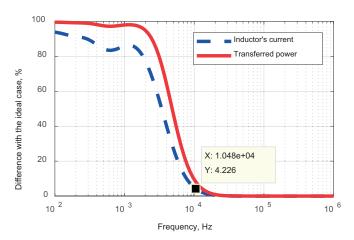

| Figure 3-3: The difference between the actual and the ideal inductor peak current, and the difference between the actual and ideal transferred power                          |

|                                                                                                                                                                               |

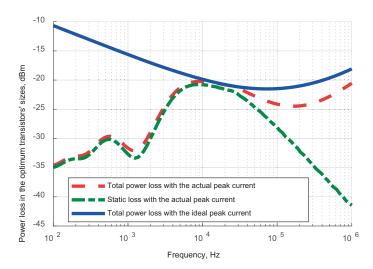

| Figure 3-4: Optimum power loss for optimized switches' sizes versus frequency                                                                                                 |

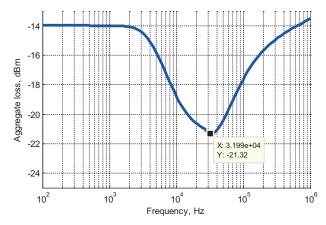

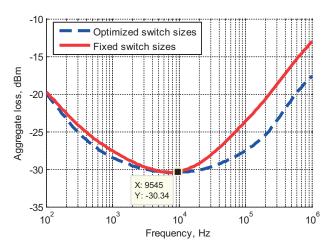

| Figure 3-5: Converter aggregate loss versus frequency for TEG1                                                                                                                |

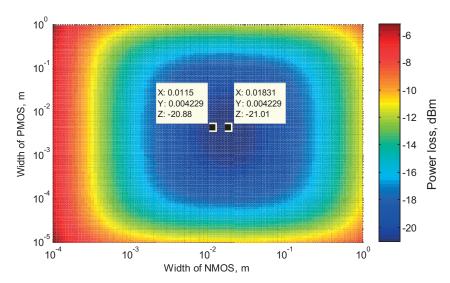

| Figure 3-6: Power loss as a function of switches' sizes at the optimum working frequency                                                                                      |

| Figure 3-7: Converter aggregate loss versus frequency for TEG250                                                                                                              |

| Figure 3-8: Pulse generator schematic                                                                                                                                         |

| Figure 3-9: Length of generated $t_2$ pulses for each input of the pulse generator                                                                                            |

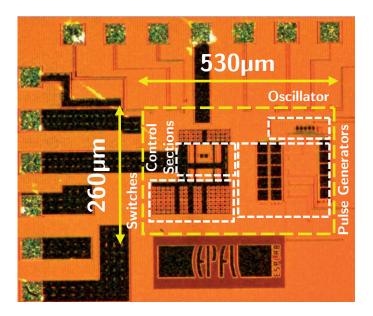

| Figure 3-10: Microchip of the converter designed in UMC 0.18 $\mu m$ CMOS56                                                                                                   |

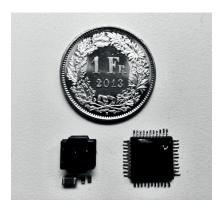

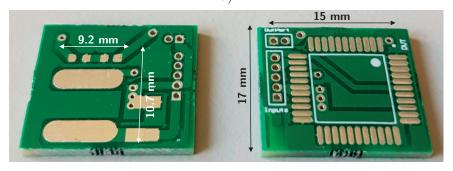

| Figure 3-11: (a) All the necessary components for the PCB, including the chip, an inductor, two capacitors and a resistor. (b) A two-sided target PCB fabricated for the chip |

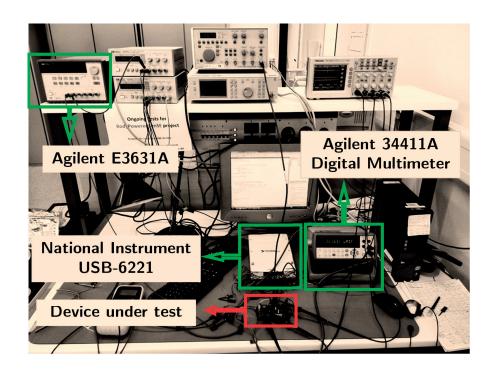

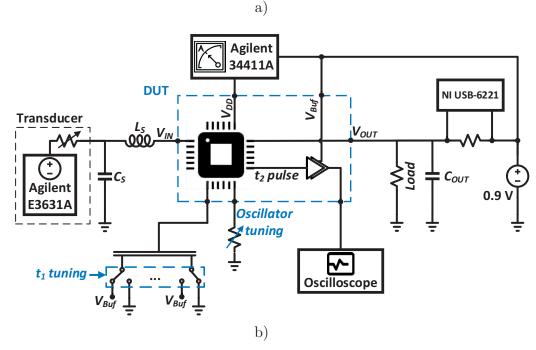

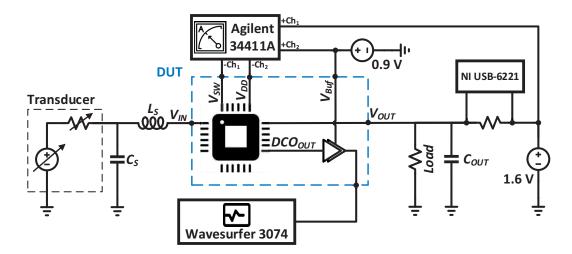

| Figure 3-12: a) actual and b) schematic of power converter measurement test setup                                                                                             |

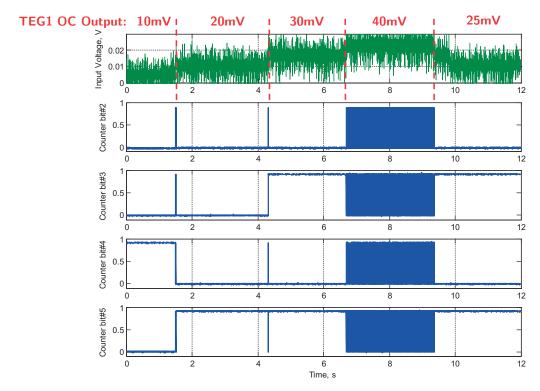

| Figure 3-13: The converter input voltage and counter output bits for lock and unlock conditions of the synchronizing feedback                                                 |

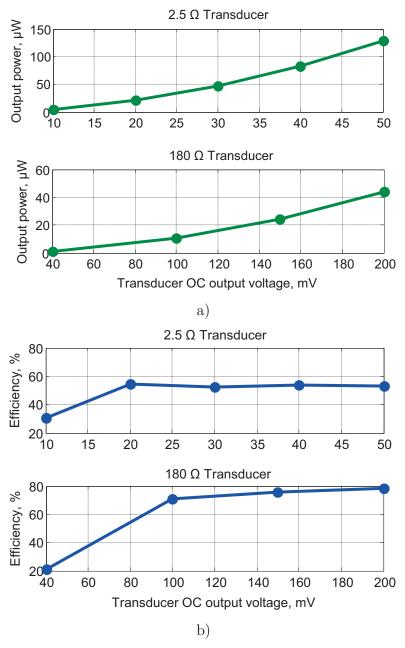

| Figure 3-14: Measurements of the converter's (a) output power and (b) efficiency for TEG1 and TEG260                                                                          |

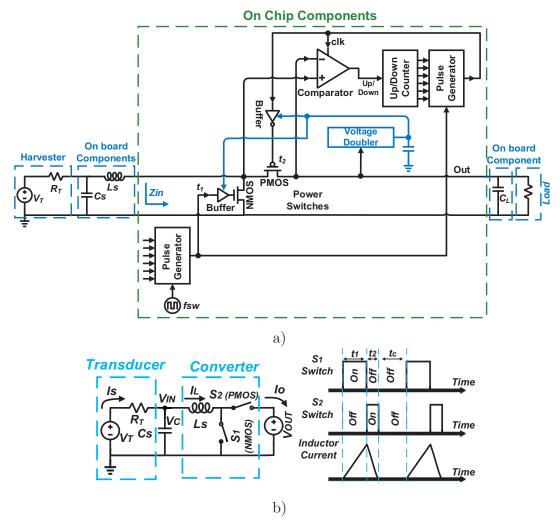

| Figure 4-1: Simplified architecture of a converter and its timing diagram66                                                                                                   |

| Figure 4-2: a) $t_2$ control loop block diagram, b) $f_{SW}$ control loop block diagram, and c) suggested feedback network $G(z)$ for the $f_{SW}$ control loop70             |

| Figure 4-3: Bode plot of the $f_{SW}$ loop for three values of the input capacitor                                                                                            |

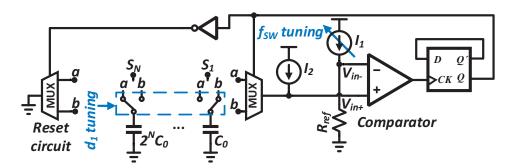

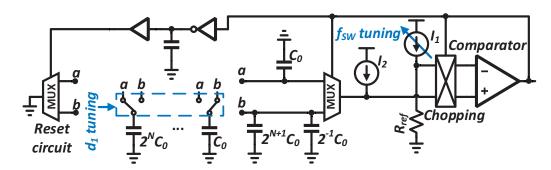

| Figure 4-4: Simplified system implementation of the control loops and the converter                                                                                           |

| Figure 4-5: Schematic of a) the latch comparator circuit and its b) variable delay generator                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4-6: a) Schematic of the hardware responsible for the multiplication and comparison needed to generate $e(n)$ and b) timing diagram of $e(n)$ updating in the $f_{SW}$ loop                               |

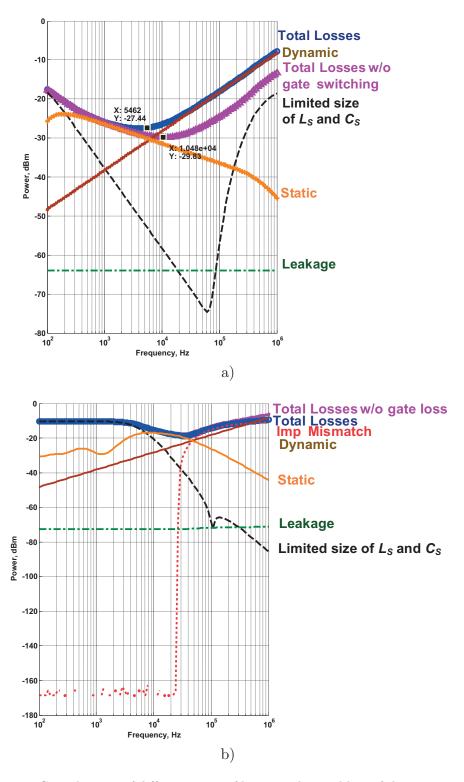

| Figure 4-7: Contributions of different types of losses in the total loss of the system with a) a high-impedance transducer and b) a low-impedance transducer                                                     |

| Figure 4-8: a) The output of <i>Counter_II</i> without fixing the initial value issue and b) hardware to fix the initial value issue of <i>Counter_II</i>                                                        |

| Figure 4-9: The output power of the implemented converter versus its duty cycles and frequencies for a) a low-impedance transducer and b) a high-impedance transducer                                            |

| Figure 4-10: a) Flow diagram to find and lock in the maximum output power and b) a simplified schematic to implement the flow diagram in a) $90$                                                                 |

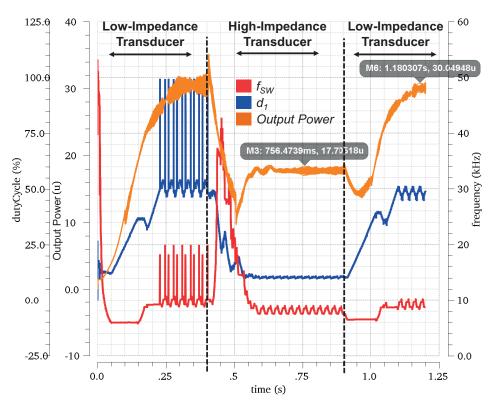

| Figure 4-11: Circuit-level simulation of the whole converter system which is showing transferred output power, $f_{SW}$ , and $d_I$ of the converter with different types of transducers.                        |

| Figure 4-12: A relaxation oscillator with a tunable frequency and duty cycle.                                                                                                                                    |

| 94                                                                                                                                                                                                               |

| Figure 4-13: The comparator's input chopping in a relaxation oscillator with a tunable frequency and duty cycle                                                                                                  |

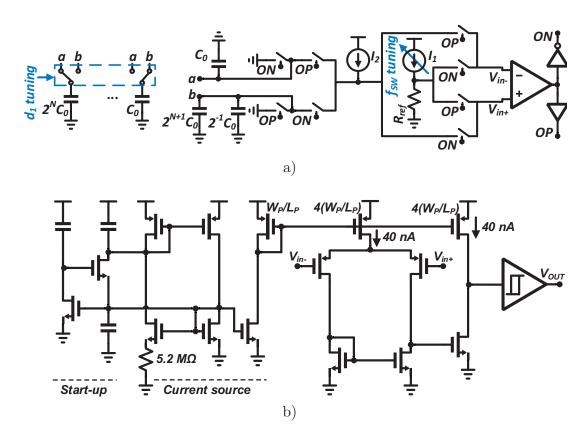

| Figure 4-14: a) Simplified schematic of the proposed tunable relaxation oscillator with a chopper at the comparator's input and b) schematic of the continuous time comparator with its low-power current source |

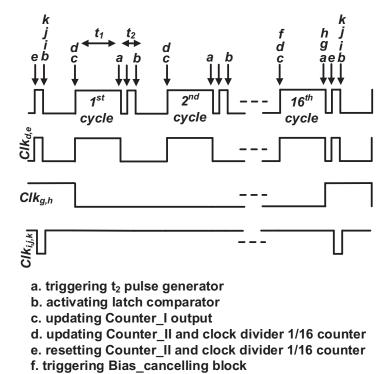

| Figure 4-15: The clock assignment for each block in the control system 98                                                                                                                                        |

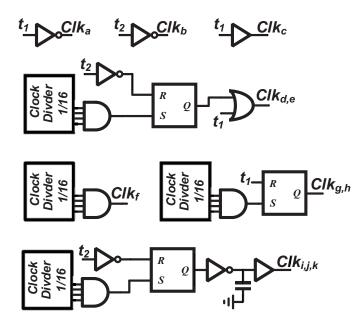

| Figure 4-16: The digital circuits implemented to create system clocks 99                                                                                                                                         |

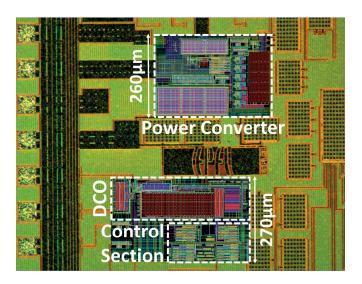

| Figure 4-17: The converter with a low-complexity control section microchip designed in UMC 0.18 $\mu m.$ $$100$                                                                                                  |

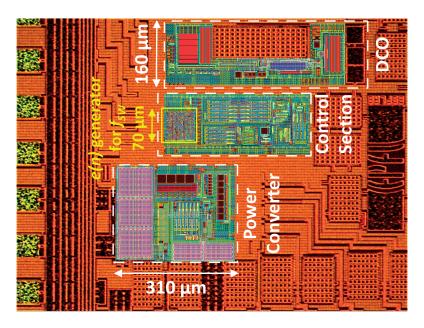

| Figure 4-18: The converter with a moderate-complexity control section microchip designed in UMC 0.18 $\mu m$                                                                                                     |

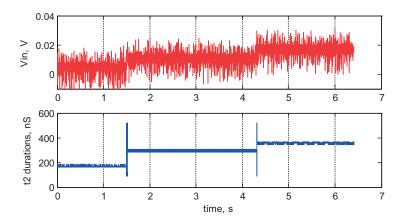

| Figure 4-19: System input voltage variations and consequent $t_2$ durations 102                                                                                                                                  |

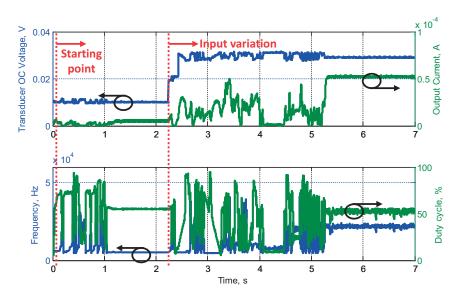

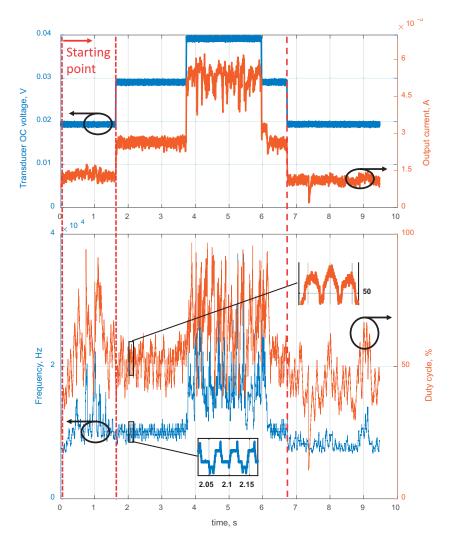

| Figure 4-20: $f_{SW}$ , $d_I$ , and output current variations of the converter in <i>Chip</i> $I$ with harvester output open-circuit voltage variation                                                           |

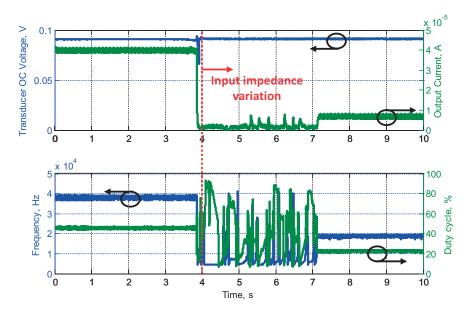

| Figure 4-21: $f_{SW}$ , $d_I$ , and output current variations of the converter in <i>Chip</i> $I$ with variations in the harvester's resistance                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4-22: <i>Chip II</i> test setup                                                                                                                                                                       |

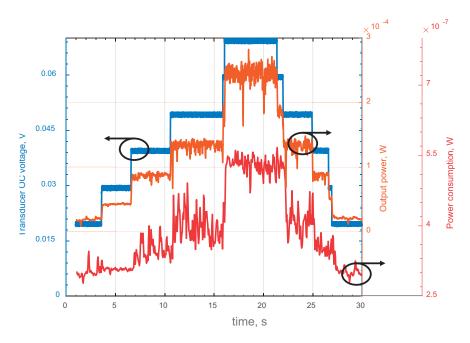

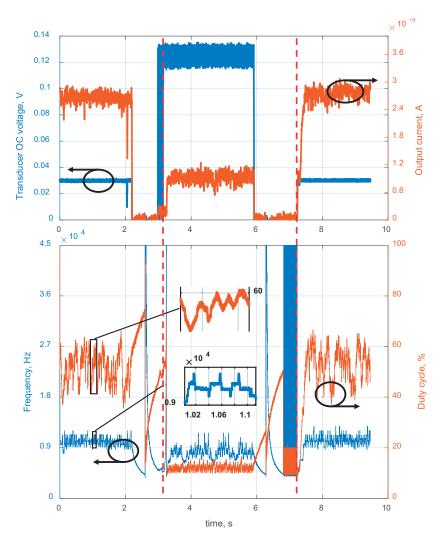

| Figure 4-23: $f_{SW}$ , $d_I$ , and output current variations of the converter in $Chip$ $II$ with harvester output open-circuit voltage variation                                                           |

| Figure 4-24: The entire power consumption of the system in <i>Chip II</i> with the variations of the harvester input available power                                                                         |

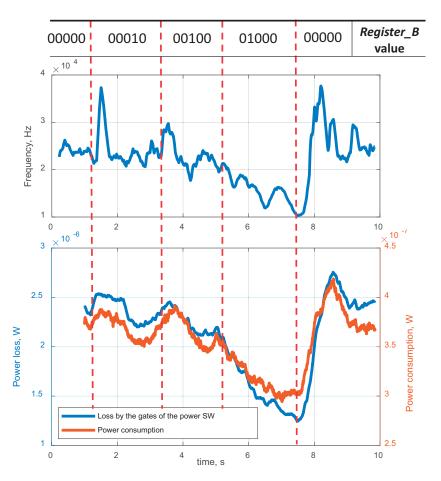

| Figure 4-25: The entire power consumption of the system, dynamic loss by the gates of the power switches, and f <sub>SW</sub> in Chip II with the variations of the dynamic loss bias value in Register_B110 |

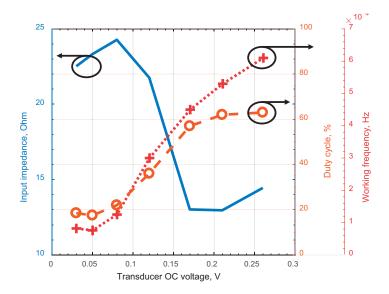

| Figure 4-26: Chip $II$ 's converter input impedance, $d_1$ , and $f_{SW}$ with the variations of the harvester output open-circuit voltage                                                                   |

| Figure 4-27: $\eta$ and output power variations of the converter in $\it Chip II$ with the harvester output open-circuit voltage.                                                                            |

| Figure 4-28: $f_{SW}$ , $d_I$ , and output current variations of the converter in $Chip$ $II$ with the harvester impedance variation                                                                         |

| Figure 4-29: $\eta$ of the converter in $\it Chip II$ for the high-, midrange-, and low-impedance TEG transducers                                                                                            |

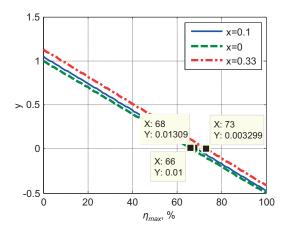

| Figure B-1: v from equation (B-11) versus maximum efficiency                                                                                                                                                 |

### List of tables

| Table 2-1: Power consumption and data generation in the different                                                             |    |

|-------------------------------------------------------------------------------------------------------------------------------|----|

| configurations of the EEG sensor                                                                                              | ٤4 |

| Table 2-2: EEG signal specification.                                                                                          | 16 |

| Table 2-3: Performance summary of this EEG amplifier                                                                          | 25 |

| Table 2-4: SAR ADC performance summary                                                                                        | 26 |

| Table 2-5: TEG body harvester and PV cell electrical characteristics at 24 °C ambient temperature.                            | 27 |

| Table 2-6: Power consumption of the different blocks in the EEG wearable sensor.                                              | 28 |

| Table 2-7: Converter efficiency required in different scenarios                                                               | 28 |

| Table 3-1: Design specifications of $t_1$ and $t_2$                                                                           | 50 |

| Table 3-2: Deadtime ranges for the no-loss condition                                                                          | 54 |

| Table 3-3: The counter output and optimum working frequency measurements with the variations in the transducer output voltage | 59 |

| Table 3-4: Summarized measurement results of this design and the prior art $\epsilon$                                         | 31 |

| Table 4-1: Chip II $\eta$ with different types of transducer                                                                  | 14 |

| Table 4-2: Summarized results of this work and the prior-arts 11                                                              | 14 |

### 1 Introduction

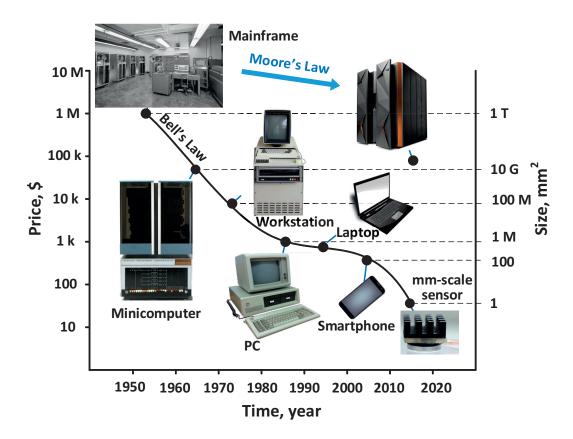

From the emergence of mainframes in the late 1950s, which belonged to the central computing processing class, to the present day's internet of things (IoT) or distributed computing class, semiconductor technology has advanced and evolved in two directions: device performance has been continuously enhanced inside a computing class while costs have been kept constant as, at the same time, devices have evolved from one class to another every decade with reduced costs and an unchanged performance. The former advancement was predicted by Moore's Law<sup>1</sup> [1, 2], the latter by Bell's Law [3]. Figure 1-1 illustrates the semiconductor industry's advancement according to Moore and Bell's Laws [4-6]. Central computing systems like mainframes have evolved in recent decades, but their market share has shrunk. The demand for small, high-volume, and cheap devices has gradually shifted the semiconductor industry from improving integration and complexity towards the development of lower-cost sensor nodes by keeping or even decreasing device performance. The exponential trends of Moore's Law are slowing down [7], and the semiconductor industry is pushing to develop small form-factor and lowcost devices more than ever before.

Wearable sensors, wireless sensors, and implantable devices aimed at medical monitoring [8-10] and environmental monitoring [11-13] of hazardous environments [14], automotive [15], and smart buildings [16, 17] are the main emerging applications of the new computing class. Wearable sensors can significantly benefit the long-term monitoring of biosignals. However, today's sensors invade the user's normal life as their platforms require removal, replacement, or recharging of the battery. This can be detrimental to medical applications, since clinicians need to monitor the psychological state of patients without any interruption. Moreover, the size of the sensors should be miniaturized to millimeter scales and their weight should

<sup>&</sup>lt;sup>1</sup> Gordon Moore predicated exponential improvements in complexity and cost per component in his first paper.

2 1.1 Thesis goal

Figure 1-1: Evolution of computing devices [4-6] from mainframes to millimeter-scale sensors.

be reduced to lower costs and make the device more user-friendly. However, the size of integrated electronic systems is often limited and set by their batteries.

To address these issues, the autonomy of the systems has to be increased while smaller form-factor batteries are used in the systems. This may not be possible unless ultra-low-power circuits are employed in the devices. Low-power circuit design has made great progress in recent years. The power consumption of electronic building blocks is steadily decreasing by reducing unnecessary performance for their intended applications. Recent innovative advances include a 0.24  $\mu$ W Bluetooth low-energy wake-up receiver [18], 600  $\mu$ W ultra-wideband transceiver [19], 0.7  $\mu$ W amplifier [20], 2.8  $\mu$ W chopper amplifier [21], 0.5  $\mu$ W analog to digital converter (ADC) [22], and 2.7  $\mu$ W microcontroller [23]. The development of these low-power integrated circuits benefits wearable sensors by making them more convenient for long-term monitoring.

When battery replacement is not an option or is too costly, it becomes necessary to look for alternative sources of energy. One solution is to power blocks by harvesting environmental energy or ambient energy through energy-scavenging technologies. Energy harvesting is an emerging research area in integrated systems.

1 Introduction 3

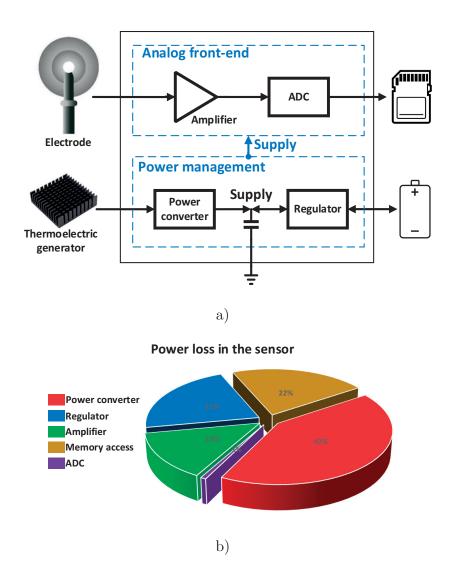

**Figure 1-2:** a) Block diagram of a medical wearable sensor node with a low-voltage TEG harvester, and b) the normalized power loss of each block in the node with the harvester.

Since energy harvesters can provide a lifetime of energy even under unyielding constraints, they are useful for applications such as medical devices that demand a relatively small amount of power for a long time. The 'zero power' medical devices approach can improve human parameters monitoring thanks to new circuits and architectures that will drastically lower power needs; their small needed energy can then be harvested directly from natural sources. This makes it possible to implement low-cost systems that minimize their impact on the everyday life of patients.

Body heat can be a source for energy harvesting when autonomous medical devices are placed directly on human skin. In this case, miniaturized thermoelectric generators (TEGs) are used as transducers. Small-scale photovoltaic cells (PV) can

4 1.1 Thesis goal

be used when a wearable device is exposed to sufficient environmental light intensity. The output voltages of these transducers change according to their environmental conditions and have been shown to be very small [24, 25]. The power converter is then responsible for transferring such infinite but unreliable low potential energy from the harvesters and providing it as a high-potential-energy and reliable power source for the application.

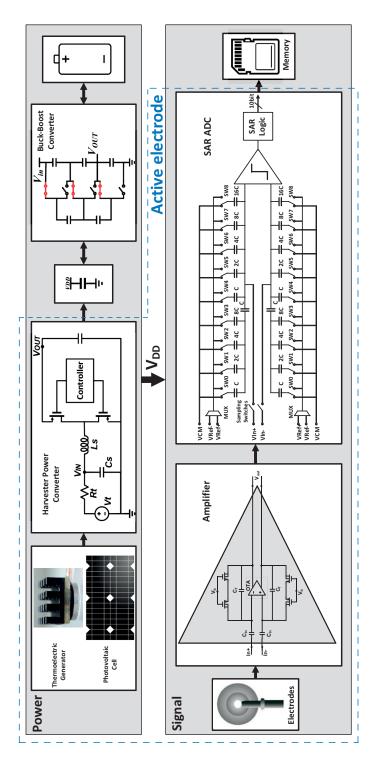

A system-level schematic of a medical sensor node supplied by a low-voltage energy harvester is shown in Figure 1-2 a). Two main sections can shape the sensor node: the analog front-end, which is responsible for conditioning and digitizing biosignals to prepare them to be stored in or transferred from the sensor node, and the power management unit, which provides a regulated supply for the sensor node. In the power management section, the power converter transfers energy from the transducer to a high-potential-energy storage element as the supply node. The switching regulator transfers extra charges from the supply to a small rechargeable battery to regulate the supply and to store additional energy. When there is not sufficient energy available from the harvest, or during a system cold-start when the supply storage is empty, the switching regulator has to charge the storage from the battery. The normalized estimated power consumption or power loss of each block is illustrated in the pie chart in Figure 1-2 b). The data were extracted from the recent literature and the practical results obtained in this work. One of the main bottlenecks in the sensor node is the power loss of the energy harvesting power converter. Therefore, the sources of this loss have to be identified, and a solution has to be proposed to mitigate this bottleneck and enhance the power converter efficiency.

### 1.1 Thesis goal

To find the sources of the power converter's losses and the factors limiting the power transfer, the constraints imposed by the sensor node have to be quantified. Therefore, the sensor node should be designed at the system level to observe its power-consumption requirements. The power converter loss must later be studied to understand the challenges in improving the converter's efficiency. Then, it is possible to propose methods to confront those challenges to optimize the converter. After that, since the harvester can be replaced due to sensor placement, the converter should be designed to with different types of harvesters without any manual adjustment. Therefore, the converter should tune and configure itself to keep its optimum point despite changes in the transducer specifications. To address these goals, this thesis is organized into chapters as follows.

1 Introduction 5

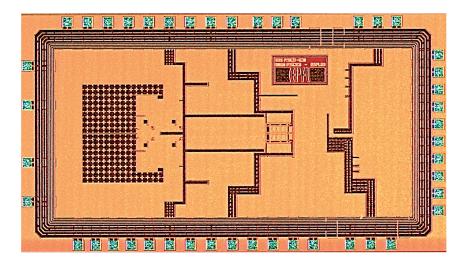

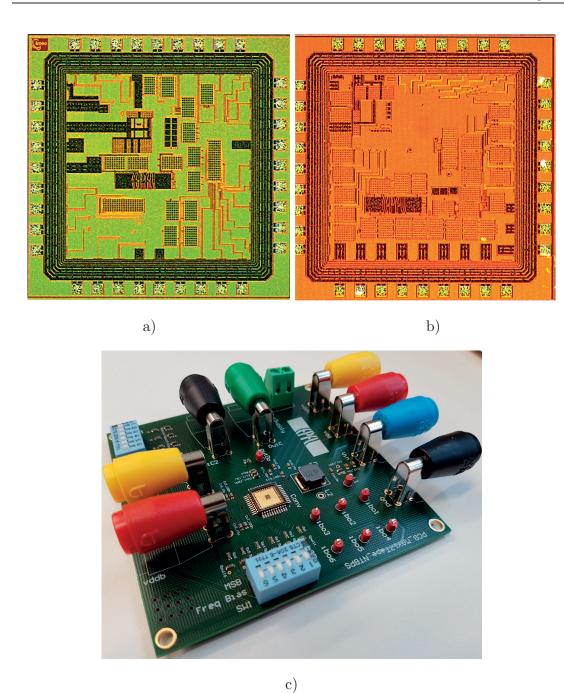

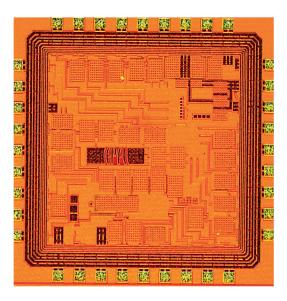

Figure 1-3: Microchip of the analog front-end.

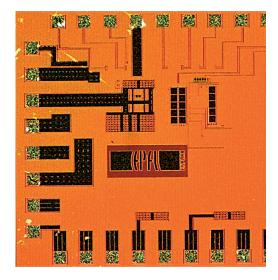

Figure 1-4: Microchip of the designed efficient converter.

#### Chapter two

In this chapter, the targeted application of the wearable sensor node is introduced. The building blocks of the node are presented. Its analog front-end is designed to study the feasibility of the sensor. A microchip of the fabricated front-end is shown in Figure 1-3. The actual requirements of the power converter are obtained with the measurements of the designed front-end. Then, the literature related to converters with similar requirements is reviewed to examine the state of the art in designing an efficient converter.

6 1.1 Thesis goal

**Figure 1-5:** Microchips of the self-reconfigurable converters with a) a low-complexity and b) a moderate-complexity control system, and c) the converters' test board.

#### Chapter three

The losses and limitations in the power transfer in a converter are examined in this chapter. A design approach based on this examination is suggested to implement an optimal integrated power converter. Inflexible converter parameters are 1 Introduction 7

Figure 1-6: Microchip of the stand-alone converters' main blocks.

designed and fixed, and the tuning ranges for the converter's timings are suggested. The fabricated microchip of this converter is shown in Figure 1-4. The converter is measured and the results illustrate that it can efficiently transfer power from different low-voltage transducers.

#### Chapter four

In this chapter, a closed-loop design is proposed to tune and configure the converter's timings to decrease losses and increase the power transfer. This allows the converter to maintain its efficiency, regardless changes in the transducer's characteristics. A time-domain state-space averaging model is used to design the closedloop system. Based on this approach, two architectures are suggested and implemented in 0.18 µm CMOS technology. The microchips of these self-reconfigurable converters are shown in Figure 1-5 a) and b). The converters are measured with the test board shown Figure 1-5 c). The results illustrate that the converters can harvest from different types of transducers. One of the converters is designed with a more elaborate control system without any significant overhead on the power consumption and the area. This converter can efficiently harvest energy from millimeter-scale transducers with available power of a few tens of microwatts to larger transducers with available power of several hundred microwatts. The entire system of the converters is implemented with low-power and sufficiently precise, custom building blocks. To characterize these blocks, some of them are implemented separately on a chip shown in Figure 1-6. This chip provides the possibly to control the converter by an external control system if necessary.

# Designing a zero-power wearable medical device

In a wide range of diseases, clinicians are looking for solutions to provide an early diagnosis. For early diagnosis of neurological disorders such as Alzheimer's and epilepsy, physicians monitor a subject's physiology and development of symptoms through body signals over long periods without interruption. These examinations such as electroencephalography (EEG) and electrocardiography (ECG), which are carried out with sophisticated devices, are currently costly. Furthermore, they disturb the ordinary life of patients because they have to be performed in a hospital environment.

Long-term monitoring of body signals is not convenient unless a lightweight fit and forgettable<sup>1</sup> wearable sensor is used. A lightweight, low-power EEG or ECG sensor can have an acceptable precision if its signal conditioning blocks are placed right next to the electrodes. If these blocks are supplied by a battery, the signal recording may be interrupted for charging or replacement of the battery, which is not acceptable for clinicians. To supply the device without interruption and a large battery, an autonomous active electrode is the proposed solution. It consists of an EEG or ECG electrode, a harvester, a power converter and an amplifier with the size of one electrode. Harvester types here will be TEGs and PV cells, based on sensor placement.

This chapter examines the realization of the autonomous wearable device and the requirements of its energy harvesting power converter. Section 1 introduces the device at the system level. The design and characterization of the electronic subsystems of the device are discussed in section 2. Finally, the requirements of the

<sup>&</sup>lt;sup>1</sup> The device has to be comfortable to the point that a user would forget after a while that he/she was wearing the device.

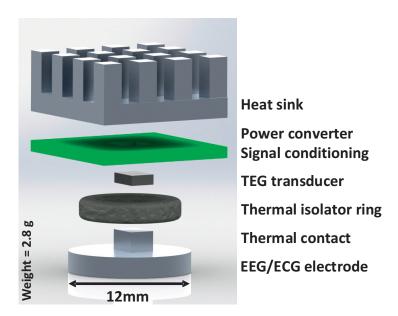

Figure 2-1: Exploded view of the zero-power active electrode [24].

energy harvesting power converter are investigated in detail in section 3. The power converter challenges, the state-of-the-art solutions, and the remaining open questions are introduced in this section as well.

# 2.1 A wearable device for early diagnosis of Alzheimer's and epilepsy

Long-term EEG or ECG signal monitoring devices must be convenient while maintaining precision. Accordingly, readout electrodes and electronic components must be small and lightweight. They must deliver a high signal-to-noise ratio (SNR) and a low distortion signal at their output. EEG signals are weak and are accompanied by substantial interferences. To achieve a high SNR and low distortion signal aimed at processing, it is mandatory to amplify the signal and reject interferences immediately after acquiring the signal from the electrodes. Introducing an analog front-end responsible for amplifying and digitalizing the signal right next to the electrodes can be solution. However, active components increase the energy budget, and they limit the system runtime for a medical device that employs a tiny light-weight battery as an energy storage element.

An autonomous active EEG electrode [24] based on a TEG harvester or PV cells as a solution are suggested in a multidisciplinary project called BodyPoweredSenSE [26]. Seven academic partners including two university hospitals have collaboration

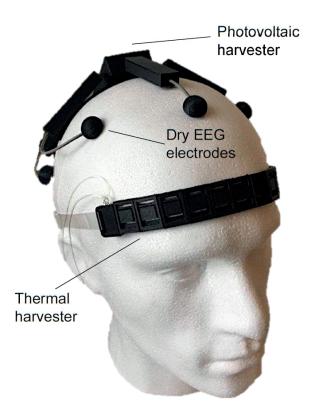

**Figure 2-2:** Wearable device scheme in BodyPoweredSenSE project, courtesy of Dennis Majoe from ETHZ, Laboratory for Software Technology.

in this project. Figure 2-1 illustrates the mm-scale of the BodyPoweredSenSE wearable sensor scheme. The sensor can be placed on the forehead or on the chest for EEG and ECG signal recording. A sufficient area of skin and an adequate source of body heat is expected to be available there. A metallic plate is placed at the bottom of the sensor to serve the function of the electrode and at the same time as a thermal contact to transfer body heat to a TEG. The body heat is transferred to the TEG transducer through a thermal isolator ring. Ultra-low-power electronics responsible for EEG signal conditioning and TEG power conversion are placed on the top of the TEG. A small heat sink is used at the top of the sensor to have a better heat flux from the body to the environment.

The size of the entire system should be the same as one electrode ( $12 \times 12 \text{ mm}^2$  here). A printed circuit board (PCB) of the electronic circuits should be less than  $12 \times 12 \text{ mm}^2$ . This implies a hard limit form-factor for the electronic circuits. Besides area constraints, the analog front-end has to be ultra-low power, and the power converter must have enough efficiency to provide adequate power for the EEG amplifier. Due to the form-factor and power efficiency constraints, the use of an ultra-low-power integrated circuit will be an inevitable choice for electronic parts.

If the sensor is placed on the scalp and in middle of the hair, a different type of a dry electrode should be employed. The electrodes are fabricated by silver chloride (AgCl) pins, which are matched relatively well with scalp skin. They can penetrate well between hairs to establish a better electrical contact with the skin. Since there is not enough thermal connection here, the mm-scale TEG cannot be an apt candidate for energy harvesting. The electrodes are connected to a central part as is shown in Figure 2-2. PV cells and a small battery are placed in the central part to supply the analog front-end. A TEG with the broader area located on the forehead provides energy in this case. This structure can be assembled on a sun hat to shape a wearable device.

The system-level schematic of the wearable sensors which was shown in Figure 1-2 is depicted in detail in Figure 2-3. The power converter processes the energy extracted from the harvesters. The energy has to be efficiently transferred to an energy storage element which can be capacitor bank or a supercapacitor. The potential level of this energy storage element should be almost constant to supply the analog front-end. Therefore, the excess charge on the energy storage element is transferred by a converter to a small battery that is located in the central section of the system. In the signal path, the EEG or ECG signals acquired by the electrodes are delivered to a low-power amplifier that is placed right next to the electrode. It amplifies the signal to a level suitable for ADC while reducing the level of common-mode interferences and noises. The digitized data is recorded on a secure digital (SD) memory card. The raw data is analyzed later by clinicians, or processed by a higher level algorithms to extract the features aimed at early diagnosis of Alzheimer's and epilepsy. As stated before, the mm-scale TEG transducer, power converter, electrode, and the analog front-end are part of the active electrode. The rechargeable battery and its converter, the memory, PV cell, and the broader area TEG belong to the wearable device.

Our medical partner has reported that low-frequency components (mainly alpha waves) of the EEG signal should be studied to monitor progression Alzheimer's [27] and epilepsy in their early stages. A bandwidth of less than 100 Hz is needed to record these low-frequency components. The performance of the EEG activity recording system depends on its "spatial" and "detection" resolutions. To achieve high spatial resolution, a large number of closely placed electrodes are required, and to reach a high detection resolution, a low-noise analog front-end is necessary. The EEG signal is typically extracted from 128 or 64 electrodes. However, in this project, a low-density EEG signal recording has been tried with just 32 electrodes to have a more convenient wearable device.

${\bf Figure~2\hbox{--}3\hbox{:}~ The~BodyPoweredSenSE~project~system~implementation}.$

| Table 2-1: Power consumption and data generation in the different configurations of | or the |

|-------------------------------------------------------------------------------------|--------|

| EEG sensor.                                                                         |        |

|                                                                                     |        |

| # of electrodes            | 32   | 64   | 128   |

|----------------------------|------|------|-------|

| # of microcontrollers      | 1    | 2    | 4     |

| Required BW, Hz            | 100  | 100  | 100   |

| ADC $\#$ of bits           | 12   | 12   | 12    |

| Data flow, kbps            | 38.4 | 76.8 | 153.6 |

| Raw data size in 24 h, GB  | 0.4  | 0.8  | 1.6   |

| SD card size, GB           | 16   | 16   | 16    |

| Power consumption, $\mu W$ | 400  | 800  | 1600  |

The generated electrode raw data is recorded on the SD card memory. A low-power microcontroller manages the memory. An MSP430 microcontroller [28] which has a ferroelectric random-access memory (FRAM) is used here to transfer the data to the SD card. The FRAM is a nonvolatile memory that is faster and consumes much lower write power than traditional flash memories. Therefore, a microcontroller with FRAM can save data internally with lower power, before formatting and transferring it to the SD card. The data from each of 32 electrodes is transferred to the SD card by one microcontroller. The microcontroller is interrupted with the rate of the data flow to wake up and save the output of the ADC into its FRAM. Once the FRAM is filled, the data is transferred in blocks to the SD card as the file allocation table (FAT) format dictates. A 16 GB SD card flash memory, which provides the best trade-off between power consumption and capacity, is used here. This setup has been measured over fifteen hours, and the results show that it consumes 400 µW on average. Table 2-1 summarizes the data generation flow and power consumption of the different EEG sensor configurations.

### 2.2 Analog front-end

Monitoring the EEG signals produced by the neural cells as a means of observing brain activity requires signal conditioning circuits. The general block diagram of such a system is illustrated in the lower part of Figure 2-3. The electrodes are used to pick up EEG signals, which are an average of action potentials of a large number of neurons located in the area below the electrode. The signal picked up by each electrode is then amplified by a dedicated EEG amplifier with suitable gain and

bandwidth. These amplified signals are then delivered to the sampling/processing domain. The sampling/processing circuitry, employing an ADC, samples the amplified signal with an adequate sampling rate dictated by the frequency content of the target EEG signal. The sampled data can then be either recorded in memory as in this project or transmitted using an active/passive wireless telemetry link [29] or a simple wired serial connection.

Since every electrode is associated with its dedicated EEG analog front-end, the total number of front-ends is equal to the number of electrodes employed. Considering the very limited available harvested power, it is crucial that the system have ultra-low-power consumption. In addition to the power consumption constraint, the front-end is required to have adequate gain and sensitivity to capture the weak and noisy EEG signals. The input-referred noise of the system should be kept below the minimum required input detectable signal. The EEG signal amplitude can be as low as 5 μV [30-32]. With dry electrodes, a value of even less than 5 μV is expected here. This minimum EEG detectable signal imposes very severe constraints on front-end noise and dynamic range, and consequently on its power consumption. Commercial products like a TI ADS1299 [33], or an AD AD82224 [34] amplifier with an AD AD7768 [35] ADC, which have an input-referred noise of less than the mentioned detectable signal, consume about 5 mW and 1 mW, respectively. State-of-the-art solutions consume in a range of 80 µW to 1 mW [36-38] which is more than the available power from mm-scale harvesters as well. Therefore, it is impossible to utilize commercial products or to redesign the prior-arts in this work.

To realize the wearable device, the front-end should be then implemented as a custom integrated circuit (IC) for this application. Thanks to the expertise of our medical partners, the analog front-end requirements can be more relaxed than a general EEG acquisition device. As mentioned in section 2.1, extracting of all the EEG rhythmic components is not necessary. Just the alpha component, which has a minimum amplitude about 20  $\mu V$  [32], is needed here. Considering a possible reduction in the signal level due to an unmatched connection between the dry electrodes and the skin, the front-end should have an input-referred noise of less than 15  $\mu V$ , which is much more relaxed in comparison to the general scenario. The EEG signal can reach an amplitude of  $\pm 500~\mu V$  [30] at its maximum point. The EEG processing algorithms can tolerate 1% harmonic distortion. The entire frequency content of an EEG signal ranges from 0.5 Hz to 150 Hz [31]. In this work, though, it is sufficient to detect only a part of this bandwidth up to 30 Hz.

Table 2-2: EEG signal specification.

|                                                      | Minimum | Maximum |

|------------------------------------------------------|---------|---------|

| EEG signal on scalp, μV                              | 5       | 500     |

| The desired EEG signal on scalp, $\mu V$             | 20      | 200     |

| EEG frequency content, Hz                            | 0.5     | 150     |

| Acceptable harmonic distortion, $\%$                 | -       | 1       |

| DC offset at the amplifier input, V                  | -       | 0.3     |

| Common-mode 50 Hz signal at the electrode, ${\bf V}$ | -       | 1.5     |

| Front-end input-referred noise, $\mu V$              | -       | 15      |

A DC offset of about  $\pm 300$  mV, which is related to the quality of the connection between the electrode and the skin, is produced at the input of the amplifier. Additionally, the power-line noise can create a significant common-mode signal with an amplitude of 1.5 V [39] around 50 Hz on electrodes. The common-mode noises impose a hard constraint on the system power consumption. However, if a bandwidth smaller than 50 Hz is selected, the front-end can be more relaxed. The front-end specifications are summarized in Table 2-2. The ECG sensor front-end in this application is even more relaxed than that of the EEG. The maximum ECG signal can reach 5 mV [39], and its minimum detectable signal level is much higher than EEG. Therefore, a reduced gain EEG front-end can be employed for the ECG conditioning as well.

In this section, based on the above application-specific requirements, a low-power custom IC front-end is designed to demonstrate that the autonomous mm-scale sensor is feasible. The section is organized as follows. First, a design methodology of the amplifier and its core operational transconductance amplifier (OTA) is discussed. After that, the ADC topology and its implementation are described. The measurement results of both circuits are presented in the final part of this section. Given that the design is not solely the author's [40]<sup>2</sup> and that it is not the main direction of this thesis, the design steps are not discussed in great detail.

<sup>&</sup>lt;sup>2</sup> The author contributed the architecture and system design and about 20% of the circuit design.

### 2.2.1 EEG amplifier

Since the EEG amplifier is the first stage in the signal's path, it is required to have an adequate gain and sensitivity to capture the weak and noisy target signal and to satisfy the specifications in Table 2-2. The noisy supply voltage provided by the harvester and the required linearity from Table 2-2 impose severe constraints on the tolerable common-mode rejection ratio (CMRR), power supply rejection ratio (PSSR), and total harmonic distortion (THD). The requirements prohibit the front-end from employing high-gain open-loop [41] architectures.

The amplifier must also be able to reject the DC offset voltage at the electrode-electrolyte interface. In [42], a low-frequency feedback was employed to reject the DC offset along with the low-frequency noise. This approach, however, requires an additional OTA for the integrator block, thus consuming more power. Moreover, the open-loop operation of the system as seen by the signal results in an amplifier gain that is sensitive to process and temperature variations. The PSRR and THD parameters are also degraded as a result of this open-loop operation. Another method, used in [43], is to attenuate the DC offset using a resistive voltage divider and a high-value (pseudo-)resistor (HVR). Nevertheless, the variation in the pseudo-resistor and the DC offset values results in a different offset from one electrode to another and a system that cannot be fully symmetric.

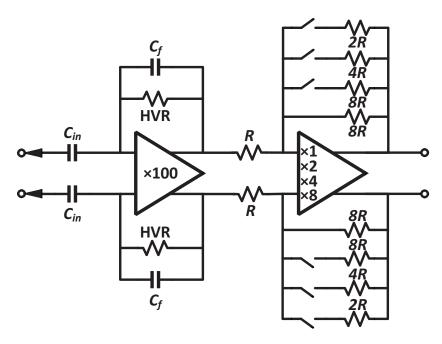

The most common approach to eliminate the offset of biosensor amplifiers is to employ an AC-coupled architecture [44-46]. Despite the required large-area-consuming capacitors, this method is superior regarding power consumption, noise, and robustness. Therefore, the AC-coupled capacitive-feedback architecture is adopted in this work. The topology of the EEG amplifier is shown in Figure 2-3. The gain of the closed-loop amplifier is approximately equal to the inverse of the gain of the feedback.

$$A_m = V_{out}/V_{in} \approx -C_{in}/C_f , \qquad (2-1)$$

where  $C_{in}$  and  $C_f$  are the input and feedback capacitors, respectively. The gain should be limited to the value that the output amplitude reaches in its full range for the maximum in-band single-ended signal. The amplitude full range is less than the amplifier's supply voltage by just a few transistors' overdrive voltages. Considering a supply voltage near to 1.2 V and the maximum in-band voltage from Table 2-2, the amplifier (closed-loop) gain should be around 55 dB.

Capacitor  $C_f$  with a parallel resistor,  $R_p$  creates the amplifier closed-loop highpass corner around 0.5 Hz. This high-pass filtering rejects strong low-frequency

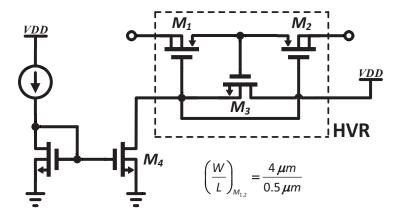

Figure 2-4: Schematic of the tunable high-value resistor.

noises around DC. To avoid a sizeable passive capacitor as  $C_6$ , and as a result from equation (2-1) a significant  $C_{in}$ , an HVR is employed as  $R_p$ . Two PMOS transistors biased in the subthreshold region can create the HVR as shown in Figure 2-4. The gate-source voltages of the transistors  $M_{1,2}$  are kept by  $M_3$  in which the current mirror  $M_4$  forces the current. The HVR value changes with its gate-source voltage; therefore, it can be adjusted by tuning the current mirror as [47] suggested.

Four HVRs are connected in series to create resistance as large as possible with a sufficient bandwidth for the application. The values of the HVRs are susceptible to their gate-source voltages. The HVRs' source voltages are changed when the amplifier output sweeps. The  $M_3$  non-idealities and mismatches with  $M_4$  do not allow the gate of  $M_3$  to perfectly follow its source. This results in nonlinearity in the amplifier, particularly at low frequencies. NMOS transistors have to be initiated on the substrate of CMOS technology. Therefore, the cascode transistor  $M_3$  has a different substrate-source voltage than  $M_4$  and their threshold voltages cannot be matched. The CMOS technology employed here provides the option to place NMOS transistors in an isolated P-well. Then,  $M_3$  is placed in the P-well, and its bulk connection is tied to its source similar to  $M_4$  to have a better matching and higher linearity.

The amplifier should have flat gain in the desired EEG bandwidth, and it has rigorous linearity requirements as mentioned. The high-density MOS capacitor cannot be used as  $C_{in}$  or  $C_f$ . The lower density metal-insulator-metal (MIM) capacitors are used here. These capacitors should be big enough to satisfy the gain and the high-pass corner requirements while having a reasonable area. With the designed HVR, a  $C_f$  equal to 1 pF is selected. Then with the schematic shown in Figure 2-4, the high-pass corner in the frequency response of the amplifier can be tuned in the

Figure 2-5: Overall architecture of the EEG amplifier.

range of 0.1 Hz to 2 Hz. This is sufficient to create a high-pass corner at 0.5 Hz with given set of the technology process and temperature variations. The maximum  $C_{in}$  that can be fit in a given area of about 0.2 mm<sup>2</sup> is 200 pF (differentially), which results in a 40 dB gain. To achieve the recommended gain in section 2.2, the amplifier is cascaded in two stages. The same core as in the first stage is employed in the second stage for simplicity. The second stage is designed to have a variable gain as shown Figure 2-5. The variable gain enables the front-end to be employed in the ECG sensor as well.

The amplifier has to drive an off-chip low-pass filter to reject unwanted signal and noise, especially power-line noise at 50 Hz. The core OTA is designed with a two-stage architecture [48] in which the second stage can provide current for the external load. Therefore, it is possible to use the resistor feedback instead of the capacitive network in the cascade stage to provide a small signal gain and input DC biasing at the same time.

### 2.2.1.1 OTA design

The common-mode signal levels from Table 2-2 leave strict requirements for the CMRR of the amplifier. The common-mode signal should be attenuated at the output of the amplifier below the level of the amplified minimum detectable signal  $V_{n,amp}$ . The DC common mode is expected to be attenuated enough with the selected AC-coupled architecture. As for the power-line noise, a CMRR on the order

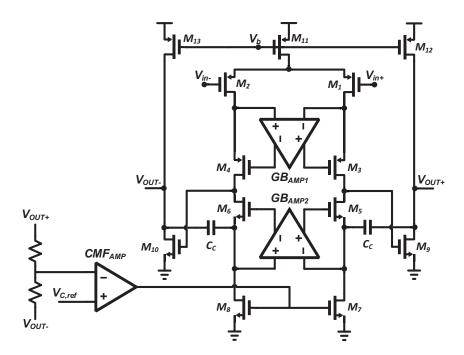

Figure 2-6: The two-stage gain-boosting amplifier with its common-mode feedback.

of 80 dB is recommended for a more general EEG signal conditioning circuit with dry electrodes [36, 49]. Since the 50 Hz noise is partially filtered after the first stage and the minimum detectable signal has a higher level than the general case, a CMRR of more than 65 dB is expected to be required for the amplifier with 40 dB gain. The core of the amplifier is designed to be entirely symmetric for the severe CMRR requirement. Thus, a common-mode feedback (CMF) is adopted, as depicted in the schematic of Figure 2-6.

To maximize the OTA gain, the transistors  $M_{1,2}$ ,  $M_{3,4}$ ,  $M_{5,6}$ ,  $M_{9,10}$  are placed in the weak inversion operating region where their transconductance to drain current  $g_{I\!M}/I_D$  is maximized. The choice of the aspect ratio of transistors is made with regard to the gain and noise characteristics of the OTA. The second stage of the OTA has a limited gain. Therefore, the gain of the first stage is enhanced by  $GB_{AMP1}$  and  $GB_{AMP2}$  gain-boosting OTAs. A single-stage common source is employed as the gain-boosting amplifier. The limited gain of  $GB_{AMP1,2}$  cannot change the dominated poles and zeros of the OTA, and it does not deteriorate the OTA phase margin.

$C_C$  is a compensation capacitor to stabilize the OTA. However, it creates an unwanted right-hand-side zero in the frequency response. The common gate  $M_5$  moves the zero to the left side of the response. The zero shapes the noise response of the  $M_9$  as well. This noise contributes to the output with a differentiator response.

Therefore, considering the limited bandwidth of the amplifier, the main noise contributors are the transistors at the first stage.

The noise of the tail current source  $M_{II}$  does not appear at the OTA output due to the symmetry in the circuit topology. The equivalent noise voltage source at the gate of the cascode transistors  $M_{3,4}$ ,  $M_{5,6}$  encounters a large degeneration impedance which can attenuate their input-referred noise voltage. The input transistors  $M_{I,2}$  are the major contributor to the noise of the OTA. The input-referred noise contribution of these transistors is proportional to the inverse of their  $g_m$ . As stated before,  $M_{I,2}$  are placed in the weak inversion to maximize  $gm/I_D$ . This reduces the  $M_{I,2}$  noise contribution as well. Furthermore, to minimize their low-frequency flicker noise, PMOS transistors are employed as the input stage, and a large width and length are chosen to increase  $W \times L$ .

$M_{7,8}s'$  noise is not attenuated due to degeneration impedance or symmetry, and it contributes to the output of the OTA by the  $g_{m7,8}/g_{m1,2}$  ratio. Therefore, their noise contribution is desired to be suppressed by minimizing their  $g_m$ . It is better to place these transistors in the strong inversion operating region with a small width-to-length aspect ratio (W/L). Moreover, to minimize their flicker noise, a large  $W \times L$  must be selected. Reducing these transistors'  $g_m$  does not affect the gain of the OTA. Besides, increasing  $L_{7,8}$  maximizes the mirror matching and the output resistance of the first stage and boosts the OTA gain. However,  $M_{7,8}$  with the  $CMF_{AMP}$  create a two-stage amplifier. A low  $g_{m7,8}$  and a large  $W_{7,8}$  or  $L_{7,8}$  push the second pole of this amplifier close to its first pole and can make the CMF unstable. To sum up, a small W/L ratio with large values for  $W_{7,8}$  and  $L_{7,8}$  is desired up to the point that the CMF stays stable.

## 2.2.2 ADC design

The ADC described in this section [40] is based on the successive approximation (SAR) architecture, as it is the most suitable for the mentioned requirement of the analog front-end. The resolution of the ADC is set by the system minimum detectable signal  $V_{n,system}$ , the amplifier input-referred noise  $V_{n,amp}$ , and amplifier gain  $A_m$ . In the worst-case scenario, when the available power noise from the output of the amplifier is transferred to the ADC input, the minimum detectable ADC signal or its the least significant bit LSB can be written as:

$$LSB = \sqrt{\left(V_{n,system}^{2} - V_{n,amp}^{2}\right) \times A_{m}^{2}} . \tag{2-2}$$

Then, the required ADC number of bits can be written as:

$$N = \log_2 \frac{\text{Full scale}}{LSB} \,. \tag{2-3}$$

From equation (2-2) and equation (2-3), it can be approximated that the full dynamic range of an EEG signal can be covered with an 8-bit ADC. EEG acquisition systems employ ADCs with a vast range of resolutions, between 8 bits and 24 bits [33, 50, 51]. The reason for this large variety is related to the power budget of the system (portable or stationary) and the coupling strategy between the ADCs and the EEG signal amplifiers. Here to achieve an ultra-low-power system and still leave some margin for low-frequency interferences, an ADC with 10 bits of resolution has been implemented. The ADC was designed to operate at 400 S/s, a sufficiently high frequency for acquiring the full spectrum of EEG signals.

The block diagram of the SAR differential ADC described in this section is shown in Figure 2-3. This circuit is power-efficient and does not require any complicated high-performance analog blocks. Therefore, it can operate with a low supply voltage. The ADC operates as follows. In the first phase, the sampling switches are closed, connecting one side of the capacitors to the input voltages  $V_{In+}$  and  $V_{In-}$ . The other side of the capacitors is connected to the common-mode voltage  $V_{CM}$ . Then, the sampling switches open, and the comparator is triggered a small instant afterward. The result of the comparison is used to select which reference voltage connects to the capacitor bank by using two multiplexers. The capacitors are switched sequentially between  $V_{CM}$  and  $V_{Ref+}$  or  $V_{Ref-}$ . After each comparison, the most significant indeterminate output bit is resolved, and the voltage difference at the inputs of the comparator is reduced proportionally.

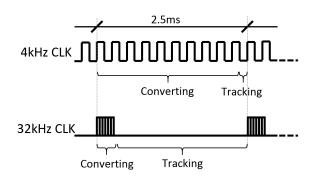

SAR ADCs require one clock cycle per bit resolved. However, if the minimum clock frequency of 4 kHz for a 10-bit 400 S/s ADC is used, the time available for tracking the input signal is only half a clock period. This creates a difficulty for the sampling switches, which will be in an open state during most of the time, and closed during only a small instant. As the time available for tracking the input is very small, the on-resistance of the switches should be very low. Conversely, the charge leakage is proportional to the duration that the switches are open. Therefore, the off-resistance of the switches should be very high to limit the contamination of the sample when it is being processed.

The double-sampling scheme used by [52] mitigates this issue but requires additional hardware and introduces a tone at half of the sampling frequency. It can result in charge injection mismatches for the odd and even samples. The technique used here to address the issue increases the ratio of the tracking time to the hold time by employing a higher clock frequency. Here, a clock frequency 8 times higher

Figure 2-7: The clocking scheme of the designed ADC.

is used, and the ADC conversion proceeds during just 1/8th of the available time. The ADC is disabled during the rest of the period. This principle, which requires a 32 kHz clock signal, is illustrated in Figure 2-7. When the ADC was using the minimum clock frequency, the switches were closed for 5% and opened for 95% of the time, whereas with the 8-times-faster clock, they are closed for 88% and opened for only 12% of the time.

This operating method is also advantageous regarding the static power consumption of the ADC. A buffer with a static consumption interfaces the comparator's input with the capacitor's bank. This block is now disabled during 7/8ths of the clock period, which enables considerable power saving. On the other hand, both the dynamic power consumption and the area stay almost unchanged, since the effective switching clock frequency of the ADC remains 4 kHz and the added circuits have a negligible area and power consumption. The main disadvantage of this technique is the requirement of a higher frequency clock; however, this can be a minor issue given the low-speed operation requirement for this application.

#### 2.2.2.1 Sampling Switches

The switches used for sampling the analog input signals are the transmission gate type. The distortion introduced by the sampling switches should be small in comparison to the resolution of the ADC. This distortion is caused mainly by the nonlinear on-resistance of the switches. The harmonic distortion introduced by the switches has been simulated for a 200 Hz full-swing sine wave input signal, for a given set of process and temperature corners. The result indicates that the highest harmonics are at about -79 dB and -83 dB for the slow-slow-cold and the fast-slow-cold corners. These levels of harmonic distortion are well below the requirements for an ADC with a resolution of 10 bits, and it is not necessary to introduce boot-strapping or an OTA-based method for the sampling switches.

## 2.2.2.2 Comparator and buffer

The comparator used in this design is a dynamic latch, as presented in [53]. The simulation results have shown that the comparator has 50  $\mu$ V of input-referred noise, which is much smaller than the ADC's LSB. The comparator's offset distribution has been extracted from Monte Carlo simulations. It has a standard deviation of 6.4 mV, which is tolerable for this ADC. The comparator's input transistors have been designed to be relatively large to reduce its offset and noise. However, the large transistors can intensify the kickback noise. This noise affects the voltage level that is going to be processed and can degrade the linearity of the ADC significantly. To attenuate the kickback noise to a tolerable value, a buffer circuit has interfaced the capacitor bank with the comparator. This circuit increases the offset to 9.4 mV (standard deviation) and the noise to 250  $\mu$ V. The new values of both the offset and the noise are still acceptable for the application. The offset corresponds to 0.6% of the comparator's input range, and the noise accounts for only 16% of the LSB.

### 2.2.2.3 Capacitor bank

For a 10-bit SAR ADC, the ratio of the smallest capacitor to the biggest one in the bank goes up to 256. Assuming that the smallest capacitor consists of multiples of a unit capacitor, which is essential for matching, a bank of 1022 unit capacitors would be required. It would be impractical to route such a large number of components, and the parasitic capacitances from the routing would very likely degrade the overall matching. For these reasons, the well-known split capacitor technique has been applied here. In this method, a series capacitor is used to attenuate the values of the capacitors placed after it, as shown in the schematic of the ADC in Figure 2-3. This allowed reducing the total number of capacitors to 94. The unit capacitor used is a 25  $\mu$ m<sup>2</sup> MIM device with 26.5 fF. The total sampling capacitance is 846 fF for each input. The resulting sampling noise is about 100  $\mu$ V, which is an acceptable value that corresponds to 6.4% of the LSB amplitude.

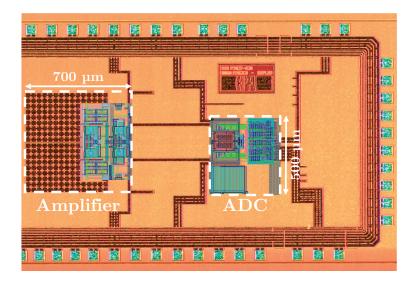

## 2.2.3 Characterization of the analog front-end

Both the EEG amplifier and the SAR ADC are designed in UMC 0.18  $\mu$ m CMOS technology. A chip microphotograph of these circuits is shown in Figure 2-8. The core area of the amplifier and ADC are 0.53 mm2 and 0.13 mm2, respectively. The amplifier consumes 9  $\mu$ W from a 1.2 V voltage supply. An Agilent 34411A Digital multimeter device is used to measure the power consumption of the circuit. The gain can be set to 40 dB, 46 dB, or 58 dB. The measurements show that the amplifier high pass corner frequency can be set 0.5 Hz. The input-referred noise voltage

Figure 2-8: The analog front-end microchip designed in 0.18  $\mu m$  CMOS.

Table 2-3: Performance summary of this EEG amplifier.

|                                         | Requirements | This work        |