# Efficient Adaptive Hard Real-time Multi-processor Systems

THÈSE Nº 8146 (2017)

PRÉSENTÉE LE 10 NOVEMBRE 2017 À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS LABORATOIRE DES SYSTÈMES INTÉGRÉS (IC/STI) PROGRAMME DOCTORAL EN INFORMATIQUE ET COMMUNICATIONS

## ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

## Stefanos SKALISTIS

acceptée sur proposition du jury:

Prof. J.-Y. Le Boudec, président du jury Prof. G. De Micheli, Prof. J. Sifakis, directeurs de thèse Prof. S. Baruah, rapporteur Prof. I. Puaut, rapporteuse Prof. D. Atienza Alonso, rapporteur

Οἱ καιροὶ οὐ μενετοί — Θουχυδίδης

Times do not wait — Thucydides

Στους γονείς μου, Στους διδάσχοντες μου, Σε όσους πίστεψαν σε εμένα.

To my parents, To those who taught me, To those who believed in me.

# Acknowledgements

I had the honour and privilege to be advised by Prof. Joseph Sifakis and Prof. Giovanni De Micheli. As an expert of hard real-time systems once told me: "No graduate student simply chooses the problem of hard real-time systems; it is always assigned to them by their advisor." — Prof. Baruah.

I would like to extend my gratitude towards my main advisor, Prof. Sifakis, for providing me with the opportunity of exploring the research problems present in the domain of hard real-time systems. The true value of such systems, as well as the difficulty of the underlying challenges, only becomes apparent after years of efforts, for which I now am thankful. Additionally, his constant persistence towards theoretical and scientific rigour has equipped me with a valuable research skill-set that will accompany me for the rest of my life. I also vastly appreciate Prof. De Micheli's provisions that allowed this work to be completed, as well as his patience and understanding during personally challenging periods. I feel deeply indebted to both of them for this opportunity in my professional life. Their support and guidance is unparalleled and I honestly aspire that some day my contributions will be able to compensate their efforts.

I am grateful to Prof. Sanjoy Baruah, Prof. Isabelle Puaut, Prof. David Atienza Alonso and Prof. Jean-Yves Le Boudec for honouring me in serving as the thesis jury. I thank them for taking the time to read my thesis and for their invaluable comments on my work and its perspectives. I would like to additionally thank Prof. Baruah for being my mentor during a research visit at University of North Carolina at Chapel Hill, which enabled me to significantly increase my knowledge on mixed-criticality systems and scheduling under uncertainty. I thank him for the insightful scientific discussions, which I greatly enjoyed. I could not possibly omit the unseen heroes behind this dissertation; Dr. Alena Simalatsar and Dr. Federico Angiolini. Their day-to-day efforts in instilling a scientific spirit will never be forgotten. Special thanks go to Dr. Angiolini, Anastasia Mavridou and Stefanos Antaris for proofreading my thesis. Their assistance in improving this manuscript on all levels was precious.

I want to thank all members of the Rigorous System Design (RiSD) lab and Integrated Systems (LSI) lab for creating a pleasant and motivating working environment. I thank Mrs. Arianne Staudenmann and Mrs. Christina Govoni for their constant availability and assistance on administrative tasks, while maintaining a positive spirit at all times. I would also like to express my gratitude to my dear friends for enriching my life with happiness, joy and laughter. Thank you Abbas, Alex, Androklis, Apostolos, Ashkan, Despina, Eleni, Eleni, Evangelos, Evgenia, Grigorios, Ignatio, Ioannis, Ioulia, Katerina, Loukia, Manos, Matt, Myrsini, Pavlos, Panagiotis, Stefanos and Theodoros. Last, but most importantly, I thank my parents, Stamatia and Georgios, for their trust and unconditional love throughout the years. Ultimately, there are no words to express the magnitude of my gratitude towards them. Finally, I am deeply grateful to Georgios Bootsalis; the first man who expressed his belief in me (beyond my family). Without it, I would not have never started this journey.

Lausanne, 10 November 2017

S. S.

# Abstract

Modern computing systems are based on *multi-processor* systems, i.e. multiple cores on the same chip. *Hard real-time* systems are required to perform particular tasks within certain amount of time; failure to do so characterises an unaccepted behavior. Hard real-time systems are found in safety-critical applications, e.g. airbag control software, flight control software, etc. In safety-critical applications, failure to meet the real-time constraints can have catastrophic effects.

The safe and, at the same time, efficient deployment of applications on multi-processors with hard real-time constraints is a challenging task. Scheduling methods and Models of Computation, that provide safe deployments, require a realistic estimation of the Worst-Case Execution Time (WCET) of tasks. The simultaneous access of shared resources by parallel tasks causes *interference delays*, due to hardware arbitration, which affecs WCET. Interference delays can be accounted for, with the pessimistic assumption that all possible interference will occur. Resulting schedules would be exceedingly conservative, thus the benefits of a multi-processor would be significantly negated. Producing less pessimistic schedules is challenging due to the inter-dependency between WCET estimation and deployment optimisation. Accurate estimation of interference delays - and thus estimation of task WCET- depends on the way an application is deployed; deployment is an optimisation problem that depends on the estimation of task WCET. Another efficiency gap, which is of consequence in several systems (e.g. airbag control), stems from the fact that rarely tasks execute with their WCET. Safe runtime adaptation based on the Actual Execution Times, can yield additional improvements in terms of latency (more responsive systems).

To achieve *efficiency* and retain *adaptability*, we propose that interference analysis should be coupled with the deployment process. The proposed interference analysis method estimates the possible amount of interference, based on an architecture and an application model. As more information is provided, such as *scheduling*, *memory mapping*, etc, the per-task interference estimation becomes more accurate. Thus, the method computes *interference-sensitive* WCET estimations (*is*WCET).

Based on the *is*WCET method, we propose a method to break the inter-dependency between WCET estimation and deployment optimisation. Initially, the *is*WCETs are over-approximated, by assuming worst-case interference, and a safe deployment is derived. Subsequently, the proposed method computes accurate *is*WCETs by *spatio-temporal* exclusion, i.e. excluding interferences from non-overlapping tasks that share resources

#### Acknowledgements

(space). Based on accurate isWCETs, the deployment solution is improved to provide better latency guarantees.

We also propose a distributed runtime adaptation technique, that aims to improve run-time latency. Using *is*WCET estimations restricts the possible adaptations, as an adaptation might increase the interference and violate the safety guarantees. The proposed technique introduces statically scheduling dependencies between tasks that prevent additional interference. At runtime, a self-timed scheduling policy that respects these dependencies, is applied, proven to be safe, and with minimal overhead.

Experimental evaluation on Kalray MPPA-256 shows that our methods improve isWCET up to 36%, guaranteed latency up to 46%, runtime performance up to 42%, with a consolidated performance gain of 50%.

${\bf Key}$  words: hard real-time systems, interference-sensitive WCET, runtime adaptation, Kalray MPPA-256

# Résumé

Les systèmes informatiques modernes sont basés sur des systèmes multiprocesseurs, c'est-à-dire avec plusieurs cœurs sur la même puce. Des systèmes temps-réel durs sont nécessaires pour effectuer des tâches particulières en un certain laps de temps; un échec caractérise un comportement non accepté. Des systèmes temps-réel durs se retrouvent dans des applications critiques pour la sécurité, par exemple dans les logiciels de contrôle des airbags, les logiciels de contrôle de vol, etc.. Pour des applications critiques pour la sécurité, le non-respect des contraintes de temps réel peut avoir des effets catastrophiques. Le déploiement  $s\hat{u}r$  et, en même temps, efficace des applications sur un multiprocesseur, sous des contraintes de temps réel dur, pose un problème difficile. Les méthodes d'ordonnancement et les modèles de calcul visées à des déploiements sûrs nécessitent une estimation réaliste du temps d'exécution le plus pessimiste (Worst Case Execution Time - WCET) des tâches. L'accès simultané par des tâches parallèles aux ressources partagées entraîne des retards d'interférence en raison de l'arbitrage hardware. Les retards d'interférence peuvent bien être pris en compte, en faisant l'hypothèse pessimiste selon laquelle toute interférence possible se produirait. Les ordonnancements résultants seraient extrêmement conservateurs, de sorte que les avantages du multiprocesseur seraient significativement réduits. Cependant, produire des ordonnancements moins pessimistes est difficile en raison de l'interdépendance entre l'estimation du WCET et l'optimisation du déploiement. L'estimation précise des retards d'interférence - et donc l'estimation du WCET des tâches - dépend de la façon dont une application est déployée; le déploiement est un problème d'optimisation qui dépend de l'estimation du WCET des tâches. Une autre inefficacité, qui peut être lourde dans plusieurs systèmes (par exemple, le contrôle des airbags), découle du fait que rarement les tâches s'exécutent avec leur WCET. Une adaptation de l'exécution basée sur les temps d'exécution réels, pourvu qu'elle soit sûre, peut apporter des améliorations supplémentaires en termes de temps de réponse (systèmes plus réactifs).

Pour atteindre l'*efficacité* et conserver l'*adaptabilité*, nous proposons que l'analyse des interférences soit associée au processus de déploiement. La méthode d'analyse d'interférence proposée identifie les interférences possibles, en fonction d'une architecture et d'un modèle d'application. À mesure que d'autres informations sont fournies, telles que l'ordonnancement, la répartition de la mémoire, etc., l'estimation de l'interférence pour chaque tâche devient plus précise. Ainsi, la méthode calcule un temps d'exécution tenant les interférences en compte (*interference-sensitive* WCET - *is*WCET).

#### Acknowledgements

Sur la base de l'*is*WCET, nous proposons une méthode pour découpler l'interdépendance entre l'estimation du WCET et l'optimisation du déploiement. En une première phase, les *is*WCET sont surestimés, en supposant les interférences les plus défavorables, et un déploiement sûr est dérivé. Par la suite, la méthode proposée calcule des *is*WCETs plus précis par exclusion spatio-temporelle, c'est-à-dire en excluant les interférences des tâches qui partagent des ressources (espace) mais ne se chevauchent pas dans le temps. Basé sur ces *is*WCETs précis, la solution de déploiement est améliorée pour optimiser les temps de réponse.

Nous proposons également une technique d'adaptation répartie, qui vise à améliorer les temps de réponse en temps réel. L'utilisation des estimations d'*is*WCET restreint les adaptations possibles, car une adaptation pourrait augmenter les interférences et violer les garanties de sûreté. La technique proposée introduit statiquement des dépendances d'ordonnancement entre les tâches, ce qui empêche l'apparition d'interférences supplémentaires. Au moment de l'exécution, une politique d'ordonnancement auto-cadencée qui respecte ces dépendances est appliquée, et prouvée comme étant sûre et peu lourde. L'évaluation expérimentale sur une plate-forme Kalray MPPA-256 montre que nos méthodes améliorent les isWCETs jusqu'à 36%, les temps de réponse garantis jusqu'à 46%, et les performances jusqu'à 42%, avec un gain de performance consolidé de 50%.

**Mots clefs** : systèmes en temps réel durs, WCET sensible aux interférences, adaptation d'exécution, Kalray MPPA-256, NoC

# Contents

| Ac            | cknov           | vledge  | ments                                          | i   |

|---------------|-----------------|---------|------------------------------------------------|-----|

| Al            | bstra           | ct (En  | glish/Français)                                | iii |

| $\mathbf{Li}$ | List of figures |         |                                                |     |

| $\mathbf{Li}$ | st of           | tables  |                                                | xi  |

| 1             | Intr            | oducti  | on                                             | 1   |

|               | 1.1             | The ne  | eed of Multi-processors                        | 1   |

|               | 1.2             | Challe  | nges in Hard Real-time Multi-processor Systems | 2   |

|               | 1.3             | Thesis  | Statement and Contributions                    | 7   |

|               | 1.4             | Dissert | cation Outline                                 | 8   |

| <b>2</b>      | Pre             | liminar | ries                                           | 11  |

|               | 2.1             | Real-ti | me Deployment Problem Formulation              | 14  |

|               | 2.2             | Proces  | sor Architecture Models                        | 15  |

|               |                 | 2.2.1   | Homogeneous Architecture Types                 | 16  |

|               |                 | 2.2.2   | Generic Architecture Model                     | 18  |

|               |                 | 2.2.3   | Kalray MPPA-256                                | 19  |

|               | 2.3             | Applic  | ation and System model                         | 20  |

|               |                 | 2.3.1   | Application Model                              | 23  |

|               |                 | 2.3.2   | System Model                                   | 25  |

|               |                 | 2.3.3   | Deployment                                     | 26  |

| 3             | Inte            | rferen  | ce-sensitive WCET                              | 29  |

|               | 3.1             | Interfe | rence Model                                    | 30  |

|               |                 | 3.1.1   | Hardware Arbitration Policies                  | 32  |

|               | 3.2             | Interfe | rence Analysis                                 | 34  |

|               |                 | 3.2.1   | Intra-cluster Interference                     | 37  |

|               |                 | 3.2.2   | Inter-cluster Interference                     | 38  |

|               |                 | 3.2.3   | NoC Interference                               | 39  |

|               |                 | 3.2.4   | Safety                                         | 41  |

|               | 3.3             | Evalua  | tion                                           | 43  |

|         |            | ulum V            |                                              | 102        |

|---------|------------|-------------------|----------------------------------------------|------------|

| 6<br>Bi |            | clusion<br>graphy | ns and Future Work                           | 89<br>102  |

| 6       | Cor        | alugios           | ng and Future Work                           | <b>6</b> 0 |

|         | 5.5        | Summ              | ary                                          | . 87       |

|         | 5.4        | Relate            | d work                                       | . 86       |

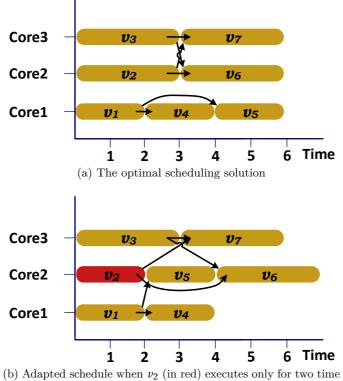

|         |            | 5.3.2             | Evaluation Results                           | . 84       |

|         |            | 5.3.1             | Evaluation Setup                             | . 83       |

|         | 5.3        | Evalua            | ation                                        |            |

|         |            | 5.2.3             | Safety                                       |            |

|         |            | 5.2.1             | Monitor Overhead                             |            |

|         | 0.2        | 5.2.1             | Runtime Monitor Operation                    |            |

|         | 5.1<br>5.2 |                   | erence-sensitive Runtime Adaptation          |            |

| Ð       | 5.1        |                   | Adaptation         etical Results            |            |

| 5       | D          | time              | Adaptation                                   | 73         |

|         | 4.4        | Summ              | ary                                          | . 70       |

|         | 4.3        | Relate            | d work                                       | . 68       |

|         |            | 4.2.2             | Evaluation Results                           |            |

|         |            | 4.2.1             | Experimental Setup                           |            |

|         | 4.2        |                   | ation                                        |            |

|         |            | 4.1.6             | Safety                                       |            |

|         |            | 4.1.5             | Deployment tightening                        |            |

|         |            | 4.1.4             | Memory Mapping, NoC Routing                  |            |

|         |            | 4.1.2<br>4.1.3    | Scheduling, Task Mapping and FIFO Allocation |            |

|         |            | 4.1.1<br>4.1.2    | Partitioning/Placement                       |            |

|         | 4.1        |                   | Deployment                                   |            |

| 4       |            |                   | n Deployment                                 | 53         |

|         |            |                   | •                                            |            |

|         | 3.5        | 0                 | ary                                          |            |

|         | 3.4        | 3.4.1             | d work                                       |            |

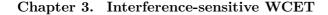

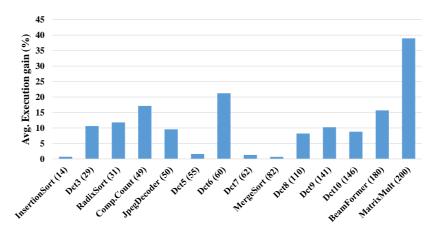

|         | 9.4        | 3.3.2             | Evaluation Results                           |            |

|         |            | 3.3.1             | Experimental Setup                           |            |

|         |            |                   |                                              |            |

# List of Figures

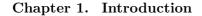

| 1.1  | Power trends for desktop processors                                        | 2  |

|------|----------------------------------------------------------------------------|----|

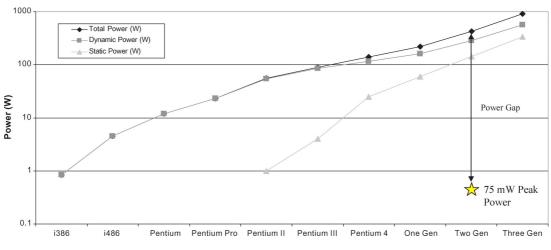

| 1.2  | A typical design process for hard real-time uni-processor systems          | 3  |

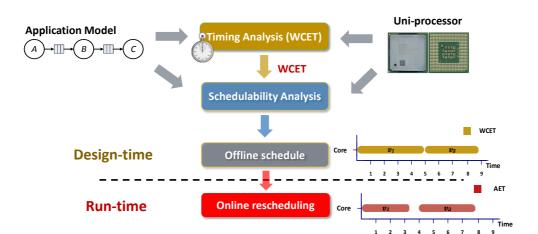

| 1.3  | Example of varying WCET due to interference                                | 4  |

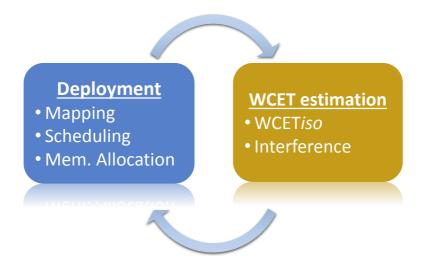

| 1.4  | "WCET estimation" and "deployment optimisation" inter-dependency $\ . \ .$ | 5  |

| 1.5  | State-of-the-art                                                           | 6  |

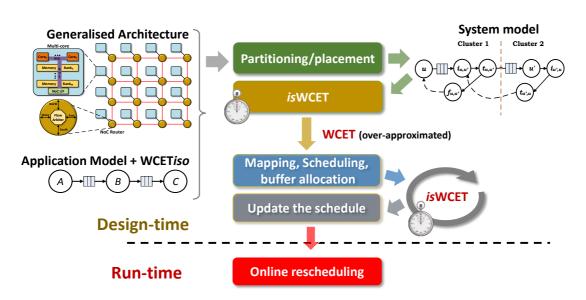

| 1.6  | Global overview of the proposed approaches                                 | 8  |

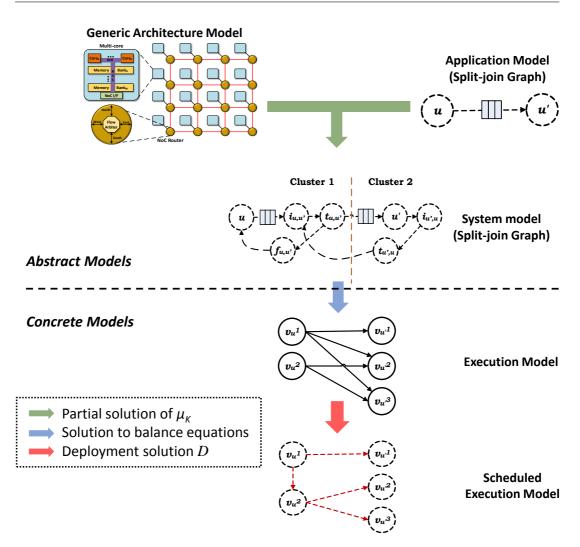

| 2.1  | Abstract and concrete models                                               | 13 |

| 2.2  | Optimal real-time deployment for known WCET                                | 14 |

| 2.3  | Different types of processor architectures                                 | 15 |

| 2.4  | A typical centralised multi-processor architecture                         | 16 |

| 2.5  | A typical distributed multi-processor architecture                         | 17 |

| 2.6  | A typical mixed multi-processor architecture                               | 18 |

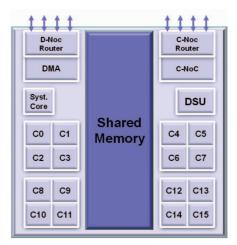

| 2.7  | Kalray MPPA-256 compute cluster                                            | 19 |

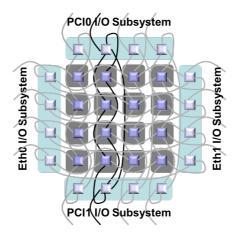

| 2.8  | Kalray MPPA-256 NoC topology                                               | 20 |

| 2.9  | Example of underflow protection                                            | 23 |

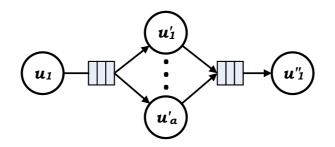

| 2.10 | A split join graph                                                         | 24 |

| 2.11 | Corresponding task graph, with arrows denoting the input/output FIFOs      | 24 |

| 2.12 | Example of a system model                                                  | 26 |

| 3.1  | Overview of the <i>is</i> WCET approach                                    | 30 |

| 3.2  | Kalray MPPA-256 memory bank arbitration                                    | 39 |

| 3.3  | Kalray MPPA-256 NoC router arbitration                                     | 40 |

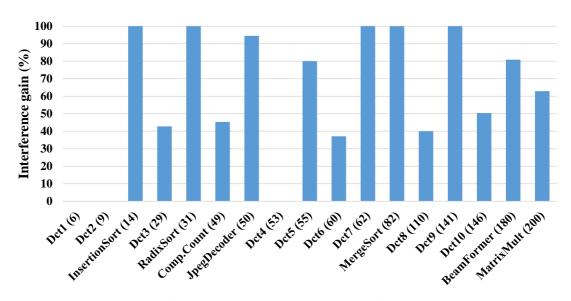

| 3.4  | Percentage of spatio-temporally excluded interference                      | 45 |

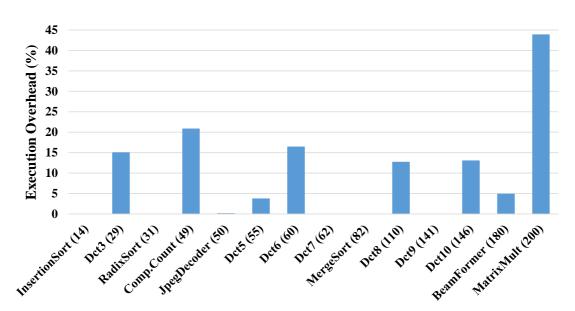

| 3.5  | Percentage overhead due to interference                                    | 46 |

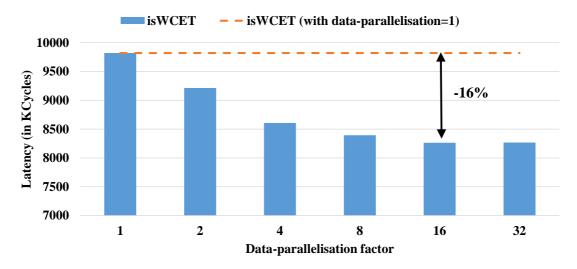

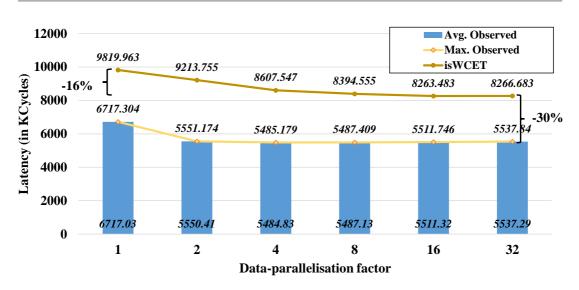

| 3.6  | Task model for various data-parallelisation factors                        | 47 |

| 3.7  | Latency reduction due to data-parallelisation                              | 47 |

| 3.8  | Average percentage reduction of tasks WCET                                 | 48 |

| 4.1  | Overview of the deployment approach                                        | 54 |

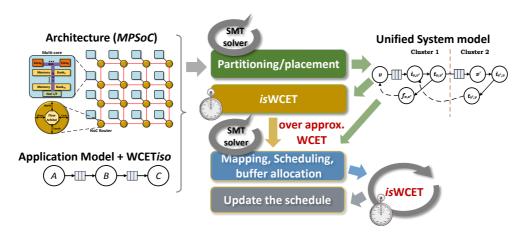

| 4.2  | System model for two dependent actors                                      | 59 |

| 4.3  | Example of schedules $\beta$ and $\beta'$                                  | 65 |

| 4.7  | Percentage of guaranteed latency reduction                                 | 68 |

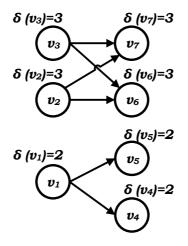

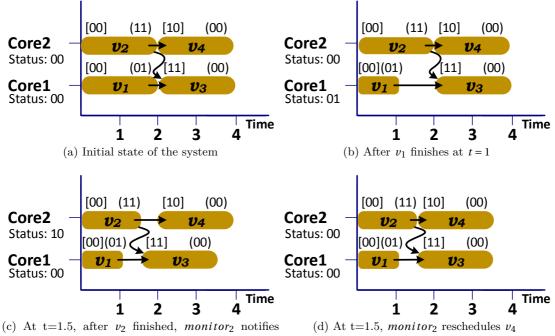

| 5.1 | Example task set that can cause a timing-anomaly                    | 76 |

|-----|---------------------------------------------------------------------|----|

| 5.2 | Example of a timing-anomaly                                         | 76 |

| 5.3 | Example of monitor operation for four tasks on two cores            | 80 |

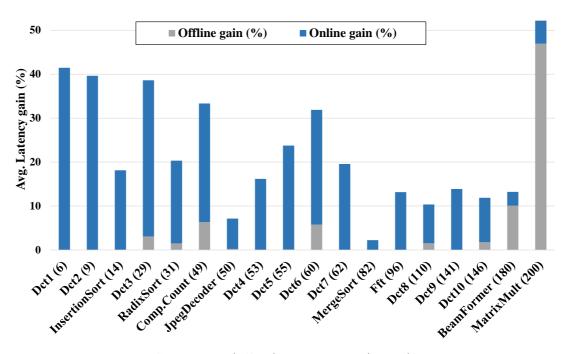

| 5.4 | Guaranteed (offline) and runtime (online) latency gain              | 85 |

| 5.5 | Comparison of the observed latency vs the guaranteed latency of the |    |

|     | produce-process-consume application                                 | 86 |

| 6.1 | Deployment process, revised for multi-processors.                   | 90 |

# List of Tables

| 3.1 | Projections of a task-set $V$ , a dependency relation $E$ and an execution     |    |

|-----|--------------------------------------------------------------------------------|----|

|     | model $EM = (V, E)$                                                            | 37 |

| 3.2 | Kalray MPPA-256 arbitration constants                                          | 43 |

| 3.3 | Worst-case latency of StreamIt benchmarks deployed on Kalray MPPA-256          | 44 |

| 4.1 | Extension of functions $\alpha, \delta_{iso}, \sigma$ for communication actors | 59 |

| 5.1 | Monitor computation overhead                                                   | 82 |

| 5.2 | Monitor interference overhead                                                  | 82 |

# **1** Introduction

#### 1.1 The need of Multi-processors

Modern computing systems are based on *multi-processor* systems, i.e. processors with more than one processing element (PE) integrated in the same chip. Architectures based on the multi-processor paradigm allowed systems to scale and accommodate more demanding applications. This is apparent nowadays, from large distributed systems and cloud services to mobile applications and autonomous vehicles. The main reason that led the processor manufacturing industry to the multi-processor paradigm was the need for higher performance. While it is not the purpose of this thesis to study the concrete phenomena that mandated the use of multi-processors, it is important to outline the main reasons, as they do affect hard real-time systems which did not scale as the rest computing systems. From the '80s until the beginning of the millennium, the processor manufacturing industry was focusing its efforts in increasing the density of transistors in a chip. Smaller transistors present smaller capacitive loads to their drivers, which can thus switch faster. As an immediate consequence, transistor-based units could be operated at higher clock frequencies, resulting in faster processors. This would lead in faster processors that could meet the increasing processing demand.

Despite that the increase of transistor density continued at the same rate for years, known as Moore's Law [92], the processor manufacturing industry shifted its focus to *multi-processor* architectures. The main reasons for this shift are related to power demand, heat dissipation and operating frequency. As a higher operating frequency requires a higher power supply, it results in higher heat dissipation due to power leakage. Therefore, there is limit in frequency at which a chip can be operated for long periods of time without overheating and requiring a reasonable amount of power [6]. This limit, often called Power Wall [65], was reached in 2004 when prototypes of the Tejas processor (the cancelled Pentium IV successor), operating at 2.8 GHz, required 150 Watts.

The proposed alternative to accommodate the demand for more processing power was

Figure 1.1 – Trends of required power for desktop processors [113]

multi-processor architectures, where multiple PEs — called *cores* — are bundled in the same integrated circuit. The first designs and implementations consisted of 8 or fewer cores on the same die, sharing resources of the chip, e.g. memories, bus interconnect, buses to the shared and main memory, etc. This scheme could not scale up to several dozens or hundreds of cores, as sharing the same communication medium was deemed an impractical approach [55]. This gave birth to a new interconnection paradigm, the *Network-on-Chip* (NoC) [12, 32], which consists of routing nodes, network interfaces and links among them forming a network. Behind each network interface are located one (or more) cores with a private memory. Cores can exchange data over the NoC, accessed through the network interface, thus decoupling computation and communication operations. NoC routers, as in computer networks, are responsible for data routing between the source and target core.

### 1.2 Challenges in Hard Real-time Multi-processor Systems

While multi-processor and NoC based architectures were realised to meet the increasing processing demand in several computing domains, the fact that multiple resources are extensively shared, compared to uniprocessor systems, has a significant impact for *real-time computing*. Real-time systems are computing systems which are required to perform particular tasks within certain amount of time, called deadlines. Whether there is value in responding beyond the deadline distinguishes *hard* from *soft* real-time systems [26, 14]. In order to prove that deadlines are met, hard real-time systems are required to be formally modelled, while soft real-time – being defined as not hard – have no such requirement, in general. For example, the airbag control system of modern cars is a hard real-time system, as deploying the airbag after its deadline can potentially harm the driver. On the other hand, responding to keyboard strokes or mouse clicks is considered a soft real-time, as it is desirable to react to such events even past their deadlines. Therefore,

Figure 1.2 – A typical design process for hard real-time uni-processor systems

in order to prove that deadlines are met, it is important for hard real-time systems to have analysable and predictable timing behavior.

Modelling, analysing and optimising the timing behavior of uniprocessor-based real-time systems was the focus for several decades, for the Scheduling [14, 26, 82] and Verification communities [53, 22, 75, 31]. Formal models of real-time systems are based on the notion of *tasks*, which are units of execution, ranging from a bundle of instructions up to a whole set of programming functions. Using such models, the timing behavior of the system can then be studied, analysed and/or optimised. Typically, approaches that provide hard real-time guarantees [14, 26, 34, 25] are based on the notion of Worst-Case *Execution Time* (WCET) of tasks, i.e. the maximum amount of time required for a task to execute in the target architecture under any possible valid input [112, 41]. Acquiring the exact WCET for a task is rather challenging, and not feasible in all cases. Acquiring exact WCET requires to consider all possible execution paths of the application (at source/binary code level) an all possible execution scenarios of instructions at the target architecture, including out-of-order execution, branch prediction, cache replacement policy, data/instruction prefetching, etc. [112, 110]. This leads to an exponential number of possible executions which have to be explored. Even for small-sized applications this exploration cost is prohibiting, rendering acquisition of exact WCET impractical [112].

Figure 1.2 illustrates a typical design process [26, 34, 25, 14, 112, 31] for realizing hard real-time uni-processor systems. Given a set of application tasks, the first step of such a process is to perform timing analysis of those tasks in order to acquire their WCET estimation for the target architecture. Using these WCET estimations, the process performs a schedulability analysis, for a given scheduling policy decided at design-time, to determine if all the real-time constraints (internal deadlines, latency guarantees, etc.) are met. Upon success, the process may generate (offline) static schedules and timing information, which could be used as input for a run-time scheduler. At runtime, the

Figure 1.3 – Example of varying WCET for four equivalent tasks executed on three cores. Tasks  $v_1, v_2$  will experience, in the worst-case, two time units of interference due to their mutual overlapping and the overlapping with  $v_3$ ; Task  $v_3$  will experience three time units from tasks  $v_1, v_2, v_4$ , while task  $v_4$  only one time unit from  $v_3$  (WCET*iso* denotes WCET in isolation, i.e. in absence of interference)

predetermined scheduling policy is implemented or, if additional information is provided, a run-time policy is enforced which, nevertheless, must be proven that preserves the acquired real-time guarantees (deadlines, latency).

Certainly, there are several variations of the "typical" design process for realising hard real-time systems, each with its benefits and shortcomings, on a uni-processor. However, with the rise of new architectures with multiple PEs, timing analysis and optimisation becomes even more challenging [14, 33, 105, 70, 40]. This is due to sharing several arbitrated resources among these PEs (memories and interconnects) which introduces timing delays and changes the timing behavior in a non-deterministic manner. As pointed out by Davis and Burns [34]: "A recent survey of WCET techniques [112] concluded that no static analysis currently exists for multi-core processors which have such<sup>1</sup> complex hardware interactions. Research in this area has either aimed to develop a fully statically analysable multi-core CPU, or to move from providing deterministic WCET estimates to providing probabilistic ones with a high degree of confidence."

A motivating example of the variability of WCET estimations, due to resource sharing, is outlined in Figure 1.3. Consider four equivalent tasks, e.g. an image filter applied to four different parts of an image. These tasks, being equivalent, have the same WCET when executed in isolation. If the overhead per overlapping task is of one unit, it is clear that the WCET of each task will increase, with the amount of WCET increase being dependent on how and when these tasks are executed. Therefore, despite the fact that these tasks are equivalent, thus have the same WCET in isolation, their WCET varies according to the chosen deployment.

In order to naturally extend the uni-processor deployment approaches to multi-processor architectures, one would have to over-approximate the tasks WCET, such that the WCET

<sup>&</sup>lt;sup>1</sup>Referring to timing delays due to contention on shared resources

Figure 1.4 – "WCET estimation" and "deployment optimisation" inter-dependency; optimisation of the former depends on the latter, and vice versa

accounts for all possible interferences. Nevertheless, such a pessimistic WCET estimation will result in under-utilised systems, thus seriously undermining the advantages of utilising multi-processors. This is often called the "one-out-of-m processors" problem [63], where the additional processing capacity is negated by the pessimism of the WCET. In fact recent research [64], including research performed within this dissertation [100, 99, 97] shows that WCET estimations which account for interferences from parallel tasks can be 150%, or even 750%, of the corresponding estimations in absence of interference.

Yet, the vast majority of scheduling approaches that aim to address hard real-time systems, either for standard task models [34, 14, 26, 82, 50] or Models of Computation (MoCs) [68, 49, 67, 17, 72, 19], require the *a-priori* knowledge of tasks WCETs. This, of course, is not without reason; one being that research performed from the '60s until late '90s made a then reasonable assumption that delays due to arbitration of shared resources are negligible since processors operated in low frequencies and comprised of a low-number of cores.

Another, and more important reason for the *a-priori* knowledge of WCET assumption, is the inter-dependency between "WCET estimation" and "deployment optimisation" that appears in multi-processor systems [34]. Accurate estimation of interference delays -and by extension estimation of tasks WCET- depends on the way an application is deployed. But, optimisation of hard real-time deployment (in terms of latency) is a constrained optimisation problem that depends on the estimation of tasks WCET, thus creating a cyclic dependency between the two main aspects of realising hard real-time systems.

#### Chapter 1. Introduction

|  |               |                                                              | Software                           |                                                                                                |                         | Hardware |                                              |

|--|---------------|--------------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------|-------------------------|----------|----------------------------------------------|

|  |               | Scheduling<br>Theory                                         | Model-based                        | Resource Partitioning                                                                          | Reso<br>Regula          |          | Deterministic<br>Resources                   |

|  |               | •EDF-based<br>•RM-based<br>•Ad-hoc<br>•Mixed-<br>criticality | •SDF<br>•KPN<br>•Timed<br>automata | •Memory / Cache<br>coloring / partitioning<br>•Time partitioning<br>•PREM<br>•Sliced Execution | •Memory<br>•Bus<br>•NoC |          | • Caches<br>• Scratchpad<br>• Buses<br>• NoC |

|  | WCET          | Assume known                                                 | Assume known                       | Improved                                                                                       | Impro                   | oved     | Improved                                     |

|  | Efficiency    | (varies)                                                     | (varies)                           | Improved                                                                                       | Impro                   | oved     | Improved                                     |

|  | Adaptability* | (varies)                                                     | (varies)                           | Restricted/None                                                                                | Fu<br>(slows-down       |          | Full<br>(slows-down runtime)                 |

\* Ratio of safe adaptations to total adaptations (directly affects runtime performance)

Figure 1.5 – Overview of the state-of-art

In order to resolve this cyclic dependencies and still acquire reasonable WCET estimations, several state-of-the-art approaches (Figure 1.5) employ resource isolation [34, 94, 21, 81], or resource regulation [78, 36, 66, 64] techniques. In resource isolation, access to shared resources (buses, memories, NoC routers) is restricted to strictly one core (e.g. spatial partitioning [102], memory coloring) or one core at a given time (e.g. temporal partitioning [23, 48], temporal isolation [21, 81]). This is achieved either at the hardware level (e.g. TDMA) or using software mechanisms [34]. Resource regulation techniques, on the other hand, allow the simultaneous use of resources, but restrict the amount of requests to a shared resource per core within a predefined time window.

While such approaches restrict the pessimism in WCET estimations, and thus provide more *efficient* deployments, they can undermine run-time performance as they restrict *adaptability*. Consider, as an example, the hypothetical scenario where the airbag (SRS) control software of a vehicle is executed in the same multi-processor as the automatic braking (ABS) control software. Both software have real-time guarantees and there is a benefit in executing them as fast as possible. In the case of resource isolation techniques, the SRS cannot access resources dedicated to ABS while ABS is executing, and vice versa. In the case of resource regulation, while accessing a shared resource is permitted, the amount of requests is restricted over time, which essentially slows down the execution of both the SRS and ABS software.

This dissertation holistically provides methods for deployment of applications to multiprocessors architectures, as the authors of [33, 104], but with the aim of providing hard real-time guarantees. In order to realise efficient hard real-time systems, without sacrificing adaptability [94, 21, 81], task WCETs are improved as the deployment process progresses. A similar idea [41] is being advocated by the on-going European-funded project Argo [84].

## **1.3** Thesis Statement and Contributions

This dissertation aims to stand between the two ends of the spectrum of approaches, that is (i) methods that do not restrict *adaptability*, but overestimate WCET and provide pessimistic latency guarantees, and (ii) methods that provide *accurate* WCET estimations and tight latency guarantees, but restrict run-time performance. To bridge that gap, this dissertation proposes novel methods for safely deploying a streaming application to a generic homogeneous architecture, by coupling the WCET estimation method to the deployment process.

The first proposed method is an interference analysis, called *is*WCET method, which given an architecture model, an application model with data-dependencies, and the WCET estimations of the application's tasks (in absence of interference), estimates the possible amount of interference. As more information is provided, such as *task mapping*, *scheduling*, *memory mapping*, etc., the per-task interference estimation becomes more accurate, but also more sensitive to changes. These *interference-sensitive* estimations are considered safe only for deployments in which the maximum interference each task can experience is at most as those interference-sensitive estimations.

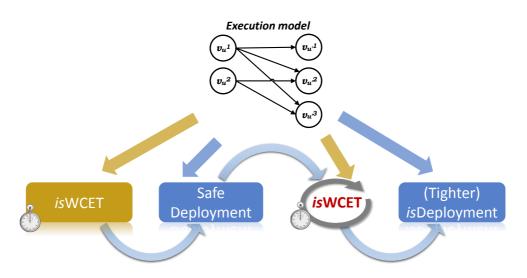

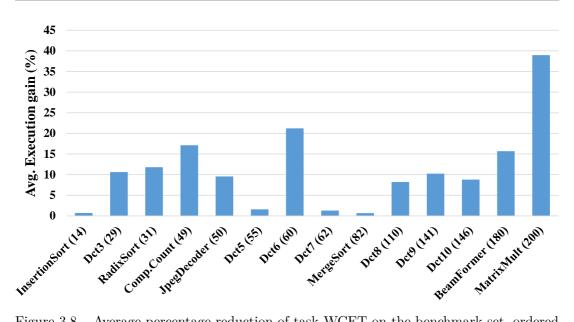

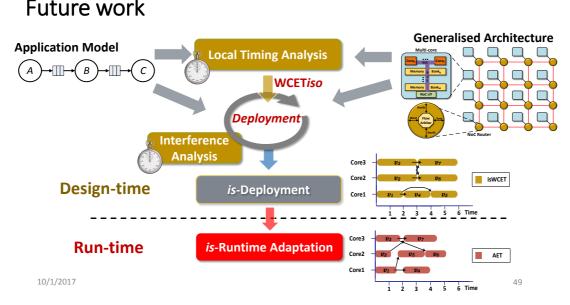

The second proposal is to couple such an *is*WCET method to a deployment process for a multi-processor architecture, as shown in Figure 1.6. The proposed process derives safe (in terms or real-time constraints, buffer protection and deadlock freedom) and efficient deployments, by gradually providing information to the *is*WCET method. To illustrate the benefits of such coupling, we apply such an approach to a variant of SDF graphs, called split-join graphs. Intuitively, split-join graphs model explicitly task-/dataparallelism of actors, by allowing potentially parallel firings of actors to read/write to the same channel.

Still, while the generated deployment solution is safe and improved in terms of guaranteed latency, run-time performance can be severely undermined, since the worst-case is unlikely to occur at runtime. While the *is*WCET-based deployments are more efficient, in order to avoid violating the real-time guarantees, such deployments permit only certain adaptations out of the possible many. The adaptations that are deemed safe should not increase the interference any task may suffer in the worst-case. Therefore, the third contribution of this dissertation is a novel, interference-sensitive, runtime adaptation technique, called *is*RA, which is suitable for deployments based on *is*WCET estimations. Being a distributed approach, the execution of the runtime monitors responsible for enforcing the adaptation policy can also cause interference. For this reason, the runtime monitors are designed, and implemented, having minimal execution time and induced interference, thus avoiding undermining runtime performance and still meeting the real-time guarantees.

The final contribution of this thesis, is the realisation of all the aforementioned methods and techniques for an actual multi-processor (Kalray MPPA-256). All of the approaches

Figure 1.6 – Global overview of the proposed approaches

were evaluated on this multi-processor with real-life applications (StreamIt benchmark), outlining the benefits that each method contributes to the the problem of application deployment with real-time guarantees.

## **1.4** Dissertation Outline

*Chapter 2* presents the fundamental models used for streaming applications and generic architectures. Based upon these models, an execution model is derived which faithfully captures possible executions of the application deployed on a generic architecture and serves as the intermediate representation for the various steps of the proposed approaches.

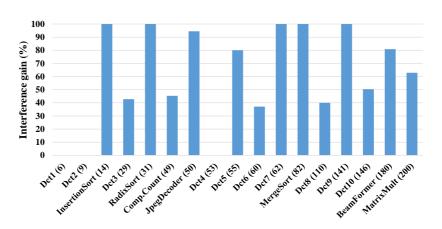

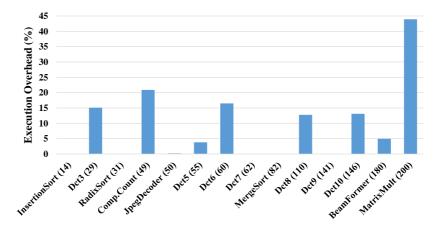

Based on an execution model, in *Chapter 3*, a novel interference analysis and WCET estimation method is presented, called *is*WCET. As more information is available about the application deployment (such as memory mapping, task mapping, task scheduling, etc.), the *is*WCET method provides more accurate interference estimations, via iteratively applying *spatio-temporal* exclusion, thus acquiring more accurate, but sensitive, WCET estimations. The method is formally proven to be (i) *safe*, (ii) *exact* and (iii) always *converges*. Experimental results of the StreamIt benchmark deployed on the Kalray MPPA-256 multi-processor show that the *is*WCET method is able to exclude 74% of the interference delays on average, improve WCET estimations up to 36% and reduce the average overhead due to interference to less than 10%.

In *Chapter 4*, a safe deployment process is presented that leverages the outcomes of the *is*WCET method. The deployment method manages to break the inter-dependency cycle by coupling the WCET estimation with the deployment process. Specifically, the

proposed deployment process estimates tasks WCET using the *is*WCET method, without any information regarding the deployment. Once a safe deployment is acquired, the process provides the deployment information to the *is*WCET method to derive tighter WCET estimations and adapts accordingly the acquired deployment. Extending the results of Chapter 3, experimental evaluation shows that coupling the *is*WCET with the deployment process, can improve guaranteed latency up to 46%.

Chapter 5 presents a novel distributed runtime adaptation technique, called isRA, which builds upon isWCET estimations and aims at improving run-time latency. The proposed isRA technique restricts executions that would introduce additional interferences, beyond the ones already accounted for by the deployment process. The method is proven to be safe and illustrated to have minimal overhead in execution time and induced interference. The isRA is experimentally evaluated with the StreamIt benchmark deployed on the Kalray MPPA-256 multi-processor, using the isWCET method and the proposed deployment process. Experimental results show that the isRA improves runtime latency by 22% on average, up to 42%. Thus, the consolidated improvement in latency, from all the proposed methods, can be of more than 50%.

# **2** Preliminaries

To provide real-time guarantees for an application deployed on an architecture, formal models for the application and the target architecture are necessary. An application is often considered in literature (e.g. [82, 14, 40, 34]) to consist of a set of *computation tasks* which may be data-dependent. When all these computation tasks are executed, the application is considered to have completed its execution, that is, the input data have been consumed and the desired output has been produced. The output is considered to be correct if during the execution there are no data-races, deadlocks etc. In a very abstract manner, we can represent an application as a *task graph* A = (V', E') where V' is the set of computation tasks and E' is the dependency relation among the computation tasks. Deploying an application on a multi-processor architecture may also require additional tasks in order to faithfully model *architecture-specific* operations of the underlying architecture, such as hardware synchronisation, NoC transfers, etc. Therefore, the resulting system can be viewed as a task graph S = (V, E), derived from the application graph, which contains the original computation and additional architecture-specific tasks and respects the data-dependencies of the application.

Given a set of given real-time constraints for an application, the real-time deployment of an application on a multi-processor architecture involves several decisions. These decisions drill down to well known problems, that is (i) *processor mapping*, (ii) *memory mapping*, (iii) *NoC routing* and (iv) *processor scheduling*. Processor mapping (often also called task mapping) refers to the decision of assigning tasks to PEs (without considering the order of execution), while processor scheduling is the decision of the order of task execution. Often, especially in Scheduling Theory [82], these are collectively referred as scheduling problem, but we will make the aforementioned distinction as it has a significant impact on our approaches. The memory mapping problem refers to the decision of which parts of the memory will be assigned to each task in order to perform its execution. Finally, NoC routing is a typical network problem of deciding the sequence of routers that packets or flows should traverse, in order to reach their destination. All these decisions have an impact on the resource demands and execution times of tasks, thus affecting the efficiency of the system.

As a semi-formal definition of what a *real-time deployment* consists of, let the tuple  $D = (\mu_K, \mu_M, \rho, \beta, \epsilon)$  be the non-preemptive *deployment solution*, i.e the collective solution of these problems, where:

- $\mu_K$  is the function which assigns tasks to PEs (processor or task mapping problem)

- $\mu_M$  is the function which maps tasks data-dependencies, private variables and binary code to memory (*memory mapping* problem)

- $\rho$  is the routing of the data-flows on the NoC (*NoC routing* problem)

- $\beta$  and  $\epsilon$  are the functions which denote the begin and end times of tasks, respectively (*scheduling* problem)

In order to generate a deployment solution which meets certain real-time constraints, e.g. tasks finish before some given deadlines and/or the execution finishes prior to a given latency constraint, timing information of the application's tasks must be provided. The required timing information for each task is called *Worst-Case Execution Time* (WCET), which is the maximum amount of time required for a task to execute in the target architecture under any possible valid input. In architectures with multiple PEs the actual WCET of any task v can vary according to the *deployment*, due to sharing arbitrated resources among PEs which introduces *interference* delays and changes the timing behavior in a non-deterministic way.

In principle, the WCET of a task v can be decomposed into the WCET in isolation, i.e. in absence of interference, and the interference delays. Thus, given a deployment solution D, for any task v its total duration of execution is:

$$\delta_{\iota^{D}}(v) \stackrel{def}{=} \delta_{iso}(v) + \iota^{D}(v) \tag{2.1}$$

where  $\delta_{iso}(v)$  is the WCET in isolation, which is assumed constant regardless of the deployment D, and  $\iota^D(v)$  is the amount of delays that task v experiences from simultaneously executed tasks. The assumption that the WCET in isolation is constant, and does not depend on the deployment D, implies a homogeneous architecture, i.e. all PEs are identical. Even in such architectures, while the WCET in isolation  $\delta_{iso}(v)$  for any task v does not depend on the deployment D, the same is not true for the interference delays  $\iota^D(v)$  as they vary based on the deployment D. We will call  $\delta_{\iota^D}$  the *interference-sensitive* WCET, or simply *is*WCET.

Our approaches involve several models (Figure 2.1); Initially, two abstract models are consider as input, i.e. *application model* and *architecture model*. These are used to construct the *system model*, which faithfully models the execution of the *application*

Figure 2.1 – Abstract and concrete models

*model* to the target *architecture model*. The system model is transformed in the execution model, which contains all the tasks of the system. The purpose is to solve the majority of optimisation problems, required to acquire a safe deployment, on the abstract model, i.e. system model. Whenever the system model cannot be used efficiently, its corresponding execution model is used. The execution model, serves also another purpose. When the safe deployment is derived, the execution model is transformed to the scheduled execution model, which is the input for our runtime adaptation, along with the deployment solution. This transformation of the execution model will play a crucial role in the efficiency of the proposed runtime adaptation, but this will be discussed on Chapter 5.

In the next subsections the real-time deployment problem is formulated and the aforementioned abstract and concrete models (in Figure 2.1) are formally defined.

### 2.1 Real-time Deployment Problem Formulation

The *optimal*, in terms of time, *deployment* of an application on the target architecture consists of finding the solution with the smallest *latency* to the i) processor mapping  $(\mu_K)$ , ii) memory mapping  $(\mu_M)$ , iii) NoC routing  $(\rho)$  and iv) scheduling  $(\beta, \epsilon)$  sub-problems, such that given *real-time* constraints are met. Thus, the real-time deployment problem can be formulated as a constrained optimisation problem:

Find  $D = (\mu_K, \mu_M, \rho, \beta, \epsilon)$  s.t.  $\min\left(\max_{v \in V} (\epsilon(v))\right)$  subject to  $C_{RT}$

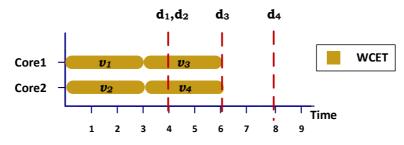

where  $C_{RT}$  is a set of real-time constraints of the form "some tasks should finish before their deadline", i.e.  $v \in V$ ,  $\epsilon(v) \leq d_v$ . To illustrate a simplified version of the whole problem, consider Figure 2.2, where four tasks are deployed on two cores. Each task has a (known) WCET of three times units and its respective deadlines is illustrated with a dashed-line.

Figure 2.2 – Optimal real-time deployment for known WCET

The focus of this dissertation is on *non-preemptive, homogeneous* systems. In homogeneous systems the PEs of the architecture are identical and the WCET in isolation,  $\delta_{iso}(v)$ , of any task  $v \in V$  is the same on all PEs. Non-preemptive systems are those in which once a task has started its execution, it cannot be interrupted and the task's required resources (memory locations, PE) cannot be used until the task finishes execution. Thus, given the *is*WCET  $\delta_{,D}$  the task-end function  $\epsilon$ , for non-preemptive systems, is defined as:

$$\epsilon(v) \stackrel{def}{=} \beta(v) + \delta_{v^{D}}(v) \quad \forall v \in V$$

(2.2)

Notice that even for non-preemptive systems the optimisation problem becomes rather complicated, as the exact valuation of the optimisation function  $\epsilon$  depends on the solution of the optimisation problem D.

There are several variations of the same problem depending on the type of architecture and the assumptions made about the WCET. For example, for a multi-processor architecture with a bus-based interconnect, the deployment reduces to a tuple without the NoC routing function  $\rho$  (i.e.  $D = (\mu_K, \mu_M, \beta)$ ), while if the WCET estimations are pessimistically

estimated to include all possible interference delays, the deployment can even reduce to  $D = (\mu_K, \beta)$ . These variations can reduce the complexity of the deployment problem but also lead to inefficient systems (details can be found in Section 3). As opposed to many techniques in the literature, this dissertation does not rely on overly pessimistic WCET estimations, since one of its aims is to explore and outline the impact of such pessimism to the efficiency of the resulting system.

## 2.2 Processor Architecture Models

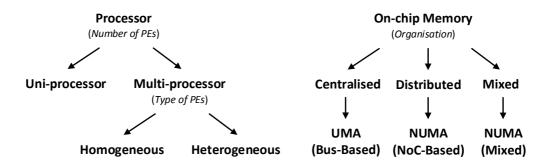

At the time this dissertation was written, several research [58] and commercial [61, 108, 60, 87, 46] computing platforms with multiple PEs were available. These broadly can be categorised according to i) the type of PEs and ii) the on-chip memory organisation, as illustrated in Figure 2.3.

Homogeneous (as opposed to heterogeneous) are the platforms where the PEs are of the same type, e.g. CPU [60, 80], GPU [79], DSP, and have the same overall speed when executing a task, i.e. all PEs have the same clock speed, cache size, I/O interfaces and any other mechanism that can affect the PEs' timing behavior. From the perspective of how the shared memory is organised, there are three main categories, i.e. centralised, distributed and mixed. In centralised memory organisation, the time for any PE to access any memory location (typically via a bus) is uniform, when there is no interference, that is the time does not depend on the targeted memory location/address. On the other hand, in the distributed memory organisation, PEs use a different mechanism, such as Direct Memory Access (DMA) engines or NoC, to access various memory locations, thus having a Non-Uniform Memory Access (NUMA) in terms of timing. The mixed memory organisation is a combination of the centralised and distributed memory organisations, where a subset of PEs access their shared memory uniformly, but accessing the memory shared by another set of PEs is non-uniform.

Figure 2.3 – Different types of processor architectures.

#### 2.2.1 Homogeneous Architecture Types

The focus of this dissertation is on *homogeneous multi-processor* architectures, with the PEs being general purpose cores, for reasons explained in the Introduction. Following is a description of the homogeneous architectures covered in this dissertation according to their on-chip memory organisation. It must be pointed out that while the terms "centralised", "Uniform Memory Access", "distributed", "Non-Uniform Memory Access" frequently refer to main memory organisation, here are used for the on-chip memory.

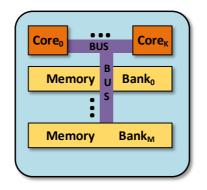

#### Centralised architectures

Figure 2.4 – A typical centralised multi-processor architecture.

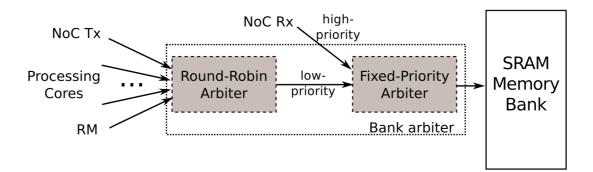

In centralised homogeneous architectures, a number of general purpose PEs, henceforth cores, have a private cache memory (for instructions and data) but also share a part of the on-chip memory. The shared memory can be divided in several banks and cores can access a bank via a bus. Thus, in the general case, a bus connects a subset of the cores with a subset of the banks. To resolve conflicts of simultaneous requests for shared resources, i.e. buses, memory, these resources are arbitrated causing *timing interference*. Thus, a simultaneous memory request can be arbitrated at the bus arbiter, to resolve which core uses the bus first, and also at the memory arbiter, to resolve which memory request is served first by the memory controller of the memory bank.

For the purpose of interference analysis, it is assumed that a memory arbiter is dedicated to one memory bank. This is assumption is not restrictive as, in the case of multiple banks per memory arbiter, these banks can be considered as one. Also, it assumed that a continuous region on a memory bank can be allocated, as in sequential memory addressing, e.g. Kalray MPPA-256 [37], or strided memory allocation, e.g. CUDA [51].

Figure 2.5 – A typical distributed multi-processor architecture.

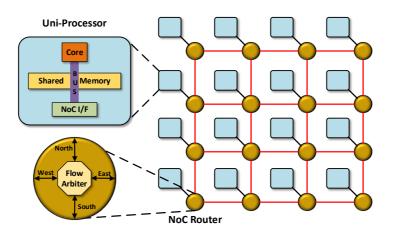

#### **Distributed architectures**

In distributed homogeneous architectures several computing nodes are interconnected with a NoC. The computing nodes have a single core, with its private instruction and data caches, connected with a bus to the shared memory. In that sense, it is no different than a uni-processor. Additionally, a computing node has a NoC interface (NoC I/F) through which data are sent/received from other computing nodes. In order to parallelise data transfers, the NoC I/F can have multiple channels. A data transfer between a source and a destination computing node, the source NoC I/F (using its channels independently of what the core is executing) reads data from the shared memory, forms the network packets and injects them into the NoC, via a link to its corresponding NoC router. The packets are then forwarded from router to router, according to a routing policy, until they reach their destination. At the receiving end, the destination NoC I/F retrieves the data from the packets and places them into the destination shared memory, thus completing the data transfer.

Apart from the bus and memory arbiter that exist to resolve conflicts between the core and the NoC I/F of a computing node, there is an additional arbiter at each NoC router. For the purpose of interference analysis, it is assumed that when two packets simultaneously arrive at a NoC router from different input network links and are directed to the same output links, the flow arbiter decides which packet will be served first. As, the focus of this dissertation is in interference, it is also assumed that NoC routers will not block and cause back-pressure (which can be achieved by flow regulation at the source [36]). We consider that such assumption can be alleviated with proper adaptations of the interference analysis, but in principle should be handled by the deployment process and not the interference analysis.

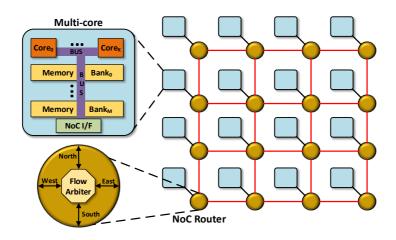

#### Mixed architectures

Figure 2.6 – A typical mixed multi-processor architecture.

Mixed homogeneous architectures are a combination of the centralised and distributed architectures. Their main difference from the distributed paradigm is that the computing node is replaced by a computing *cluster*, which essentially is a multi-processor with a NoC I/F. In terms of arbitration points, mixed architectures are the same as distributed architectures, i.e. they have memory, bus and flow arbitras. But, compared to distributed architectures, the number of sources of arbitrated requests, and by extension sources of timing interference, is larger.

Stemming out from the focus on homogeneous architectures, it is assumed that the computing clusters are identical in the sense that the time to execute a task does not depend on which computing cluster is executed.

#### 2.2.2 Generic Architecture Model

In order to capture the different architectures with a single model that will be used in the proposed methods of this dissertation, the *generic architecture model* is introduced. A single model is important as it enhances applicability of the proposed methods, which in the context of hard real-time systems is desirable, as safety properties have to be proven only once.

**Definition 2.2.1** (Generic architecture model). A generic architecture model is a tuple  $\mathcal{GA} = (\mathcal{C}, \mathcal{K}, \mathcal{L}, \mathcal{M}, \mathcal{N})$  where:

- C is a set of computing clusters

- $\mathcal{K}$  is a set of processing cores per cluster

- $\mathcal{L} \subseteq \mathcal{C} \times \mathcal{C}$  is a set of links among computing clusters that form the NoC

- $\mathcal{M}$  is a set of memory banks per cluster

- ${\cal N}$  is the set of NoC channels of a NoC I/F

When the generic architecture model is instantiated to a concrete architecture model matching with one of the homogeneous architecture types described earlier, i.e. (i) the centralised architectures  $\mathcal{MA} = (\mathcal{C}, \mathcal{K}, \emptyset, \mathcal{M}, \emptyset)$  which do not have a NoC interconnect, (ii) the distributed architectures  $\mathcal{DA} = (\mathcal{C}, \{k\}, \mathcal{L}, \mathcal{M}, \mathcal{N})$  with one core k per cluster, and (iii) the mixed architectures  $\mathcal{MX} = (\mathcal{C}, \mathcal{K}, \mathcal{L}, \mathcal{M}, \mathcal{N})$ .

For the architectures that have a NoC it is assumed that each cluster has one NoC I/F, with multiple channels, connected to a single dedicated NoC router [32] and has a separate bus to access the shared memory.

#### 2.2.3 Kalray MPPA-256

The Kalray MPPA-256 chip consists of 256 processing VLIW cores grouped in 16 computing clusters with each cluster comprising 16 processing cores at 400MHz and 2MB of shared scratchpad memory (Figure 2.7). The shared memory consists of 16 independent 128kB memory banks with 64-bit words organised in two sides, *odd* and *even*. Each cluster has one NoC I/F, subdivided in transmit (Tx) and (Rx) interfaces, implemented with an a 8-channel DMA engine [38].

Each cluster NoC I/F is coupled with a dedicated NoC router, which are organised in a 2D-torus topology (Figure 2.8). Each router has 5 full duplex links, one for each direction plus one for its corresponding computing cluster. Each link to another router has an

Figure 2.7 – Kalray MPPA-256 compute cluster [37].

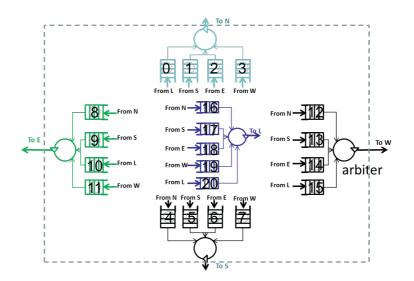

Figure 2.8 – Kalray MPPA-256 NoC topology [36].

independent round-robin arbiter and 4 FIFOs, one per input direction. The link to its dedicated cluster has one additional FIFO, so the cluster can send packets to itself. This means that the router can send back received packets from its cluster, but not from other routers.

Having this particular architecture that matches the generic architecture model  $\mathcal{GA}$ , the Kalray MPPA-256 can be reconfigured (depending on how an application is deployed) according to the different types of architectures considered. In specific the Kalray MPPA-256 can serve as:

- Centralised architecture: where only one computing cluster is utilised

- Distributed architecture: where only one core from each cluster is utilised

- Mixed architecture: where the full chip, i.e all 256 cores, are utilised

## 2.3 Application and System model

To provide real-time guarantees for an application, deployed on an architecture, a formal model for the application is also necessary. An application consists of a set of *computation tasks*. There is one significant distinction, encountered especially in the Scheduling Theory community, for the set of computation tasks. *Independent* tasks are those tasks which, if ready, can be scheduled in any order, while for *dependent* tasks there is an inherent scheduling order imposed. For example, compressing an image according to the JPEG standard requires that the image is split in blocks before it is transformed using the *Discrete Cosine Transformation* (DCT) method. So, from a task perspective, there is a data-dependency between the tasks that form the blocks and the DCT transformation tasks.

When all of these computation tasks are executed, the application is considered to have completed an *execution*, that is, the input data have been consumed and the desired output has been produced. The output is considered to be correct if during the execution there are no data-races, deadlocks etc. This dissertation considers applications that are composed of *data-dependent* computation tasks and are *iteratively executed* on a stream of input data, called *streaming* [109] or *data-flow* [68, 49] applications. This particular class of applications is suitable for architectures with large number of cores, as they exhibit a high degree of task- and data- parallelism.

An application composed of a set of *computation tasks* with dependencies can be modelled with various *Models of Computations* (MoCs), such as *Synchronous Data-Flow graphs* (SDFs) [68] and *Kahn Process Networks* (KPNs) [49]. Such models provide necessary correctness properties (such as deadlock freedom, absence of data-races, confluency, buffer protection, etc.) by-construction, if their semantics are respected. Without being strictly restricted to, an application will be modelled as a particular class of SDFs, called split-join graphs [106]. The choice of this particular model is due to (i) the explicit modelling of parallelisation factors and (ii) available tool-chain for these models.

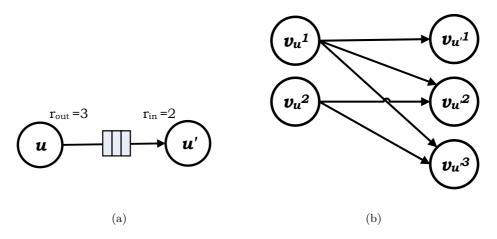

Generally, an SDF model is a directed graph  $SDF = (\mathcal{U}, \mathcal{E})$  with  $\mathcal{U}$  being a set of computation *actors* and the binary relation  $\mathcal{E}$  representing a set of FIFO channels among them.. In this model, *actors* communicate with each other by sending ordered streams of data elements (called tokens). When an actor is *fired* —which corresponds to the notion of task execution— it consumes a fixed amount of data tokens from its input FIFOs and produces a fixed amount of data tokens to its output FIFOs. These amounts are called production-/consumption *rates* and are defined for each of the actor's FIFOs. The production/consumption of data tokens are blocking operations, that is, if an input FIFO is empty (respectively an output FIFO is full) the corresponding read (respectively write) operation will be blocked until the FIFO contains enough data (respectively has enough free space).

Generally, it is considered acceptable in SDF models to fire an actor before input data and output space is available, as the actor would block when it would try to access a FIFO. Nevertheless, typical scheduling approaches generate schedules that avoid such situations. In our case where timing correctness is of importance, blocking of an actor would mean that its WCET would change. Thus, to guarantee correctness, a deployment solution must ensure that prior to firing an actor, there is enough data at its input FIFOs and enough free space at its output FIFOs. Otherwise, the actor would block, which would alter its WCET in isolation. Additionally, for efficient utilisation of the on-chip memory, it is assumed that actors can use their allocated space in their input/output FIFOs, to load/store intermediate results of their computation.

To guarantee that there is an *unbounded execution* of the SDF with *bounded FIFOs*, certain *consistency constraints* must be met. These are called balance equations [68]

which essentially state that after a finite number of actor firings all data, which were produced, are consumed.

**Definition 2.3.1** (SDF Consistency). For each FIFO  $e \in \mathcal{U}$ , with e = (u, u'), let  $\#_u, \#_{u'}$  be the number of times actors u, u' are fired, respectively. Also let  $r_{out}^e$  be the production rate of u and  $r_{in}^e$  the consumption rate u' for FIFO e; a SDF is *consistent* if there is a non-zero integer solution to the following *balance* equations, for all edges  $e = (u, u') \in \mathcal{U}$ :

$$\exists \#_{u}, \#_{u'} \in \mathbb{N}_{+}: \quad \#_{u} * r_{out}^{e} = \#_{u'} * r_{in}^{e}$$

(2.3)

For consistent SDFs, the existence of *unbounded*, i.e. deadlock free, *execution* of that SDF with bounded FIFOs is decidable [67].

There are several advantages of SDF models apart from guaranteeing correctness properties; SDF models can be used to model complex applications and allows to explore the latency-throughput-buffer trade-offs.

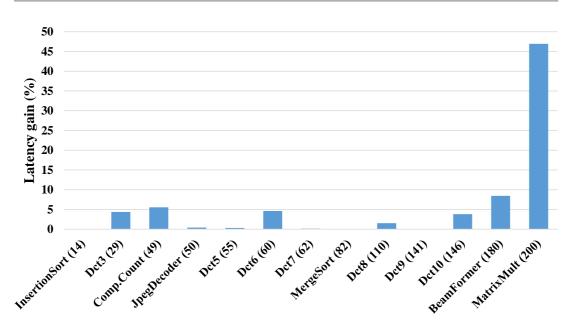

Given a solution to the balance equations, the *execution model* can be constructed, by deriving a task graph containing one task for each actor firing and a dependency relation that describes which firings of two dependent actors can be performed in parallel. This is essential to compute the set of tasks that can be executed in parallel with a given task, which affects the interference estimations in Chapter 3.

**Definition 2.3.2** (Execution model). An execution model  $EM(E_S)$  of a directed acyclic task graph G = (V, E) is its parameterised version  $EM(E_S) = (V, E \cup E_S)$  where the data-dependency relation E is augmented with additional scheduling dependencies  $E_S$ , such that  $EM(E_S)$  is also a DAG.

**Definition 2.3.3.** Given a consistent SDF graph  $SDF = (\mathcal{U}, \mathcal{E})$  and the solution of the balance equations (the number of firings  $\#_u$  for each actor  $u \in \mathcal{U}$ ) and  $r_u^e$  (the rate of actor u for its FIFO e), the execution model  $EM(\emptyset)$  with unbounded FIFOs is derived as follows:

- $V = \{v_u^i \mid \forall u \in \mathcal{U}, \forall i \in [1, \#_u]\}$ , that is  $v_u^i$  denotes the  $i^{th}$  firing of actor u

- $E = \left\{ (v_u^i, v_{u'}^j) \mid (u, u') \in \mathcal{E}, (i-1) * r_u^{(u,u')} < j * r_{u'}^{(u,u')} \right\}$ , that is, between two datadepend actors u, u', the task  $v_{u'}^j$  cannot be executed before its input data from task  $v_u^i$  have been produced.

The dependencies of the execution model essentially prevent from FIFOs to underflow, by preventing a task v' to execute, if the task v that produces the input data of v' has not finished its execution. This is illustrated in the following example:

Figure 2.9 – Example of underflow protection through the dependency relation E of the execution model EM

**Example 2.3.4.** Consider the SDF graph of Figure 2.9a, with actor u producing three tokens at each firing and actor u' consuming two. In Figure 2.9b, the corresponding execution model is presented for the minimal solution of the balance equation of the SDF graph. The dependency relation constructed prevents all tasks of actor u', i.e.  $v_{u'}^1, v_{u'}^2, v_{u'}^3$ , to be executed before the first firing of actor u, i.e.  $v_u^1$ . The second firing of u' requires tokens from the first and the second firing of u, according to production/consumption rates, therefore task  $v_{u'}^2$  is forced to execute after  $v_u^2$ . The same does not hold for the first firing of u', so task  $v_{u'}^1$  can executed in parallel with the second firing of actor u. This is permitted in the execution model as task  $v_{u'}^1$  does not depend on  $v_u^2$ .

#### 2.3.1 Application Model

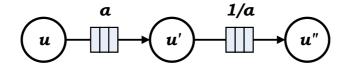

A split-join graph [106]  $SJ = (\mathcal{U}, \mathcal{E}, \alpha)$  is a directed acyclic (DAG) SDF graph  $(\mathcal{U}, \mathcal{E})$ annotated with a parallelisation function  $\alpha$ , assigning a parallelisation factor  $\alpha(e) \in \mathbb{Q}_+$ for each edge e of the graph. An edge e with parallelisation factor  $\alpha(e) > 1$  is called *split*, with  $\alpha(e) < 1$  is called *join* and with  $\alpha(e) = 1$  is called *neutral*. Split-join graphs also require a *well-formedness* condition which states that "the product of parallelisation factors should be 1 for any path from a starting actor (i.e. with no predecessors) to an ending actor (i.e. with no successors) and the sequences of parallelisation factors of those paths respect the *matching-parenthesis* grammar<sup>1</sup>. This condition essentially ensures that all splits are joined in a meaningful manner, that is, all splits are eventually joined and that a split factor a is matched with a join factor  $\frac{1}{a}$ . For example consider the following sequences:

$<sup>^1{\</sup>rm The}\ matching-parenthesis,$  a.k.a. matching-braces, is a classic problem in compilers.

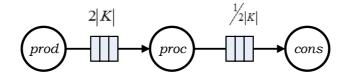

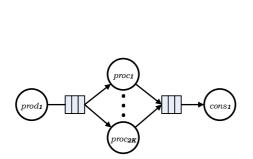

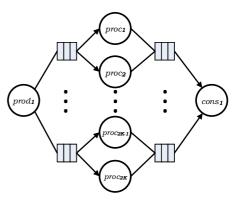

Figure 2.10 – A split join graph

Figure 2.11 – Corresponding task graph, with arrows denoting the input/output FIFOs

- " $2 \cdot 3 \cdot 1/3 \cdot 1/2$ " is well-formed

- " $2 \cdot 3 \cdot 1/2 \cdot 1/3$ " is not balanced as 3 is followed by the the non-matching 1/2

- " $2 \cdot 3 \cdot 1/3$ " is not complete as the product of parallelisation factors is not 1

Split-join graphs are a natural variation of SDF graphs. In an SDF model a FIFO channel between two actors cannot be shared with another actor, but tasks originating from those two actors inherently share that FIFO. In a similar manner, in split-joint graphs functionally equivalent actors can access the same FIFO according to. A split-join graph  $SJ = (\mathcal{U}, \mathcal{E}, \alpha)$  is *consistent* if there is a non-zero integer solution to the following *balance* equations, for all edges  $e \in \mathcal{E}$ :

$$\exists \#_{u'}, \#_{u'} \in \mathbb{N}_+ : \quad \#_u * r_{out}^e = \#_{u'} * r_{in}^e * \alpha(e) \tag{2.4}$$

Intuitively, these balance equations relate the degree of parallelisation between the firing of the connected actors. For example consider two adjacent actors e = (u, u'), with u having a production rate  $r_{out}^e = 4$ , u' a consumption rate  $r_{in}^e = 1$  and a parallelisation factor  $\alpha(e) = 4$ . This can be interpreted in multiple ways; tokens produced by a single firing of u will be consumed either by four firings of u', or two firings with double duration of that actor or by a single firing with quadruple duration.

Generally SDF and split-join models have no timing information or model the size of data exchanged between actors. Nevertheless, such information is important for hard real-time systems and WCET estimation. Thus, as in [105], we model an application as an annotated split-join graph, as follows:

**Definition 2.3.5** (Application Model). An application model is an annotated well-formed split-join graph  $A = (\mathcal{U}, \mathcal{E}, \alpha, \delta_{iso}, \sigma)$  where:

- $\mathcal{U}$  is the set of computation *actors*

- $\mathcal{E} \subseteq \mathcal{U} \times \mathcal{U}$  is the set of *FIFO channels*

- $\alpha: \mathcal{E} \to \mathbb{Q}_+$  is the parallelisation function

- $\delta_{iso}: \mathcal{U} \to \mathbb{N}_+$  is the WCET in isolation function which represents the *worst-case* execution time  $\delta_{iso}(u)$  of single firing of an actor  $u \in \mathcal{U}$  when executed in isolated environment with no interference

- $\sigma: \mathcal{E} \cup \mathcal{E}^{-1} \to \mathbb{N}_0$  is the *data-size* function, representing the memory requests each actor firing performs to FIFO *e*. That is, for a FIFO e = (u, u') of two actors  $u, u' \in \mathcal{U}$  then  $\sigma(u, u') = r_{out}^e * tk$  is the amount of memory requests that a single firing of *u* will perform when producing tokens of size *tk* Similarly,  $\sigma(u', u) = r_{in}^e * tk$  is the amount of memory requests that a single firing of *u'* will perform when consuming tokens produced by *u*

#### 2.3.2 System Model

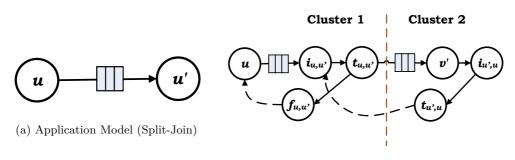

While such a model is sufficient to describe the execution of an application on a multiprocessor architecture, it does not fit architectures that have a NoC interconnect, as it does not capture the behavior of the NoC. A faithful model for the execution of an application on a generic architectures should account for the NoC transfers.

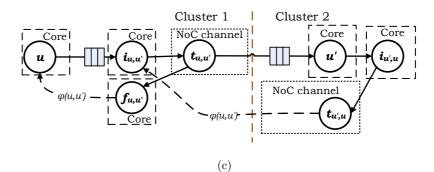

For this reason additional actors have to be introduced in the model. These are called *communication* actors, and model the three phases of a NoC communication. An *inter*cluster data-exchange between actors u and u' consists of:

- 1. <u>the NoC initialisation</u>: where a core configures the NoC I/F with the length of the data-transfer along with the base memory addresses from where to fetch and where to deposit the data and the NoC channels that should be used for the transfer.

- the NoC transfer: during which the NoC channel fetches the data from the memory, forms the packets and forwards them to the destination cluster over the NoC. The NoC I/F of the target cluster receives the data and places them in the destination memory.

- 3. <u>the NoC finalisation</u>: where the core that initialised the transfer polls the NoC interface to check if all the data have been transferred, so as to release the memory space occupied by the data.

(b) System model (Split-Join)

Figure 2.12 – Example of a system model

The worst-case duration of the NoC initialisation and finalisation is assumed to be constant, while the duration of the NoC transfer depends on the amount of data and the distance between the source and destination clusters. It is assumed that NoC packets are not lost/dropped or that the WCET in isolation integrates the induced delays from such effects.

Such a system model can faithfully model the behavior of the system in terms of computation and communication. An application model *A* can be transformed into a *system model* if some partial knowledge is available about the mapping of actors. More precisely, to derive the system model, one would have to know in which cluster each actor is going to be executed. As an illustrative example of system model for a producer/consumer application model is illustrated in Figure 2.12. The producer and consumer are executed on different clusters, thus the have to utilise the NoC to exchange data. The dependency relation among the original actors and the, newly added, communication actors protect the FIFOs. Further details will be presented in Section 4 were the precise transformation is formally defined.

A consistent split-join graph  $S = (\mathcal{U}, \mathcal{E}, \alpha, \delta_{iso}, \sigma)$  that faithfully models the behavior of the system is called *system model*. Given a system model S, the corresponding execution model can be derived, which will be used for our interference-sensitive WCET analysis.

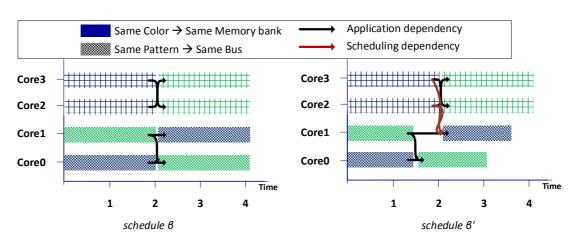

#### 2.3.3 Deployment