# Fabrication, Characterization and Integration of Resistive Random Access Memories

#### THÈSE Nº 8097 (2017)

PRÉSENTÉE LE 7 NOVEMBRE 2017

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR

LABORATOIRE DE SYSTÈMES MICROÉLECTRONIQUES

PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

Jury SANDRINI

acceptée sur proposition du jury:

Dr J.-M. Sallese, président du jury Prof. Y. Leblebici, directeur de thèse Dr A. Sebastian, rapporteur Dr K. H. Kyung, rapporteur Prof. G. De Micheli, rapporteur

Nullius in verba.

— Epistle, Orace

To my family...

### **Acknowledgements**

First, I would like to express my gratitude to my advisor Prof. Yusuf Leblebici for giving me the opportunity to work in his lab and for always allowing me to explore new technologies and paths. He encouraged me to try new ideas, without ever complaining about my clean room expenses.

I would like also to thank the jury members, Prof. Giovanni De Micheli and Prof. Jean-Michel Sallese from EPFL, Dr. Abu Sebastian from IBM Zurich and Dr. Kye Hyun Kyung from Samsung Electronics, for their useful feedbacks which helped in improving this manuscript.

This work would not have been possible without the precious help of several people. I am particularly grateful to the master students I had the opportunity to supervise: Michele Pezzarossa, for his work on single memory cells, Marios Barlas, for the e-beam and etching process development, and Eleonora Testa, for her work in CMOS integration. Moreover, I wish to thank Igor Krawczuk for the development of the Python library and Sebastian Blanc for the probe station automatization. I would like to express my gratitude to Elmira Shahrabi for all the useful discussions we had in these years. I am also extremely grateful to Maxime Thammasack and Prof. Pierre-Emmanuel Gaillardon for their precious help, guidance and comments during the first years of this work. I thank Michail Zervas for the fruitful discussions on fabrication processes. Moreover, I wish to thank Anna Krammer and Prof. Andreas Schueler for the depositions of VO<sub>2</sub>, Mahmoudand Hadad and Prof. Paul Muralt for the depositions of CGO ans YSZ.

The major part of this work was accomplished in the EPFL-CMi clean room. I would like to thank all the clean room staff for their guidance and support, particularly Cyrille Hibert, Didier Bouvet, Zdenek Benes, Patrick Madliger, Remy Juttin, Giovanni Monteduro, Giancarlo Corradini and Anthony Guillet.

Additionally, I would like to thank all former and current members of LSM. Special thank goes to my office-mates Cosimo and Jonathan for their friendships and for all the laughs we had over the years. I would like to thank Elmira for her patience and support. Thanks to the LSM staff, Sylvain, Melinda, Prof. Alexandre Schmid and Prof. Alain Vachoux, for their professionalism and dedication – this lab could not work without you – and to my colleagues Clemens, Kiarash, Navid, Sebastian, Can, Selman, Seniz, Gain, Radisav, Nikola, Davide, Alessandro for all the funny and joyful moments we shared.

Thanks to Mariazel, Emanuele, Niccolo, Jacopo, Rachele, Luca Baldassarre, Luca Pirro, Morgane, Mino, Raffaele, Ioulia and Valentine for their friendship and for the moments spent together.

#### Acknowledgements

I also wish to thanks all the Samsung friends who helped during this work: Doohyun Kim, Wook Ghee (Tony) Hahn, Woo Yeong (Bruno) Cho, Jin Lee (KJ) Kwang, Oh Suk Kwon, Chi-Weon (Jason) Yoon and Hyangja (Elen) Yang.

Last but foremost, I am extremely thankful to my parents, Oscar and Ines, my sister, Anais, and other family members who have always believed in me and supported my studies with patience and encouragement.

Lausanne, 20 September 2017

J. S.

### **Abstract**

The functionalities and performances of today's computing systems are increasingly dependent on the memory block. This phenomenon, also referred as the Von Neumann bottleneck, is the main motivation for the research on memory technologies. Despite CMOS technology has been improved in the last 50 years by continually increasing the device density, today's mainstream memories, such as SRAM, DRAM and Flash, are facing fundamental limitations to continue this trend. These memory technologies, based on charge storage mechanisms, are suffering from the easy loss of the stored state for devices scaled below 10 nm. This results in a degradation of the performance, reliability and noise margin. The main motivation for the development of emerging non volatile memories is the study of a different mechanism to store the digital state in order to overcome this challenge. Among these emerging technologies, one of the strongest candidate is *Resistive Random Access Memory* (ReRAM), which relies on the formation or rupture of a conductive filament inside a dielectric layer.

This thesis focuses on the fabrication, characterization and integration of ReRAM devices. The main subject is the qualitative and quantitative description of the main factors that influence the resistive memory electrical behavior. Such factors can be related either to the memory fabrication or to the test environment.

The first category includes variations in the fabrication process steps, in the device geometry or composition. We discuss the effect of each variation, and we use the obtained database to gather insights on the ReRAM working mechanism and the adopted methodology by using statistical methods.

The second category describes how differences in the electrical stimuli sent to the device change the memory performances. We show how these factors can influence the memory resistance states, and we propose an empirical model to describe such changes. We also discuss how it is possible to control the resistance states by modulating the number of input pulses applied to the device.

In the second part of this work, we present the integration of the fabricated devices in a CMOS technology environment. We discuss a Verilog-A model used to simulate the device characteristics, and we show two solutions to limit the sneak-path currents for ReRAM crossbars: a dedicated read circuit and the development of selector devices. We describe the selector fabrication, as well as the electrical characterization and the combination with our ReRAMs in a 1S1R configuration. Finally, we show two methods to integrate ReRAM devices in the BEoL of CMOS chips.

#### Acknowledgements

Key words: nanotechnology, emerging memory technology, non volatile memory, resistive random access memory, ReRAM, bipolar resistive switching, selector device, CMOS integration.

### **Sommario**

Nei moderni sistemi di calcolo le funzionalità e le prestazioni dipendono sempre più dal blocco di memoria. Questo fenomeno, chiamato anche "Von Neumann bottleneck", è la motivazione principale che anima la ricerca di nuove tecnologie. Nonostante la tecnologia CMOS ha continuamente evoluto negli ultimi 50 anni aumentando la densità dei dispositivi, le principali tipologie di memorie, come SRAM, DRAM e Flash, stanno affrontando dei limiti fondamentali che impediscono di continuare questo ritmo d'innovazione. Queste tecnologie di memoria, basate sui meccanismi di accumulo di carica, soffrono della facile perdita dello stato memorizzato per dispositivi scalati sotto i 10 nm. Ciò comporta un degrado del rendimento, dell'affidabilità e del margine di rumore. La motivazione principale per lo sviluppo di nuovi tipi di memorie non volatili è quindi lo studio di nuovi meccanismi per memorizzare lo stato digitale che permetterebbero di superare queste difficoltà. Tra le tecnologie emergenti piu promettenti ci sono le *Memorie Resistive ad Accesso Casule* (ReRAM), il cui meccanismo di commutazione é basato sulla formazione o rottura di un filamento conduttivo all'interno di uno strato dielettrico.

Questa tesi si concentra sulla fabricazione, caratterizzazione e integrazione di ReRAM. Il soggetto principale di questo lavoro è la descrizione qualitativa e quantitativa dei principali fattori che influenzano il comportamento elettrico delle memorie resistive. Tali fattori possono essere collegati alla fabbricazione della memoria stessa o ai parametri usati duarnte la caratterizzazione elettrica.

La prima categoria include variazioni nei passaggi del processo di fabbricazione, nella geometria o nella composizione del dispositivo. In questo lavoro, discutiamo nei dettagli gli effetti di ogni variazione. Inoltre utilizziamo i dati ottenuti per ottenere delle informazioni sul meccanismo di funzionamento delle ReRAM e sulla metodologia adottata utilizzando dei metodi statistici.

La seconda categoria descrive come le differenze negli stimoli elettrici inviati al dispositivo modificano le prestazioni della memoria. Mostriamo come questi fattori possono influenzare gli stati di resistenza della memoria e proponiamo un modello empirico per descrivere tali cambiamenti. Discutiamo anche come è possibile controllare gli stati di resistenza modulando il numero di impulsi di ingresso applicati al dispositivo.

Nella seconda parte di questo lavoro, presentiamo l'integrazione dei dispositivi fabbricati in un sistema di tecnologia CMOS. Discutiamo un modello Verilog-A utilizzato per emulare le caratteristiche dei dispositivi, e mostriamo due soluzioni per limitare le correnti parassite per configurazioni di ReRAM ad alta densità: un circuito di lettura dedicato e lo sviluppo

#### Acknowledgements

di dispositivi di selezione. Descriviamo quindi la fabbricazione del selettore, così come la caratterizzazione elettrica e la combinazione con le ReRAM in una configurazione 1S1R. Infine mostriamo due metodi per integrare i dispositivi ReRAM nei metalli superiori di chip CMOS.

Parole chiave: nanotecnologia, nuove tecnologie di memoria, memorie non volatili, memorie resistive ad accesso casuale, ReRAM, commutazione resistiva bipolare, selettori, integrazione CMOS.

# Contents

| Ac | knov  | wledge  | ments                               | i   |

|----|-------|---------|-------------------------------------|-----|

| Ał | ostra | ct (Eng | dish/Italiano)                      | iii |

| Li | st of | Figure  | S                                   | хi  |

| Li | st of | Tables  |                                     | xix |

| Li | st of | Acrony  | vms                                 | xxi |

| 1  | Intr  | oducti  | on                                  | 1   |

|    | 1.1   | Thesi   | s goal                              | 4   |

|    | 1.2   |         | s overview                          |     |

| 2  | ReR   | AM in   | troduction                          | 7   |

|    | 2.1   | Memo    | ory technology overview             | 7   |

|    | 2.2   | Emer    | ging memory technologies            | 9   |

|    |       | 2.2.1   | Energy efficiency                   | 11  |

|    |       | 2.2.2   | Data integrity                      | 11  |

|    |       | 2.2.3   | Switching time                      | 14  |

|    |       | 2.2.4   | Performance comparison              | 14  |

|    | 2.3   | Resist  | ive Random Access Memories          | 14  |

| 3  | Dev   | ice fab | rication                            | 21  |

|    | 3.1   | Gener   | ral considerations                  | 21  |

|    | 3.2   | Fabrio  | cation process types                | 23  |

|    | 3.3   | Mask    | design and fabrication              | 25  |

|    | 3.4   | Wafer   | -based process                      | 26  |

|    |       | 3.4.1   | Substrate                           | 29  |

|    |       | 3.4.2   | Bottom electrode deposition         | 29  |

|    |       | 3.4.3   | Bottom electrode lithography        | 29  |

|    |       | 3.4.4   | Bottom electrode etching            | 32  |

|    |       | 3.4.5   | Resist strip                        | 37  |

|    |       | 3.4.6   | Passivation deposition              | 38  |

|    |       | 3.4.7   | Passivation lithography and etching | 38  |

#### **Contents**

|   |     | 3.4.8 Switching oxide deposition                                 | 39  |

|---|-----|------------------------------------------------------------------|-----|

|   |     | 3.4.9 Buffer layer and top electrode deposition                  | 43  |

|   |     | 3.4.10 Top electrode lithography and etching                     | 44  |

|   | 3.5 | Die-based process                                                | 45  |

|   |     | 3.5.1 Die preparation                                            | 45  |

|   |     | 3.5.2 Switching oxide, buffer layer and top electrode deposition | 46  |

|   |     | 3.5.3 Top electrode lithography                                  | 46  |

|   |     | 3.5.4 Top electrode etching                                      | 47  |

|   | 3.6 | Shadow mask-based process                                        | 50  |

|   |     | 3.6.1 Shadow mask fabrication                                    | 50  |

|   |     | 3.6.2 Die preparation and device fabrication                     | 53  |

|   | 3.7 | E-beam lithography process                                       | 53  |

|   |     | 3.7.1 E-beam process: first version                              | 54  |

|   |     | 3.7.2 E-beam process: second version                             | 57  |

|   | 3.8 | Summary                                                          | 61  |

| 4 | Dev | rice characterization: DC analysis                               | 63  |

|   | 4.1 | •                                                                | 63  |

|   | 4.2 | Process variations and measured ReRAM parameters                 | 64  |

|   | 4.3 | Device DC characteristics                                        | 68  |

|   | 4.4 | Influence of the process modifications on the ReRAM parameters   | 72  |

|   |     | 4.4.1 Process type                                               | 73  |

|   |     | 4.4.2 Resistive material                                         | 76  |

|   |     | 4.4.3 Buffer layer                                               | 76  |

|   |     | 4.4.4 Passivation                                                | 80  |

|   |     | 4.4.5 Top electrode etching                                      | 82  |

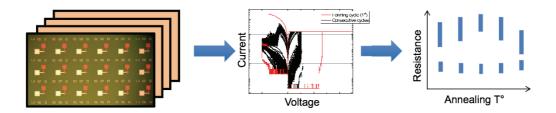

|   |     | 4.4.6 Post metallization annealing                               | 84  |

|   |     | 4.4.7 VIA size                                                   | 86  |

|   |     | 4.4.8 Bottom electrode, top electrode and capping layer          | 88  |

|   | 4.5 | Correlation between the ReRAM characteristics                    | 89  |

|   |     | 4.5.1 Forming, set and reset voltage relation                    | 90  |

|   |     | 4.5.2 Voltages and resistance states relation                    | 94  |

|   |     | 4.5.3 All switching parameters relation                          | 97  |

|   | 4.6 |                                                                  | 97  |

|   | 4.7 | Summary                                                          | 101 |

| 5 | Dev | rice characterization: pulse analysis                            | 05  |

|   | 5.1 | Pulse characterization methodology                               | 105 |

|   | 5.2 | Test parameter variations and measured ReRAM parameters          | 106 |

|   | 5.3 | Device pulse characteristics                                     | 111 |

|   | 5.4 | Failure analysis                                                 | 114 |

|   | 5.5 | Influence of the test parameters on the ReRAM resistance states  | 121 |

|   |     | 5.5.1 Qualitative description                                    | 122 |

|    |       | Cont                                                | ents |

|----|-------|-----------------------------------------------------|------|

|    |       |                                                     |      |

|    |       | 5.5.2 Analysis of variance                          |      |

|    |       | 5.5.3 Empirical model                               |      |

|    | 5.6   | Pulse number modulation                             | 133  |

|    | 5.7   | Summary                                             | 137  |

| 6  | CM    | OS system integration                               | 139  |

|    | 6.1   | Background                                          | 139  |

|    | 6.2   | Verilog-A model                                     | 141  |

|    | 6.3   | Circuit strategies for sneak-path current reduction | 143  |

|    | 6.4   | Selector devices                                    | 147  |

|    |       | 6.4.1 Introduction                                  | 148  |

|    |       | 6.4.2 Fabrication                                   | 152  |

|    |       | 6.4.3 Electrical characterization                   | 153  |

|    | 6.5   | ReRAM chip-level integration                        | 156  |

|    |       | 6.5.1 MMC-based approach                            | 156  |

|    |       | 6.5.2 Top-metal integration approach                | 161  |

|    | 6.6   | Summary                                             | 163  |

| 7  | Con   | clusion and future work                             | 165  |

| A  | Cha   | racterization methodology                           | 169  |

|    | A.1   | Electrical test setups                              | 169  |

|    | A.2   | Data treatment functions                            | 173  |

|    | A.3   | Measurement database                                | 176  |

|    | A.4   | Data analysis functions                             | 177  |

|    |       | A.4.1 Pearson's correlation coefficient             | 177  |

|    |       | A.4.2 Analysis of variance                          | 179  |

|    |       | A.4.3 Data regression                               | 182  |

| В  | SKI   | LL code for mask layout                             | 185  |

| C  | Sing  | gle cell process flow                               | 191  |

| Bi | bliog | graphy                                              | 210  |

**Curriculum Vitae**

211

# List of Figures

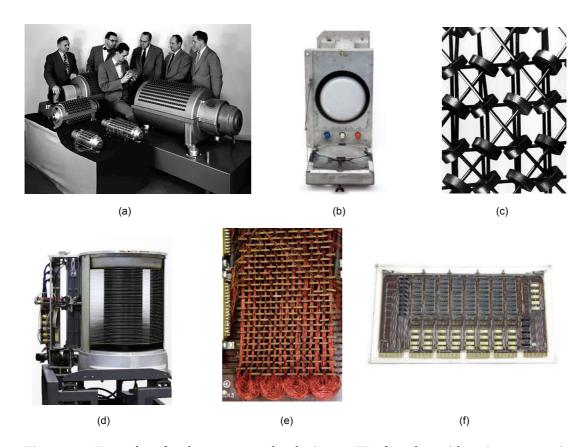

| 1.1 | Examples of early memory technologies: (a) ERA founders with various magnetic drum memories, (b) Manchester Mark I Williams-Kilburn tube, (c) detail of Whirlwind core memory, (d) RAMAC 305 disks and head assembly, (e) close up shot of Apollo Guidance Computer read-only rope memory, (f) DEC VAX memory board with Intel 1103 memory chips. Images taken from [2] | 2  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

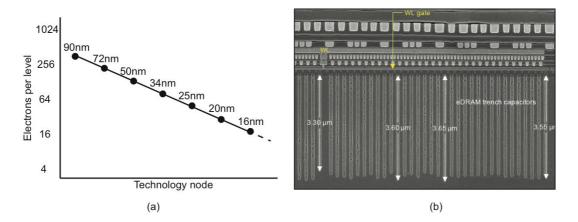

| 2.1 | Charge based memories: (a) evolution of electrons required per level in NAND technology (adapted from [4]) and (b) capacitor trenches in IBM Power 7+ e-DRAM (32 nm) [5]                                                                                                                                                                                                | 8  |

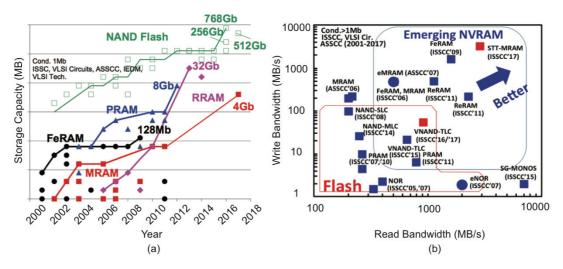

| 2.2 | (a) Memory capacity trends and (b) read/write bandwidth comparison for NVMs (adapted from [7])                                                                                                                                                                                                                                                                          | 10 |

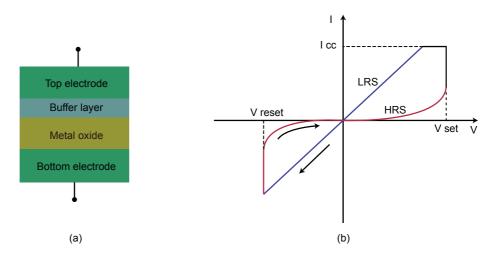

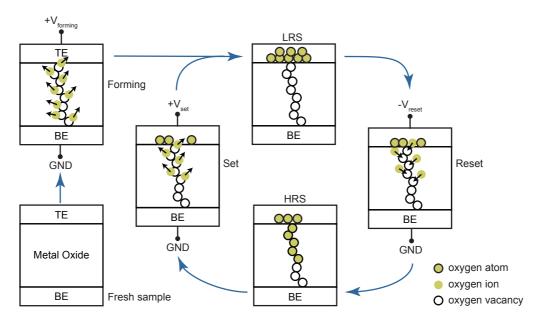

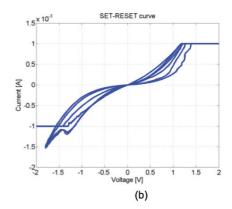

| 2.3 | (a) Schematic representation of the ReRAM structure and (b) I-V curve                                                                                                                                                                                                                                                                                                   | 17 |

| 2.4 | Schematic representation of the ReRAM switching mechanism (adapted from                                                                                                                                                                                                                                                                                                 |    |

| 2.1 | [38])                                                                                                                                                                                                                                                                                                                                                                   | 18 |

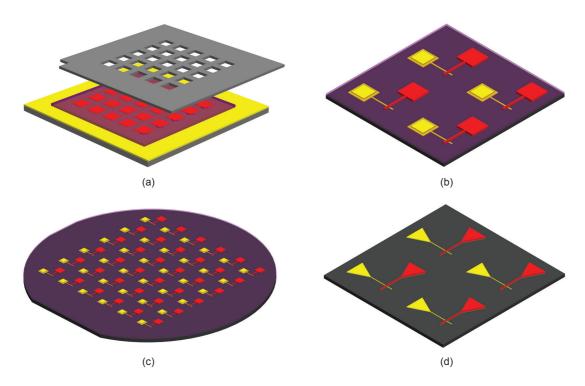

| 3.1 | Schematic representation of the developed fabrication process flows: (a) shadow mask-based process, (b) die process, (c) wafer process and (d) e-beam process.                                                                                                                                                                                                          | 23 |

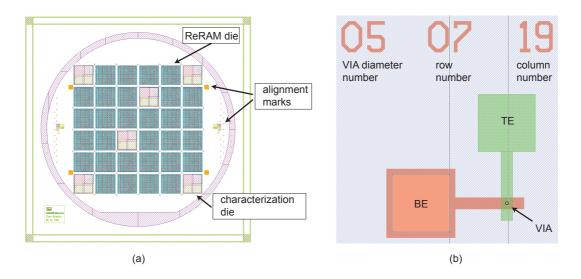

| 3.2 | Mask layout for (a) wafer scale process and (b) parametric ReRAM cell with                                                                                                                                                                                                                                                                                              |    |

|     | numbers for the via dimension, the row and the column position of the device.                                                                                                                                                                                                                                                                                           | 26 |

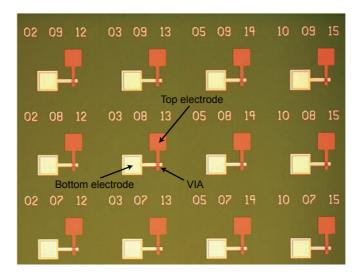

| 3.3 | Summary of the wafer-based device fabrication steps                                                                                                                                                                                                                                                                                                                     | 27 |

| 3.4 | ReRAM device micrograph                                                                                                                                                                                                                                                                                                                                                 | 27 |

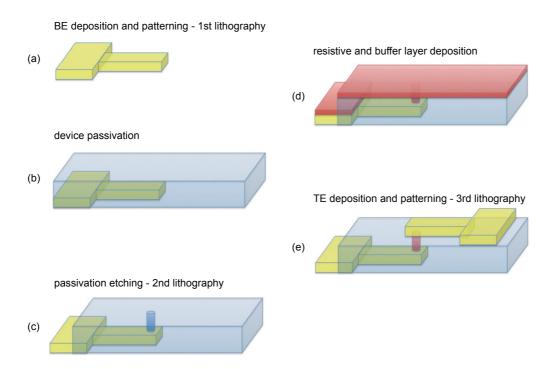

| 3.5 | Schematic representation of the wafer-process devices: (a) BE deposition and patterning, (b) device passivation, (c) passivation etching, (d) resistive and buffer layer deposition and (e) TE deposition and patterning                                                                                                                                                | 28 |

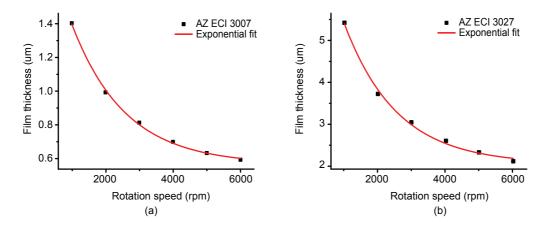

| 3.6 | Spincurve for (a) AZ ECI 3007 and (b) AZ ECI 3027 resists obtained from the CMI                                                                                                                                                                                                                                                                                         |    |

|     | website [45]                                                                                                                                                                                                                                                                                                                                                            | 30 |

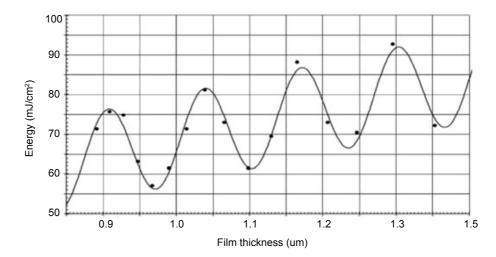

| 3.7 | Example of g-line swing curve for AZ 3312 Photoresist on Si ( $\lambda$ =435 nm). Taken                                                                                                                                                                                                                                                                                 |    |

|     | from product datasheet [46]                                                                                                                                                                                                                                                                                                                                             | 31 |

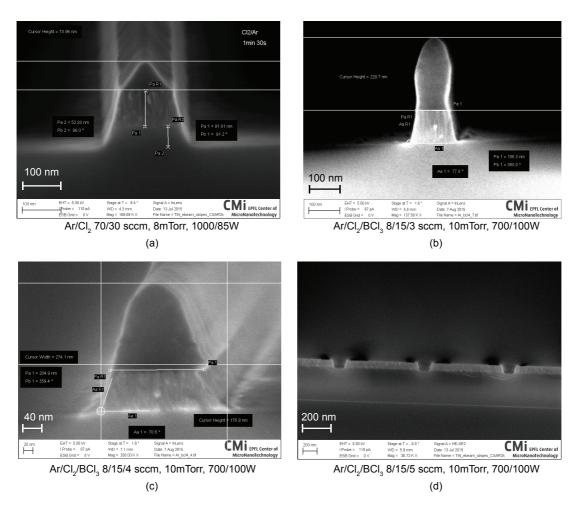

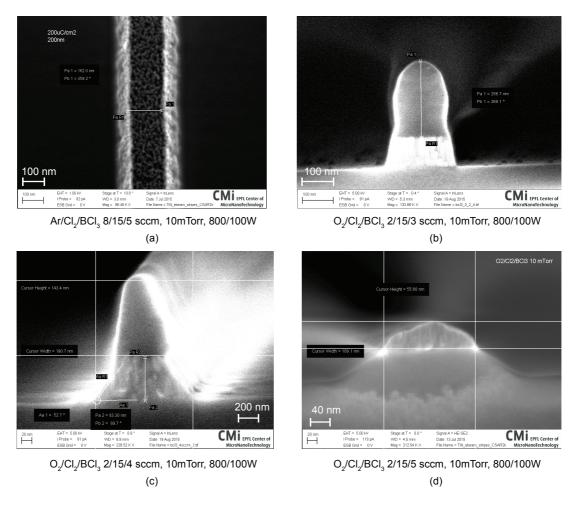

| 3.8 | Scanning electron micrograph for TiN etching test structures under $Ar/Cl_2$ and                                                                                                                                                                                                                                                                                        |    |

|     | $Ar/Cl_2/BCl_3$ chemistries                                                                                                                                                                                                                                                                                                                                             | 34 |

| 3.9 | Scanning electron micrograph for TiN etching test structures under $Ar/Cl_2/BCl_3$ and $O/Cl_2/BCl_3$ chemistries                                                                                                                                                                                                                                                       | 35 |

|     | and 5, 5,2,2013 enomination                                                                                                                                                                                                                                                                                                                                             | 50 |

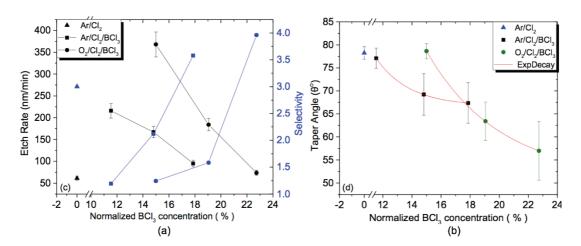

| 3.10 | (a) Etch rate and selectivity with respect to photoresist for the tested TiN etch-            |    |

|------|-----------------------------------------------------------------------------------------------|----|

|      | ing chemistries and (b) sidewall profile angle trends for TiN with CSAR-62 for                |    |

|      | $Ar/Cl_2/BCl_3$ and $O/Cl_2/BCl_3$ chemistries                                                | 36 |

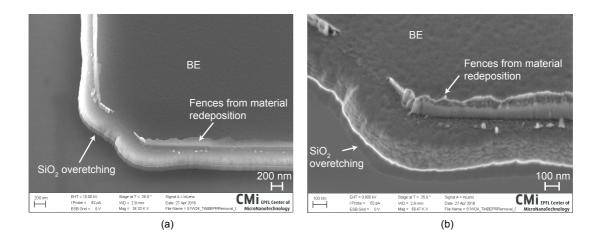

| 3.11 | (a) TiN BE after etching and photoresist removal step and (b) close-up image                  | 38 |

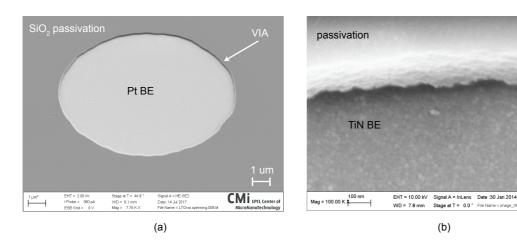

| 3.12 | (a) SiO <sub>2</sub> VIA for Pt BE device after wet etching and photoresist removal step, (b) |    |

|      | close-up image of the VIA for a TiN BE device                                                 | 40 |

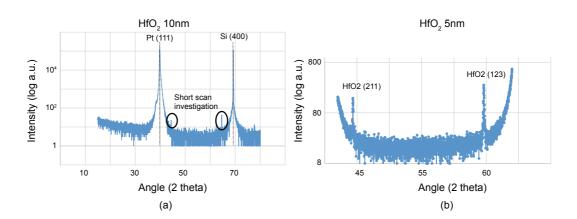

| 3.13 | XRD analysis for the $HfO_2$ material deposited by ALD. (a) Shows two major peaks             |    |

|      | corresponding to the Pt (111) and Si (400) substrates, and two minor ones, which              |    |

|      | have been investigated by a high resolution scan. (b) Shows that the peaks                    |    |

|      | corresponds to HfO2 (211) and HfO2 (123).<br>                                                 | 41 |

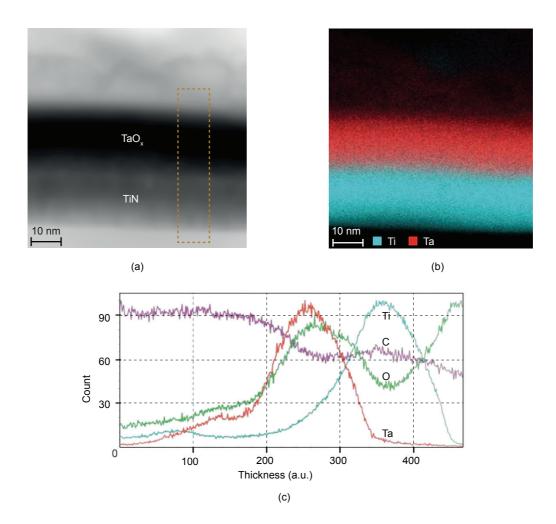

| 3.14 | Material analysis for the $TiN-TaO_2$ material stack showing (a) TEM micrograph,              |    |

|      | (b) EDX analysis for the Ti and Ta atoms and (c) line profile. The line profile               |    |

|      | has been obtained along the line scan shown in (a). The ${\rm TaO_2}$ layer has been          |    |

|      | deposited by reactive sputtering from a ${\rm Ta_2O_5}$ target at 1000 W, 15 sccm Ar, and     |    |

|      | 3 sccm O                                                                                      | 42 |

| 3.15 | Summary of the die-based device fabrication steps                                             | 45 |

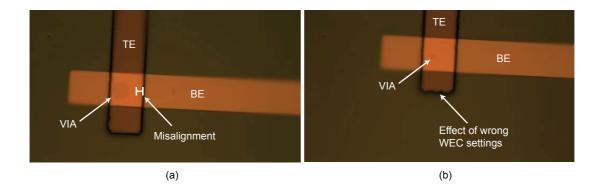

| 3.16 | Micrograph of the TE after the TiN etching: (a) shows the misalignment for                    |    |

|      | a 10 $\mu m$ VIA device, which is about 5 um, (b) shows the effects of wrong WEC              |    |

|      | settings for a 2 $\mu m$ device                                                               | 48 |

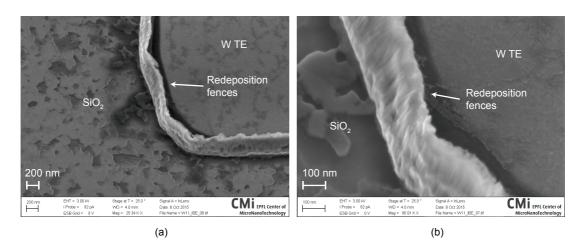

| 3.17 | (a) Scanning electron micrograph of the W TE after the IBE etching and (b)                    |    |

|      | close-up image                                                                                | 49 |

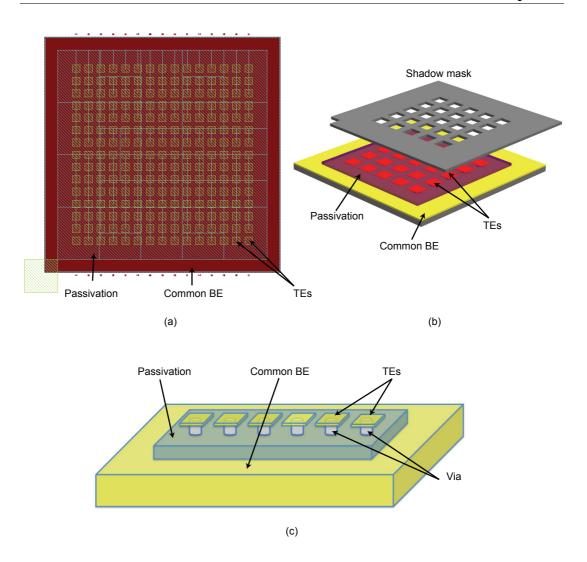

| 3.18 | (a) Mask layout for the shadow mask process die, (b) schematic representation                 |    |

|      | of the TE patterning by shadow mask and (c) schematic representation of the                   |    |

|      | final ReRAM devices                                                                           | 51 |

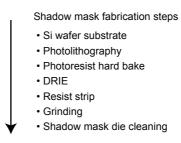

|      | Summary of the shadow mask fabrication steps                                                  | 51 |

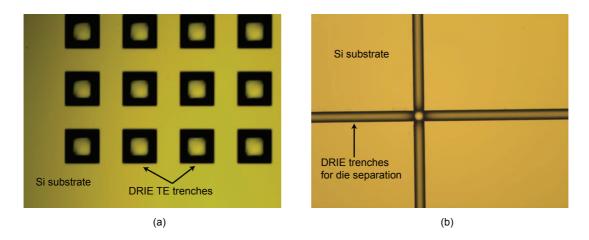

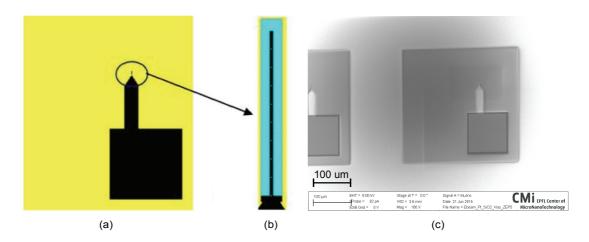

| 3.20 | Micrograph of the shadow mask after DRIE and resist strip: (a) TE trenches for                |    |

|      | the TE openings and (b) trenches for the die separations                                      | 52 |

|      | Summary of the shadow mask-based device fabrication steps                                     | 53 |

|      | Summary of the fabrication steps for the first e-beam process                                 | 54 |

| 3.23 | (a) Exposure pattern for the large BE features (in yellow color), (b) exposure                |    |

|      | pattern for the BE features below 1 $\mu m$ (in blue color) and (c) transferred pattern       |    |

|      | after the BE etching and the passivation opening                                              | 55 |

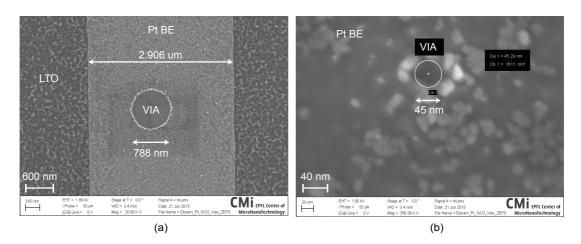

| 3.24 | (a) 780 nm and (b) 45 nm VIAs after LTO dry etching                                           | 57 |

| 3.25 | Summary of the second e-beam process fabrication steps                                        | 58 |

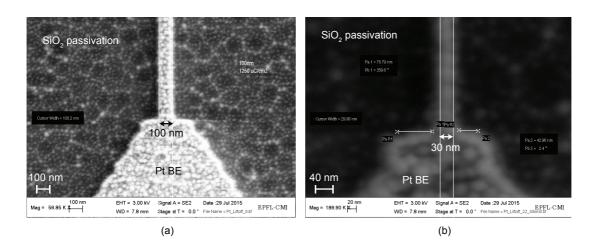

| 3.26 | Crosspoint devices after Pt lift off: (a) 100 nm BE and (b) 30 nm BE                          | 60 |

| 3.27 | Crosspoint devices after the TE lithography: (a) 30 nm TE patterning and (b)                  |    |

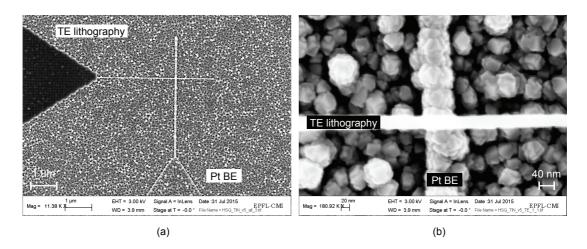

|      | detail view                                                                                   | 61 |

| 4.1  | Schematization of the DC characterization methodology. DC tests are used to                   |    |

|      | characterize ReRAMs fabricated with different process variations with a stan-                 |    |

|      | dardized test procedure that is common for all the devices. The goal is to study              |    |

|      | how the fabrication steps influence the ReRAM behavior                                        | 64 |

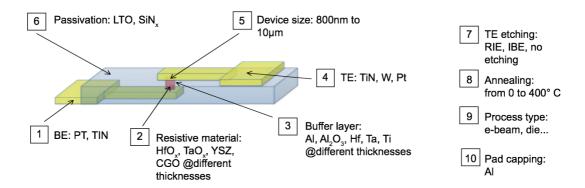

| 4.2  | Schematic representation of the process variations analyzed with the DC tests.                                                                            | 65 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.3  | Schematic representation of the measured quantities for the DC tests                                                                                      | 65 |

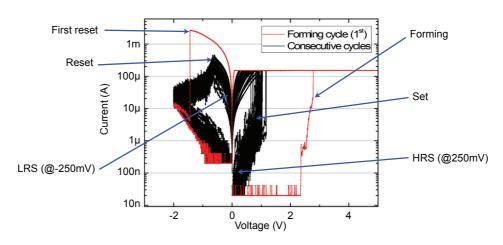

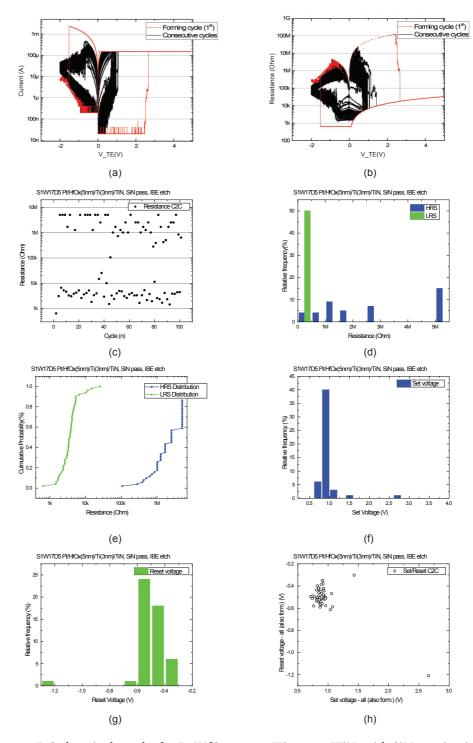

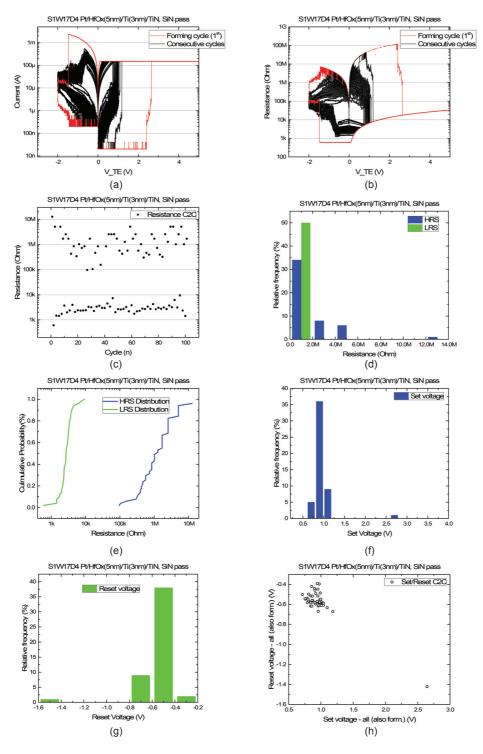

| 4.4  | DC electrical results for Pt/HfO <sub>2</sub> (5 nm)/Ti (3 nm)/TiN, with SiN passivation                                                                  |    |

|      | and IBE for the TE definition: (a) I-V curve, (b) R-V curve, (c) cycle-to-cycle                                                                           |    |

|      | resistance, (d) relative frequency and (e) cumulative probability of the resistance                                                                       |    |

|      | states, relative frequency for the (f) set and (g) reset voltages, (h) set voltage                                                                        |    |

|      | versus reset voltage plot                                                                                                                                 | 69 |

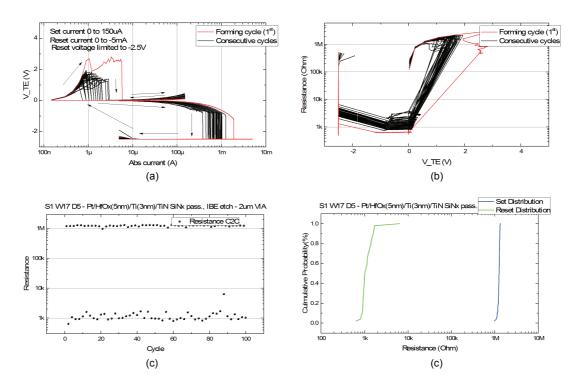

| 4.5  | DC electrical results in current mode for Pt/HfO <sub>2</sub> (5 nm)/Ti (3 nm)/TiN, with                                                                  |    |

|      | SiN passivation and IBE for the TE definition: (a) I-V curve, (b) R-V curve, (c)                                                                          |    |

|      | cycle-to-cycle resistance, (d) cumulative probability of the resistance states                                                                            | 71 |

| 4.6  | Process type influence on the electrical characteristics of $Pt/HfO_2$ (5 nm)/Hf                                                                          |    |

|      | (3 nm)/TiN devices: the boxplots show (a) the forming voltage, (b) the resistance                                                                         |    |

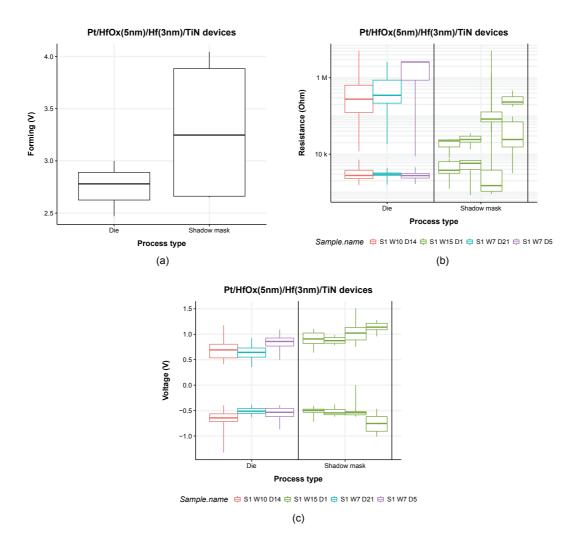

|      | state and (c) the switching voltage measurements                                                                                                          | 74 |

| 4.7  | Results for Pt/HfO <sub>2</sub> (5 nm)/TiN devices devices fabricated with the e-beam                                                                     |    |

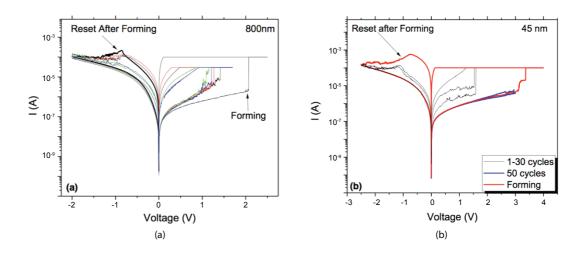

|      | process: (a) 800 nm VIA and (b) 45 nm VIA diameter device                                                                                                 | 75 |

| 4.8  | Resistive material influence on the electrical characteristics of $Pt/x/Hf(3 nm)/TiN$ ,                                                                   |    |

|      | Pt/x/TiN, TiN/x/TiN and Pt/x/Ti (3 nm)/TiN devices. The boxplot shows (a) the                                                                             |    |

|      | forming voltage, (b) the resistance state and (c) the switching voltage measure-                                                                          |    |

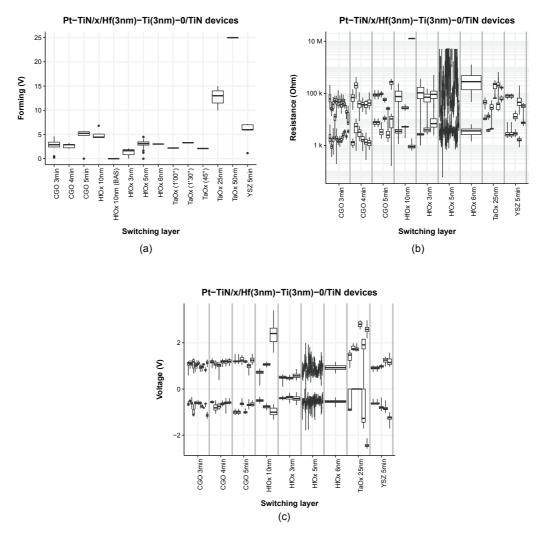

|      | ments                                                                                                                                                     | 77 |

| 4.9  | Buffer layer influence on the electrical characteristics of $Pt/HfO_2$ (3 nm)/x/TiN                                                                       |    |

|      | and Pt/HfO <sub>2</sub> (5 nm)/x/TiN devices. (a) Shows the device representative DC                                                                      |    |

|      | cycles; while the boxplots show (b) the forming voltage, (c) the resistance state                                                                         |    |

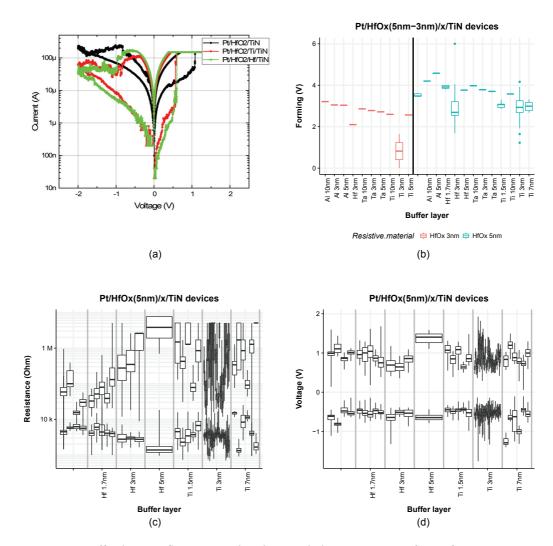

|      | and (d) the switching voltage measurements                                                                                                                | 79 |

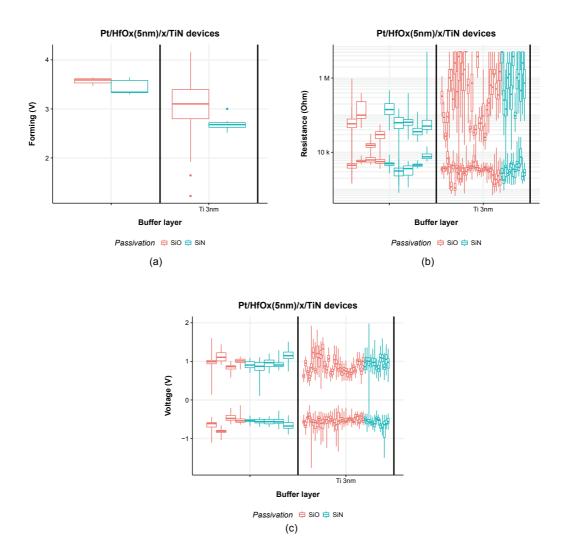

| 4.10 | Passivation influence on the electrical characteristics of $Pt/HfO_2$ (5 nm)/TiN                                                                          |    |

|      | and Pt/HfO $_2$ (5 nm)/Ti (3 nm)/TiN devices. The boxplots show (a) the forming                                                                           |    |

|      | voltage, (b) the resistance state and (c) the switching voltage measurements $$                                                                           | 81 |

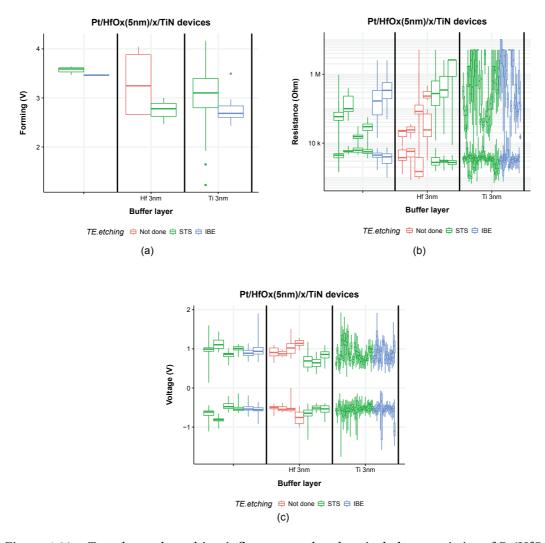

| 4.11 | Top electrode etching influence on the electrical characteristics of $Pt/HfO_2$                                                                           |    |

|      | $(5\text{nm})/\text{TiN},\text{Pt/HfO}_2(5\text{nm})/\text{Hf}(3\text{nm})/\text{TiN}$ and $\text{Pt/HfO}_2(5\text{nm})/\text{Ti}(3\text{nm})/\text{TiN}$ |    |

|      | devices. The boxplots show (a) the forming voltage, (b) the resistance state and                                                                          |    |

|      |                                                                                                                                                           | 83 |

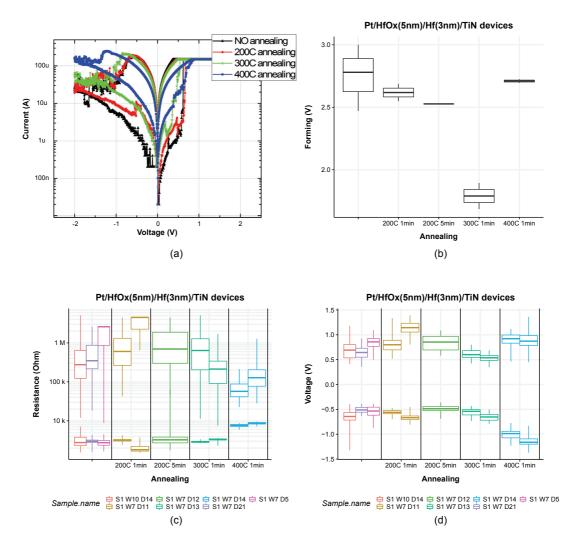

| 4.12 | Annealing influence on the electrical characteristics of Pt/HfO $_2$ (5 nm)/Hf (3 nm)/Til $_2$                                                            | N  |

|      | devices. (a) Shows the device representative DC cycles; while the boxplots show                                                                           |    |

|      | (b) the forming voltage, (c) the resistance state and (d) the switching voltage                                                                           |    |

|      | measurements                                                                                                                                              | 85 |

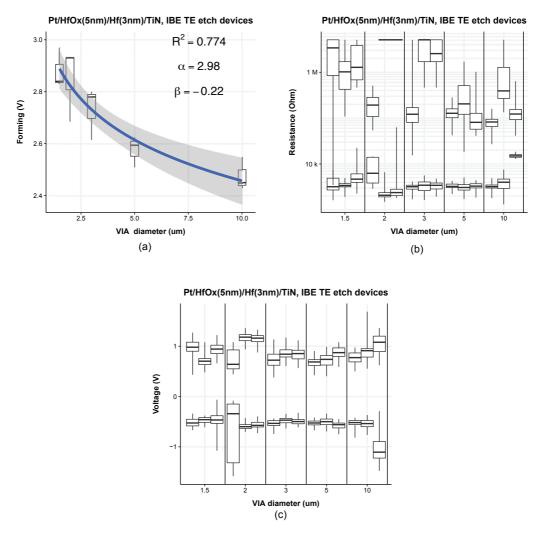

| 4.13 | VIA size influence on the electrical characteristics of Pt/HfO $_2$ (5 nm)/Hf (3 nm)/TiN                                                                  |    |

|      | devices with IBE TE etching. The boxplots show (a) the forming voltage, (b) the                                                                           |    |

|      |                                                                                                                                                           | 87 |

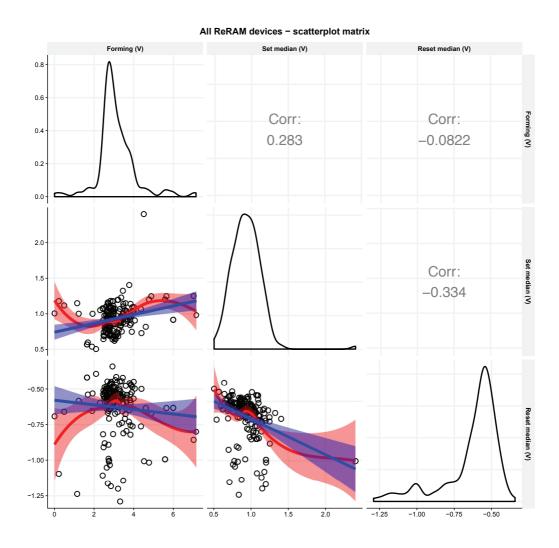

| 4.14 | Correlation analysis between forming, set and reset voltages for all the fabri-                                                                           |    |

|      | cated ReRAM cells. The diagonal elements show the density plots obtained                                                                                  |    |

|      | from the data distribution. The lower elements are the scatterplot matrix plots                                                                           |    |

|      | between forming, set and reset, while the upper elements report the correlation                                                                           |    |

|      | coefficient values                                                                                                                                        | 91 |

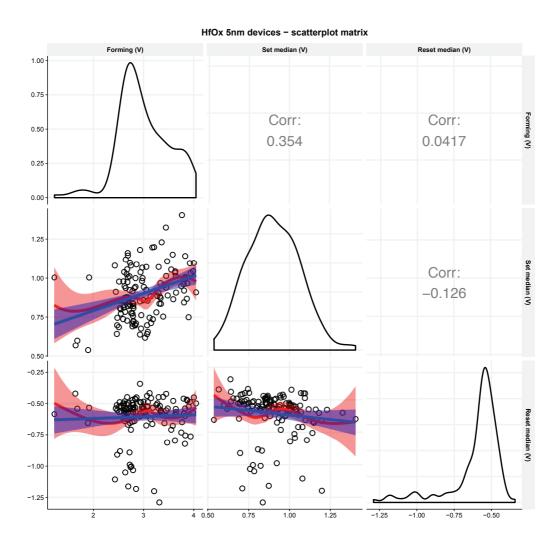

| 4.15 | Correlation analysis between forming, set and reset voltages for the HfO <sub>2</sub> (5 nm) fabricated ReRAM cells. The diagonal elements show the density plots obtained from the data distribution. The lower elements are the scatterplot matrix plots between forming, set and reset, while the upper elements report the correlation |      |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | between forming, set and reset, while the upper elements report the correlation coefficient values                                                                                                                                                                                                                                         | 92   |

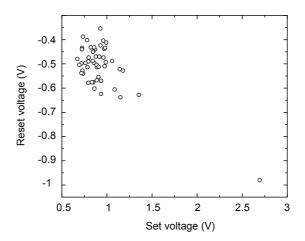

| 4 16 | Cycle-to-cycle relation for set and reset voltage of a Pt/HfO <sub>2</sub> (5 nm)/Ti (3 nm)/TiN                                                                                                                                                                                                                                            | 32   |

| 1.10 | cell with $\mathrm{Si}_3\mathrm{N}_4$ passivation. The bottom right data point shows the forming and                                                                                                                                                                                                                                       | 0.4  |

| 4.17 | the first reset                                                                                                                                                                                                                                                                                                                            | 94   |

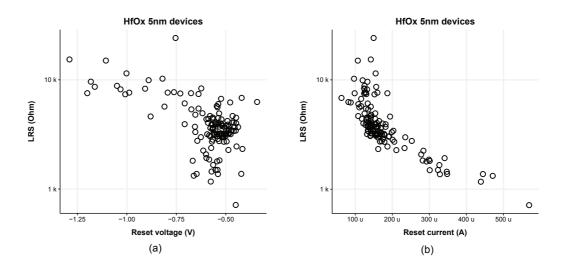

|      | based ReRAMs.                                                                                                                                                                                                                                                                                                                              | 95   |

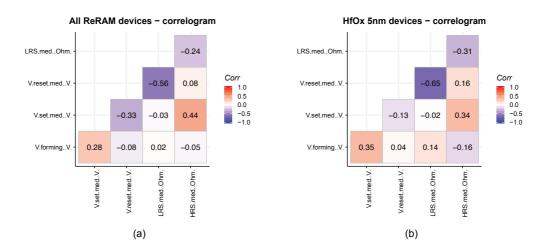

| 4.18 | Correlation analysis between forming, set, reset, LRS and HRS for (a) all the                                                                                                                                                                                                                                                              |      |

| 4.10 | fabricated cells and (b) the HfO <sub>2</sub> (5 nm) based ReRAMs                                                                                                                                                                                                                                                                          | 96   |

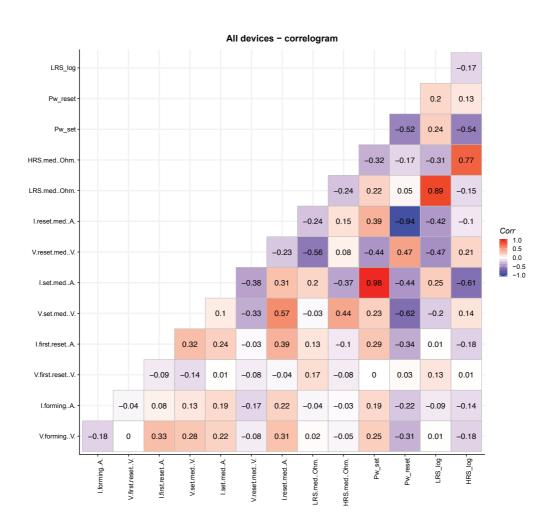

| 4.19 | Correlation analysis between all the measured electrical characteristics for all the fabricated ReRAM cells                                                                                                                                                                                                                                | 98   |

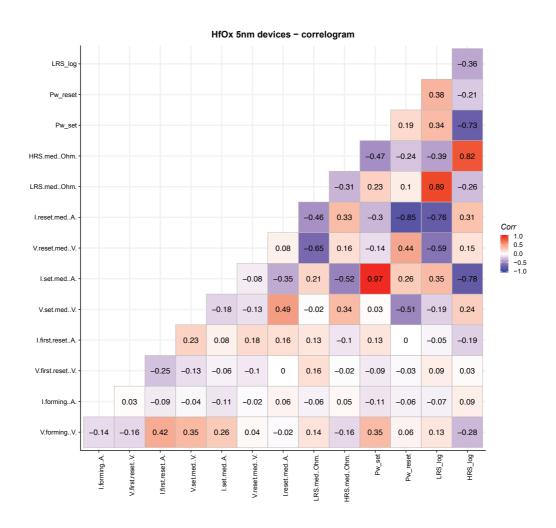

| 4.20 | Correlation analysis between all the measured electrical characteristics for the                                                                                                                                                                                                                                                           |      |

|      | HfO <sub>2</sub> (5 nm) ReRAM cells                                                                                                                                                                                                                                                                                                        | 99   |

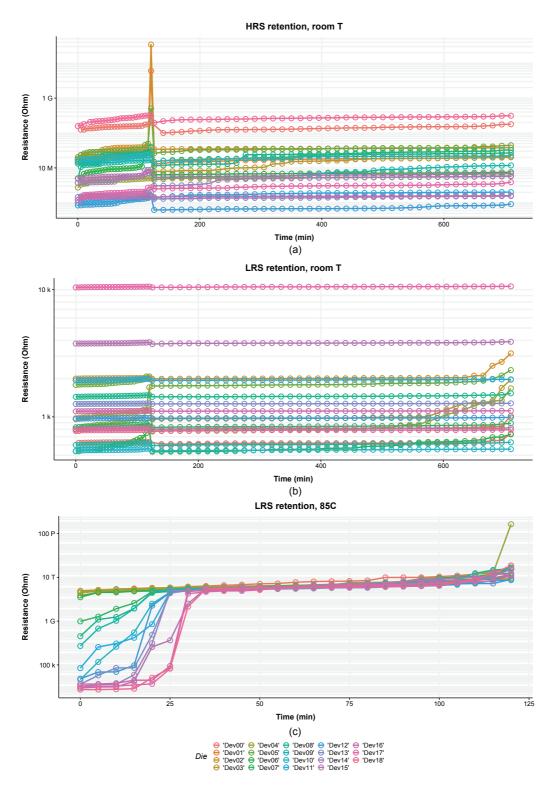

| 4.21 | (a) HRS, (b) LRS and (c) LRS at $85^{\circ}$ C retention tests for Pt/HfO <sub>2</sub> (5 nm)/TiN devices                                                                                                                                                                                                                                  | .100 |

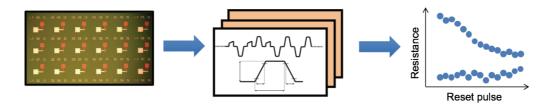

| 5.1  | Schematization of the pulse characterization methodology. Pulse tests are used                                                                                                                                                                                                                                                             |      |

|      | to characterize ReRAMs fabricated from a fixed process flow with pulses with                                                                                                                                                                                                                                                               |      |

|      | different electrical characteristics. The goal is to study how the test parameters                                                                                                                                                                                                                                                         |      |

|      | influence the ReRAM behavior                                                                                                                                                                                                                                                                                                               | 106  |

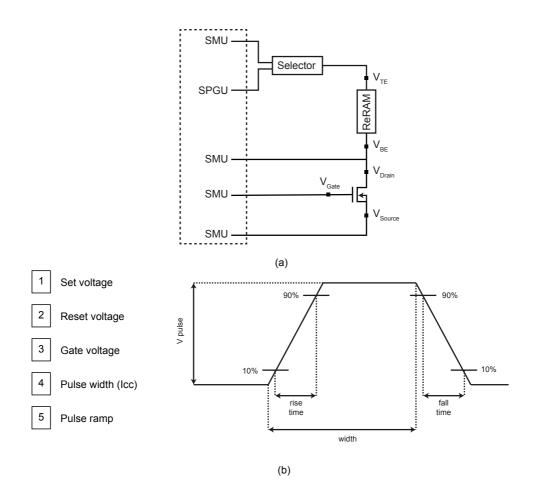

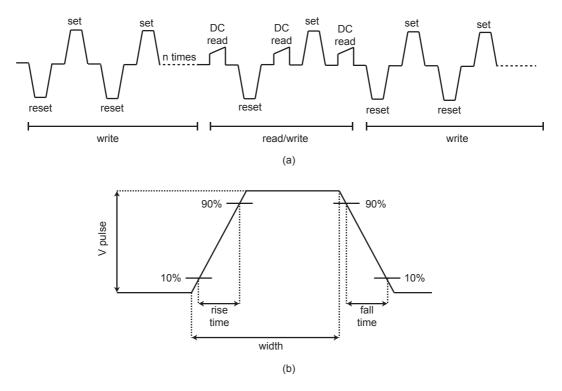

| 5.2  | Schematic representation of (a) pulse test setup and (b) characterization param-                                                                                                                                                                                                                                                           |      |

|      | eters varied during the pulse tests                                                                                                                                                                                                                                                                                                        | 107  |

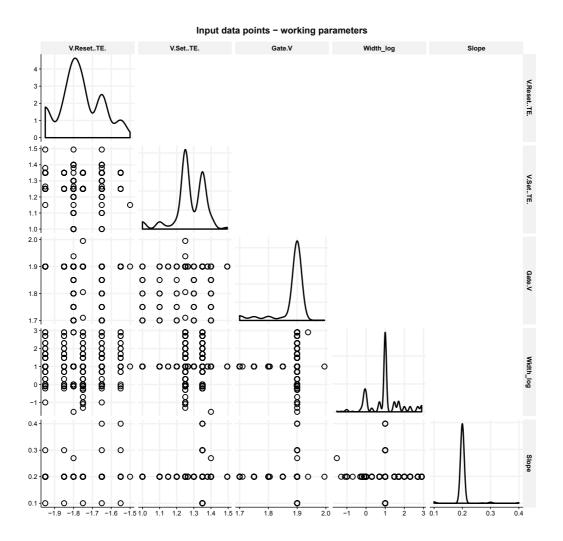

| 5.3  | 1                                                                                                                                                                                                                                                                                                                                          | 109  |

| 5.4  | Scatterplot matrix showing the input domain for the pulse test parameters.                                                                                                                                                                                                                                                                 |      |

|      | The quantities varied during the analysis are the reset voltage, set voltage, gate                                                                                                                                                                                                                                                         |      |

|      | voltage, pulse width and pulse slope. The diagonal elements show the density                                                                                                                                                                                                                                                               |      |

|      | plots obtained from the data distribution, while the lower elements are the                                                                                                                                                                                                                                                                |      |

|      | scatterplot between the modified quantities. The x-axis is common for all the                                                                                                                                                                                                                                                              |      |

|      | plots on the same column, while the y-axis is in common for all the plots in the                                                                                                                                                                                                                                                           | 110  |

|      | same row.                                                                                                                                                                                                                                                                                                                                  | 110  |

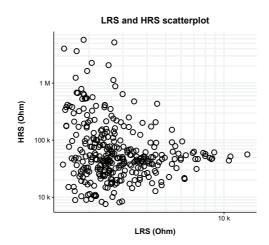

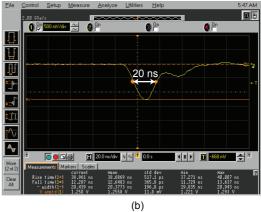

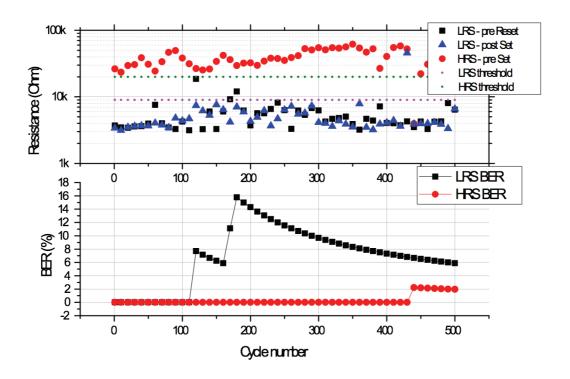

| 5.5  | Scatterplot between the LRS and HRS obtained from the pulse analysis. The                                                                                                                                                                                                                                                                  | 111  |

| F.C  | figure shows that is not possible to obtain all the possible resistance configurations                                                                                                                                                                                                                                                     | .111 |

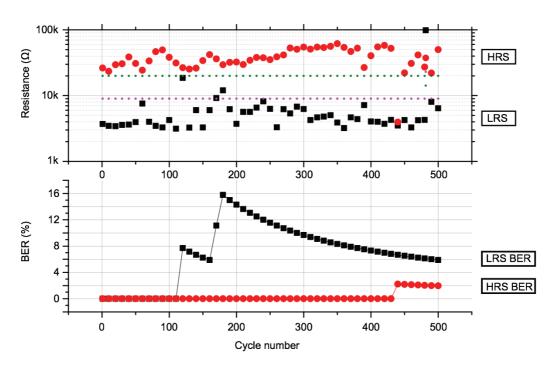

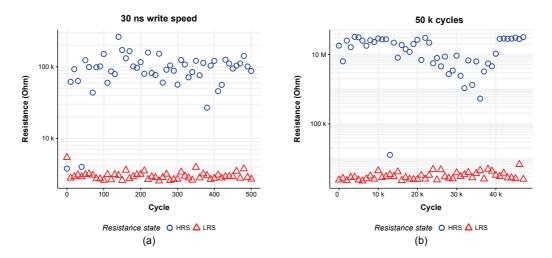

| 5.6  | Example of speed and retention tests for Pt/HfO <sub>2</sub> (5 nm)/Ti (3 nm)/TiN devices: (a) 30 ns write pulse and (b) 50 k cycles                                                                                                                                                                                                       | 112  |

| F 7  |                                                                                                                                                                                                                                                                                                                                            | 112  |

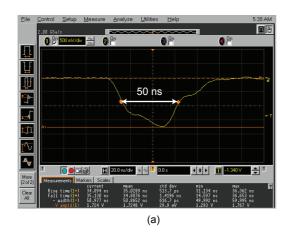

| 5.7  | Example of pulse distortion for sub-50 ns inputs: (a) 50 ns and (b) 20 ns write pulse                                                                                                                                                                                                                                                      | 113  |

| F 0  | Current transient behavior for Pt/HfO <sub>2</sub> (5 nm)/Hf (3 nm)/TiN ReRAM devices.                                                                                                                                                                                                                                                     | 113  |

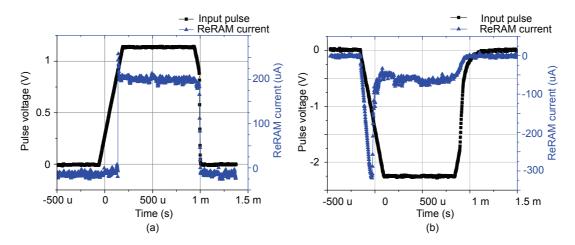

| 5.8  | The current is measured from the voltage drop of a series $1 \text{ k}\Omega$ resistor. The test                                                                                                                                                                                                                                           |      |

|      | conditions are 1.15 V set voltage, –2.25 V reset, 1.9 V gate, 1 ms pulse width and                                                                                                                                                                                                                                                         |      |

|      | 20% slope                                                                                                                                                                                                                                                                                                                                  | 114  |

|      | 20/0 stope:                                                                                                                                                                                                                                                                                                                                | 114  |

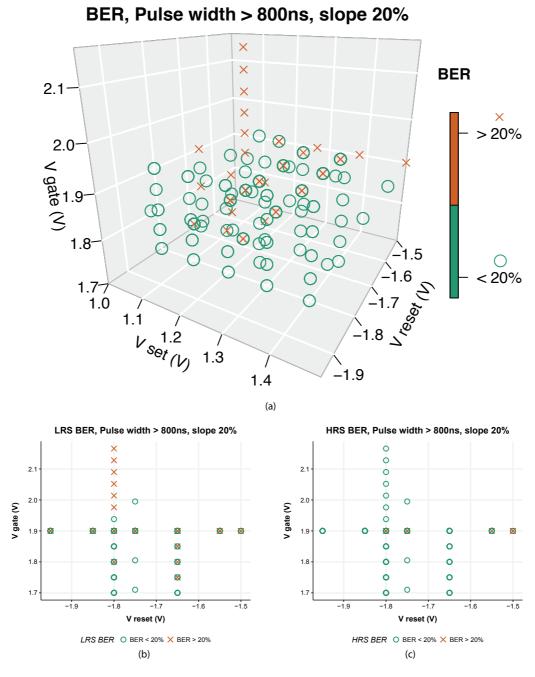

| 5.9  | Representation of the BER for input pulses with width larger that 800 ns and a slope of 20%: (a) 3D scatterplot of the BER with respect to set, reset and gate |      |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | voltage, (b) 2D scatterplot of the LRS BER and (c) the HRS BER with respect to                                                                                 |      |

|      | reset and gate voltage.                                                                                                                                        | 116  |

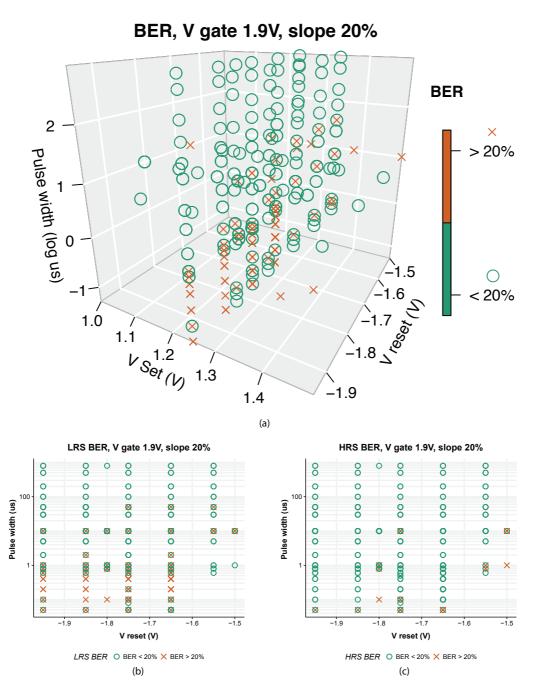

| 5.10 | Representation of the BER for input with gate voltage of 1.9 V and a slope of 20%:                                                                             |      |

|      | (a) 3D scatterplot of the BER with respect to set, reset voltage and pulse width, (b)                                                                          |      |

|      | 2D scatterplot of the LRS BER and (c) the HRS BER with respect to reset voltage                                                                                |      |

|      | and pulse width                                                                                                                                                | 118  |

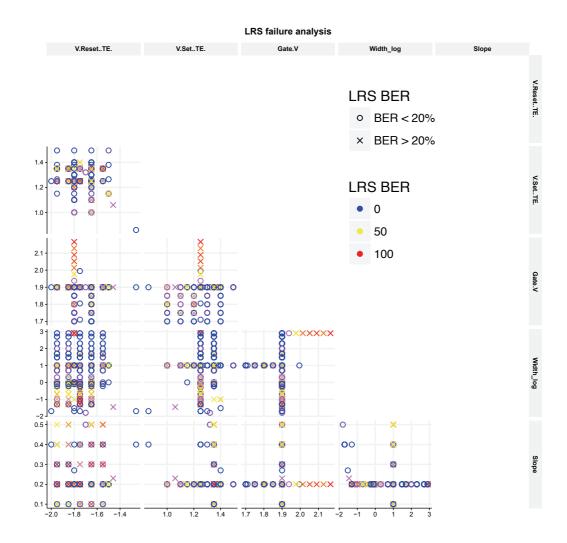

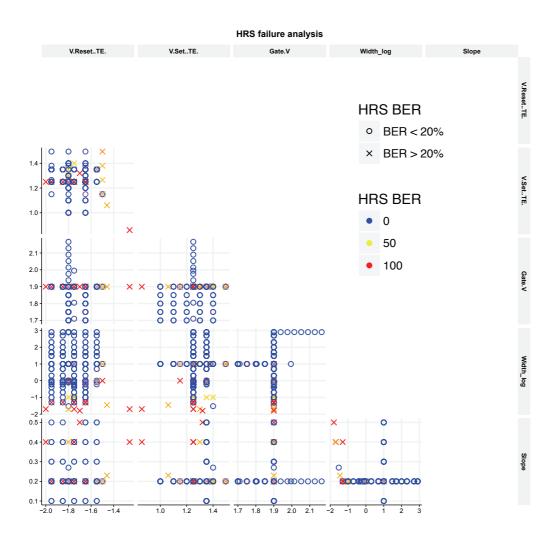

| 5.11 | Scatterplot matrix showing the relation between the input test parameters and                                                                                  |      |

|      | the LRS BER. The quantities varied during the analysis are the reset voltage, set                                                                              |      |

|      | voltage, gate voltage, pulse width and pulse slope. The x-axis is common for all                                                                               |      |

|      | the plots on the same column, while the y-axis is in common for all the plots in                                                                               |      |

|      | the same row.                                                                                                                                                  | 119  |

| 5 12 | Scatterplot matrix showing the relation between the input test parameters and                                                                                  | 110  |

| 3.12 | the HRS BER. The quantities varied during the analysis are the reset voltage, set                                                                              |      |

|      | voltage, gate voltage, pulse width and pulse slope. The x-axis is common for all                                                                               |      |

|      | the plots on the same column, while the y-axis is in common for all the plots in                                                                               |      |

|      |                                                                                                                                                                | 120  |

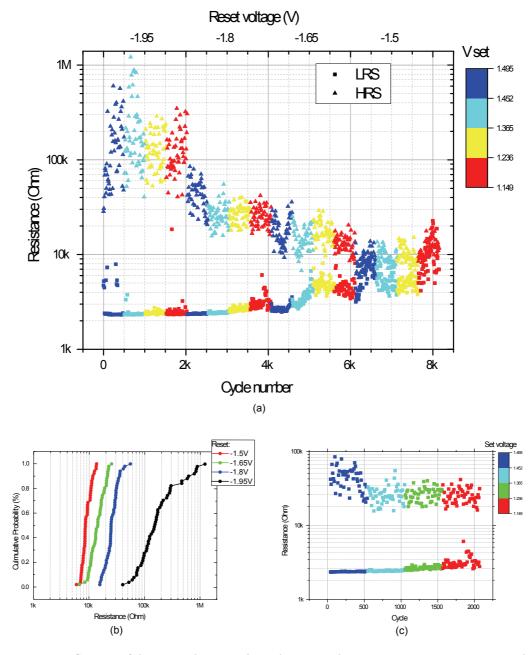

| 5 12 | Influence of the set and reset pulse voltages on the memory resistance states                                                                                  | 120  |

| 5.15 | with 1.9 V gate voltage, 10 µs pulse and 20% slope. (a) Resistance states obtained                                                                             |      |

|      |                                                                                                                                                                |      |

|      | by changing the reset pulse level every 2 k cycles from $-1.95$ V to $-1.5$ V, and the                                                                         |      |

|      | set pulse level, color coded in the image, every 500 cycles from 1.5 V to 1.15 V.                                                                              |      |

|      | (b) HRS cumulative resistance probability plot for different reset voltage values,                                                                             |      |

|      | while the set voltage pulse is fixed at 1.38 V. (c) Modulation of the LRS with a                                                                               | 100  |

|      |                                                                                                                                                                | 123  |

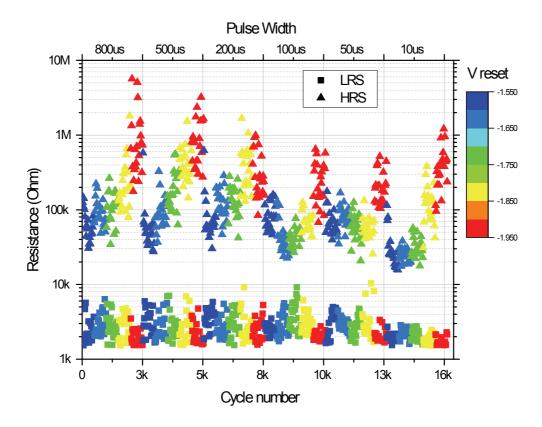

| 5.14 | Influence of the pulse width and reset voltages on the memory resistance states                                                                                |      |

|      | with 1.35 V set pulse, 1.9 V gate voltage and 20% slope. The reset pulse level                                                                                 |      |

|      | changes every 3 k cycles from $800\mu s$ to $10\mu s$ , while the reset pulse, color coded                                                                     |      |

|      | in the image, varies every 500 cycles from $-1.55\mathrm{V}$ to $-1.95\mathrm{V}$                                                                              | 124  |

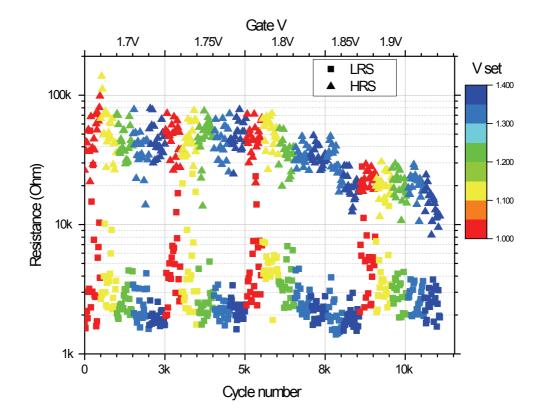

| 5.15 | Influence of the gate and set voltages on the memory resistance states with $-1.8\mathrm{V}$                                                                   |      |

|      | reset pulse, 10 µs pulse width and 20% slope. The gate voltage level changes                                                                                   |      |

|      | every 3 k cycles from 1.7 V to 1.9 V, while the set voltage, color coded in the image,                                                                         |      |

|      | varies every 500 cycles from 1 V to 1.4 V                                                                                                                      | 125  |

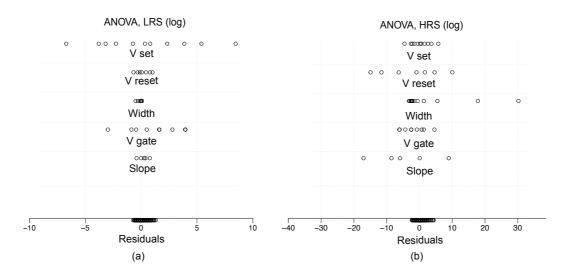

| 5.16 | ANOVA dot plot for the test input influence over the (a) $log(LRS)$ and (b) $log(HRS)$ .                                                                       | .128 |

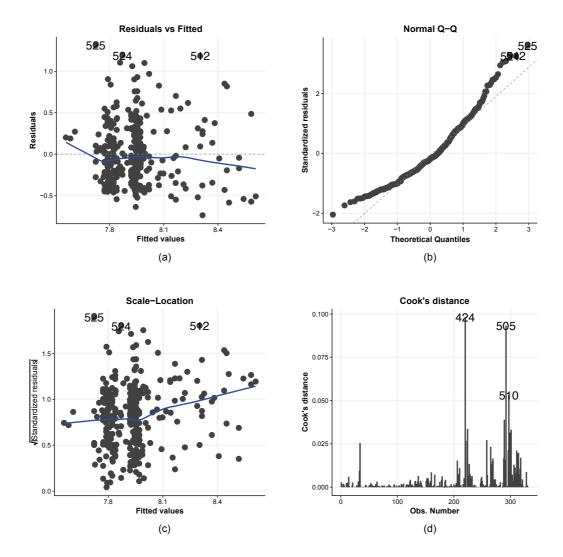

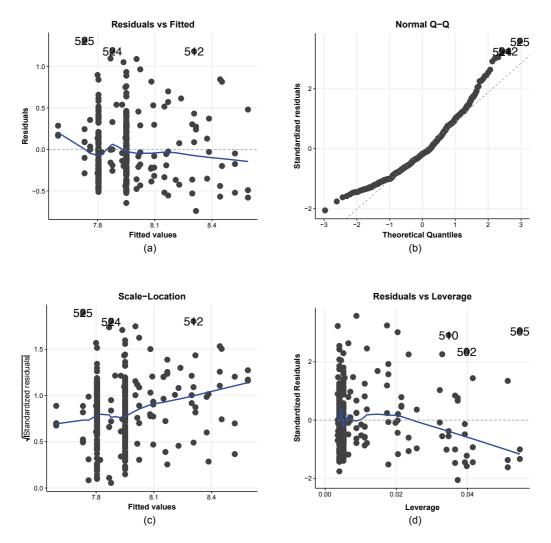

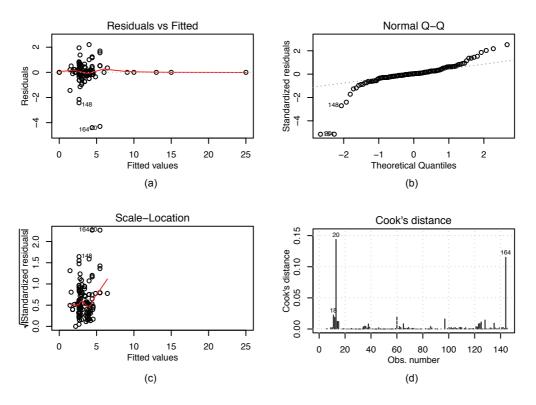

| 5.17 | ANOVA diagnostic plots for the test input influence over the log(LRS): (a) fitted                                                                              |      |

|      | values with respect to the residuals, (b) residuals normal Q-Q plot, (c) fitted                                                                                |      |

|      | values with respect to the standardized residuals, (d) Cook's distance for the data                                                                            |      |

|      | points                                                                                                                                                         | 129  |

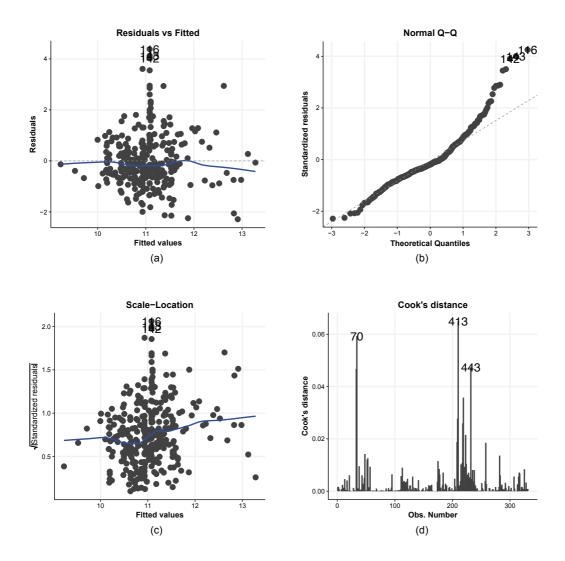

| 5.18 | ANOVA diagnostic plots for the test input influence over the log(HRS), (a) fitted                                                                              |      |

|      | values with respect to the residuals, (b) residuals normal Q-Q plot, (c) fitted                                                                                |      |

|      | values with respect to the standardized residuals, (d) Cook's distance for the data                                                                            |      |

|      |                                                                                                                                                                | 130  |

|      |                                                                                                                                                                |      |

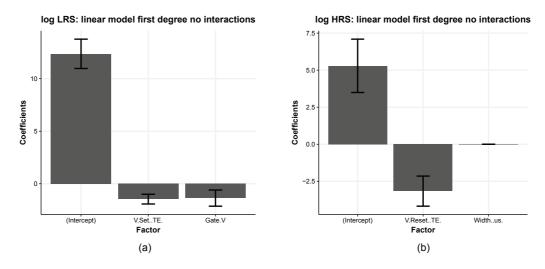

| 5.19 | Calculated coefficients with 2.5% and 97.5% confidence levels for the (a) log(LRS) and (b) log(HRS) models                                                                                                                                                                                                                                                                  | 133 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

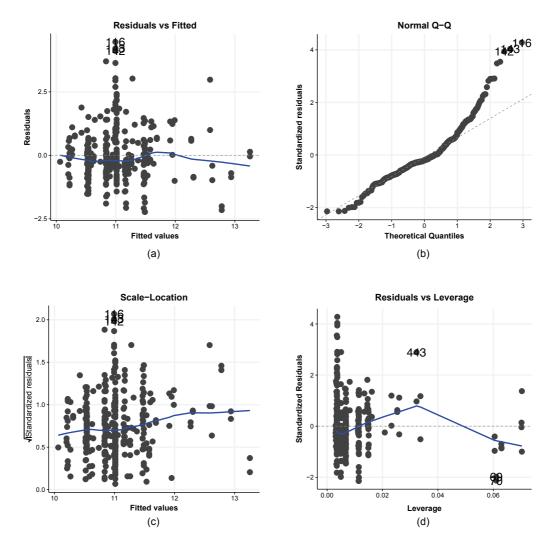

| 5.20 | Diagnostic plots for the log(LRS) model: (a) fitted values with respect to the residuals, (b) residuals normal Q-Q plot, (c) fitted values with respect to the standardized residuals, (d) leverage with respect to the standardized residuals.                                                                                                                             | 134 |

| 5.21 | Diagnostic plots for the log(HRS) model: (a) fitted values with respect to the residuals, (b) residuals normal Q-Q plot, (c) fitted values with respect to the standardized residuals, (d) leverage with respect to the standardized residuals.                                                                                                                             | 135 |

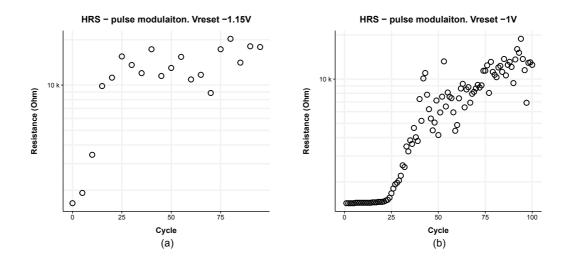

| 5.22 | Example of pulse number resistance modulation. The reset pulses have 1 $\mu$ s width, 20% slope, a period of 100 ms and a width of (a) $-1.15$ V and (b) $-1$ V                                                                                                                                                                                                             | 137 |

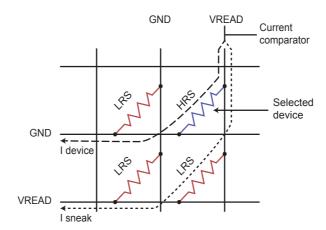

| 6.1  | Schematic representation of the sneak-path current. The total current has two components: one is the current flowing through the selected device, in blue in the figure, and one resulting from the unselected memory components in a LRS.                                                                                                                                  | 141 |

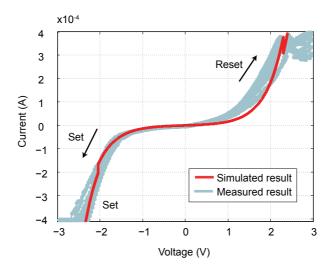

| 6.2  | I-V curve measurement for the fabricated TiN/TaO <sub>2</sub> (25 nm)/TiN ReRAM cells and Verilog-A model                                                                                                                                                                                                                                                                   | 142 |

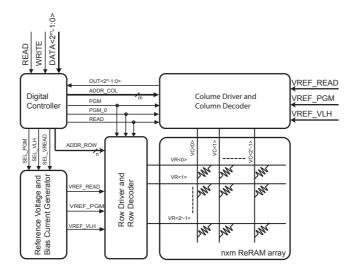

| 6.3  | Read/Write circuit block diagram. The system is composed by row and column drivers, a digital controller and a reference voltage generator                                                                                                                                                                                                                                  | 144 |

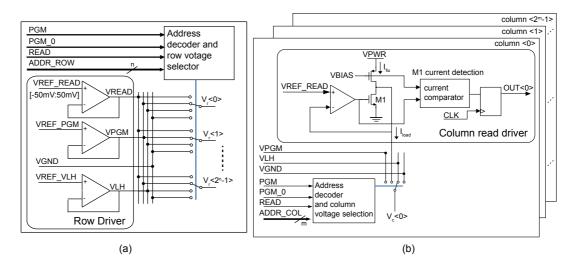

| 6.4  | Schematic representation of (a) the row driver and (b) the column driver                                                                                                                                                                                                                                                                                                    | 145 |

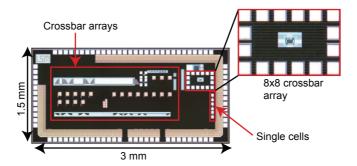

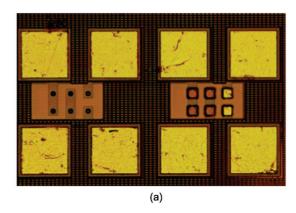

| 6.5  | Chip micrograph. The systems includes different size of ReRAM arrays (up to 128×8), a read/write circuitry and single cell test areas                                                                                                                                                                                                                                       | 146 |

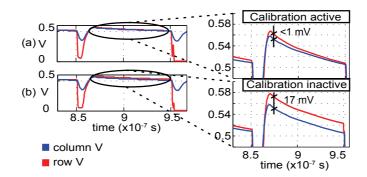

| 6.6  | Post layout simulation of the voltage drop across an unselected ReRAM cell (a) with and (b) without the calibration circuit during the read operation. The voltage difference between the column (blue) and row (red) voltages, directly proportional to the cell sneak-path current, is reduced by more than one order of magnitude when the calibration circuit is active | 147 |

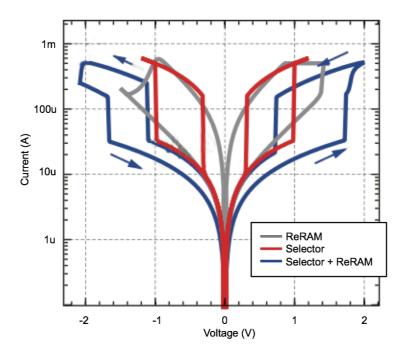

| 6.7  | Representative I-V characteristic for ReRAM, threshold type selector and 1S1R device (adapted from [29])                                                                                                                                                                                                                                                                    | 148 |

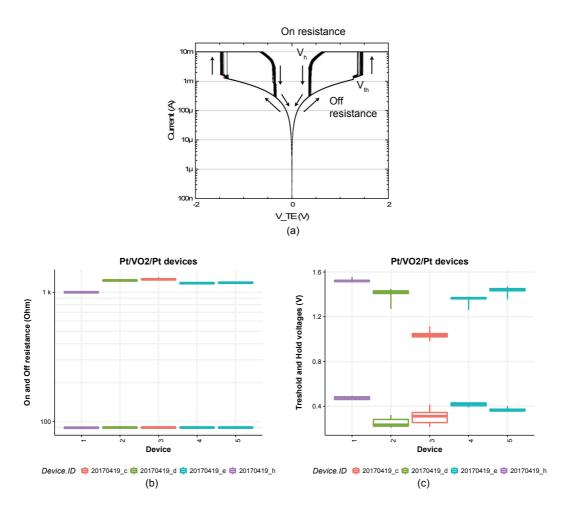

| 6.8  | DC characteristics for the $Pt/VO_2/Pt$ selector devices. (a) Shows the representative DC cycles; while the boxplots show (b) the resistance state and (c) the switching voltage measurements                                                                                                                                                                               | 154 |

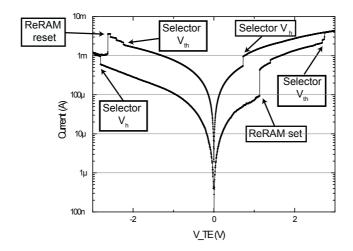

| 6.9  | I-V characteristic for the 1S1R device stack. The $Pt/VO_2/Pt$ selector is in series with the $Pt/HfO_2$ (5 nm)/Ti (3 nm)/TiN ReRAM                                                                                                                                                                                                                                         | 155 |

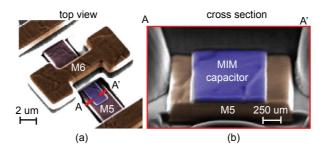

| 6.10 | (a) Scanning electron micrograph of the MMC capacitor and (b) FIB-SEM cross section                                                                                                                                                                                                                                                                                         | 156 |

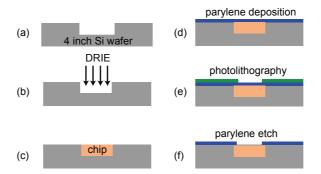

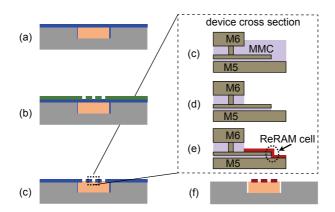

| 6.11 | Process flow representation for the carrier wafer fabrication: (a) Si substrate, (b) Si DRIE, (c) chip mounting, (d) parylene deposition, (e) photolithography, (f) parylene RIE.                                                                                                                                                                                           | 157 |

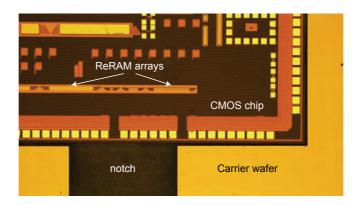

| 6.12 | Micrograph of the carrier wafer with embedded the CMOS chip. The visible notch is used to facilitate the chip release.                                                                                                                                                                                                                                                      | 157 |

|      |                                                                                                                                                                                                                                                                                                                                                                             |     |

| 6.13 | Process flow representation for ReRAM post-processing: (a) parylene layer coat-                 |     |

|------|-------------------------------------------------------------------------------------------------|-----|

|      | ing, (b) photolithography, (c) parylene RIE, (d) passivation BHF, (e) ${\rm TaO_{X}}$ sputter-  |     |

|      | ing, (f) parylene lift off                                                                      | 158 |

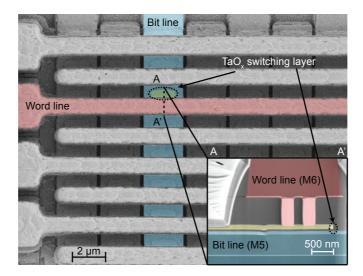

| 6.14 | Scanning electron micrograph of an 8 Bit line-8 Word line crossbar array with                   |     |

|      | Word and Bit lines in M6 and M5. Inset shows a TEM cross section of the memory                  |     |

|      | cross point. One of the ReRAM cells is highlighted in yellow                                    | 159 |

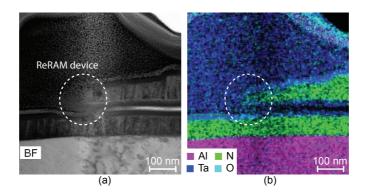

| 6.15 | Transmission electron micrograph of the MMC-M5 interface. (a) Bright field                      |     |

|      | image and (b) EDX elemental analysis.                                                           | 159 |

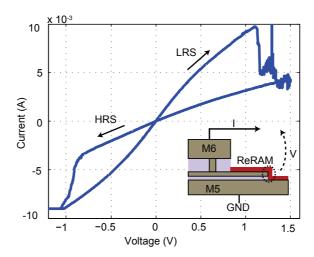

| 6.16 | Electrical results for the TiN/TaO <sub>2</sub> /TiN ReRAM integrated cell. Set voltage is      |     |

|      | -1 V, Reset voltage is 1.3 V. The operating voltages are compatible for low-voltage             |     |

|      | applications                                                                                    | 160 |

| 6.17 | (a) Micrograph of the 2×2 ReRAM array integrated on the chip. (b) I-V curve of                  |     |

|      | the TiN/TaOTaO <sub>x</sub> /TiN integrated ReRAM                                               | 162 |

|      |                                                                                                 |     |

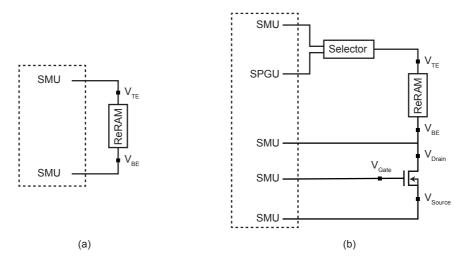

| A.1  | Setup for the (a) DC and (b) pulse measurements                                                 | 170 |

| A.2  | (a) Pulse measurement procedure and (b) single pulse parameters                                 | 171 |

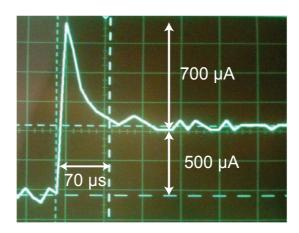

| A.3  | Oscilloscope data of a 50 $\Omega$ resistor in series to TiN/TaO <sub>2</sub> (25 nm)/TiN ReRAM |     |

|      | cell during the forming operation: the parameter analyzer $500\mu\text{A}$ current com-         |     |

|      | pliance is reached just after 70 µs and with a peak current of 1.2 mA                           | 172 |

| A.4  |                                                                                                 |     |

|      | tance, (d) relative frequency and (e) cumulative probability of the resistance                  |     |

|      | states, relative frequency for the (f) set and (g) reset voltages, (h) set voltage              |     |

|      | versus reset voltage plot                                                                       | 174 |

| A.5  | Pulse data analysis example                                                                     | 175 |

| A.6  | ANOVA diagnostic plot example: (a) fitted values with respect to the residuals,                 |     |

|      | (b) residuals normal Q-Q plot, (c) fitted values with respect to the standardized               |     |

|      | residuals, (d) Cook's distance for the data points.                                             | 181 |

| A.7  | ANOVA plot example: (a) fitted values with respect to the residuals, (b) residuals              |     |

|      | normal Q-Q plot, (c) fitted values with respect to the standardized residuals, (d)              |     |

|      | Cook's distance for the data points                                                             | 182 |

# List of Tables

| 2.1 | Number of particles per bit for memory technologies (adapted from [4])                  | 9   |

|-----|-----------------------------------------------------------------------------------------|-----|

| 2.2 | Emerging memory products                                                                | 10  |

| 2.3 | Energy efficiency for memory technologies (adapted from [4])                            | 12  |

| 2.4 | Barrier heights for memory technologies (adapted from [4])                              | 13  |

| 2.5 | Switching time for memory technologies (adapted from [4])                               | 15  |

| 2.6 | Device characteristics of mainstream and emerging memory technologies $[12]$ .          | 15  |

| 3.1 | Investigated recipes for TiN dry plasma etching                                         | 33  |

| 3.2 | $TaO_x$ compositions                                                                    | 41  |

| 4.1 | Process variations and measured quantities during the DC tests                          | 65  |

| 4.2 | Process variations                                                                      | 68  |

| 4.3 | Summary of the DC electrical characteristics for Pt/HfO <sub>2</sub> (5 nm)/TiN devices |     |

|     | fabricated with die and ebeam process                                                   | 75  |

| 5.1 | Test variations and measured quantities for the pulse tests                             | 108 |

| 5.2 | ANOVA table for the test input influence over the log(LRS)                              | 127 |

| 5.3 | ANOVA table for the test input influence over the log(HRS)                              | 127 |

| 5.4 | Regression model summary for the LRS                                                    | 131 |

| 5.5 | Regression model summary for the log(LRS)                                               | 132 |

| 5.6 | Regression model summary for the log(HRS)                                               | 132 |

| 6.1 | Verilog-A model fitting parameters                                                      | 143 |

| 7.1 | Summary and comparison of the fabricated device performances                            | 166 |

| A.1 | Example of a regression model summary                                                   | 183 |

## **List of Acronyms**

**AES** Auger Electron Spectroscopy

**AFM** Atomic Force Microscope

**ALD** Atomic Layer Deposition

**ANOVA** Analysis of Variance

**BE** Bottom Electrode

**BEoL** Back End of the Line

**BER** Bit Error Ratio

**BHF** Buffered Hydrofluoric Acid

**CMI** Center of MicroNanoTechnology of EPFL

**CMOS** Complementary Metal Oxide Semiconductor

**DRAM** Dynamic Random Access Memory

**DRIE** Deep Reactive Ion Etching

**EBR** Edge Bead Removal

**EDX** Energy-Dispersive X-Ray Spectroscopy

**FeRAM** Ferroelectric Random Access Memory

FIB Focused Ion Beam

**HRS** High Resistance State

**IBE** Ion Beam Etching

**LER** Line Edge Roughness

**LPCVD** Low Pressure Chemical Vapor Deposition

#### **List of Acronyms**

**LRS** Low Resistance State

**LTO** Low Temperature Oxide

MIEC Mixed Ionic Electronic Conduction

**MIT** Metal-Insulator Transition

MMC Metal to Metal Capacitor

MRAM Magnetoresistive Random Access Memory

**NVM** Non Volatile Memory

**OTS** Ovonic Threshold Switch

**OxRAM** Oxide-Based Random Access Memory

**PAM** Pre Alignment Marker

**PCRAM** Phase Change Random Access Memory

**PEC** Proximity Effect Correction

**PECVD** Plasma Enhanced Chemical Vapor Deposition

**RAM** Random Access Memory

**ReRAM** Resistive Random Access Memory

**RIE** Reactive Ion Etching

**RTP** Rapid Thermal Processing

**SEM** Scanning Electron Microscope

**SIMS** Secondary Ions Mass Spectroscopy

**SMU** Source Measure Unit

**SPGU** Semiconductor Pulse Generator Unit

**SRAM** Static Random Access Memory

**SRD** Spin Rinse Dryer

**SSD** Solid-State Drive

**STTRAM** Spin-Transfer Torque Random Access Memory

**TE** Top Electrode

**TEM** Transmission Electron Microscope

xxii

**WEC** Wedge Error Compensation

**XPS** X-Ray Photoemission Spectroscopy

**XRD** X-Ray Diffraction

## 1 Introduction

The history of computer memory, summarized in details in [1], starts in the first part of the XIX century with Charles Babbage. In 1837, Babbage invented the Analytical Engine, which was the first Turing-complete machine. His design contained the five key characteristics of modern computers: an input device, a processor or number calculator, a unit to control the task and the sequence of its calculations, an output device, and a memory storage system. In case of the Analytical Engine, the memory was based on three different types of punch cards used for arithmetical operations, for numerical constants, and for load and store operations.

The next important step in memory technology was about 100 years later, when, in 1932, Gustav Thauschek invented the magnetic drum (based on an earlier discovery credited to Fritz Pfleumer). The magnetic drum memory stored information on the outside of a rotating cylinder coated with ferromagnetic material and circled by read/write heads in fixed positions. This type of memory was used in the computer Atlas [Fig. 1.1 (a)], completed in 1950, which was commissioned by the US Navy to the *Engineering Research Associates* (ERA) in order to build a stored program computer with the goal of enhancing the America's codebreaking capabilities.

The first random access memory was later developed in 1947 at Manchester University by Freddie Williams and Tom Kilburn. The prototype, called the Williams-Kilburn tube [Fig. 1.1 (b)], used a cathode ray tube to store bits as dots on the screen surface. Each dot lasted a fraction of a second before fading so the information was constantly refreshed. Information was read by a metal pickup plate that would detect a change in electrical charge. The prototype allowed to successfully store 1024 bits of information.

In the 50s and 60s there was an impressive development in memory technologies. Few years after the Williams-Kilburn tube, while working on the Whirlwind project at MIT, Jay Forrester develops the idea of using magnetic-core memories, which will be the first reliable high-speed random access memory for computers. In 1953, MIT's Whirlwind becomes the first computer to use magnetic core memory. The core memory, shown in Fig. 1.1 (c), is made up of tiny toroidal shapes made of magnetic material fixed on wires into a grid. Each core

Figure 1.1 – Examples of early memory technologies: (a) ERA founders with various magnetic drum memories, (b) Manchester Mark I Williams-Kilburn tube, (c) detail of Whirlwind core memory, (d) RAMAC 305 disks and head assembly, (e) close up shot of Apollo Guidance Computer read-only rope memory, (f) DEC VAX memory board with Intel 1103 memory chips. Images taken from [2].

stored a bit, magnetized one way for a "zero," and the other way for a "one." The wires could both detect and change the state of a bit. Magnetic core memory was widely used as the main memory technology for computers well into the 1970s, when Intel introduced the 1103 *Dynamic Random Access Memory* (DRAM) integrated circuit, which signaled the beginning of the end for magnetic core memory in computers.

Few years later, the era of magnetic disk storage dawns in 1956 with IBM's RAMAC 305 computer system. The computer was based on the new technology of the hard disk drive. The RAMAC disk drive [Fig. 1.1 (d)] consisted of 50 magnetically coated metal platters capable of storing about 5 million characters of data. RAMAC allowed real-time random access to large amounts of data, unlike magnetic tape or punched cards. A working RAMAC hard disk assembly is still demonstrated regularly at the Computer History Museum in Mountain View (California).