### A Nine Decade Femtoampere Current to Frequency Converter

THÈSE Nº 7853 (2017)

PRÉSENTÉE LE 12 OCTOBRE 2017 À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR GROUPE KAYAL PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

### **Evgenia VOULGARI**

acceptée sur proposition du jury:

Dr J.-M. Sallese, président du jury Prof. M. Kayal, Dr F. Szoncsó, directeurs de thèse Prof. Y. Papananos, rapporteur Dr N. Khosro Pour, rapporteur Prof. P.-A. Farine, rapporteur

Beyond the horizon of the place we lived when we were young In a world of magnets and miracles Our thoughts strayed constantly and without boundary The ringing of the division bell had begun... —High Hopes, Pink Floyd

To my family.

### Acknowledgements

This thesis is the outcome of my work at EPFL and CERN and was possible thanks to the support of many people. I would like to thank all those people who contributed to the completion of this work and encouraged me throughout my studies.

Firstly, I would like to express my sincere gratitude to my advisor Prof. Maher Kayal who kindly accepted me in his lab and gave me the opportunity to pursue a PhD at EPFL. Thank you for the help, support, guidance and trust during all these years.

Then I would like to deeply thank Dr. François Krummenacher who helped and encouraged me in every step of my scientific work. I feel really lucky and inspired to have worked with him. This thesis is not a "*utopia*" anymore because of him.

I would also like to thank the members of my thesis jury, Dr. Jean Michel Sallese, Prof. Yannis Papananos who was my first professor in electronics at the National Technical University of Athens, Prof. Pierre-André Farine and Dr. Naser Khosro Pour, for reading my thesis and providing me with useful comments and improvements on this manuscript.

From the CERN site, I would like to thank my thesis co-advisor Dr. Fritz Szoncsó who believed in me from the very first moment. I always enjoy our discussions about science and about electrical engineering in general.

I would also like to thank my CERN supervisor Daniel Perrin who kindly encouraged and supported my choices. Merci pour ton aide à apprendre le français.

I was lucky to meet Dr. Matthew Noy in one of the most critical phases of this PhD. I would like to thank him for motivating me and helping me during the measurements procedure. He taught me how to work systematically and his contribution to the implementation of the DAQ system and during the long measurements was invaluable. Thanks Matt!

I am also grateful to Francis Anghinolfi for his fruitful advice and his valuable and detailed comments on this work. Accepting me in his section helped me a lot to improve and work harder.

I would like to thank Cédric Meinen, Gaël Ducos and Michel Morel for their practical support. They were always willing to help me immediately each time that I needed something.

I would also like to thank all the colleagues with whom I have shared an office all these years.

#### Acknowledgements

From CERN Nicola, Antonio, Vito, Nico and Michal and from EPFL Camillo, Pietro and Mathieu. We spent hours of discussions with Nicola and we shared our knowledge when I first came at CERN. Vito and Nico were always willing to share their physics background with me. Camillo, Mathieu and Pietro thanks for our useful discussions on electronics that taught me a lot and for your friendship. Nicola, Vito, Nico and Michal, it is great to share the office with people who appreciate the same kind of music as I do.

There are numerous other people that I want to acknowledge. Doctoral students from the ELAB, Denis, François, Guillaume, Giorgos and Theo. And colleagues from HSE-RP and EP-ESE groups.

Special thanks to Sandro Marchioro for our pizza sessions, Winnie Wong for our coffee meetings, her encouragement and her advice on the thesis, Rafa Ballabriga for his comments and William Vigano for his general advice during our coffee breaks.

Traveling between two institutes all these years and moving from France to Switzerland, thank you Ritsa for the rides to EPFL and Leda for your hospitality.

During these years in Switzerland I have met some friends for life. They cheer up my weekends and share many ideas about the trips we will take together and the future that we will share. Giorgos, Ioanna, Manos, Margarita, Yanna, Iraklis, Lefteris, Natasa, Giannis, Nadia, thank you all!

I would like to thank Thanasis for being here since the beginning of this long journey to *"Ithaca"*. For following me to Switzerland, for making me smile, for helping me in any possible way with positive and optimistic thoughts.

Finally, I would like to thank my family, my mother, father and sisters, who encouraged and supported me all these years of my studies with love and patience. In all the difficult moments they are standing by me and make me stronger reminding me that "Κι αν είσαι στο σχαλί το πρώτο, πρέπει νάσαι υπερήφανη χ' ευτυχισμένη. Εδώ που έφτασες λίγο δεν είναι, τόσο που έχαμες, μεγάλη δόξα." Ευχαριστώ!

Lausanne, 16 June 2017

Εύη

### Abstract

Various applications require ultra-low current sensing. Some of these applications are related to ionizing radiation detection. Radiation monitoring is important in particle physics experiments, nuclear facilities, hadron therapy institutes and hospitals. In these cases the detectors used are mostly gas-filled detectors like ionization chambers. The output of these detectors is a current that is normally proportional to the energy deposited by the incident radiation.

The European Organization for Nuclear Research (CERN) has a legal obligation to comply with the legislation in matters of radiation protection in order to avoid any unjustified dose to people or pollution of the environment. According to the existing detectors, the current output varies from a few femtoamperes up to the microampere range.

The scope of this thesis is the design of a microelectronic integrated wide dynamic range front-end for radiation monitoring.

Firstly, the state of the art has been investigated and different technologies have been compared. The selected architecture is based on current to frequency conversion with charge balancing. The main limitation in ultra-low current sensing is related to the leakage currents that are present in the front-end input. A demonstrator Application Specific Integrated Circuit (ASIC) named Utopia 1 was built in AMS 0.35  $\mu$ m technology to estimate the different sources of leakage currents and provide guidelines or design solutions for femtoampere measurements. According to the achieved results, a new ASIC named Utopia 2 was designed that has been optimized to minimize the non-ideal effects.

The Utopia 2 is able to digitize currents from 1 femtoampere (fA) up to 5 microamperes ( $\mu$ A). To achieve such performance, the ASIC includes an active on-chip leakage current compensation circuit and a multi-range charge balancing circuit. The ASIC integrates the input current in a constant acquisition time, but for the sub-picoampere current measurements the measuring time needs to be increased.

The ASIC has been characterized for its low current performance in the Swiss Federal Institute of Metrology (METAS). The ASIC's calibration procedure and qualitative radiation measurements with the detector in the presence of radiation sources have been performed. The designed ASIC is the ultra-low current sensing circuit and digitizer that will be used at CERN for radiation monitoring for personnel and environmental safety.

### Abstract

Key words: radiation monitoring, femtoamperes, leakage currents, current to frequency conversion, active leakage compensation

### Résumé

De nombreuses applications nécessitent la détection de courants ultra-faibles. Certaines de ces applications sont liées à la détection des rayonnements ionisants. La surveillance des radiations est importante dans les expériences de physique des particules, les installations nucléaires, les centres de thérapie hadronique et les hôpitaux. Les détecteurs utilisés sont principalement des détecteurs remplis de gaz telles les chambres à ionisation. Le signal de sortie de ces chambres est un courant qui est généralement proportionnel à l'énergie déposée par le rayonnement incident.

L'Organisation européenne pour la recherche nucléaire (CERN) a l'obligation légale de se conformer à la législation en vigueur en matière de radioprotection pour empêcher toute dose injustifiée pour les personnes et l'environnement. Selon les détecteurs actuellement utilisés, leur courant de sortie varie de quelques femtoampères (fA) jusqu'à atteindre la gamme du microampère ( $\mu$ A).

Le sujet de cette thèse est la conception d'une interface microélectronique intégrée à large dynamique de mesure adaptée à la surveillance des radiations.

Tout d'abord, l'état de l'art dans le domaine de la mesure de courants ultra-faibles a été investigué et les différentes technologies ont été comparées. L'architecture finalement retenue est basée sur la conversion de courant en fréquence avec équilibrage de charges. La principale limitation de la mesure de courants ultra-faibles est liée aux courants de fuite présents à l'entrée du circuit de mesure. Un démonstrateur, basé sur la mise en œuvre d'un circuit intègré spécialisé ou ASIC (Application Specific Integrated Circuit), a été réalisé en technologie 0.35  $\mu$ m d'AMS pour estimer les différentes sources de courants de fuite et fournir des lignes directrices ou des solutions de conception pour la mesure au niveau du femtoampère. Sur la base des résultats obtenus, un nouvel ASIC Utopia 2 a été conçu et optimisé afin de minimiser les effets non idéaux.

L'ASIC Utopia 2 est capable de numériser des courants de 1 femtoampére (fA) jusqu'à 5 microampères ( $\mu$ A). Pour obtenir une telle performance, l'ASIC comprend un circuit actif de compensation des courants de fuite et un circuit d'équilibrage de charges à plusieurs gammes. L'ASIC intègre le courant d'entrée avec un temps d'acquisition constant, mais pour la mesure de courants inférieurs au picoampère (pA), le temps de mesure doit être augmenté.

Les performances de mesure de bas courants de l'ASIC ont été caractérisées à l'Institut fédéral

#### Résumé

de métrologie suisse (METAS). La procédure d'étalonnage de l'ASIC et les mesures qualitatives réalisées avec un détecteur de rayonnements ionisants en présence de sources radioactives ont été effectuées. L'ASIC conçu sera le circuit de détection de courants ultra-faibles et le numériseur utilisés au CERN dans le cadre de la surveillance des rayonnements ionisants pour la protection du personnel et de l'environnement.

Mots clés : surveillance des rayonnements, femtoampères, courants de fuite, conversion de courant en fréquence, compensation active des courant de fuite

# Contents

| Ac | i       |                                                                                                   |     |  |

|----|---------|---------------------------------------------------------------------------------------------------|-----|--|

| Ał | ostra   | ct (English/Français)                                                                             | iii |  |

| Li | st of ] | Figures                                                                                           | xi  |  |

| Li | st of ' | Tables                                                                                            | XV  |  |

| 1  | Intr    | oduction                                                                                          | 1   |  |

|    | 1.1     | CERN                                                                                              | 1   |  |

|    | 1.2     | Radiation Monitoring at CERN                                                                      | 2   |  |

|    | 1.3     | Thesis Outline                                                                                    | 4   |  |

| 2  | Fro     | nt-end Electronics for Gas-Filled Detectors                                                       | 7   |  |

|    | 2.1     | Introduction                                                                                      | 7   |  |

|    | 2.2     | Gas-Filled Detectors                                                                              | 7   |  |

|    |         | 2.2.1 Ionization chambers                                                                         | 7   |  |

|    |         | 2.2.2 Ionization chambers used at CERN                                                            | 8   |  |

|    | 2.3     | Evaluation of the Total Integrated Dose over Time                                                 | 10  |  |

|    | 2.4     | State of the Art                                                                                  | 12  |  |

|    | 2.5     | Chapter Conclusions                                                                               | 14  |  |

| 3  | Eva     | luation of Leakage Current and Dynamic Range in a CFC Architecture                                | 17  |  |

|    | 3.1     | Introduction                                                                                      | 17  |  |

|    | 3.2     | Operating Principle of a Current to Frequency Converter                                           | 17  |  |

|    | 3.3     | Leakage Currents in the Input of the System                                                       | 18  |  |

|    |         | 3.3.1 Leakage current of the switches                                                             | 19  |  |

|    |         | 3.3.2 Leakage of the electrostatic discharge (ESD) protection diodes <i>I</i> <sub>leak_ESD</sub> | 25  |  |

|    |         | 3.3.3 Extrinsic leakage current sources                                                           | 25  |  |

|    | 3.4     | A Demonstrator Chip for Evaluation of the Leakage Currents                                        | 26  |  |

|    |         | 3.4.1 Technology selection                                                                        | 26  |  |

|    |         | 3.4.2 Architecture of the Utopia 1 ASIC                                                           | 27  |  |

|    |         | 3.4.3 Design variations for leakage current measurement                                           | 31  |  |

|    | 3.5     | Leakage Current Measurements                                                                      | 31  |  |

|    |         | 3.5.1 Input switch leakage current measurement                                                    | 32  |  |

|   |      | 3.5.2 ESD protection leakage current measurement                             | 4 |

|---|------|------------------------------------------------------------------------------|---|

|   |      | 3.5.3 Package and adjacent pins leakage current measurement                  | 6 |

|   |      | 3.5.4 Leakage current measurement of the printed circuit board 3             | 7 |

|   | 3.6  | Synchronous versus Asynchronous Mode                                         | 9 |

|   | 3.7  | Dynamic Range Measurement                                                    | 0 |

|   | 3.8  | Chapter Conclusions                                                          | 2 |

| 4 | Des  | ign of an Ultra-low Picoammeter for Radiation Monitoring 4                   | 7 |

|   | 4.1  | Introduction                                                                 | 7 |

|   | 4.2  | System Architecture                                                          | 7 |

|   | 4.3  | Detailed Description of Circuit's Behavior 4                                 | 9 |

|   | 4.4  | Reference Charge    5                                                        | 4 |

|   | 4.5  | Utopia 2 Design Values                                                       | 5 |

|   | 4.6  | Integrator Requirements                                                      | 7 |

|   | 4.7  | Expected Non-Idealities 6                                                    | 2 |

|   |      | 4.7.1 Capacitor values                                                       | 2 |

|   |      | 4.7.2 OTA DC offset, limited $g_m$ and DC gain                               | 2 |

|   |      | 4.7.3 Comparator and logic delay                                             | 3 |

|   |      | 4.7.4 Charge injection and clock feedthrough 6                               | 3 |

|   |      | 4.7.5 Effect of noise                                                        | 4 |

|   |      | 4.7.6 Mismatch in leakage currents between channel 1 and channel 2 6         | 4 |

|   | 4.8  | Circuit Level Design 6                                                       | 4 |

|   |      | 4.8.1 Folded cascode OTA design                                              | 4 |

|   |      | 4.8.2 Feedback circuit of the integrator                                     | 9 |

|   |      | 4.8.3 Comparator                                                             | 1 |

|   |      | 4.8.4 Discharging circuits of channel 1                                      | 2 |

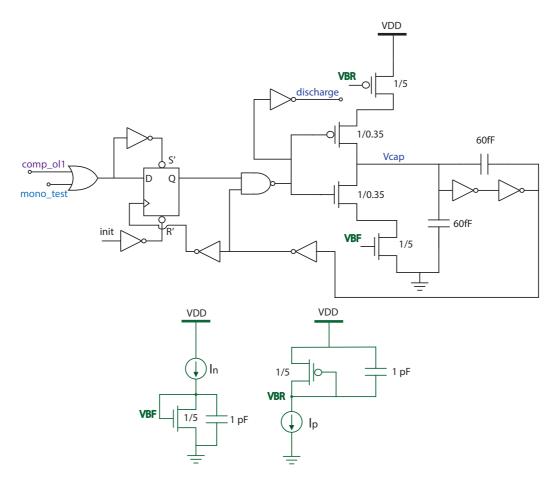

|   |      | 4.8.5 Monostable                                                             | 3 |

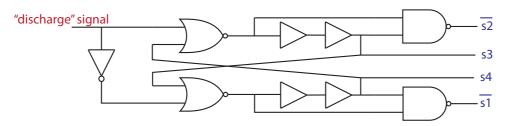

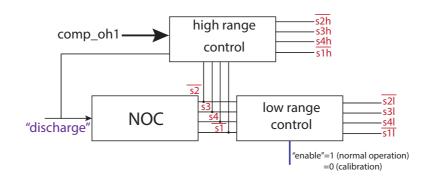

|   |      | 4.8.6 Non-overlapping signals and control of the two ranges in the measuring |   |

|   |      | channel                                                                      | 5 |

|   |      | 4.8.7 Discharging circuit of channel 2                                       | 6 |

|   |      |                                                                              | 7 |

|   | 4.9  | System Integration                                                           | 0 |

|   |      | 4.9.1 Minimize leakage currents at system level                              | 1 |

|   |      | 4.9.2 Printed circuit board (PCB)                                            | 2 |

|   | 4.10 | Chapter Conclusions    8                                                     | 4 |

| 5 | Cha  | racterization of the Utopia 2 ASIC 8                                         |   |

|   | 5.1  | Introduction                                                                 |   |

|   | 5.2  | Data Acquisition System    8                                                 |   |

|   | 5.3  | Calibration Procedure 8                                                      |   |

|   |      | 5.3.1 Charging and discharging time calibration                              |   |

|   |      | 5.3.2 Reference charge calibration                                           |   |

|   | 5.4  | Leakage Current Measurements    9                                            | 3 |

### Contents

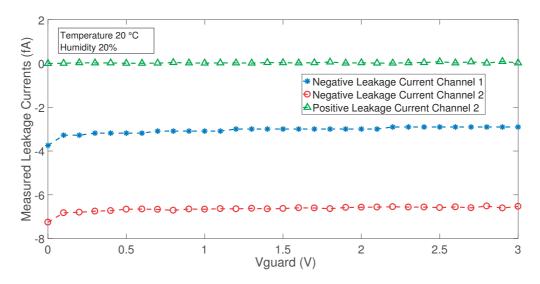

|            |                               | 5.4.1   | Leakage current versus <i>VDDA1</i> and <i>V</i> <sub>guard</sub>              | 94  |

|------------|-------------------------------|---------|--------------------------------------------------------------------------------|-----|

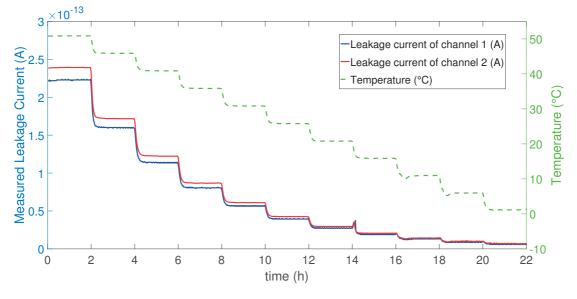

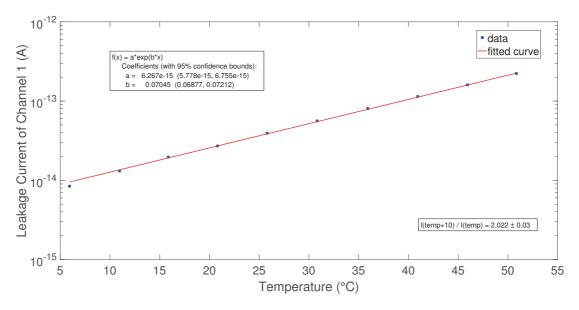

|            |                               | 5.4.2   | Leakage current versus temperature                                             | 95  |

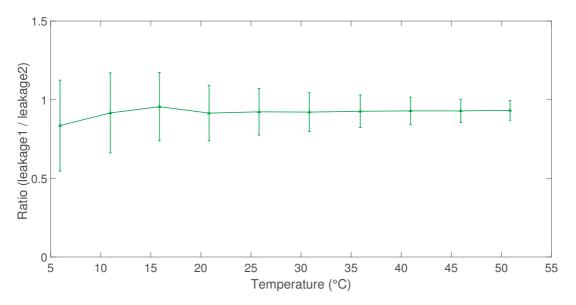

|            |                               | 5.4.3   | Ratio $\rho$ of leakage currents of channel 1 and 2 for different temperatures | 97  |

|            | 5.5                           | Measu   | urements with a Standard Laboratory Current Source                             | 97  |

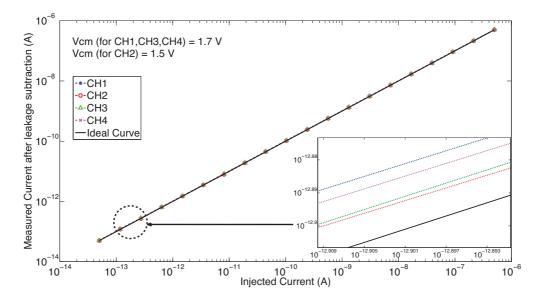

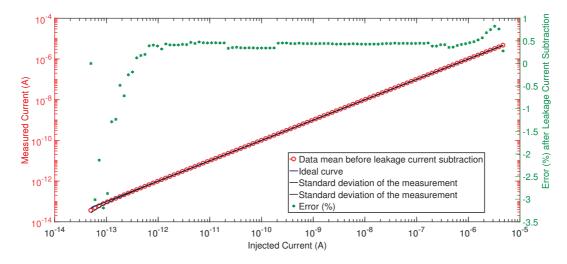

|            | 5.6                           | Measu   | urements with a Calibrated Current Source at METAS                             | 100 |

|            | 5.7                           | Dyna    | mic Range of Utopia 2 ASIC                                                     | 102 |

|            | 5.8                           | Measu   | urements with the Ionization Chamber                                           | 103 |

|            | 5.9                           | Additi  | ional Calibration                                                              | 105 |

|            | 5.10                          | Chapt   | ter Conclusions                                                                | 105 |

| 6          | Con                           | clusio  | ns                                                                             | 109 |

|            | 6.1                           | Sumn    | nary                                                                           | 109 |

|            | 6.2                           | Thesis  | s Contributions and Future Perspectives                                        | 110 |

| Bi         | Bibliography 12               |         |                                                                                | 121 |

| <b>Δ</b> ŀ | bbreviations and Acronyms 123 |         |                                                                                |     |

| ΛL         | DICV                          | lations | s and Acronyms                                                                 | 123 |

# List of Figures

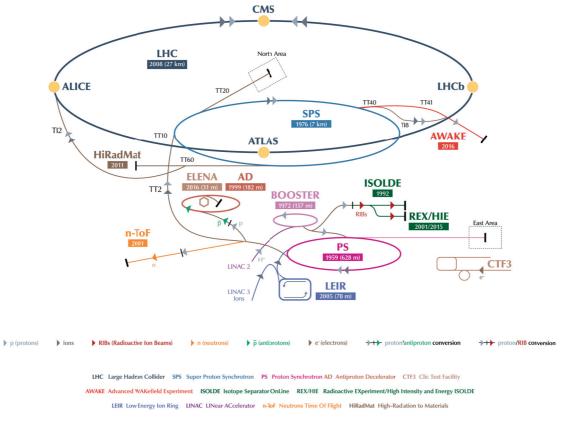

| 1.1  | CERN accelerator complex [2]                                                          | 2  |

|------|---------------------------------------------------------------------------------------|----|

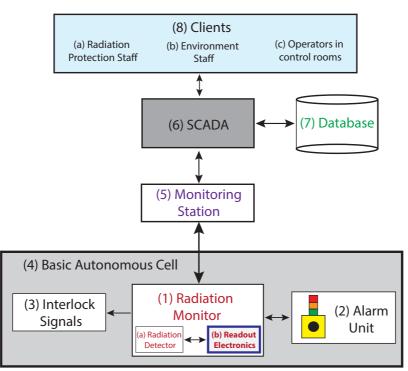

| 1.2  | Functional diagram of the CERN radiation monitoring system [3]                        | 3  |

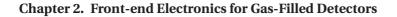

| 2.1  | Cylindrical gas-filled detector                                                       | 8  |

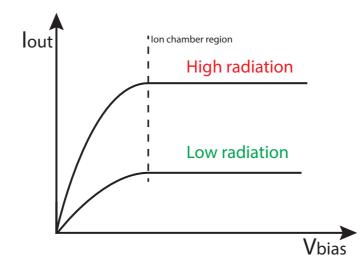

| 2.2  | Output current and bias voltage characteristic curves of an ionization chamber        |    |

|      | at different incident radiation intensities                                           | 8  |

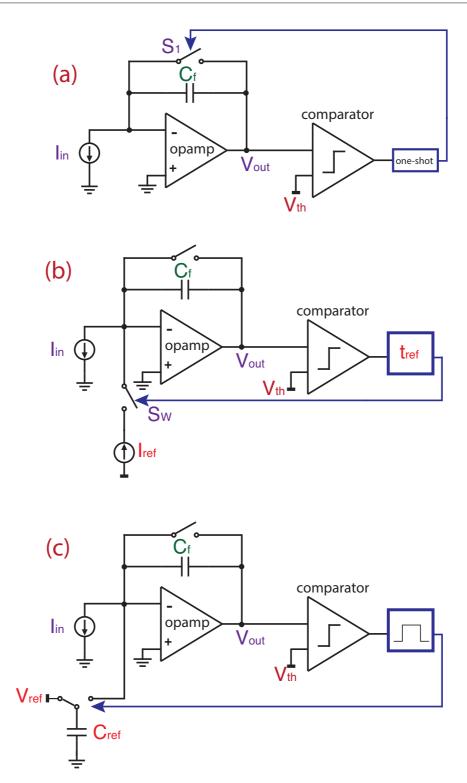

| 2.3  | (a) CFC with shorting switch, (b) CFC with charge balancing using a current           |    |

|      | source, (c) CFC with charge balancing using a switched capacitor                      | 13 |

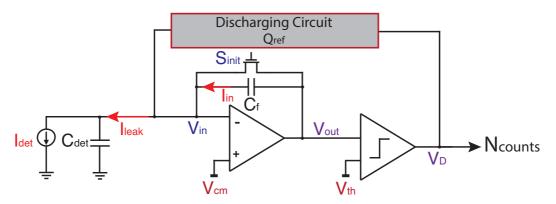

| 3.1  | Simple Current to Frequency Converter (CFC) scheme                                    | 18 |

| 3.2  | Potential leakage current sources in the input of the integrator                      | 19 |

| 3.3  | Leakage current mechanisms in an nMOS transistor                                      | 20 |

| 3.4  | Drain current versus gate voltage for different CMOS technologies ( $T = 300K$ ,      |    |

|      | drain voltage has the nominal value for the given technology). Reproduced with        |    |

|      | permission from [55]                                                                  | 20 |

| 3.5  | Bulk (substrate) current versus gate voltage for different CMOS technologies          |    |

|      | $(T = 300K, V_D = 1.2 \text{ V})$ . Reproduced with permission from [55]              | 21 |

| 3.6  | p-n junction with reverse bias                                                        | 21 |

| 3.7  | Source shifting in an nMOS switch                                                     | 23 |

| 3.8  | Simulation of the drain current versus gate voltage for different $V_S$ for a minimum |    |

|      | size switch in AMS 0.35 $\mu$ m technology                                            | 24 |

| 3.9  | Simple Electrostatic Discharge (ESD) protection circuit                               | 25 |

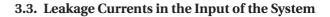

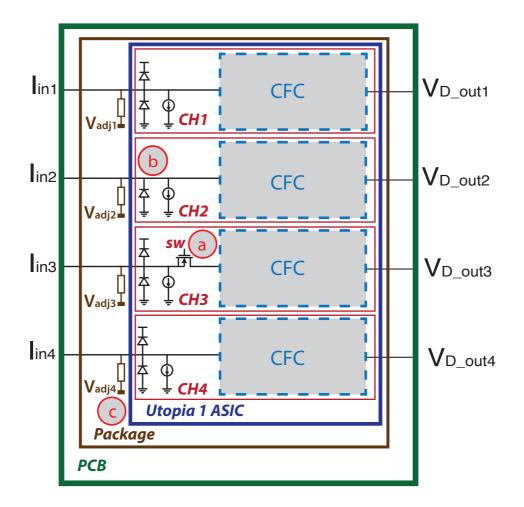

|      | Architecture of the system and potential leakage current sources                      | 28 |

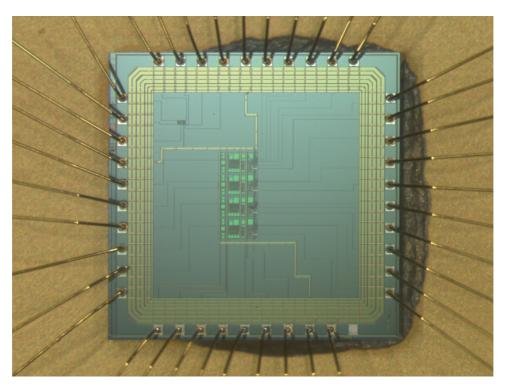

|      | Microscopic picture of Utopia 1 ASIC                                                  | 29 |

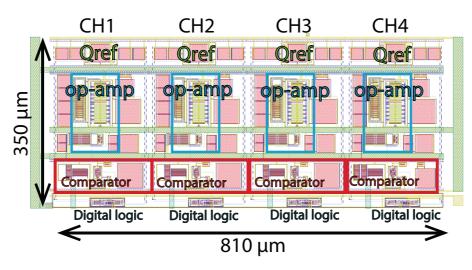

|      | Layout of the core of Utopia 1 ASIC                                                   | 31 |

|      | Block diagram of the four channels of Utopia 1 ASIC                                   | 32 |

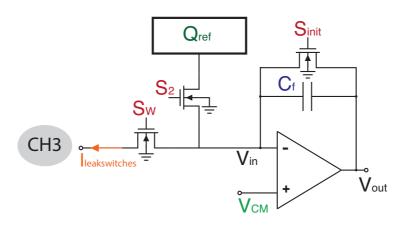

|      | Input of CH3 of Utopia 1 ASIC                                                         | 33 |

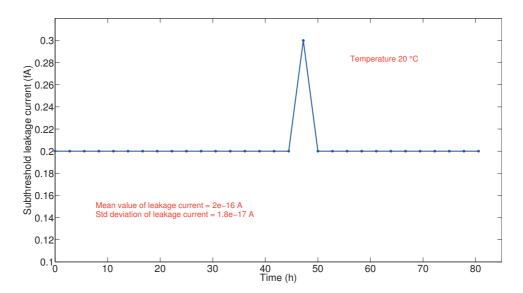

|      | Subthreshold leakage of switches $S_W$ , $S_{init}$ and $S_2$ when measuring CH3      | 33 |

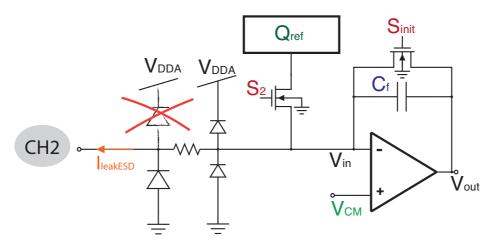

|      | Input of CH2 of Utopia 1 ASIC                                                         | 34 |

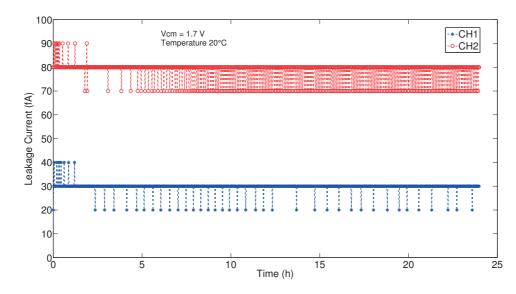

| 3.17 | Absolute value of the leakage current of CH1 and CH2 as a function of time            |    |

|      | measured at the same temperature and with the same $V_{cm}$ (negative polarity) .     | 35 |

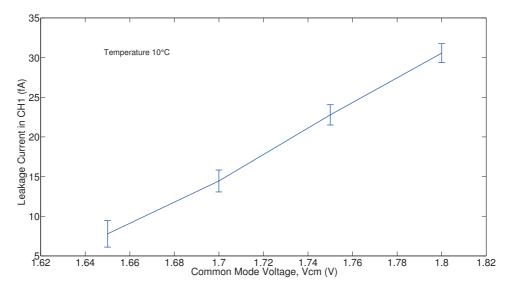

|      | Mean value of leakage current of CH1 versus common mode voltage $V_{cm}$              | 35 |

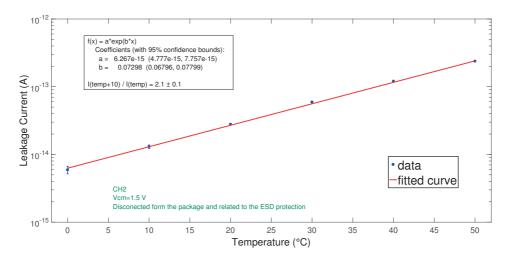

| 3.19 | Mean value of ESD protection leakage current of CH2 versus temperature                | 36 |

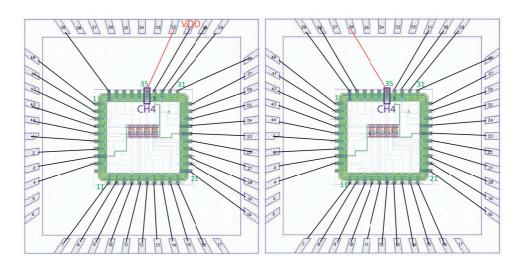

| 3.20 | Difference in CH4 bonding that resulted in different leakage current                                                                       | 36 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

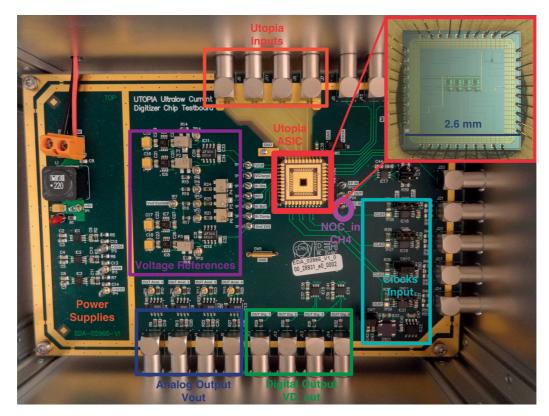

| 3.21 | The testboard of the Utopia 1 ASIC                                                                                                         | 37 |

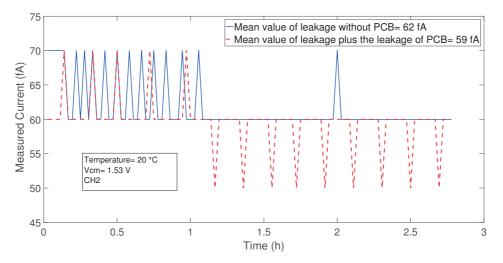

| 3.22 | Measurements with and without the PCB connected                                                                                            | 38 |

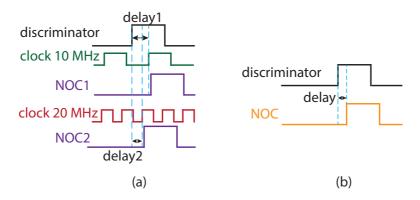

| 3.23 | (a) Synchronous versus (b) asynchronous mode pulses in the discriminator and                                                               |    |

|      | the pulse that generates the non-overlapping clocks (NOC)                                                                                  | 39 |

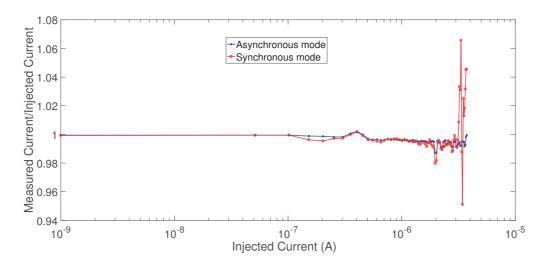

| 3.24 | Synchronous versus asynchronous mode in CH4                                                                                                | 40 |

| 3.25 | Measurements when input currents from 50 fA to 500 nA are injected into the                                                                |    |

|      | channels of Utopia 1 in synchronous mode                                                                                                   | 40 |

| 3.26 | Dynamic range measurements when input currents from 50 fA to 5 $\mu$ A are                                                                 |    |

|      | injected using Keithley 6430 in CH4 in asynchronous mode                                                                                   | 41 |

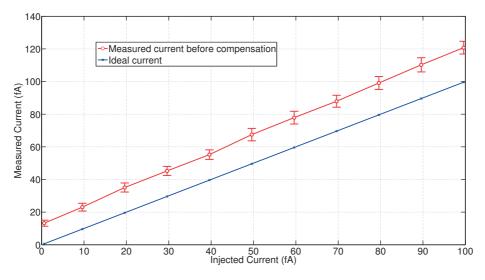

| 3.27 | Mean value of ultra-low injected current from 1 fA to 100 fA versus measured                                                               |    |

|      | current for CH1 at 10°C with 0% humidity                                                                                                   | 41 |

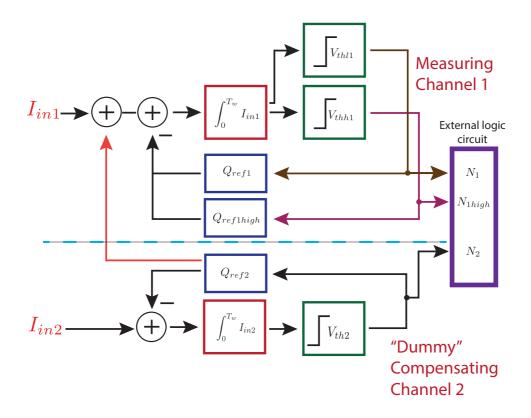

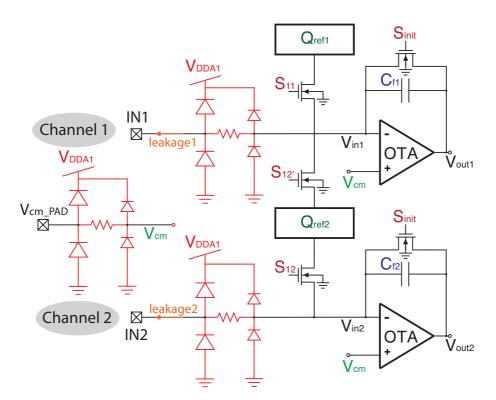

| 4.1  | Utopia 2 leakage current compensation CFC scheme                                                                                           | 48 |

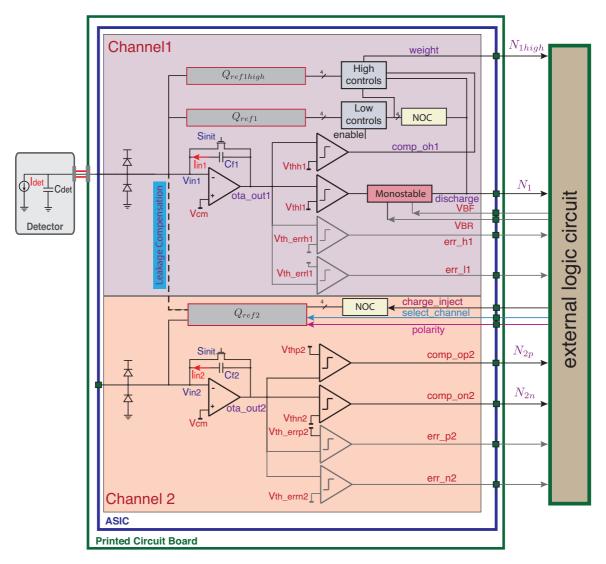

| 4.2  | Utopia 2 block diagram                                                                                                                     | 49 |

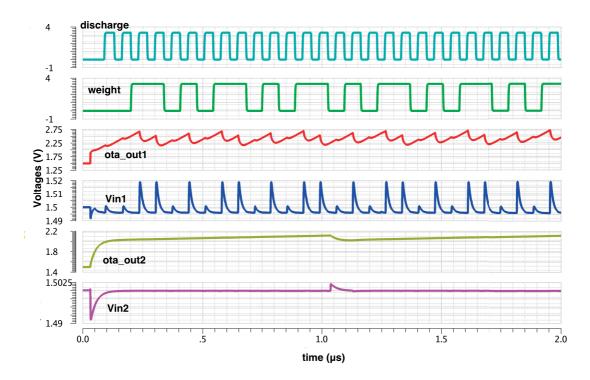

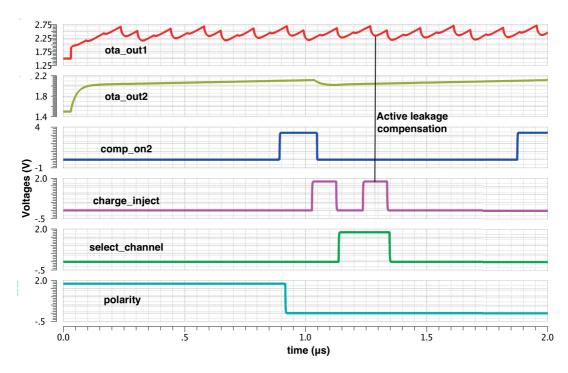

| 4.3  | Simulation of the signals "weight", "ota_out1", " $V_{in1}$ ", "ota_out2", " $V_{in2}$ " (values                                           |    |

| 110  | expressed in (V)), when $I_{in1}$ = -5 $\mu$ A and $I_{in2}$ = -10 nA in a measuring time window                                           |    |

|      | $T_w = 2\mu s \qquad \dots \qquad$ | 52 |

| 4.4  | Simulation of the signals "ota_out1", "ota_out2", "comp_on2", "charge_inject",                                                             |    |

|      | "select_channel", "polarity" (values expressed in (V)) during active leakage cur-                                                          |    |

|      | rent compensation                                                                                                                          | 53 |

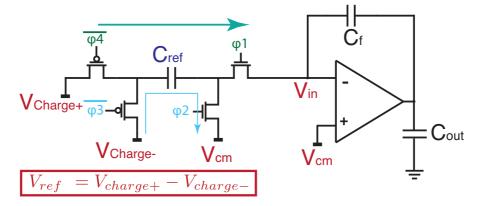

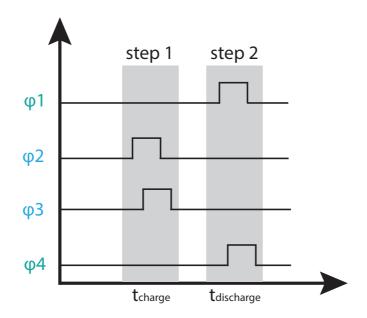

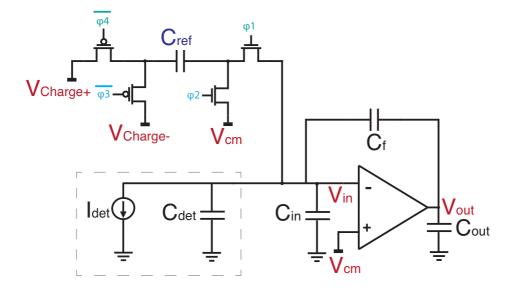

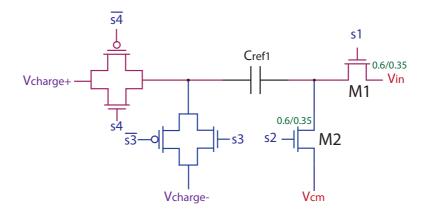

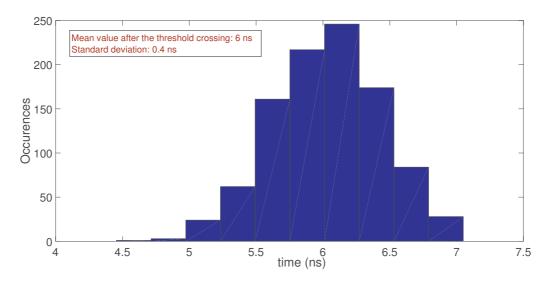

| 4.5  | Parasitic insensitive switched capacitor inverting integrator                                                                              | 55 |

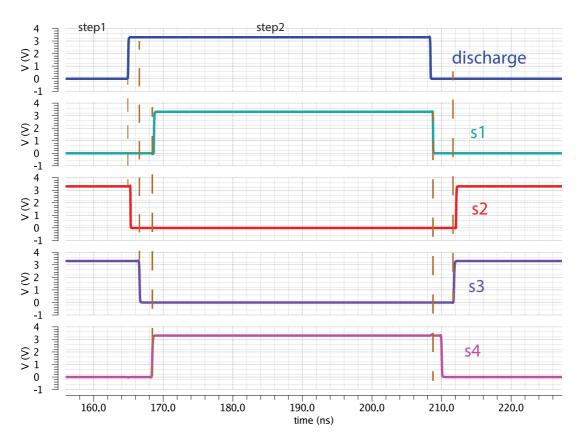

| 4.6  | Switch timing for a charge subtraction                                                                                                     | 56 |

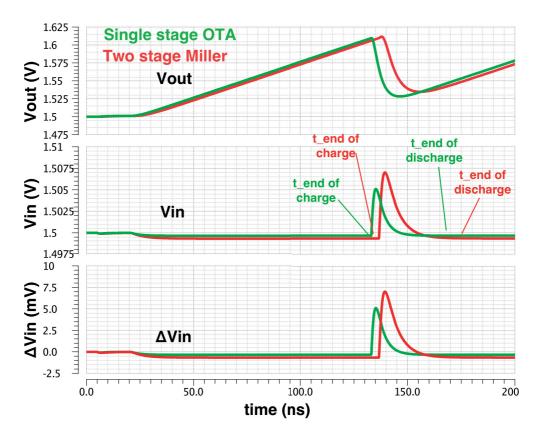

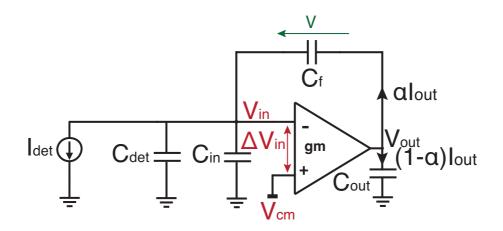

| 4.7  | Integrator with switched capacitor circuit                                                                                                 | 57 |

| 4.8  | The integrators' output voltage $V_{out}$ , input voltage $V_{in}$ and $\Delta V_{in}$ for a single                                        |    |

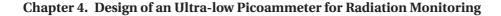

|      | stage OTA and a two stage op-amp                                                                                                           | 58 |

| 4.9  | Single stage OTA                                                                                                                           | 59 |

| 4.10 | Two stage op-amp                                                                                                                           | 60 |

| 4.11 | Percentage error in the expected number of counts in a single stage OTA, a two                                                             |    |

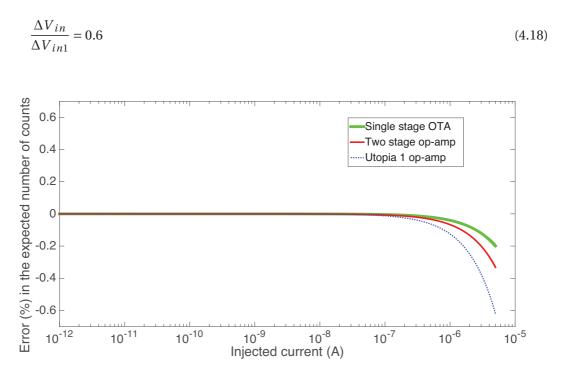

|      | stage op-amp and the Utopia 1 Miller op-amp                                                                                                | 61 |

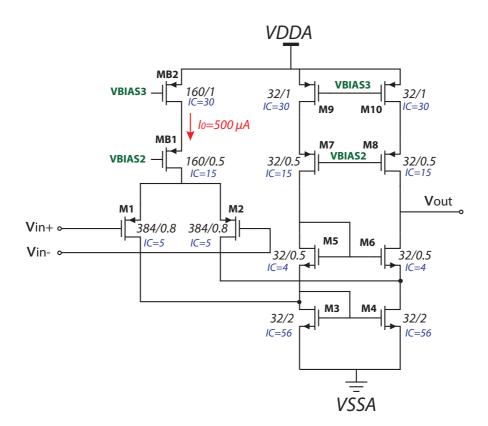

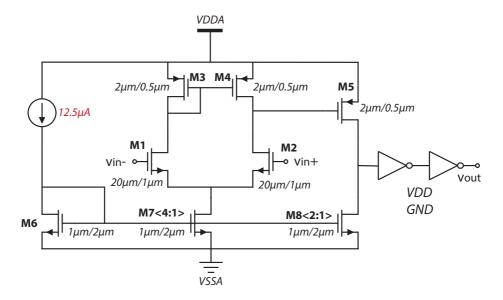

| 4.12 | Folded cascode OTA of Utopia 2 ASIC. The presented transistor sizes are in $\mu$ m                                                         | 65 |

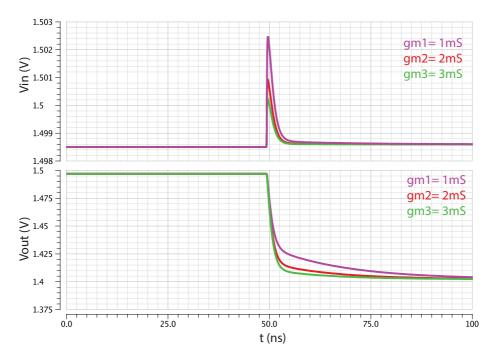

| 4.13 | Simulation of the discharging phase in a single stage OTA for different $g_m$ values                                                       | 66 |

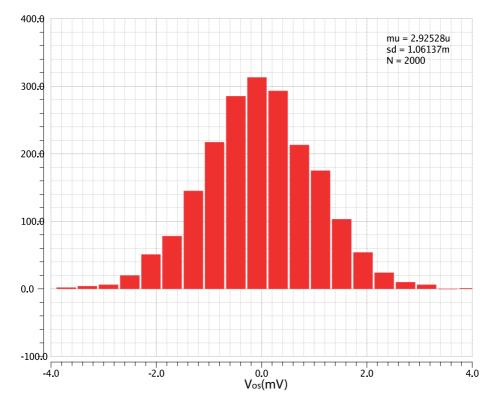

| 4.14 | Offset voltage of the folded cascode OTA                                                                                                   | 66 |

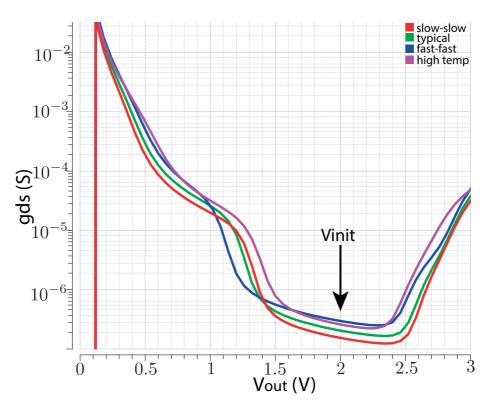

| 4.15 | Output conductance of the folded cascode OTA of Utopia 2 ASIC                                                                              | 67 |

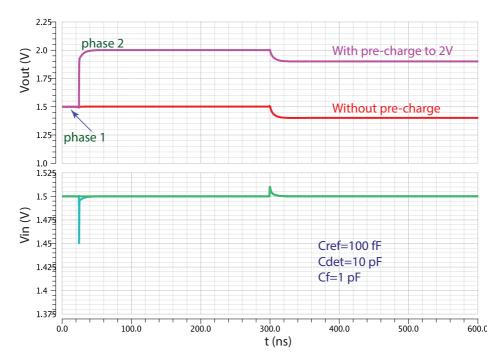

| 4.16 | Transient analysis ( $V_{out}$ and $V_{in}$ ) during charge injection in channel 1                                                         | 67 |

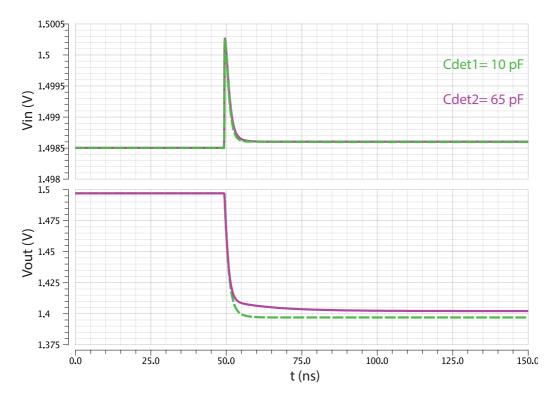

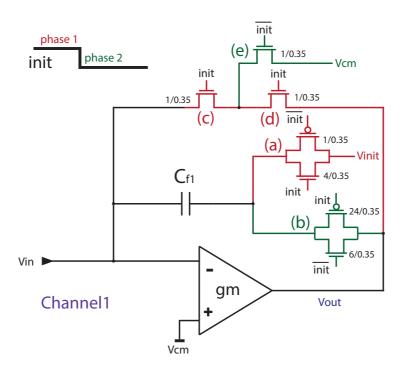

| 4.17 | Transient simulation ( $V_{in}$ and $V_{out}$ ) for the two different detector capacitances                                                |    |

|      | $C_{det1}$ = 10pF and $C_{det2}$ = 65pF                                                                                                    | 68 |

| 4.18 | Initialization (phase 1) and operating (phase 2) phases of the integrator for                                                              |    |

|      | channel 1. All the transistor sizes are in $\mu$ m                                                                                         | 70 |

| 4.19 | Comparator schematic                                                                                                                       | 71 |

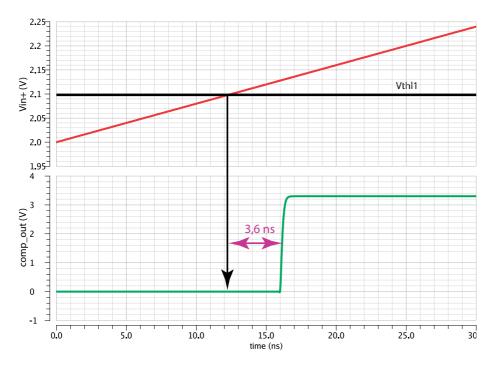

| 4.20 | Transient simulation of comparator's input and output voltages                                                                             | 71 |

| 4.21 | Low range switched capacitor discharging circuit                                                                                           | 72 |

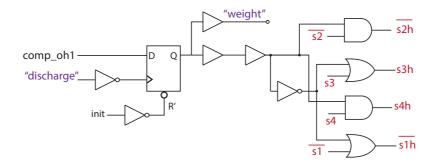

| 4.22 | Signals generated from the NOC that manage the switches of the switched                                  |     |

|------|----------------------------------------------------------------------------------------------------------|-----|

|      | capacitor circuits. The presented signals correspond to nMOS switches                                    | 73  |

| 4.23 | Monostable schematic                                                                                     | 74  |

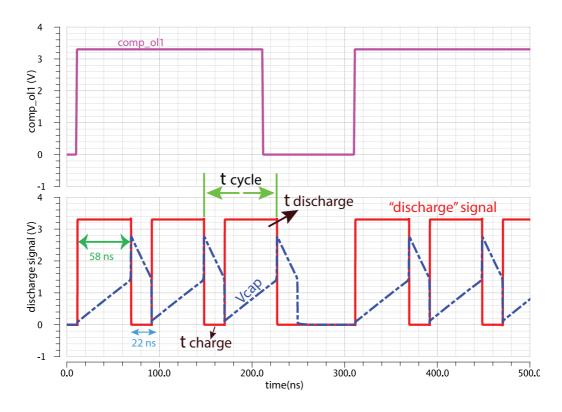

| 4.24 | Simulation of " <i>comp_ol1</i> " and " <i>discharge</i> " when $V_{BR}$ = 1.68 V and $V_{BF}$ = 1.94 V. | 75  |

| 4.25 | Non-overlapping clock circuit                                                                            | 75  |

| 4.26 | Controls of high and low range for channel 1                                                             | 76  |

| 4.27 | ' High range control circuitry                                                                           | 76  |

| 4.28 | Schematic of the discharging circuit of channel 2 for both polarities                                    | 77  |

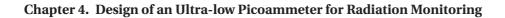

| 4.29 | Jitter in the "discharge" signal                                                                         | 78  |

| 4.30 | Noise across $C_{ref}$ capacitor during charging and discharging phase                                   | 78  |

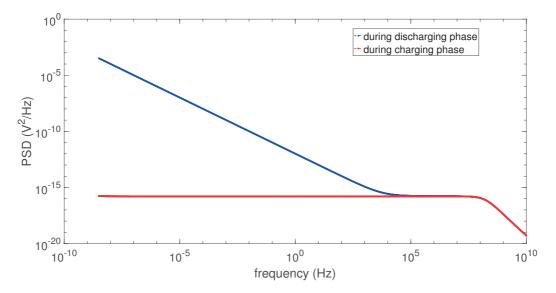

| 4.31 | PSD of the voltages across $C_{ref}$ during charging and discharging phase                               | 79  |

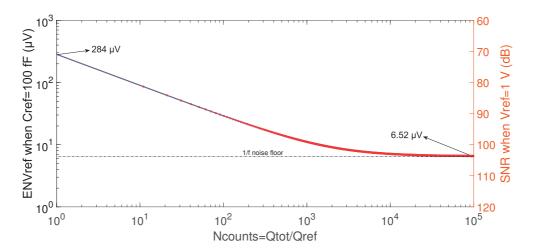

| 4.32 | $V_{ref}$ -referred noise contribution of $C_{ref}$ switching noise versus number of                     |     |

|      | counts N <sub>counts</sub>                                                                               | 80  |

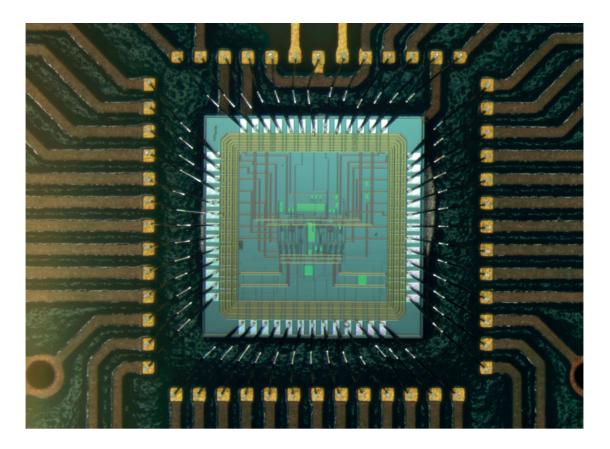

| 4.33 | Utopia 2 microscopic picture                                                                             | 81  |

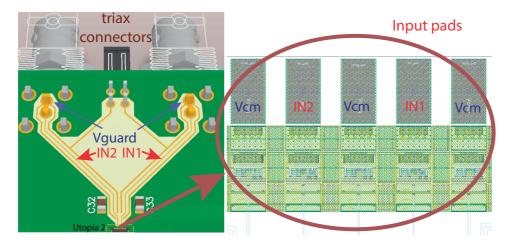

| 4.34 | Utopia 2 PCB input and pads                                                                              | 82  |

| 4.35 | Utopia 2 input pads with their ESD protection diodes                                                     | 83  |

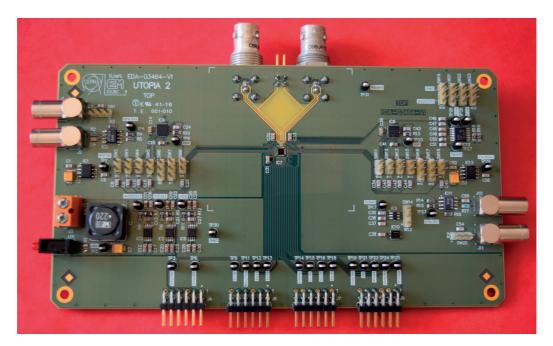

| 4.36 | Utopia 2 PCB                                                                                             | 83  |

|      |                                                                                                          |     |

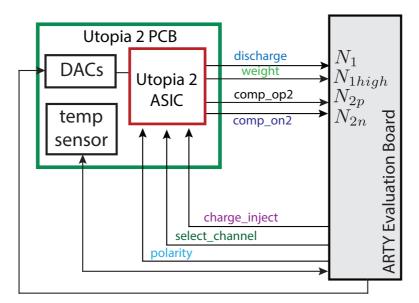

| 5.1  | Block diagram of Utopia 2 measuring system                                                               | 86  |

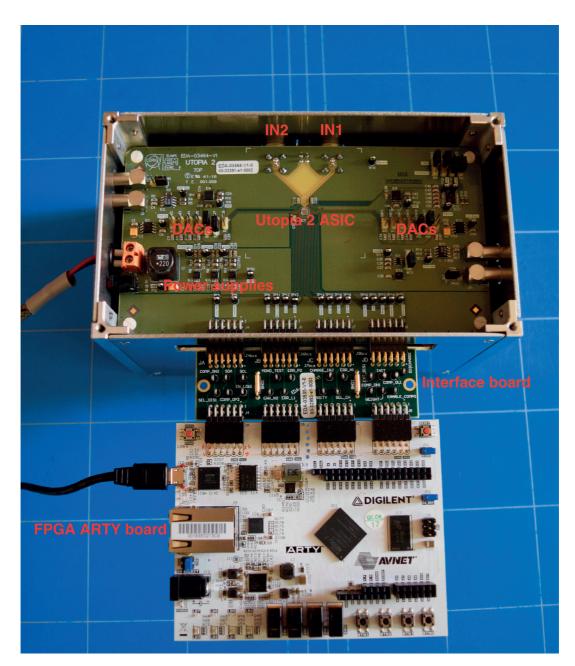

| 5.2  | Utopia 2 PCB and DAQ board                                                                               | 87  |

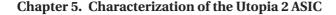

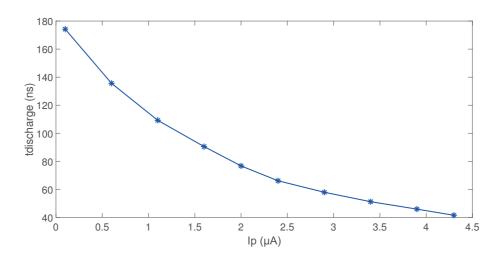

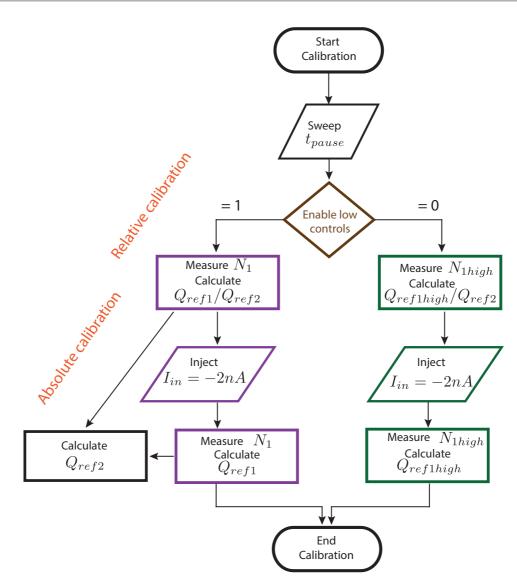

| 5.3  | Utopia 2 ASIC calibration procedure                                                                      | 88  |

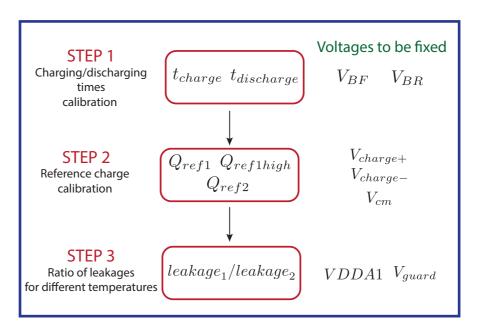

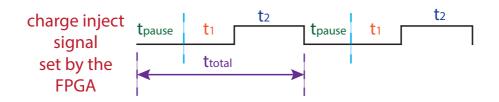

| 5.4  | Charging time $t_{charge}$ of the switched capacitor circuit versus $I_n$                                | 89  |

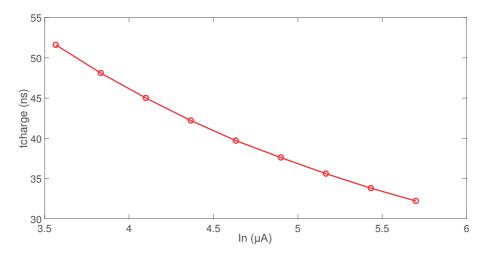

| 5.5  | Discharging time $t_{discharge}$ of the switched capacitor circuit versus $I_p$                          | 89  |

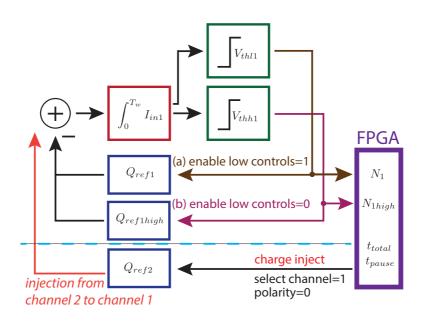

| 5.6  | Block diagram of the reference charge calibration                                                        | 90  |

| 5.7  | Flowchart of the reference charge calibration procedure                                                  | 91  |

| 5.8  | "Charge_inject" signal during $Q_{ref1}$ , $Q_{ref1high}$ and $Q_{ref2}$ calibration                     | 91  |

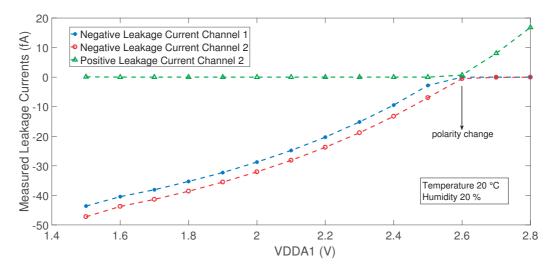

| 5.9  | Measured leakage currents versus <i>VDDA1</i> at 20°C and 20% humidity                                   | 94  |

|      | Measured leakage currents versus $V_{guard}$ at 20°C and 20% humidity                                    | 95  |

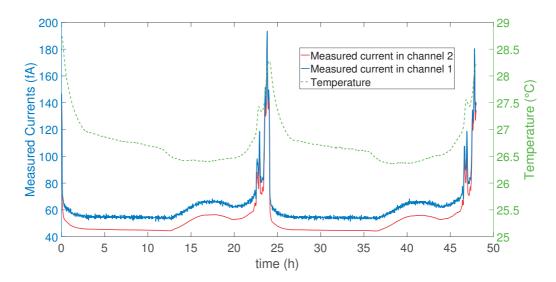

|      | Measured leakage currents and temperature over time when $VDDAI = 1.6 V$                                 | 96  |

|      | Measured leakage current in channel 1 as a function of temperature                                       | 96  |

|      | Ratio of the leakage currents between channel 1 and channel 2                                            |     |

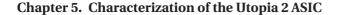

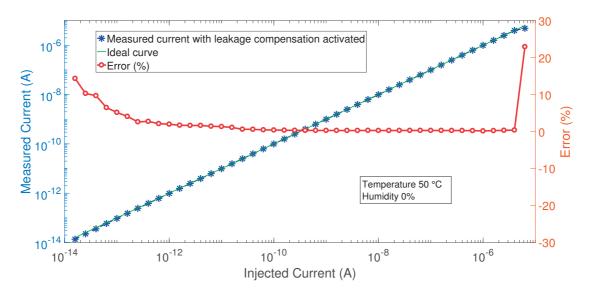

|      | Dynamic range sweep from 20 fA to 6 $\mu$ A at 25°C without the leakage compensation                     |     |

| 5.15 | Dynamic range sweep from 20 fA to 6 $\mu \rm A$ at 50 $^{\circ}\rm C$ without the leakage compensation   | 98  |

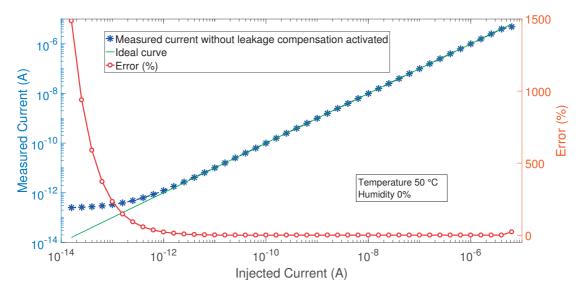

| 5.16 | Dynamic range sweep from 20 fA to 6 $\mu$ A at 25°C with the leakage compensation                        |     |

|      | enabled                                                                                                  | 99  |

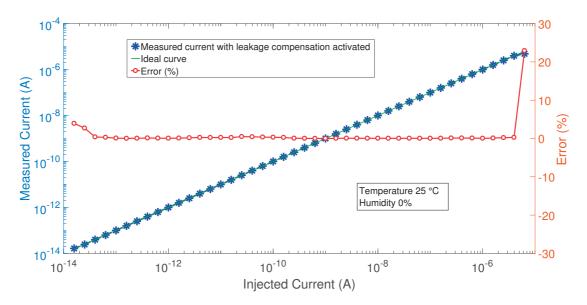

| 5.17 | Dynamic range sweep from 20 fA to 6 $\mu$ A at 50°C with the leakage compensation                        |     |

|      | enabled                                                                                                  | 99  |

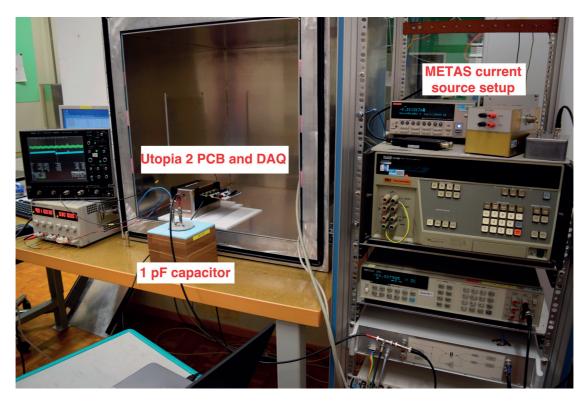

| 5.18 | Testbench at METAS                                                                                       | 100 |

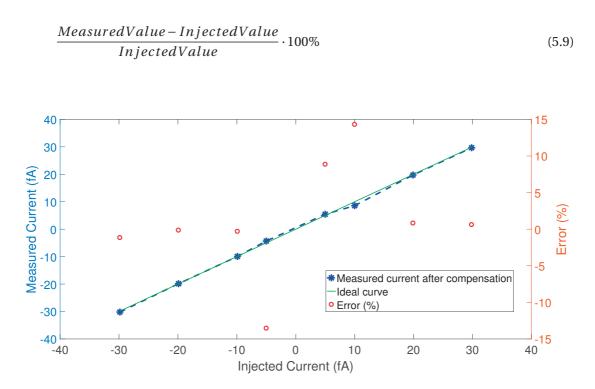

| 5.19 | Injected current from $\pm 5$ fA up to $\pm 30$ fA versus measured current after leakage                 |     |

|      | current compensation                                                                                     | 101 |

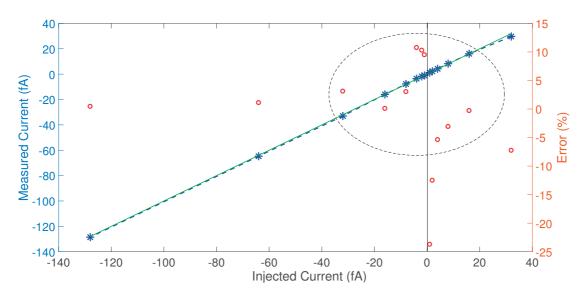

| 5.20 | Injected current from $\pm 1$ fA up to $\pm 128$ fA versus measured current after leakage                |     |

|      | current compensation                                                                                     | 102 |

### List of Figures

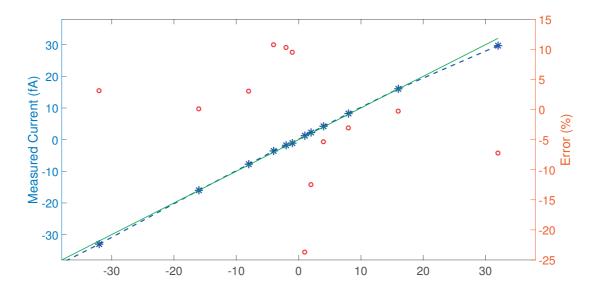

| 5.21 | Injected current from -30 fA up to +30 fA versus measured current after leakage                                                  |   |

|------|----------------------------------------------------------------------------------------------------------------------------------|---|

|      | current compensation                                                                                                             | 2 |

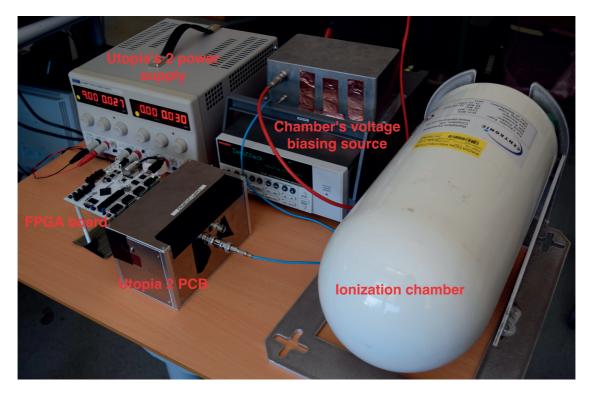

| 5.22 | Laboratory setup for the detector measurements 10                                                                                | 3 |

| 5.23 | Detector's output current for background radiation measurement and measured                                                      |   |

|      | leakage current                                                                                                                  | 4 |

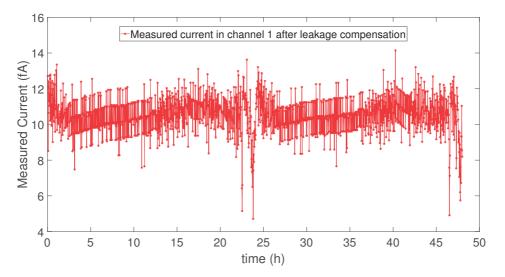

| 5.24 | Detector's compensated output current for background radiation measurement 10                                                    | 4 |

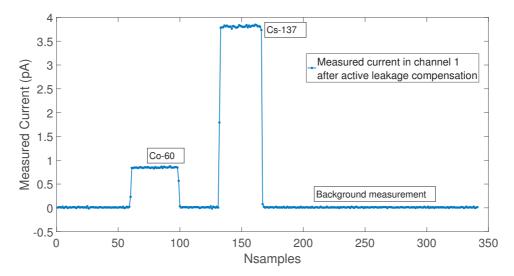

| 5.25 | Detector's output current $I_{det}$ for two different radiation sources, <sup>60</sup> <i>Co</i> and <sup>137</sup> <i>Cs</i> 10 | 5 |

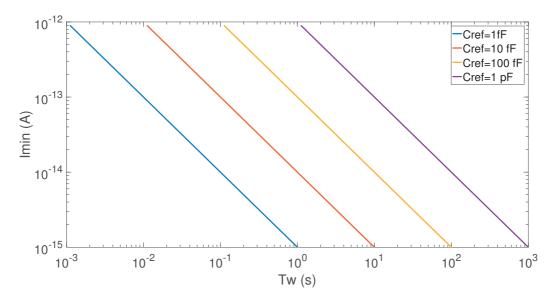

| 6.1  | Sub-picoampere currents $I_{min}$ versus $T_w$ for different $C_{ref}$ values                                                    | 1 |

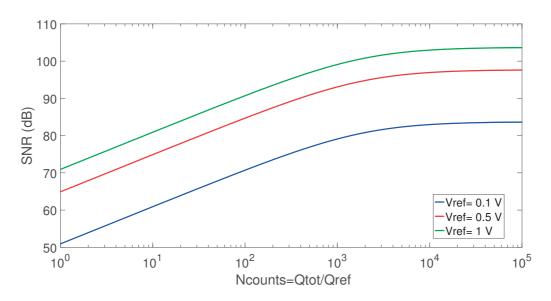

| 6.2  | SNR versus $N_{counts}$ for different voltage reference $V_{ref}$ values                                                         | 2 |

# List of Tables

| 2.1 | Radiation Protection Ionization Chambers used at CERN                        | 9   |

|-----|------------------------------------------------------------------------------|-----|

| 2.2 | Detector Types with Associated Conversion Factors and Derived Output Current |     |

|     | Ranges [21]                                                                  | 10  |

| 2.3 | Readout Electronics Performance Requirements [21]                            | 10  |

| 2.4 | Comparison among ASICs for Radiation Monitoring                              | 15  |

| 3.1 | Volume Resistivity of Various Insulating Materials [73]                      | 26  |

| 3.2 | Summary of Utopia 1 ASIC Characteristics                                     | 30  |

| 3.3 | Leakage Current Measurements                                                 | 38  |

| 3.4 | Updated Comparison among ASICs for Radiation Monitoring                      | 45  |

| 4.1 | Utopia 2 Outputs                                                             | 53  |

| 4.2 | Utopia 2 Inputs                                                              | 54  |

| 4.3 | Possible $Q_{ref}$ Implementations                                           | 54  |

| 4.4 | Utopia 2 Design Values                                                       | 56  |

| 4.5 | Expected Non-Idealities Summary                                              | 65  |

| 4.6 | Simulated Charge Injection Error                                             | 72  |

| 4.7 | Summary of Utopia 2 ASIC Characteristics                                     | 81  |

| 5.1 | Relative Calibration of $Q_{ref1}$ and $Q_{ref1high}$                        | 93  |

| 5.2 | Calibrated $Q_{ref1}$ , $Q_{ref1high}$ and $Q_{ref2}$ values                 | 93  |

| 5.3 | Measurements at METAS                                                        | 101 |

| 5.4 | Updated Comparison among ASICs for Radiation Monitoring including Utopia     |     |

|     | 2 ASIC                                                                       | 107 |

### **1** Introduction

### **1.1 CERN**

The European Organization for Nuclear Research (CERN) sits astride the Franco-Swiss border near Geneva and was founded in 1954. It has since become the largest particle physics laboratory in the world. The purpose of CERN is to study the basic constituents of matter, the fundamental particles and enhance our understanding of the fundamental laws of nature. Inside CERN's accelerator complex, particle beams collide with targets or against each other at speeds close to the speed of light. The detectors that monitor the collisions give the physicists clues about how particles interact.

Protons and lead ions are accelerated in the Large Hadron Collider (LHC). For the protons firstly, Linac 2 accelerates them to the energy of 50 MeV. The proton beam is then injected into the Proton Synchrotron Booster (PSB), which accelerates it to 1.4 GeV, followed by the Proton Synchrotron (PS), which enhances the beam to 25 GeV. Protons are then sent to the Super Proton Synchrotron (SPS) where they are accelerated to 450 GeV. The protons are finally transferred to the two beam pipes of the LHC, where the beam in one pipe circulates clockwise, while the beam in the other pipe circulates anti-clockwise. There, beams are accelerated to energy up to 6.5 TeV and then circulate for many hours being focused and brought into collision inside the four detectors installed in underground caverns. The detectors are [1]:

- A Large Ion Collider Experiment (ALICE)

- ATLAS

- Compact Muon Solenoid (CMS)

- Large Hadron Collider beauty (LHCb)

The total energy at the collision point is equal to 13 TeV.

Similarly, the lead ions for the LHC start from Linac 3, before being collected and accelerated in the Low Energy Ion Ring (LEIR) and then follow the same route as the protons. The current CERN accelerator complex is shown in figure 1.1 [2].

Figure 1.1 – CERN accelerator complex [2]

### 1.2 Radiation Monitoring at CERN

The operation of the CERN accelerators induces ionizing radiation and radioactivity due to the interaction of high energy beam particles with matter. Monitoring of the ionizing radiation inside and around CERN's accelerator complex is challenging due to the pulsed nature of the particle beams and the large dimensions of the CERN facilities [3]. The radiation levels should be continuously monitored in order to protect the public and the personnel from any unjustified exposure to ionizing radiation. This is a legal obligation set by national and international regulations. CERN has to comply with the environmental regulations that set an annual dose limit which must not be exceeded [4].

The CERN's radiation protection policy [5] stipulates that the exposure of persons to ionizing radiation and the radiological impact and pollution of the environment should be As Low As Reasonably Achievable (ALARA) [6], [7]. The ALARA principle sets the requirements for a sophisticated radiation monitoring system. The general principles of the radiation protection

legislation and the classification of radiological risks and areas inside CERN are analyzed in the "Radiation protection at CERN" article [8].

CERN's Occupational Health & Safety and Environmental Protection (HSE) Unit monitors the ambient dose equivalent rates inside and outside CERN's perimeter. The radiation monitoring allows the preventive assessment of the radiological hazards and the minimization of individual and collective doses to the public or workers. The RAdiation Monitoring System for the Environment and Safety (RAMSES) comprises more than 350 monitors that perform continuous real time measurements of the radiation levels on the surface of CERN premises and in underground accessible areas [9]. The RAMSES system includes the radiation monitors, the data acquisition and the processing unit. The system also generates alarms and interlock signals. It provides long term data logging of the measured values and of the alarms. The recorded data are required to prove CERN's compliance with the relevant legislation and to report to the host states authorities.

Figure 1.2 - Functional diagram of the CERN radiation monitoring system [3]

The functional diagram of the CERN's radiation monitoring system is illustrated in figure 1.2. The ionizing radiation monitor (1) is selected according to the specific properties of the monitored area and includes the ionizing radiation detector (a) and its readout electronics (b). The system includes an alarm unit (2) and can generate interlock signals (3) if required. Parts (1), (2) and (3) form a Basic Autonomous Cell (4) that is supplied by the monitoring station (5) that acquires and stores the produced data. The Supervisory Control and Data Acquisition (SCADA) system noted as (6) transfers the monitored data to the Database (7). Finally, the data can be assessed by the Clients (8) using a user friendly interface [3].

### **1.3 Thesis Outline**

A state of the art radiation monitoring system is important for CERN for avoiding any unjustified doses to the public or pollution of the environment. To achieve its objectives the system should integrate a set of functions presented in the functional diagram of figure 1.2. The current thesis focuses on the dedicated integrated circuit design of the most demanding part of the system, the readout front-end electronics (b) used to digitize the signals that are generated by the radiation detector (a). Up to now, commercial off-the-shelf (COTS) electronics were used for the readout system at CERN. These components do not meet all the required specifications. The design of an integrated circuit is motivated by the need to digitize ultra-low input currents over a wide dynamic and temperature range.

The thesis is organized as follows:

In the **second chapter**, the various radiation detectors currently used at CERN are presented. The main challenge is that the detectors produce output currents that start from the femtoampere range (fA) and span up to microamperes ( $\mu$ A). The existing systems for monitoring ionizing radiation used in High Energy Physics (HEP) experiments, nuclear facilities and hospitals are reviewed and the state of the art is presented.

The **third chapter** focuses in sub-picoampere current measurements and discusses the main limitations when measuring in the femtoampere (fA) range. The net leakage current in the input of the front-end is comparable to the signal to be measured. The different leakage current sources present at the input of the readout system are identified and characterized in order to set the achievable limits for ultra-low current measurements. The development of an Application Specific Integrated Circuit (ASIC) named Ultra-low Picoammeter 1 (Utopia 1) is presented. Its design aims at estimating the lowest possible current that can be measured with a system built with the selected technology. The guidelines that this prototype set for ultra-low current measurements are outlined.

The **fourth chapter** presents the design procedure and the architecture of the Ultra-low Picoammeter 2 (Utopia 2) ASIC. This ASIC is the proposed integrated solution for the front-end of the new radiation and environmental monitoring system for personnel and public safety at CERN. This ASIC is designed in a way that the net leakage current is minimized according to the guidelines that were set with the demonstrator Utopia 1 ASIC. It operates faster than Utopia 1 and incorporates an on-chip active leakage current compensation technique that makes the chip performance insensitive to temperature variations. The automatic two-range charge balancing circuit that manages the higher input currents is also presented.

In the **fifth chapter**, the data acquisition system, the calibration procedure, the characterization and the measurements of Utopia 2 ASIC are reported. The results of the tests performed at the Swiss Federal Institute of Metrology (METAS) are shown. Qualitative radiation measurements with the detector are also presented. Finally, the conclusions and the contributions of the current thesis are drawn. The performance of the designed ASIC is discussed. The presented guidelines for the femtoampere current measurements can be followed in any system that targets ultra-low current sensing performance.

## 2 Front-end Electronics for Gas-Filled Detectors

### 2.1 Introduction

The most widely used ionizing radiation detectors are ionization chambers. In this chapter, the available radiation detectors used at CERN are presented. The specifications for the front-end readout electronics for the new radiation monitoring system are set according to the detectors in use at CERN. The readout system should be able to cover the required dynamic range of the various detectors. Depending on the detector, the output current is as low as a few femtoamperes (fA) and spans up to the microampere ( $\mu$ A) range. This chapter also presents the Current to Frequency Converter (CFC) architecture that is suitable for current digitization over the required wide dynamic range. The state of the art for radiation monitoring front-ends is reviewed and the most recent developments in particle physics experiments and hadron therapy institutes are briefly explained.

### 2.2 Gas-Filled Detectors

When radiation passes through a gas, it ionizes the gas molecules. The produced electron and ion pairs move in opposite directions due to the applied external electric field, thus resulting in an electric charge that can be collected and measured [10]. A gas-filled detector consists of the enclosure, the positive and the negative electrodes as shown in figure 2.1. The bias voltage is applied to the electrodes in order to produce the desired electric field. Based on the applied bias voltage, the gas detectors operate in different regions. In the ion chamber region, all the produced charges are efficiently collected by the electrodes. The gas detectors that operate in this region are called ionization chambers.

#### 2.2.1 Ionization chambers

Ionization chambers are the most widely used radiation detectors because of their design simplicity and their well understood operating principle [11]. The output current measured

Figure 2.1 - Cylindrical gas-filled detector

by the readout electronics is proportional to the energy deposited by the incident radiation as shown in figure 2.2. An advantage of the ionization chamber is the existence of a plateau region without significant slope, where the measured current does not increase with a bias voltage increase.

Figure 2.2 – Output current and bias voltage characteristic curves of an ionization chamber at different incident radiation intensities

Apart from the applied voltage, the production of charge pairs also depends on the geometry of the detector and the choice of the gas. Regarding the geometry, the most common are the parallel plates ionization chambers and the cylindrical ionization chambers [12]. The choice of the gas and its pressure is application dependent.

### 2.2.2 Ionization chambers used at CERN

The monitoring of the mixed radiation fields is important when performing High Energy Physics (HEP) experiments. In case of high energy accelerators like the LHC, the radiation fields consist of neutrons, charged hadrons and photons [13]. This is why it is important

to use detectors that respond to the different types of radiation without compromising the required sensitivity, according to the area and to the parameters that need to be monitored [14]. The detectors currently used at CERN for radiation monitoring of the work places are high pressure ionization chambers. These ion-chambers are also suitable for environmental radiation monitoring.

The characterization and the calibration of the Argon IG5-A20 and Hydrogen IG5-H20 filled high-pressure ionization chambers manufactured by Centronic Ltd [15], is performed at CERN using standard source generated photon and neutron fields. The selected chambers were characterized by simulating their response using the FLUKA software [16] [17]. These chambers have an active volume of 5000  $cm^3$  and a pressure of 20 bar.

Inside CERN's accelerator complex, simple and robust air-filled plastic chambers (PTW T32006) [18] are installed. These ionization chambers, that operate at atmospheric pressure, are used for the remote reading of the ambient dose equivalent rates inside the tunnels and the experimental caverns after the beam has been stopped. They measure the radiation that is emitted by the decay of the radionuclides induced during operation [19]. These air-filled detectors are made of polyethylene (PE) and have an active volume of  $3079 \ cm^3$ . These devices have also been characterized using FLUKA simulations and experimental measurements at the CERN facilities [20].

| Monitor type                          | Detector<br>model    | Radiation type                                               | Detector type                                      | Measurement<br>range      |

|---------------------------------------|----------------------|--------------------------------------------------------------|----------------------------------------------------|---------------------------|

| Area gamma<br>monitor<br>AGM          | CENTRONIC<br>IG5-A20 | Photons, muons                                               | High pressure<br>Argon<br>ionization<br>chamber    | 50 nSv/h - 0.1 Sv/h       |

| Area mixed<br>field monitor<br>AMF    | CENTRONIC<br>IG5-H20 | High energy<br>charged particles,<br>neutrons<br>and photons | High pressure<br>Hydrogen<br>ionization<br>chamber | 50 nSv/h - 0.1 Sv/h       |

| Induced<br>activity<br>monitor<br>IAM | PTW T32006           | Photons                                                      | Air filled<br>ionization<br>chamber                | 1 <i>µ</i> Sv/h - 10 Sv/h |

| Table 2.1 – Radiation | Protection Ior | nization Chamb | ers used at CERN |

|-----------------------|----------------|----------------|------------------|

|                       |                |                |                  |

Table 2.1 presents the ionization chambers used at CERN and the radiation type that they are sensitive to. It also shows the requested measurement range. By using the typical conversion factor for each detector, the output current is calculated as shown in Table 2.2 [3], [21]. The input current requirements for the front-end electronics are determined by this table.

The readout electronics should be able to digitize input currents starting from 2 fA up to 250 nA. In extreme cases, due to the pulsed radiation fields the output current can reach a few  $\mu$ A.

| Monitor type | Measurement range                     | Typical conversion<br>factor [A/Sv/h]                | Output current range            |

|--------------|---------------------------------------|------------------------------------------------------|---------------------------------|

| AGM          | 50 nSv/h - 0.1 Sv/h                   | $\gamma$ : 1.6 $\cdot$ 10 <sup>-6</sup>              | 80 fA - 160 nA                  |

| AMF          | 50 nSv/h - 0.1 Sv/h                   | $\gamma: 1.13 \cdot 10^{-7}$<br>$n: 4 \cdot 10^{-8}$ | 5.7 fA - 11.3 nA<br>2 fA - 4 nA |

| IAM          | $1 \mu\text{Sv/h}$ - $10 \text{Sv/h}$ | $\gamma$ : 2.5 $\cdot$ 10 <sup>-8</sup>              | 25 fA - 250 nA                  |

Table 2.2 – Detector Types with Associated Conversion Factors and Derived Output Current Ranges [21]

| Parameter               | Range / Value                         | Remark                        |

|-------------------------|---------------------------------------|-------------------------------|

| Measurement range       | 2 fA to 5 $\mu$ A                     | Input current range           |

|                         |                                       | Smallest change in the input  |

| Resolution              | 1 fA                                  | current which causes change   |

|                         |                                       | in the indication             |

|                         |                                       | Closeness of the agreement    |

| A 0.01170.011           | $(1 f \Lambda + 50\% of the reading)$ | between the measurement and   |

| Accuracy                | $\pm$ ( 1 fA + 5% of the reading)     | the conventionally true value |

|                         |                                       | of the measured quantity      |

| Measurement time        | 100 ms for $I_{in} \ge 1$ pA          | Data acquisition time for     |

| Measurement unie        | >100 ms for $I_{in}$ < 1 pA           | current measurements          |

| Operational temperature | 10°C to 40°C                          | Inside temperature            |

| range                   | -15°C to 55°C                         | Outside temperature           |

Table 2.3 - Readout Electronics Performance Requirements [21]

The specifications for the new front-end electronics for radiation monitoring at CERN, are presented in Table 2.3. A single readout circuit is required for all detector types.

### 2.3 Evaluation of the Total Integrated Dose over Time

The radiation monitoring system has to evaluate the total ionizing radiation dose over time. This is possible by using charge sensitive amplifiers where the input current is integrated in a capacitor. Historically, in nuclear physics experiments, for example for ionizing radiation monitoring or when measuring electric charge for dosimetry, the most common and widely used approach is the Current to Frequency Converter (CFC).

The CFC is the best way to evaluate the total integrated dose in terms of linearity, simplicity and dynamic range. In a CFC, the input current is integrated using an integrator. The inte-

grator's output voltage  $V_{out}$  ramp slope varies according to the input current  $I_{in}$ . When that ramp voltage reaches a predetermined threshold  $V_{th}$  set by a comparator, the integrator's feedback capacitance  $C_f$  is discharged and the cycle repeats. Therefore, the output frequency of operation is proportional to the input current.

The circuit's operating frequency f is given by equation (2.1), where  $Q_{ref}$  is the reference charge that balances the operation.

$$f = \frac{I_{in}}{Q_{ref}} \tag{2.1}$$

The discharge of the feedback capacitance is possible by using a switch to short out the feedback capacitor. The approach of using a feedback switch  $S_1$  for discharging the feedback capacitor  $C_f$  is presented in figure 2.3(a). After the comparator threshold  $V_{th}$  crossing, the one-shot produces a pulse that closes the switch  $S_1$  and discharges the capacitor. The capacitor  $C_f$  loses a charge  $Q_{ref}$  equal to  $C_f V_{th}$  and the cycle restarts. This approach has the disadvantages of charge loss and linearity error [22], [23]. The circuit is insensitive during the discharge-reset time because the integrating capacitor is shorted and the input current is not integrated. Additionally, the reset time  $t_{reset}$  has an effect on the linearity of the circuit since:

$$I_{in} = \frac{C_f V_{th}}{T - t_{reset}} \tag{2.2}$$

where *T* is the output period. From equation (2.2) it can be seen that the output frequency and the average input current are not proportional especially when the circuit operates at high frequencies.

An alternative method that has more advantages is based on the recycling integrator circuit through charge balancing, where the input current is continuously integrated and thus there is no charge lost [24], [25], [26], [27], [28] and [29]. When the integrator's output voltage reaches a threshold voltage  $V_{th}$ , a reference charge  $Q_{ref}$  is added to or subtracted from the input according to the input current polarity. A pulse is issued at the output every time the reference charge is injected. By pulse counting, the input ionization current can be measured.

Figures 2.3(b) and 2.3(c) present two different implementations of the CFC with charge balancing. The reference charge injected in the input can be realized using current sources or switched capacitors. In the first case, an accurate current  $I_{ref}$  is injected into the input for a precise time  $t_{ref}$ . In that case  $Q_{ref} = I_{ref} t_{ref}$ . In the second case, a capacitor  $C_{ref}$  is charged to a precise voltage  $V_{ref}$  and then is connected to the integrator's input so  $Q_{ref} = C_{ref} V_{ref}$ .

The current to frequency conversion through charge balancing is suitable for radiation mon-

itoring because the current integration is not interrupted, the input charge is not lost due to switching and the conversion depends only on the reference charge  $Q_{ref}$ . This method demonstrates good linearity and wide dynamic range [22].

### 2.4 State of the Art

The most recent developments for radiation monitoring for beam monitor chambers are based on the same principle of current to frequency conversion through charge balancing.

A family of multipurpose ASICs named TERA [30] has been developed by the Istituto Nazionale di Fisica Nucleare (INFN) and the University of Torino for the monitoring and control of hadron therapy beams. In the past years there have been many developments in many technologies starting from 1.2  $\mu$ m CMOS [31] and 0.8  $\mu$ m CMOS [32], [33], [34], with the most recent implemented in 0.35  $\mu$ m technology [35], [36], [37], [38]. The ASICs are used to equip ionization chambers for medical treatment facilities. They are based on the current to frequency conversion and the recycling integrator principle. These 64-channel ASICs demonstrate a wide dynamic range. The measured background current has a mean value of 230 fA in TERA07 designed in 0.35  $\mu$ m technology. The recently developed ASIC in 0.35  $\mu$ m technology named TERA09, has extended the maximum current range up to 750  $\mu$ A in order to comply with clinical pulsed particle beams [39], [40].

Another important development is an ASIC that was designed for CERN's beam loss monitoring (BLM) system. The BLM ASIC aims at digitizing current signals from ionization chambers and diamond detectors [41], [42], [43], [44]. It is a radiation tolerant 120-dB dynamic range incremental charge to digital converter. The conversion is performed using an adjustable temperature-compensated current reference in a 40  $\mu$ s integration time window. This two-channel synchronous multi-ranging converter is implemented in a commercial 0.25  $\mu$ m CMOS technology and is able to digitize bipolar input currents from a few pA after averaging, up to 1.05 mA.

Another ASIC for radiation monitoring was designed by the GSI Helmholtz Centre for Heavy Ion Research in AMS 0.35  $\mu$ m technology [45]. This ASIC demonstrates a dynamic range of more than 7 decades without range switching. The operating principle again is based on the charge to frequency converter. The integrator's output voltage is continuously compared with a threshold voltage generated by a Digital to Analog Converter (DAC). The first version of the ASIC named QFW I, can measure currents from 1.6 pA up to 180  $\mu$ A. The readout chip interfaces with Multi-Wire Proportional Chambers (MWPC) and other beam devices like Faraday-cups and ionization chambers [46], [47].

The aforementioned works and their upgrades, mostly aim at increasing the dynamic range at the upper end [38]. However, all these ASICs are limited at the lower end by the net input leakage currents. This is the reason why the lowest reported measurable current is limited to 194 fA for TERA06 [34] and -188 fA for BLM ASIC [41]. The specifications for the CERN's

Figure 2.3 – (a) CFC with shorting switch, (b) CFC with charge balancing using a current source, (c) CFC with charge balancing using a switched capacitor

readout electronics require a minimum measurable current of 2 fA.

Table 2.4 summarizes the characteristics of these ASICs.

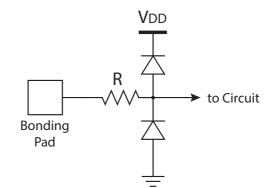

The commercial system currently used at CERN for radiation monitoring is built with COTS components. It is based on the current to frequency converter architecture where a feedback switch is shorting the input and the output to reset the integrator. The switched capacitor integrator currently used at CERN is the IVC 102 from Texas Instruments [48] which has a typical leakage current of 100 fA at 25°C.

Some other commercial ultra-low leakage amplifiers are available on the market [49], [50], [51].

### 2.5 Chapter Conclusions

Ultra-low current measurements are important for radiation monitoring when using ionization chambers. The output of the detector, especially when the natural background radiation is measured, is in the order of femtoamperes. The current to frequency converter topology can be used for the evaluation of the total ionizing radiation dose over time. The design of the readout circuit for radiation monitoring is challenging because of the dynamic range requirements, the linearity constraints and the leakage currents present at the input of the system.

The ASIC implementations presented in Table 2.4 are limited in the low range because of the leakage currents that are injected from various sources and are added to the input signal. The strict requirements for the background radiation monitoring at CERN require a digitizer that demonstrates better performance than the current state of the art. Currents as low as 2 fA should be digitized and measured.

| ng        |

|-----------|

| itoring   |

| ito       |

| n         |

| Ă         |

| 'n        |

| <u>io</u> |

| diation M |

| idi       |

| R         |

| or R      |

| sf        |

| SIC       |

| S         |

| ğ         |

| nc        |

| Ш         |

| 5         |

| on        |

| is        |

| ar        |

| omp       |

|           |

| 0         |

| 4-        |

| 5         |

| ble       |

| ab        |

| Г         |

| Characteristics  | TERA06 [33], [34] | TERA06 [33], [34] TERA09 [39], [40] | QFW I ASIC [45]        | BLM ASIC [41]    |

|------------------|-------------------|-------------------------------------|------------------------|------------------|

| Publication Year | 2004              | 2016                                | 2004                   | 2012             |

| Technology       | AMS 0.8 $\mu m$   | AMS 0.35 $\mu m$                    | AMS 0.35 $\mu m$       | IBM 0.25 $\mu m$ |

| Die Size         | 6mm x 7mm         | 4.68mm x 5.8mm                      | 3.28mm x 3.38mm        | 2.4mm x 3.775mm  |

| Dynamic Range    | 5 decades         | 6 decades                           | 1.60 pA to 180 $\mu A$ | 1 pA to 1.05 mA  |

| Leakage Current  | 194 fA            | 2 pA                                | 1.65 pA                | -188 fA          |

| Linearity Error  | $\pm 1\%$         | ±2%                                 | $\pm 1.5\%$            | ± 5%             |

| Polarity         | Unipolar          | Bipolar                             | Unipolar               | Bipolar          |

| Clock Frequency  | 20 MHz            | 250 MHz                             | 10 MHz                 | 12.8 MHz         |

|                  |                   |                                     |                        |                  |

## 3.1 Introduction

The scope of this chapter is to discuss the main limitations when measuring ultra-low currents, namely the leakage currents in the input of the system. The signal to be measured is comparable to the sum of the leakage currents in the input of the circuit. A basic Current to Frequency Converter (CFC) architecture is presented and the related leakage current contribution is evaluated. The proposed technologies are theoretically compared in terms of leakage current and the selected technology AMS 0.35  $\mu$ m, is verified experimentally by building a demonstrator that allows to measure the different potential sources of leakage currents in the input of the measuring system.

A set of guidelines that can be followed in order to minimize or compensate for the leakage currents is established. These guidelines were not specifically outlined or followed in the previous designs of radiation monitoring systems. The main principles may, however, be used in any similar application that aims at measuring femtoampere currents.

# 3.2 Operating Principle of a Current to Frequency Converter

The front-end electronics that interface with radiation detectors have to digitize the generated current over a wide dynamic range. The simple CFC topology that is depicted in figure 3.1, is based on the recycling integrator scheme and charge balancing. The integrator is continuously integrating without inflicting any dead time. The current  $I_{det}$  that is generated from the current source, in this case the radiation detector, is integrated along with the sum of the leakage currents  $I_{leak}$  in a capacitor  $C_f$  and the output voltage  $V_{out}$  of the integrator is compared with a voltage threshold  $V_{th}$ . When the discriminator triggers, a fixed amount of charge  $Q_{ref}$  is injected into the input through a discharging circuit to discharge the  $C_f$  and balance the accumulated charge. Additionally, a pulse is issued at the output. The injected reference charge  $Q_{ref}$  sets the gain of the conversion. By counting how many times  $N_{counts}$  the reference charge  $Q_{ref}$  is injected in a measuring time window  $T_w$ , the total input current

$I_{in}$  can be calculated using equation (3.1):

$$I_{in} = \frac{N_{counts}Q_{ref}}{T_w}$$

(3.1)

Figure 3.1 - Simple Current to Frequency Converter (CFC) scheme

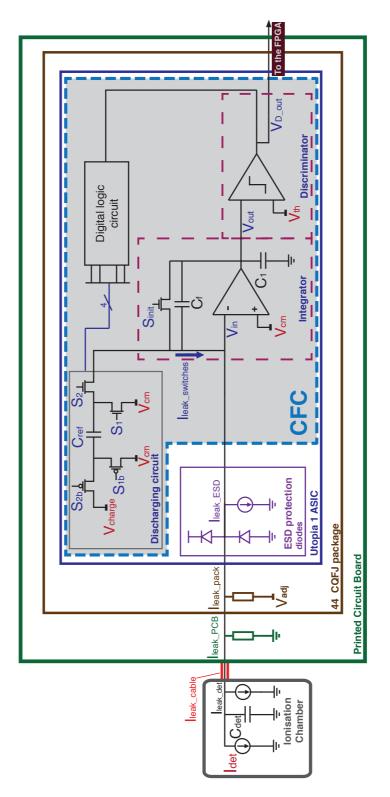

## 3.3 Leakage Currents in the Input of the System

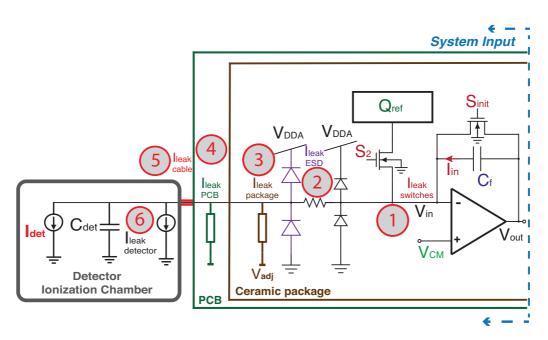

The total current  $I_{in}$  in the input of the system consists of the current signal from the detector  $I_{det}$ , and the sum of all leakage currents that are also injected into the input from various sources. The potential leakage current sources in the input of the integrator, which is the basic structure in the selected system architecture, are depicted in figure 3.2. The net leakage includes the intrinsic leakage related to the chip, but also the leakage that is related to the testbench and the laboratory setup. The leakage related to the chip is dominated by the leakage of the switches (1)  $I_{leak\_switches}$  that are connected to the input and the leakage of the Electrostatic Discharge (ESD) protection diodes (2)  $I_{leak\_ESD}$ . On top of that, the leakage of the package (3)  $I_{leak\_package}$ , the leakage of the Printed Circuit Board (PCB) (4)  $I_{leak\_PCB}$ , the leakage of the cable and the connector (5)  $I_{leak\_cable}$  and finally the leakage of the detector (6)  $I_{leak\_detector}$  should be added as shown in equation (3.2). It should be noted that any contamination with dust or other conductive means close to the signal traces could induce stray leakage current.

$$I_{in} = I_{det} + I_{leak\_detector} + I_{leak\_cable} + I_{leak\_PCB} + I_{leak\_package} + I_{leak\_ESD} + I_{leak\_switches}$$

(3.2)

One of the major challenges in the design of the front-end electronics for radiation monitoring is the leakage current suppression. Depending on the detector's output signal, the net leakage seen in the input of the front-end is comparable or in some cases higher than the ion-current

Figure 3.2 - Potential leakage current sources in the input of the integrator

generated from the detector. This is the limiting case for CERN's ionization chambers that can have an output current starting from a few femtoamperes. The various leakage current sources shown in figure 3.2 are analyzed in this section.

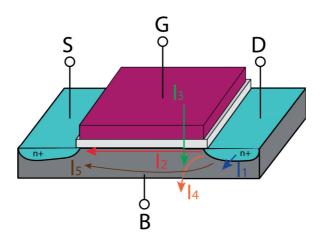

## 3.3.1 Leakage current of the switches

The leakage of the switches  $I_{leak\_switches}$  that are connected to the input can be estimated by studying the leakage current mechanisms for a single MOS device in the OFF-state. A detailed analysis of the leakage current sources in CMOS technologies is presented in [52], [53], [54]. The leakage current mechanisms for an nMOS transistor are depicted in figure 3.3 and namely are the reverse bias p-n junction leakage  $I_1$ , the subthreshold leakage  $I_2$  and the oxide tunneling gate leakage current  $I_3$ . There are also the secondary leakage mechanisms like the Gate-Induced Drain Leakage (GIDL)  $I_4$  and the channel punchthrough current  $I_5$ .

The total OFF-state current can be generally grouped into two categories, the source to drain current and the substrate current. The source to drain includes the subthreshold current  $I_2$  and the punchthrough current  $I_5$  and the substrate current includes the conventional p-n junction leakage  $I_1$  and the GIDL  $I_4$ .

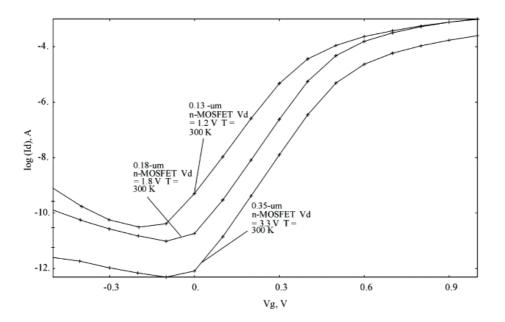

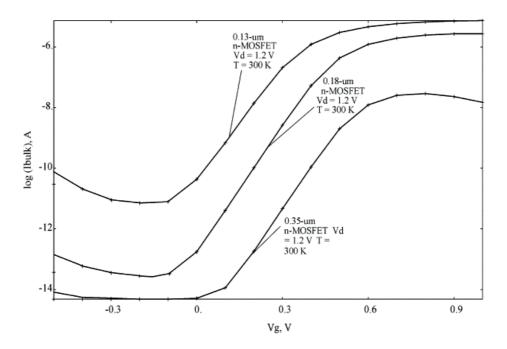

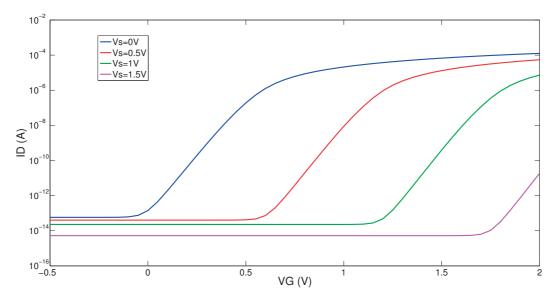

In [55], the drain and bulk current components are simulated and plotted as a function of the gate voltage for the technologies 0.35  $\mu$ m, 0.18  $\mu$ m and 0.13  $\mu$ m. For the sake of clarity these plots taken from that article, are also reproduced with permission and shown in figures 3.4 and 3.5.

These technologies will be considered and compared in terms of leakage currents in order to

Figure 3.3 - Leakage current mechanisms in an nMOS transistor

Figure 3.4 – Drain current versus gate voltage for different CMOS technologies (T = 300K, drain voltage has the nominal value for the given technology). Reproduced with permission from [55]

find the most suitable technology for our application. In the considered technologies, the two dominant contributors are the reverse diode leakage  $I_1$  and the subthreshold leakage  $I_2$ .

Regarding the transistor's leakage mechanisms, the reverse biased drain and source to well junctions, cause a leakage current  $I_1$  that is a function of the junction geometry area and perimeter and the physical parameters of the semiconductor material like doping concentration [56]. The  $I_1$  has two main components, the minority carrier diffusion/drift near the edge of the depletion region and the leakage due to electron-hole pair generation [52], [57].

Figure 3.5 – Bulk (substrate) current versus gate voltage for different CMOS technologies (T = 300K,  $V_D = 1.2$  V). Reproduced with permission from [55]

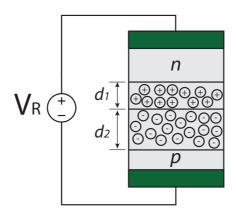

Figure 3.6 – p-n junction with reverse bias

The physical mechanism of the p-n junction, that is shown in figure 3.6 under reverse biasing, is important in order to understand the effects of reverse bias voltage and temperature on the leakage current. If a reverse bias  $V_R > 0$  is applied from the n terminal to the p terminal, the electrostatic potential across the depletion region will increase by  $V_R$ . This leads the depletion region to widen more than in the zero bias, since the reverse biasing moves the electrons upward away from the upper edge of the depletion region and the holes downward away from the lower edge of the region. More impurity atoms are uncovered that contribute to a larger electric field [58]. However, although the polarity of the reverse bias does not help the flow of the majority carriers, a small junction leakage current does flow because some of the minority

carriers near the depletion region of the n side are swept down by the field. Equivalently, some of the electrons near the depletion region edge of the p side are swept upwards by the field. A net external leakage current flows. In reality the reverse bias current is higher than the theoretical model, since other phenomena, like the electron-hole pair thermal generation in the depletion region, make the reverse current magnitude larger [59].

It should be noted, that the diode reverse leakage current  $I_1$  is highly affected by temperature and can double for every 10°C or even less of temperature change [58].

As the CMOS devices are scaled down to increase their performance and to achieve lower power consumption, the supply voltage  $V_{DD}$  and also the threshold voltage  $V_{T0}$  are scaled. The ion implantation for lowering the threshold voltage of modern CMOS devices has a dramatic effect on the subthreshold or weak inversion leakage current  $I_2$  [54], [60], [61].

The subthreshold current between source and drain occurs when the gate voltage  $V_G$  is smaller than the threshold voltage  $V_{T0}$  [58], [62]. In the weak inversion, although the drift component of the subthreshold current is negligible, the subthreshold conduction is dominated by the diffusion current. The carriers move by diffusion along the surface similarly to the charge moving across the bipolar transistor's base [62].

The analytical MOS transistor model valid in all regions of operation [63] and details on the weak inversion operation can be found in [64].

The drain current  $I_D$  for an nMOS transistor in weak inversion according to the EKV model [64] is given by equation (3.3)

$$I_D = I_{spec} exp \frac{V_G - V_{T0}}{nU_T} \left( exp \frac{-V_S}{U_T} - exp \frac{-V_D}{U_T} \right), \quad IC \ll 1$$

$$(3.3)$$

where  $I_{spec}$  is the specific current of the transistor,  $V_G$  is the gate voltage,  $V_{T0}$  is the threshold voltage, n is the slope factor,  $U_T$  is the thermal voltage and  $V_S$  and  $V_D$  are the source and the drain voltages respectively. According to the EKV model, the level of inversion of the transistor can be characterized by an inversion coefficient *IC*. When the transistor operates in the weak inversion, the condition  $IC \ll 1$  holds.

The specific current  $I_{spec}$  is defined as:

$$I_{spec} = 2n\mu C_{ox} \frac{W}{L} U_T^2 = 2n\beta U_T^2$$

(3.4)

where  $\beta$  is the transfer parameter that depends on the width *W* and the length *L* ratio of the channel,  $\mu$  is the equivalent mobility of electrons in the channel and *C*<sub>ox</sub> is the gate oxide

capacitance per unit area. The thermal voltage  $U_T$  is defined as:

$$U_T = \frac{kT}{q} \tag{3.5}$$