# Characterization of GigaRad Total Ionizing Dose and Annealing Effects on 28 nm Bulk MOSFETs

Chun-Min Zhang, *Student Member, IEEE*, Farzan Jazaeri, *Member, IEEE*, Alessandro Pezzotta, Claudio Bruschini, *Member, IEEE*, Giulio Borghello, Federico Faccio, Serena Mattiazzo, Andrea Baschirotto, *Fellow, IEEE* and Christian Enz, *Senior Member, IEEE*

Abstract—This paper investigates the radiation tolerance of 28 nm bulk *n*- and *p*MOSFETs up to 1 Grad of total ionizing dose (TID). The radiation effects on this commercial 28 nm bulk CMOS process demonstrate a strong geometry dependence as a result of the complex interplay of oxide and interface charge trapping relevant to the gate-related dielectrics and the shallow trench isolation. The narrowest/longest-channel devices have the most serious performance degradation. In addition, *n*MOSFETs present a limited on-current variation and a significant offcurrent increase, while *p*MOSFETs show a negligible off-current change and a substantial on-current degradation. The postirradiation annealing annihilates or neutralizes oxide trapped positive charges and tends to partly recover the degraded device performance. To quantify the effects of TID and post-irradiation annealing, parameters including the threshold voltage, the free carrier mobility, the subthreshold swing, and the drain-induced barrier lowering are extracted.

*Index Terms*—annealing, charge trapping, high-*k*, interface traps, oxide traps, spacer, STI, total ionizing dose, TID, 28 nm bulk MOSFETs.

#### I. INTRODUCTION

**T** O extend the discovery potential at the forefront of research in high-energy physics (HEP), the Large Hadron Collider (LHC) at CERN will be upgraded for a tenfold increase in the integrated luminosity. The high-luminosity LHC (HL-LHC) is expected to experience an unprecedented radiation level up to 1 Grad (10 MGy) of total ionizing dose (TID) and  $10^{16}$  neutrons/cm<sup>2</sup> of hadron fluence over ten years of operation. Hence, the experimental equipments need highly improved radiation-tolerant tracking systems with higher bandwidth and more radiation-tolerant front-end (FE) electronics [1], [2]. The aggressive down-scaling of deep-submicron CMOS technologies brings analog and mixed-signal circuit designers

Manuscript received March 27, 2017; revised July 10, 2017 and August 18, 2017; accepted August 20, 2017. This work is part of the GigaRadMOST project funded by the Swiss National Science Foundation (SNSF) under grant number 200021\_160185, in collaboration with the ScalTech28 project funded by the Istituto Nazionale di Fisica Nucleare (INFN).

Chun-Min Zhang, Farzan Jazaeri, Alessandro Pezzotta, Claudio Bruschini, and Christian Enz are with the Integrated Circuits Laboratory (ICLAB), École Polytechnique Fédérale de Lausanne (EPFL), Neuchâtel 2002, Switzerland (e-mail: chunmin.zhang@epfl.ch).

Giulio Borghello and Federico Faccio are with the EP-ESE Group, CERN, Geneva 1211, Switzerland. Giulio Borghello is also with the University of Udine, Udine 33100, Italy.

Serena Mattiazzo is with the Department of Information Engineering, University of Padova, Padova 35131, Italy.

Andrea Baschirotto is with the Microelectronic Group, INFN Milano-Bicocca and University of Milano-Bicocca, Milano 20126, Italy. the benefits of a higher operation speed and an extended circuit functionality [3]. Furthermore, the gate dielectric with ultrascaled silicon dioxide (SiO<sub>2</sub>) demonstrates a higher radiation tolerance and relevant CMOS technologies are promising for radiation-tolerant applications [4].

Nonetheless, since the device dimensions shrank into 45 nm technology node and beyond, hafnium oxide (HfO2) has been increasingly used for a higher physical oxide thickness to resolve the crucial gate direct tunneling issue [5]. However, a physically thicker gate dielectric degrades the radiation tolerance improvement of the aggressive gate-oxide scaling in terms of oxide charge trapping. Considering also the fact that the interface charge trapping relies on the interface quality instead of the oxide thickness, efforts are still needed for investigating the radiation response of the HfO<sub>2</sub>-based material system [6]–[8]. On the other hand, it is reported in [9], [10] that the thick spacers severely affect 65 nm short-channel MOSFETs. Especially, the irradiated short-channel pMOSFETs almost degrade to the point of not having any on-current after 1 Grad. Additionally, the shallow trench isolation (STI) oxide is still in the order of 100 nm. The relevant charge buildup imposes strong effects on deep-submicron MOSFETs [11]-[13]. One of the main phenomena is the parasitic sidewall leakage current. Concerning the gate-related dielectrics and the thick STI oxide, it is still of importance to investigate TID effects on ultra-scaled MOSFETs for selecting the most appropriate candidates for radiation-tolerant circuits in the HL-LHC.

This paper studies DC characteristics of 28 nm bulk MOS-FETs up to 1 Grad that is the foreseen radiation level in the innermost detectors of the HL-LHC. We also investigate the electrical evolution of the irradiated devices during annealing. Various sizes of individual MOSFETs are explored for comprehending the dominant mechanisms of TID effects. The results are also helpful for circuit designers to better choose the suitable sizes of MOSFETs for their radiation-tolerant applications. Extending our previous work on *n*MOSFETs [14], [15], this paper includes a detailed analysis of TID and annealing effects on important parameters of 28 nm bulk *n*- and *p*MOSFETs. The main mechanism of TID effects on a MOSFET is introduced in Section II. Test structures and the measurement protocol is described in Section III. Then in Section IV, we discuss TID and annealing effects on key device parameters, including the threshold voltage, the free carrier mobility, the subthreshold swing, and the drain-induced barrier lowering. The conclusion

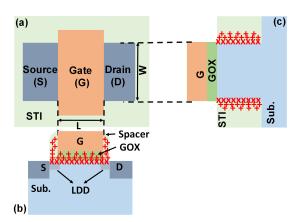

Fig. 1. (a) Top-view of a general MOSFET; (b) cross section along the length of the MOSFET; (c) cross section along the width of the MOSFET. "+" indicates oxide trapped charges  $(Q_{ot})$  and " $\times$ " stands for interface charged traps  $(Q_{it})$ .

comes in Section V.

# II. BASIC PHYSICAL PROCESSES OF TID EFFECTS ON A MOSFET

When a MOSFET is exposed to high-energy ionizing radiation, electron-hole pairs are produced by the absorbed energy in oxides [16], [17]. Depending on the magnitude of the electric field and the energy of the incident radiation, some of electron-hole pairs undergo recombination immediately. The remaining electrons are swept out of the oxides toward the corresponding electrodes within picoseconds or so. Through a hopping transport mechanism, the remaining holes move through the localized shallow trap sites arising from the disorder of the oxides [18]. This distorts the local potential field of the oxide lattice and tends to confine a fraction of the transporting holes into the relatively deep hole traps (e.g., oxygen vacancies, oxygen interstitials) within the oxide bulk. Oxide trapped charges  $(Q_{ot})$ , labeled by "+" in Fig. 1, are positive for both n- and pMOSFETs. In addition, the holes remaining in the oxide volume form protons (H<sup>+</sup>) via reacting with hydrogen-contained oxide defects [19]. The protons moving to the Si/oxide interfaces break the hydrogenpassivated dangling bonds. This generates electrically active and amphoteric interface defects. Depending on the midgap energy level, interface charged traps  $(Q_{it})$ , labeled by " $\times$ " in Fig. 1, are negative in *n*MOSFETs and positive in *p*MOSFETs [20].

Fig. 1b is the cross section along the length of a MOSFET and illustrates the charge trapping related to gate oxide and spacers. Fig. 1c shows the cross section along the width of the MOSFET and presents the charge trapping related to the STI. The charge trapping from both the gate-related dielectrics and the thick isolation oxide influences the device behaviors. In particular, TID effects induce several types of performance degradation, including a threshold voltage shift, a free carrier mobility reduction, a subthreshold swing degradation, and a radiation-modified drain-induced barrier lowering.

TABLE I Device-under-test (DUT) list

| Dimension  | DUT1   | DUT2  | DUT3   | DUT4   | DUT5   |

|------------|--------|-------|--------|--------|--------|

| Width (W)  | 3 µm   | 1 µm  | 1 µm   | 1 µm   | 300 nm |

| Length (L) | 30 nm  | 30 nm | 60 nm  | 90 nm  | 30 nm  |

| W/L        | 100    | 33.3  | 16.7   | 11.1   | 10     |

| Dimension  | DUT6   | DUT7  | DUT8   | DUT9   | DUT10  |

| Width (W)  | 100 nm | 3 µm  | 400 nm | 200 nm | 100 nm |

| Length (L) | 30 nm  | 1 µm  | 1 µm   | 1 µm   | 1 µm   |

| W/L        | 3.3    | 3     | 0.4    | 0.2    | 0.1    |

#### (a) *n*MOS with ESD protection diodes at gate

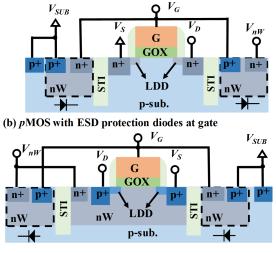

Fig. 2. Cross sections of n- (a) and pMOSFETs (b) with two diodes for each as the electrostatic discharge (ESD) protection at the gate terminal. The regions with dashed lines form the ESD protection diodes.

## **III. EXPERIMENTAL DETAILS**

#### A. Test structures

Test chips were fabricated with a commercial 28 nm bulk CMOS process [14], [15]. This work studies *n* and *p* types of standard  $V_T$  MOSFETs separately with two chips. Each chip has ten devices-under-test (DUTs) of the same type, which feature widths ranging from 3 µm to 100 nm and lengths from 1 µm to 30 nm, as listed in Tab. I. Each DUT has one sample that was tested comprehensively. Each MOSFET has two diodes connected to the gate terminal as the electrostatic discharge (ESD) protection, as shown in Fig. 2. Field-oxide FETs (FOXFETs) are often used for investigating TID effects on the thick STI oxide. Enclosed-layout transistors (ELTs) are often applied for isolating the effects on the STI from the gate-related dielectrics. However, the strict design rules of this commercial 28 nm bulk CMOS process exclude such special structures.

# B. Measurement protocol

The irradiation was conducted at CERN's in-house 10 keV X-ray irradiation system (Seifert RP149). It has a customized probe card with two columns of 16 probe tips installed at a semi-automatic 8-inch wafer prober station (Karl-Suss PA200). Through a switching matrix (Keithley 707), two voltage supplies provided the bias for all DUTs during irradiation

and annealing. The terminals labeled in Fig. 2 were biased with  $V_G = V_D = V_{nW} = 1.1 \text{ V}$ ,  $V_S = V_{SUB} = 0$  for *n*MOSFETs and  $V_G = V_D = V_{SUB} = 0$ ,  $V_S = V_{nW} = 1.1$  V for pMOSFETs. The temperature-controlled chuck equipped with the irradiation system allows a temperature ranging from -50 °C to 200 °C. At a dose rate of  $8.82 \text{ Mrad/h}(\text{SiO}_2)$ , the chips were irradiated at room temperature (25 °C) up to 1 Grad with steps of 0, 10, 50, 140, 340, 540, 740, 940, 963, and 1000 Mrad. To study the post-irradiation annealing effects, the irradiated nMOSFETs were kept at the same temperature  $(25 \,^{\circ}\text{C})$  with the same bias condition for 450 hours. To speed up the annealing process, pMOSFETs were biased at an elevated temperature (100 °C) for 16 hours. It should be mentioned that with our bias conditions, devices were conducting a high drain current during irradiation. To differentiate the radiation damage from the stress effects, we carried out additional stress tests at the same bias conditions for a comparable time but without irradiation.

Static electrical measurements were performed with the semiconductor parameter analyzer HP4145/55 through the switching matrix at room temperature during irradiation and at the annealing temperature after irradiation. A large amount of measurements were conducted to investigate TID effects on all regions of operation. Transfer characteristics were measured from linear  $(|V_{DS}| = 0.01 \text{ V})$  to saturation  $(|V_{DS}| = 1.1 \text{ V})$ by sweeping the gate voltage  $(V_G)$  from -0.2 V to 1.1 V. The output characteristics were measured from depletion region ( $|V_{GS}| = 0.1 \text{ V}$ ) to strong inversion ( $|V_{GS}| = 1.1 \text{ V}$ ) by sweeping the drain voltage  $(V_D)$  from 0 to 1.1 V. Since the radiation damage anneals with time [21], a voltage step of 25 mV was chosen as a suitable compromise between limiting the measurement duration and providing a sufficient measurement resolution. In this paper, the on-current, the threshold voltage, the free carrier mobility, the off-current, and the subthreshold swing are extracted from the measured drain current  $(I_D)$  versus  $V_G$  curves in the saturation operation. The drain-induced barrier lowering (DIBL) parameter is obtained from the  $I_D$ - $V_G$  curves with 0.01 V and 1.1 V of  $|V_{DS}|$ . pDUT10 demonstrates an unexpected abrupt increase in the off-current around 140 Mrad that is not seen for other DUTs. Due to the fact that its source and substrate are connected with other DUTs and its gate is coupled with the ESD protection diodes, we are not able to obtain the intrinsic currents from gate, source and substrate. Therefore, it is not straightforward to clearly identify the source of this off-current increase. In order not to mislead the reader by the suspect behavior of pDUT10, we exclude it from our discussion. Note that nMOSFETs lost the bias for hours between 540 and 740 Mrad. pMOSFETs were not biased for hours between 940 and 963 Mrad. This bias loss explains the discontinuous evolution of the extracted parameters.

#### **IV. RESULTS AND DISCUSSIONS**

# A. Bias-dependence of TID effects

TID effects strongly depend on the applied electric field. It is reported in [9] that for a commercial 65 nm bulk CMOS process, the real worst-bias cases are  $V_{GB} = V_{DS} = V_{DD}$  for *n*MOSFETs and  $V_{GB} = V_{DS} = -V_{DD}$  for *p*MOSFETs that are different from the historically worst-bias cases ( $V_{GB} = 1.1$  V,  $V_{DS} = 0$  for *n*MOSFETs and  $V_{GB} = V_{DS} = 0$  for *p*MOSFETs [22]). We compare the effects of these two bias conditions on 28 nm bulk *n*- and *p*MOSFETs. No big difference is seen between them and the slight difference is actually within the chip variability

(~6%). It is not straightforward to decide which are the worstbias cases for this 28 nm bulk CMOS process. However, in most analog circuits and particularly the analog front-end electronics used in HEP, the transistors are biased in saturation with a nonzero  $V_{DS}$  except the switches working with a zero  $V_{DS}$ . In order to reproduce as close as possible the realistic bias conditions for analog circuits, we therefore chose to bias the devices with  $V_{GB} = V_{DS} = 1.1 \text{ V}$  for *n*MOSFETs and  $V_{GB} = V_{DS} = -1.1 \text{ V}$ for *p*MOSFETs.

Since the devices conducted a high drain current during irradiation with our bias conditions, it is of importance to see how much of the performance degradation comes from TID effects. For *n*MOSFETs, the stress without irradiation does not cause any performance degradation, leaving the whole range of  $I_D$ - $V_G$  curves unaffected. Therefore, the performance degradation of the irradiated *n*MOSFETs is attributed only to the radiation effects. However, pMOSFETs demonstrate some stress-induced shift in the threshold voltage. The ratio of the stress effects to the radiation damage depends on the transistor dimension. However, except the largest pMOSFETs  $(3 \mu m/1 \mu m)$  for which the damage is mostly due to the stress, the degradation of all the others is dominated by TID effects (70%-95%). Additionally, there might be selfheating during irradiation due to the high conducting current. However, between the end of the irradiation and the start of the first DC measurement, the time (a couple of seconds) should be sufficient for the chips to cool down to the room temperature [23]. Since the self-heating normally appears at the high current level, we believe that the important parameters extracted from the low current region of the measured  $I_D$ - $V_G$  curves, such as the threshold voltage, the free carrier mobility, the subthreshold swing, and the off-current, are not affected by self-heating. Nevertheless, we are mostly interested in the realistic bias conditions that are close to the real circuit operating regime, even though there might be self-heating affecting the on-current.

Section III-B mentioned the bias loss between 540 and 740 Mrad for nMOSFETs and 940 and 963 Mrad for pMOSFETs that causes the parameter discontinuities. Electron tunneling from the oxides to the substrate is expected to be the underlying mechanism. At a positive gate-to-bulk bias, electrons tunnel from the substrate to electron traps in oxides and neutralize the associated holes that are mostly trapped at near-interfacial oxide traps (i.e., border traps). Removing the bias, these electrons tunnel back to the substrate and lead to a higher amount of oxide trapped charges. This decreases the threshold voltage, increases the on-current, and degrades the subthreshold swing. The negative threshold voltage shift also leads to a higher off-current for short-channel *n*MOSFETs. Long-channel *n*MOSFETs present a lower off-current, which could be explained by the compensation of the interface charge trapping. The bias loss between 940 and 963 Mrad for *p*MOSFETs explains the slight fluctuation of the extracted parameters for the last two TID steps.

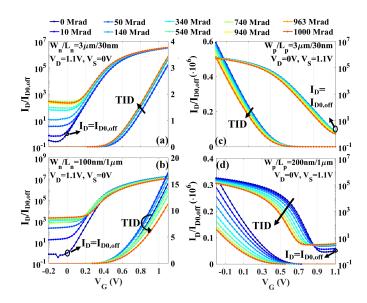

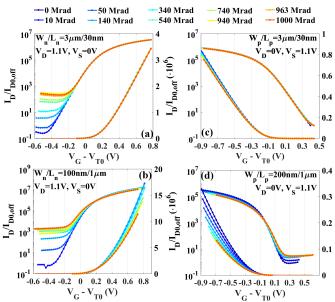

Fig. 3. Transfer characteristics of both n (ab) and p (cd) types of MOSFETs in saturation mode ( $|V_{DS}| = 1.1$  V) with respect to TID. (ac) are for DUT1 with the largest W/L ratio  $(3 \mu m/30 \text{ nm})$ . (b) is for *n*DUT10 with the smallest W/L ratio (100 nm/1 µm) and (d) is for pDUT9 with 100 nm/1 µm.  $I_{D0, off}$  is the off-current ( $V_{GS} = 0$ ) before irradiation.

#### B. TID effects on transfer characteristics

Fig. 3 plots the normalized off-current of *n*DUT1, *n*DUT10, pDUT1, and pDUT9 with respect to TID. The on-current  $(I_{D,on})$  is defined at  $|V_{GS}| = 1.1$  V, and the off-current  $(I_{D,off})$ at  $V_{GS} = 0$ . *n*DUT1 has a negative threshold voltage shift and a monotonic on-current increase, as shown in Fig. 3a. Nevertheless, as seen in Fig. 3b, the threshold voltage of nDUT10 first decreases and then increases, leading to the corresponding on-current evolution. Both irradiated nDUT1 and *n*DUT10 have a significant off-current increase. In contrast, the threshold voltage of both pDUT1 (Fig. 3c) and pDUT9 (Fig. 3d) decreases with TID, leading to a continuous on-current loss. Note that when the threshold voltage of a pMOSFET decreases, it becomes more negative and its absolute value increases. The off-current of both pDUT1 and pDUT9 is not sensitive to TID and has a slight off-current change.

## C. On-current

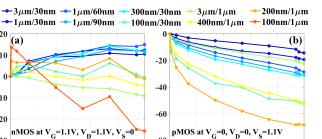

The relative on-current variation is plotted as a function of TID in Fig. 4. All *n*MOSFETs present an on-current improvement at a lower TID (~10 Mrad) in Fig. 4a. Then for *n*DUT1-5, the on-current increase continues until reaching a ~15% increase. However, the on-current of *n*DUT6-10 starts to decrease at a higher TID. *n*DUT10 with the smallest W/Lratio (100 nm/1 µm) evidences as the most dynamic case with a maximum on-current loss of  $\sim 25\%$ . Fig. 4b shows that pMOSFETs are grouped into two distinct categories: pDUT1-6 and pDUT7-9. In each group, the narrower the channel, the higher the on-current loss. Eventually, most of pMOSFETs show a less than 30% degradation in the on-current. Narrowchannel pMOSFETs with a smaller W/L (pDUT6 and pDUT8-9) present a more than 50% on-current loss. Nevertheless, these results are much better compared to the commercial 65 nm bulk CMOS technology from the same foundry [9].

-80

200 400 600 800

Total Ionizing Dose (Mrad)

20

10

0

-10

200 400 600 800

Total Ionizing Dose (Mrad)

ต์ ดั-20

Variation (%)

Fig. 4. TID-induced on-current  $(I_{D,on})$  variation of both n (a) and p (b) types of MOSFETs in saturation mode ( $|V_{DS}| = 1.1$  V).  $I_{D,on}$  is obtained at  $|V_{GS}| = 1.1 \,\mathrm{V}.$

1000 0

Fig. 5. Drain current  $(I_D)$  versus the overdrive voltage  $(V_G - V_{T0})$  with respect to TID for both n (ab) and p (cd) types of MOSFETs in saturation mode  $(|V_{DS}| = 1.1 \text{ V}).$

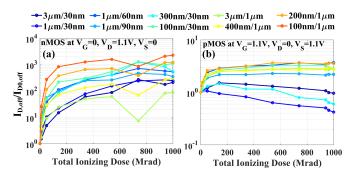

Both the threshold voltage  $(V_{T0})$  shift and the free carrier mobility  $(\mu)$  reduction influence the on-current. To extract  $V_{T0}$  and  $\mu$ ,  $\sqrt{I_D}$ - $V_G$  curves are extrapolated linearly at the maximum slope. The intercept at the  $V_G$  axis is defined as  $V_{T0}$ . The slope of the linear extrapolation provides insights into  $\mu$ . We now plot  $I_D$  with respect to  $V_G - V_{T0}$  in Fig. 5 to isolate the effects of the free carrier mobility reduction from the threshold voltage shift. It is seen in Fig. 5ac that for the widest/shortest-channel DUTs ( $3 \mu m/30 nm$ ), the  $I_D$  versus  $V_G - V_{T0}$  curves overlap in strong inversion, demonstrating that only the threshold voltage shift accounts for the on-current variation. For the narrowest/longest-channel DUTs, as shown in Fig. 5bd, the  $I_D$  versus  $V_G - V_{T0}$  curves deviate in strong inversion, indicating the additional contribution of the mobility reduction to the on-current loss. We also suspect that for shortchannel *p*MOSFETs, the positive charges trapped in the spacers reduce the effective doping of the LDD region and increase the resistance for the drain current. This might partly contribute to the significant on-current loss of pDUT6 (100 nm/30 nm). However, with our current measurements, we are not able to

1000

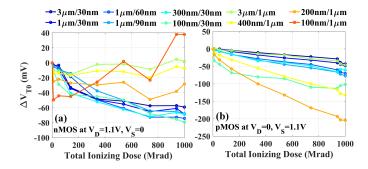

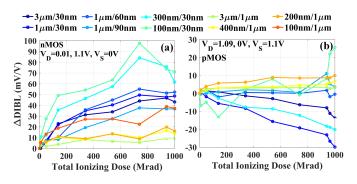

Fig. 6. TID-induced threshold voltage  $(V_{T0})$  shift of both *n* (a) and *p* (b) types of MOSFETs in saturation mode  $(|V_{DS}| = 1.1 \text{ V})$ .

isolate the effects of the spacers from the gate oxide. Further investigations are therefore needed to verify if this technology does undergo the effects of the charge buildup in the spacers.

1) Threshold voltage:  $Q_{ot}$  decreases the threshold voltage of both *n*- and *p*MOSFETs, whereas  $Q_{it}$  increases that of nMOSFETs and decreases that of pMOSFETs. For nMOSFETs, the counterbalance of  $Q_{ot}$  and  $Q_{it}$  leads to a limited influence on the switched-on region. Fig. 6a shows a less than 80 mV shift in the threshold voltage, corresponding to a less than 30% variation. This explains the limited on-current variation in Fig. 4a. It is also observed that at a lower TID, the threshold voltage decreases for all *n*MOSFETs, which is due to the initial oxide trapped charges. Then the threshold voltage of nDUT1-6 continues to decrease until 1 Grad. For nDUT7-10,  $Q_{it}$  starts at a certain TID to compensate the  $Q_{ot}$ -induced negative threshold voltage shift. Eventually, nDUT10 has an overall positive threshold voltage shift that is consistent with the net on-current decrease. Fig. 6b shows that even with the superposed effects of  $Q_{ot}$  and  $Q_{it}$ , most of pMOSFETs still have a threshold voltage shift of less than 80 mV. However, the threshold voltage of narrow-channel pMOSFETs with a smaller W/L ratio (pDUT6 and pDUT8-9) decreases by more than 100 mV that corresponds to their significant on-current loss. It should be mentioned that the threshold voltage variation for all pMOSFETs is within 30%. The significant effect on narrow-channel pMOSFETs is attributed to the charge trapping in the thick STI oxide, which modifies the electric field at the STI edges and prevents the inversion of the silicon channel [9], [11], [24].

2) Free carrier mobility: The radiation-induced mobility reduction demonstrates a strong dependence on the Coulomb scattering of the trapped charges at border traps [25] and interface traps [26]. Fig. 7a shows that wide/short-channel MOSFETs have a negligible mobility reduction, which indicates the radiation hardness of the interface of the gate oxide and the silicon channel. The significant negative threshold voltage shift in Fig. 6a actually indicates a large amount of trapped charges at border traps in *n*DUT6 and at interface traps in *n*DUT10, which contributes to their high mobility reduction. Compared to *n*MOSFETs, *p*MOSFETs demonstrate a higher mobility reduction, as seen in Fig. 7b. The mobility of *p*DUT6 and *p*DUT8-9 degrades more that is consistent with their significant on-current loss depicted in Fig. 4b. The highest mobility reduction in narrowest/longest-channel DUTs (*n*DUT10 and

Fig. 7. TID-induced free carrier mobility ( $\mu$ ) reduction of both *n* (a) and *p* (b) types of MOSFETs in saturation mode ( $|V_{DS}| = 1.1$  V).  $\mu_0$  is the free carrier mobility before irradiation.

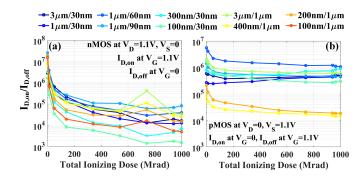

Fig. 8. TID-induced off-current  $(I_{D,off})$  increase of both *n* (a) and *p* (b) types of MOSFETs in saturation mode  $(|V_{DS}| = 1.1 \text{ V})$ .  $I_{D,off}$  is obtained at  $V_{GS} = 0$ .

*p*DUT9) is clearly illustrated by the down-bending of the  $I_D$ - $(V_G - V_{T0})$  curves in Fig. 5bd.

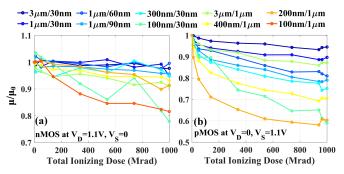

# D. Off-current

The off-current normalized to pre-irradiation values is plotted as a function of TID in Fig. 8. Fig. 8a demonstrates a significant off-current increase by two to three orders of magnitude for *n*MOSFETs. It should be mentioned that different mechanisms are dominating the region around a zero  $V_{GS}$  for short- and long-channel *n*MOSFETs, as seen in Fig. 3a and Fig. 3b. The extracted off-current of short-channel *n*MOSFETs is still in the subthreshold region before irradiation. At a lower TID, trapped holes in the thick STI oxide deplete the channel along the STI edges. This connects the source/drain depletion regions and results in a surface punchthrough current [27]. At a higher TID, the positive charges trapped in the thick STI oxide enhances the drain-induced barrier lowering (DIBL) and further increases the off-current. The radiation-enhanced DIBL will be discussed in detail in Section IV-F.

For long-channel nMOSFETs, the dominant off-current contributor is the parasitic leakage current along the STI edges [11]. Trapped holes in the thick STI oxide could be strong enough to invert the adjacent p-type substrate and to form the n-channel. Thus two parasitic leakage paths forms even when the main transistor is switched off. This effect has a stronger influence on a narrow channel, as seen with the highest off-current increase for nDUT10. Furthermore, up to a certain TID, the off-current of long-channel nMOSFETs enters into a region less dependent on the gate voltage. It almost saturates up

Fig. 9. TID-induced on/off-current ratio  $(I_{D,on}/I_{D,off})$  degradation of both *n* (a) and *p* (b) types of MOSFETs in saturation mode  $(|V_{DS}| = 1.1 \text{ V})$ .

to 340 Mrad that indicates the complete filling of the traps in the STI oxide or the compensation of the interface charge trapping from the STI. It should also be emphasized that it is more difficult to invert a highly doped silicon. Therefore, the nonuniform doping profile in nanoscale MOSFETs, including the increased channel doping concentration due to the scaling rule, the surface implantation for adjusting the threshold voltage, and the higher doping from the retrograde well and the halo pockets for suppressing short-channel effects, could be advantageous in terms of the radiation tolerance at the switch-off state [28], [29]. For all *n*MOSFETs, the radiation-induced charge buildup is not strong enough to influence the electrostatic potential in the middle of the channel. Therefore, as shown in Fig. 9a, there is still an on/off-current ratio of three orders of magnitude, leaving a sufficient margin for circuit design.

Compared to *n*MOSFETs, the switched-off region of pMOSFETs is much less susceptible to TID. The off-current changes only by a maximum factor of 3. The slight offcurrent increase might be from the peripheral drain to substrate junction leakage current. It is mostly contributed by the surface generation at the intersection of the depletion region and the STI sidewalls where a high density of interface traps are located [30]. Some of the short-channel pMOSFETs present a slight offcurrent decrease. This is due to the fact that short-channel pMOSFETs still work in the subthreshold region around a zero  $V_{GS}$ , as shown in Fig. 3c for pDUT1. The negative threshold voltage shift together with the radiation-suppressed DIBL (Section IV-F) leads to the off-current decrease. Owing to the negligible influence on the off-current, the irradiated pMOSFETs still demonstrate an on/off-current ratio of more than four orders of magnitude, as shown in Fig. 9b.

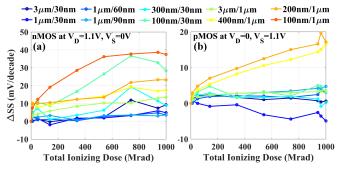

## E. Subthreshold swing

Trapped charges at border traps and interface traps cut off part of the electric field lines from the gate electrode. This reduces the effective gate potential and the transistors could not be switched off effectively. Fig. 10 shows a less than 20 mV/dec increase in the subthreshold swing for most of *n*- and *p*MOSFETs. This confirms the radiation hardness of the interface of the gate oxide and the silicon channel. Two narrowest-channel *n*MOSFETs (*n*DUT6 and *n*DUT10) demonstrate a ~40 mV/dec subthreshold swing increase. Note that the higher increase in the off-current of *n*DUT6 and

Fig. 10. TID-induced subtreshold swing (SS) degradation of both n (a) and p (b) types of MOSFETs in saturation mode ( $|V_{DS}| = 1.1$  V).

Fig. 11. TID-modified drain-induced barrier lowering (DIBL) of both *n* (a) and *p* (b) types of MOSFETs. The DIBL is extracted as  $DIBL = -(V_{T0}^{|V_{DS}|=1.1 \text{ V}} - V_{T0}^{|V_{DS}|=0.01 \text{ V}})/(1.1V - 0.01V).$

*n*DUT10 raises up the  $I_D$ - $V_G$  curves and starts to mask the subthreshold region. This degrades the precision of the subthreshold swing extraction.

# F. Drain-induced barrier lowering

The drain-induced barrier lowering (DIBL) represents one of the most fundamental short-channel effects in nanoscale MOSFETs. The STI-related charge trapping is among the most important DIBL factors [27]. In the proposed dipole theory [31],  $Q_{ot}$  in the thick STI oxide terminates the drain-to-gate fringing field at the switched-off state. This decreased drain-to-gate coupling in turn enhances the drain-to-source coupling. In addition,  $Q_{ot}$  in the thick STI oxide enhances the electric field along the STI edges. Thus the electric field lines in the center of the channel will be denser and the drain-to-source coupling will be further strengthened. Both enhance the DIBL of *n*MOSFETs, as shown in Fig. 11a.

As mentioned in Section IV-D, the STI-related charge trapping makes the parasitic depletion regions interact with the source/drain ones and forms a thicker depletion region in short-channel nMOSFETs. This will shorten the effective channel length near the corners of the STI and the gate oxide, adding another enhancing factor for the DIBL. If the width is narrow, trapped charges in the thick STI oxide even raise the nearby body potential in the main channel, which significantly lowers down the potential barriers with source and drain. This is shown in Fig. 11a: the narrower the channel, the more severe the radiation-enhanced DIBL.

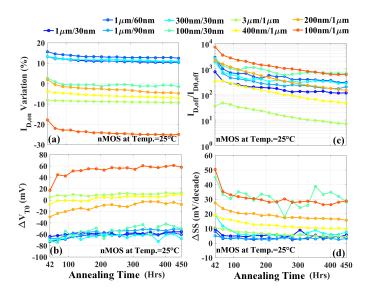

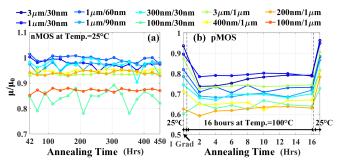

Fig. 12. Post-irradiation annealing effects on the on-current  $(I_{on})$ , the threshold voltage  $(V_{T0})$ , the off-current  $(I_{off})$ , and the subthreshold swing (SS) of *n*MOSFETs. There is no result for the widest/shortest-channel *n*MOSFET (3 µm/30 nm) due to the physical damage from moving and reconnecting the chip.

The radiation has a negligible influence on the DIBL of most of pMOSFETs, as seen in Fig. 11b. However, pDUT1-2 and pDUT5 demonstrate an radiation-suppressed DIBL. This could be explained by the proposed dipole theory. Both the trapped charges in the thick STI oxide and the image charges in the gate electrode are positive. This weakens the drain-to-source coupling and suppresses the DIBL [32]. Due to STI-related trapped charges, electrons accumulate around the corners of the gate oxide and the STI. This will lengthen the effective channel near the edges, which further decreases the DIBL of pDUT1-2 and pDUT5.

## G. Post-irradiation annealing

The long-term post-irradiation annealing is believed to annihilate or neutralize the oxide trapped charges even at room temperature [33]. This annealing process can be accelerated by a stronger positive gate-to-bulk bias and a higher temperature [34]. It is reported that in some cases the interface-trap annealing can happen below 100 °C [35]. However, a higher temperature is generally required to anneal interface traps effectively [36].

Fig. 12 and Fig. 13a present the room temperature  $(25 \,^{\circ}\text{C})$  annealing effects on important parameters of *n*MOSFETs. The first measurement was taken after 42 hours of annealing. Since the room temperature is not high enough to anneal the interface traps, the observation gives more insights into the evolution of the oxide trapped charges. The threshold voltage of *n*MOSFETs increases due to the trapped-hole annealing, as observed in Fig. 12b. Fig. 13a demonstrates a negligible change in the free carrier mobility, which confirms no annealing evolution for radiation-induced interface traps. Therefore, the room temperature annealing decreases the oncurrent of *n*MOSFETs, as seen in Fig. 12a. The trapped-hole annealing also decreases the off-current significantly, as shown

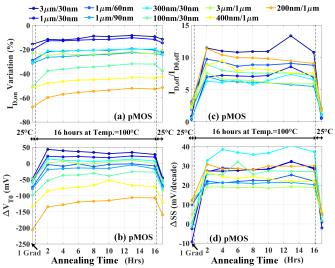

Fig. 13. Post-irradiation annealing effects on the free carrier mobility ( $\mu$ ) of n (a) and p (b) types of MOSFETs. In (b), the first measurement corresponds to 1 Grad at room temperature. The second is with respect to 2 hours of high temperature annealing. The last is a room temperature measurement after the high temperature annealing. The dashed lines indicate the changing of the temperature.

Fig. 14. Post-irradiation annealing effects on the on-current  $(I_{on})$ , the threshold voltage  $(V_{T0})$ , the off-current  $(I_{off})$ , and the subthreshold swing (SS) of *p*MOSFETs.

in Fig. 12c. An observable improvement in the subthreshold swing is seen in Fig. 12d, indicating the annealing of the trapped holes at border traps. The remaining subthreshold swing degradation for nDUT6 and nDUT8-10 could be attributed to the interface charged traps at the STI/channel edges.

Fig. 14 and Fig. 13b present the high temperature  $(100 \,^{\circ}\text{C})$  annealing effects on important parameters of *p*MOSFETs. The chip was annealed at 100  $^{\circ}\text{C}$  for 16 hours and then cooled down to 25  $^{\circ}\text{C}$ . The first measurement point corresponds to 1 Grad at room temperature. The second refers to 2 hours of high temperature annealing. The big differences between these two sets of measurement points include the effects of the temperature dependence that is demonstrated as a higher off-current, an increased threshold voltage, a degraded subthreshold swing and a reduced free carrier mobility. The oncurrent increase is due to the dominant effects of the positive threshold voltage shift over the free carrier mobility reduction. Since the subthreshold swing increase is less than 1.25 that is the temperature ratio of the first two measurements, the second measurement point also includes the effect of high

temperature annealing. In the following hours, the degraded performance of pMOSFETs is partly recovered. The threshold voltage (Fig. 14b) increases and the free carrier mobility improves slightly (Fig. 13b), which leads to an observable oncurrent increase (Fig. 14a). The differences between two room temperature measurements demonstrate the net performance improvements. It is observed that after 16 hours of high-temperature annealing, the threshold voltage increases by up to 40 mV, the mobility improves by up to 12%, and the on-current recovers by up to 20%. The off-current and the subthreshold swing almost reaches the original values.

## V. CONCLUSION

The effects of total ionizing dose (TID) up to 1 Grad and post-irradiation annealing on 28 nm bulk n- and pMOSFETs are investigated. The counterbalance of interface and oxide charge trapping results in a limited influence on the switchedon region of the irradiated *n*MOSFETs, which demonstrate a less than 25% free carrier mobility reduction, a less than 80 mV threshold voltage shift and a less than 25% on-current loss. However, due to the STI-induced parasitic leakage paths and the radiation-enhanced DIBL, *n*MOSFETs present a two to three orders of magnitude increase in the off-current. In contrast, most of *p*MOSFETs have a negligible off-current change. Even with the superposed effects of interface and oxide charged traps, most of pMOSFETs still undergo a less than 30% performance degradation, which is much less compared to the 65 nm counterparts. Owing to the radiationinduced narrow channel effects, the narrowest/longest-channel *p*MOSFET presents the strongest susceptibility to TID with a 200 mV threshold voltage shift and a 40% free carrier mobility reduction as well as a 70% on-current loss. The limited subthreshold swing degradation indicates the strong radiation tolerance of the interface of the gate dielectric and the silicon channel.

Due to the complex interplay of the charge trapping relevant to the gate-related dielectrics and the STI, TID effects demonstrate a strong geometry dependence. This implies the importance of choosing the suitable sizes of transistors for radiation-tolerant circuit design. In addition, oxide trapped holes anneal with time, which leads to a significant off-current decrease in nMOSFETs and a substantial on-current recovery in pMOSFETs. Considering the long-term irradiation and annealing in realistic applications, the degradation might be mitigated.

## ACKNOWLEDGMENT

The authors would like to thank Dr. Alessandro Marchioro from the CERN EP-ESE Group for the fruitful collaborations.

#### REFERENCES

- J. Butler, M. Klute, L. Silvestris, J. Mans, D. Contardo *et al.*, "CMS Phase II Upgrade Scope Document," CERN-LHCC-2015-020, Tech. Rep., 2015.

- [2] K. Einsweiler and L. Pontecorvo, "ATLAS Phase-II Upgrade Scoping Document," CERN-LHCC-2015-019, Tech. Rep., 2015.

- [3] F. Ellinger, M. Claus, M. Schröter, and C. Carta, "Review of advanced and beyond CMOS FET technologies for radio frequency circuit design," in 2011 SBMO/IEEE MTT-S International Microwave and Optoelectronics Conference (IMOC 2011), Oct 2011, pp. 347–351.

- [4] J. M. Benedetto, H. E. Boesch, F. B. McLean, and J. P. Mize, "Hole removal in thin-gate MOSFETs by tunneling," *IEEE Trans. Nucl. Sci.*, vol. 32, no. 6, pp. 3916–3920, Dec 1985.

- [5] K. Choi, T. Ando, E. A. Cartier, A. Kerber, V. Paruchuri, J. Iacoponi, and V. Narayanan, "The past, present and future of high-k/metal gates," *ECS Trans.*, vol. 53, no. 3, pp. 17–26, 2013.

- [6] A. Y. Kang, P. M. Lenahan, and J. F. Conley, "The radiation response of the high dielectric-constant hafnium oxide/silicon system," *IEEE Trans. Nucl. Sci.*, vol. 49, no. 6, pp. 2636–2642, Dec 2002.

- [7] S. K. Dixit, X. J. Zhou, R. D. Schrimpf, D. M. Fleetwood, S. T. Pantelides, R. Choi, G. Bersuker, and L. C. Feldman, "Radiation induced charge trapping in ultrathin HfO<sub>2</sub>-based MOSFETs," *IEEE Trans. Nucl. Sci.*, vol. 54, no. 6, pp. 1883–1890, Dec 2007.

- [8] G. X. Duan, C. X. Zhang, E. X. Zhang, J. Hachtel, D. M. Fleetwood, R. D. Schrimpf, R. A. Reed, M. L. Alles, S. T. Pantelides, G. Bersuker, and C. D. Young, "Bias dependence of total ionizing dose effects in SiGe-SiO<sub>2</sub>/HfO<sub>2</sub> pMOS FinFETs," *IEEE Trans. Nucl. Sci.*, vol. 61, no. 6, pp. 2834–2838, Dec 2014.

- [9] F. Faccio, S. Michelis, D. Cornale, A. Paccagnella, and S. Gerardin, "Radiation-induced short channel (RISCE) and narrow channel (RINCE) effects in 65 and 130 nm MOSFETs," *IEEE Trans. Nucl. Sci.*, vol. 62, no. 6, pp. 2933–2940, Dec 2015.

- [10] M. Menouni, M. Barbero, F. Bompard, S. Bonacini, D. Fougeron, R. Gaglione, A. Rozanov, P. Valerio, and A. Wang, "1-Grad total dose evaluation of 65 nm CMOS technology for the HL-LHC upgrades," *J. Instrum.*, vol. 10, no. 05, p. C05009, 2015.

- [11] F. Faccio and G. Cervelli, "Radiation-induced edge effects in deep submicron CMOS transistors," *IEEE Trans. Nucl. Sci.*, vol. 52, no. 6, pp. 2413–2420, Dec 2005.

- [12] M. Gaillardin, V. Goiffon, S. Girard, M. Martinez, P. Magnan, and P. Paillet, "Enhanced radiation-induced narrow channel effects in commercial 0.18 μm bulk technology," *IEEE Trans. Nucl. Sci.*, vol. 58, no. 6, pp. 2807–2815, Dec 2011.

- [13] M. Gaillardin, S. Girard, P. Paillet, J. L. Leray, V. Goiffon, P. Magnan, C. Marcandella, M. Martinez, M. Raine, O. Duhamel, N. Richard, F. Andrieu, S. Barraud, and O. Faynot, "Investigations on the Vulnerability of Advanced CMOS Technologies to MGy Dose Environments," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 4, pp. 2590–2597, Aug 2013.

- [14] A. Pezzotta, C. M. Zhang, F. Jazaeri, C. Bruschini, G. Borghello, F. Faccio, S. Mattiazzo, A. Baschirotto, and C. Enz, "Impact of GigaRad ionizing dose on 28 nm bulk MOSFETs for future HL-LHC," in 2016 Proceedings of the 46th European Solid-State Device Research Conference (ESSDERC), Sept 2016, pp. 146–149.

- [15] C.-M. Zhang, F. Jazaeri, A. Pezzotta, C. Bruschini, G. Borghello, F. Faccio, S. Mattiazzo, A. Baschirotto, and C. Enz, "GigaRad total ionizing dose and post-irradiation effects on 28 nm bulk MOSFETs," in 2016 IEEE Nuclear Science Symposium Conference Record.

- [16] D. M. Fleetwood, "Total ionizing dose effects in MOS and low-doserate-sensitive linear-bipolar devices," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 3, pp. 1706–1730, June 2013.

- [17] J. R. Schwank, M. R. Shaneyfelt, D. M. Fleetwood, J. A. Felix, P. E. Dodd, P. Paillet, and V. Ferlet-Cavrois, "Radiation effects in MOS oxides," *IEEE Trans. Nucl. Sci.*, vol. 55, no. 4, pp. 1833–1853, Aug 2008.

- [18] R. C. Hughes, "Time-resolved hole transport in a-SiO<sub>2</sub>," *Phys. Rev. B*, vol. 15, no. 4, p. 2012, 1977.

- [19] N. S. Saks, R. B. Klein, and D. L. Griscom, "Formation of interface traps in MOSFETs during annealing following low temperature irradiation," *IEEE Trans. Nucl. Sci.*, vol. 35, no. 6, pp. 1234–1240, Dec 1988.

- [20] P. J. McWhorter and P. S. Winokur, "Simple technique for separating the effects of interface traps and trapped-oxide charge in metal-oxidesemiconductor transistors," *Appl. Phys. Lett.*, vol. 48, no. 2, pp. 133–135, 1986.

- [21] G. F. Derbenwick and H. H. Sander, "CMOS hardness prediction for low-dose-rate environments," *IEEE Trans. Nucl. Sci.*, vol. 24, no. 6, pp. 2244–2247, Dec 1977.

- [22] P. V. Dressendorfer, J. M. Soden, J. J. Harrington, and T. V. Nordstrom, "The effects of test conditions on MOS radiation-hardness results," *IEEE Trans. Nucl. Sci.*, vol. 28, no. 6, pp. 4281–4287, Dec 1981.

- [23] E. Pop, S. Sinha, and K. E. Goodson, "Heat generation and transport in nanometer-scale transistors," *Proc. IEEE*, vol. 94, no. 8, pp. 1587–1601, Aug 2006.

- [24] M. Gaillardin, V. Goiffon, C. Marcandella, S. Girard, M. Martinez, P. Paillet, P. Magnan, and M. Estribeau, "Radiation effects in CMOS

isolation oxides: Differences and similarities with thermal oxides," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 4, pp. 2623–2629, Aug 2013.

- [25] D. Fleetwood, M. Shaneyfelt, W. Warren, J. Schwank, T. Meisenheimer, and P. Winokur, "Border traps: Issues for MOS radiation response and long-term reliability," *Microelectronics Reliab.*, vol. 35, no. 3, pp. 403 – 428, 1995.

- [26] F. W. Sexton and J. R. Schwank, "Correlation of radiation effects in transistors and integrated circuits," *IEEE Trans. Nucl. Sci.*, vol. 32, no. 6, pp. 3975–3981, Dec 1985.

- [27] G. U. Youk, P. S. Khare, R. D. Schrimpf, L. W. Massengill, and K. F. Galloway, "Radiation-enhanced short channel effects due to multidimensional influence from charge at trench isolation oxides," *IEEE Trans. Nucl. Sci.*, vol. 46, no. 6, pp. 1830–1835, Dec 1999.

- [28] A. H. Johnston, R. T. Swimm, G. R. Allen, and T. F. Miyahira, "Total dose effects in CMOS trench isolation regions," *IEEE Trans. Nucl. Sci.*, vol. 56, no. 4, pp. 1941–1949, Aug 2009.

- [29] M. McLain, H. J. Barnaby, K. E. Holbert, R. D. Schrimpf, H. Shah, A. Amort, M. Baze, and J. Wert, "Enhanced TID susceptibility in sub-100 nm bulk CMOS I/O transistors and circuits," *IEEE Trans. Nucl. Sci.*, vol. 54, no. 6, pp. 2210–2217, Dec 2007.

- [30] A. Czerwinski, E. Simoen, and C. Claeys, "PN junction peripheral current analysis using gated diode measurements," *Appl. Phys. Lett.*, vol. 72,

no. 26, pp. 3503-3505, 1998.

- [31] Z. Liu, Z. Hu, Z. Zhang, H. Shao, B. Ning, M. Chen, D. Bi, and S. Zou, "Total ionizing dose enhanced DIBL effect for deep submicron NMOSFET," *IEEE Trans. Nucl. Sci.*, vol. 58, no. 3, pp. 1324–1331, June 2011.

- [32] C. H. Wang and P. F. Zhang, "Three-dimensional DIBL for shallowtrench isolated MOSFET's," *IEEE Trans. Electron Devices*, vol. 46, no. 1, pp. 139–144, Jan 1999.

- [33] A. J. Lelis, T. R. Oldham, H. E. Boesch, and F. B. McLean, "The nature of the trapped hole annealing process," *IEEE Trans. Nucl. Sci.*, vol. 36, no. 6, pp. 1808–1815, Dec 1989.

- [34] J. R. Schwank, P. S. Winokur, P. J. McWhorter, F. W. Sexton, P. V. Dressendorfer, and D. C. Turpin, "Physical mechanisms contributing to device "rebound"," *IEEE Trans. Nucl. Sci.*, vol. 31, no. 6, pp. 1434–1438, Dec 1984.

- [35] S. N. Rashkeev, D. M. Fleetwood, R. D. Schrimpf, and S. T. Pantelides, "Effects of hydrogen motion on interface trap formation and annealing," *IEEE Trans. Nucl. Sci.*, vol. 51, no. 6, pp. 3158–3165, Dec 2004.

- [36] A. J. Lelis, T. R. Oldham, and W. M. DeLancey, "Response of interface traps during high-temperature anneals," *IEEE Trans. Nucl. Sci.*, vol. 38, no. 6, pp. 1590–1597, Dec 1991.