# École Polytechnique Fédérale de Lausanne

SEMESTER PROJECT

BACHELOR IN COMMUNICATION SYSTEMS

# Bidirectional transformation between BIP and SysML for visualisation and editing

*Authors:* Clément NUSSBAUMER Leandro KIELIGER Supervisors: Dr. Simon BLIUDZE Dr. Anton IVANOV

January 13, 2017

# Contents

| 1 | Intro<br>1.1<br>1.2<br>1.3 | oduction       3         Designing software and advantages of model-based design       3         Link between the visualisation and the code       3         Our work and structure of the report       3 |

|---|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 |                            | kground 5                                                                                                                                                                                                 |

|   |                            | BIP model and tool set                                                                                                                                                                                    |

|   |                            | 2.1.1 Atoms                                                                                                                                                                                               |

|   |                            | 2.1.2 Connectors 5                                                                                                                                                                                        |

|   |                            | 2.1.3 Compounds                                                                                                                                                                                           |

|   | 2.2                        | SysML model and tool set                                                                                                                                                                                  |

|   |                            | 2.2.1 Profiles                                                                                                                                                                                            |

|   |                            | 2.2.2 Stereotypes                                                                                                                                                                                         |

|   |                            | 2.2.3 Blocks and properties                                                                                                                                                                               |

|   |                            | 2.2.4 Ports                                                                                                                                                                                               |

|   |                            | 2.2.5 Connectors                                                                                                                                                                                          |

|   |                            | 2.2.6 Internal Block Diagram                                                                                                                                                                              |

|   |                            |                                                                                                                                                                                                           |

| 3 |                            | presentation of BIP models in SysML 9                                                                                                                                                                     |

|   | 3.1                        | BIP $\leftrightarrow$ SysML conceptual mapping and transformation challenges 9                                                                                                                            |

|   |                            | 3.1.1       Representing atoms       9         3.1.2       Representing port types       9                                                                                                                |

|   |                            |                                                                                                                                                                                                           |

|   |                            |                                                                                                                                                                                                           |

|   | 2.2                        |                                                                                                                                                                                                           |

|   | 3.2                        | Customization                                                                                                                                                                                             |

|   |                            | 3.2.1BIP2 profile (UML extension)103.2.2MagicDraw custom descriptor11                                                                                                                                     |

|   |                            | 3.2.2 MagicDraw custom descriptor                                                                                                                                                                         |

| 4 | Too                        | l overview 12                                                                                                                                                                                             |

|   | 4.1                        | MD Workbench                                                                                                                                                                                              |

|   | 4.2                        | MD Access                                                                                                                                                                                                 |

|   | 4.3                        | BIP compiler libraries                                                                                                                                                                                    |

|   | 4.4                        | MagicDraw                                                                                                                                                                                                 |

|   |                            | Ŭ                                                                                                                                                                                                         |

| 5 | -                          | elementation details 14                                                                                                                                                                                   |

|   | 5.1                        | Preliminary explanations                                                                                                                                                                                  |

|   |                            | 5.1.1 Package transformation                                                                                                                                                                              |

|   |                            | 5.1.2 Port types transformation                                                                                                                                                                           |

|   |                            | 5.1.3 Atom type transformation                                                                                                                                                                            |

|   |                            | 5.1.4 Connector type transformation                                                                                                                                                                       |

|   |                            | 5.1.5 Compound transformation                                                                                                                                                                             |

|   | 5.2                        | Inverse transformation                                                                                                                                                                                    |

| 6 | Ucir                       | ng MagicDraw to generate BIP models 23                                                                                                                                                                    |

| 0 | 6.1                        | Populating the root compound   23                                                                                                                                                                         |

|   | 6.2                        | Adding behavior to the atoms   25                                                                                                                                                                         |

|   | 6.3                        | Global structure visualization                                                                                                                                                                            |

|   | 6.4                        | Generating the BIP code                                                                                                                                                                                   |

|   | 0.1                        |                                                                                                                                                                                                           |

| 7  | Usiı   | ng the developed tools                                                            | 28 |

|----|--------|-----------------------------------------------------------------------------------|----|

|    | 7.1    | Command line interface                                                            | 28 |

|    | 7.2    | Using the CLI to transform models                                                 | 28 |

|    |        | 7.2.1 CLI usage                                                                   | 28 |

|    |        | 7.2.2 Sample BIP2 $\rightarrow$ SysML transformation                              | 29 |

|    |        | 7.2.3 Sample SysML $\rightarrow$ BIP2 transformation                              | 29 |

|    | 7.3    | CLI usage additional information                                                  | 29 |

|    |        | 7.3.1 Defining the logging level                                                  | 29 |

|    |        | 7.3.2 Serializing BIP models                                                      | 29 |

|    |        | 7.3.3 MD Workbench license                                                        | 30 |

|    | 7.4    | MagicDraw extensions                                                              | 30 |

|    |        | 7.4.1 Importing and using the custom profile                                      | 30 |

|    |        | 7.4.2 Importing and using the custom descriptor                                   | 30 |

|    | 7.5    | Tool limitations                                                                  | 31 |

|    |        |                                                                                   |    |

| 8  | Case   | e study 1: Multiple layers nested compound                                        | 32 |

|    | 8.1    | Port type                                                                         | 32 |

|    | 8.2    | Atom type                                                                         | 32 |

|    | 8.3    | Connector type                                                                    | 34 |

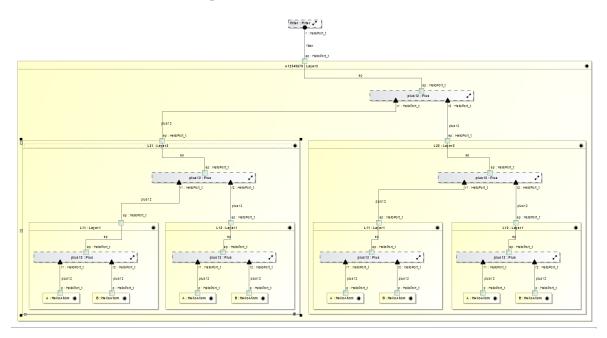

|    | 8.4    | Compound type                                                                     | 35 |

|    | 8.5    | Encompassing compound                                                             | 37 |

|    | 8.6    | Modifying the SysML representation and generating the corresponding code          | 37 |

| 0  | Con    | a study 0. Houseksening perdead                                                   | 39 |

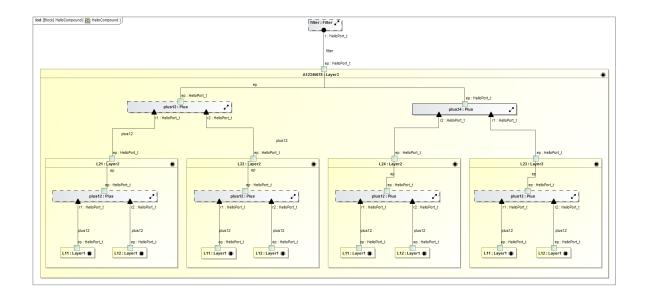

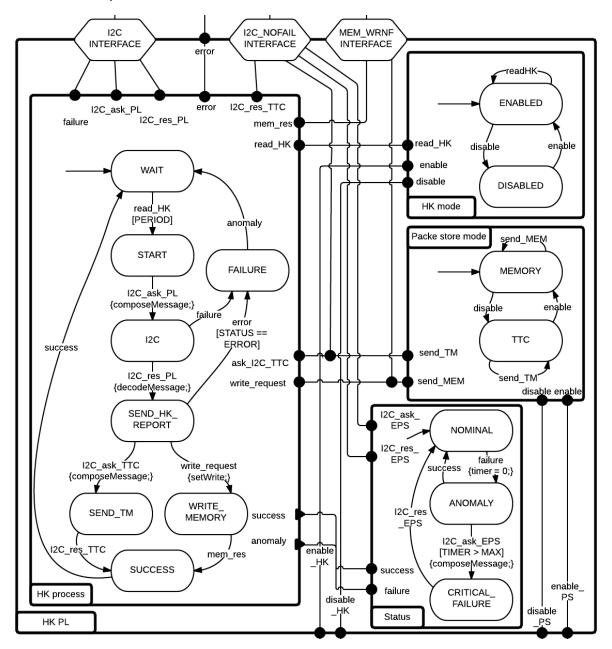

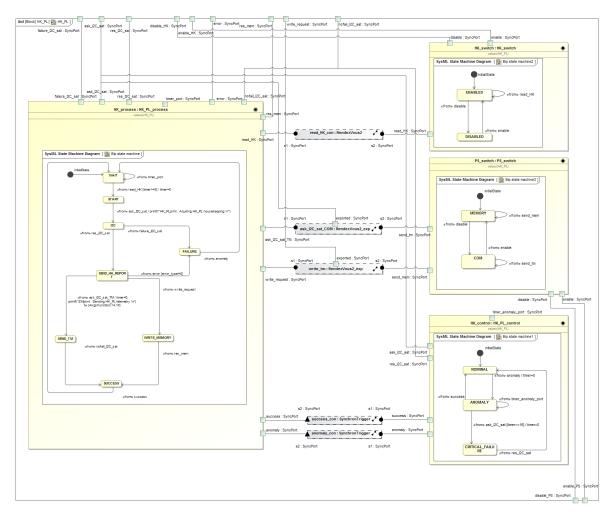

| 9  | Case   | e study 2: Housekeeping payload                                                   | 39 |

| 10 | Con    | clusion                                                                           | 41 |

| 10 |        | Results                                                                           | 41 |

|    |        | Potential project extensions                                                      | 41 |

|    | 10.2   | 10.2.1 Extending the transformation beyond the structural features of a BIP model | 41 |

|    |        | 10.2.2 Developing the transformation as part of the BIP compiler                  | 43 |

|    | 10.3   | Suggestions for tool improvements                                                 | 43 |

|    | 10.0   | 10.3.1 MD Workbench and MD Access                                                 | 43 |

|    |        | 10.3.2 BIP ports interfacing                                                      | 44 |

|    |        | 10.0.2 Dif porto interfacing                                                      | 11 |

| Re | eferer | ices                                                                              | 45 |

| А  | BIP    | code                                                                              | 46 |

| 11 |        | ComplexPackage BIP code                                                           | 46 |

|    |        | Code generated from the DFA SysML model                                           | 47 |

|    | 11.2   |                                                                                   | т/ |

# 1 Introduction

# 1.1 Designing software and advantages of model-based design

When it comes to designing software, the classic procedure consists of writing code that complies with the projects requirements first, and then to extensively test for bugs and defects. Although this approach is valid and can produce correct results, it is both time consuming and error prone. Moreover, depending on the time of detection, errors can turn out to be very difficult to correct. Model-based design however allows for verification prior to the coding task. The component-based approach allows to master complexity by structuring systems hierarchically into sub-components where each of them can be designed and validated individually. Despite this approach leading to an increased initial cost of development, it has the significant advantage of detecting and correcting problems early in the life cycle of a project, when errors are relatively inexpensive to fix. Using the BIP framework and its semantics, it is possible to develop models which are correct by construction. This further reduces testing and validation costs.

# **1.2** Link between the visualisation and the code

Visualisation of systems helps engineers better detect design problems, as well as better conceptualize the system as a whole. It facilitates the communication between the teams involved in a project. Indeed, each subsystem can be displayed at any level of detail, thus efficiently encapsulating complexity when working on different parts of the system. Model-based design creates by definition a well-defined structure which is perfectly suited for visual representations. Each component of the model along with its interactions with the rest of the system be can represented by entities in a diagram.

Of course, visual representations are far beyond the abstraction level usually employed to program a computer. Therefore, to simulate, verify or deploy a model on hardware, a set of instructions needs to be generated from a given programming language. Because of the inherent structure of the model, it is natural to express the need of modifying the system directly from its visual representation, rather than modifying the underlying code.

This observation leads us to a central feature required for most component-based frameworks: the need of having a direct and consistent link between the visual representation of a model and its underlying code. Changes should be bidirectional, this means that any alteration made to the visual representation should be propagated accordingly to the code, and vice versa.

# 1.3 Our work and structure of the report

In this project we experimented the possibility of visually expressing the structure of a BIP model in a modeling language. We call this conversion the *forward* transformation while modification of the BIP code upon changes made to the SysML model is called the *backward* transformation.

The modeling language chosen to express the BIP semantics is the "Unified Modeling Language" (UML) extension for systems modeling: SysML. It is strictly speaking a profile for UML and is one of the industry standards for designing systems. This choice offers us in the scope of this project the ability to leverage powerful modeling tools designed to work with SysML such as NoMagic's "MagicDraw".

In this report we will start by briefly providing in section 2 the necessary background on the BIP and SysML languages needed to understand how the transformation works. We will continue by offering an overview of the tools we used in section 4. Sections 5, 6 and 7 will explain in details

how the transformation is implemented and how to use the developed tools in order to apply the transformation algorithm. We will finish this report by studying 2 transformations in section 8; one, done step-by-step, for a relatively simple BIP model and one, more complex, which contains nested components and which was used in the context of the CubETH project. [1], [2]

# 2 Background

# 2.1 BIP model and tool set

Using the definition from the Verimag laboratory which is in charge of the BIP project [3]:

The BIP (Behavior / Interaction / Priority) framework is intended for design and analysis of complex, heterogeneous embedded applications. BIP is a highly expressive, componentbased framework with rigorous semantics. It allows the construction of complex, hierarchically structured models from atomic components.

In the BIP language, a system is defined in terms of its internal components. Every component expresses a behavior and can be connected to other components of the system via connectors. Those connectors define what we call the "interactions" between components of the system. Finally, the BIP language uses priorities to reduce non-determinism, when a choice has to be made between multiple possible interactions.

The BIP language is specified by an ECore meta-model which is used for parsing and generating code: first, the BIP parser creates an instance of the meta-model which corresponds to the entities declared in the code [4]. Then, this model instance is used by the compiler for generating code in a common programming language (C++ by default). We will see later in this report how a BIP Ecore model instance can be used to generate a visual representation of a BIP system.

## About ECore

ECore is the base meta-model for the Eclipse Modeling Framework (EMF), a project initially developed by IBM and then transferred to the Eclipse Foundation, which provides code generation and model manipulation tools.

## 2.1.1 Atoms

The Atom is the most basic component in BIP. It has an internal behavior which is defined by a finite state automaton. An atom can declare a list of ports which allow interactions with neighboring components in the system as well as a list of internal variables.

Ports in an atom have a type, a name and an optional list of previously declared variables that can be exported. This signifies that they become accessible outside the atom itself. An example of a port type declaration can be found in section 8.1.

#### 2.1.2 Connectors

A connector is a stateless element that defines how components in the system interact with each other. They can enforce strong synchronization between a subset of the components they connect but also transfer data between them. A connector can declare an exported port which is unique and can in turn be connected to another component. When a connector connects ports exported by other connectors, it is said to be *hierarchical*.

## 2.1.3 Compounds

A compound is also a component, but unlike an atom, it does not define its own behavior. Instead, it can contain other components such as atoms and compounds, as well as a set of connectors wiring those components together. Equivalently to the atom, it can declare a set of exported ports that become visible to other components in the model. These ports can reference ports exported either by inner components or inner connectors.

# 2.2 SysML model and tool set

According to the definition of the Object Management Group (OMG) [5]:

*SysML is a general-purpose graphical modeling language for specifying, analyzing, designing, and verifying complex systems.*

SysML is an extension<sup>1</sup> of the more general "Unified Modeling Language" (UML), which provides engineers a way of conceptualizing products in terms of subsystems. It allows them to specify the requirements, the behaviors and the constraints for each component of the system in order to ensure the product's effective operation.

#### About the Object Management Group

OMG is a nonprofit international technology standards consortium. They are at the base of the UML and SysML specifications. [6]

Using SysML, it is possible to create a model representation synthesizing all engineering aspects of a product. It allows a nested model representation of a system, which is used to describe the model at various levels of abstraction: the deeper sub-models cover a tiny part of the product's operation but in great details, whereas the higher-level components link all the elements together while hiding their complexity.

SysML defines nine diagram types, out of which two were used in the scope of this project. Each diagram type specify how SysML entities are visualized as graphical symbols. There are three main categories of diagrams, where each one helps characterizing an aspect of the system:

- Requirements diagram

- Behavior diagrams:

Activity diagram: behavior based on flow and transformation of input to outputs

Sequence diagram: behavior based on message exchange between components

State machine diagram: behavior based on a current state and its transitions

Use case diagram

• Structure diagrams:

Block Definition Diagram: describe hierarchy and associations between components

Internal Block Diagram: shows the internal structure and wiring of a component

Parametric Diagram: shows constraints that components should respect

Package Diagram: organisation of the project in terms of packages

In the next subsections we will describe the main components from SysML that were used in the scope of this project.

<sup>&</sup>lt;sup>1</sup>We explain what we mean by "extension" in section 2.2.1

## 2.2.1 Profiles

A profile is a mechanism for extending and customizing UML for a particular domain. It contains a collection of stereotypes (see section 2.2.2, below), properties (which can be referred to as tag definitions) and constraints. SysML is an example of such extension; it was designed to allow systems modeling in contrast to UML which is more software oriented.

When modeling the structure of a project, it is necessary to apply a profile in order to use customized elements. A model with a profile applied to it is said to be *profiled*. It is possible to apply multiple profiles to a single model and it is in fact what was realized for this project; we applied to a single model created from a BIP package both the SysML profile and an additional profile we designed specifically for BIP (see section 3.2). Once a model is profiled, it is possible to apply the stereotypes defined by the profile to the model elements.

## 2.2.2 Stereotypes

A stereotype is a way of defining new elements that are specific to a given domain through the extension of an existing UML metaclass. For example the SysML stereotype «ProxyPort» extends the UML metaclass "Port" and the «Block» stereotype extends the "Class" metaclass. Stereotypes may have properties which help define a customized terminology for a specific domain. We describe in the next section which SysML stereotypes were useful in the context of this project.

#### Note

Stereotypes are usually drawn in diagrams as being surrounded by French quotation marks:  $\ll \gg$ . Since we juggle various terminologies in this report, we keep this convention to avoid confusion with other types and names.

#### 2.2.3 Blocks and properties

A block is a discipline-independent element and as the name suggests, it is the building block for modeling systems. Blocks can be assembled to form complex architectures that represent how different elements in the system co-exist. A block can contain properties which are structural features. Those properties have a type (which can be another block or a primitive type such as an Integer) that defines their characteristics. Properties are assembled to stipulate the behavior of the block. There exist three kinds of properties which are distinguishable from each other depending on the entity used to type them:

- Part properties: they are typed by blocks and decompose their owning block into constituent elements thus defining a composite relationship.

- Reference properties: they are typed by blocks but do not have a composite relationship with their owning block. Instead, they refer to parts of other blocks.

- Value properties: they are typed by value types and represent quantifiable characteristics of a block.

For example, we can create a SysML block describing a car and another block describing a wheel. The car block can then have four part properties (or simply parts) which are typed by the wheel block to describe the composition relationship existing between a car and a set of wheels.

## 2.2.4 Ports

A port represents an access part on the boundary of a block or any part or reference typed by that block. They can be connected to each other using binary connectors to support interactions between them. SysML defines two types of ports; full ports and proxy ports. Full ports constitute integral parts of their owning block that can cross the boundary of the block and access external features. They are typed by a block and can have their own behavior as well as the ability of modifying their inputs and outputs. Proxy ports on the other hand are not a part of their parent block. Instead, they provide external access to the feature of the parent block, without having any effect on the inputs or outputs. Proxy ports are typed by an "Interface Block" which specifies the features that can be accessed through the port.

## 2.2.5 Connectors

Connectors are used to connect two parts inside a block and provide an opportunity for those parts to interact. However, the connector itself does not say anything about the nature of the interaction. The latter is specified by the behavior of the parts it connects and can consist of a flow of inputs and outputs, the invocation of a service in one of the parts or an exchange of messages.

## 2.2.6 Internal Block Diagram

An internal block diagram is used to show the connections and relationships between parts owned by that block. The boundaries of an internal block diagram always represent a block which is the parent of all entities shown on the internal block diagram.

# 3 Representation of BIP models in SysML

We leverage the fact that BIP is defined by an Ecore meta-model in order to perform the transformation. Indeed, when compiling a project, the BIP compiler will generate an instance of the BIP Ecore meta-model. It is then possible to intercept the compilation at this stage and directly work with the Ecore model representation. Conversely, we can generate BIP code from the Ecore model instance.

This meta-model instance will be the "source" representation for BIP models. The "destination" will be an instance of a UML model with the SysML profile and the BIP profile (see section 3.2.1 applied to it. The transformation we implemented is then actually performed between these two model representations. The reason for this is that on one hand the BIP compiler can be used to generate BIP code from the Ecore model instance and on the other hand, standard tools for SysML can easily load the profiled UML model.

# **3.1 BIP** $\leftrightarrow$ **SysML** conceptual mapping and transformation challenges

## 3.1.1 Representing atoms

We expressed BIP atoms in SysML using the  $\ll$ Block $\gg$  stereotype. Exported ports are expressed as SysML proxy ports, as they are passive entities that only offer access to the atom behavior and cannot modify the (optional) data they export. (See subsection 2.2.4)

It is quite straightforward to transform the behavior of a BIP atom into SysML as both domains use automata to this end.

## 3.1.2 Representing port types

The equivalent to a BIP port type in SysML is the «InterfaceBlock» stereotype. Interface blocks are a special kind of block that does not contain any internal structure and are therefore well suited for typing ports.

## 3.1.3 Representing connectors

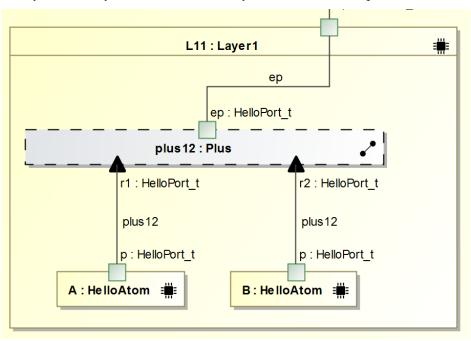

The main difference between BIP and SysML is the fact that SysML connectors are binary and cannot affect the parts they connect whereas BIP connectors can connect multiple components and transfer data between them. To overcome this limitation in SysML, we decided to model BIP connectors by declaring a "Block" for each connector type. We add to this block one port per component to connect and wire them to all components referenced in the BIP connector. This choice of representation has the notable advantage of allowing the SysML connector block to have an effect on the data it carries, just like in BIP. However, as this goes beyond the pure structural aspect of a BIP package that we intended to translate, interactions and data transfers transformations were not implemented in the context of this project, although the structure we chose to put in place would permit it.

## 3.1.4 Representing compounds

BIP compounds are also expressed using the  $\ll$ Block $\gg$  stereotype. Indeed, in SysML, blocks can contain other components just like in BIP. Therefore, BIP components declared inside the compound are modeled as Part Properties. There is nevertheless one subtlety that arises when transforming BIP compounds to SysML blocks.

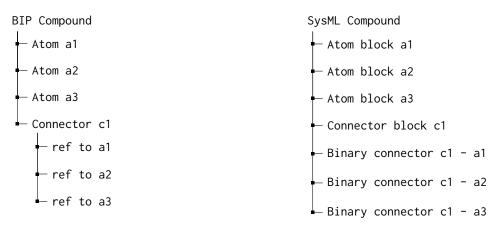

As said in the previous subsection, SysML connectors are purely binary and we must declare a connector block to be able to replicate the BIP connector structure. This leads to a structural change:

in SysML, binary connectors connecting the connector block to the connected components must be owned by the enclosing compound block whereas in BIP they are owned by the connector declaration itself. The following hierarchical diagram illustrates the structural difference:

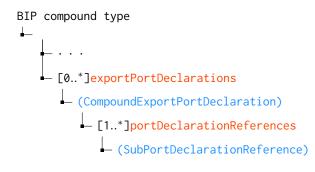

BIP compounds have the ability to export ports declared by their internal components. This is translated in SysML by creating a new port owned by the SysML compound block and then connecting this new port to the corresponding port exported by an internal part. As this port is only here to give access to some internal feature, it is typed by the SysML «ProxyPort» stereotype.

# 3.2 Customization

The need for customizing UML for BIP arose for two main reasons. Since all SysML components are modeled using blocks, they are displayed in the same fashion in the diagrams and can be difficult to tell apart. Therefore, it is more convenient to have a way of visually differentiating atoms from connectors and compounds. Moreover, when it comes to the backward transformation, we need a way of differentiating the SysML components to translate them back to BIP. This is why we took the decision of extending the possibilities offered by UML. This was executed by first adding customized stereotypes in a new profile and then customizing the way the SysML modeling tool, MagicDraw, displayed components where such stereotypes were applied.

## 3.2.1 BIP2 profile (UML extension)

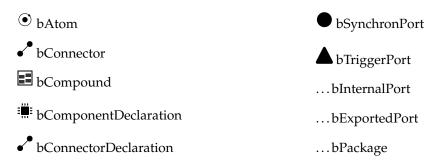

As described in section 2.2.1, it is possible to extend the possibilities offered by UML by the means of a *profile*. We therefore devised a BIP2 profile which contains the stereotypes described below. Note that because of the similarities between stereotype names in the profiles we used for this project, all BIP stereotypes are prefixed with the lowercase letter 'b'.

These stereotypes are intended to be used in addition to SysML stereotypes. For example, an atom translated in SysML will have both  $\ll$ Block $\gg$  and  $\ll$ bAtom $\gg$  stereotypes applied to it.

In summary, the SysML profile describes to the SysML-compliant tools how to handle the model and the BIP profile helps us identify the different components visually and for the backward transformation.

## 3.2.2 MagicDraw custom descriptor

Now that all transformed element types are in theory distinguishable from each other, we can define how MagicDraw will display those elements to the user. MagicDraw uses what is called a "descriptor" to specify how different elements should be drawn on a diagram. A descriptor defines colors, shapes and layout properties for each element type and there exists at least one descriptor per diagram type. For our project we customized the "Internal Block Diagram" descriptor in order to express the structure of BIP models.

This custom descriptor can be found in the "ExtendedSysML" folder as explained in section 7.4. It modifies the diagram as follows:

- Connector declarations are drawn as a rectangle with a gray background

- Synchron ports are drawn with a black circle

- Trigger ports are drawn with a black triangle with rounded corners

All other elements are left with their default display properties: a rectangle with a yellow/orange background for component declaration and a gray square with green outline for all ports which are not explicitly typed  $\ll$ bSynchronPort $\gg$  or  $\ll$ bTriggerPort $\gg$ .

# 4 Tool overview

# 4.1 MD Workbench

MD Workbench[7] is an Eclipse extension commercialized by the SODIUS company that enables transformations between various data structures and models (e.g. UML, Ecore, XML, ...). During this project, we used it to read serialized BIP files to generate meta-model instances and then to convert them to SysML.

As explained earlier, SysML is a profile for UML and therefore SysML files generated using MD Workbench are strictly speaking "UML files profiled with SysML". However, for the sake of simplicity, we will call them SysML files in this report.

The UML meta-model is available in MD Workbench as a MD Access plugin that also contains the SysML 1.3 Profile. Therefore, in order to generate SysML files, we need to create a UML Model using MD Workbench's UML meta-model handler, and then to apply the SysML profile onto it.

The serialized BIP files, which are model instances based on the BIP meta-model, are not natively supported by MD Workbench. However MD Workbench allows for the generation of a specialized meta-model handler, called a MD Access plugin. This process is covered in the following subsection.

# 4.2 MD Access

MD Workbench provides a generic way of creating "MD Access plugins" from an Ecore meta-model. These plugins provide a way of reading from, or writing to, meta-model instances. They enable the MD Workbench software to work with any kind of data structure, thus making it a universal model transformation tool.

Generation of a MD Access plugin is done using the "MD Workbench/Metamodel" import wizard. This wizard first asks the user for the Ecore Meta-model describing the data structure for which to create a MD Access plugin, and it then lets the user select which namespace prefix and which namespace URI to use for the generated MD Access plugin.

#### Namespace prefix and URI

A namespace is a mean of providing structure and of categorizing elements in an XM-L/XMI/Ecore/... file. A namespace is specified by a namespace prefix and URI; the namespace prefix can be seen as the folder in which elements belonging to a namespace are located, and the URI is used to uniquely identify the namespace. This is better explained by an example: in the BIP2 meta-model, there are several namespaces: one of them is the types namespace. Its namespace prefix is bip2.ujf.verimag.bip.types, the associated URI is http://bip2/ujf/verimag/bip/types/1.0 and it contains the various BIP types mentioned in section 2.1 (e.g. AtomType, ConnectorType, ...)

The choice was done not to change the default values, hence the BIP2 MD Access namespace prefix is bip2, and the associated namespace URI is http://www.mdworkbench.com/bip2.

unfortunately, when the BIP MD Access plugin is generated via MD Workbench, the original BIP Ecore meta-model structure is modified, and its package structure is flattened. In the original BIP meta-model we have 11 sub packages (e.g. types, data, port, behavior, priority, connector, ...) each with a specific namespace prefix and URI and each containing specific BIP classes, whereas in the BIP MD Access meta-model, all the BIP classes are located in the same namespace (with the namespace prefix bip2 and the namespace URI http://www.mdworkbench.com/bip2). This package flattening limitation will prevent any use of the BIP MD Access extension to generate BIP models

that are compatible with the BIP compiler, as the models generated with the BIP MD Access plugin will not have the same structure as the models generated using the original BIP meta-model.

# 4.3 **BIP compiler libraries**

As the BIP MD Access plugin can not be used to generate BIP model instances, we decided to use the original BIP2 libraries contained in the BIP compiler distributed by Verimag [8] to generate model instances. These Java libraries contain the BIP2 Ecore meta-model with the correct sub-package structure, and we can therefore use them to generate .xmi files that will be correctly parsed by the BIP compiler.

# 4.4 MagicDraw

MagicDraw is a software and system modeling tool developed by NoMagic [10]. It fully supports the UML2 meta-model and is one of the standard tools used in the industry. In the context of this project we used MagicDraw to generate SysML diagrams for the profiled models we exported via our transformation software. Naturally, we also used MagicDraw to modify or even create from scratch SysML models that were later passed as input to the inverse transformation for generating BIP code.

MagicDraw allows for customization at various levels through user-defined modules. We used for instance in this project the ability to change the visual representation of an entity based on its type or its applied stereotypes via a descriptor. (See section 3.2.2)

# 5 Implementation details

## 5.1 **Preliminary explanations**

Since the terminologies used in the meta-models and in the Java code can be quite confusing, we used in the following sections a color code to distinguish different types of elements:

- Java-related fields and variables are colored in purple

- BIP and SysML meta-model types such as BIP AtomType or UML Property are colored in blue

- Attributes of meta-model types such as BIP atoms' internalPortDeclarations list or UML ownedAttribute list are colored in orange.

When transforming BIP entities to SysML, one problem that often arise is to keep track of the created components to access them later when they are referenced from another entity.

For example, suppose that at the beginning of the transformation, we find a BIP PortType called "bip\_type\_A". We create the appropriate SysML *«InterfaceBlock»* for it, say "sysml\_type\_A", and further in the transformation process, we find a BIP AtomType which precisely uses a port of type "bip\_type\_A". When converting the BIP AtomType, we will need to set up its port with the right SysML type, that is to say "sysml\_type\_A".

Therefore, to find this type back, we must keep track of the association between "bip\_type\_A" and "sysml\_type\_A" during the whole transformation process. This can be done in Java using HashMaps<sup>2</sup>. For the forward transformation we created the association tables listed below (similar tables were used for the return transformation):

| PortType to Class                            | portTypeMap                                     |

|----------------------------------------------|-------------------------------------------------|

| ConnectorPortParameterDeclaration to Port    | portDeclarationMap                              |

| ComponentType to Class                       | componentTypeMap                                |

| ConnectorType to Class                       | connectorTypeMap                                |

| PortDeclaration to Port                      | internalPortMap                                 |

| PortDeclaration to Port                      | exportedPortMap                                 |

| ComponentDeclaration to Property             | componentDeclarationToPropertyMap               |

| ConnectorDeclaration to Property             | connectorDeclarationToPropertyMap               |

| • bip2.State to uml21.State                  | statesMap                                       |

| <ul> <li>String to uml21.DataType</li> </ul> | dataTypeMap                                     |

| - 1                                          | . In the imported Declarge Cost California in t |

To keep track of imported BIP packages we store them in the importedPackagesSet field which is of type HashSet. See section 5.1.1 for explanations about the utility of such a set.

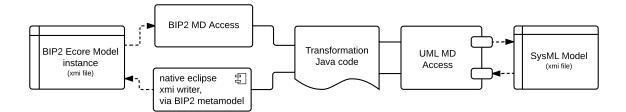

The following diagram illustrate how our transformation software integrates with the existing tools to perform the model transformation.

Note how the MDAccess plugin offers an interface for manipulating the model instances, except for the return transformation where we directly used the BIP libraries, for the reasons mentioned in section 4.2.

<sup>&</sup>lt;sup>2</sup>Note that in Java, if an object does not redefine the "equals" and "hashCode" methods then two keys in a HashMap are considered to be the same if and only if they reference the same object in memory. Since the meta-model elements do not redefine those methods, the hash map will create an entry for every BIP entity transformed, which is precisely what we want.

Figure 1: Transformation flow BIP  $\leftrightarrow$  SysML

#### 5.1.1 Package transformation

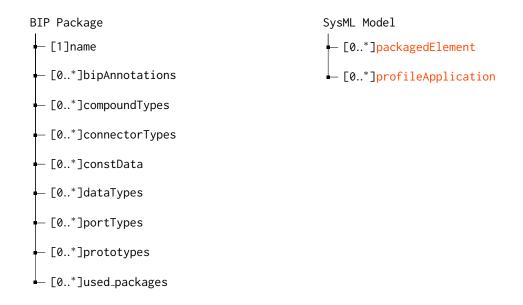

The main challenge in converting the BIP packages to SysML is to keep the package structure from one representation to the other. We leveraged the fact that each BIP Package references imported packages in its used\_packages attribute. When we encounter a Package import, it means that we first have to transform the imported Package, otherwise we may arrive at a point in the transformation where there are references to types that have not yet been transformed. To avoid this, we iterate over the imported packages list and recursively apply the transformation to them before pursuing with the transformation of the "root" package.

#### – Note

For simplicity purposes, our implementation of the package transformation does not support cyclic imports. That is, if package A uses package B and package B uses package A, our transformation will not halt.

Every SysML package created is added to the importedPackagesSet so that a given BIP package is transformed only once even if it is imported in multiples places.

Each BIP package transformation creates its own atom, connector and compound converters. Therefore entities created during a given Package transformation will have the corresponding SysML package as their owning package. Association tables however, are global to the model transformation which allows SysML entities registered during the transformation of a Package to be retrieved during all subsequent Package transformations.

For example, if a Package declares every AtomType for the project and nothing else, then during the transformation of this package we will have created all the corresponding SysML atom **«Blocks»**. The componentTypeMap will be populated with BIP AtomType - SysML Class pairs (We use the Class meta-type as it is the supertype of **«Blocks»**). Suppose that later on, there is a compound which declares components typed by the previously converted BIP AtomTypes. Then, thanks to the association tables, we will be able to retrieve the corresponding SysML atom **«Blocks»** type even if the transformation is now happening inside another package.

Local converters allied with global association tables allow us to replicate the BIP package structure. Note that the transformation is done in the order formed by the following sub-sections of this report.

#### 5.1.2 Port types transformation

BIP PortTypes declaration are quite simple to transform; they only store a list of PortDataParameter-Declarations. Therefore, to convert a BIP PortType declaration to SysML, we create a new *«Inter-faceBlock»* and add as owned attributes the specified data parameters which are represented using UML's Property type. We finally register a key-value pair where the BIP port type is the key and the newly created SysML interface block is the value into the portTypeMap association table.

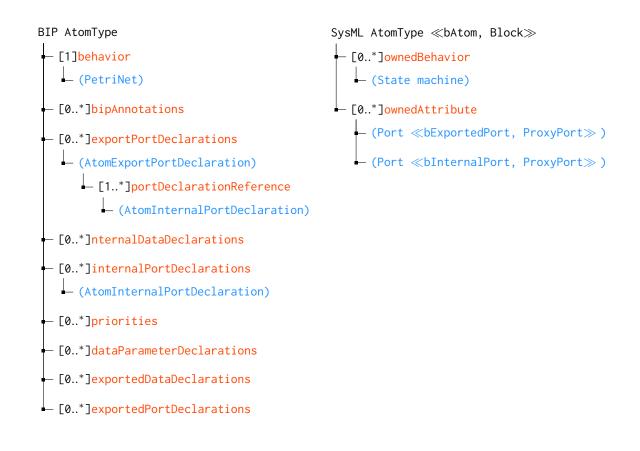

The tree diagrams that you will find in the following sub-sections illustrates on the left-hand side the structure of BIP types as they are organized in the BIP Ecore meta-model, as well as the multiplicity of their attributes. The right-hand side shows the structure of a corresponding SysML model. Meta-model types between parenthesis denote which types of entities could be contained in a given tree node.

| BIP PortType                                       | <code>SysML PortType</code> $\ll$ InterfaceBlock $\gg$ |  |

|----------------------------------------------------|--------------------------------------------------------|--|

| [0*]dataParameterDeclaration                       | <pre>[0*]ownedAttribute</pre>                          |  |

| <ul> <li>(PortDataParameterDeclaration)</li> </ul> | - (Property)                                           |  |

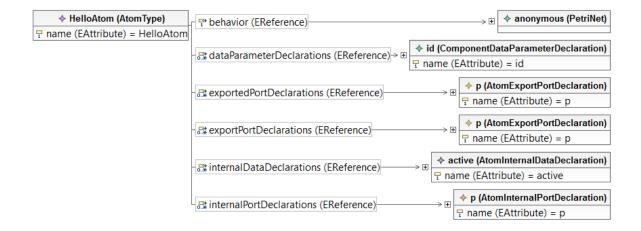

#### 5.1.3 Atom type transformation

Note in the following tree diagram how BIP defines exported ports for the AtomTypes: it first defines the internal ports of the atom and then references a subset of those internal ports as being exported. On the SysML structure side, ports are registered as "owned attributes" and the state machine as an "owned behavior".

In the SysML Model we applied the *description* stereotype to the exported ports, and the *description* stereotype to the other ports (i.e. the internal ports).

The BIP behavior attribute, which is a PetriNet, is converted to a SysML StateMachine. The details of the conversion for transitions between states are the following:

- If a BIP port labels a transition, then the corresponding SysML port is marked as a trigger for the SysML transition.

- Transition effects are mapped to SysML OpaqueBehaviors which contain a textual representation of the original BIP Expressions.

- Guards for BIP transitions are mapped to OpaqueExpressions that contain a textual representation of the BIP guards.

The dataParameters, internalDataDeclarations, priorities, exportedPortDeclarations, exported-DataDeclarations and DataParameterDeclarations attributes were not converted to SysML as they do not influence directly the structure of the system.

We keep track of the newly created internal and exported ports by registering a key-value pair where the BIP port is the key and the SysML port is the value in the internalPortMap and exportedPortMap respectively. This allow us to easily retrieve the corresponding SysML ports whenever a reference to the BIP ports shows up in the meta-model instance.

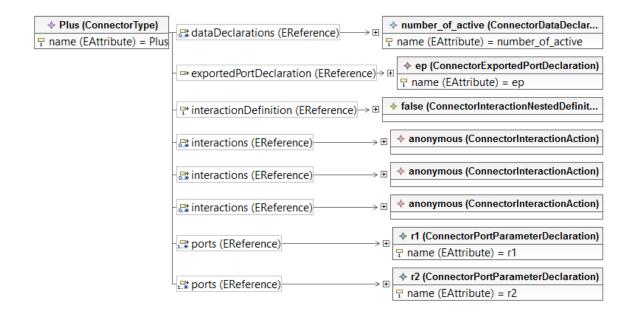

#### 5.1.4 Connector type transformation

The following diagram illustrates the mapping between BIP ConnectorType and SysML connectors, which are in fact SysML  $\ll$ Classes $\gg$  typed with the  $\ll$ Block $\gg$  and  $\ll$ bConnector $\gg$  stereotypes.

The BIP language defines the properties of the ports at multiple places: the ports are declared within the ConnectorPortParameterDeclarations attribute, but the trigger/synchron property is defined in the interactionDefinition attribute, which itself references the aforementioned ConnectorPortParameterDeclaration. In the SysML representation however, we made the choice to simply store the trigger/synchron property of each port in the port definition itself.

There can only be one exported port per BIP connector, and the corresponding SysML port is typed with the *description* stereotype.

Additional information such as the interactions, bipAnnotations and DataDeclarations were not converted.

BIP ConnectorType

[1..\*]ports

[0..\*]ownedAttribute

[0..\*](Port ≪bConnector, Block≫

[0..\*]ownedAttribute

[0..\*](Port ≪bTriggerPort, ProxyPort≫)

[0..\*]interactionDefinition

[0..\*]interactions

[0..\*]interactions

[0..\*]bipAnnotations

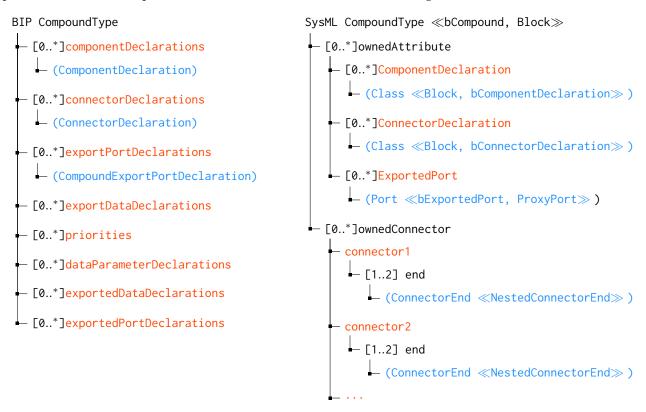

5.1.5 Compound transformation

- [0..\*]DataDeclarations

— [0..\*]dataParameterDeclarations

- [0..\*]exportedDataDeclarations

- [0..\*]exportedPortDeclarations

BIP Compounds are by far the most complex elements to transform. Indeed, they usually employ components whose type were previously declared during the transformation process and they store the actual structure and wiring of the system. As usual, you will find below the structure of a BIP Compound as it is represented in the Ecore meta-model, as well as the target structure we achieved for SysML. The transformation of BIP Compounds is done in four phases:

- 1. Instantiate the components inside the compound block.

- 2. Instantiate the connectors and connect components and connectors inside the compound block.

- 3. Create exported ports declared by the compound.

- 4. Connect exported ports to the ports of the internal parts they refer to.

Of course, the order in which we apply the different transformation phases matter as it would be impossible to connect components and connectors if there were still missing declarations.

**First phase** We iterate over the ComponentDeclarations and, for each declaration, create a Property which is stereotyped *<bcomponentDeclaration*. This property is added as an ownedAttribute of the compound we are transforming. The Property name is set to match the name used in the BIP model for the ComponentDeclaration. To set the correct type for the SysML property, we need to retrieve the BIP type of the BIP ComponentDeclaration and find the associated SysML type in the componentTypeMap association table. Finally, we register a key-value pair where the BIP ComponentDeclaration is the key and the UML Property is the value into the componentDeclarationToProperty association table. This will be useful for the second phase, when we connect components and connectors.

**Second phase** It consists of two steps. First, we iterate over the ConnectorDeclaration and, for each declaration, create a Property which is stereotyped **ConnectorDeclaration**. The procedure is similar to the first phase but this time we query the connectorTypeMap and register the key-value pair into the connectorDeclarationToProperty map.

The second step is to actually connect the connector declaration Property to the correct parts. As explained in section 3.1.3, this is done by using SysML binary connectors. Such connectors have two ends (typed «NestedConnectorEnd»), each of which must declare a role and a partWithPort attribute (optional). A role is the port entity defined in an atom or connector type while the partWithPort

is the actual component or connector declaration that owns the port.

The difference between these attributes is better explained by an example: suppose we declare a compound C and an atom type A which has an exported port p. Inside the compound C are declared two components (atoms) typed by A: comp1 and comp2. To connect them using a SysML connector, the **role** attribute of both ends will be the port p. However, the **partWithPort** attribute will be comp1 on one side and comp2 on the other.

```

SysML connector

↓ [2]end

↓ (ConnectorEnd ≪NestedConnectorEnd≫)

↓ role

↓ partWithPort

↓ (ConnectorEnd ≪NestedConnectorEnd≫)

↓ role

↓ partWithPort

```

The information about which part to connect is stored in the BIP ConnectorDeclaration. For each port specified in the ConnectorType, there is a PortDeclarationReferenceParameter in the ConnectorDeclaration. This reference holds a subPortDeclarationReference attribute which is a grouping of two elements very similar to the SysML attributes for connectors; a forwardPortDeclaration which is the equivalent of role and a componentDeclaration which is the equivalent of the partWithPort attribute. We therefore use these attributes to create the SysML connector, as illustrated by the tree structure below:

#### BIP connector declaration

- └── [0..\*]portParameters

- - [1]subPortDelcarationReference

- (subPortDeclarationReference)

- componentDeclaration

- forwardPortDeclaration

Using this information we are now able to connect connector-component pairs. SysML ports corresponding to BIP ports specified in the forwardPort attribute are retrieved using the exportedPortMap association table and SyML part properties using either componentDeclarationToProperty or the connectorDeclarationToProperty depending on the type of the entity at the other end of the connector.

Due to a rendering issue on MagicDraw where connectors do not appear to be connected to the right components, we needed to manually set an attribute specific to the ConnectorEnd type. This special

attribute, called propertyPath takes the same value as the partWithPort attribute in the connector end<sup>3</sup>.

**Third phase** This phase is trivial as it only consists of creating exported ports for the compound, based on the exportPortDeclarations of the BIP compound. All SysML compound ports are associated with their respective BIP compound ports into the exportedPortMap.

**Fourth phase** The last step shares many similarities with the component connecting phase. Each time a compound exports a port from one of its internal components, it creates in the meta-model instance a compoundExportPortDeclaration.

To create the corresponding SysML connector, we set the **role** attribute in the connector ends as explained previously. However, this time one end of the connector is connected to the compound itself, therefore it does not correspond to any part property inside the compound  $\ll$ Block  $\gg$  and the partWithPort attribute should be left empty on this particular side. We can set partWithPort as usual on the opposite side as we know that it will be connected to a component or a connector declaration. Again, the special attribute propertyPath is set manually to ensure a correct representation in MagicDraw.

To conclude the compound transformation we only need to add the newly created SysML compound to the componentTypeMap. Compounds are considered components because they should be usable inside other compounds to define a nested structure.

## 5.2 Inverse transformation

The backward transformation follows a similar process than what has been described in the previous sections. Therefore, we will not cover its details, as they mainly consist of rebuilding the original BIP structure from the SysML entities. Since SysML models were customized to reflect the BIP nature of their components, it is very easy to retrieve entities by their type and perform the inverse transformation in the same order as the forward transformation. (First the packages, then the port types and so on.)

There exists one main difference nevertheless. Instead of using MD Workbench and MD Access to set up the BIP model from the SysML representation, we directly used the BIP libraries provided by Verimag (as mentioned in section 4.3). This had the immense advantage of providing us with Java factories for creating BIP types. These factories provide complete interfaces for instantiating BIP entities easily while they take care of creating the proper structure and setting the appropriate

$<sup>^{3}</sup>$ It is not clear whether the issue comes from the MD Workbench implementation or if the propertyPath is intended to be set manually

references for the objects in the background.

Ideally, the forward transformation should have been done the same way as explained in section 10.2.2. Unfortunately, because of time constraints this was not possible.

The following snippet shows how a connector factory can be used to create a BIP connector declaration. This connector declaration is then added to its owning compound:

```

1 ConnectorDeclaration conDecl = ConnectorFactory.eINSTANCE.createConnectorDeclaration();

2 conDecl.setName(...);

3 conDecl.setType(...);

4

5 [...]

7 compoundType.getConnectorDeclarations().add(conDecl);

```

# 6 Using MagicDraw to generate BIP models

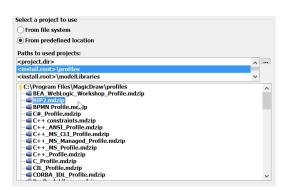

Figure 2: Importing the BIP2 profile

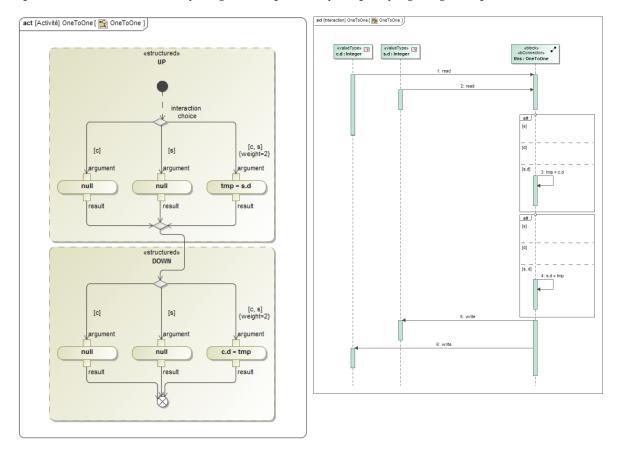

In this section we demonstrate how to model a simple system from scratch using MagicDraw with the objective of generating BIP code from it. We first create a new SysML project that we will call "DFA". DFA stands for Deterministic Finite Automaton, as the system described below is a classical example used in automata theory. Before starting, make sure you configured MagicDraw to use both the custom BIP profile and the BIP descriptor. Instructions for carrying out this operation are given in section 7.4.1 and 7.4.2.

We can now start modeling our system. For this demonstration we will create the structure of a Tur-

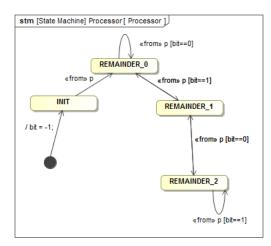

ing machine capable of determining if its input is a number divisible by 3 or not. This project consists of two atoms and one connector; the tape atom models the input of the Turing machine while the processor models the action table and the transition table. Upon each " tick" from the BIP engine, the connector transfers one bit from the tape to the processor. For this example however, the data transfer, which represent the reading head of the machine, will not be modeled. The input on the tape is supposed to be an integer representing a binary number stored in little-endian format.

Now that we have an idea of what the system consists of, we can start creating SysML entities for it. First, we add two atom types to the root model (DFA). This is done by right-clicking the DFA model and selecting "Create Element" (or Ctrl+Shift+E). We select the BIP atom type as this will create a new UML class with the  $\ll$ Block $\gg$  and  $\ll$ bAtom $\gg$  stereotypes applied to it. Name the two atom types "Tape" and "Processor" respectively.

Duplicate this procedure to create a new connector type that we will call "ReadingHead".

To allow for data transfers using the exported ports, we create the equivalent of a BIP port type, which is an  $\ll$ InterfaceBlock $\gg$ , and add to it a value property "k" of type Integer.

| Zoom Documentation   | Properties                | )            |

|----------------------|---------------------------|--------------|

| Properties           | <b>=</b>                  | ∎ <b>∓</b> × |

| Element Language pro | operties                  |              |

| ti 2↓                | Expert                    | $\sim$       |

| Value Property       |                           | ^            |

| Name                 | k                         |              |

| Qualified Name       | numPort::k                |              |

| • Туре               | 🛛 🗹 Integer [SysML::Libr. |              |

| Type Modifier        | Integer [SysM             | L            |

| Visibility           | Integer [Sysivi           | L::LIDI      |

| Default Value        |                           |              |

| Applied Stereotype   | ValueProperty [Prop       | erl          |

| Multiplicity         | (Unspecified)             |              |

| Is Read Only         | false                     |              |

| Is Static            | false                     |              |

| Aggregation          | composite                 |              |

| Is Derived           | false                     |              |

| Is Derived Union     | false                     |              |

| Is Ordered           | false                     | $\sim$       |

Figure 3: Property panel for Interface Block

Specifying the type of an element can be done

via the "Property panel" on the bottom left of the screen. We can now add a root compound that will contain every element of our system. To do so, create a new compound element in the same fashion as previously done for the atoms and name it "EnclosingCompound".

# 6.1 Populating the root compound

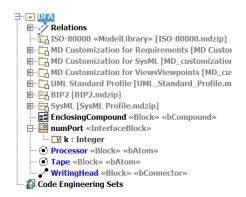

Figure 4 shows what the project structure should look like at this point. We will now start assembling our system using the previously declared entities. Select the "EnclosingCompound" object and press

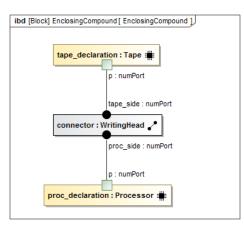

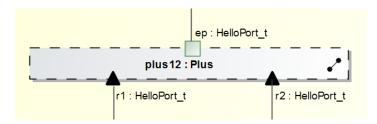

the "Create diagram" button (or Ctrl+N). We will create a BIP-specific diagram (Section 7.4.2 shows how to import the BIP descriptor), which is a modified version of an "InternalBlockDiagram". Using the palette on the bottom left of the diagram window, we create two components. Using the "Smart manipulators" which are the buttons that appear when clicking on an element in the diagram, we can specify the type of all three declared inner elements by clicking the red "T" character.

Again using the "Smart manipulators", we can add one external port for the Tape and the Processor, and two synchron ports to the connector. With the same procedure, we specify the type of each declared port to be the "numPort"  $\ll$ InterfaceBlock $\gg$ .

Figure 4: Project containment tree.

Note

Ports added via the internal block diagram are automatically added to the port type as it can be seen on the project containment tree on the left of the screen. However, deleting an element in the diagram does not remove it from the project structure.

Finally, we connect the corresponding ports and press the "Quick Layout Button" to get the following structure:

Tip

As the name suggests, the quick layout button (Ctrl+Q) allows to quickly reorganize the diagram content to improve readability.

## 6.2 Adding behavior to the atoms

| ransition          |                             |

|--------------------|-----------------------------|

| Name               |                             |

| Qualified Name     | Tape::Tape::::              |

| Owner              | 📖 [Tape::Tape]              |

| Applied Stereotype |                             |

| Guard              |                             |

| Target             | READ [Tape::Tape::]         |

| Source             | READ [Tape::Tape::]         |

| Image              |                             |

| Το Do              |                             |

| Documentation      |                             |

| Trigger            |                             |

| Event Type         | <unspecified></unspecified> |

| Trigger            |                             |

| Event Element      |                             |

| Port               |                             |

| Effect             |                             |

| Behavior Type      | <unspecified></unspecified> |

| Behavior Element   |                             |

Figure 5: Property panel for transitions. The port field specifies which port enables the transitions, the guard field is self-explanatory Atom behavior are specified using SysML state machines. To create state machines, simply create a new diagram (Ctrl+N) of type "SysML State Machine Diagram". MagicDraw automatically creates an initial region that we can leave unnamed. Since BIP uses 1safe automata, we will not need any additional region.

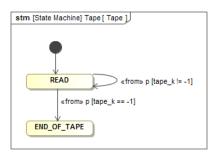

Thanks to the palette on the bottom left of the diagram window, we can add states and transitions to the state machine. We start by defining the Tape's behavior. It needs two states, READ and END\_OF\_TAPE, READ being the initial state of the machine.

The idea is that from the initial state to READ, we load an integer parameter given when instantiating the Tape atom. This will model the content of the Tape. At each "tick", we advance the tape head by one position by dividing the current number by 10, thus eliminating the rightmost bit (the most significant one). The rightmost bit is sent to the processor atom and the cycle is repeated until the integer number is left equal to zero.

Transitions for the Tape atom are defined as shown in the state machine diagram below. Guards and ports references can be specified using the property panel for a transition instance (see figure 5).

#### • Note

Functions calls and effects can be specified in SysML and will be printed along the transition arrows, but they will not be converted to BIP as our implementation does not handle functional elements. Similarly, we construct the state machine for the processor atom:

# 6.3 Global structure visualization

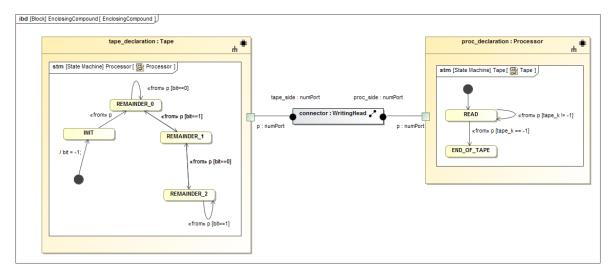

We would now like to visualize the atom behavior directly in the enclosing compound. This is achievable by creating an internal block diagram or BIP diagram for each atom type and then dragging the state machine diagram from the project containment tree into the internal block diagram.

In the BIP diagram for the enclosing compound, right-clicking on the components and selecting "Display internal parts" allows us to visualize the behavior of each atom. (Remember that you can use the quick layout button in case adding the behavior made the diagram unreadable)

Figure 6: Final structure

# 6.4 Generating the BIP code

To perform the backward transformation we need to export the project into files comprehensible by our software. This is done via the File menu and the export option. We use the "Eclipse UML2 (v2.X) XMI File" format.

Among the files exported by MagicDraw we find an UML file whose name corresponds to our SysML project name. This is the file that we need to specify for the backward transformation. Upon completion of the transformation, the software will produce as output an XMI file whose name corresponds to the base SysML model; in our case "DFA". The inverse BIP compiler can work on this XMI file to generate the code shown in appendix A.2.

# 7 Using the developed tools

The transformation tool is distributed as a Java Archive (jar) with a Command Line Interface (CLI).

In order to better visualize and work with SysML models, we also developed a set of extensions and settings for NoMagic Inc. "MagicDraw" software.

# 7.1 Command line interface

The transformation tool is contained in the file Bip2ToSysML.jar, and it depends on several libraries that are located in the modules/ folder. The directory structure of the transformation tool and its dependencies is represented in the following diagram:

modules/

bip2MDAccess/

Contains the BIP2 MD Access plugin, used to read serialized BIP files

bipc-2014.05/

Contains the BIP Compiler libraries, from which we use the BIP meta-model

eclipse-libs/

Contains the eclipse libraries from the BIP compiler

sodius/

Contains SODIUS MD Workbench libraries

jopt-simple-6.0.jar

A small library used for the command line interface

# 7.2 Using the CLI to transform models

#### 7.2.1 CLI usage

The CLI is executed with the following command: java - jar BIP2ToSysML.jar, to which we append the argument --mode to specify the transformation mode.

- --mode direct (or shorter -m d), when doing a BIP2  $\rightarrow$  SysML transformation

- --mode inverse (or shorter -m i), when doing a SysML  $\rightarrow$  BIP2 transformation

The CLI then takes a mandatory --input-file argument, that specifies the file that is to be transformed, and an optional --output-file argument. The --output-file argument specifies the file in which the SysML model is written when doing a direct transformation.

When doing an inverse transformation, --output-file, is used to specify the folder in which the converted BIP packages will be written (each BIP package will be written to a file whose name corresponds to the package name). If the output-file argument is not specified, the output files will be located in the same folder as the input files.

## 7.2.2 Sample BIP2 $\rightarrow$ SysML transformation

One can convert for example the ComplexPackage [12] model from a BIP2 serialized .xmi file<sup>4</sup> to a SysML .xmi file with the following command:

java -jar Bip2ToSysML.jar --mode direct --input-file /some/path/ComplexPackge.xmi \

--output-file /output/path/ComplexPackage\_SysML.xmi

## 7.2.3 Sample SysML $\rightarrow$ BIP2 transformation

The command to convert a SysML .xmi model to (a) BIP2 serialized file(s) is similar:

java -jar Bip2ToSysML.jar --mode inverse --input-file /some/path/ComplexPackage\_SysML.xmi \

--output-file /output/path/

## 7.3 CLI usage additional information

#### 7.3.1 Defining the logging level

In order for the transformation tool to print more debugging information, the logging level can be specified with the argument --level LOGGING\_LEVEL, where LOGGING\_LEVEL can be one of the following levels: SEVERE, WARNING, INFO, CONFIG, FINE, ... (the levels are those specified in the documentation of the java.util.logging.Level class [14]).

In order to obtain maximum information during the transformation, append the argument --level ALL to the transformation command.

#### 7.3.2 Serializing BIP models

When doing a direct transformation, the BIP input file is the serialized version of the meta-model instance created during the parsing of the .bip file. This input BIP file is an .xmi file, and it can be obtained with the following arguments appended to the BIP compiler (bipc.sh) command: -s xmi -so serialized. These arguments specify that the output format for the serialized file is xmi, and that the output folder is serialized/.

For the "hello-world" example that is on Verimag documentation website [13], this gives :

```

bipc.sh -I . -p HelloPackage -d "HelloCompound()" -s xmi -so serialized

```

The xmi file(s) created in the serialized/ folder can then be used as input files for a direct transformation.

<sup>&</sup>lt;sup>4</sup>Generation of BIP serialized models is explained in section 7.3.2

## 7.3.3 MD Workbench license

You need a valid SODIUS MD Workbench license in order to use the transformation tool. You can specify it either by:

• adding a mdw.lic file<sup>5</sup> containing the license information in the modules/sodius/ folder

```

modules/

sodius/

mdw.lic The SODIUS license file

```

specifying the license location as a java System property with the following argument:

Dmdw.license=@license\_server appended to the java command that executes the tool. i.e.

java -Dmdw.license=@license\_server -jar BIP2ToSysML.jar --...

# 7.4 MagicDraw extensions

There are several files (located in the ExtendedSysML folder) that are used for the integration of the BIP2 UML Profile, as described in section 3.2.1:

- BIP2.mdzip : this file contains the BIP2 Profile stored in mdzip<sup>6</sup> format, and it is needed by MagicDraw when opening a BIP SysML model.

- descriptors/BIP Diagram descriptor.xml This file re-defines MagicDraw behavior when it comes to the drawing of an "Internal Block Diagram", as explained in section 3.2.2.

#### 7.4.1 Importing and using the custom profile

We need to inform MagicDraw of the location of the BIP profile before it can display and apply BIP stereotypes to our model. We recommend copying the BIP2Profile.mdzip file that can be found in the ExtendedSysML folder of our project into the profiles folder folder of the *MagicDraw installation*. Doing so will help you faster select the BIP profile when opening a model coming out of the transformation process.

To use the BIP profile when creating a project from scratch, navigate to File >Use project >Use local project and select the BIP2Profile.mdzip file. You should be able to see in the project containment tree that the BIP profile was imported.

#### 7.4.2 Importing and using the custom descriptor

In order to be able to display and use SysML diagrams customized for BIP, you need to import the custom descriptor we prepared for this project. To accomplish this, navigate in the menu the following way: Diagrams > Customize. From the dialog window that appeared on the screen, you should be able to import a descriptor. Select the descriptor contained in the "ExtendedSysML/descriptor/" folder and restart MagicDraw.

<sup>&</sup>lt;sup>5</sup>The license file is a text file complying with the Flexera license file format. For a standard license setup, its content is the following:

SERVER someServer.epfl.ch 27000

<sup>&</sup>lt;sup>6</sup>The mdzip file format corresponds to a zip-compressed MagicDraw project

From now on, you can create BIP-adapted SysML diagrams by pressing the "Create Diagram" button on the top of the screen (Ctrl + N). The customized descriptor should be located in the SysML category.

#### . Tip

When creating a new diagram, MagicDraw will prompt you to indicate which elements you want to initially display. By pressing the Shift key during a click on the containment tree, you can automatically select every sub-element of the selected entity.

# 7.5 Tool limitations

Because the transformation software is a prototype, the program may fail when encountering "corner cases". Note that the following cases are not supported:

- Cyclic dependencies between BIP packages

- Two levels of nested interaction definitions in BIP connectors

- In a BIP Atom, if an ExportPortDeclaration (see section 5.1.3) references more than one internalPort, then only the first internalPort will be set up as exported in the SysML model

Moreover, invalid BIP or SysML models fed to the transformation program will most likely raise an exception. You may be able to locate the source of the issues based on the output of the Java logger and the exception message. However, due to time constraints we did not implement an extensive validity check on the inputs. Providing as much information as possible to the user in case the transformation could not be completed would be a welcome improvement to the project.

# 8 Case study 1: Multiple layers nested compound

In this section, we will document how the various parts of a simple BIP compound are converted. The reference compound is the ComplexCompound with hierarchical components presented on the BIP documentation website tutorial section [12]. The BIP code of this compound is available in appendix A.1.

# 8.1 Port type

The BIP language works by connecting components through typed ports that can convey information. The syntax used to define these typed ports is straightforward, as well as their meta-model representation.

#### **BIP** code

port type HelloPort\_t(int d)

#### Meta-model representation

| HelloPort_t (PortType)          | - 🕞 dataParameterDeclarations (EReference) → 🗉 | ♦ d (PortDataParameterDeclaration) |

|---------------------------------|------------------------------------------------|------------------------------------|

| name (EAttribute) = HelloPort_t |                                                | name (EAttribute) = d              |

#### SysML representation

The converted SysML port has a list of typed attributes corresponding to the list of variables defined in the BIP port type, and the  $\ll$ InterfaceBlock  $\gg$  stereotype is applied to it.

```

HelloPort_t «InterfaceBlock»

```

The port will be represented on SysML internal block diagrams as a  $\ll$ ProxyPort $\gg$ , with the following icon:

#### 8.2 Atom type

A simple BIP Atom is presented here: it has one exported port, and its behavior only defines one state (LOOP). There is a transition from the state LOOP to itself that is labeled by the port p. A guard was put on this transition so that it is allowed only if the variable active is equal to 1.

#### **BIP** code

```

atom type HelloAtom(int id)

data int active

a export port HelloPort_t p(active)

place LOOP

a initial to LOOP

a do { active = 1; }

on p from LOOP to LOOP

```