## A Steep-Slope Transistor Combining Phase-Change and Band-to-Band-Tunneling to Achieve a sub-Unity Body Factor

Wolfgang A. Vitale<sup>1†</sup>, Emanuele A. Casu<sup>1</sup>, Arnab Biswas<sup>1</sup>, Teodor Rosca<sup>1</sup>, Cem Alper<sup>1</sup>, Anna Krammer<sup>2</sup>, Gia V. Luong<sup>3</sup>, Qing-T. Zhao<sup>3</sup>, Siegfried Mantl<sup>3</sup>, Andreas Schüler<sup>2</sup> & A. M. Ionescu<sup>1</sup>

## **Supplementary Figures**

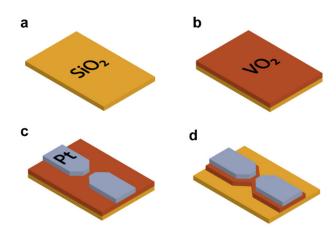

**Supplementary Figure 1** | **Fabrication Process of VO<sub>2</sub> devices**. (a) VO<sub>2</sub> devices are fabricated starting from a silicon substrate with a thermal silicon oxide layer of 200 nm on top. (b) A 200 nm thick VO<sub>2</sub> layer is deposited with reactive sputtering of a Vanadium target in an O<sub>2</sub>/Ar plasma at 600 °C substrate temperature. (c) Switch electrodes are defined via electron beam lithography on PMMA/MMA and lift-off of a 100 nm thick Platinum film. (d) VO<sub>2</sub> is removed around the switch area using electron beam lithography on ZEP and ion beam etching.

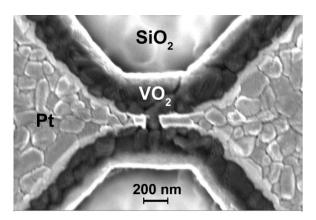

**Supplementary Figure 2** | **VO<sub>2</sub>-based MIT switch.** SEM image of a VO<sub>2</sub> switch, showing a relatively large VO<sub>2</sub> average grain size ~100 nm, resulting in a large and steep thermal MIT.

<sup>&</sup>lt;sup>1</sup> Nanoelectronic Devices Laboratory (NanoLab), Ecole Polytechnique Fédérale de Lausanne (EPFL), 1015 Lausanne, Switzerland

<sup>&</sup>lt;sup>2</sup> Solar Energy and Building Physics Laboratory (LESO-PB), Ecole Polytechnique Fédérale de Lausanne (EPFL), 1015 Lausanne, Switzerland

<sup>&</sup>lt;sup>3</sup> Peter Grünberg Institut 9 (PGI-9), Forschungszentrum Jülich, 52425 Jülich, Germany

<sup>†</sup> Corresponding author; mail: wolfgang.vitale@epfl.ch

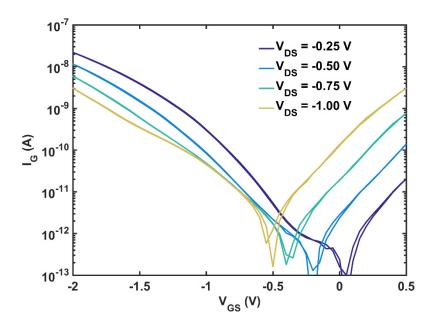

**Supplementary Figure 3** | **TFET gate leakage**. Leakage current in the TFET used as a component for the PC-TFET for different values of drain voltage  $V_{\rm DS}$ , ranging from -0.25 V to -1 V. Measurements performed at room temperature.

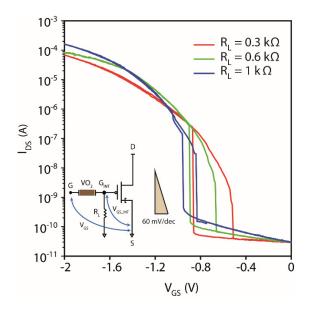

Supplementary Figure 4 | Effect of the load resistance  $R_{\rm L}$  on the actuation voltage  $V_{\rm GS\_act}$  in gate configuration.  $I_{\rm DS}$ - $V_{\rm GS}$  of PC-TFET in gate configuration measured at room temperature with different  $R_{\rm L}$  values, ranging from 0.3 k $\Omega$  to 1 k $\Omega$ , keeping constant  $V_{\rm DS}$  = -0.75 V.

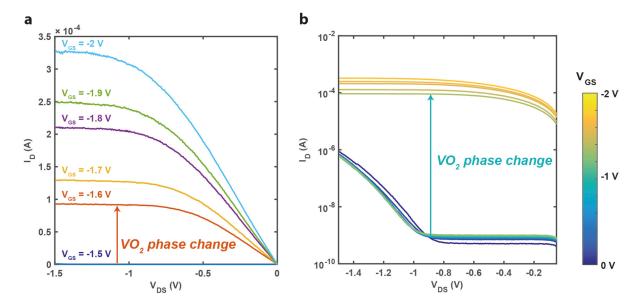

Supplementary Figure 5 | Output characteristics of PC-TFET in gate configuration. (a) Output characteristics of a PC-TFET in gate configuration for different applied  $V_{\rm GS}$ , ranging from -0.25 V to -1 V, measured at room temperature. (b) Same output characteristics in logarithmic scale, to better show the effect of the phase change in VO<sub>2</sub>.

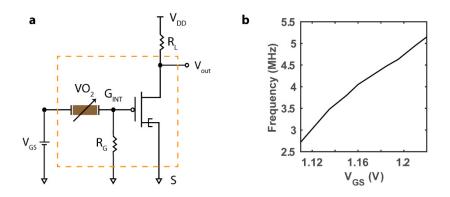

Supplementary Figure 6 | Voltage-controlled buffered oscillator based on the PC-TFET in gate configuration. (a) Circuit schematic diagram, highlighting the PC-TFET in gate configuration. The oscillation induced in the internal gate node  $V_{\rm GS\_INT}$  is read at the output  $V_{\rm out}$ . The PC-TFET in this configuration offers a high output impedance, allowing to decouple the output load from the oscillating source.  $V_{\rm GS}$  varied from 1.11 V to 1.22 V.  $R_{\rm G} = 1~\rm k\Omega$ ,  $R_{\rm L} = 1~\rm k\Omega$ .  $R_{\rm VO2\_OFF} = 10~\rm k\Omega$ ,  $R_{\rm VO2\_ON} = 100~\rm \Omega$ .  $V_{\rm act} = 1~\rm V$ , VO<sub>2</sub> hysteresis: 0.2 V. TFET gate capacitance  $C_{\rm GS} = 50~\rm pF$ . (b) Simulation results, showing a linear dependence of the oscillation frequency on  $V_{\rm GS}$ , from 2.72 MHz to 5.12 MHz.

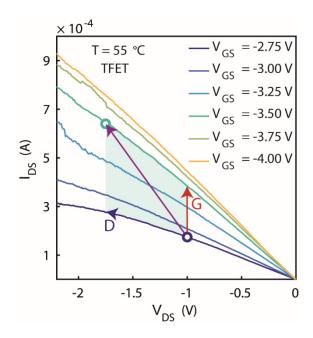

Supplementary Figure 7 | TFET output characteristics and effect of the internal voltage gains in the PC-TFET. The phase transition in VO<sub>2</sub> allows to switch abruptly between the two current points highlighted by a circle in the TFET output characteristics. This abrupt current increase is due to the combined effect of the gate voltage gain  $G = dV_{GS\_int}/dV_{GS} = 75$  (red arrow) and the drain voltage gain  $D = dV_{DS\_int}/dV_{GS} = 75$  (blue arrow). The values of G and D correspond to the ones measured in the PC-TFET in source configuration. Even if G = D, the gate voltage gain has a higher effect on the current increase.

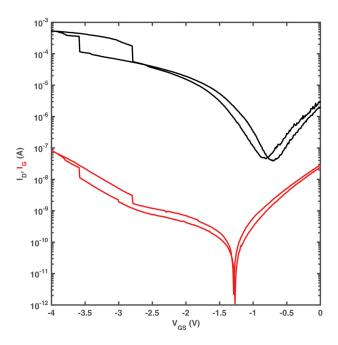

Supplementary Figure 8 | Gate leakage for the PC-TFET in source configuration, compared to drain current. Gate leakage (red) and drain current (black) in function of  $V_{\rm GS}$  for the PC-TFET in source configuration. Measurements performed at T=55 °C with an applied external  $V_{\rm DS}=-2$  V. The gate leakage is negligible compared to the drain current over the whole domain of operation of the PC-TFET.

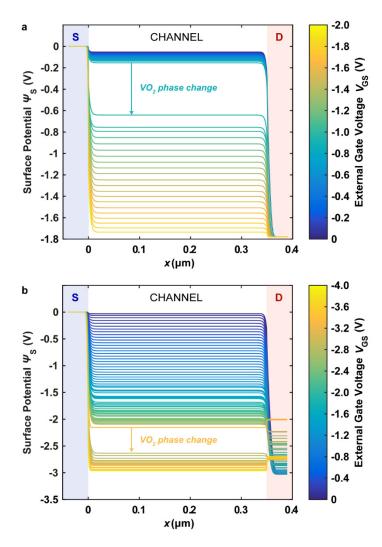

**Supplementary Figure 9** | **Potential cuts along the TFET channel. (a)** Gate configuration. External gate voltage  $V_{\rm GS}$  varying from 0 V to -2 V. External drain voltage  $V_{\rm DS}$  = -0.75 V. Measurements performed at T = 25 °C. **(b)** Source configuration. External gate voltage  $V_{\rm GS}$  varying from 0 V to -4 V. External drain voltage  $V_{\rm DS}$  = -2 V. Measurements performed at T = 55 °C.