# High Voltage and Low Leakage AlGaN/GaN Tri-anode Schottky Diodes with Integrated Tri-gate **Transistors**

Jun Ma and Elison Matioli

Abstract-We present AlGaN/GaN nanostructured Schottky barrier diodes (SBDs) on silicon substrate with high breakdown voltage  $(V_{br})$  and low reverse leakage current  $(I_R)$ , based on a hybrid of tri-anode and tri-gate architectures. The fabricated SBDs presented a small turn-on voltage  $(V_{on})$  of  $0.76 \pm 0.05$  V since the tri-anode architecture formed direct Schottky contact to the 2-dimensional electron gas (2DEG). The reverse characteristic was controlled electrostatically by an embedded tri-gate transistor, instead of relying only on the Schottky barrier. This resulted in low  $I_R$  below 10 and 100 nA/mm at large reverse biases up to 500 and 700 V, respectively. In addition, these devices exhibited record  $V_{br}$  up to 1325 V at  $I_R$  of 1  $\mu$ A/mm, rendering an excellent high power figure-of-merit (FOM) of 939  $\stackrel{\smile}{MW}\!/cm^2$  and demonstrating the significant potential of nanostructured GaN SBDs for future efficient power conversion.

Index Terms-GaN, Schottky diode, tri-gate, tri-anode, breakdown, leakage current.

## I. INTRODUCTION

With the rapid development of GaN power transistors on silicon substrate, GaN lateral SBDs are attracting large attention [1]-[12] since they can be easily and monolithically integrated with such transistors, reducing parasitic inductances, which is highly desirable for future efficient and low-cost power converters. However, conventional AlGaN/GaN lateral SBDs suffer from high  $V_{on}$ , large  $I_R$ , and poor  $V_{br}$ . Sophisticated schemes have been proposed to overcome these issues such as recessed anodes [1] and field plates [2]. However, the reverse blocking performance of GaN SBDs, such as  $V_{br}$  and  $I_R$ , is still much inferior than in state-of-the-art GaN transistors. These are general limitations of SBDs even in other semiconductors. When defining  $V_{br}$  at a leakage current of 1  $\mu$ A/mm, GaN-on-silicon transistors have presented values over 1400 V [13], while only a few SBDs with  $V_{br}$  over 500 V have been reported [2],[4],[11],[12], and the highest value up to date is Texton-state and reverse-blocking performances. The fabricated about 900 V [2].

Novel nanostructured AlGaN/GaN SBDs based on a hybrid combination of tri-anode and tri-gate architectures have been proposed [14] and investigated in our previous studies [15],[16], which yielded a reduced  $V_{on}$ , an improved ideality factor, a diminished  $I_R$ , and an enhanced heat dissipation of the SBDs, at

This work was supported in part by the European Research Council (ERC) under the European Union's H2020 programme/ERC Grant Agreement 679425 and in part by the Swiss National Science Foundation under Assistant Professor (AP) Energy Grant PYAPP2\_166901. The authors are with the Power and Wide-bandgap Electronics Research Laboratory (POWERlab), École polytechnique fédérale de Lausanne (EPFL), CH-1015 Lausanne, Switzerland (e-mail: jun.ma@epfl.ch; elison.matioli@epfl.ch).

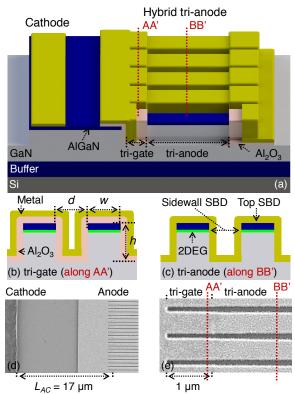

Fig. 1. (a) Schematic of the fabricated tri-anode SBDs. Cross-sectional schematics of (b) the tri-gate region along line AA' and (c) the tri-anode region along line BB'. (d) Top-view SEM image of the fabricated hybrid tri-anode SBDs. (e) Zoomed-in SEM image of the tri-gate and tri-anode regions.

the expense of a larger  $R_{on}$  and a smaller current capability. In addition, the potential of this architecture for high-voltage power SBDs has not been presented. In this work, we demonstrate hybrid tri-anode power SBDs with state-of-the-art SBDs presented a small  $V_{on}$  of 0.76  $\pm$  0.07 V since tri-anode formed Schottky contact directly to the 2DEG. The integrated tri-gate transistor in the SBD largely improved the reverse blocking performance of the device. A record  $V_{br}$  of 1325 V (at  $I_R$  =1  $\mu$ A/mm) among GaN lateral diodes on silicon was achieved, along with a high power FOM of 939 MW/cm<sup>2</sup>. The  $I_R$  of the SBDs was below 10 and 100 nA/mm at blocking voltages up to 500 and 700 V, respectively, which was more than 2 orders of magnitude smaller than up-to-date high-voltage GaN lateral SBDs.

© 2016 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

## II. DEVICE FABRICATION

The AlGaN/GaN epitaxy in this work consisted of 3.75 µm of buffer, 0.3 µm of un-doped GaN (u-GaN) channel, 23.5 nm of AlGaN barrier and 2 nm of u-GaN cap layer. A schematic of the hybrid tri-anode SBD is shown in Fig. 1(a). The anode was formed by a combination of a tri-gate transistor and a tri-anode SBD in series (cross-sectional schematics are shown in Fig. 1(b) and (c)). The device fabrication started with e-beam lithography to define the mesa and nanowires, which were then etched by Cl2-based inductively coupled plasma and followed by ohmic metal deposition and rapid thermal annealing. The height (h) of the nanowires was 166 nm, and the width (w) varied from 100 to 1000 nm while the spacing (d) was fixed at 200 nm. Then 20 nm of Al<sub>2</sub>O<sub>3</sub> was deposited by atomic layer deposition and selectively removed in tri-anode region. Finally the entire anode was formed by Ni/Au, which was later used as the mask for wet-etching of the Al<sub>2</sub>O<sub>3</sub> in access and ohmic regions. Figure 1(d) and (e) show the top-view SEM images of the SBD and the hybrid tri-anode, respectively. The device characteristics such as  $R_{on}$ , forward current  $(I_F)$  and  $I_R$  were normalized by device width (60  $\mu$ m). The error bars presented in all results were determined from measurements on up to 10

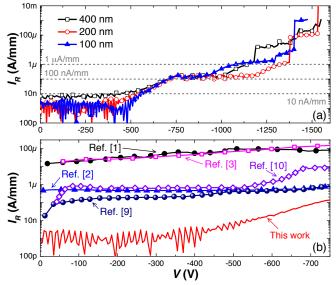

Fig. 2. (a)  $R_{on}$  and  $I_R$  (at -10 V) of tri-anode SBDs with different w. (b) Reverse and (c) forward I-V characteristics of the tri-anode SBDs with w of 400, 200 and 100 nm, normalized by device width of 60  $\mu$ m.

TABLE 1

SUMMARY OF TRI-ANODES WITH DIFFERENT NANOWIRE WIDTHS

|                                       | w = 400  nm     | w = 200  nm     | w = 100  nm     |

|---------------------------------------|-----------------|-----------------|-----------------|

| $V_{on}$ (V, at 1 mA/mm)              | $0.76 \pm 0.07$ | $0.76 \pm 0.05$ | $0.73 \pm 0.06$ |

| $R_{on} \ (\Omega \cdot \mathrm{mm})$ | $10.3 \pm 0.4$  | $11.0\pm0.6$    | $13.1\pm0.8$    |

| $I_F$ (mA/mm, $V = 5V$ )              | $355 \pm 10$    | $332\pm13$      | $275 \pm 13$    |

| $I_R$ (nA/mm, $V = -10V$ )            | $3.03 \pm 1.02$ | $0.96 \pm 0.81$ | $0.15 \pm 0.13$ |

separate devices of the same kind.

## III. Results and Discussion

The impact of w on the  $R_{on}$  and  $I_R$  of the tri-anode SBDs is presented in Fig. 2(a). The observed reduction of  $R_{on}$  with wincreasing from 100 to 400 nm is mainly attributed to the increasing filling factor (FF = w / (w + d)), which preserved more 2DEG in the tri-gate region and hence reduced the resistance of the integrated tri-gate transistors. After w reached 400 nm (FF = 66.7%), the  $R_{on}$  saturated regardless of the increasing w, or equivalently the FF, at about  $10.2 \pm 0.45$  $\Omega$ ·mm, and the  $I_R$ , taken at V = -10 V, kept reducing with decreasing w due to the enhanced gate depletion of the integrated tri-gate transistor with narrower nanowires. With w below 400 nm, the  $I_R$  of all tri-anode SBDs was below 10 nA/mm at a bias of -10 V, and a w of 400 nm yielded a good balance between  $I_R$  and  $R_{on}$ . The  $I_R$  and  $I_f$  of the tri-anode SBDs with w of 400, 200 and 100 nm are plotted in Fig. 2(b) and (c) versus anode voltage (V), respectively, with their detailed characteristics listed in Tab. 1. The tri-anode SBDs with w of 100 nm exhibited  $I_R$  of  $0.15 \pm 0.13$  nA/mm, which is, to the best of our knowledge, the smallest leakage current for GaN lateral SBDs up to date.

Figure 3(a) presents the  $I_R$  of the tri-anode SBDs versus V. All devices exhibited very small  $I_R$  below 10 and 100 nA/mm with V up to about 500 and 700 V, respectively. For V below 400 V, the  $I_R$  of the tri-anode SBDs with w of 200 and 100 nm was close or below the measurement limit of our setup, hence large oscillations in current were observed. The best  $V_{br}$  measured at  $I_R = 1 \mu$  A/mm was 1140, 1325 and 1075 V for the tri-anode SBDs with w of 400, 200 and 100 nm. We have not observed a clear dependence of the  $V_{br}$  on w in this work, and the difference in  $V_{br}$  was likely impacted by local variations in oxide quality or possible fabrication misalignments. Nevertheless, the  $I_R$  profile was quite consistent up to 900 V

Fig. 3. (a) Reverse-bias characteristics of the tri-anode SBDs versus anode bias for different w and (b) comparison of  $I_R$  of the tri-anode SBD (w = 200 nm) and state-of-the-art high-voltage GaN lateral SBDs on silicon. The  $I_R$  for SBDs with w of 200 and 100 nm was likely around or below the measurement limit of our setup.

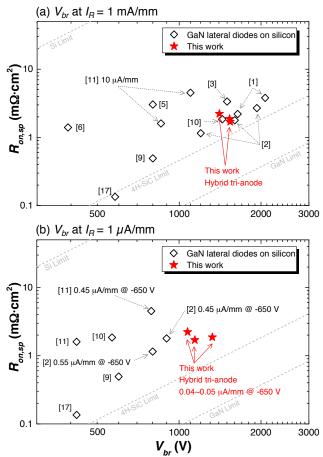

Fig. 4.  $R_{on,sp}$  versus  $V_{br}$  benchmarks of the tri-anode SBDs with state-of-the-art GaN lateral power diodes by defining  $V_{br}$  at  $I_R = 1$  mA/mm (a) and  $1 \mu$ A/mm (b). For fair comparison, lieterature results with unspecified  $R_{on,sp}$  or  $I_R$  were not included.

among all devices with w from 100 to 400 nm, as well as their hard breakdown voltage at around 1400 - 1550 V.

The reverse leakage current of the tri-anode SBDs (w = 200nm) was much lower than that from state-of-the-art high-voltage GaN-on-silicon lateral SBDs (with breakdown voltage beyond 1000 V) in the literature, as plotted in Fig. 3(b). For reverse voltages below 500 V, the  $I_R$  of the tri-anode SBD was about 2 orders of magnitude lower with respect to the smallest  $I_R$  [9] among these references and over 4 orders of magnitude as compared to the reference SBD with the highest reported hard  $V_{br}$  [1]. Most of the references presented  $I_R$  beyond 100 nA/mm and 1  $\mu$ A/mm at V of -100 and -650 V, respectively. In contrast, the  $I_R$  of the tri-anode SBD did not reach 100 nA/mm until -725 V and was as small as 41 nA/mm at -650 V. Such significant reduction in  $I_R$  can potentially improve the reliability of the device, and more importantly, reduce the off-state power dissipation and increase the efficiency of power converters. The off-state power dissipation, calculated using  $Power = I_R \times V$ , varied from 0.31 - 78 mW/mm at -650 V for the reference SBDs, while that of the tri-anode SBD was several orders of magnitude smaller, below 0.03 mW/mm.

The tri-anode SBDs presented in Fig. 3 were benchmarked against state-of-the-art GaN lateral diodes on silicon substrate,

as shown in Fig. 4. Two commonly used definitions of  $V_{br}$  for GaN power devices were adopted, taken at  $I_R = 1$  mA/mm and 1  $\mu$ A/mm. In the benchmark considering  $V_{br}$  at  $I_R = 1$  mA/mm (Fig. 4(a)), the tri-anode SBDs with w of 400, 200 and 100 nm exhibited high power FOMs of 1355, 1255 and 865 MW/cm<sup>2</sup>, respectively, which are comparable to the best results for GaN lateral diodes on silicon and even other substrates [4],[18],[19]. Since 1 mA/mm is a large leakage current level to define the  $V_{br}$ for power devices, 1  $\mu$ A/mm level is becoming more commonly used to compare more fairly the blocking performance of power devices. Figure 4(b) shows the benchmark with  $V_{br}$  at  $I_R = 1 \mu \text{A/mm}$ . The  $V_{br}$  for all reference devices was re-calculated based on the reported data, following the definition of  $V_{br}$  at  $I_R = 1 \mu \text{A/mm}$ . The tri-anode SBDs with w of 400, 200 and 100 nm presented FOM values of 747, 939 and 518 MW/cm<sup>2</sup>. These are high FOM values with record  $V_{br}$ among up-to-date GaN lateral power diodes on silicon, which in addition to the low turn-on voltage, low  $I_R$  and small on-resistance, reveal the extraordinary potential nanowire-based approaches for GaN power electronics.

#### IV. CONCLUSION

In this work we demonstrated high voltage and low leakage AlGaN/GaN tri-anode SBDs with integrated tri-gate transistors. The SBDs exhibited a small  $V_{on}$  of  $0.76 \pm 0.05$  V due to the tri-anode structure. The embedded tri-gate transistor enabled electrostatic control over the leakage current in addition to the Schottky barrier, leading to ultra-low  $I_R$  below 100 nA/mm at reverse bias of 700 V, and high  $V_{br}$  up to 1325 V (1  $\mu$ A/mm). These results confirm the superb potential of the hybrid tri-anode SBDs for future high-efficiency power conversion systems, and offer a technology platform to improve the reverse blocking in lateral SBDs even in other materials.

#### ACKNOWLEDGMENT

The authors would like to thank the staff in CMi and ICMP cleanrooms at EPFL for technical support.

### REFERENCES

- [1] C. -W. Tsou, K. -P. Wei, Y. -W. Lian, and S. S. H. Hsu, "2.07-kV AlGaN/GaN Schottky barrier diodes on silicon with high Baliga's Figure-of-Merit," *IEEE Electron Device Letters*, vol. 37, no. 1, pp. 70-73, Jan. 2016. doi: 10.1109/LED.2015.2499267.

- [2] M. Zhu, B. Song, M. Qi, Z. Hu, K. Nomoto, X. Yan, Y. Cao, W. Johnson, E. Kohn, D. Jena, H. G. Xing, "1.9-kV AlGaN/GaN lateral Schottky barrier diodes on silicon," *IEEE Electron Device Lett.*, vol. 36, pp. 375-377, Feb. 2015. doi: 10.1109/LED.2015.2404309.

- [3] Y.-W. Lian, Y.-S. Lin, J.-M. Yang, C.-H. Cheng, and S. S. H. Hsu, "AlGaN/GaN Schottky barrier diodes on silicon substrates with selective Si diffusion for low onset voltage and high reverse blocking," *IEEE Electron Device Lett.*, vol. 34, pp. 981-983, Jul. 2013. doi: 10.1109/LED.2013.2269475.

- [4] E. B. Treidel, O. Hilt, R. Zhytnytska, A. Wentzel, C. Meliani, J. Würfl, and G. Tränkle, "Fast-switching GaN-based lateral power Schottky barrier diodes with low onset voltage and strog reverse blocking," *IEEE Electron Device Lett.*, vol. 33, pp. 357-359, Jan. 2012. doi: 10.1109/LED.2011.2179281.

- [5] E. B. Treidel, O. Hilt, A. Wentzel, J. Würfl, and G. Tränkle, "Fast GaN based Schottky diodes on Si (111) substrate with low onset voltage and

- strong reverse blocking," *Phys. Status . Solidi C*, vol. 10, pp. 849-852, Jan. 2013. doi: 10.1002/pssc.201200569.

- [6] W. Chen, K. -Y. Wong, W. Huang, and K. J. Chen, "High-performance AlGaN/GaN lateral field-effect rectifiers compatible with high electron mobility transistors," *Appl. Phys. Lett.*, vol. 92, pp. 253501, Jun. 2008. doi: 10.1063/1.2951615.

- [7] W. Lim, J.-H. Jeong, J.-H. Lee, S.-B. Hur, J.-K. Ryu, K.-S. Kim, T.-H. Kim, S. Y. Song, Y.-I. Yang, and S. J. Pearton, "Temperature dependence of current-voltage characteristics of Ni-AlGaN/GaN Schottky diodes," *Appl. Phys. Lett.*, vol. 97, pp. 242103, Dec. 2010. doi: 10.1063/1.3525931.

- [8] J. -H. Lee, C. Park, K. -S. Im, and J. -H. Lee, "AlGaN/GaN-based lateral-type Schottky barrier diode with very low reverse recovery charge at high temperature," *IEEE Trans. Electron Devices*, vol. 60, pp. 3032-3039, Jul. 2013. doi: 10.1109/TED.2013.2273271.

- [9] S. Lenci, B. D. Jaeger, L. Carbonell, J. Hu, G. Mannaert, D. Wellekens, S. You, B. Bakeroot, and S. Decoutere, "Au-free AlGaN/GaN power diode on 8-in Si substrate with gated edge termination," *IEEE Electron Device Lett.*, vol. 34, pp. 1035-1037, Jul. 2013. doi: 10.1109/LED.2013.2267933.

- [10] J. -G. Lee, B. -R. Park, C. -H. Cho, K. -S. Seo, and H. -Y. Cha, "Low turn-on voltage AlGaN/GaN-on-Si rectifier with gated ohmic anode," *IEEE Electron Device Lett.*, vol. 34, pp. 214-216, Jan. 2013. doi: 10.1109/LED.2012.2235403.

- [11] Q. Zhou, Y. Jin, Y. Shi, J. Mou, X. Bao, B. Chen, and B. Zhang, "High reverse blocking and low onset voltage AlGaN/GaN-on-Si lateral power diode with MIS-gated hybrid anode," *IEEE Electron Device Lett.*, vol. 36, pp. 660-662, May 2015. doi: 10.1109/LED.2015.2432171.

- [12] J. Hu, S. Stoffels, S. Lenci, B. D. Jaeger, N. Ronchi, A. N. Tallarico, D. Wellekens, S. You, B. Bakeroot, G. Groeseneken, and S. Decoutere, "Statistical analysis of the impact of anode recess on electrical characteristics of AlGaN/GaN Schottky diodes with gated edge termination," *IEEE Trans. Electron Devices*, vol. 63, pp. 3451-3458, Jul. 2016. doi: 10.1109/TED.2016.2587103.

- [13] N. Ikeda, S. Kaya, J. Li, T. Kokawa, M. Masuda, and S. Katoh, "High-power AlGaN/GaN MIS-HFETs with field plates on Si substrates," 2009 21st International Symposium on Power Semiconductor Devices & IC's, Barcelona, 2009, pp. 251-254. doi: 10.1109/ISPSD.2009.5158049.

- [14] E. Matioli, B. Lu, and T. Palacios, "Ultralow leakage current AlGaN/GaN Schottky diodes with 3-D anode structure," *IEEE Trans. Electron Devices*, vol. 60, pp. 3365-3370, Sep. 2013. doi: 10.1109/TED.2013.2279120.

- [15] J. Ma, G. Santoruvo, P. Tandon, and E. Matioli, "Enhanced electrical performance and heat dissipation in AlGaN/GaN Schottky barrier diodes using hybrid tri-anode structure," *IEEE Trans. Electron Devices*, vol. 63, pp. 3614-3619, Jul. 2016. doi: 10.1109/TED.2016.2587801.

- [16] J. Ma and E. Matioli, "Improved electrical and thermal performances in nanostructured GaN devices," 2016 International Conference on IC Design and Technology (ICICDT), Ho Chi Minh City, 2016, pp. 1-4. doi: 10.1109/ICICDT.2016.7542061.

- [17] J. Hu, S. Stoffels, S. Lenci, B. Bakeroot, B. D. Jaeger, M. V. Hove, N. Ronchi, R. Venegas, H. Liang, M. Zhao, G. Groeseneken, and S. Decoutere, "Performance optimizaiton of Au-free lateral AlGaN/GaN Schottky barrier diode with gated edge termination on 200-mm silicon substrate," *IEEE Trans. Electron Devices*, vol. 63, pp. 997-1004, Jan. 2016. doi: 10.1109/TED.2016.2515566.

- [18] G. -Y. Lee, H. -H. Liu, and J. -I. Chyi, "High-performance AlGaN/GaN Schottky diodes with an AlGaN/AlN buffer layer," *IEEE Electron Device Lett.*, vol. 32, pp. 1519-1521, Sep. 2011. doi: 10.1109/LED.2011.2164610.

- [19] H. Ishida, D. Shibata, H. Matsuo, M. Yanagihara, Y. Uemoto, T. Ueda, T. Tanaka, and D. Ueda, "GaN-based natural super junction diodes with multi-channel structures," 2008 IEEE International Electron Devices Meeting, San Francisco, CA, 2008, pp. 1-4. doi: 10.1109/IEDM.2008.4796636