Silicon-rich silicon-carbide hole-selective rear contacts for crystalline silicon based solar cells

Gizem Nogay<sup>1\*</sup>, Josua Stuckelberger<sup>1</sup>, Philippe Wyss<sup>1</sup>, Quentin Jeangros<sup>1,3</sup>, Christophe Allebé<sup>2</sup>, Xavier Niquille<sup>1</sup>, Fabien Debrot<sup>2</sup>, Matthieu Despeisse<sup>2</sup>, Franz-Josef Haug<sup>1</sup>, Philipp Löper<sup>1</sup>, Christophe Ballif<sup>1</sup>

<sup>1</sup> École Polytechnique Fédérale de Lausanne (EPFL), Institute of Microengineering (IMT),

Photovoltaics and Thin-Film Electronics Laboratory, Rue de la Maladière 71b, 2002 Neuchâtel,

Switzerland

<sup>2</sup> CSEM PV-Center, Jaquet-Droz 1. 2002 Neuchâtel, Switzerland

<sup>3</sup> Department of Physics, University of Basel, Klingelbergstrasse 82, Basel CH-4056, Switzerland

\* Corresponding author e-mail: gizem.nogay@epfl.ch

**KEYWORDS** passivating contacts, silicon carbide, solar cell, chemical oxide, surface passivation

# **ABSTRACT**

The use of passivating contacts compatible with typical homo-juntion thermal processes is one of the most promising approaches to realize high efficiency silicon solar cells. In this work, we investigate an alternative rear passivating contact targeting facile implementation to industrial *p*-type solar cells. The contact structure consists of a chemically grown thin silicon oxide layer,

which is capped with a boron-doped silicon-rich silicon-carbide ( $SiC_x(p)$ ) layer and then annealed at 800°C-900°C. Transmission electron microscopy reveals that the thin chemical oxide layer disappears upon thermal annealing up to 900°C, leading to degraded surface passivation. We interpret this in terms of a chemical reaction between carbon atoms in the  $SiC_x(p)$  layer and the adjacent chemical oxide layer. To prevent this reaction, an intrinsic silicon inter-layer was introduced between the chemical oxide and the  $SiC_x(p)$  layer. We show that this intrinsic silicon inter-layer is beneficial for surface passivation. Optimized passivation is obtained with a 10-nm-thick intrinsic silicon inter-layer, yielding an emitter saturation current density of 17 fA cm<sup>-2</sup> on p-type wafers, which translates into an implied open-circuit voltage of 708 mV. The potential of the developed contact at the rear side is further investigated by realizing a proof-of-concept hybrid solar cell, featuring a heterojunction front side contact made of intrinsic amorphous silicon and phosphorus-doped amorphous silicon. Even though the presented cells are limited by front side reflection and front side parasitic absorption, the obtained cell with a  $V_{oc}$  of 694.7 mV, a FF of 79.1% and an efficiency of 20.44% demonstrates the potential of the  $p^+/p$ -wafer full side passivated rear-side scheme shown here.

## 1. Introduction

State-of the art commercial homo-junction c-Si solar cells are limited by voltage losses due to recombination of charge carriers at the direct metal-semiconductor interfaces. Partial rear contacts (PRC) are currently being implemented by the industry to limit contact recombination by restricting the contact area. However, as a reduced contact area fraction also leads to increased series resistance, PRC cells are inherently limited by a trade-off between minimized recombination and series resistance.<sup>1-2</sup> In addition, the realization of partial rear contacts requires an additional

patterning step, which increases the process complexity. An alternative way to mediate contact recombination is the concept of "passivating contacts" that consists of a thin buffer layer for surface passivation, capped with an additional layer which selectively collects one type of charge carrier. A prime example of passivating contacts are silicon heterojunctions (SHJ), in which surface passivation is provided by intrinsic amorphous silicon (a-Si:H) and carrier selectivity by doped a-Si:H. Recently, Kaneka-Japan reported a record efficiency of 26.33% for a c-Si solar cell using an interdigitated back contacted (IBC) SHJ design.<sup>3</sup> Nevertheless, since the electronic quality of a-Si:H deteriorates at temperatures above 250°C, SHJ solar cells are incompatible with industrial firing through metallization schemes as these include processing at temperatures up to 800°C. For enhanced temperature stability and compatibility with standard solar cell manufacturing processes based on diffusion and firing, a promising approach consists in using silicon oxide as a thin buffer layer capped with doped poly-silicon, semi-insulating poly-silicon (SIPOS) or doped Si-based mixed-phase layers, <sup>4-8</sup> which are thermally annealed to diffuse dopants into the c-Si wafer. Recently, a remarkable efficiency of 25.1% was demonstrated using a similar approach as a rear n-contact in an n-type solar cell with a boron diffused front side. <sup>9</sup> The contact structure consists of a chemically<sup>10</sup> or photo-chemically<sup>11</sup> grown ultra-thin SiO<sub>x</sub> buffer layer capped with a phosphorus-doped amorphous silicon  $(a-Si:H(n))^{8, 12}$  layer deposited by plasma enhanced chemical vapour deposition (PECVD). After an hydrogenation step to passivate electronic defects, this contact structure yields an emitter saturation current density  $(J_0)$  of 7 fA cm<sup>-</sup>  $^{2}$  and a contact resistance of below 5 m $\Omega$  cm $^{2}$ . Analogous structures were used for hole-selective contacts using boron-doped amorphous silicon (a-Si:H(p)), resulting however in slightly lower performance compared to electron-selective contacts. Their lower performance is commonly explained by the high surface recombination velocity occurring at boron-diffused surfaces that are

passivated with  $SiO_x^{14}$  and additional defect-creation by boron diffusion through the  $SiO_x$  buffer layer. <sup>15</sup> For in-situ doped layers deposited by PECVD,  $J_0$  values of around 50 fA cm<sup>-2</sup> and implied open circuit voltages ( $iV_{oc}$ ) of 680 mV were obtained. <sup>16</sup> Using ion implantation techniques, slightly better results with  $J_0$  of 22 fA cm<sup>-2</sup> and  $iV_{oc}$  of 696 mV have been demonstrated. <sup>17-18</sup> Peibst et al. showed impressively low  $J_0$  values down to 8 fA cm<sup>-2</sup> with p-type poly-Si deposited by PECVD technique on thermally grown buffer oxide. <sup>19</sup> Also, Nemeth et al. reported an  $iV_{oc}$  of 700 mV with hole selective contact as high-low junction using a thermal SiO<sub>x</sub> as a thin buffer oxide. <sup>20</sup> Yan et al. demonstrated an approach to form p-type passivating contacts based on PECVD of undoped a-Si followed by thermal diffusion of boron from a BBr<sub>3</sub> and attained the  $J_0$  values of 16 fA cm<sup>-2</sup>. <sup>21</sup> An additional practical complication of hole-selective contacts is the blistering of the a-Si:H(p) layer, which poses severe processing restrictions to the deposition and thermal annealing processes. <sup>20</sup> 22 For lean process integration, single-side deposition and in-situ doping are desired. Also a passivating hole contact should ideally be co-annealed using the thermal process of phosphoryl chloride (POCl<sub>3</sub>) diffusion or the contact firing.

In this study, an alternative full area rear passivating contact fabricated by PECVD and thermal annealing is investigated with targeting a facile implementation to industrial p-type solar cells. The contact consists of a triple layer stack comprising a chemically grown  $SiO_x$ , an intrinsic silicon (Si(i)) inter-layer, and a boron-doped silicon-rich silicon-carbide  $(SiC_x(p))$  layer. The choice of  $SiC_x$  is motivated by several advantages: the material is more resilient to blistering than a-Si:H when deposited on chemical  $SiO_x$ , as C-H bonds are more stable than Si-H bonds with respect to hydrogen effusion.  $^{23-24}$  Moreover, as  $SiC_x$  is stable in standard wet chemical solutions used in Si solar cell fabrication, the rear contact can also serve as rear side protection through the entire cell process, providing large flexibility for the latter. The structural transformations of the passivating

contact during the annealing step is discussed along with the influence of the intrinsic Si inter-layer in between chemical  $SiO_x$  and  $SiC_x(p)$ . Finally, a proof-of-concept hybrid solar cell, which features a developed passivated back contact and an heterojunction front side contact made of intrinsic a-Si:H and phosphorus-doped a-Si:H(n), is presented.

## 2. Experimental

Passivating hole contacts were investigated using symmetrical structures based on either 280 µm thick double side polished 4-inch p-type float-zone <100> c-Si wafers with a resistivity of 2.8  $\Omega$ cm or 250  $\mu$ m thick chemically polished 4-inch p-type float-zone <100> c-Si wafers with a resistivity of 2 Ωcm. After standard wet chemical cleaning, an ~1 nm SiO<sub>x</sub> layer was formed by wet chemical oxidation using HNO<sub>3</sub> solution at 80°C<sup>10, 25</sup>, referred to as "chemical SiO<sub>x</sub>". Subsequently,  $SiC_x(p)$ —amorphous as deposited state— was deposited on both sides by PECVD operated at 40.86 MHz with silane (SiH<sub>4</sub>), hydrogen (H<sub>2</sub>), trimethylboron (TMB) and methane (CH<sub>4</sub>) as process gases. The typical substrate temperature and power density were kept constant at 200°C and 0.06 W cm<sup>-2</sup>, respectively, during the deposition. The samples were then annealed for 5 minutes in an inert gas atmosphere at a temperature of 800°C. This was followed by a hydrogenation step to passivate electronic defects at the c-Si wafer / chemical SiO<sub>x</sub> interface using SiN<sub>x</sub> as a hydrogen donor layer. The surface passivation properties were investigated by photo-conductance decay (PCD) technique, giving access to the effective minority-carrier lifetime as a function of the excess minority carrier density and the resulting implied open circuit voltage  $(iV_{oc})$  values. The method of Kane and Swanson<sup>26</sup> was applied to extract the emitter saturation current density  $(J_{\theta})$  at an excess carrier density of  $5\times10^{15}$  cm<sup>-3</sup>. The spatial homogeneity of the passivation was analyzed using photoluminescence imaging (PLI). The transfer length measurement (TLM) technique with linear contact pads array<sup>27</sup> was applied to extract the contact resistivity on *p*- type wafer. The structural changes occurring upon annealing at 800°C and 900°C were characterized using transmission electron microscopy (TEM) performed in either an FEI Titan Themis or an FEI Tecnai Osiris, both operated at 200 kV. In addition to the acquisition of high-resolution (HR)TEM micrographs, scanning TEM (STEM) images were recorded using a high-angle annular dark field (HAADF) detector and were combined with energy-dispersive X-ray spectroscopy (EDX) to obtain a chemical assessment of the layers of interest. For this purpose, TEM lamellae were prepared from samples after deposition and annealing at 800°C and 900°C, respectively, using the conventional focused ion beam (FIB) lift-out technique in a Zeiss Nvision 40 workstation. The crystallinity of the contact layers after annealing was analyzed by grazing incidence X-ray diffraction spectroscopy (GI-XRD) using a Bruker D8 Discover Tool with the Cu-Kα (λ=1.542 Å) radiation source at a fixed incidence angle of 0.3°.

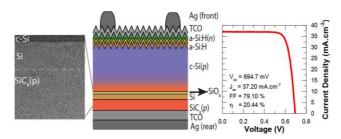

Figure 1. Process flow and final device structure. The  $p^+$  region at the rear side of the c-Si(p) wafer created by in-diffusion of boron from the a-SiC<sub>x</sub>(p) layer and the structural change of the deposited layers upon annealing at high temperatures ( $\geq 800^{\circ}$ C) are indicated in the sketch by change in the colors.

After the analysis of the symmetric lifetime samples, they were further processed to realize as solar cells. The rear side of the wafer was protected, while the layer stack on the front side was etched and textured in potassium hydroxide solution. After removal of the rear protection layer, the wafers

were cleaned in standard wet chemistry and finally dipped in 5% diluted HF to remove the native oxide. Subsequently, a 7 nm intrinsic a-Si:H passivation layer and a 6 nm phosphorus-doped a-Si:H(n) electron collection layer were prepared by PECVD on the front side. To extract the collected carriers efficiently and to increase the light in-coupling into the wafer, 70 nm and 200 nm indium tin oxide (ITO) were sputtered onto the front and rear sides of the cells, respectively. The active cell area was defined by depositing the ITO layers through a 2.2 cm  $\times$  2.2 cm shadow mask. A silver reflector / contact was sputtered onto the rear side and silver paste was screen-printed to realize the front metallization grid, followed by curing for 25 minutes at 190°C in a belt furnace. The process flow and final device structure are depicted in Figure 1. Current-voltage (I-V) characteristics of the cells were measured at 25°C with a source-meter (Keithley, 2601A), using an AAA solar simulator (Wacom) calibrated to 100 mW cm<sup>-2</sup> with a c-Si reference cell. Furthermore, the cells were measured by suns- $V_{oc}$  to obtain the series-resistancefree pseudo I–V curves. The external quantum efficiency (EQE) and reflectance (R) were measured using the Loana (pv-tools) tool and the internal quantum efficiency (IQE) calculated according to IQE = EQE / (1-R).

### 3. Results and discussion

### 3.1 . Structural Properties

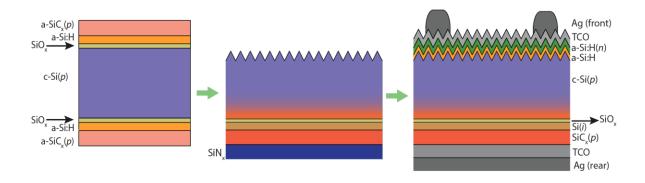

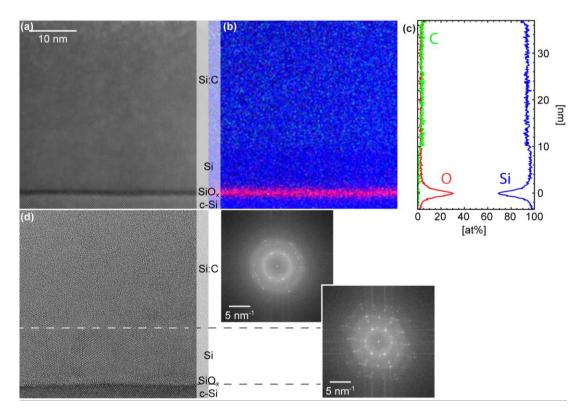

The structure of the hole selective contact and its evolution during thermal annealing was investigated by TEM. STEM HAADF images together with corresponding EDX maps and line scans are shown in Figure 2 for the contact structure in *as deposited* state and after annealing for 5 minutes at 800°C and 900°C. The EDX data confirms that the thin dark line observed at the c-Si wafer interface in the STEM HAADF images shown in Figure 2(a)-(b) corresponds to the chemical

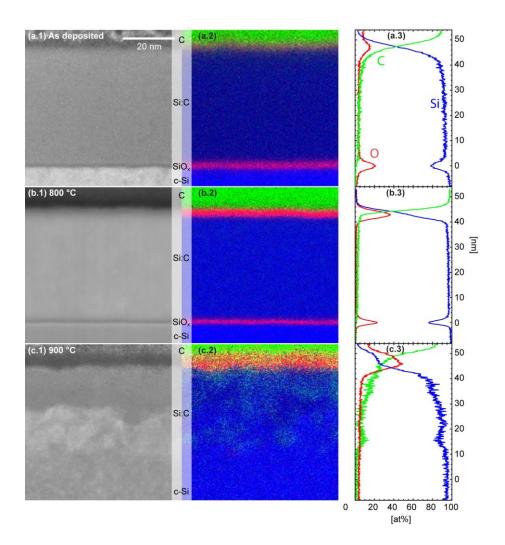

SiO<sub>x</sub>. In the *as deposited* state, depicted in Figure 2(a), a clearly defined, sharp interface is observed between the c-Si wafer and the chemical SiO<sub>x</sub>. After annealing at 800°C, contact structure preserves the sharp interface [see Figure 2(b)]. After annealing at 900°C as shown in Figure 2(c), however, the chemical SiO<sub>x</sub> layer at the Si wafer interface is not present any more. C appears to be incorporated into the a recrystallized Si layer that presents epitaxial re-growth with the c-Si wafer [see Figure 3(a)]. The HRTEM micrograph and corresponding Fourier transform also highlight the presence of stacking faults along the (111) crystalographic planes (seen as streaks in the reciprocal space transform). These stacking faults are likely induced by thermal stressing<sup>28-29</sup> due to the presence of C in the Si lattice. In addition to c-Si reflections, a reflection at 4 nm<sup>-1</sup>, which corresponds to the (111) planes of cubic (beta-) SiC, is also measured in the Fourier transform [see Figure 3(a)].

Figure 2. STEM-HAADF micrographs (left), corresponding EDX maps (middle), and EDX line scans (right, quantified using the Cliff-Lorimer methods<sup>30</sup>) of the c-Si wafer /  $SiO_x$  / a- $SiC_x(p)$  contact structure. (a) As-deposited, and after thermal annealing for 5 minutes at (b) 800°C and (c) 900°C.

Furthermore, the crystallinity of the structures was investigated by GI-XRD technique. Figure 3(b) shows the diffraction patterns of the samples annealed at 800°C and 900°C. The peaks appearing at diffraction angles of 28.4°, 47.4°, 56.3° are attributed to the (111), (220) and (311) reflections of Si crystals. The expected reflections of cubic SiC at 35.4°, 60.0°, 71.8°, which correspond to the (111), (220) and (311) planes, respectively, are also indicated in Figure 3(b). The full-width-half-maxima of the Si-related peaks (excluding the (111) peak arises mainly from the wafer) are narrower for the sample annealed at 900°C, which is the signature of a larger mean

crystallite size. 31 Additionally, after annealing at 900°C a peak at 35.4°, which corresponds to the (111) reflection from cubic SiC, becomes visible, confirming SiC crystallization observed by TEM [c.f. Figure 3(a)]. The results are in agreement with previous studies, which also reported a degraded surface passivation after annealing at temperatures above 875°C due to a local break-up of the SiO<sub>x</sub> buffer layer with epitaxial re-growth of the deposited Si layer.<sup>32</sup> However, to the best of our knowledge, there is no report showing the complete disappearance of the SiO<sub>x</sub> layer. Chemical bonding in a-SiC<sub>x</sub> layers prepared by PECVD technique strongly depends on the deposition parameters and related plasma regime.<sup>23, 33</sup> Especially in the low power regime identified by Solomon et al., 34 the decomposition probability of CH<sub>4</sub> is much lower than that of SiH<sub>4</sub><sup>35-36</sup> and CH<sub>4</sub> is dissociated only by the reaction of the CH<sub>4</sub> molecules with the species created by the decomposed SiH<sub>4</sub>. Since there is no primary decomposition of CH<sub>4</sub>, carbon (C) atoms are incorporated in the layer mostly as CH3 groups. As these establish only one bond to the a-Si network, they are only poorly incorporated in the latter. Upon heating, hydrogen effuses from the amorphous network at temperatures far below 800°C, 33 leaving "dehydrogenated" C atoms that are only bond to one Si atom. Overall, it suggests that the SiO<sub>x</sub> layer reacts with the loosely bond C according to at least one of the reactions  $zC + xSiO_2 \rightarrow xSi + yCO$  or  $3C + SiO_2 \rightarrow$ SiC + 2CO, <sup>37</sup> and the oxygen effuses in gaseous form as CO or CO<sub>2</sub>. While the reported reaction temperatures are higher than the annealing temperature employed here, it should be noted that the C source is in immediate contact with the chemical SiO<sub>x</sub> layer and the total O quantity rather low. Upon thermal annealing of a-SiC<sub>x</sub> layers, SiC crystallites are usually observed as soon as Si crystallites are detected despite the higher crystallization energy of SiC. This effect is explained by the heterogeneous nucleation of SiC at the Si crystals lowering the activation energy for crystalline growth.<sup>38</sup> While O effuses as CO from the layer, the remaining C forms SiC, partially

grown as crystallites on or into the c-Si wafer surface epitaxially. The chemical  $SiO_x$  layer is still visible in the TEM images after annealing at 800°C. However as the chemical  $SiO_x$  layer vanishes after annealing at 900°C for 5 minutes, we speculate that also after annealing at 800°C for 5 minutes, the chemical  $SiO_x$  layer has likely already been weakened by reaction with C since the symmetrical lifetime sample employing this contact structure attains only an  $iV_{oc}$  of 685 mV.

Figure 3. (a) HRTEM image of the sample annealed at 900°C together with Fourier transforms computed from the recrystallized  $SiC_x$  region containing stacking faults (top right) and at the position of the c-Si wafer (bottom right) (b) GI-XRD diffractograms after annealing at 800°C and 900°C. The dashed lines indicate the positions of the Si (111), (220) and (311) reflections at 28.4°, 47.4° and 56.3° and of the cubic SiC (111), (220) and (311) reflections at diffraction angles of 35.4°, 60.0°, 71.8°.

As structural defects act as recombination centers, an untainted interface between the chemical  $SiO_x$  and c-Si wafer is indispensable for good surface passivation. To mitigate the mentioned

chemical reaction of the chemical SiO<sub>x</sub> with the C from the deposited SiC<sub>x</sub>(p) layer, we introduce an additional intrinsic Si inter-layer in between the chemical SiO<sub>x</sub> and the a-SiC<sub>x</sub>(p) layer during the deposition. Figure 4 shows the  $iV_{oc}$  and  $J_{\theta}$  values for the contact structures that have different inter-layer thicknesses after annealing at 800°C with a dwell time of 5 minutes. It is observed that the intrinsic Si inter-layer boosts the  $iV_{oc}$  from 685 mV up to 708 mV and lowers the  $J_{\theta}$  down to 17 fA cm<sup>-2</sup> for the sample with a 10 nm thick inter-layer. Based on the diffusivity of C in Si,<sup>39</sup> we assume that for very thin intrinsic Si inter-layer, C atoms can still reach the chemical SiO<sub>x</sub>, which might explain the lower performance of the samples with 2-nm and 4-nm-thick intrinsic Si inter-layer. As the intrinsic Si inter-layer thickness increases further from 10 nm to 15 nm, the  $iV_{oc}$  shows a drastic decay to 670 mV. We tentatively explain this with a reduced dopant diffusion from the SiC<sub>x</sub>(p) layer to the c-Si wafer, which weakens the field effect passivation. Corresponding  $J_{\theta}$  values show an agreement with the  $iV_{oc}$  values and decrease with increasing intrinsic Si inter-layer thickness.

Figure 4. The impact of the intrinsic Si inter-layer thicknesses on implied open circuit voltage ( $iV_{oc}$ ) and emitter saturation current density ( $J_{\theta}$ ) of the contact structure after annealing at 800°C for 5 minutes and subsequently hydrogenating with SiN<sub>x</sub>.

The microstructure of a sample with 10 nm-thick intrinsic Si inter-layer after annealing at  $800^{\circ}$ C is shown in Figure 5. The HAADF image shows a sharp and well preserved c-Si / chemical SiO<sub>x</sub> interface, and the SiO<sub>x</sub> layer is clearly resolved in the EDX map as well. The EDX map further shows that C concentration in the top most layer is  $4.8 \pm 1\%$ , while the C content in the intrinsic Si inter-layer is below the detection limit. According to the Fourier transform computed from the HRTEM micrograph [see Figure 5(d)], the intrinsic Si buffer layer is highly crystalline after the annealing process. Based on these findings, we speculate that the presence of the intrinsic Si inter-layer hinders the reaction of the chemical SiO<sub>x</sub> with C from the SiC<sub>x</sub>(p) layer and thus enables an untainted interface between the chemical SiO<sub>x</sub> and the c-Si wafer with excellent surface passivation as shown in Figure 4.

Figure 5. TEM characterization of the c-Si wafer/chemical  $SiO_x/$  intrinsic Si buffer /  $SiC_x(p)$  contact structure after annealing at 800°C for 5 minutes. (a) STEM HAADF image, (b) EDX map together with (c) EDX line scan and (d) HRTEM micrograph along with Fourier transforms computed at the position of both the buffer layer (bottom) and the a-SiC<sub>x</sub>(p) (top).

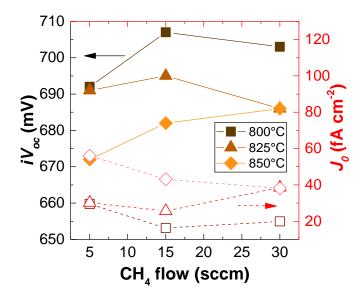

In order to optimize the contact structure further, the optimum inter-layer thickness of 10 nm was selected. The effect of the CH<sub>4</sub> gas flow during the deposition of the a-SiC<sub>x</sub>(p) layer was investigated, while keeping all other process gases constant. The dependence of the  $iV_{oc}$  and  $J_0$  on CH<sub>4</sub> flow is shown in Figure 6 for samples annealed for 5 minutes at temperatures of 800°C, 825°C and 850°C. For all investigated CH<sub>4</sub> flows, the best annealing temperature is 800°C.  $J_{\theta}$  is decreasing with increasing CH<sub>4</sub> flow for the samples annealed at 850°C, but is worse than all other investigated conditions. In general, the passivation deteriorates with annealing temperatures higher than 800°C due to either more pronounced diffusion of the boron that increases the Auger recombination and the defect states at the chemical SiO<sub>x</sub> / wafer interface, the reaction of C with the chemical SiO<sub>x</sub> or the combination of both effects. Even though the intrinsic Si inter-layer is introduced to protect the chemical SiO<sub>x</sub> interface, at high temperatures C may still diffuse through the intrinsic layer and reach the chemical SiO<sub>x</sub>. For the latter, among the samples annealed at 800°C and 825°C, the best results were achieved with a CH<sub>4</sub> flow of 15 sccm. These excellent results demonstrate that boron-doped SiC<sub>x</sub> is a promising material to realize hole-selective contacts in combination with an interfacial chemical SiO<sub>x</sub> and an additional intrinsic Si inter-layer.

Figure 6. Measured implied open circuit voltage ( $iV_{oc}$ ) and emitter saturation current density ( $J_0$ ) of the contact structure annealed at different temperatures and subsequently hydrogenated with SiN<sub>x</sub>, as a function of the CH<sub>4</sub> flow. Filled symbols represent the  $iV_{oc}$  and open symbols represent the  $J_0$ .

# 3.2 Cell Results

To investigate the potential of the chemical  $SiO_x/Si(i)/SiC_x(p)$  contact stack at the device level, the best symmetrical lifetime samples were processed to form solar cells. In addition, we varied the dopant—TMB—flow in order to explore eventually more favorable conditions, considering that the high doping level of the layer might increase surface recombination and therefore increase  $J_0$ . One side of the symmetrical lifetime sample was etched back, textured, and finished with a standard heterojunction front side as described in detail above.

Table 1.  $iV_{oc}$  and  $J_0$  values of the Cell A and Cell B after a-Si:H(i/n) deposition and completed hybrid cell parameters.

|        | a-SiC <sub>x</sub> $(p)$ | After − <i>i</i> / <i>n</i> |                        | Cell Parameters        |      |          |      |           |      |

|--------|--------------------------|-----------------------------|------------------------|------------------------|------|----------|------|-----------|------|

| Sample | TMB flow                 | $iV_{oc}$                   | $J_o$                  | $J_{sc}$               | FF   | $V_{oc}$ | η    | $pV_{oc}$ | pFF  |

|        | [sccm]                   | [mV]                        | [fA cm <sup>-2</sup> ] | [mA cm <sup>-2</sup> ] | [%]  | [mV]     | [%]  | [mV]      | [%]  |

| Cell A | 1.9                      | 713                         | 12.8                   | 36.95                  | 77.2 | 678.0    | 19.4 | 684       | 80.1 |

| Cell B | 1.5                      | 717                         | 12.3                   | 37.20                  | 79.1 | 694.7    | 20.4 | 699       | 82.2 |

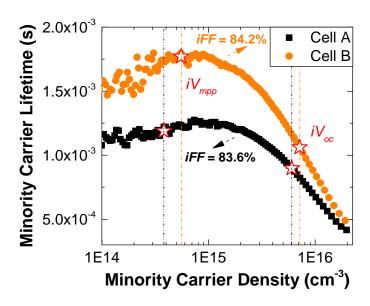

Figure 7. Effective carrier lifetimes of the samples after a-Si:H(i/n) front side PECVD deposition as a function of the excess carrier density together with associate implied voltages at maximum power point and in open circuit conditions.

The  $iV_{oc}$  and  $J_0$  values after deposition of the a-Si:H(i/n) layer stack, I-V parameters of the completed cells as well as the  $pV_{oc}$  and pFF values at one-sun, are given in Table 1 for the best cells out of three on each wafer. The characteristic form of the lifetime curves reveal a direct information about the nature of the sample's surface passivation—chemical or field-effect—. The low injection level where the minority carrier density is lower than  $10^{15}$  cm<sup>-3</sup>, is mostly known to be associated with field-effect passivation. In Figure 7, the injection dependence of the minority carrier lifetimes for the samples after deposition of the a-Si:H(i/n) front side together with associated implied FF (iFF) and implied voltages at maximum power point and open circuit conditions are shown. After deposition of the a-Si:H(i/n) stack on the front side, for both samples the low injection tailing which implies the weak field-effect passivation is observed. Even though the tailing is slightly more pronounced for the cell B prepared with 1.5 sccm TMB flow, the same sample shows better chemical passivation. Overall, both cells prepared with TMB flow of 1.9 sccm (cell A) and 1.5 sccm (cell B) yield an  $iV_{oc}$  of above 710 mV and a  $J_0$  of around 13 fA cm<sup>-2</sup>.

However, cell A —the cell with the more heavily doped a-SiC<sub>x</sub>(p) at the rear side— has slightly worse cell parameters. Although both samples were processed following the same fabrication steps, the texturization of the front sides might not be the same since they were processed at different time periods and the texturization was not optimized for this purpose. Additionally we measure a contact resistivity of 17 m $\Omega$  cm<sup>-2</sup> on the sample prepared with the TMB flow of 1.5 sccm on p-type wafer. However, since the front side of the cell employs a standard silicon heterojunction electron contact which has a contact resistivity of 200 m $\Omega$  cm<sup>-2</sup> on n-type,<sup>40</sup> the FF of the cell could be limited by the front side.

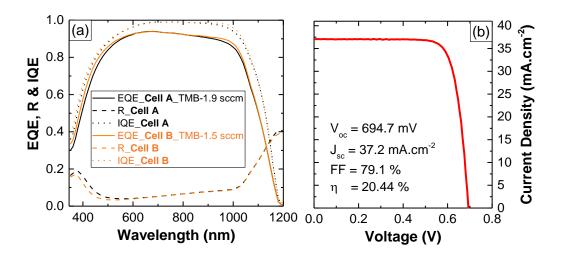

Figure 8(a) depicts the EQE, reflectance, and IQE spectra. Cell A exhibits a considerably higher reflectance in the blue part of the spectrum, which is the signature of a non-optimized front texturization. This results in a reduced  $J_{sc}$ , but most likely is also negatively effecting the  $V_{oc}$  and FF. It has to be noted also that the  $J_{sc}$  of 37 mA cm<sup>-2</sup> is a typical value for standard SHJ solar cells, and is limited by parasitic absorption in the a-Si:H layers on the front side. Figure 8(b) shows the I-V characteristics of the best cell obtained (cell B). In conclusion, the chemical SiO<sub>x</sub> / intrinsic Si inter-layer / SiC<sub>x</sub>(p) rear side structure allows excellent rear passivation, and has proven good cell performance with both doping conditions, enabling a  $V_{oc}$ =694.7 mV and a FF=79.1%. The developed rear contact thus demonstrates great potential to eliminate the patterning processes necessary for fabrication of PRC cells while boosting the  $V_{oc}$ .

Figure 8. (a) EQE, reflectance (R), and IQE spectra of both cells, (b) I-V characteristic of the best cell (cell B).

## 4. Conclusion

In conclusion, we have presented a thermally stable hole-selective rear contact for p-type c-Si solar cells prepared by PECVD with in-situ doping. The contact consists of a chemical SiO<sub>x</sub> / intrinsic Si inter-layer / SiC<sub>x</sub>(p) layer stack. Detailed structural analyses showed that the C-free intrinsic Si inter-layer is needed to obtain an optimized chemical SiO<sub>x</sub> / c-Si wafer interface and high quality high-low juntion after the thermal process. An optimum annealing temperature of 800°C was identified. By optimizing the carbon content in doped SiC<sub>x</sub> layer,  $iV_{oc}$  values of up to 708 mV and  $J_0$  values of 17 fA cm<sup>-2</sup> were demonstrated on symmetrical lifetime test structures. To show the potential of the passivating rear contact at device level, we presented a proof-of-concept solar cells with standard SHJ electron selective contact at the front side. The presented cells are limited by the front side reflection due to issues related to texturization and parasitic absorption in the SHJ electron contact employed on the front side. Despite these limitations, a  $V_{oc}$  of 694.7 mV, a FF of 79.1% and an efficiency of 20.44% demonstrate the potential of this SiC<sub>x</sub>(p) rear side scheme. We believe that the developed hole-selective contact would be an ideal replacement for partial rear

contact designs in industrial solar cells that employ a diffused POCl<sub>3</sub> front side. Indeed, such design eliminates the need for laser structuring of the passivation layer, which is currently necessary at the rear of PRC cells.

#### **AUTHOR INFORMATION**

Corresponding Author

\*E-mail gizem.nogay@epfl.ch. Phone +41 21 69 54308

### **ACKNOWLEDGMENT**

The authors would like to thank Dr. Derk Bätzner (Meyer Burger) for support. The authors gratefully acknowledge support by the Swiss National Science Foundation (SNF) under grant No. 200021\_14588/1 and No. IZLIZ2\_156641 and by the Swiss Federal Office for Energy (SFOE) under grant No. SI/501253-01. The Interdisciplinary Centre for Electron Microscopy of EPFL is acknowledged for FIB and TEM access.

### REFERENCES

- (1) Wolf, A.; Biro, D.; Nekarda, J.; Stumpp, S.; Kimmerle, A.; Mack, S.; Preu, R., Comprehensive Analytical Model for Locally Contacted Rear Surface Passivated Solar Cells. *J. Appl. Phys.* **2010**, *108* (12), 124510.

- (2) Cuevas, A., Physical Model of Back Line-Contact Front-Junction Solar Cells. *J. Appl. Phys.* **2013**, *113* (16), 164502.

- (3) Saomoto, S., World's Highest Conversion Efficiency of 26.33% Achieved in a Crystalline Silicon Solar Cell A World First in a Practical Cell Size –, Press Release from New Energy and Industrial Technology Development Organization Kaneka Corporation **2016**, http://www.nedo.go.jp/english/news/AA5en\_100109.html

- (4) Kwark, Y. H.; Sinton, R.; Swanson, R. M., SIPOS Heterojunction Contacts to Silicon, IEEE Int. Electron Devices Meet. **1984**, 30, 742-745.

- (5) Yablonovitch, E.; Gmitter, T.; Swanson, R.; Kwark, Y., A 720 mV Open Circuit Voltage SiOx: c-Si: SiOx Double Heterostructure Solar Cell. *Appl. Phys. Lett.* **1985**, *47* (11), 1211-1213.

- (6) Gan, J.-Y.; Swanson, R., Polysilicon Emitters for Silicon Concentrator Solar Cells, IEEE Photovoltaic Spec. Conf., 21st, **1990**, 21, 245-250.

- (7) Stuckelberger, J.; Nogay, G.; Wyss, P.; Jeangros, Q.; Allebé, C.; Debrot, F.; Niquille, X.; Ledinsky, M.; Fejfar, A.; Despeisse, M.; Haug, F-J.; Loper, P.; Ballif, C., Passivating Electron Contact Based on Highly Crystalline Nanostructured Silicon Oxide Layers for Silicon Solar Cells. *Sol. Energy Mater. and Sol. Cells* **2016**, 158, 2-10

- (8) Feldmann, F.; Bivour, M.; Reichel, C.; Hermle, M.; Glunz, S. W., Passivated Rear Contacts for High-Efficiency n-type Si Solar Cells Providing High Interface Passivation Quality and Excellent Transport Characteristics. *Sol. Energy Mater. and Sol. Cells* **2014**, *120*, 270-274.

- (9) Glunz, S.; Feldmann, F.; Richter, A.; Bivour, M.; Reichel, C.; Steinkemper, H.; Benick, J.; Hermle, M., The Irresistible Charm of a Simple Current Flow Pattern—25% with a Solar Cell Featuring a Full-Area Back Contact, European Photovoltaic Solar Energy Conference and Exhibition 31st, **2015**, 259-263, DOI: 10.4229/EUPVSEC20152015-2BP.1.1.

- (10) Kobayashi, T.; Maida, O.; Inoue, M.; Takahashi, M.; Todokoro, Y.; Kobayashi, H., Ultrathin Silicon Dioxide Layers with a Low Leakage Current Density Formed by Chemical Oxidation of Si. *Appl. Phys. Lett.* **2002**, *81* (18), 3410-3412.

- (11) Moldovan, A.; Feldmann, F.; Krugel, G.; Zimmer, M.; Rentsch, J.; Hermle, M.; Roth-Fölsch, A.; Kaufmann, K.; Hagendorf, C., Simple Cleaning and Conditioning of Silicon Surfaces with UV/Ozone Sources. *Energy Procedia* **2014**, *55*, 834-844.

- (12) Feldmann, F.; Bivour, M.; Reichel, C.; Steinkemper, H.; Herm, M.; Glunz, S. W., Tunnel Oxide Passivated Contacts as an Alternative to Partial Rear Contacts. *Sol. Energy Mater. and Sol. Cells* **2014**, *131*, 46-50.

- (13) Feldmann, F.; Bivour, M.; Reichel, C.; Moldovan, A.; Steinkemper, H.; Richter, A.; Benick, J.; Hermle, M.; Glunz, S., Advanced Passivated Contacts and Their Applications to High-Efficiency Cells, Workshop on Crystalline Silicon Solar Cells and Modules, Keystone, CO, **2015**.

- (14) Maritan, C. M.; Tarr, N. G., Polysilicon Emitter pnp Transistors. *IEEE Trans. Electron Devices* **1989**, *36* (6), 1139-1144.

- (15) Yamamoto, T.; Uwasawa, K. i.; Mogami, T., Bias Temperature Instability in Scaled p+ Polysilicon Gate p-MOSFET's. *IEEE Trans. on Electron Devices* **1999**, *46* (5), 921-926.

- (16) Feldmann, F.; Simon, M.; Bivour, M.; Reichel, C.; Hermle, M.; Glunz, S., Carrier-Selective Contacts for Si Solar Cells. *Appl. Phys. Lett.* **2014**, *104* (18), 181105.

- (17) Feldmann, F.; Reichel, C.; Müller, R.; Hermle, M., Si Solar Cells with Top/Rear Poly-Si Contacts, IEEE Photovoltaic Spec. Conf., 43rd, **2016**.

- (18) Reichel, C.; Feldmann, F.; Müller, R.; Reedy, R. C.; Lee, B. G.; Young, D. L.; Stradins, P.; Hermle, M.; Glunz, S. W., Tunnel Oxide Passivated Contacts Formed by Ion Implantation for Applications in Silicon Solar Cells. *J. Appl. Phys.* **2015**, *118* (20), 205701.

- (19) Peibst R., L. Y., Reiter S., Turcu M., Brendel R., Tetzlaff D., Krügener J., Wietler T., Höhne U., Kähler J.-D., Mehlich H., Frigge S., Implementation of n+ and p+ Poly Junctions on Front and Rear Side of Double-Side Contacted Industrial Silicon Solar Cells. European Photovoltaic Solar Energy Conference and Exhibition 32nd, **2016**, 323 327, DOI: 10.4229/EUPVSEC20162016-2BO.3.2

- (20) Nemeth, B.; Young, D. L.; Page, M. R.; LaSalvia, V.; Johnston, S.; Reedy, R.; Stradins, P., Polycrystalline Silicon Passivated Tunneling Contacts for High Efficiency Silicon Solar Cells. *J. Mater. Res.* **2016**, *31* (06), 671-681.

- (21) Yan, D.; Cuevas, A.; Wan, Y.; Bullock, J., Passivating Contacts for Silicon Solar Cells Based on Boron-Diffused Recrystallized Amorphous Silicon and Thin Dielectric Interlayers. *Sol. Energy Mater. and Sol. Cells* **2016**, *152*, 73-79.

- (22) Street, R. A., Hydrogenated amorphous silicon. Cambridge University Press: New York, 2005.

- (23) Bullot, J.; Schmidt, M., Physics of Amorphous Silicon–Carbon Alloys. Phys. Status Solidi B 1987, 143 (2), 345-418.

- (24) Boccard, M.; Holman, Z. C., Amorphous silicon carbide passivating layers for crystalline-silicon-based heterojunction solar cells. *J. Appl. Phys.* **2015**, 118 (6), 065704.

- (25) Asuha, H. K.; Maida, O.; Takahashi, M.; Iwasa, H., Nitric Acid Oxidation of Si to Form Ultrathin Silicon Dioxide Layers with a Low Leakage Current Density. *J. Appl. Phys.* **2003**, *94* (11), 7328-7335.

- (26) Kane, D.; Swanson, R. Measurement of the Emitter Saturation Current by a Contactless Photoconductivity Decay Method, IEEE photovoltaic specialists conference. 18, **1985**; pp 578-583.

- (27) Berger, H., Contact Resistance and Contact Resistivity. J. Electrochem. Soc. 1972, 119 (4), 507-514.

- (28) Liu, J.; Chung, H.; Kuhr, T.; Li, Q.; Skowronski, M., Structural Instability of 4H–SiC Polytype Induced by n-type Doping. *Appl. Phys. Lett.* **2002**, *80* (12), 2111-2113.

- (29) Brillson, L.; Tumakha, S.; Jessen, G.; Okojie, R.; Zhang, M.; Pirouz, P., Thermal and Doping Dependence of 4H-SiC Polytype Transformation. *Appl. Phys. Lett.* **2002**, *81* (15), 2785-2787.

- (30) Cliff, G.; Lorimer, G. W., The Quantitative Analysis of Thin Specimens. J. Microsc. 1975, 103 (2), 203-207.

- (31) Patterson, A., The Scherrer Formula for X-ray Particle Size Determination. *Phys.Rev.* **1939**, *56* (10), 978.

- (32) Wolstenholme, G.; Jorgensen, N.; Ashburn, P.; Booker, G., An Investigation of the Thermal Stability of the Interfacial Oxide in Polycrystalline Silicon Emitter Bipolar Transistors by Comparing Device Results with High-Resolution Electron Microscopy Observations. *J. Appl. Phys.* **1987**, *61* (1), 225-233.

- (33) Beyer, W.; Mell, H., Composition and Thermal Stability of Glow-Discharge a-Si: C: H and a-Si: N: H Alloys in Disordered Semiconductors, Springer: 1987, pp 641-658.

- (34) Solomon, I.; Schmidt, M.; Tran-Quoc, H., Selective Low-Power Plasma Decomposition of Silane-Methane Mixtures for the Preparation of Methylated Amorphous Silicon. *Phys. Rev. B* **1988**, *38* (14), 9895.

- (35) Schmitt, J., Fundamental Mechanisms in Silane Plasma Decompositions and Amorphous Silicon Deposition. *J. Non-Cryst. Solids* **1983**, *59*, 649-657.

- (36) Winters, H. F., Dissociation of Methane by Electron Impact. *The Journal of Chemical Physics* **1975**, *63* (8), 3462-3466.

- (37) Schröder, F., Si Silicon: System Si-C. SiC: Natural Occurrence. Preparation and Manufacturing Chemistry. Special Forms. Manufacture. Electrochemical Properties. Chemical Reactions. Applications. Ternary and Higher Systems with Si and C. Springer-Verlag Berlin Heidelberg, 1986, DOI: 10.1007/978-3-662-06994-3.

- (38) Summonte, C.; Allegrezza, M.; Bellettato, M.; Liscio, F.; Canino, M.; Desalvo, A.; López-Vidrier, J.; Hernández, S.; López-Conesa, L.; Estradé, S., Silicon Nanocrystals in Carbide Matrix. *Sol. Energy Mater. and Sol. Cells* **2014**, *128*, 138-149.

- (39) Goetzberger, A.; Voß, B.; Knobloch, J., Sonnenenergie: Photovoltaik: Physik und Technologie der Solarzelle. Teubner: Germany, 1997.

- (40) Nogay, G.; Seif, J. P.; Riesen, Y.; Tomasi, A.; Jeangros, Q.; Wyrsch, N.; Haug, F.-J.; De Wolf, S.; Ballif, C., Nanocrystalline Silicon Carrier Collectors for Silicon Heterojunction Solar Cells and Impact on Low-Temperature Device Characteristics. *IEEE J. Photovoltaics* **2016**, *6* (6), 1654 1662.

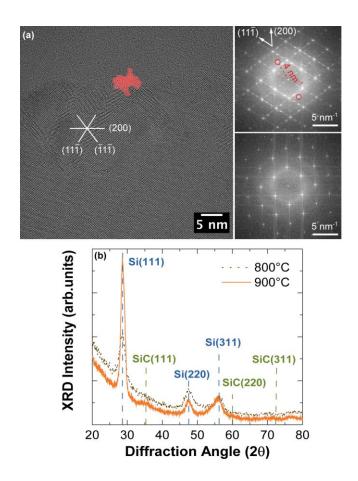

# Table Of Contents (TOC) graphic