# **Modelling Architecture Styles**

THÈSE Nº 7324 (2016)

PRÉSENTÉE LE 21 DÉCEMBRE 2016 À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS LABORATOIRE POUR LA CONCEPTION RIGOUREUSE DES SYSTÈMES PROGRAMME DOCTORAL EN INFORMATIQUE ET COMMUNICATIONS

## ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

# Anastasia MAVRIDOU

acceptée sur proposition du jury:

Prof. B. Faltings, président du jury Prof. J. Sifakis, Dr S. Bliudze, directeurs de thèse Prof. J. Sztipanovits, rapporteur Prof. B. Rumpe, rapporteur Prof. R. Guerraoui, rapporteur

Σα βγεις στον πηγαιμό για την Ιθάκη, να εύχεσαι νάναι μακρύς ο δρόμος, γεμάτος περιπέτειες, γεμάτος γνώσεις. Κ. Π. Καβάφης

Στους παππούδες μου Αναστασία & Ιωάννη, στους γονείς μου Ισαβέλλα & Ιωάννη, & σε όλους τους δασκάλους μου.

To my grandparents Anastasia & Ioanni, to my parents Isavella & Ioanni, & to all my teachers.

# Acknowledgements

I had the fortune, the honour and the absolute privilege to be advised by Prof. Joseph Sifakis and Dr. Simon Bliudze. Prof. Sifakis gave me the opportunity to explore very interesting research problems, while teaching me the beauty of theoretical rigour. Working with Prof. Sifakis has been a unique experience; I truly admire his passion and energy, as well as the enthusiasm with which he disseminates his knowledge. Dr. Bliudze always kept an open door, was happy to help with any kind of issue and patiently answer my numerous questions. I thank him for the insightful scientific discussions, which I greatly enjoyed. Ultimately, a few sentences would show nothing about how indebted I feel towards both Prof. Sifakis and Dr. Bliudze. The support and guidance I received was unbounded and highly motivational. I sincerely hope that my future work would partly meet their efforts.

I am grateful to Prof. Boi Faltings, Prof. Rachid Guerraoui, Prof. Bernhard Rumpe and Prof. Janos Sztipanovits for honouring me by accepting to serve on my thesis committee. I thank them for taking the time to read my thesis and for their invaluable comments on my work and its perspectives. I would like to additionally thank Prof. Sztipanovits for being my mentor during a summer internship at Vanderbilt University, which helped me to significantly increase my knowledge on model-based software engineering.

Special thanks go to Stefanos Skalistis, Goran Radanovic, Manos Karpathiotakis and Aron Laszka for proofreading my thesis. They helped me improve the flow and presentation of the thesis by finding several places in which further clarifications were needed.

I want to thank all my colleagues with whom I co-authored a paper: Emmanouela Stachtiari, Prof. Panagiotis Katsaros, Dr. Anton Ivanov and Alina Zolotukhina. Special thanks go to Dr. Radoslaw Szymanek for his invaluable guidance on the implementation parts of this thesis. Special thanks also go to Eduard Baranov with whom I had the pleasure to extensively interact, constructively argue and co-author several papers. I also thank my colleagues Alena Simalatsar, Wang Qiang, Wajeb Saab, Alexandre Sikiaridis and Vladimir Ilievski for creating a pleasant and motivating working environment. I thank Mrs. Arianne Staudenmann for her continuous help on administrative tasks while always having a smile on her face.

I would also like to express my gratitude to my dear friends for their continuous support and for making my life happier. Thank you Alex, Christos, Eleni, Eralia, Evi, Giannis, Iliana, Katerina, Kiki, Loukia, Manos, Matt, Pavlos, Stefanos, Theano and Zoi.

#### Acknowledgements

Last but not least, I thank my parents, Isavella and Ioannis, and my sister, Ifigeneia for their unconditional love throughout the years. They were there for me, even when we were physically apart.

Lausanne, 14 December 2016

A. M.

# Abstract

Software systems tend to increase over time in size and complexity. Their development usually spans a long period of time and may result in systems that are hard to understand, debug and maintain. *Architectures* are common means for organising coordination between components in order to build complex systems and make them manageable. They allow thinking on a higher plane and avoiding low-level mistakes. Grouping architectures that share common characteristics into *architecture styles* assists component re-use and thus, the cost-effective development of systems. Architecture styles provide means for ensuring correctness-by-construction by enforcing global properties. The main goal of this thesis is to propose and study formalisms for modelling architectures and architecture styles.

For the specification of architectures, we study *interaction logics*, which are Boolean algebras on a set of component actions. We study a modelling methodology based on first-order interaction logic for writing architecture constraints. To validate the applicability of the approach, we developed the JavaBIP framework that integrates architectures into mainstream software development. JavaBIP receives as input architecture specifications, which it then uses to coordinate software components without requiring access to their source code. JavaBIP implements the principles of the BIP component framework.

For the specification of architecture styles, we propose *configuration logics*, which are powerset extensions of interaction logic. Propositional configuration logic formulas are generated from formulas of interaction logic by using the operators union, intersection and complementation, as well as a coalescing operator. We provide a complete axiomatisation of the propositional configuration logic and a decision procedure for checking that an architecture satisfies given logical specifications. To allow genericity of specifications, we study higher-order extensions of the propositional configuration logic. We provide several examples illustrating the application of configuration logics to the characterisation of architecture styles.

For the specification of architecture styles, we also propose *architecture diagrams*, which is a graphical language rooted in rigorous semantics. We provide methods to assist software developers to specify consistent architecture diagrams, generate the conforming architectures of a style and check whether an architecture model meets given style requirements. We present a full encoding of architecture diagrams into configuration logics. Finally, we report on applications of architecture diagrams to modelling architecture styles identified in realistic case studies of on-board satellite software.

#### Acknowledgements

**Keywords**: architecture styles, architectures, interaction logics, configuration logics, architecture diagrams, architecture-based design, BIP, JavaBIP, component coordination.

# Résumé

Les logiciels informatiques ont tendance à augmenter au fil du temps en taille et en complexité. Leur développement couvre généralement une longue période de temps et se traduit souvent par des systèmes qui sont difficiles à comprendre, réparer et maintenir. Les architectures sont un moyen répandu pour organiser la coordination de composants afin de construire des systèmes complexes et simplifier leur gestion. Ils permettent de penser à un niveau d'abstraction supérieur et éviter les erreurs de bas niveau. Regrouper des architectures partageant des caractéristiques communes en des styles d'architecture aide à la réutilisation des composants et ainsi, au développement rentable de systèmes. En outre, les styles d'architecture offrent des moyens pour assurer l'exactitude par construction de systèmes, par l'application de propriétés globales. Le principal objectif de cette thèse est de proposer et étudier des formalismes pour modéliser des architectures et des styles d'architecture.

Pour la spécification d'architectures, nous étudions des logiques d'interaction, c'est-à-dire l'application d'algèbre booléenne sur des ensembles d'actions de composants. Nous étudions une méthodologie de modélisation basée sur la logique d'interaction de premier ordre pour l'écriture des contraintes d'architecture. Pour valider cette approche, nous avons développé le cadre JavaBIP, qui intègre les architectures dans le développement de logiciels grand public. JavaBIP reçoit comme entrée les spécifications d'architectures, qui sont ensuite utilisées pour coordonner les composants logiciels sans nécessiter l'accès à leur code source. JavaBIP met ainsi en œuvre les principes du cadre de programmation de composants BIP.

Pour la spécification des styles d'architecture, nous proposons des logiques de configuration, qui sont des extensions en ensemble des parties d'un ensemble (powerset en anglais) de la logique d'interaction. Les formules logiques de configuration propositionnelles sont générées à partir des formules logiques d'interaction à l'aide des opérateurs d'union, d'intersection et de complémentation, ainsi qu'un opérateur coalescent. Nous fournissons une axiomatisation complète de la logique de configuration propositionnelle et une procédure de décision pour vérifier qu'une architecture satisfait les spécifications logiques données. Pour permettre la généricité des spécifications, nous étudions les extensions d'ordre supérieur de la logique de configuration propositionnelle. Nous proposons plusieurs exemples illustrant l'application de la logique de configuration à la caractérisation des styles d'architecture.

Pour la spécification des styles d'architecture, nous proposons également des diagrammes d'architecture, c'est-à-dire un langage graphique basé sur une sémantique rigoureuse. Nous fournissons des méthodes pour aider les développeurs de logiciels à spécifier des diagrammes

#### Résumé

d'architecture cohérents, à générer des architectures conformes à un style, et à vérifier qu'un modèle d'architecture réponde aux exigences d'un style donné. Nous présentons un encodage complet des diagrammes d'architecture dans les logiques de configuration. Enfin, nous présentons des applications de diagrammes d'architecture à des styles d'architecture de modélisation, identifiées dans des études de cas réalistes de logiciel embarqué pour un satellite.

**Mots clefs** : styles d'architecture, architectures, logiques d'interaction, logiques de configuration, diagrammes d'architecture, design basé sur une architecture, BIP, JavaBIP, coordination de composants.

# Contents

| A             | Acknowledgements i |         |                                                                                                                    |   |

|---------------|--------------------|---------|--------------------------------------------------------------------------------------------------------------------|---|

| A             | bstra              | ict (En | glish/Français) iii                                                                                                | i |

| $\mathbf{Li}$ | st of              | figure  | s xi                                                                                                               | i |

| $\mathbf{Li}$ | st of              | tables  | xv                                                                                                                 | r |

| 1             | Intr               | oducti  | ion 1                                                                                                              | L |

|               | 1.1                | Archit  | ectures in BIP                                                                                                     | 3 |

|               | 1.2                | Archit  | ecture styles                                                                                                      | 1 |

|               | 1.3                | Our co  | ontributions                                                                                                       | 5 |

|               |                    | 1.3.1   | Modelling and implementation of architectures                                                                      | 5 |

|               |                    | 1.3.2   | Modelling architecture styles                                                                                      | 7 |

|               | 1.4                | Thesis  |                                                                                                                    | ) |

| <b>2</b>      | $\mathbf{Pre}$     | limina  | ries 11                                                                                                            | L |

|               | 2.1                | BIP co  | pmponent framework                                                                                                 | L |

|               | 2.2                | Basic   | semantic model of BIP                                                                                              | 2 |

|               | 2.3                | Repres  | sentations of the BIP interaction model 15                                                                         | í |

|               |                    | 2.3.1   | Algebra of interactions                                                                                            | í |

|               |                    | 2.3.2   | Algebra of connectors 16                                                                                           | ; |

|               |                    | 2.3.3   | Propositional interaction logic                                                                                    | 7 |

|               | 2.4                | Archit  | ectures in BIP                                                                                                     | ) |

| 3             | Inte               | eractio | n logic and JavaBIP 21                                                                                             | L |

|               | 3.1                | JavaB   | IP design workflow                                                                                                 | 2 |

|               | 3.2                | JavaB   | IP by example: Camel routes                                                                                        | } |

|               | 3.3                | Theore  | etical foundations $\ldots \ldots 27$ | 7 |

|               |                    | 3.3.1   | Component model without data                                                                                       | 7 |

|               |                    | 3.3.2   | Extension of the model with data                                                                                   | ) |

|               |                    | 3.3.3   | First-order interaction logic                                                                                      | 2 |

|               |                    | 3.3.4   | Macro notation based on component types                                                                            | 3 |

|               | 3.4                | System  | n specification $\ldots \ldots 38$    | 3 |

|               |                    | 3.4.1   | Behaviour specification                                                                                            | 3 |

|          |                                                                             | 3.4.2                                                                                                                                                                                                 | Architecture specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                                                                             |                                                                                                                                                                                                       | Data-wire specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

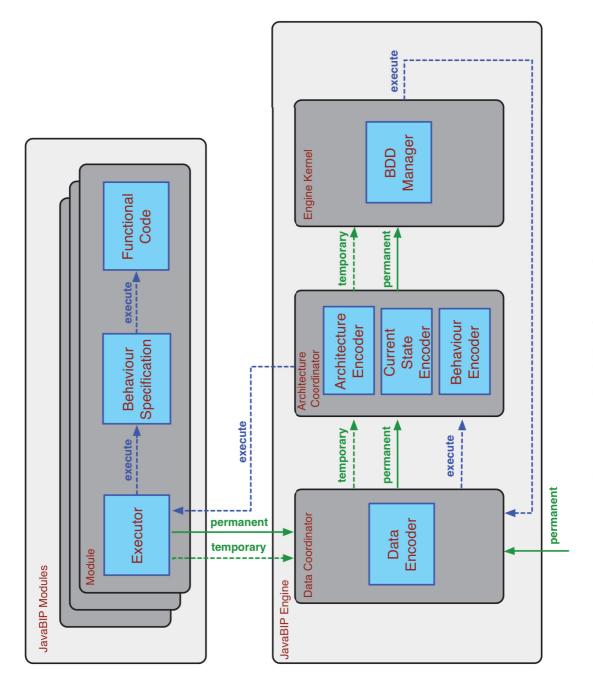

|          | 3.5                                                                         | -                                                                                                                                                                                                     | entation of the JavaBIP engine $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 43$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          |                                                                             |                                                                                                                                                                                                       | Engine kernel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |                                                                             |                                                                                                                                                                                                       | Coordinators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

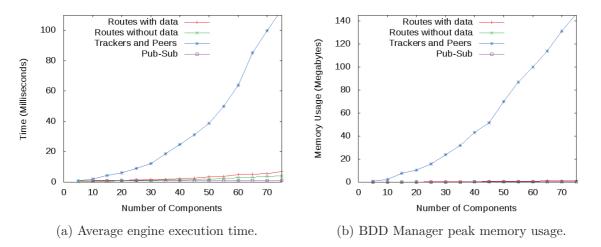

|          |                                                                             |                                                                                                                                                                                                       | Experimental evaluation $\ldots \ldots 45$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          | 3.6                                                                         | Related                                                                                                                                                                                               | work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          | 3.7                                                                         | Summa                                                                                                                                                                                                 | ry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <b>4</b> | Con                                                                         | 0                                                                                                                                                                                                     | on logics 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

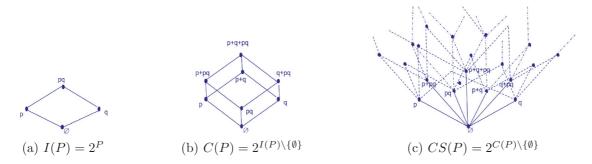

|          | 4.1                                                                         | -                                                                                                                                                                                                     | tional configuration logic (PCL) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 52$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

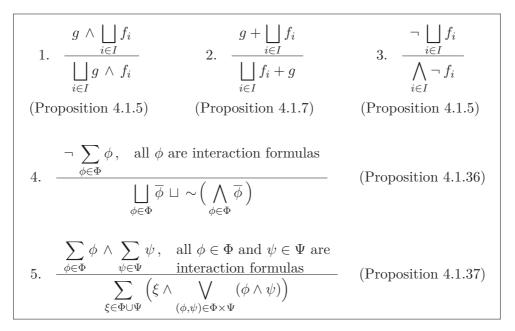

|          |                                                                             | 4.1.1                                                                                                                                                                                                 | Properties of PCL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|          |                                                                             | 4.1.2                                                                                                                                                                                                 | Normal form and axiomatisation of PCL formulas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |                                                                             | 4.1.3                                                                                                                                                                                                 | Soundness and completeness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|          |                                                                             | 4.1.4                                                                                                                                                                                                 | Checking satisfaction of PCL formulas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          | 4.2                                                                         | First an                                                                                                                                                                                              | d second order extensions of PCL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          |                                                                             | 4.2.1                                                                                                                                                                                                 | First-order configuration logic $\ldots \ldots 74$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|          |                                                                             | 4.2.2                                                                                                                                                                                                 | First-order configuration logic with ordered components $\ldots \ldots \ldots 80$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|          |                                                                             | 4.2.3                                                                                                                                                                                                 | Second-order configuration logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          | 4.3                                                                         | Related                                                                                                                                                                                               | work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          | 4.4                                                                         | Summa                                                                                                                                                                                                 | ry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          |                                                                             |                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5        | Arc                                                                         | hitectur                                                                                                                                                                                              | e diagrams 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

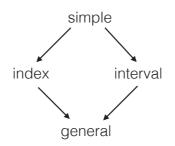

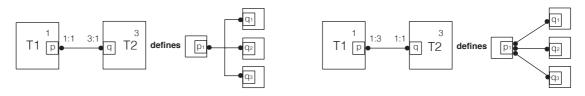

| 5        | <b>Arc</b><br>5.1                                                           |                                                                                                                                                                                                       | e diagrams 89<br>architecture diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5        |                                                                             | Simple                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5        |                                                                             | Simple 5.1.1                                                                                                                                                                                          | architecture diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5        |                                                                             | Simple 5.1.1 5.1.2                                                                                                                                                                                    | architecture diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

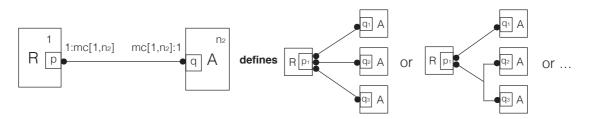

| 5        |                                                                             | Simple :<br>5.1.1 5<br>5.1.2 5<br>5.1.3 5                                                                                                                                                             | architecture diagrams91Syntax and semantics91Consistency conditions93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5        |                                                                             | Simple 3<br>5.1.1 5<br>5.1.2 6<br>5.1.3 5<br>5.1.4 4                                                                                                                                                  | architecture diagrams91Syntax and semantics91Consistency conditions93Synthesis of configurations94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

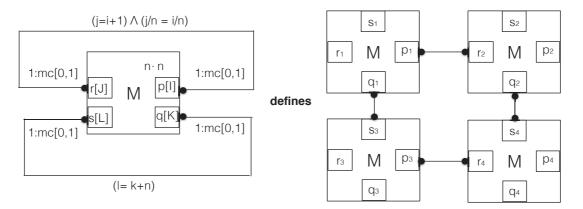

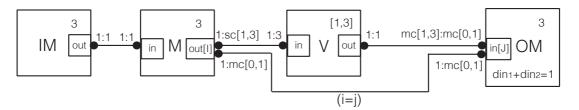

| 5        | 5.1                                                                         | Simple :<br>5.1.1 5<br>5.1.2 6<br>5.1.3 5<br>5.1.4 1<br>Interval                                                                                                                                      | architecture diagrams91Syntax and semantics91Consistency conditions93Synthesis of configurations94Architecture style specification examples98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

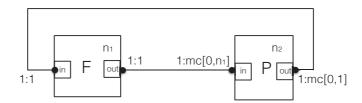

| 5        | 5.1                                                                         | Simple 3<br>5.1.1 5<br>5.1.2 6<br>5.1.3 5<br>5.1.4 4<br>Interval<br>5.2.1 5                                                                                                                           | architecture diagrams91Syntax and semantics91Consistency conditions93Synthesis of configurations94Architecture style specification examples98architecture diagrams98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5        | 5.1                                                                         | Simple 3<br>5.1.1 5<br>5.1.2 5<br>5.1.3 5<br>5.1.4 1<br>Interval<br>5.2.1 5<br>5.2.2 6                                                                                                                | architecture diagrams91Syntax and semantics91Consistency conditions93Synthesis of configurations94Architecture style specification examples98architecture diagrams98Syntax and semantics99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5        | 5.1                                                                         | Simple 3<br>5.1.1 5<br>5.1.2 5<br>5.1.3 5<br>5.1.4 5<br>5.2.1 5<br>5.2.2 5<br>5.2.3 5                                                                                                                 | architecture diagrams91Syntax and semantics91Consistency conditions93Synthesis of configurations94Architecture style specification examples98architecture diagrams98Syntax and semantics99Consistency conditions91Consistency conditions91Syntax and semantics92Consistency conditions91Consistency conditions91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5        | 5.1                                                                         | Simple 3<br>5.1.1 5<br>5.1.2 5<br>5.1.3 5<br>5.1.4 5<br>5.2.1 5<br>5.2.2 5<br>5.2.3 5<br>5.2.4 5                                                                                                      | architecture diagrams91Syntax and semantics91Consistency conditions93Synthesis of configurations94Architecture style specification examples98architecture diagrams98Syntax and semantics99Consistency conditions91Syntax and semantics91Syntax and semantics91Consistency conditions91Synthesis of configurations91Synthesis of configurations91Synthesis of configurations91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5        | 5.1<br>5.2                                                                  | Simple 3<br>5.1.1 5<br>5.1.2 5<br>5.1.3 5<br>5.1.4 5<br>5.2.1 5<br>5.2.2 5<br>5.2.3 5<br>5.2.4 5<br>5.2.4 5<br>5.2.4 5                                                                                | architecture diagrams91Syntax and semantics91Consistency conditions93Synthesis of configurations94Architecture style specification examples98architecture diagrams98Syntax and semantics99Consistency conditions99Consistency conditions101Syntax and semantics101Synthesis of configurations104Architecture style specification examples105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

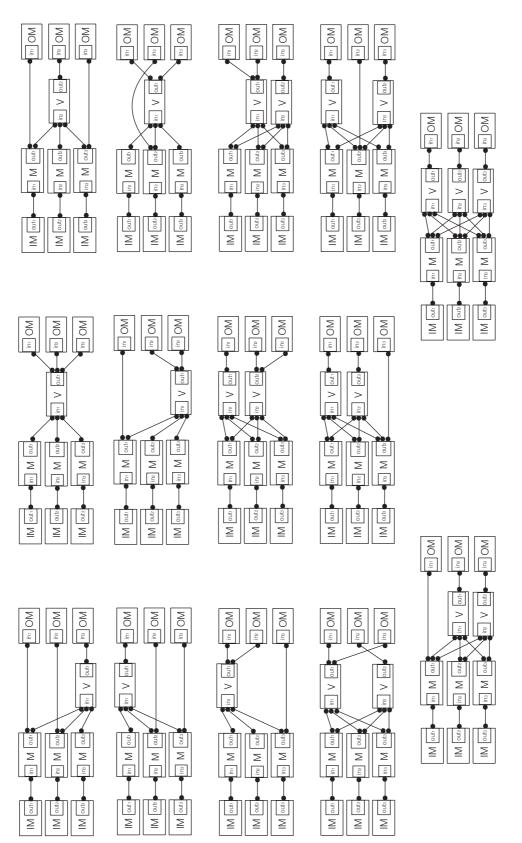

| 5        | 5.1<br>5.2                                                                  | Simple 3<br>5.1.1 3<br>5.1.2 4<br>5.1.3 5<br>5.1.4 4<br>Interval<br>5.2.1 5<br>5.2.2 4<br>5.2.3 5<br>5.2.4 4<br>Index at<br>5.3.1 5                                                                   | architecture diagrams91Syntax and semantics91Consistency conditions93Synthesis of configurations94Architecture style specification examples98architecture diagrams98Syntax and semantics99Consistency conditions101Synthesis of configurations104Architecture style specification examples105consistency conditions105consistency conditions108consistency conditions105consistency style specification examples108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5        | 5.1<br>5.2                                                                  | Simple 3<br>5.1.1 5<br>5.1.2 5<br>5.1.3 5<br>5.1.4 5<br>5.2.1 5<br>5.2.2 5<br>5.2.3 5<br>5.2.4 5<br>5.2.4 5<br>5.2.4 5<br>5.3.1 5<br>5.3.2 5                                                          | architecture diagrams91Syntax and semantics91Consistency conditions93Synthesis of configurations94Architecture style specification examples98architecture diagrams98Syntax and semantics99Consistency conditions101Synthesis of configurations104Architecture style specification examples105consistency conditions105consistency conditions105consistency conditions105configurations108Syntax and semantics108Syntax and semantics108Syntax and semantics108Syntax and semantics108                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5        | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                               | Simple 3<br>5.1.1 5<br>5.1.2 5<br>5.1.3 5<br>5.1.4 5<br>5.2.1 5<br>5.2.2 5<br>5.2.3 5<br>5.2.4 5<br>5.2.4 5<br>5.3.1 5<br>5.3.2 5<br>General                                                          | architecture diagrams91Syntax and semantics91Consistency conditions93Synthesis of configurations94Architecture style specification examples98architecture diagrams98Syntax and semantics99Consistency conditions101Synthesis of configurations104Architecture style specification examples104Syntax and semantics105Consistency conditions105Synthesis of configurations105Synthesis of configurations108Architecture diagrams108Architecture style specification examples109                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5        | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                               | Simple :<br>5.1.1 5<br>5.1.2 5<br>5.1.3 5<br>5.1.4 5<br>5.2.1 5<br>5.2.2 5<br>5.2.3 5<br>5.2.4 5<br>5.2.4 5<br>5.2.4 5<br>5.3.1 5<br>5.3.2 5<br>General 5.4.1 5                                       | architecture diagrams91Syntax and semantics91Consistency conditions93Synthesis of configurations94Architecture style specification examples98architecture diagrams98Syntax and semantics99Consistency conditions101Synthesis of configurations104Architecture style specification examples104Syntax and semantics105Consistency conditions105Synthesis of configurations105Synthesis of configurations108Architecture diagrams108Syntax and semantics108Architecture style specification examples109architecture style specification examples109architecture style specification examples109architecture diagrams109architecture diagrams109architecture diagrams109                                                                                                                                                                                                                                  |

| 5        | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                               | Simple 3<br>5.1.1 5<br>5.1.2 5<br>5.1.3 5<br>5.1.4 4<br>Interval<br>5.2.1 5<br>5.2.2 5<br>5.2.3 5<br>5.2.4 4<br>Index at<br>5.3.1 5<br>5.3.2 4<br>General<br>5.4.1 5                                  | architecture diagrams91Syntax and semantics91Consistency conditions93Synthesis of configurations94Architecture style specification examples98architecture diagrams98Syntax and semantics99Consistency conditions101Synthesis of configurations104Architecture style specification examples104Syntax and semantics105Consistency conditions105Synthesis of configurations105Synthetic ture diagrams108Syntax and semantics108Syntax and semantics109architecture style specification examples109architecture diagrams109architecture diagrams109architecture diagrams110Syntax and semantics109architecture diagrams110Syntax and Semantics110Syntax and Semantics110                                                                                                                                                                                                                                  |

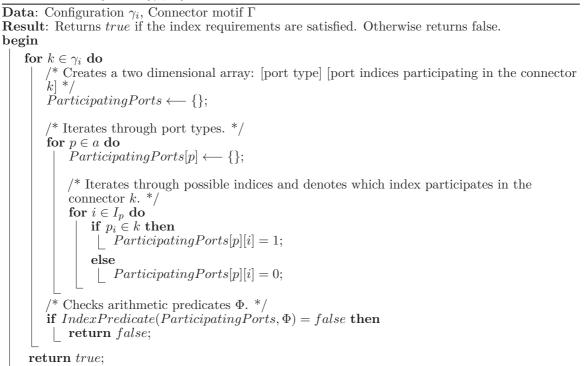

| 5        | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul>                   | Simple 3<br>5.1.1 3<br>5.1.2 4<br>5.1.3 5<br>5.1.4 4<br>Interval<br>5.2.1 5<br>5.2.2 4<br>5.2.3 5<br>5.2.4 4<br>Index at<br>5.3.1 5<br>5.3.2 4<br>General<br>5.4.1 5<br>5.4.2 4<br>Checkin            | architecture diagrams91Syntax and semantics91Consistency conditions93Synthesis of configurations94Architecture style specification examples98architecture diagrams98Syntax and semantics99Consistency conditions101Synthesis of configurations104Architecture style specification examples104Architecture style specification examples105Syntax and semantics105Synthesis of configurations105Synthetecture style specification examples108Syntax and semantics108Architecture style specification examples109architecture style specification examples109Architecture style specification examples109Architecture style specification examples110Syntax and semantics110Architecture style specification examples110Architecture style specification examples110Architecture style specification examples110Architecture style specification examples110Architecture style specification examples110 |

| 5        | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ul> | Simple 3<br>5.1.1 5<br>5.1.2 6<br>5.1.3 5<br>5.1.4 4<br>Interval<br>5.2.1 5<br>5.2.2 6<br>5.2.3 5<br>5.2.4 4<br>Index at<br>5.3.1 5<br>5.3.2 4<br>General<br>5.4.1 5<br>5.4.2 4<br>Checkin<br>Encodir | architecture diagrams91Syntax and semantics91Consistency conditions93Synthesis of configurations94Architecture style specification examples98architecture diagrams98Syntax and semantics99Consistency conditions99Consistency conditions101Synthesis of configurations101Syntax and semantics101Synthesis of configurations104Architecture style specification examples105chitecture diagrams108Syntax and semantics109architecture style specification examples109architecture diagrams109architecture style specification examples109Architecture style specification examples110Syntax and semantics110Architecture style specification examples110Architecture style specification examples110Syntax and Semantics110Syntax and Semantics110Architecture style specification examples112g conformance of diagrams115                                                                              |

| 6            | Cas   | e studies 1                                                   | 133 |

|--------------|-------|---------------------------------------------------------------|-----|

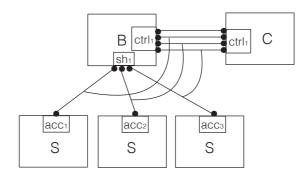

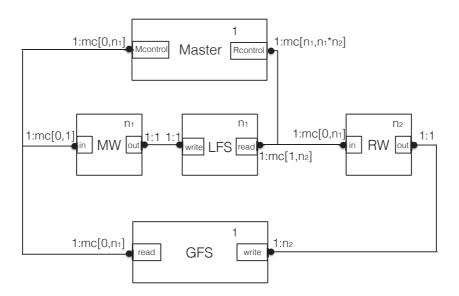

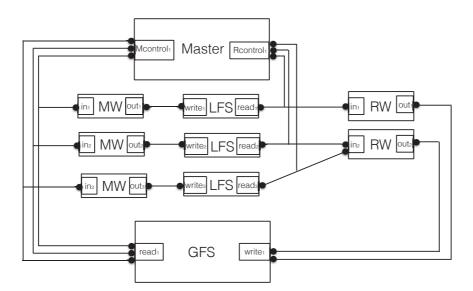

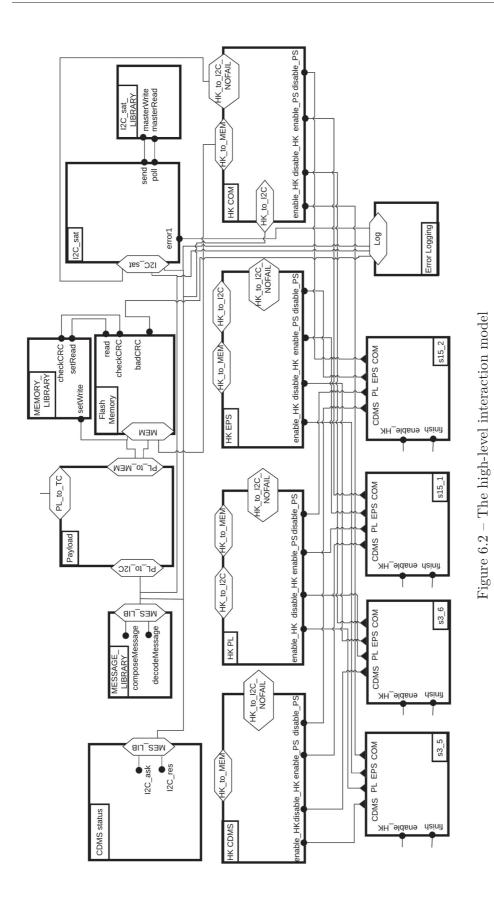

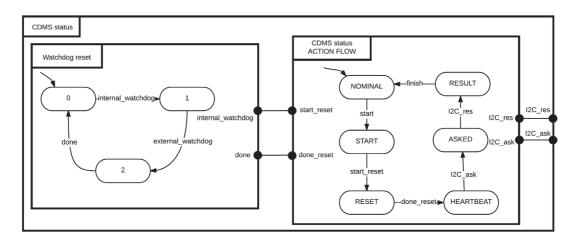

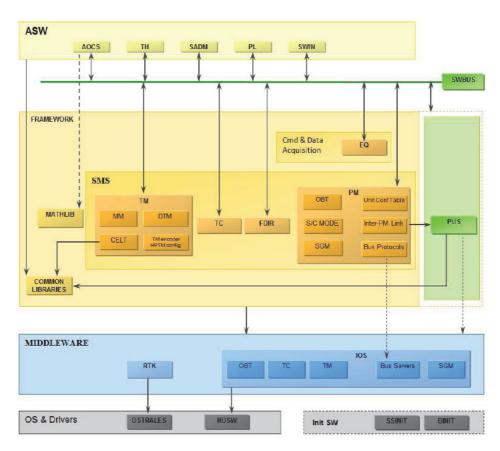

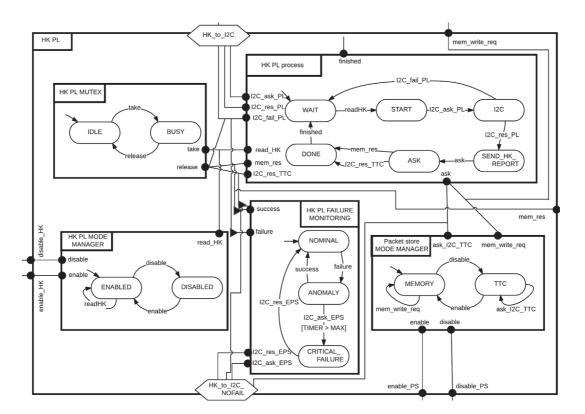

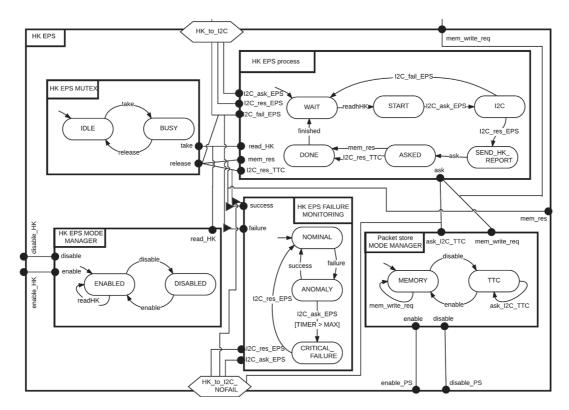

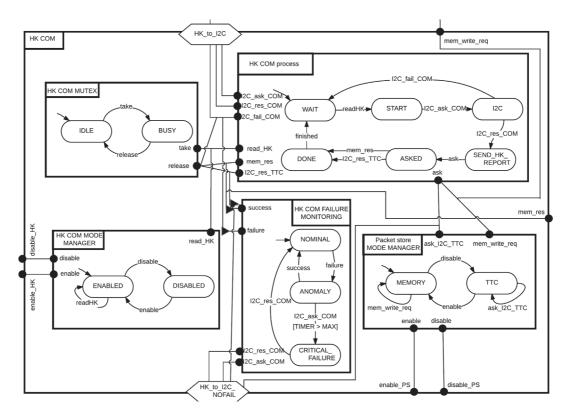

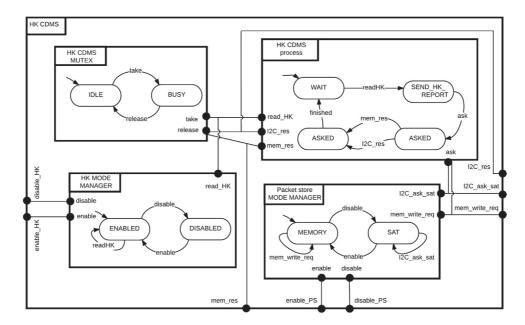

|              | 6.1   | The CubETH case study                                         | 133 |

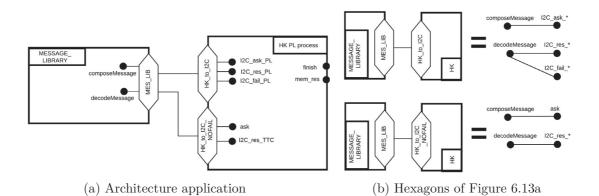

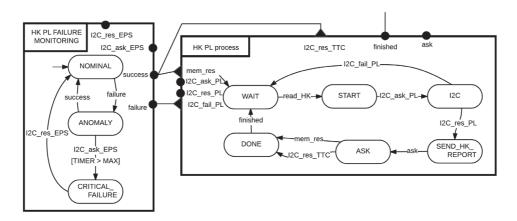

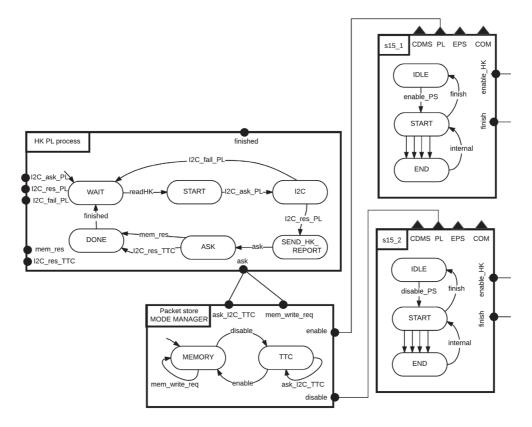

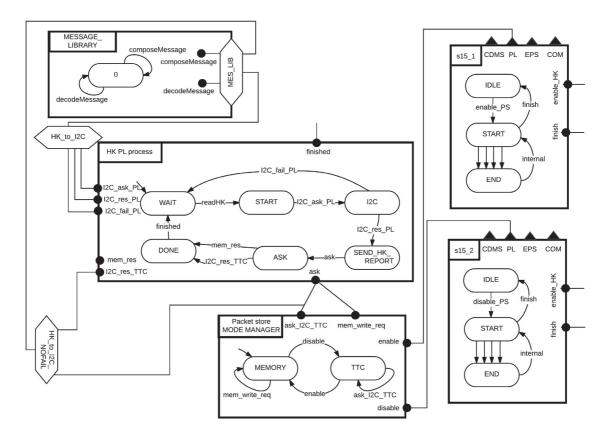

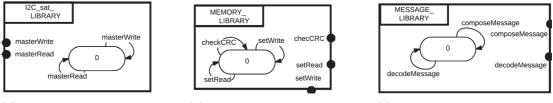

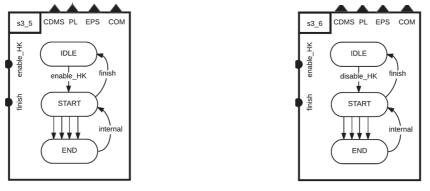

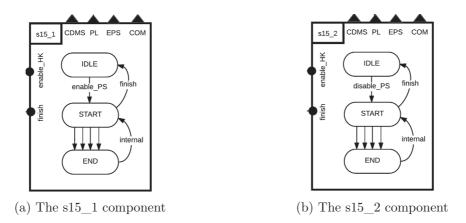

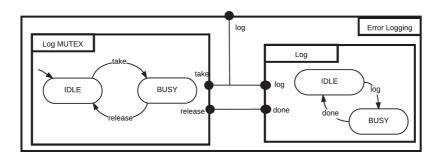

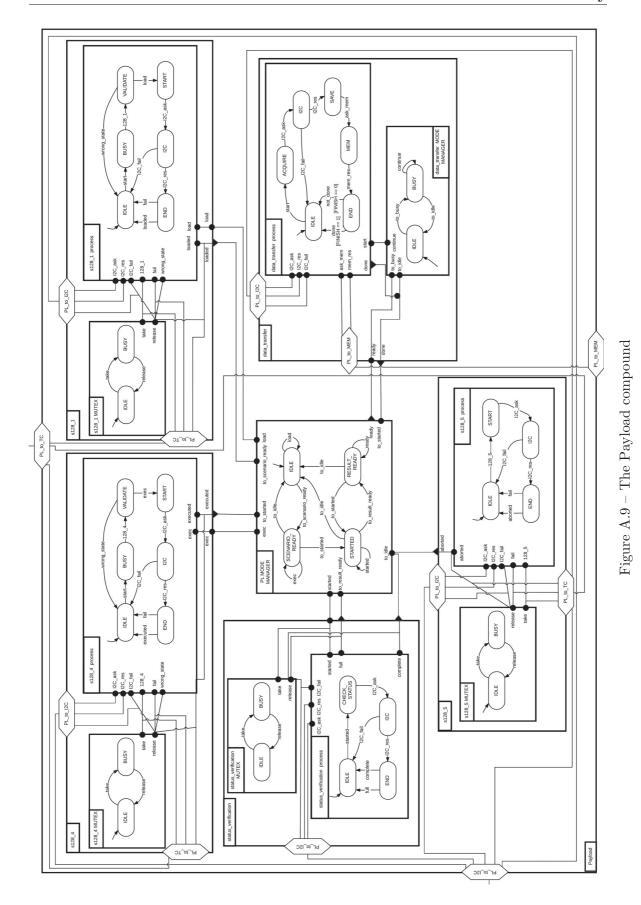

|              |       | 6.1.1 A taxonomy of architecture styles for on-board software | 134 |

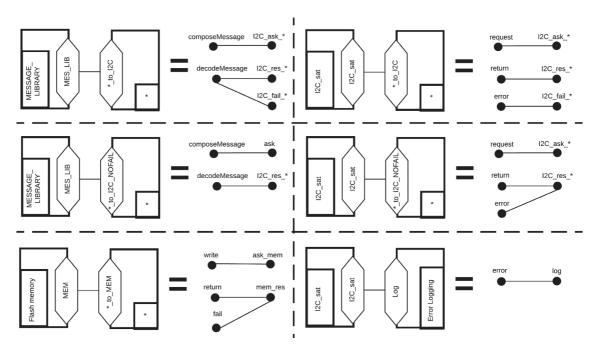

|              |       | 6.1.2 Architecture application and composition examples       | 145 |

|              |       | 6.1.3 Model verification                                      | 148 |

|              |       | 6.1.4 Validation of the approach                              | 149 |

|              | 6.2   | The Sentinel 3 case study                                     | 150 |

|              | 6.3   | Summary                                                       | 152 |

| 7            | Con   | clusion and future work 1                                     | 153 |

|              | 7.1   | Modelling and implementation of architectures                 | 153 |

|              | 7.2   | Modelling architecture styles                                 | 154 |

| $\mathbf{A}$ | App   | pendix 1                                                      | 157 |

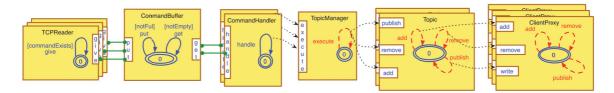

|              | A.1   | JavaBIP use case: Publish-Subscribe server                    | 157 |

|              | A.2   | List of requirements of CubETH case study                     | 160 |

|              | A.3   | BIP model of CubETH case study                                | 161 |

| Bi           | bliog | graphy 1                                                      | 179 |

# List of Figures

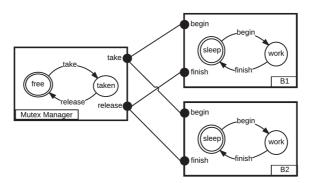

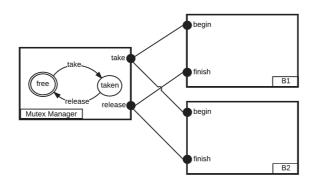

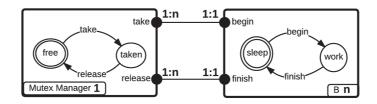

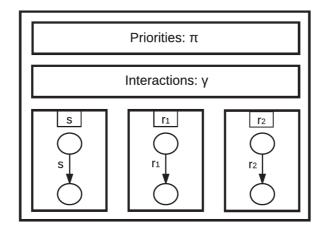

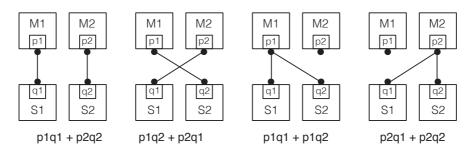

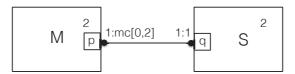

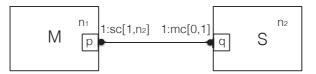

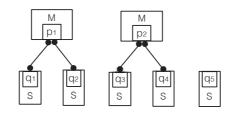

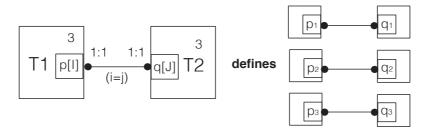

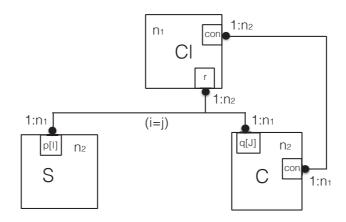

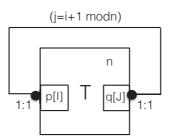

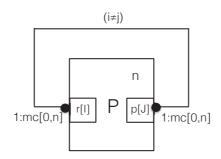

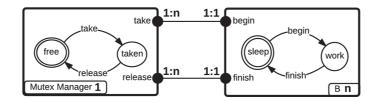

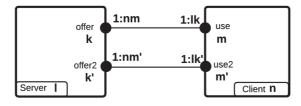

| $\begin{array}{c} 1.2 \\ 1.3 \end{array}$                                                      | Mutual exclusion model in BIP          Mutual exclusion architecture          Architecture diagram of the Mutual exclusion style                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3     4     8                                            |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

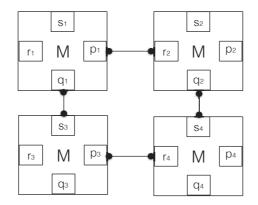

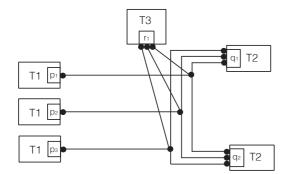

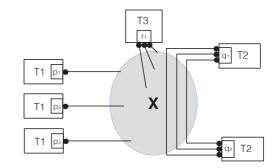

| 2.1                                                                                            | A BIP system with three atomic components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14                                                       |

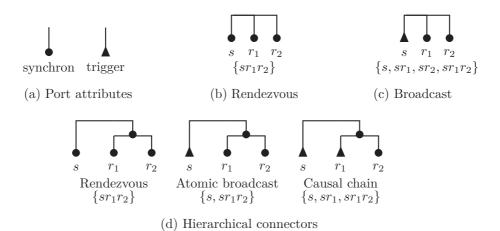

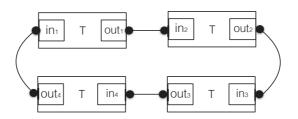

| 2.2                                                                                            | BIP connectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                       |

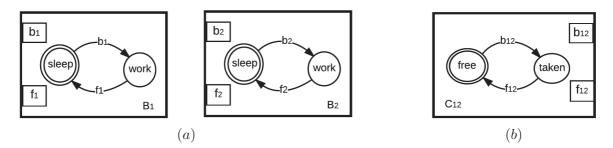

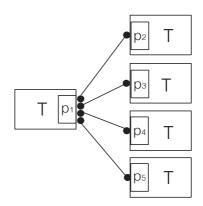

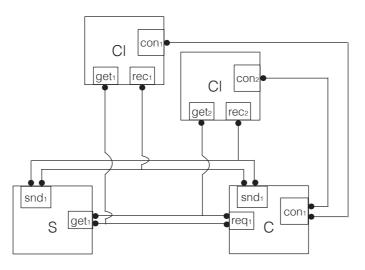

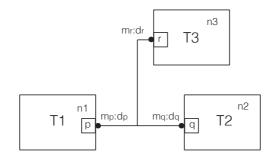

| 2.3                                                                                            | Components $(a)$ and coordinator $(b)$ for Example 2.4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20                                                       |

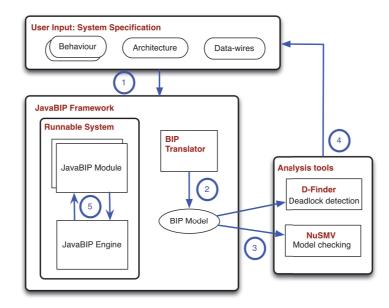

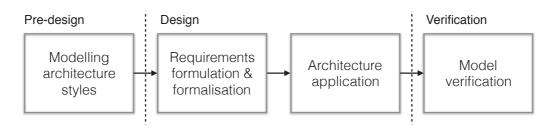

| 3.1                                                                                            | JavaBIP design workflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22                                                       |

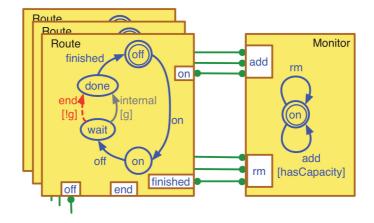

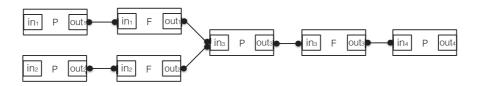

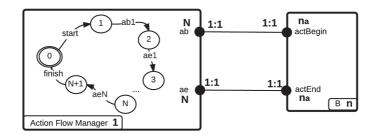

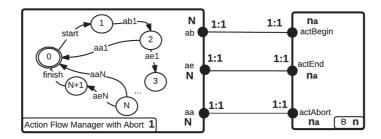

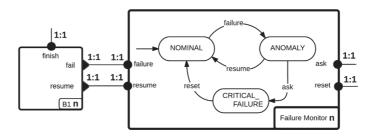

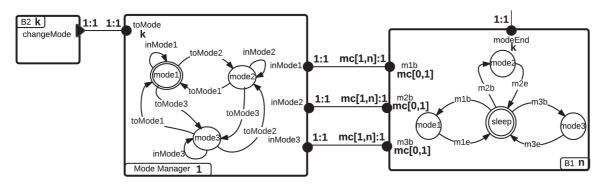

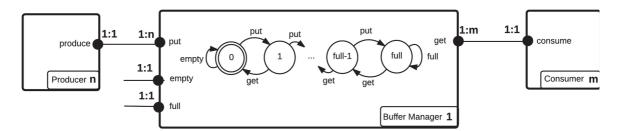

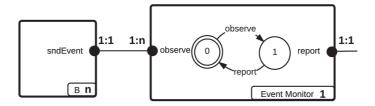

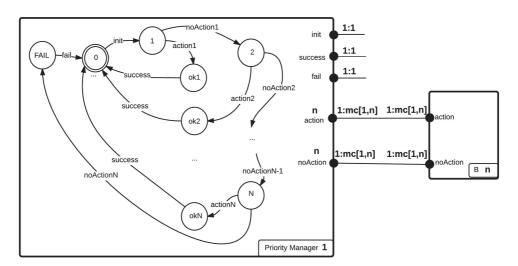

| 3.2                                                                                            | JavaBIP models of three routes and a monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 24                                                       |

| 3.3                                                                                            | Annotations for the Route component type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25                                                       |

| 3.4                                                                                            | Annotations for the Monitor component type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 26                                                       |

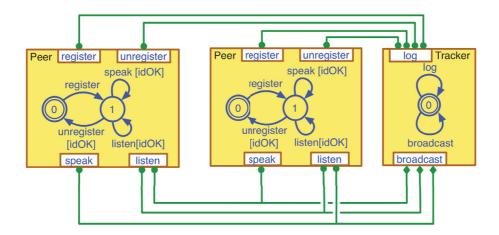

| 3.5                                                                                            | JavaBIP models of one tracker and two peers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37                                                       |

| 3.6                                                                                            | Architecture specification for the Trackers and Peers example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 41                                                       |