## Hardware/Software Co-Design of Ultra-Low Power Biomedical Monitors

THÈSE Nº 7314 (2016)

PRÉSENTÉE LE 9 DÉCEMBRE 2016 À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR LABORATOIRE DES SYSTÈMES EMBARQUÉS PROGRAMME DOCTORAL EN GÉNIE ÉLECTRIQUE

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

## Ruben BRAOJOS LOPEZ

acceptée sur proposition du jury:

Prof. J.-Ph. Thiran, président du jury Prof. D. Atienza Alonso, directeur de thèse Prof. F. Catthoor, rapporteur Prof. L. Pozzi, rapporteuse Prof. A. P. Burg, rapporteur

The present is theirs; the future, for which I really worked, is mine. — Nikola Tesla

To my grandfather Basilio. To my parents. To my family.

-

A mi abuelo Basilio. A mis padres. A mi familia.

## Acknowledgements

I would not have been able to carry out the work presented in this thesis without the excellent guidance and support given by my advisor, *Prof. David Atienza*. Back in 2009, when I arrived to EPFL as an exchange student who did not know anything about research and almost nothing about the topic of this thesis, he gave me an opportunity to join his group as a trainee. Later, in 2011, he accepted me to start my PhD, which now concludes with this manuscript. During all this time, he has made me understand what research is, how to collaborate in a team and why critical thinking, patience and hard work are the foundations to do a good job. Not only I have learned a lot from him on the professional and academic sides but also we have developed a personal friendship that I hope will last for many years ahead.

I would like to dedicate the next words to thank the members of the jury that evaluated this thesis. I wanted to show my gratitude to *Prof. Jean-Philippe Thiran*, who accepted to be the president of the jury, and who has been a superb director of the EE doctoral school to which I had the honor to belong; to *Prof. Francky Catthoor* for his outstanding feedback in the elaboration of the final version of this manuscript; to *Prof. Laura Pozzi* for her careful and thorough comments on the text; and to *Prof. Andy Burg* for his infinite support not only during the evaluation of the thesis but also throughout all these last years.

In the next lines I want to thank my family for their help, sacrifice and support, which has allowed me to reach this point of my life. I take the liberty to address the next paragraph to them in our native language, Spanish:

Como decía en las líneas anteriores, me gustaría agradecer a mi familia toda la ayuda, el sacrificio y el apoyo incondicional que me han permitido llegar a este punto de mi vida. Gracias especialmente a mis padres, **José Antonio y Rosa María**, sin los cuales no podría haber llegado a ser quien soy. A mi padre, por ser el ejemplo de superación que he seguido desde pequeño y por enseñarme que casi nada es imposible si se trabaja duro. A mi madre, a quien debo mi forma de ser, quien me ha educado en el respeto y quien, aún estando lejos de ello, me ha hecho sentir capaz de todo. No puedo olvidarme de mi hermano Borja, que aún siendo menor que yo en edad, es mucho más grande en cualquier otro buen aspecto. Debo también recordar a mi hermana Inma, a la que tanto quiero, y a mi sobrino Aitor, que tantas alegrías me ha dado a pesar de su corta edad. Quiero recordar especialmente a mi abuelo Basilio, a cuya memoria está dedicada esta tesis doctoral y quien ha sido para mi otro ejemplo a seguir. También a mi abuela Carmen, que tan querido me hace sentir cada vez que puede con pequeños gestos que para mi representan un mundo. Finalmente, me gustaría acabar este párrafo agradeciendo al resto de mi familia por todo el ánimo y la fuerza que me han dado durante este periodo.

At this point, I cannot continue without mentioning one of the most important persons in my life, *Marina*. My PhD has been like running a marathon: exciting, difficult, exhausting... Marina arrived to my life just in time, during the last period where the strength started to diminish. She has helped me to look ahead, to believe in myself and she has made me feel what I had never felt before for someone. I want to thank her for her unlimited support, her unquestionable patience and her unbreakable love.

In Spain, it is common to say that one does not choose his own family, but I do not agree with this idea. I think that you choose certain people with whom to share important moments of you life. Those that make you feel good and beloved. Those that you also love. With these words I would like to thank that second family, composed of friends that are there when you need them, that make you feel like at home, even if you are thousands of kilometers away. Special thanks to *Patricia Tovar, Kepa* (and *little Daniela*), *Marta Tovar, Michelangelo, Julia, Lara* (and *little Alessia*), *Fran, Laura* (and *little Alba*), *Hossein, Ivan, Miguel, Marta Camarena, Victor, Mateo* and *Patricia F. Varela*.

If one could have one more family, I would say that my third one is formed by all the members and ex-members of the Embedded Systems Laboratory. First, I would like to thank *Homeira* – without whom this lab would not be the same – for her silent but constant support and her selfless help. Then, I would like to thank all my officemates (*Hossein, Giovanni, Fabio, Leila* and *Eli*) for being one of the reasons why I want to come to work everyday. Next, I would like to thank *Ivan, Vincenzo* and *Pablo*, because even if we never were officemates, we spent so much time and shared so many good moments together. I would like to thank the first ESL group (*Ahmed, Mohamed, Martino, Alessandro, Arvind, Shivani, Emi and Karim*) for all the good memories that I will keep forever. Also to the new generation (*Dixie, Loris, Soumya, Greg, Tim, Yasir, Amir, Ali and Arman*), for the nice atmosphere they have created that I hope will last for years. Of course I do not want to forget those that temporary passed by the lab (*Alair, Ale Nacci, PRG, Joaquín, Nil, Camilo, Jungsoo, Srini* and many others) who, in some sense or another, collaborated to make this group so special. Finally, I would like to thank *Francine* and our IT master, *Rodolphe*, for their daily assistance.

Special thanks go to those who I collaborated with during my PhD and from whom I have learnt priceless lessons, particularly *Jeremy, Daniele, Andrea, Tony, Simone, Prof. Benini, Prof. Vesin and Prof. Mitra*. Also to *Raphael, Elvira* and all the members of the EDEE Coaching Team with whom I have spent so many good experiences at the EE doctoral school.

Finally, I would not like to finish these acknowledgements without mentioning the friends that I met during my PhD, particularly *Jacopo, Shashi, Camilla, Andrea, Cristina, Matteo and Anna*. Thanks also to those friends I met during my studies in Madrid (*Javi, Hector, David, Jose, Alex* and all the FDI guys). And of course, special thanks to my longtime friends who I enjoy to meet every time I come back to my hometown (*Juan Luís, Tania, Leti, Fati, Ángel, Inma* and many others).

Lausanne, 17 November 2016

Rubén Braojos López

## Abstract

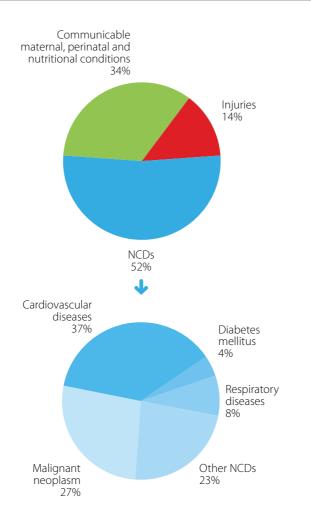

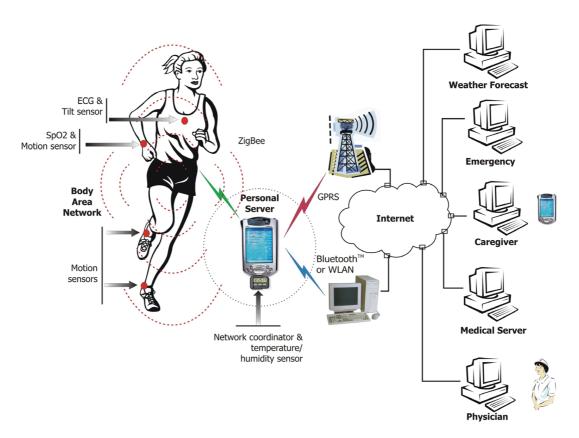

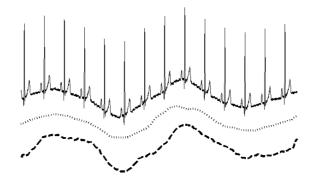

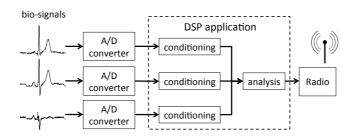

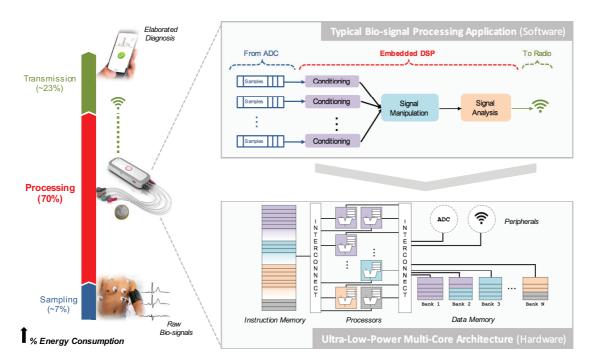

Ongoing changes in world demographics and the prevalence of unhealthy lifestyles are imposing a paradigm shift in healthcare delivery. Nowadays, chronic ailments such as cardiovascular diseases, hypertension and diabetes, represent the most common causes of death according to the World Health Organization. It is estimated that 63% of deaths worldwide are directly or indirectly related to these non-communicable diseases (NCDs), and by 2030 it is predicted that the health delivery cost will reach an amount comparable to 75% of the current GDP. In this context, technologies based on Wireless Sensor Nodes (WSNs) effectively alleviate this burden enabling the conception of wearable biomedical monitors composed of one or several devices connected through a Wireless Body Sensor Network (WBSN). These resourceconstrained systems allow for long term recording of biological signals and perform embedded advanced digital signal processing (DSP) enabling autonomous diagnosis even outside a hospital environment. Energy efficiency is of paramount importance for these devices, which must operate for prolonged periods of time with a single battery charge. Therefore, in order to minimize power consumption, both the software executing in these platforms and the underlying hardware require a carefully tailored design.

In this thesis I propose a set of hardware/software co-design techniques to drastically increase the energy efficiency of biomedical monitors. To this end, I jointly explore different alternatives to reduce the required computational effort at the software level while optimizing the power consumption of the processing hardware by employing ultra-low power multi-core architectures that exploit DSP application characteristics.

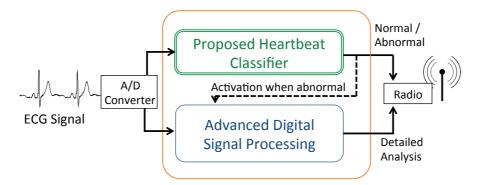

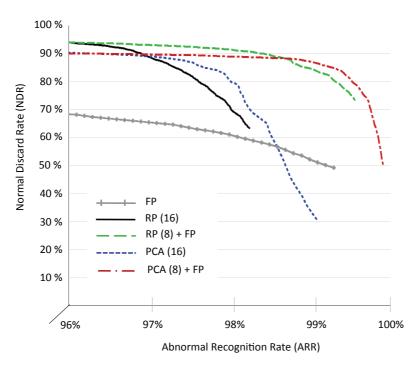

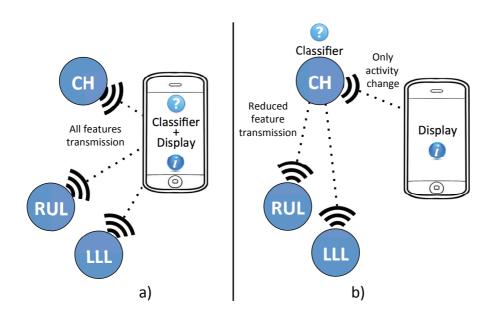

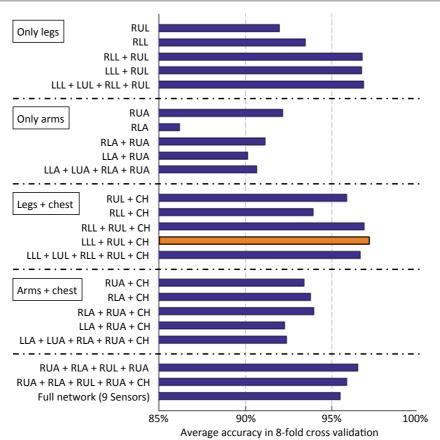

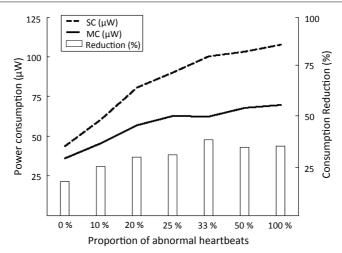

First, at the sensor level, I study the utilization of a heartbeat classifier to perform **selective advanced DSP** on state-of-the-art ECG biomedical monitors. To this end, I developed a framework to design and train real-time, lightweight heartbeat neuro-fuzzy classifiers, detailing the required optimizations to efficiently execute them on a resource-constrained platform. Then, at the network level I propose a more complex transmission-aware WBSN for activity monitoring that provides different tradeoffs between classification accuracy and transmission volume. In this work, I study the combination of a minimal set of WSNs with a smartphone, and propose two classification schemes that trade accuracy for transmission volume. The proposed method can achieve accuracies ranging from 88% to 97% and can save up to 86% of wireless transmissions, outperforming the state-of-the-art alternatives.

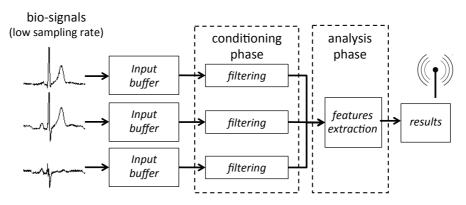

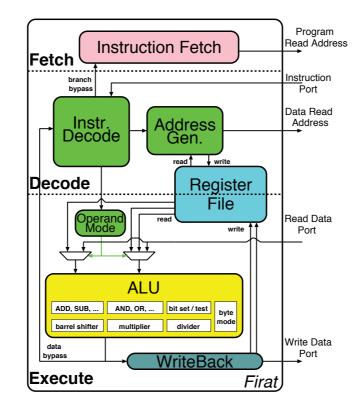

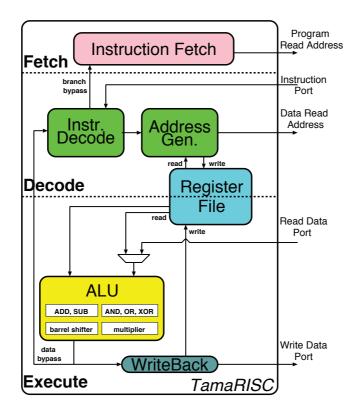

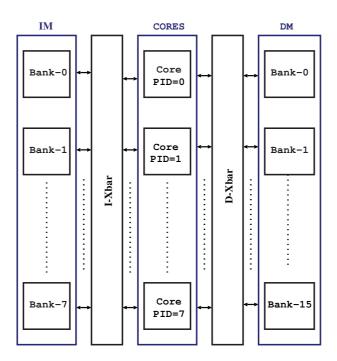

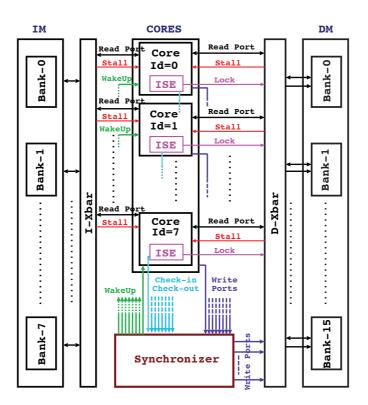

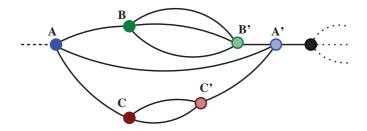

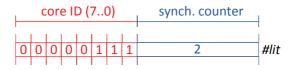

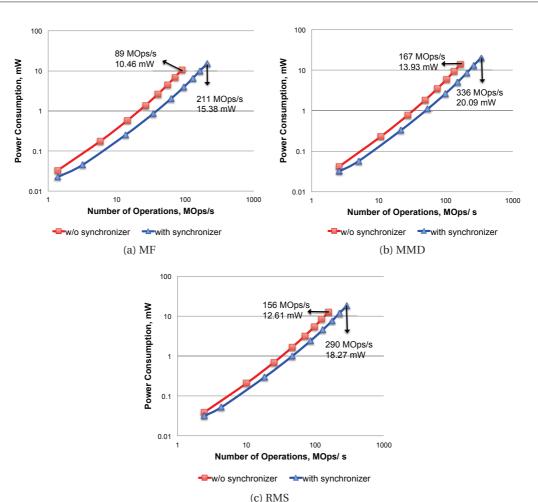

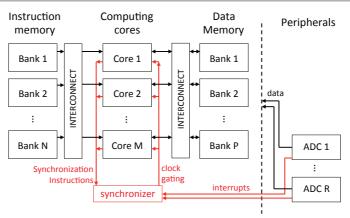

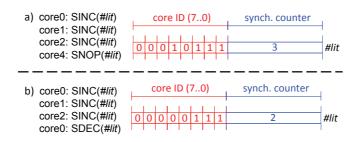

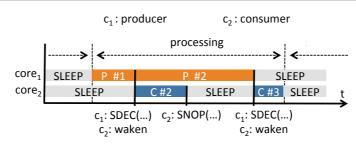

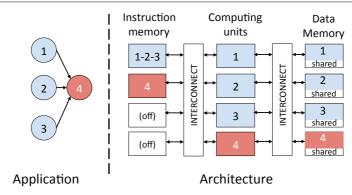

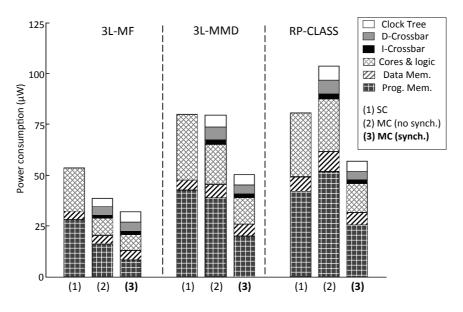

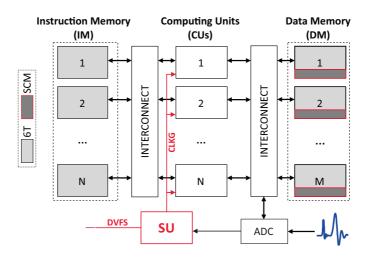

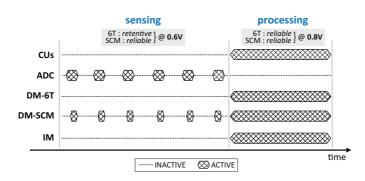

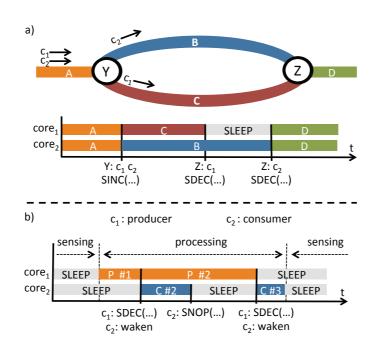

Second, I propose a **synchronization-based low-power multi-core architecture** for bio-signal processing. I introduce a hardware/software synchronization mechanism that allows to achieve high energy efficiency while parallelizing the execution of multi-channel DSP appli-

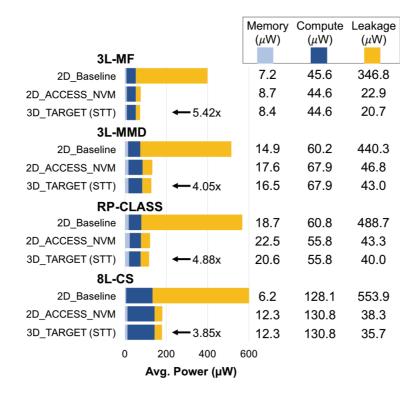

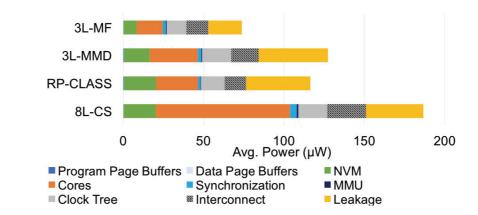

cations. Then, I generalize the methodology to support bio-signal processing applications with an arbitrarily high degree of parallelism. The proposed technique includes a dedicated lightweight synchronizer and an instruction set extension (ISE) of the processing cores. Due to the benefits of SIMD execution and software pipelining, the architecture can reduce its power consumption by up 38% when compared to an equivalent low-power single-core alternative. Finally, I focus on the optimization of the multi-core memory subsystem, which is the major contributor to the overall system power consumption. First I considered a **hybrid memory subsystem** featuring a small reliable partition that can operate at ultra-low voltage enabling low-power buffering of data and obtaining up to 50% energy savings. Second, I explore a **two-level memory hierarchy based on non-volatile memories** (NVM) that allows for aggressive fine-grained power gating enabled by emerging low-power NVM technologies and monolithic 3D integration. Experimental results show that, by adopting this memory hierarchy, power consumption can be reduced by 5.42x in the DSP stage.

*Key words*: Bio-signal processing; Ultra-low Power Architectures; Hardware/Software Co-Design; Biomedical Monitors; Multi-Core Code Synchronization; Energy-Efficient Multi-Core Platforms; Electrocardiogram Embedded Processing; Lightweight Heartbeat Classification;

## Résumé

La croissance démographique actuelle et l'augmentation des modes de vie malsains à l'échelle mondiale, imposent des changements significatifs en ce qui concerne les prestations de soins de santé. De nos jours, les maladies chroniques telles que les maladies cardiovasculaires, l'hypertension et le diabète, représentent les causes principales de décès d'après l'Organisation Mondiale de la Santé. Il a été estimé que 63% des décès à l'échelle mondiale sont directement ou indirectement en lien avec ces maladies chroniques. Par ailleurs, d'ici 2030, il a été prévu que le coût des soins atteindra environ 75% du PIB actuel. Dans ce contexte, les technologies basées sur les Nœuds de Capteurs Sans-Fil (WSN en anglais), réduisent efficacement les coûts engendrés lors des soins des maladies mentionnées ci-dessus, ce qui à terme pousse à la conception d'équipements biomédicaux portables, composés d'un ou de plusieurs appareils interconnectés au sein d'un Réseau de Capteurs Corporels Sans-Fil (WBSN en anglais). Ces systèmes disposant de ressources limitées, permettent un enregistrement long durée de signaux biologiques et effectuent sur ces derniers un traitement numérique avancé, afin de délivrer de façon autonome un diagnostic médical, et cela même en dehors d'un environnement hospitalier. L'efficacité énergétique de ces appareils est d'importance capitale, étant donné qu'ils doivent fonctionner sur de longues périodes de temps, avec pour seule source d'énergie une unique batterie. C'est pourquoi, afin de minimiser la consommation énergétique, les parties logicielles et matérielles de ces appareils doivent être développées avec le plus grand soin.

Dans cette thèse, je propose un ensemble de techniques de conception mixtes logiciel/matériel, permettant d'augmenter de façon significative, l'efficacité énergétique de ces appareils de surveillance biomédicale. Afin d'atteindre cet objectif, j'explore conjointement différentes solutions dans le but de réduire l'effort en terme de calcul au niveau du logiciel, tout en optimisant la consommation énergétique de la partie matérielle, en employant une architecture multi-cœurs ultra-basse consommation, qui exploite les caractéristiques des applications logicielles effectuant le traitement numérique des signaux biologiques.

En premier lieu, au niveau des capteurs, j'effectue une étude de l'utilisation d'un classificateur de battement de cœurs, afin d'effectuer un traitement numérique sélectif sur des signaux cardiaques, à l'aide d'appareils de surveillance biomédicale de dernière génération. Pour ce faire, j'ai développé une plateforme me permettant de concevoir et de tester des classificateurs de battement de cœurs, afin d'établir la liste des optimisations nécessaires, dans le but d'exécuter efficacement ces classificateurs sur des systèmes à ressource limitée. Par la suite, au niveau réseau, je propose un *WBSN* plus élaboré, utilisé pour la surveillance de l'activité des patients et qui propose différents compromis entre précision de la classification des bat-

tements de cœurs et le volume de données transmises. Dans ce travail, j'étudie l'association d'un ensemble restreint de *WSN* connecté avec un smartphone, et je propose deux modèles de classifications qui comparent l'évolution de la précision en fonction de la quantité de données transmises. L'intervalle de qualité de la classification évolue entre 88% et 97%, tout en permettant d'économiser jusqu'à 86% des transmissions sans fil, dépassant même, les performances des solutions de dernière génération.

En second lieu, je propose une architecture multi-cœurs basse consommation, reposant sur un mécanisme de synchronisation et conçu pour le traitement des signaux biologiques. J'introduis lors de cette recherche, un mécanisme de synchronisation matériel/logiciel, permettant d'atteindre un haut niveau d'efficacité énergétique, tout en parallélisant l'exécution des applications de traitement des signaux biologiques. Ensuite, je généralise la méthodologie afin de supporter différentes applications disposant d'un degré arbitraire de parallélisme au sein de leur exécution. La technique proposée incorpore un synchroniseur à faible encombrement et une extension du jeu d'instructions pour les différents cœurs de traitement. De par les bénéfices prodigués par le mode d'exécution *Single-Instruction Multiple-Data* (SIMD) et l'exécution logiciel en pipeline, l'architecture atteint une réduction jusqu'à 38% de sa consommation énergétique, en comparaison avec un système basse consommation mono-cœur.

Pour finir, je me suis concentré sur l'optimisation de la hiérarchie mémoire du système multicœur, qui consomme une part majoritaire de l'énergie totale utilisée par le système. En premier lieu, j'ai considéré une hiérarchie mémoire hybride, intégrant une petite partition mémoire protégée et pouvant fonctionner avec une très basse tension d'alimentation, et permettant d'atteindre ainsi, 50% d'économie d'énergie. En second lieu, j'explore une hiérarchie mémoire à deux niveaux, basée sur une technologie à cellules Mémoire Non-Volatile (*NVM* en anglais), permettant d'effectuer un "power gating" avec une granularité très fine, soutenue par les technologies émergentes telles que : NVM basse tension et fabrication monolithique tridimensionnel de circuits. Des résultats expérimentaux montrent qu'en adoptant cette hiérarchie mémoire, la consommation énergétique peut être divisée par 5,42 dans l'étage de traitement numérique des signaux.

*Mots clefs* : Traitement de Signaux Biologiques, Architectures Ultra-basse Consommation, Conception Mixte Matériel/Logiciel, Systèmes de Surveillance Biomédicale, Synchronisation de Systèmes Multi-Cœurs, Plateforme Multi-Cœurs à Haut Rendement Energétique, Traitement Embarqué d'Electrocardiogramme, Classification de Battements de Cœur

## Contents

| Acknowledgements |                                   |                                                                     |      |

|------------------|-----------------------------------|---------------------------------------------------------------------|------|

| Abstra           | ct                                |                                                                     | iii  |

| Resum            | né (Fra                           | nçais)                                                              | v    |

| Table o          | of Cont                           | ents                                                                | vii  |

| List of          | Figure                            | s                                                                   | xi   |

|                  | -                                 |                                                                     |      |

| List of          | Tables                            |                                                                     | XV   |

| List of          | Abbrev                            | viations                                                            | xvii |

| 1 Int            | roducti                           | ion                                                                 | 1    |

| 1.1              | Embe                              | edded Bio-Signal Processing                                         | 3    |

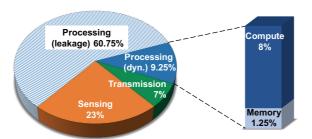

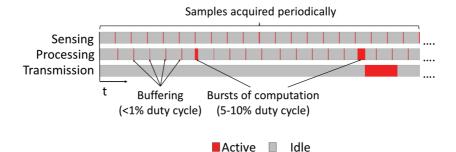

|                  | 1.1.1                             | Energy-Saving Opportunities in Bio-signal Processing Applications   | 4    |

| 1.2              | Low I                             | Power Architectures for Bio-Signal Processing                       | 5    |

|                  | 1.2.1                             | Low-power Design Limitations                                        | 6    |

| 1.3              | Thesi                             | s contributions                                                     | 7    |

| 1.4              | Thesi                             | s Outline                                                           | 10   |

| 2 Opt            | timized                           | l Embedded Digital Signal Processing for Health Monitoring          | 13   |

| 2.1              | intro                             | duction                                                             | 13   |

|                  | 2.1.1                             | Embedded Processing and Limitations                                 | 14   |

|                  | 2.1.2                             | Contributions and Outline of this Chapter                           | 15   |

| 2.2              | Existi                            | ng Advanced Embedded Signal Processing Methods                      | 16   |

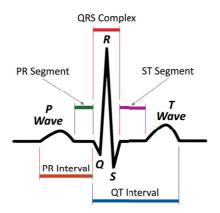

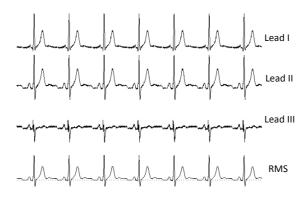

|                  | 2.2.1                             | ECG Conditioning                                                    | 16   |

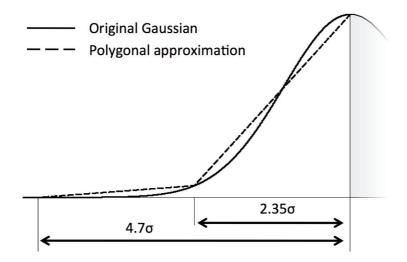

|                  |                                   | 2.2.1.1 Spline Filtering (SF)                                       | 17   |

|                  |                                   | 2.2.1.2 Morphological Filtering (MF)                                | 17   |

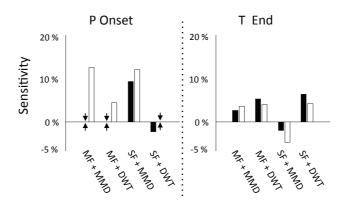

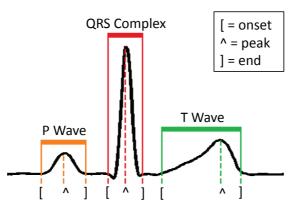

|                  | 2.2.2                             | ECG Analysis: Delineation                                           | 18   |

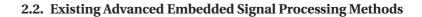

|                  |                                   | 2.2.2.1 Wavelet-based Delineation (DWT)                             | 19   |

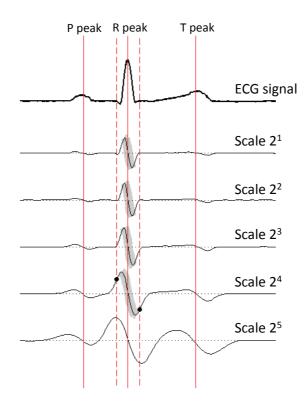

|                  |                                   | 2.2.2.2 Multi-scale Morphological Derivative-based Delineation (MMD | ) 20 |

|                  | 2.2.3 Multi-Channel Signal Fusion |                                                                     |      |

|                  | 2.2.4                             | ECG Compression: Compressed Sensing                                 | 22   |

#### Contents

|   | 2.3 | Propo  | sed Selective ECG Processing Based on Embedded Heartbeats Classification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 23         |

|---|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

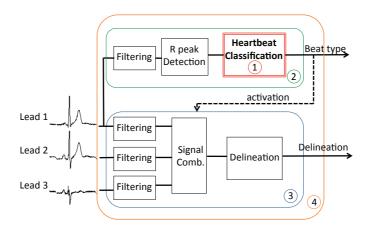

|   |     | 2.3.1  | Target Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23         |

|   |     | 2.3.2  | State of the Art and Problem Challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 24         |

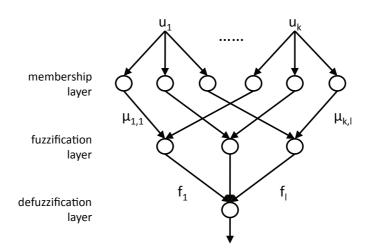

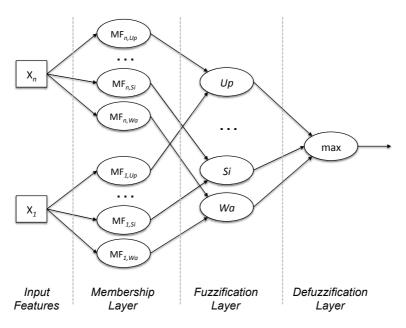

|   |     | 2.3.3  | Classification Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25         |

|   |     | 2.3.4  | Dimensionality Reduction Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 26         |

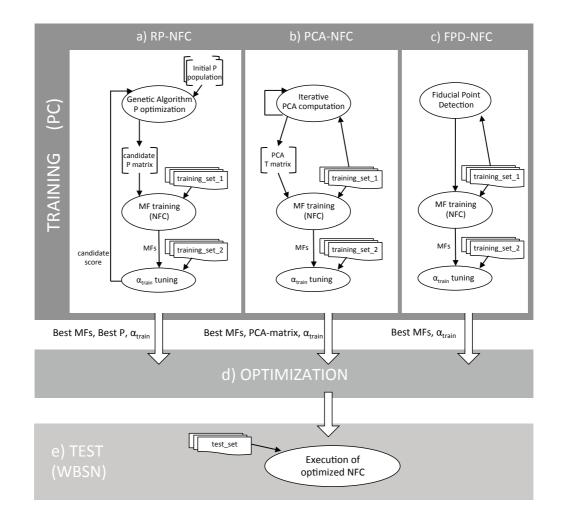

|   |     | 2.3.5  | Proposed Training Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 28         |

|   |     | 2.3.6  | Resource-Constrained Optimization Phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 30         |

|   |     | 2.3.7  | Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32         |

|   |     |        | 2.3.7.1 Experimental Set-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 32         |

|   |     |        | 2.3.7.2 Classification Accuracy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34         |

|   |     |        | 2.3.7.3 Run-time Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 35         |

|   |     |        | 2.3.7.4 Communication Savings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 38         |

|   |     | 2.3.8  | Comparison of Classification Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39         |

|   | 2.4 | Prope  | sed Energy-aware Distributed Wireless Body Sensor Network (WBSN) for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

|   |     | Physi  | cal Activity Monitoring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40         |

|   |     | 2.4.1  | State-of-the-art and Challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 41         |

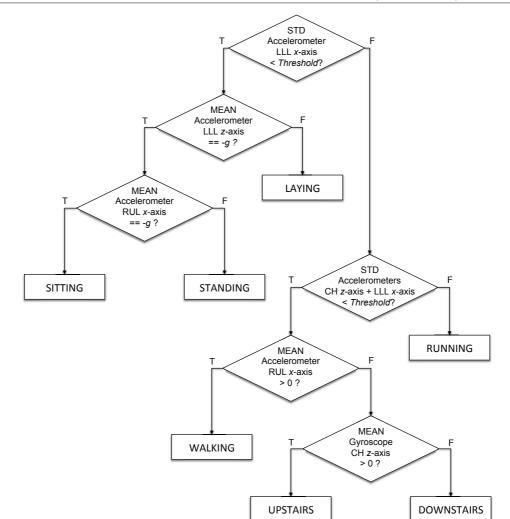

|   |     | 2.4.2  | Target System Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 43         |

|   |     |        | 2.4.2.1 Device Taxonomy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 43         |

|   |     |        | 2.4.2.2 Network Topology and Task Assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 45         |

|   |     | 2.4.3  | On-node Feature Extraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 46         |

|   |     | 2.4.4  | Classification Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 47         |

|   |     |        | 2.4.4.1 On-Node Classification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48         |

|   |     |        | 2.4.4.2 Smartphone-Based Classification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 48         |

|   |     | 2.4.5  | Experimental Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50         |

|   |     |        | 2.4.5.1 Experimental Set-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 50         |

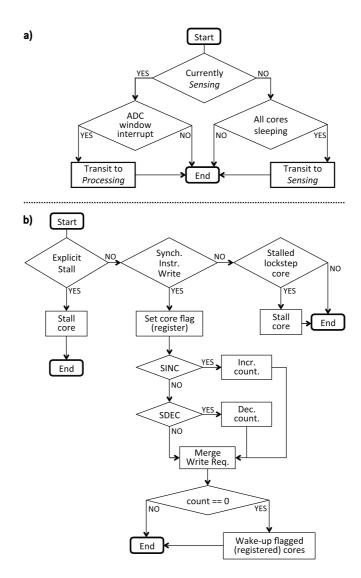

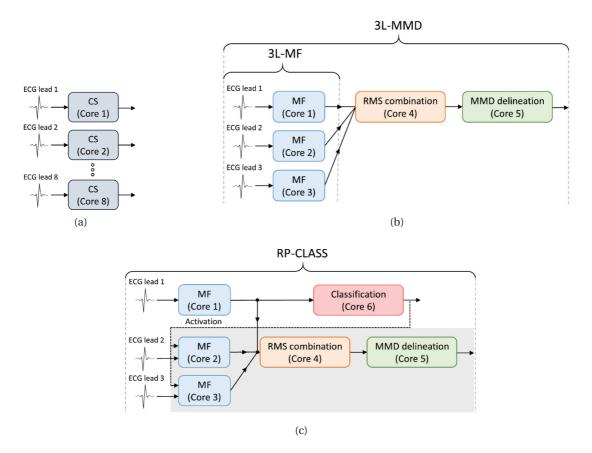

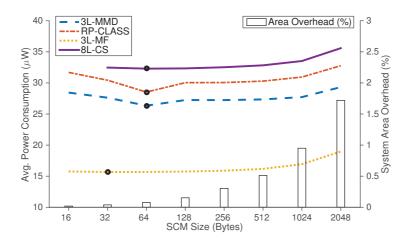

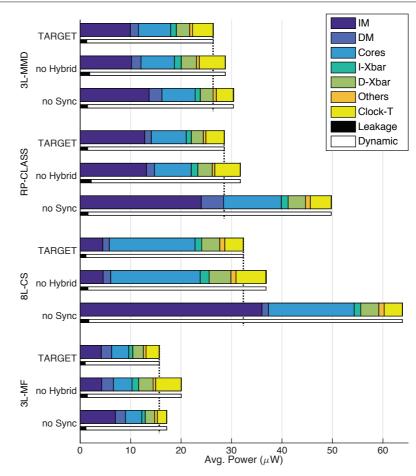

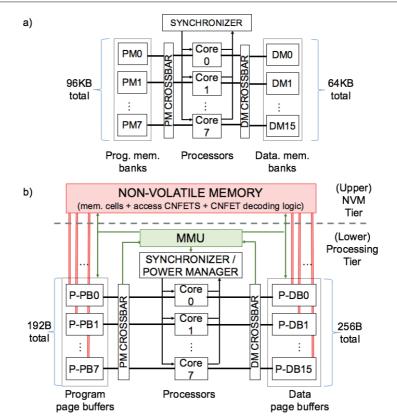

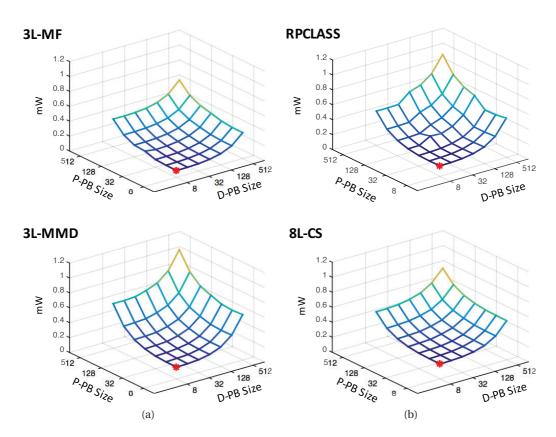

|   |     |        | 2.4.5.2 Data Collection Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 51         |