# Master Thesis

## Advanced NEMS Group

Department of Physics and Microengineering

## 2D Material-Based Bolometer

Professors: Guillermo Villanueva and Tobias Kippenberg

Supervisor: Tom Larsen

Author: Marco Di Gisi

Submitted in June 2016

ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

THIS PAGE

WAS INTENTIONALLY

LEFT BLANK

#### **Abstract**

Measurement of thermal radiation through uncooled bolometers is at the heart of many industrial applications. From the development of the Honey-well silicon microstructure developed in 1982, no particular change in paradigm was recorded. The advent of 2D-materials offers a whole new promising future for bolometric measurements and thermal detection. 2D-materials have record properties extremely sensitive to external stimuli making them great candidates for boosting bolometers performance.

In this work, a method to model, fabricate and characterise 2D material-based bolometers is presented. The proposed design uses a suspended 2D-material beam as thermal sensor and IR absorber. The model suggests an improvement of the state of the art on three different aspects. Reduction of thermal losses, tunable enhancement of absorption and increased bandwidth. An innovative read-out technique is also suggested.

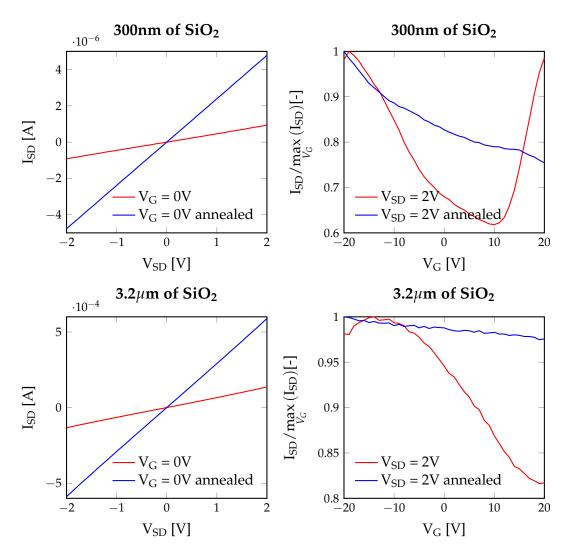

Bolometers employing graphene as suspended beam were successfully fabricated. An optimised fabrication process is proposed and allow to consistently produce devices having optimal properties to host graphene. Electrical measurements on graphene beams lying on silicon dioxide showed good tunability of graphene resistance through electrostatic gating proving possible to enhance thermal radiation absorption in graphene. The results obtained offers a promising outlook toward the future of 2D material-based bolometers.

THIS PAGE WAS INTENTIONALLY LEFT BLANK

## **Contents**

|          |                       |         |                                   | Page |  |  |  |  |  |  |

|----------|-----------------------|---------|-----------------------------------|------|--|--|--|--|--|--|

| Abstract |                       |         |                                   |      |  |  |  |  |  |  |

| Li       | List of Figures       |         |                                   |      |  |  |  |  |  |  |

| Li       | st of '               | Tables  |                                   | vii  |  |  |  |  |  |  |

| 1        | Intr                  | oductio | on                                | 1    |  |  |  |  |  |  |

| 2        | Bac                   | kgroun  | ıd                                | 5    |  |  |  |  |  |  |

|          | 2.1                   | Bolon   | neters modelling                  | . 5  |  |  |  |  |  |  |

|          |                       | 2.1.1   | Mathematical model                | . 5  |  |  |  |  |  |  |

|          |                       | 2.1.2   | Figures of merit                  | . 8  |  |  |  |  |  |  |

|          |                       | 2.1.3   | Discussion                        | . 9  |  |  |  |  |  |  |

|          | 2.2                   | Adva    | ntages of 2D-materials            | . 10 |  |  |  |  |  |  |

|          | 2.3                   |         | of the art                        |      |  |  |  |  |  |  |

| 3        | Design and motivation |         |                                   |      |  |  |  |  |  |  |

|          | 3.1                   | Desig   | n schematic and working principle | . 13 |  |  |  |  |  |  |

|          |                       | 3.1.1   | Resistive read-out                | . 13 |  |  |  |  |  |  |

|          |                       | 3.1.2   | Resonant frequency read-out       | . 14 |  |  |  |  |  |  |

|          | 3.2                   | Signif  | ficance of the study              | . 15 |  |  |  |  |  |  |

| 4        | Fab                   | ricatio | n                                 | 17   |  |  |  |  |  |  |

|          | 4.1                   | First f | fabrication run                   | . 17 |  |  |  |  |  |  |

|          |                       | 4.1.1   | Process flow                      | . 17 |  |  |  |  |  |  |

|          |                       | 4.1.2   | Mask design                       | . 22 |  |  |  |  |  |  |

|          |                       | 4.1.3   | Issues encountered and solutions  | . 28 |  |  |  |  |  |  |

|          |                       | 4.1.4   | Results                           | . 34 |  |  |  |  |  |  |

|          |                       | 4.1.5   | Summary and conclusion            | . 35 |  |  |  |  |  |  |

| 4                                          | .2 Secon   | Second fabrication run           |    |  |  |

|--------------------------------------------|------------|----------------------------------|----|--|--|

|                                            | 4.2.1      | Process flow                     | 36 |  |  |

|                                            | 4.2.2      | Mask design                      | 38 |  |  |

|                                            | 4.2.3      | Issues encountered and solutions | 40 |  |  |

|                                            | 4.2.4      | Results                          | 43 |  |  |

|                                            | 4.2.5      | Summary and conclusion           | 45 |  |  |

| 4                                          | 4.3 Comp   | parison                          | 45 |  |  |

| 5 (                                        | Characteri | sation                           | 47 |  |  |

| 5                                          | 5.1 Grapl  | hene beams on silicon dioxide    | 47 |  |  |

| 6 Conclusion                               |            |                                  |    |  |  |

| Appendices                                 |            |                                  |    |  |  |

| A Fabrication details                      |            |                                  |    |  |  |

| B Devices distribution on chips and wafers |            |                                  |    |  |  |

| C T-Cell code                              |            |                                  |    |  |  |

| Acronyms                                   |            |                                  |    |  |  |

| Glossary of mathematical symbols           |            |                                  |    |  |  |

| Bibliography                               |            |                                  |    |  |  |

# **List of Figures**

| 1.1  | Elements in a bolometer                                             | 2  |

|------|---------------------------------------------------------------------|----|

| 2.1  | Model of a monolithic bolometer                                     | 6  |

| 3.1  | Schematic of the proposed device                                    | 14 |

| 4.1  | Process flow of the first fabrication run                           | 18 |

| 4.2  | Process flow for wet graphene transfer                              | 21 |

| 4.3  | Varieties of bolometers masks designs in the first fabrication run. | 23 |

| 4.4  | Test structures for graphene characterisation                       | 25 |

| 4.5  | Alignment crosses, dicing cross and exposure grid                   | 26 |

| 4.6  | Chips and wafer masks                                               | 27 |

| 4.7  | Graphene masks and graphene beams shapes                            | 27 |

| 4.8  | Delamination of the chromium-gold layer during wet etching          | 28 |

| 4.9  | Exposure non-uniformity across the wafer                            | 29 |

| 4.10 | Delamination of silicon dioxide on gold                             | 30 |

| 4.11 | Variations of the etch rate of silicon dioxide across the wafer     | 31 |

| 4.12 | Issues with graphene transfer, patterning and release               | 32 |

| 4.13 | Bolometers before graphene transfer                                 | 34 |

| 4.14 | Graphene beams obtained in the first fabrication run                | 35 |

| 4.15 | Process flow of the second fabrication run                          | 37 |

| 4.16 | Bolometer mask design in the second fabrication run                 | 38 |

| 4.17 | Improved exposure grid                                              | 39 |

| 4.18 | Improved alignment marks                                            | 40 |

|      | Additional issues with wet etching of thin layers                   | 41 |

|      | Lift-off tests to avoid fences                                      | 42 |

|      | Wiggly lines in lithography with the Heidelberg VPG200 tool         | 43 |

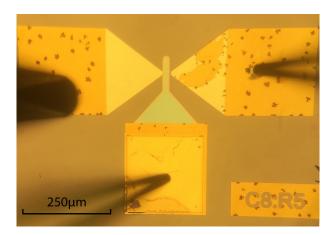

|      | Optical microscope image of the second run bolometers               | 44 |

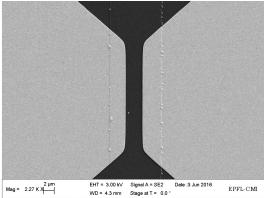

|      | Scanning electron microscope image of the second run bolometers.    | 45 |

## **List of Tables**

| A.1 | Detailed runsheet for the first fabrication run  | 63 |

|-----|--------------------------------------------------|----|

| A.2 | Detailed runsheet for the second fabrication run | 67 |

| B.1 | Types of bolometers with relative beam dimension | 69 |

THIS PAGE

WAS INTENTIONALLY

LEFT BLANK

### 1 | Introduction

This thesis presents the development of a 2D material-based bolometer. A lot of time was spent on the micro-fabrication of bolometers and therefore the majority of attention is focused upon this. The devices fabricated following this thesis could be used for a multitude of sensing applications, but in this report it was decided to follow the pathway of bolometers. However, before diving into technical explanations, it is probably worth spending some words elucidating what bolometers are and what the so called Two Dimensional materials (2D-materials) look like.

Bolometers (from Greek:  $\beta o \lambda o$ - means "thrown things" and  $-\mu \epsilon \tau \rho o \nu$  means measurer) are thermal detectors specifically designed for thermal radiation. This definition is not univocal and some people like to define bolometers as being sensors used to detect the power of electromagnetic radiation. In this report it is preferred to stick to the more restrictive former definition. A thermal detector is a device that can transduce a variation in temperature into a change of another physical property, which can be easily measured. Thermal radiation, instead, is a type of radiation emitted though the relaxation of thermally excited particles. Planck described the power spectrum of thermal radiation the first time in 1900 with the nowadays named Plank's law:

$$u(\lambda, T) = \frac{2hc^2}{\lambda^5} \frac{1}{e^{\frac{hc}{\lambda kT}} - 1}$$

(1.1)

where: u is the radiated power per area, solid angle and wavelength  $\lambda$ , T is the temperature, h is the Plank constant, c is the speed of light and k is the Boltzmann constant. The total emitted power can be deduced from Plank's law and takes the name of Stefan–Boltzmann law:

$$P = A\epsilon\sigma T^4 \tag{1.2}$$

where: A is the emitting surface,  $\epsilon$  is the emissivity and  $\sigma$  is the Stefan–Boltzmann constant. Plank's law is valid at thermal equilibrium for an idealised body

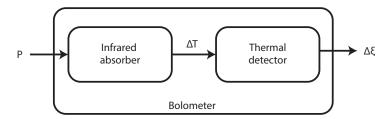

**Figure 1.1** – Elements in a bolometer. The incoming thermal IR radiation power P is absorbed by the IR absorber and converted into a temperature variation  $\Delta T$ . The thermal sensor transduces the temperature variation into a change in another physical quantity  $\Delta \xi$ , where  $\xi$  is often a voltage or current signal. Monolithic bolometers have the IR absorber and thermal sensor collapsed into one single physical element.

called "black body", which is a body that absorbs all incident radiation. Nevertheless, all bodies with a temperature different from the absolute zero emit thermal radiation. Plank's law tells that the power spectrum is uniquely defined for each fixed temperature. For instance, the peak of radiation for a body at room temperature (normally fixed at  $T_r \sim 295$ K) is around  $\lambda = 10 \mu$ m. Or again, the majority of radiation emitted by bodies with temperature close to room temperature lies in the InfraRed (IR) region of the electromagnetic spectrum. Hence, bolometers dedicated to thermal imaging of the world around us must be particularly good in absorbing the power of this portion of the electromagnetic spectrum. When this happens, the temperature of the sensing element of the bolometer changes and the signal transduced by the thermal detector is measured. Bolometers employed for thermal imaging such as night-vision goggles, infrared thermometers,...Operates in the range of  $\lambda = 8 - 14 \mu m$ , which correspond to the transmitted window by air for a body with temperature close to room temperature. From now on with the word "bolometer", it is meant those devices dedicated to IR radiation detection. Bolometers are made of two elements: the IR absorber which transduces the absorbed radiation into a temperature variation and the thermal sensor which further transduces the thermal variation into (most likely) an electrical signal as shown in figure 1.1. In other words, a bolometer is an electromagnetic radiation detector dedicated to thermal radiation (specific application) whose transduction uses a variation in temperature (specific working principle). Obviously, they can detect all types of radiations in the range of wavelengths they operate on, but bolometers are generally used for thermal radiation. Two main groups of bolometers exist. Cooled

Ι

bolometers, which operate at low temperature and uncooled bolometers. The former have the advantage of reducing thermal noise (Johnson–Nyquist noise), which is an intrinsic limiting factor of all materials. On the other hand, the latter are, more easily reduced to small sized Micro ElectroMechanical Systems (MEMS) for portable devices. The adjective "uncooled" delineate a device that does not use artificial methods to alter its own temperature. Hence, uncooled bolometers generally operate at room temperature. Many transduction methods can be used in bolometers. Some examples are: resistive bolometers, pyroelectric bolometers and ferroelectric bolometers. For instance, in resistive bolometers, the absorbed IR radiation causes a change in resistance that can be electrically detected in different ways. The simplest is to apply a voltage and measure how the current changes in function of incident radiation.<sup>1</sup>

The discovery of 2D-materials launches a whole new perspective for bolometers and bolometric measurements. In fact, these materials have extraordinary properties compared to their bulk relatives. 2D-materials belong to a larger category named nano-structural materials. The latter are defined as materials having at least one dimension at the nanometric scale. At this scale the electron wavelength is comparable to the material size. Hence, quantum confinement has an impact upon the band structure of materials and therefore upon their physical properties. Nano-structural materials are divided into three main categories:

- 0D-materials: quantum dots, nanoparticles binary arrays,...

- 1D-materials: nanowires, nanotubes, nanoribbons,...

- 2D-materials: nanosheets, nanoplates, nanowalls,...

It is generally meant that an xD material has nanoscale dimensions along 3-x directions. In this sense, dimensionality affects the physical properties of materials. Among 2D-materials one finds nanosheets. Nanosheets are further divided into three categories that define how 2D-materials are found in their bulk equivalent: layered van der Waals solids, layered ionic solids and surface assisted non-layered solids. The first are the most commonly known. Solids are organised in arrays of randomly oriented 2D-sheets bound to each other through van der Waals bounds. These 2D-materials can be obtained using different techniques: mechanical exfoliation, liquid exfoliation, epitaxial growth, Chemical Vapour Deposition (CVD),...Many 2D-materials have been isolated

<sup>&</sup>lt;sup>1</sup>This paragraph was strongly based on reference [1].

up to these days, among them one finds graphene (zero-gap semimetal), MoS<sub>2</sub> (semiconductor), Black Phosphorous (semiconductor) and hBN (insulator) [2].<sup>2</sup>

In this thesis, *CVD-graphene* is used as IR absorber and thermal sensor as it will be extensively explained later. It is important to understand from the beginning that it doesn't have to be graphene. In fact, the approach developed in this thesis is similarly applicable to all 2D-materials and the most favourable one need to be chosen depending on the detection technique employed by the bolometer. In summary, the goal of this report is to provide a method to model, fabricate and characterise 2D material-based bolometers and justify their technological importance.

<sup>&</sup>lt;sup>2</sup>This paragraph was strongly based on reference [3].

## 2 | Background

The purpose of this chapter is to give the necessary background to understand the importance of the steps undergone in this report as well as the motivation driving them. Many statements expressed in the introduction will be justified with a more scientific foundation.

Initially, a mathematical method to quantitatively compare bolometers performance will be presented. Then, the advantages of 2D-materials for bolometric measurements will be exhibited. Finally, the state of the art of bolometers and the fabrication techniques for graphene beams suspension will be discussed.

#### 2.1 Bolometers modelling

ultra It is useful to have a model for bolometers that allows to predict their behaviour and more importantly to compare their performance independently from the transduction technology employed. Some figures of merit will be discussed in the following sections. The model is developed in a rather generic way and should provide a strong fundamental understanding of the problem to help comprehend the results taken from literature.

#### 2.1.1 Mathematical model

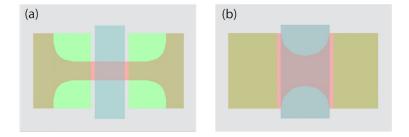

The mathematical model considers uncooled monolithic bolometers (thermal sensor and IR absorber are collapsed into only one element) in opposition to uncooled hybrid bolometers (separated elements). The physical situation is rather complicated, but it can be simplified into a very simple model [4, 5]. **Figure 2.1** shows all the important elements one needs to account for when he describes bolometers behaviour and performance. One of the critical factors determining bolometers performance is noise. The latter can be divided in two categories, namely: interfering noise and random noise [6]. The former consist in thermal fluctuation noises in the IR absorber due to the environment, such

**Figure 2.1 –** Model of a monolithic bolometer. Physical situation on the left hand side and simplified mathematical model on the right hand side. C is the heat capacity of the IR absorber and thermal sensor component, G has units of thermal conductance and  $P_s$  is the power source. In red the target signal to be measured.

as: background radiation, emitted radiation, convection and conduction to the environment. While, the latter consists in all intrinsic forms of noise such as: Johnson–Nyquist noise, Flicker noise (also known as Pink or 1/f noise), Shot noise and phonon noise. It is said that a device is working at its background limit if all interfering noises are reduced to radiation only.

The *response in temperature* of a bolometer to a radiative incoming power can be mathematically determined. It is worth reminding the definition of thermal conductance:

$G := \frac{\mathrm{d}P}{\mathrm{d}T} \tag{2.1}$

where: P is power and T is temperature. In what follows, it is supposed that the surface area of the IR absorber and thermal sensor element is small enough to have the same temperature across the whole surface (no temperature spatial distribution). In this example, the read-out is performed by applying a bias voltage  $V_{\rm bias}$  to the IR absorber and thermal sensor in order to measure a current change as a function of incoming radiation. The model structure is not modified by the read-out technique method. Temperature variations are considered to be small  $\delta T/T \ll 1$ . The first step toward modelling a monolithic bolometer is to define a generalised thermal conductance G = G(T) such that:

$$G = G_{\text{joule effect}} + G_{\text{conduction to substrate}} + G_{\text{conduction to environment}} + G_{\text{convection}} + G_{\text{emitted radiation}}$$

(2.2)

Τ

It can be shown that each term on the right hand side of the equation can be generally expressed as a power law:  $G(T) = G_0 T^{\chi}$  [4,7]. Some examples are:

$$G_{\text{emitted radiation}} = \frac{dP_{\text{emitted radiation}}}{dT} = 4A\epsilon\sigma T^3$$

(2.3)

$$G_{\text{joule effect}} = \frac{dP_{\text{joule effect}}}{dT} = -\frac{V_{bias}^2}{TR} \frac{R - R_L}{R_L + R} \alpha$$

(2.4)

where the first one has been obtained from Stefan-Boltzmann law (equation (1.2)), while details for the second equation can be found in reference [4]. In this formulae: A is the total emitting surface,  $\epsilon$  is the emissivity,  $\sigma$  is the Stefan–Boltzmann constant, R is the IR absorber and thermal sensor element resistance,  $R_L$  the internal resistance of the generator applying the bias voltage and  $\alpha$  is the Temperature Coefficient of Resistance (TCR). The power source term can be written as:

$$P_s = P_s(t) = P_{\text{thermal radiation}} + P_{\text{background}}$$

(2.5)

Basically, what was done by defining the generalised conductivity was bringing the dissipative terms on the left hand side of the thermal equation and reexpress them as conduction terms. Consider now that the temperature of the IR absorber and thermal sensor element is close to the substrate temperature  $T_s$  (equal if at thermal equilibrium with  $P_s = 0$ ), say  $T_s + \delta T$ . The equation describing the behaviour of the IR-absorber and thermal sensor element temperature  $T_s + \delta T$  is:

$$C\frac{\mathrm{d}(T_s + \delta T)}{\mathrm{d}t} + \int_{T_s}^{T_s + \delta T} G(T') \mathrm{d}T' = \eta P_s(t)$$

$$C\frac{\mathrm{d}(\delta T)}{\mathrm{d}t} + G(T_s)\delta T = \eta P_s(t)$$

(2.6)

where:  $\eta$  is the absorbance. The equation was linearised thanks to  $\delta T/T \ll 1$  and the thermal equilibrium condition  $dT_s/dt = 0$  was used. This equation is readily solved using Fourier analysis:

$$\delta T(t) = \frac{1}{2\pi} \int_{-\infty}^{\infty} \delta T(\omega) e^{i\omega t} d\omega$$

(2.7)

$$P_s(t) = \frac{1}{2\pi} \int_{-\infty}^{\infty} P_s(\omega) e^{i\omega t} d\omega$$

(2.8)

Inserting these two equations in equation (2.6) gives:

$$\delta T(\omega) = \frac{1}{G} \frac{1}{1 + i\omega \tau} \eta P_s(\omega)$$

(2.9)

where the time constant  $\tau = C/G$  was defined. Hence, the IR absorber of the bolometer behave as a low pass filter with cut off frequency  $f_c = 1/(2\pi\tau) = G/(2\pi C)$ . It is important here to notice the significance of C and G for thermal imaging as limiting bandwidth factors. <sup>1</sup>

The *sources of random noise* still have to be introduced in the model. Random noises are modelled as signals with zero average and no correlation  $v_n$ . A good way to deal with these kind of waveforms is to consider the mean square noise:

$$\overline{v_n^2} = \lim_{t \to \infty} \frac{1}{t} \int_{-t/2}^{t/2} v_n^2 dt'$$

(2.10)

When two of such signals are summed  $v = v_{n_1} + v_{n_2}$  and the mean square noise is computed the uncorrelation between noise signals implies that  $\overline{v_{n_1}v_{n_2}} = 0$  and therefore:

$$\overline{v^2} = \overline{v_{n_1}^2} + \overline{v_{n_2}^2} \tag{2.11}$$

However, noise signals are usually described by their spectral density function  $S_n(f)$  such that:

$$\overline{v_n^2} = \int_0^\infty S_n(f) \, \mathrm{d}f \tag{2.12}$$

In general, it can be difficult to have a mathematical expression of the spectral density, but some examples are [5,6]:

$$S_{\text{Johnson-Nyquist}} = 4kTR$$

(2.13)

$$S_{\text{phonon}} = 4kGT^2 \tag{2.14}$$

$$S_{\rm Flicker} \sim K + \frac{K'}{f}$$

(2.15)

where: k is the Boltzmann constant and K and K' are some constants. All the elements presented in this chapter are critical in the quantification of bolometers performance as it will become clearer later.<sup>2</sup>

#### 2.1.2 Figures of merit

There are many figures of merit that describe the performance of bolometers, the ones considered in this report are the responsivity ( $\mathcal{R}$ ) and the Noise Equivalent Temperature Difference (NETD).

<sup>&</sup>lt;sup>1</sup>This paragraph was based on references [4,8].

<sup>&</sup>lt;sup>2</sup>This paragraph was based on reference [6].

Τ

The *responsivity* is a function of the thermal radiation power. This quantity is defined for  $P_s = P_{\text{thermal radiation}}$  and it is computed as the derivative of the output voltage signal  $V_{\text{out}}$  with respect to the icident radiant power  $P_s$ :

$$\mathcal{R} = \frac{\mathrm{d}V_{\mathrm{out}}}{\mathrm{d}P_{\mathrm{s}}} \tag{2.16}$$

This is an example for a voltage read-out. If, for instance, the output signal is a current,  $V_{\text{out}}$  must be replaced with  $I_{\text{out}}$ . Thus, the units of  $\mathcal{R}$  vary depending on the read-out signal. This quantity can be seen as an output-input gain.

The *NETD* is defined as the necessary temperature change of an infinitely large black body emitting the source power  $P_{\text{thermal radiation}}$  to increase the average signal to noise ratio  $V_{\text{out}}/\sqrt{\overline{v_n^2}}$  (in case of voltage read-out) from zero to one. In other words it is the minimal temperature difference detectable by the bolometer. Mathematically:

NETD =

$$\frac{4F^2v_n}{\tau_0 A_D \mathcal{R} \left(\Delta P/\Delta T\right)_{\lambda_1 - \lambda_2}}$$

(2.17)

where:  $\tau_0$  is the optics transmittance,  $A_D$  total pixel area and  $F=1/2\sin\theta$  with  $\theta$  the angle which the marginal ray from the optics makes with the axis of the optics at the focal point of the image.  $(\Delta P/\Delta T)_{\lambda_1-\lambda_2}$  is the change in power per unit area radiated by a blackbody at temperature T, with respect to T, measured within the spectral band from  $\lambda_1$  to  $\lambda_2$ . This values for some intervals are listed in reference [1]. Since NETD  $\propto v_n$ , according to equation (2.11), the NETD values of different noise sources can be summed as follows:

$$NETD_{total}^2 = NETD_{noise source 1}^2 + NETD_{noise source 2}^2 + \dots$$

(2.18)

Both these two quantities can be experimentally measured and used for comparison between bolometric devices. The theoretical model will serve as a guideline to establish which parameters have an impact on the improvement of bolometers.<sup>3</sup>

#### 2.1.3 Discussion

Having a theoretical approach is advantageous because it allows to extrapolate what parameters are important to be tailored in order to improve the quality of bolometric measurement. Reference [7] offers a very similar, but more complete analysis than the one presented in the previous subsections. The model

<sup>&</sup>lt;sup>3</sup>This subsection was strongly based on references [1,8].

developed in that paper is valid for an array of resistive bolometers with bias current  $I_{\text{bias}}$  and voltage read-out. In a real situation many terms are often negligible, for instance, it is often true that  $G_{\text{emitted radiation}} \ll G_{\text{conduction to substrate}}$  or  $G_{\text{convection}} \approx 0$  specially for vacuum packages. What can be easily understood is that the improvement of bolometers rely mainly on three pillars: enhancement of the IR-radiation absorption, improvement of thermal isolation and reduction of the IR absorber mass and therefore reduction of the thermal capacity. A fourth important parameter that improve bolometric measurement is the increase of the measurement resolution on the read-out physical quantity (generally voltage). The latter is not part of the presented theoretical model. In Section 3 it will be stated how 2D-materials help improving bolometric sensors based on these pillars.

### 2.2 Advantages of 2D-materials

In the introduction of this work it was already discussed how dimensionality confer to 2D-materials extraordinary properties, very different from those of their bulk equivalents. In this section the properties of graphene will mainly be reviewed. The reason is that graphene was the 2D-material available when the fabrication process started and therefore it was the one used. It is reminded that the goal is not to claim that graphene should be employed, but to present an approach to fabricate and characterise 2D material-based bolometers independently of the material and justify their technological importance.

Graphene is a 2D-material, which was first isolated by mechanical exfoliation in 2004. One of the most widely used graphene type today is probably CVD-graphene, because it can be deposited in large sheets with still high levels of purity. Graphene is a monoatomic sheet of carbon atoms covalently bound in a honeycomb structure through hybridised sp<sup>2</sup> orbitals. Graphene is a zero band gap semimetal. It is interesting for bolometric applications because of its large absorption band extending through all the IR spectrum and its constant absorption strength on the whole spectrum [2, 9]. Graphene additionally exhibit extremely high carrier mobility at room temperature, extremely high Young's modulus ( $\sim$  1TPa) and excellent thermal conductivity (3000-5000 Wm<sup>-1</sup>K<sup>-1</sup>) [10]. Graphene is extremely flexible (can sustain elastic deformations of more than 20% and has high breaking strength of 42Nm<sup>-1</sup>) and its sheet resistivity can theoretically be as low as  $\sim$ 30 $\Omega$  $\square$  [10,11]. Additionally, the mass of graphene and all 2D-materials in general is extremely small due

to their nanometric thickness. Consequently, the heat capacity of these materials is dramatically affected and low (due to the small mass) [12]. But, on the other hand the specific heat of graphene is claimed to be slightly higher than that of graphite at room temperature and it is transparent to light (white light absorbance 2.3%) [10, 13]. Another interesting feature of graphene is the high in plane thermal conductivity (due to its strong sp<sup>2</sup> covalent bonds) and relatively low out of plane thermal conductance (limited by weak van der Waals coupling) [13]. This difference is highly affected by defects in the graphene sheet.

Nevertheless, the most attractive feature of 2D-materials is that their physical properties are extremely sensitive to external stimuli such as mechanical deformation, doping, external electric fields,...Thus, it possible to tune their properties at a highly controllable manner [10]. 2D-materials are naturally great candidates for Nano ElectroMechanical Systems (NEMS) applications. The isolation of graphene was quickly followed by many others such as: MoS<sub>2</sub>, Black Phosphorous, hBN...And they all are interesting as they show extraordinary and tunable properties. The list of 2D-materials grows with time and each of them could be a good candidate for a particular bolometric application. It is therefore hugely profitable to have a generic approach to fabricate 2D material-based bolometers independently of the chosen 2D-materials.

#### 2.3 State of the art

A general trend of the last many years in the electronics market has been miniaturisation and portability of electronic devices. This trend supported uncooled resistive bolometers as being easily reducible in size and low in energy consumption. Still most modern resistive bolometers derive from the pioneering Honeywell silicon microstructure developed in 1982 [1]. The latter is made of a suspended membrane over the electronics. The membrane is made of silicon nitride (the IR absorber) and sandwiches a thin film of vanadium oxide (having a large TCR, it acts as the thermal sensor). The Honeywell bolometer is an hybrid bolometer having physically separated IR absorber and thermal sensor. Many variations of this structure exist nowadays but the basic principle stays very similar. NETD achieved are of the order of  $\sim 50$ mK. Using suspended membranes as a double advantage. First it reduces thermal losses to the environment and substrate and second a Fabry-Pérrot cavity can be created with the substrate in order to increase absorption. For IR detection in the spectral

A more recent innovation is the substitution of the bi-functional membranes of the Honeywell structure with ultra-thin  $Pt/Al_2O_3$  films, where absorption and sensing are performed by one single element [14]. These structures have two interesting advantages: first thermal isolation (thinner membranes have lower conductance) and second the absorption can be tuned by varying the film thickness [15, 16]. NETD values of 163mK and time constants of 1ms were achieved with this technique.

2D-material based bolometers can take the form of suspended beams. It is therefore interesting to bring to light a study done in 2010 on a large array of suspended CVD-graphene beams found in reference [17]. They used two distinct fabrication techniques for the beams. The first were fabricated by transferring pre-patterned graphene beams onto trenches, while the seconds were fabricated by transferring unpatterned graphene, patterning the graphene on the substrate, depositing and patterning gold on top of graphene to generate electrical contact and releasing the graphene by wet etching and critical point drying. This technique is probably the most often employed to create graphene beams up to these days (see for instance [18–21]). They further claim and demonstrate that the resonance frequency of these beams can be modulated by either gate voltage or temperature. They additionally state that buckling, ripples and variable compression/shear/tension are the sources of differences in resonance frequencies among geometrical identical beams.

One of the latest published papers about uncooled thermal sensing using 2D-materials is presented in reference [21]. In their approach they exploit the tunable seedback effect of graphene for demonstrating thermal imaging. They claim to achieve responsivities  $\mathcal{R}$  of the order of 7-9V/W at  $\lambda=10\mu\mathrm{m}$  and time constant  $\tau=23\mathrm{ms}$ . The carrier mobility of graphene seems to be the bottleneck of the intrinsic improvement of NETD. In fact, it is stated that improvements in the graphene transfer technique could enormously improve the carrier mobility and consequently reduce the NETD to values in the range of 30-150 mK. Currently, the experimentally measured NETD was 30-40K and since the latter is dependent on external factors such as the optics, it is claimed that a reduction to 1K could be reached only from extrinsic optimisation. Back in 2007, calculations showed that NETD values as low as 200mK can be achieved at room temperature and atmospheric pressure [7].

<sup>&</sup>lt;sup>4</sup>This paragraph was based on references [1,8].

## 3 | Design and motivation

This chapter is dedicated to the presentation of the schematic and working principle of the proposed device. Firstly, the schematic will be described and secondly the advantages with respect to the state of the art will be discussed.

#### 3.1 Design schematic and working principle

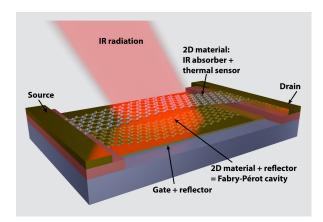

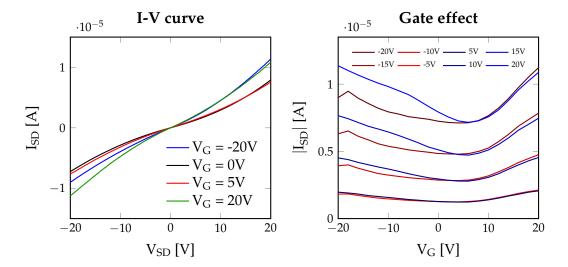

**Figure 3.1** shows the proposed device. A suspended graphene beam is connected to two gold electrodes named source and drain. A gold gate electrode for electrostatic doping of the graphene is placed under the graphene beam and forms a Fabry-Pérot cavity with the graphene beam. The graphene beam acts as the IR absorber and thermal sensor. Two different types of red-out can be employed with this bolometer. The more traditional one is through changes in beam resistance. While, the second utilises shifts in the beam resonant frequency.

#### 3.1.1 Resistive read-out

The resistive read-out is the traditional way bolometers works. In this design the IR-radiation is absorbed by the graphene sheet. Absorption at the wavelength of interest is enhanced by the Fabry-Pérot cavity. The IR-radiation infer to the graphene a temperature increase dT proportional to its power and therefore a resistance variation dR can be detected:

$$dR = R\alpha dT \tag{3.1}$$

where:  $\alpha$  is the TCR. A bias current can be applied in order to transform the variation in resistance into an easily measurable voltage variation. For this type of read-out, high values of TCR are favourable to increase responsivity. Graphene is not the most suitable material for this type of read-out method as it has low

**Figure 3.1** – Schematic of the proposed device. A graphene beam is suspended between two electrodes and functions as the IR absorber and thermal sensor. A gate electrode is placed under the graphene and create a Fabry-Pérot cavity with the graphene beam.

TCR coefficient  $\alpha = -1.2 \cdot 10^{-3} \text{K}^{-1}$  [22]. For sake of comparison vanadium oxide has a TCR coefficient of  $\alpha = 65 \cdot 10^{-3} \text{K}^{-1}$  [23].

#### 3.1.2 Resonant frequency read-out

Frequency read-out is a more innovative method of detecting variations in temperature of the graphene beam. One way to measure the resonant frequency is to apply a constant source-drain voltage and a AC/DC voltage to the gate. The AC component is used to excite the graphene beam. In a continuum model the resonant frequency of a pinned-pinned beam, which is a good first approximation of the clamped-clamped beam, is given by [17,24–27]:

$$f_{\text{res,n}} = \frac{\pi n^2}{2L^2} \sqrt{\frac{EI_y}{\rho_m A_c}} \sqrt{1 + \frac{\sigma_{\mathcal{T}} A_c L^2}{EI_y \pi^2 n^2}}$$

(3.2)

where: n is a positive integer, E is the Young's modulus,  $\rho_m$  is the beam mass density,  $I_y$  is the second moment of inertia with respect to the y-axis (set along the beam width),  $A_c$  is the beam cross-sectional area, E is the beam length and  $\sigma_T$  is the tensile stress. When tensile stress dominate  $(\sigma_T A_c L^2 / (E I_y \pi^2 n^2) \gg 1)$  the equation simplifies. If the explicit dependences on temperature T and DC gate voltage  $V_G^{DC}$  are introduced, one finds:

$$f_{\text{res,n}}\left(T, V_{\text{G}}^{\text{DC}}\right) = \frac{n}{2L} \sqrt{\frac{\sigma_{\mathcal{T}}\left(T, V_{\text{G}}^{\text{DC}}\right)}{\rho_{m}\left(T\right)}}$$

(3.3)

I

For a beam with rectangular cross section of thickness t, the tensile stress dominance condition can be re-expressed geometrically:  $\epsilon_T\gg t^2\pi^2n^2/(12L^2)$ , where  $\epsilon_T$  is the tensile strain. The tensile stress depends on the DC gate voltage (initial displacement offset) and on the temperature of the beam. In fact, when the graphene beam is heated by the IR-radiation it has tendency to contract, hence increase the tensile stress and finally cause a shift in resonant frequency. This effect is further enhanced by the substrate expansion<sup>1</sup>. Mechanical deformations cause proportional changes in the graphene electrical resistance [28]. Hence, the resonant peak is reflected in the current measurement and shifts of the current peak can be detected by Fourier analysis. Similarly to the resistive read-out, it is favourable to have high linear expansion coefficients. The one of graphene is  $\alpha_T \approx -8 \cdot 10^{-6} {\rm K}^{-1}$  [26, 29]. For sake of comparison for gold one finds  $\alpha_T \approx 14 \cdot 10^{-6} {\rm K}^{-1}$ .

### 3.2 Significance of the study

Bolometers fabricated from 2D-material have a great perspective for the future. Having suspended sheets improves thermal isolation to the surroundings and most of the heat loss is dictated by conduction to the anchors. The low beam mass enormously reduces the thermal capacity of the IR-sensor and therefore increases the bandwidth of the bolometer. Another fundamental aspect of 2D-material is the high level of tunability of their properties.

The absorbance of some of these materials may be low (for instance the one of graphene being 2.3% for white light), but this property can be electrostatically enhanced [30]. The electrical conductivity  $\sigma_e$  of the beam can be tuned by applying a DC gate voltage  $V_G^{DC}$  (field effect) [31,32]. Consequently, the absorption being a function of the electrical conductivity  $A(\sigma_e)$ , it can be maximised by impedance matching [16]. Absorption can be further increased at a specific wavelength by the Fabry-Pérrot cavity.

Graphene on its side is interesting for resonant frequency read-out due to its mechanical properties. In fact, graphene is extremely flexible, it can sustain large elastic deformations and has very high breaking strength. This innovative read-out method could have a positive effect on the device dynamic range.

The fabrication of 2D-material suspended beams is often accomplished with the following fabrication steps: (i) 2D-material transfer on sacrificial layer, (ii)

<sup>&</sup>lt;sup>1</sup>Assuming linearity:  $\sigma_{\mathcal{T}}(T, V_{G}^{DC}) = \sigma_{\mathcal{T},0} - E(T)(\alpha_{T,\text{graphene}} - \alpha_{T,\text{substrate}})(T - T_r) + \sigma_{\mathcal{T}}(V_{G}^{DC})$ , where  $\sigma_{\mathcal{T},0}$  is the initial tensile stress [24].

2D-material patterning, (iii) evaporation of gold on top of the 2D-material, (iv) patterning of source and drain electrodes and (v) release of 2D-material by sacrificial layer etching (usually wet etching followed by critical point drying). The fabrication proposed in this project has an advantageous difference: (i) evaporation and (ii) patterning of gold source and drain electrodes on sacrificial layer, (iii) graphene transfer, (iv) graphene patterning and (v) release of graphene by sacrificial layer etching (vapour HF). Graphene transfer is maximally delayed in the fabrication process. This is advantageous because any fabrication step done on top of graphene can significantly reduce graphene quality and graphene to electrode contact [33]. This is generally true for all 2D-materials. In this approach graphene will bind to the substrate through van der Waals forces.

### **4** | Fabrication

The goal of this chapter is to describe how the resonator described in the previous chapters can be transformed into a physical device. Two similar fabrication run were performed and they will be both described with a similar structure. The first part is dedicated to the description of the process flow and the microfabrication steps, while in the second part the mask and wafer layout will be discussed and justified. For each run, an extended description of the issues encountered is delineated and a brief summary and conclusion presented. Toward the end of the chapter, the devices obtained from the two runs will be compared. Detailed runsheets and recipies can be found in Appendix A and devices distribution on wafers and chips are shown in Appendix B.

#### 4.1 First fabrication run

The purpose of the first fabrication run is primarily to reach the end of the process flow and complete all the necessary trainings needed to use the tools in the cleanroom. Few concerns will be devoted to the optimisation within the same run. The process flow will then be globally optimised for the second run. This pioneeristic approach allows to have both a larger picture and a more complete feedback of the main problems of the fabrication as a whole. Additionally, it makes possible to rapidly perform repetitive tests for non-conventional fabrication steps such as graphene patterning and graphene release.

#### 4.1.1 Process flow

In this section the process flow of the fist fabrication run will be discussed in detail. The problems and issues encountered will be discussed in Section 4.1.3 and they give a strong feedback and solid starting point for the second fabrication run. The entire runsheet with all recipes used at the Center of Micronanotechnology (CMi) facility at Ecole Politechnique Fédérale de Lausanne (EPFL) can be found in Appendix A.

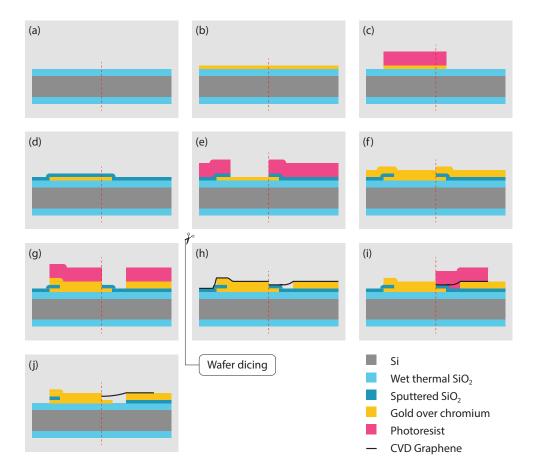

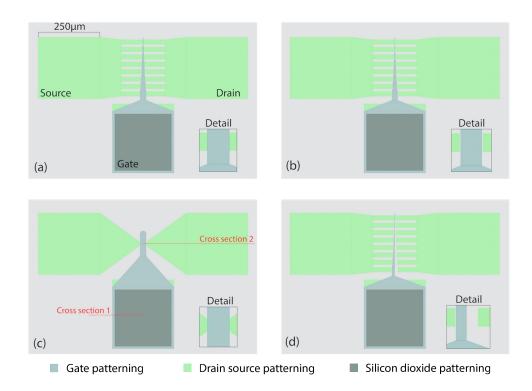

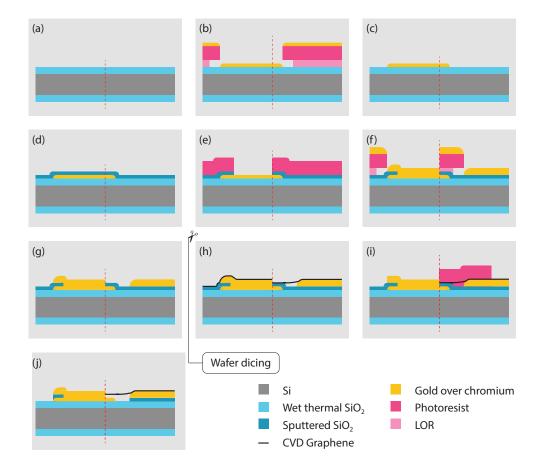

**Figure 4.1** – First fabrication run process flow. All figures are split into two in order to avoid redundant information due to the symmetry of the devices. In fact, the dashed red line can be seen as an axis of symmetry. On the left-hand side the schematic representation of the cross section 1 shown in **figure 4.3**, while the cross section 2 is represented on the right hand side. (a) The starting point is a silicon wafer with wet thermal silicon dioxide on both sides. (b) A layer of Chromium/Gold is evaporated on one side. (c) The gold is patterned with a lithography step and wet etching. (d) A layer of silicon dioxide is sputtered on the wafer. (e) Patterning of the oxide with lithography and wet etching. (f) A second layer of Chromium/Gold is evaporated on the wafer. (g) Gold patterning via lithography and wet etching. At this stage the wafer are ready to be diced into single 10mm squared chips. (h) Graphene transfer. (i) The graphene is patterned through a lithography step and oxygen plasma etching. (j) Vapour HF etching of the silicon dioxide and graphene release.

I

The *process flow* is illustrated in **figure 4.1**. Suspended beams of graphene with electrodes will be realised through a four lithography process. First gold gate electrodes are defined via wet etching using resist as etch mask. A sacrificial oxide layer is deposited and patterned in Buffered HydroFluoric acid (BHF) using resist as etch mask. Source drain electrode are defined in a similar way as the gates. After dicing of the wafer graphene is transferred to individual chips and patterned in an O<sub>2</sub> plasma using resist as etch mask. Finally vapour HydroFluoric acid (HF) is used to release the patterned graphene.

The devices are fabricated on  $\emptyset$ 100mm Single Side Polished (SSP) test p-type (0.1-100 $\Omega$ cm) wafer with 285nm of wet thermal silicon dioxide (SiO<sub>2</sub>) on both sides. The same wafers are used for other purposes than this fabrication and this specific oxide thickness is chosen to guarantee a good visibility of graphene on top of these wafers under white light [34]. In this project the silicon dioxide thickness is arbitrary and the oxide merely serve as dielectric. The first step is to evaporate a layer of 5nm of chromium and 25nm of gold on the front side of the wafer. Thin layers of metal are preferred to avoid the topography to have a negative impact on the next fabrication steps. It is well known that the gold has very poor adhesion on silicon dioxide substrates and therefore a thin layer of chromium is mandatory to promote its adhesion and prevent delamination.

The first lithography step is then performed and the gate layer is patterned into the Cr/Au layer by wet etching. The Critical Dimension (CD) of this lithography step is  $2\mu$ m. The reason for choosing wet etching rather than ion beam etching or lift-off is a matter of decreasing the risk of having fences at the gold edges, while plasma etching was not an option for gold with the tools at our disposal. Having smooth gold edges will be crucial when the drain and source pads are patterned. In fact, fences would enormously increase the risk of breaking the graphene. All dicing marks and alignment marks for single chips and wafer are also patterned during this step. The advantage of using gold is that it does not oxidise.

A layer of 250nm, or  $2.5\mu m$  silicon dioxide is sputtered on the wafer in argon atmosphere (referred to as low quality SiO<sub>2</sub>) at room temperature. The thin layer of SiO<sub>2</sub> enhances the gate effect on the graphene layer and has a Fabry-Perrot resonance in the short infrared, while a  $2.5\mu m$  thick layer increases the Fabry-Perrot effect in the long infrared region, which correspond to the peak of thermal radiation at room temperature.

The silicon dioxide is then patterned with a second lithography step and wet etching in BHF. The CD of this lithography step and the alignment are not

critical. The patterning of SiO<sub>2</sub> is necessary to guarantee the electrical contact between the gate layer and the gate pad on the drain and source layer. The silicon dioxide layer will then be used as a sacrificial layer for graphene release. This is a well known technique, but sputtered silicon oxide is rarely used for this purpose [35]. However, it was the best choice possible, since the majority of the tools available for SiO<sub>2</sub> deposition did not accept substrates with gold. The above mentioned sacrificial layer thicknesses were not successfully obtained because no deposition rate measurement test was done and the deposition rate provided by the CMi staff was not accurate (details in Appendix A).

A second layer of 25nm/100nm Cr/Au is evaporated on the wafers. This gold thickness prevents gold from delaminating during wire bonding and guarantees the mechanical support when probing. This layer was then patterned similarly to the first metal layer, but using a different etchant for chromium as suggested in Section 4.1.3. A third lithography step is therefore needed before wet etching the Cr/Au thin film. The CD of this lithography step is not critical, but the maximal error in the alignment should preferably be smaller than 500nm. Nevertheless errors in the range of 500nm -  $2\mu$ m should not compromise the working principle of the bolometers.

At this stage, the wafers are ready to be saw diced into  $10\text{mm} \times 10\text{mm}$  chips. This is necessary because graphene films are only  $7\text{cm} \times 7\text{cm}$  and wet graphene transfer is better performed on small substrates. Furthermore, it is often found in literature that graphene is transferred before patterning the drain and source pads and the gold is actually deposited on top of graphene (see for instance [18–21]). This approach is disfavoured for two reasons. First, graphene quality is affected at each fabrication step and therefore it is profitable to delay the graphene transfer as much as possible [33]. Second, transferring the graphene earlier implies dicing the wafer earlier and consequently increase the number of fabrication steps on single chips and this would necessarily slows the fabrication down.

The graphene foils are transferred to the 10mm square chips following the process flow illustrated in **figure 4.2**. This procedure will be elucidated in more detail later in this section. After the transfer is completed, a fourth lithography is then performed in order to pattern the graphene in oxygen  $(O_2)$  plasma as suggested in references [36,37]. The etching is done at 200W for 30s in a chamber with a pressure of 0.5mbar and an  $O_2$  flow of 200sccm.

In the last fabrication step the graphene is released with a vapour HF etch. Wet etching is not possible at this stage because the liquid surface tension would

I

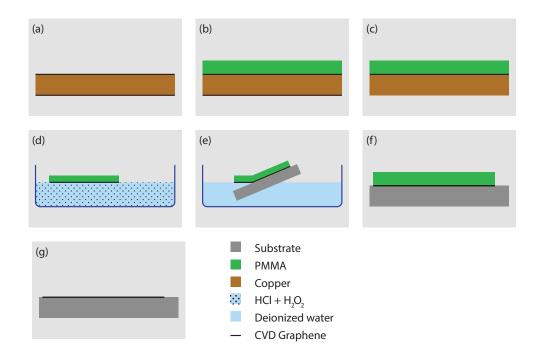

**Figure 4.2** – Wet graphene transfer on a substrate. (a) The starting point is a copper thin film with CVD graphene on both sides. (b) A PMMA layer is spin-coated on top of the foil. (c) Graphene on one side of the copper foils is etched by oxygen plasma. (d) Copper is etched in a HCl+H<sub>2</sub>O<sub>2</sub> solution. (e) The PMMA and graphene foil is transferred to the substrate using the fishing method. (f) The graphene is attached to the substrate prevalently by van der Waals bounds. (g) The PMMA is dissolved in acetone.

cause the graphene beam to collapse and stick to the substrate unless critical point drying is performed, but this would be more delicate and lengthy. During etching the chips are heated up to  $60^{\circ}$ C. At this temperature the difference in etch rate between wet thermal silicon dioxide and sputtered  $SiO_2$  is greater than at room temperature [38,39]. This increase in selectivity makes it easier to stop etching at the interface between the two silicon dioxide types. Moreover, the etch rate decreases with temperature and therefore it becomes easier to control the procedure at higher temperatures. It should be kept in mind that it is quite difficult to predict the etch rate of vapour HF specially because it is not linear in time. Another possibility could still be to release the graphene via wet etching and critical point drying but this technique was not tested during this project.

The wet graphene transfer process flow is shown in **figure 4.2** [40]. The Technical University of Denmark (DTU) is the provider of  $7 \text{cm} \times 7 \text{cm}$  copper foils with

CVD graphene on top. From the very beginning, it is advised to mark the front side of the foil with a marker, for instance with two dots. The foil may need to be gently flattened with the help of two wipes before starting the transfer.

Initially, the film is placed on a PolyDiMethylSiloxane (PDMS) coated wafer. The wafer with the foil is coated with a Poly-Methyl MathAacrylate (PMMA) film as follows. First the entire copper film must be covered with an 8% PMMA solution (8g of PMMA in 100ml of Anisole solvent). The wafer is spun for 1min with an acceleration of 1000rpm/s up to a constant speed of 1000rpm. Finally, the wafer is baked at 80°C under a lid for 20min to evaporate the solvent. The PMMA serve as mechanical support for the graphene. With the help of a scalpel, the foil can be removed from the wafer.

In order to enhance the copper etching, the graphene layer not in contact with the PMMA is etched in oxygen plasma at 50W (**figure 4.2c**). The foil can be now chopped in smaller pieces as large as the target chips size on which they have to be transferred to (approximately  $0.7\text{mm} \times 0.7\text{mm}$ ). The copper etching is done at  $60^{\circ}\text{C}$  in 5% HCl with 10 drops of  $\text{H}_2\text{O}_2$  per 100ml of HCl. The small foils are left floating in the solution with the copper facing the solution until the copper is completely etched.

With the help of a glass slide the PMMA-graphene foils are moved to a deionised water bath for rinsing. The technique used is called fishing and consist in exploiting the liquid surface tension to stick the foil onto the glass slide and prevent it from rolling on itself during transfer. In the meantime the target chips are cleaned in acetone and IsoPropyl Alcohol (IPA). Then, the PMMA-graphene foils are transferred onto the target chips using the fishing method as shown in **figure 4.2e**. The chips are then baked at 60°C for 3 hours. Finally, the PMMA is removed by submerging the chips in three acetone baths (the first one overnight). They are finally rinsed with IPA and left to dry.

#### 4.1.2 Mask design

The mask design is described with a bottom-up approach. First, the elementary mask building blocks are described and only then it is shown how they are gathered into chips and wafers. All masks designs have been drawn using a software known as L-Edit. Four lithography steps are needed in the process flow, hence four layers will be designed: gate patterning, silicon dioxide patterning, drain source patterning and graphene patterning.

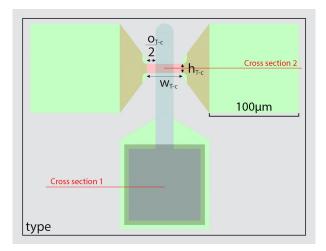

The fundamental elements of the mask and therefore the first to be presented

ı

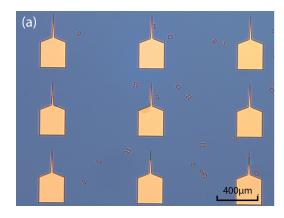

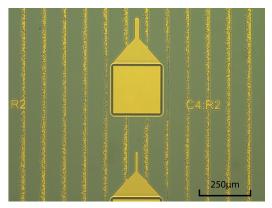

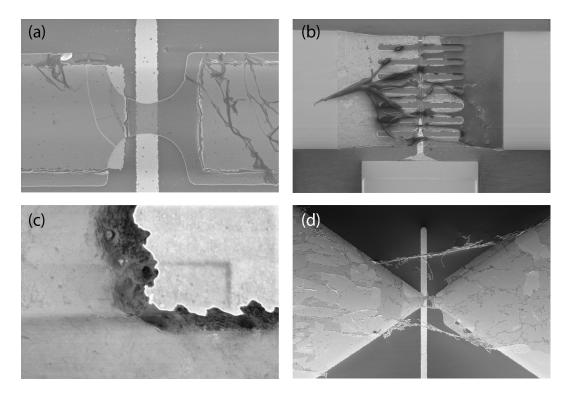

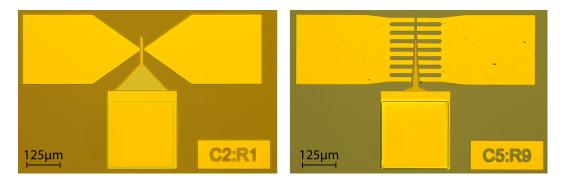

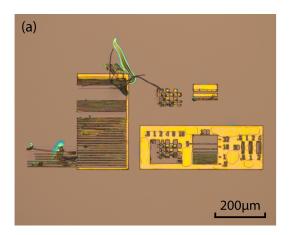

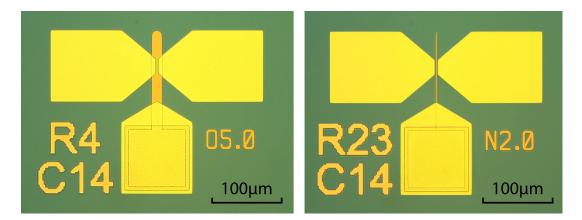

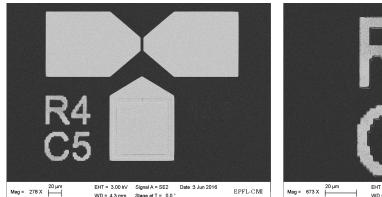

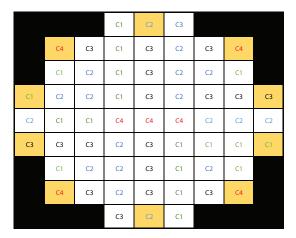

**Figure 4.3** – Varieties of bolometer masks in the first fabrication run. (a) Zig-zag design with gate tip as wide as the gap between the source and drain electrodes, named EGT design. (b) Zig-zag design with gate tip slightly narrower than the gap between the electrodes, named NGT design. (c) Single-beam design with gate tip overlapping with the electrodes, named OGT design. Many similar designs of this type are present on the chips with varying gap width  $L_g$  (c) Zig-zag design with gate tip covering only half of the gap between drain and source, named HGT design. Cross sections 1 and 2 were used earlier to describe the process flow.

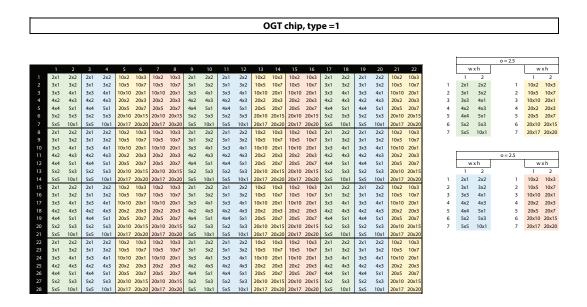

are the *bolometers* themselves. The maximal dimensions of suspended graphene beams that can be achieved with the fabrication technique employed in this project were unknown and therefore many different dimensions needed to be explored. For this reason, all designs shown in **figure 4.3** have different gaps  $L_g$  between the drain and source electrodes allowing different graphene beam lengths. The designs are named: (a) Equal Gate Tip (EGT), (b) Narrow Gate Tip (NGT), (c) Overlapping Gate Tip (OGT) and (d) Half Gate Tip (HGT). The width of the graphene beam is later tailored when the graphene mask is designed. The zig-zag designs (a), (b) and (d) allow to test many graphene beams lengths, once at a time, on a single device by simply changing the graphene mask. This is a great advantage because once the graphene dimensions are optimised, the to-

tality of devices can be used. However, design (c) has an additional parasitic capacitance between the drain-source electrodes and the gate tip. The latter would be much larger for an equivalent zig-zag design, consequently it is a better choice to adopt a single beam design and repeat it on the chips for different values of  $L_{q}$ . All bolometers types can be found in Appendix B. The gate tip metal thickness is the cause of a bump between the source and drain electrodes. The position of this bump could affect the graphene transfer and release procedure and therefore the three designs (a), (b) and (c) were made (the bump can be seen in figure 4.24). Each one of these designs has the bump in a different position as a consequence of the gate tip position with respect to the drain and source electrodes. The HGT device will be gathered on the wafer with the test structures that will be described later. When the bolometer is used as a resonator, the HGT design should make it easier to excite the graphene beams in their even modes. At this point, it should be reminded that each of the colour in these figures represent a mask for a photolithography step. The CD of all layers combined measures  $2\mu$ m and the fabrication require a total of four lithography steps (the graphene lithography mask is omitted from figure 4.3 and discussed later).

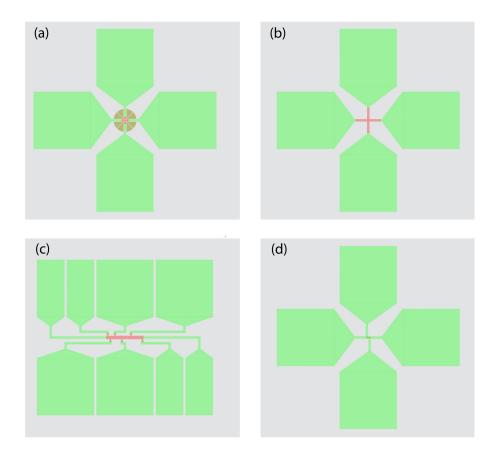

Another useful feature on the mask are the test structures. These structures not only allow to measure some of the electrical properties of graphene, but they also allow to estimate the graphene quality and to some extent the quality of the graphene transfer procedure. In fact, many of these electrical properties vary in function of the ripples on the graphene sheet, the number of defects in the graphene, the cleanliness of graphene and much more. Hence, by comparing these properties with the intrinsic theoretical values of pure graphene we can establish the quality of this 2D-material. Nevertheless, the primary usage of the test structures is to measure the contact resistivity  $\rho_c$  between gold and graphene and the sheet resistivity  $\rho_s$  of graphene. The graphene must be suspended in order to prevent these electrical properties from being affected by the insulating substrate on which it lie. Figure 4.4 doesn't exhaustively show all test structures designed, but only the principal ones. On the chips there will be some variations in shapes and dimensions, but not in physical working principle. The sheet resistivity can be estimated by using the van der Pauw method and the structures (a) and (b) [41–43]. The contact resistivity can be estimated with the Cross Bridge Kelvin Resistor (CBKR) structure (d) following reference [44]. These two measurements can be combined by using the Transmission Line Measurement (TLM) structure (c) [42,45,46].

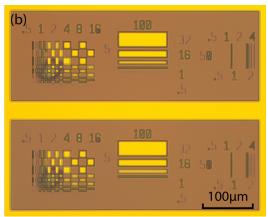

**Figure 4.4** – Test structures for graphene characterisation. (a, b) Van der Pauw cloverfild and Greek cross structure for measuring the sheet resistivity and the Hall coefficient. (c) TLM for measuring sheet resistivity and contact resistivity. (d) CBKR for measuring contact resistivity.

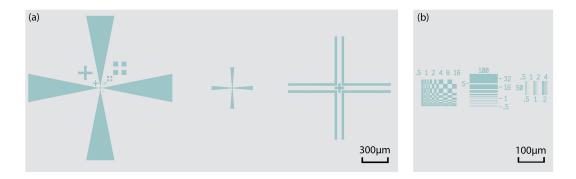

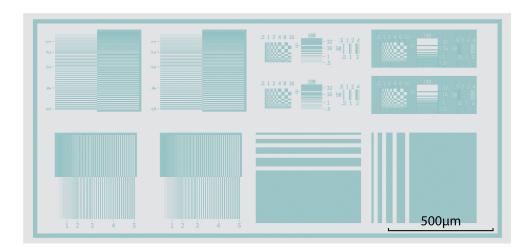

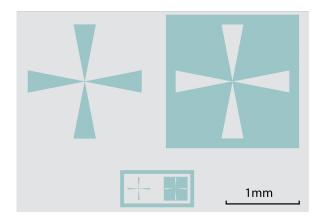

Some *miscellaneous structures* will be now discussed. **Figure 4.5a** shows the alignment marks for lithography steps on wafers and chips and alignment marks for dicing of wafers into chips. These marks may strongly vary depending on the tools used and if automatic alignment is available on the image processing techniques employed by the tools softwares for automatically finding the crosses centres. The exposure grid shown in **figure 4.5b** was used to perform exposure tests on dummy wafers allowing to determine the optimal lithography parameters and it had equally been placed on the processed wafers and chips to verify the quality of the lithographies.

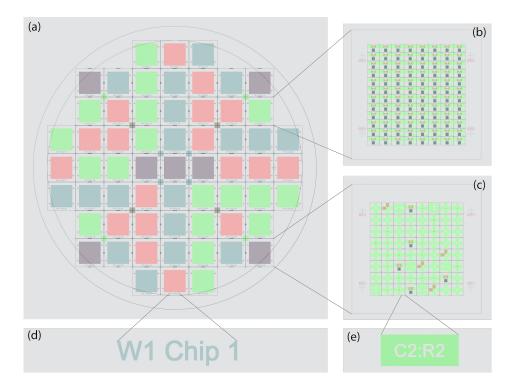

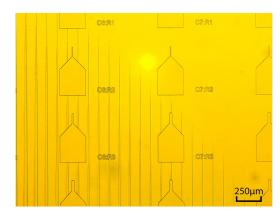

**Figure 4.6** shows how all the features presented so far are *organised into chips* and into the final wafer design. There are four types of 10mm square chips. The first three contains each only one of the designs shown in **figure 4.3a,b,c**, while

**Figure 4.5** – (a) Starting from the left: alignment cross for the lithography steps on the wafer, alignment cross for the alignment of lithography steps on the chips and dicing cross for saw alignment. (b) Exposure grid for exposure tests and for verifying the quality of lithographies on the processed wafers and chips [47].

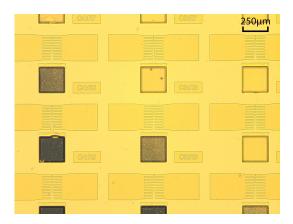

the fourth contains the test structures of figure 4.4 and the HGT bolometer of figure 4.3d. The detailed distribution of the bolometers and test structures on the chips can be found in Appendix B. When placing the bolometers designs types on the mask it should be kept in mind that the graphene transfer is better at the centre of the chip. Each chip contains 96 bolometers and each bolometer is labeled by a row (R) and column (C) number, this makes is easier to identify them when observed under the microscope. Additionally, each chip has a label indicating the wafer number and a chip number. Each wafer contains 62 chips. Letters in the chip labels are  $\sim 500 \mu m$  tall allowing reading with the naked eye. This is comfortable when handling the chips after dicing. Thus, each bolometer is uniquely identified by a set of numbers: wafer number, chip number and column and row numbers. This numbering method is very useful because, for instance, some of the processes are not uniform across the wafer surface and therefore knowing the region where the bolometer comes from could give some insight on its properties. Both the wafer and the chips are equipped with the necessary exposure grids, alignment marks and dicing crosses. The chips are not randomly organised on the wafer. As it was mentioned earlier, the properties of the chips varies across the wafer surface and therefore it is preferred to place an equal number of EGT, NGT and OGT chips at each fixed distance from the wafer centre. Seven of the 62 chips on the wafer contains only test structures, three are in the centre and four on the edge.

The last structure to be discussed concerning the design is the *mask used for* graphene patterning. As already mentioned before, the suspension of graphene

I

**Figure 4.6** – (a) Simplified mask of the Ø100mm wafer. Each coloured square correspond to a different chip type. (b) Chip containing the bolometers (EGT, NGT or OGT). Each chip accomodate only one of the three types of bolometers. (c) Chip containing the test structures. (d) Label enumerating the wafer number and the chip number. (e) Label showing the column (C) number and row (R) number of the bolometer. The wafer and chips additionally contains the following structures: exposure grid for lithography steps verification, squares for metal and oxide thickness measurements, alignment marks for lithography layers, dicing crosses and alignment crosses and exposure grid for single chips.

**Figure 4.7** – Graphene masks for a NGT design. (a) Chronologically first design tested for the graphene beam. (b) Improved graphene beam design with better mechanical support. In red the graphene mask, in blue the gate tip and in green the drain and source electrodes.

**Figure 4.8** – Delamination of the chromium-gold layer on silicon dioxide during wet etching with the commercial chromium etchant: ready-to-use CR7 (NH<sub>4</sub>)<sub>2</sub>Ce(NO<sub>3</sub>) + HClO<sub>4</sub> and gold etchant: commercial ready-to-use Kl(25g/l)+I<sub>2</sub>(12g/l). (a) Only tiny structures were delaminating. (b) A rim was also generated during etching.

beams through the fabrication techniques used in this project has still to be explored and therefore the optimal beam shape is still unknown. Many designs will be tested to try having the best mechanical properties and preventing the beams from collapsing. The designs shown in **figure 4.7** are two examples of such. The contact surface area between the gold pads and the graphene must be large in order to minimise the contact resistance negative effects.

#### 4.1.3 Issues encountered and solutions

#### Delamination of chromium-gold layer

The first problem encountered during the first fabrication run was the delamination of chromium-gold tiny structures from the thermal oxide of the wafer. This issue was first encountered after resist stripping after the first wet etch (3.x in table A.1). The evaporated metal layer was 5/25 nm of Cr/Au. Figure 4.8 shows how the bolometers labels delaminated and flew all around the wafer. To compensate for the missing labels, they were re-drawn in the source-drain layer. The same delamination happened with some of the gate tips. Another minor problem during this fabrication step is the rim that can be seen in Figure 4.8b. In order to avoid slowing the fabrication down, the same issues were regenerated on a test wafer and possible solutions were explored on the test wafer instead of the processed wafers.

The test wafer had a pre-patterned layer of 10/100 nm Cr/Au on 285nm of

**Figure 4.9** – Exposure non-uniformity across the wafer. The exposure grid showed a very good exposure in the centre of the wafer, while under-exposure stripes appeared on the bottom edge of the wafer. These stripes result in gold stripes after wet etching.

thermal silicon dioxide. To prevent similar problems for the source-drain layer, different etching of 10/100 nm Cr/Au were tested: (i) in the commercial ready-to-use CR7 (NH<sub>4</sub>)<sub>2</sub>Ce(NO<sub>3</sub>) + HClO<sub>4</sub> as was done with the processed wafer, (ii) in the ready-to-use solution: Cr selective over Cu KMnO<sub>4</sub> + Na<sub>3</sub>PO<sub>4</sub> and (iii) in oxygen peroxide (H<sub>2</sub>O<sub>2</sub>) at 50° [48]. The ready-to-use CR7 etchant showed delamination of tiny structures but no rim, oxygen peroxide showed no etching of chromium at all and the Cr selective over Cu etchant showed no delamination and no rim whatsoever.

In conclusion the origin of the rim was not completely discovered, but the delamination problem was solved (for a 10/100 nm Cr/Au thicknesses and not 5/25 nm) by employing a different chromium etchant. This alternative was applied for the second wet etching (9.x in **table A.1**) and worked perfectly, no rim was observed either. This suggests that the origin of the rim could be the gold etchant (not used in this test) or the different Cr/Au thicknesses. This problem will be revisited in the second fabrication run. Later Scanning Electron Microscope (SEM) pictures seems to reveal that the rim was chromium overetching.

#### Uniformity of the exposure intensity

In this fabrication run all lithography steps were done with direct writing with the same tool: the Heidelberg MLA150. This tool operates for h-lines photoresists only and the resolution is limited at around 1.2-2  $\mu$ m, which is close to the CD of the masks presented earlier. It was observed that this tool can be source

**Figure 4.10** – Delamination of silicon dioxide on gold. (a) 250nm of low quality sputtered oxide delaminating away from gold. (b) 250nm of high quality sputtered oxide on gold. (c) New design minimising the contact area between high quality sputtered oxide and gold.

of exposure intensity non-uniformities across the wafer. This could be a consequence of the low quality of the vacuum clamping that doesn't flatten the wafer if slightly bent. Consequently, the distance between the writing head and the wafer is not constant across the surface and non-uniformities in exposure can arise. The result of this issue is shown in **figure 4.9**. The test exposure grid in the center of the wafer revealed a good exposure, while on the bottom edge of the wafer some stripes of resist appeared. This kind of resist strips are normally sign of under-exposure. Thus, the exposure was not uniform.

A solution for this issue is to use a much more versatile tool for direct writing named: Heidelberg VPG200. The latter has a much better vacuum clamping, it works for i-line photoresists, it has three different writing heads (20mm, 5mm and 2mm) reaching resolution well below  $1\mu$ m even with the 5mm writinghead and multiple wafers can be loaded. This tool will be used for the second fabrication run with a 5mm writing head. The main drawbacks are: more difficult to perform alignments, a longer exposure time if the 5mm writing head is used. This machine was tested and never produced any stripe as the MLA150 did. Additionally, the lithography quality is observed to be superior to the one obtained at the MLA150.

#### Delamination of silicon dioxide

The low adherence of gold on silicon dioxide is a well known problem in literature and this is typically solved by introducing a adhesion layer of another metal between the gold and the oxide (in this project chromium was used). In the fabrication of bolometers, silicon dioxide is sputtered in argon atmosphere (low quality  $SiO_2$ ) on gold and then patterned (**figure 4.1d,e**). The poor ad-

**Figure 4.11** – Variations of the etch rate of silicon dioxide across the wafer due to the non-uniformity of the quality of silicon dioxide sputtered in argon atmosphere.

hesion between these two materials causes breakage and delamination of the oxide portions lying on gold as shown in **figure 4.10**. This issue is more frequent for thinner layers of silicon dioxide. The reason may be that in thicker layers, the SiO<sub>2</sub> lying on thermal silicon dioxide next to the gate pad offers the necessary mechanical support to the bands lying on gold to prevent them from breaking and delaminating. Again the fabrication was continued on these problematic wafers and solutions were tested on test wafers.

Higher quality SiO<sub>2</sub> is much denser and could provide the necessary mechanical support even for thin layers. A test wafer with the gate mask patterned on a 10/100 nm Cr/Au layer (instead of the usual 5/25 nm) was available and was used for testing solutions. This time, 250nm of silicon dioxide was sputtered in argon and oxygen atmosphere (high quality SiO<sub>2</sub>) and then etched as it was done for the processed wafers. As shown in **figure 4.10b** the delamination disappeared. An even better design is shown in **figure 4.10c**. Given that the contact surface between gold and SiO<sub>2</sub> is minimised, the risk of delamination is reduced.

In the next fabrication run only high quality sputtered silicon dioxide will be used and the design shown in **figure 4.10c** will be adopted.

#### Quality of silicon dioxide across the wafer

Another problem caused by silicon dioxide sputtered in argon atmosphere (low quality  $SiO_2$ ) is the non-uniformity of its quality across the wafer. In fact quality decreases from the centre to the edge of the wafer. The etch rate is consequently affected. It is higher on the edges and lower in the centre. In order to avoid ex-

**Figure 4.12** – Issues with graphene transfer, patterning and release. (a) Many graphene beams breaks at the edge of gold. (b) Photoresist residues are often found on graphene and it is difficult to get rid of them. (c) The jagged edges of gold could be a major cause of the graphene breakage at the gold edges. (d) Polymer residues and rolled-up chunk of graphene are also found.

treme over etching on the contour of the wafer some of the devices in the centre must be sacrificed because the silicon dioxide on gold pads is not completely removed. **Figure 4.11** clearly shows this non-uniformity.

This problem is also solved by the employment of high quality sputtered oxide. The uniformity is much higher and it is possible to etch all the SiO<sub>2</sub> from all devices in the centre of the wafer without having too much over etch on the contour of the wafer. It should be noted that if the gate is connected to an alternating source of current, the thin layer of silicon dioxide on the pad does not cause huge problems because it merely acts as a capacitance in series.

#### Issues with graphene transfer, patterning and release

Four main issues were encountered during graphene transfer, patterning and release. The first is the breakage of graphene at the gold edges as shown in **figure 4.12a**. This problem is probably enhanced by the jagged edges of the

gold (**figure 4.12c**). This is likely a consequence of the wet etching. Another problem is the difficulty of keeping the graphene clean. Residues of photoresist on graphene (**figure 4.12b**) and polymers with portion of rolled-up graphene (**figure 4.12d**) are often found.

Different solutions will be tested in the second fabrication run. For instance, lift-off with LOR could be used to have gold pads with smoother edges and therefore reduce the risk of breakage of graphene sheets. Different design of graphene masks were already tested in the first fabrication run (**figure 4.7**). Some design seemed to give more mechanical support to the graphene beam at the gold edges. To increase the cleanliness of the graphene, a protective layer or spin-on-glass silicon dioxide could be deposited onto the graphene before spin-coating the PMMA. This solution was explored, the spin-on-glass silicon dioxide was successfully etched by vapour HF when on a test wafer, but the wet graphene transfer was not working anymore because the graphene covered with SiO<sub>2</sub> was sinking in the etchant bath. Another option to reduce the polymer residues is to try different types of PMMA.

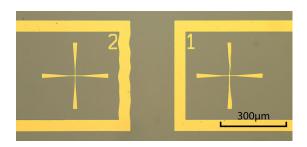

#### Generic improvements

Some additional improvements could be implemented. The first is related to the alignment mechanism of the lithography steps. The alignment marks shown in **figure 4.5a** were unnecessarily small and after exposure and development the small features got deformed. Consequently, the automatic alignment of the Heidelberg MLA150 was not working and thus all alignments were performed manually. In the future mask designs the alignment crosses must be improved to guarantee automatic alignment.

Moreover, as mentioned earlier, the etch rate of vapour HF is very difficult to control. As a consequence, it was very difficult to release the graphene without etching the thermal oxide on the wafer. A layer of AlO<sub>2</sub> could be deposited via Atomic Layer Deposition (ALD) on the thermal oxide. Aluminium oxide is not etched by vapour HF and it is an insulator. This layer would protect the thermal oxide from being etched.

It was also noticed during characterisation that the probe needles are easily aligned to the  $250\mu m$  square pads. Thus, pads could be designed much smaller to increase the level of integration of bolometers on chips. The down side of having smaller pads is that the contact area between graphene and gold diminish and consequently the contact resistance increases.

Finally, the silicon oxide mask should be modified. Labels are patterned on

**Figure 4.13** – Bolometers before graphene transfer. On the left hand side a OGT bolometer with a 300nm thick sacrificial layer of silicon dioxide, while on the right hand side a NGT device with a  $3.2\mu$ m thick sacrificial layer of silicon dioxide.

the first gold layer and then covered with silicon dioxide. Consequently, they become invisible in the SEM because of the insulating properties of the SiO<sub>2</sub>. Some openings should be added in order to make the labels visible.

#### 4.1.4 Results

In this section the results of the first fabrication run will be discussed and presented. The goal is to highlight the positive outcomes, while the issues and possible solutions for the next fabrication run were extensively discussed in Section 4.1.3.

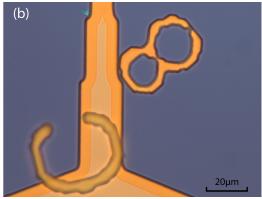

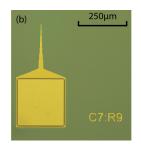

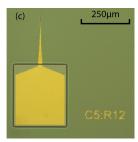

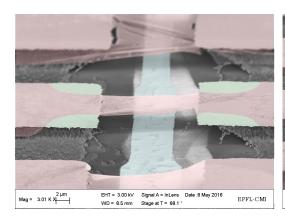

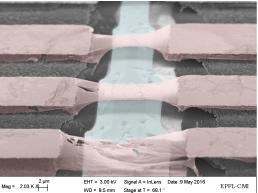

**Figure 4.13** shows two bolometers just before dicing the wafer. The one on the left hand side is a OGT bolometer with a 300nm SiO<sub>2</sub> sacrificial layer, while the one on the right hand side is a NGT bolometer with a  $3.2\mu m$  SiO<sub>2</sub> sacrificial layer. Although the first fabrication run was done hardly with any optimisation, the yield was higher than expected at this stage. However, no quantitative statistics was done. The most delicate part of the fabrication sill has to be done. **Figure 4.14** shows two suspended graphene beams produced successfully for a sacrificial layer of silicon dioxide of  $3.2\mu m$ . The dimensions of the graphene beams in this pictures are approximately: length =  $15\mu m$  and width =  $8\mu m$  for the one on the left hand side, while length =  $20\mu m$  and width =  $10\mu m$  for the one on the right hand side. The yield at this stage was quite low, but it was observed that the structure on the right hand side survived more often than the other ones. This is probably due to a better mechanical support given by the graphene wings being outside the gold pad. Unfortunately, the low yield made impossible to make any statistics to extrapolate the optimal

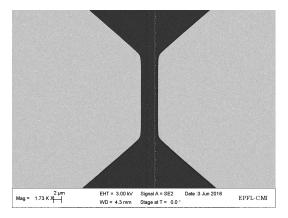

**Figure 4.14** – SEM pictures of graphene beams obtained in the first fabrication run. The graphene masks designs and colours correspond to those previously shown for the masks designs. In this chip the gap between the graphene beam and the gate tip measures approximately  $3.2\mu m$ . The graphene mask used for the fabrication of this chip was designed just to test the graphene release for different beam dimensions. This is the reason why, more than one beam connects the source to the drain.

graphene beam dimensions (from the fabrication point of view). It was still positively surprising to obtain such structures within the first fabrication run with practically any optimisation process.

## 4.1.5 Summary and conclusion