# Characterization and modeling of nanoscale MOSFET for ultra-low power RF IC design

THÈSE Nº 7030 (2016)

PRÉSENTÉE LE 27 MAI 2016 À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR LABORATOIRE DE CIRCUITS INTÉGRÉS PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

## ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

# Maria-Anna CHALKIADAKI

acceptée sur proposition du jury:

Prof. P.-A. Farine, président du jury Prof. C. Enz, directeur de thèse Prof. A. Vladimirescu, rapporteur Dr A. Juge, rapporteur Dr G. Boero, rapporteur

The most that can be expected from any model is that it can supply a useful approximation to reality: All models are wrong; some models are useful.

— George Edward Pelham Box

To the future reader

# Acknowledgements

During these PhD years, I had the chance to collaborate with and meet a lot of remarkable people, who I would like to thank in the following few lines.

First of all, I would like to thank my thesis advisor, Prof. Christian Enz, for his support and guidance during my PhD research. Not only did he transfer to me a lot of his knowledge on device modeling, but he also taught me how to be methodical and insist on the detail, and I am genuinely grateful for that.

I need to acknowledge that it would have been impossible for me to carry out this research and write this thesis without the continuous support of Dr. André Juge and Dr. Patrick Scheer. I would especially like to express my sincere gratitude for their kindness, availability and insightful advices.

A big part of this work is the outcome of the teamwork with the BSIM team. I would like to thank all of its members, in both UC Berkeley and IIT Kanpur, for their fruitful collaboration and particularly Prof. Yogesh Chauhan with whom I worked closely a lot in my first PhD steps.

Besides my advisor and Dr. André Juge, I must also thank the rest of the members of my thesis jury, Prof. Pierre-André Farine, Prof. Andrei Vladimirescu and Dr. Giovanni Boero for their comments and questions on my research and the PhD manuscript.

A big thanks to my colleagues Anurag, Farzan, Lucian, Omid, Raghav, Jérémy, Vladimir, Vincent, Claudio, François and Gabrielle for making the time spent at work pleasant and amusing, and especially to those with whom we ended up being real friends enjoying life outside the office as well. I would like to give special thanks to Jérémy who kindly accepted to translate in French the abstract of this thesis. I am also thankful to Dr. Wladek Grabinski and Dr. Jean-Michel Sallese for all the discussions we had and the encouragement they offered. Many thanks also to my Greek (and not) friends with whom I shared a lot of experiences during my stay in Switzerland.

I must mention here how much I have appreciated all the administrative help that I have received during my PhD years from Lysiane Bourquin, Lucie Auberson, Marie Halm, Nicky Taveira, Catherine Falik, Christina Govoni and Isabelle Buzzi.

This PhD has been the next phase of a device modeling "journey" that started almost a decade ago in Technical University of Crete (TUC). So, I would also like thank my Diploma and Master thesis supervisor, Prof. Matthias Bucher, for the guidance he offered during my first research

#### Acknowledgements

steps, and my labmates at that time Angelos, Nikos and Nikos.

Of course, I cannot say enough for my parents who have been constantly supporting me and caring only for my happiness. I am also grateful to my amazing friend Eva for always providing me with a different perspective on any matter.

But, above all, I would like to thank my husband Antonios and our little star Chloe, for standing by me on all occasions, filling my life with love and joy. Their smile is just enough for me!

Maria-Anna Chalkiadaki April 25, 2016

# Abstract

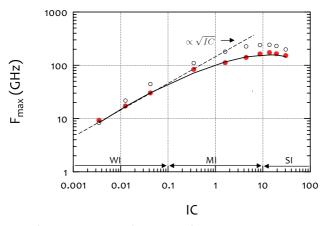

The evolution and characteristics of the electronics is directly linked to the technological and societal progress. Today, there is a huge variety of electronic solutions offered, with the RF low-power systems, such as wireless sensor networks, wireless body area networks, self-powered and energy-harvesting systems and the Internet of Things (IoT), to gain more and more ground. However, these RF low-power applications set stringent constraints on the power consumption, which complicate even more the already difficult task of the RF IC design. This can be addressed by exploiting the phenomenal RF performance offered by the state-of-the-art nanoscale CMOS technologies, with impressive peak transit frequency at the order of hundreds of GHz, and sub-1 dB minimum noise figure. More specifically, most of the RF applications operate at the low GHz range, so the cut-off frequency surplus, achieved typically in strong-inversion (SI), can be traded-off with a lower power consumption by shifting the operating point to moderate- (MI) or weak-inversion (WI), while keeping the RF performance within the desired specifications.

There is an extensive work by the semiconductor community on characterization and modeling the MOS transistor at RF. Nonetheless, most of such studies focus either on the highperformance SI or on rather mature processes with respect to the contemporary state-ofthe-art. In this thesis, an extensive and multi-faceted work on detailed characterization and accurate modeling of nanoscale MOSFETs for low-power operation, focusing therefore on subthreshold operation, is presented and discussed. The analysis is always performed under the perspective of the ultra-low power RF IC design. After all, the reliability of the RF IC simulation tools in this high-end range of frequencies and at very low current densities, which constitute the two extreme conditions in terms of operation of the transistor, strongly depends on the accuracy of the model used.

The dissertation follows a dual course. First, a simple, yet thorough, small-signal RF model is elaborated in order, to describe analytically the RF performance of nanoscale MOSFETs from SI down to the deep WI region, including its noise behavior. This aspect of the work allows the characterization of the RF performance and underlines the particularities of this mode of operation of the device. The study of the device characteristics under all levels of inversion reveals that WI displays different trends than SI region. Further, the analytical expressions are also used in order to form a step-by-step parameter extraction methodology. Especially, for the extraction of the RF noise model parameters, an innovative step-by-step procedure,

#### Abstract

which is applied directly on measurements, is developed. This whole analysis is consistent with the existing advanced standard MOSFET compact models which makes it even worth for the designer.

Then, a state-of-the-art physics-based compact model (BSIM6) is used. Within this part of the work, a set of novel advancements and contributions are introduced in order for the model to be able to capture the complexity of the behavior of modern advanced CMOS technologies. The results show excellent agreement regarding all different aspects, across all modes of operation (CV, DC, RF performance), even at very low bias conditions.

The evaluation of both the modeling approaches is done in detail and uses design oriented tools and metrics, such as the  $G_m/I_D$ , the Y-parameters, the four RF noise parameters and a wide range of figures-of-merit (FoMs). Finally, a discussion around inversion coefficient (*IC*) design methodology is carried out, where several FoMs based on *IC* are modeled with the use of very simple analytical expressions requiring only few parameters. Measurements of advanced 40 nm and 28 nm CMOS technologies, with the latter to be the ultimate process for conventional bulk CMOS, are used throughout the thesis to validate all the different modeling approaches.

Key words: Advanced CMOS, nanoscale bulk MOSFET, low-power, analytical modeling, compact modeling, BSIM6, RF small-signal, RF noise, parameter extraction, model evaluation, geometrical scaling, *IC* design methodology, RF FoMs.

# Résumé

Les caractéristiques et évolutions de l'électronique sont directement liées aux progrès technologiques et sociétaux. De nos jours, une immense variété de solutions électronique sont disponible avec des systèmes RF basse-consommation, tels que les réseaux de capteurs sans fil, les réseaux corporels sans fil, les systèmes à récupération d'énergie et auto-suffisants, et l'internet des objets gagnant de l'importance. Cependant, ces applications RF basse consommation imposent des contraintes strictes sur la consommation énergétique, compliquant d'autant plus la conception de circuits intégrés RF. Ce problème peut être résolu en exploitant les performances RF phénoménales des technologies CMOS actuelles, avec notamment des pics de fréquences de transit de l'ordre de centaines de GHz, et des figures de bruits minimum inférieures à 1dB. Plus particulièrement, la plupart des applications RF fonctionnent dans la gamme basse des fréquences GHz permettant d'échanger le surplus de fréquence de coupure contre une consommation plus basse en déplaçant le point d'opération de l'inversion forte à l'inversion modérée ou l'inversion faible, tout en maintenant les performances RF dans les spécifications requises.

La communauté des semi-conducteurs étudie de manière approfondie la caractérisation et la modélisation des transistors MOS fonctionnant en RF. Toutefois, la plupart de ces études se concentrent soit sur les hautes performances en inversion forte ou sur des procédés matures par rapport à l'état de l'art contemporain. Cette thèse présente un travail approfondi sur la caractérisation détaillée et la modélisation précise de MOSFETs nanométriques faible consommation, en se concentrant sur le fonctionnement sous la tension de seuil. L'analyse entière est faite dans la perspective de conception de circuits intégrés RF ultra basse consommation. Finalement, la fiabilité des outils de simulation de circuits intégrés RF dans la gamme haute de fréquences, et pour des densités de courant très faibles, qui constituent les deux conditions de fonctionnement extrêmes des transistors, dépend fortement de la précision du model utilisé.

Cette dissertation est séparée en deux. Dans un premier temps, un model RF petit signal simple mais complet est élaboré afin de décrire de façon analytique les performances RF des MOSFETs nanométriques, de l'inversion forte jusqu'à l'inversion très faible tout en incluant le comportement de bruit. Cet aspect du travail permet de caractériser les performances RF et souligne les particularités de ce mode de fonctionnent. L'étude des caractéristiques du composant sous tous les niveaux d'inversions révèle que l'inversion faible affiche une tendance différente de celle de l'inversion forte. De plus, les expressions analytiques sont

#### Abstract

également utilisées pour créer une méthodologie d'extraction de paramètres étape par étape. Plus particulièrement, une procédure étape par étape d'extraction des paramètres du model de bruit RF appliquée directement aux mesures est développée. Toute l'analyse est cohérente avec les modèles compact standard du MOSFET, ce qui la rend d'autant plus intéressante pour le concepteur.

Deuxièmement, le modèle compact BSIM6 basé sur la physique est utilisé. Dans cette partie du travail, un ensemble de nouvelles avancées et contributions sont introduites pour permettre au modèle de couvrir la complexité du comportement des technologies CMOS modernes. Les résultats montrent un accord excellent sur tous les aspects et pour tous les modes de fonctionnement (CV, DC et performances RF), même à polarisations très faible.

L'évaluation des deux approches de modélisation est faite de façon détaillée et utilise des outils et métriques orientés design tels que  $G_m/I_D$ , les paramètres Y, les quatre paramètres de bruit RF ainsi qu'un large panel de figures de mérite. Finalement, la méthodologie de conception basée sur le coefficient d'inversion (*IC*) est discutée avec plusieurs figures de mérite basées sur le coefficient d'inversion, tout en utilisant des expressions analytiques très simples nécessitants très peu de paramètres. Des mesures dans les technologies CMOS avancées en 40 nm et 28 nm, la seconde étant le procédé ultime pour les technologies CMOS conventionnelles à substrat, sont présentées dans cette thèse pour valider les différentes approches de modélisation.

Mots-clés : CMOS avancé, MOSFET Nanométrique à Substrat, Basse-Consommation, Modélisation Analytique, Modèle Compact, BSIM6, Petit-Signal RF, Bruit RF, Extraction de Paramètres, Evaluation de Modèle, Mise à l'échelle Géométrique, Méthodologie de Conception de Circuits Intégrés, Figure de Mérite RF.

# Περίληψη

Τα χαραχτηριστικά της σύγχρονης ηλεκτρονικής είναι άμεσα συνδεδεμένα με την τεχνολογιχή χαι την χοινωνική εξέλιξη. Σήμερα, διατίθεται μία πληθώρα ηλεκτρονικών εφαρμογών, εκ των οποίων αξίζει να σημειωθούν τα χαμηλής ισχύος υψηλών συχνοτήτων (RF) συστήματα, όπως τα ασύρματα δίχτυα αισθητήρων (wireless sensor networks), τα αυτοτροφοδοτούμενα συστήματα (self-powered systems), τα συστήματα άντλησης ενέργειας (energy-harvesting systems) και το "διαδίκτυο των πραγμάτων" (IoT), που κερδίζουν όλο και περισσότερο έδαφος. Αυτές οι εφαρμογές, εξάλλου, θέτουν πιο αυστηρούς περιορισμούς όσον αφορά στην κατανάλωση ενέργειας, δυσκολεύοντας το ήδη πολύπλοκο έργο της σχεδίασης των ολοκληρωμένων κυκλωμάτων (IC) σε υψηλές συγνότητες. Υπό αυτό το πλαίσιο καθίσταται δυνατό να εκμεταλλευτούμε την εξαιρετική RF απόδοση των σύγχρονων, υπομικρομετρικών CMOS τεχνολογιών που παρουσιάζουν συχνότητα αποκοπής της τάξης των εκατοντάδων GHz και δείκτη θορύβου χαμηλότερο του ενός dB. Πιο συγκεκριμένα, ένα σημαντικό μέρος από τις RF εφαρμογές λειτουργούν στο χαμηλότερο εύρος των RF συχνοτήτων, οπότε η μεγάλη τιμή της συχνότητας αποκοπής που επιτυγχάνεται σε ισχυρή αναστροφή (SI), μπορεί να ανταλλαχθεί με μία χαμηλότερη κατανάλωση μετακινώντας το σημείο λειτουργίας στην μέτρια (MI) ή την ασθενή αναστροφή (WI), ενώ ταυτόχρονα διατηρείται η RF απόδοση εντός των προδιαγραφών.

Στη βιβλιογραφία υπάρχει αρκετό υλικό που αφορά στον χαρακτηρισμό και τη μοντελοποιήση του MOS τρανζίστορ σε RF συχνότητες. Παρόλα αυτά, οι περισσότερες έρευνες εστιάζουν είτε στην υψηλής απόδοσης ισχυρή αναστροφή είτε σε πιο ώριμες, σε σύγκριση με τις σύγχρονες, τεχνολογίες. Σε αυτήν τη διδακτορική διατριβή, παρουσιάζεται μια εκτεταμένη και πολύπλευρη δουλειά πάνω στο λεπτομερή χαρακτηρισμό και στην ακριβή μοντελοποίηση του υπομικρομετρικού MOS τρανζίστορ για λειτουργία σε χαμηλή ισχύ, και συνεπώς επικεντρωμένη σε συνθήκες λειτουργίας στη χαμηλή αναστροφή. Όλες οι αναλύσεις γίνονται υπό το πρίσμα της σχεδίασης RF IC κυκλωμάτων με χαμηλή κατανάλωση. Εξάλλου, η αξιοπιστία των IC εργαλείων προσομοίωσης σε RF συχνότητες και σε χαμηλά ρεύματα, συνθήκες σχετικά ακραίες όσον αφορά στη λειτουργία του τρανζίστορ, βασίζεται στην ακρίβεια των μοντέλων που χρησιμοποιούνται.

Το διδακτορικό αυτό δομείται πάνω δύο βασικούς άξονες. Αρχικά χρησιμοποιείται, ένα απλό, αλλά πλήρες, RF μοντέλο μικρού σήματος προκειμένου να περιγραφεί αναλυτικά η RF συμπεριφορά του υπομικρομετρικού MOS τρανζίστορ, συμπεριλαμβανομένου του θορύβου,

#### Abstract

σε όλα τα επίπεδα αναστροφής, από την ασθενή έως την ισχυρή. Αυτό το χομμάτι της δουλειάς επιτρέπει επαρχώς το χαραχτηρισμό της RF λειτουργίας και τονίζει τις ιδιαιτερότητες που παρουσιάζονται κατά τη λειτουργία σε ασθενή αναστροφή. Οι αναλυτικές εκφράσεις χρησιμοποιούνται προχειμένου να προταθεί μία καινοτόμα διαδικασία εξαγωγής παραμέτρων, η οποία μπορεί να εφαρμοστεί κατευθείαν πάνω σε μετρήσεις. Καθώς η όλη ανάλυση γίνεται σε συνέπεια με τα ήδη υπάρχοντα σύγχρονα MOSFET compact μοντέλα καθίσταται επίσης χρήσιμη και από την μεριά του σχεδιαστή.

Έπειτα χρησιμοποιείται, το πιο σύγχρονο, πρότυπο φυσικό compact μοντέλο BSIM6. Σε αυτό το μέρος της δουλειάς, ένα σύνολο από βελτιώσεις εισάγονται στο μοντέλο ώστε να μπορεί να αναπαριστά την πολύπλοκη συμπεριφορά των σύγχρονων CMOS τεχνολογιών με ακρίβεια. Τα αποτελέσματα της σύγκρισης του μοντέλου με μετρήσεις δείχνουν μία εξαιρετική συμφωνία σε όλους τους τρόπους λειτουργίας (CV, DC, RF), ακόμα και σε πολύ χαμηλές συνθήκες πόλωσης.

Η αξιολόγηση και των δύο προσεγγίσεων μοντελοποίησης γίνεται λεπτομερώς, χρησιμοποιώντας εργαλεία και μεγέθη κατάλληλα για σχεδίαση, όπως το  $G_m/I_D$ , οι Υ-παράμετροι, οι τέσσερις RF παράμετροι θορύβου καθώς και ένα σύνολο από αξιολογικούς δείκτες (FoMs). Στο τέλος, γίνεται μία ανάλυση που χρησιμοποιεί το συντελεστή αναστροφής (IC) ως εργαλείο σχεδίασης, όπου διαφορετικά FoMs μοντελοποιούνται ως προς IC με τη χρήση πολύ απλών αναλυτικών εκφράσεων που απαιτούν για τον υπολογισμό τους μόνο ένα μικρό αριθμό παραμέτρων. Μετρήσεις από δύο σύγχρονες CMOS τεχνολογίες, συγκεκριμένα 40 nm και 28 nm, με την 28 nm να είναι και η τελευταία τεχνολογία που αναπτύσσεται για τα συμβατικά MOS τρανζίστορ, χρησιμοποιούνται προκειμένου να αξιολογηθούν οι διαφορετικές μέθοδοι μοντελοποίησης.

Λέξεις κλειδιά: Σύγχρονες CMOS τεχνολογίες, υπομικρομετρικό MOS τρανζίστορ, χαμηλή ισχύς, αναλυτική μοντελοποίηση, BSIM6, υψηλές συχνότητες, χαμηλό σήμα, θόρυβος υψηλών συχνοτήτων, εξαγωγή παραμέτρων, αξιολόγηση μοντέλου, γεωμετρική υποκλιμάκωση, μεθοδολογία σχεδίασης, συντελεστής αναστροφής (IC), αξιολογικοί δείκτες υψηλών συχνοτήτων (RF FoMs).

# Contents

| Ac     | Acknowledgements i                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                       |                                                                |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------|--|

| Ał     | stract (English/Français/Ελληνικά)                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                       | iii                                                            |  |

| Li     | st of figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       | xiii                                                           |  |

| Li     | at of tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       | xix                                                            |  |

| Sy     | mbols                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                       | xxi                                                            |  |

| Ac     | ronyms and Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       | XXV                                                            |  |

| 1      | Introduction         1.1       Motivation         1.2       The MOS Transistor         1.3       Compact and Analytical Modeling         1.4       State-of-the-Art         1.4.1       Compact Modeling         1.4.2       Analytical RF MOSFET modeling         1.4.2       Analytical RF MOSFET modeling         2.1       Introduction         2.2       Technology DUT and Measurements Description         2.3       DUT Details         2.4       Measurement Details | · · · · · · · · · · · · · · · · · · · | 1<br>1<br>2<br>4<br>8<br>8<br>11<br>13<br>13<br>13<br>15<br>16 |  |

| I<br>3 | Analytical Small-Signal RF Modeling<br>Analytical RF Modeling                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       | 19<br>21                                                       |  |

| J      | 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <br>                                  | 21<br>21<br>22<br>24<br>26<br>27                               |  |

#### Contents

|   |      | 3.5.1 Validation of the Analytical RF Model                                      | 31  |

|---|------|----------------------------------------------------------------------------------|-----|

|   | 3.6  | RF Figures-of-Merit                                                              | 31  |

|   |      | 3.6.1 Current Gain - $H_{21}$                                                    | 31  |

|   |      | 3.6.2 Transit Frequency - $F_t$                                                  | 37  |

|   |      | 3.6.3 Unilateral Gain - <i>U</i>                                                 | 39  |

|   |      | 3.6.4 Maximum Oscillation Frequency - $F_{\text{max}}$                           | 43  |

|   | 3.7  | Conclusions                                                                      | 43  |

| 4 | Ana  | lytical RF Noise Modeling                                                        | 47  |

|   |      | Introduction                                                                     | 47  |

|   | 4.2  | RF Noise Analysis                                                                | 48  |

|   |      | 4.2.1 Step-by-step Derivation of the Analytical Expressions of the Four RF Noise |     |

|   |      | Parameters                                                                       | 50  |

|   | 4.3  | Expressions for the Direct Extraction of the RF Noise Model Parameters           | 59  |

|   |      | 4.3.1 Validation of the Analytical RF Noise Model and the Parameter Extraction   |     |

|   |      | Procedure                                                                        | 60  |

|   | 4.4  | Conclusions                                                                      | 63  |

| п | Co   | ompact Modeling with BSIM6                                                       | 67  |

|   | CU   | mpact modeling with bonno                                                        | 01  |

| 5 | The  | BSIM6 Compact Model                                                              | 69  |

|   | 5.1  | Introduction                                                                     | 69  |

|   | 5.2  | A Short History                                                                  | 69  |

|   | 5.3  | BSIM6 Main Characteristics                                                       | 70  |

| 6 | Geo  | ometrical Scaling in BSIM6                                                       | 73  |

|   | 6.1  | Introduction                                                                     | 73  |

|   | 6.2  | Geometrical Scaling Approaches                                                   | 73  |

|   |      | 6.2.1 Comparison of Existing Geometrical Scaling Approaches                      | 75  |

|   | 6.3  | Selection of Geometrical Scaling Equations for BSIM6                             | 77  |

|   | 6.4  | Evaluation of the BSIM6 Scalability                                              | 82  |

|   | 6.5  | Conclusions                                                                      | 84  |

| 7 | Para | ameter Extraction Methodology of BSIM6 for CMOS Technologies                     | 89  |

|   | 7.1  | Introduction                                                                     | 89  |

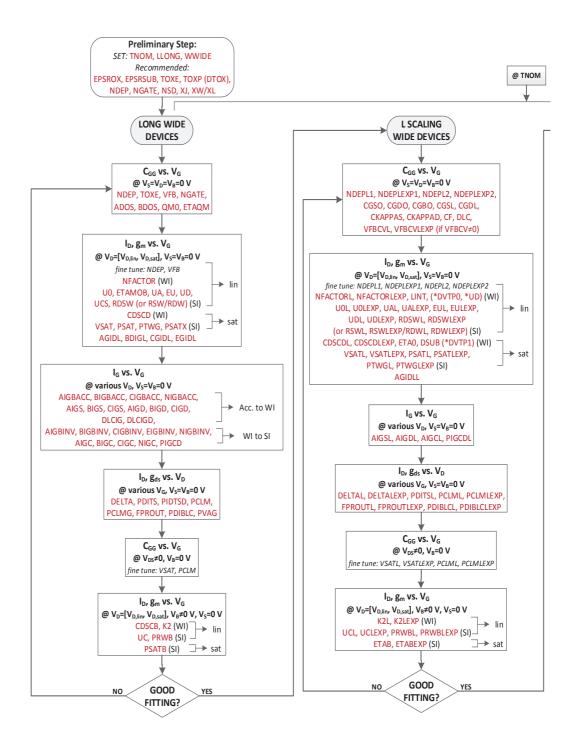

|   | 7.2  | Parameter Extraction Methodology                                                 | 90  |

|   |      | 7.2.1 Extraction of Main Physical Effects & Geometry Independent Parameters      | 91  |

|   |      | 7.2.2 Extraction of Short Channel Effects & Length Scaling Parameters            | 95  |

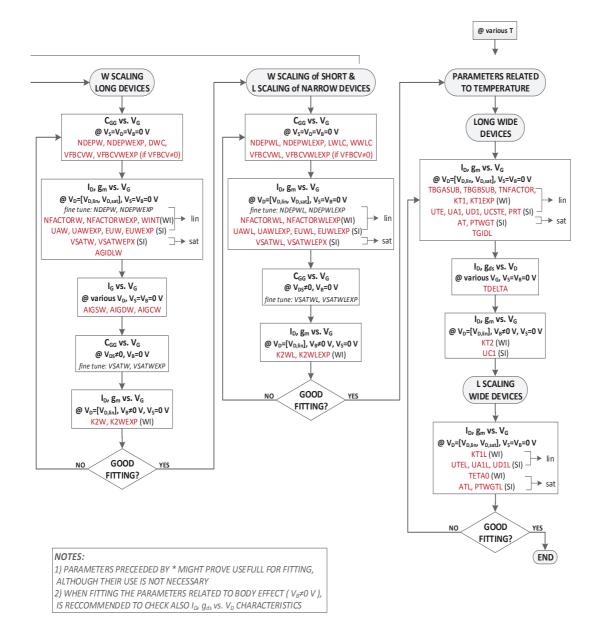

|   |      | 7.2.3 Extraction of Narrow Channel Effects & Width Scaling Parameters            | 99  |

|   |      | 7.2.4 Extraction of Parameters for Narrow/Short Channel Devices                  | 101 |

|   |      | 7.2.5 Extraction of Temperature Dependence Parameters                            | 103 |

|   | 7.3  | Conclusions                                                                      | 106 |

| 8 | Eva | luation of BSIM6 in Nanoscale CMOS Technologies | 109 |

|---|-----|-------------------------------------------------|-----|

|   | 8.1 | Introduction                                    | 109 |

|   | 8.2 | Validation against a 40 nm CMOS Process         | 110 |

|   |     | 8.2.1 CV Operation                              | 110 |

|   |     | 8.2.2 DC Operation                              | 111 |

|   |     | 8.2.3 RF Operation                              | 115 |

|   | 8.3 | Validation against a 28 nm CMOS Process         | 125 |

|   |     | 8.3.1 CV Operation                              | 126 |

|   |     | 8.3.2 DC Operation                              | 130 |

|   | 8.4 | Conclusions                                     | 130 |

|   |     |                                                 |     |

## III Analytical Modeling of FoMs

| 9  | Devi | ice Lev                              | el Figures-of-Merit as Design Guidelines                                  | 137 |

|----|------|--------------------------------------|---------------------------------------------------------------------------|-----|

|    | 9.1  | Introd                               | luction                                                                   | 137 |

|    | 9.2  | Mode                                 | ling the Gate Transconductance - $G_m$                                    | 138 |

|    |      | 9.2.1                                | Modeling the Normalized Source Transconductance - $g_{ms}$                | 138 |

|    |      | 9.2.2                                | Extraction of Parameters - $n$ , $I_{\text{spec}}$ , $\lambda_{\text{c}}$ | 140 |

|    |      | 9.2.3                                | Model Verification                                                        | 144 |

|    | 9.3  | Mode                                 | ling the Transconductance Efficiency - $G_m/I_D$                          | 147 |

|    | 9.4  | Mode                                 | ling the Output Conductance - $G_{ds}$                                    | 150 |

|    |      | 9.4.1                                | Extraction of Parameters - $\alpha_{dibl}$ , $\lambda_{sat\_gds}$         | 151 |

|    |      | 9.4.2                                | Model Verification                                                        | 155 |

|    | 9.5  | Mode                                 | ling the Intrinsic Voltage Gain - $A_{v_i}$                               | 155 |

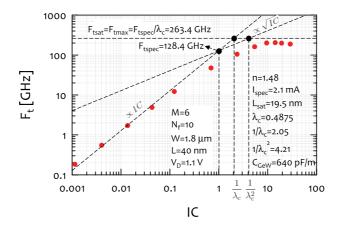

|    | 9.6  | Mode                                 | ling the Transit Frequency - $F_t$                                        | 159 |

|    |      | 9.6.1                                | Extraction of Parameters - $C_{GG_{eW}}$                                  | 160 |

|    |      | 9.6.2                                | Model Verification                                                        | 161 |

|    | 9.7  | Mode                                 | ling the $G_{\rm m}/I_{\rm D} \cdot F_{\rm t}$ RF FoM                     | 161 |

|    | 9.8  | Mode                                 | ling the Noise Factor - $F$                                               | 164 |

|    |      | 9.8.1                                | Extraction of Parameters - $R_G$ , $\gamma_{nD}$                          | 167 |

|    |      | 9.8.2                                | Model Verification                                                        | 168 |

|    | 9.9  | 0                                    | -Transistor Common-Source Amplifier                                       | 169 |

|    | 9.10 | Concl                                | usions                                                                    | 175 |

| 10 | Con  | clusio                               | n                                                                         | 177 |

| 10 |      |                                      | hary of Results                                                           | 178 |

|    | 10.1 |                                      |                                                                           |     |

|    |      |                                      |                                                                           |     |

|    |      |                                      |                                                                           |     |

|    |      |                                      |                                                                           |     |

|    | 10.2 |                                      |                                                                           |     |

|    |      | 10.1.1<br>10.1.2<br>10.1.3<br>10.1.4 | Analytical Small-Signal RF Modeling                                       |     |

Contents

| Bibliography     | 183 |

|------------------|-----|

| Curriculum Vitae | 195 |

# List of Figures

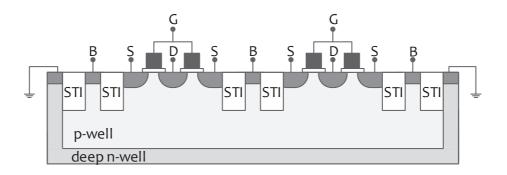

| 2.1  | Cross section of a 2x2 nMOS RF DUT across L                                                                                                                   | 15 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

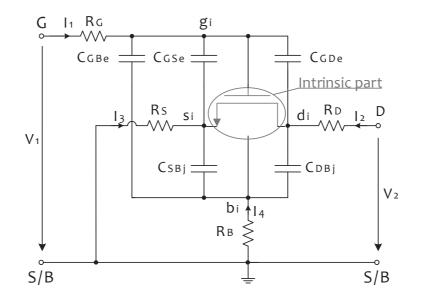

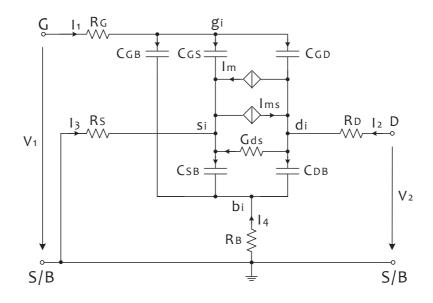

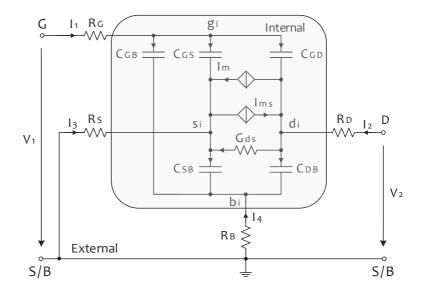

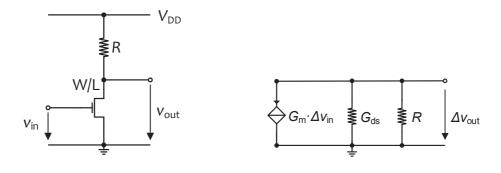

| 3.1  | Equivalent sub-circuit and its small-signal equivalent circuit in saturation of an RF MOSFET.                                                                 | 23 |

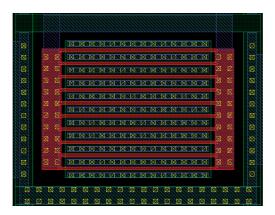

| 3.2  | Layout of a single cell of the measured RF DUT                                                                                                                | 28 |

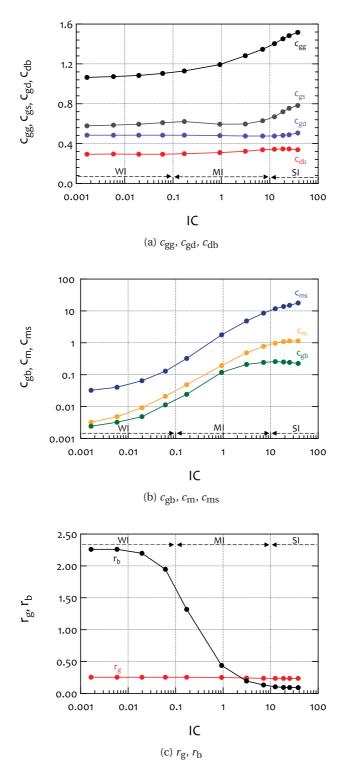

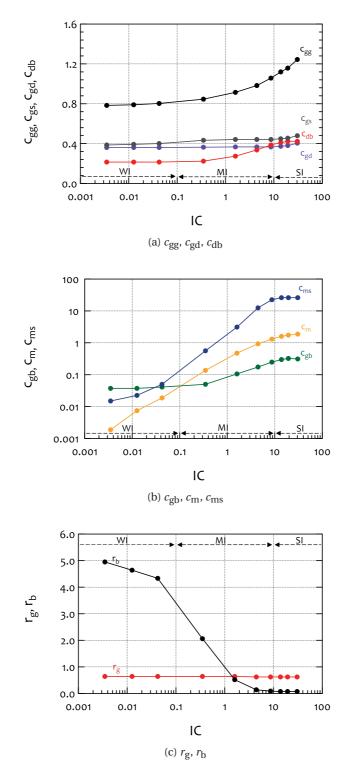

| 3.3  | Normalized extracted values of the RF components of the small-signal equivalent circuit vs. <i>IC</i> of a minimum channel length RF nMOS DUT of a 40 nm CMOS |    |

|      | process                                                                                                                                                       | 29 |

| 3.4  | Normalized extracted values of the RF components of the small-signal equivalent circuit vs. <i>IC</i> of a minimum channel length RF nMOS DUT of a 28 nm CMOS |    |

|      | process                                                                                                                                                       | 30 |

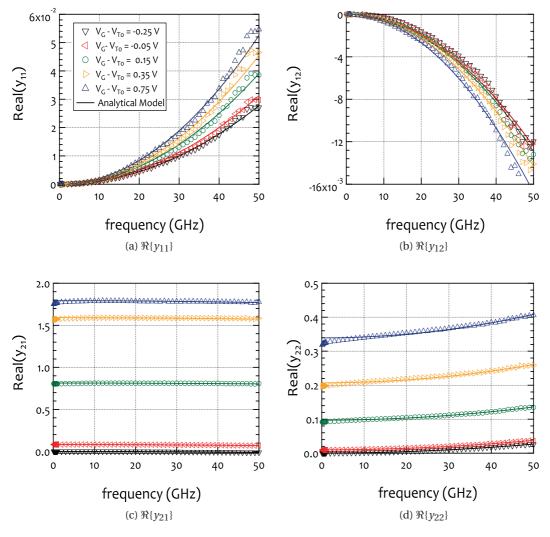

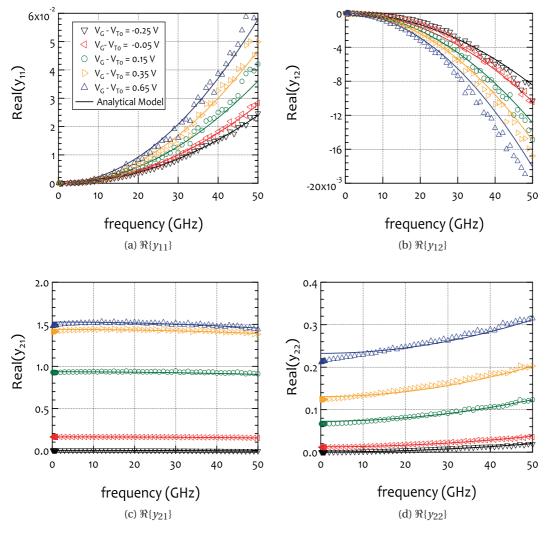

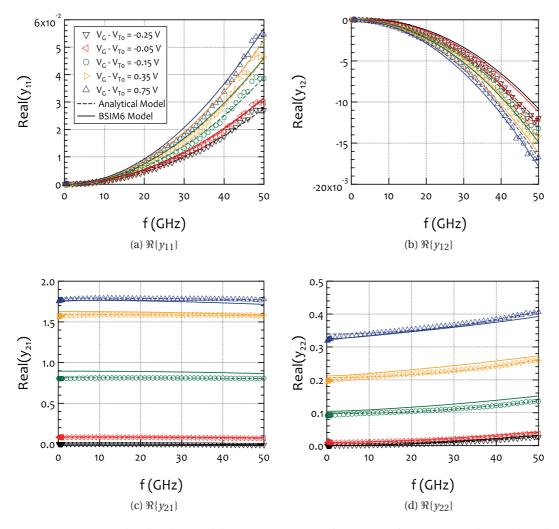

| 3.5  | Normalized real part of the Y-parameters vs. frequency of a minimum channel                                                                                   |    |

|      | length RF nMOS DUT of a 40 nm CMOS process.                                                                                                                   | 32 |

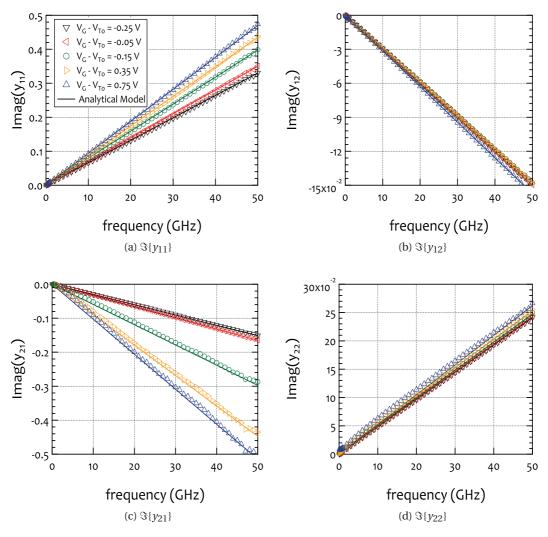

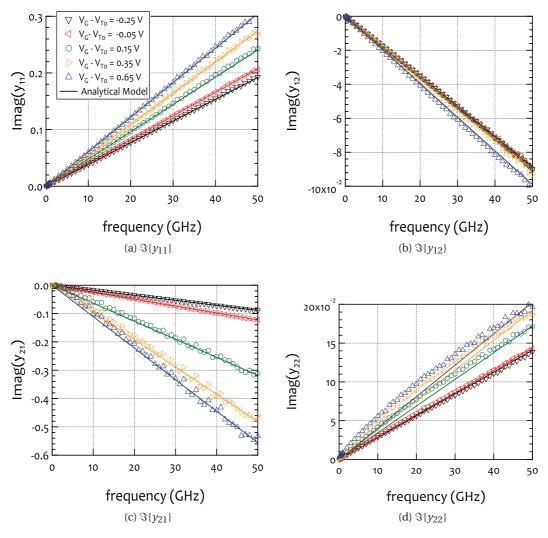

| 3.6  | Normalized imaginary part of the Y-parameters vs. frequency of a minimum                                                                                      |    |

|      | channel length RF nMOS DUT of a 40 nm CMOS process                                                                                                            | 33 |

| 3.7  | Normalized real part of the Y-parameters vs. frequency of a minimum channel                                                                                   |    |

|      | length RF nMOS DUT of a 28 nm CMOS process.                                                                                                                   | 34 |

| 3.8  | Normalized imaginary part of the Y-parameters vs. frequency of a minimum                                                                                      |    |

|      | channel length RF nMOS DUT of a 28 nm CMOS process.                                                                                                           | 35 |

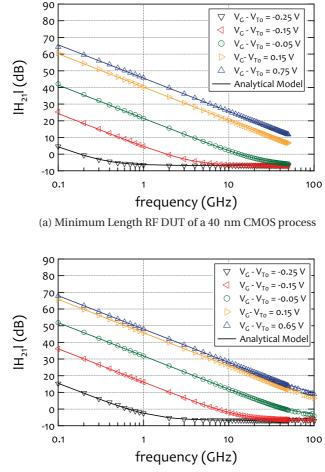

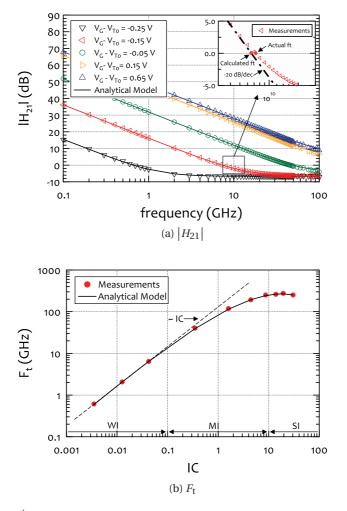

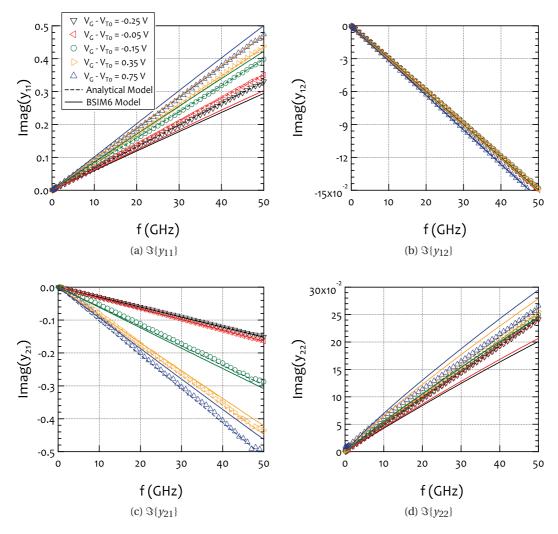

| 3.9  | $ H_{21} $ vs. frequency of minimum length RF nMOS DUTs of 40 nm and 28 nm                                                                                    |    |

|      | CMOS processes.                                                                                                                                               | 37 |

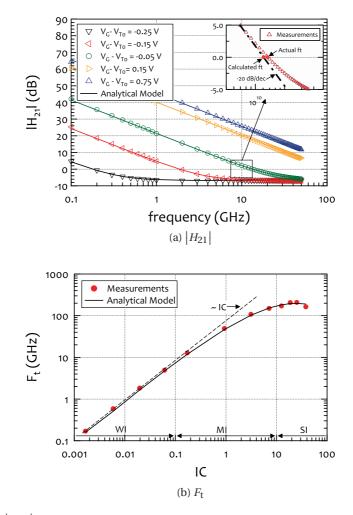

| 3.10 | $ H_{21} $ vs. frequency and $F_t$ vs. <i>IC</i> of a minimum channel length RF nMOS DUT                                                                      |    |

|      | of a 40 nm CMOS process                                                                                                                                       | 39 |

| 3.11 | $ H_{21} $ vs. frequency and $F_t$ vs. <i>IC</i> of a minimum channel length RF nMOS DUT                                                                      |    |

|      | of a 28 nm CMOS process                                                                                                                                       | 40 |

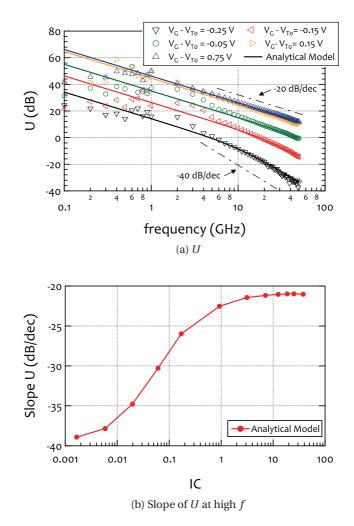

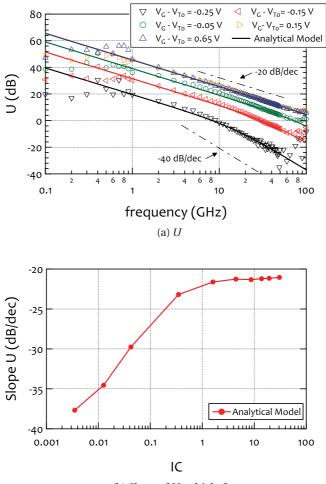

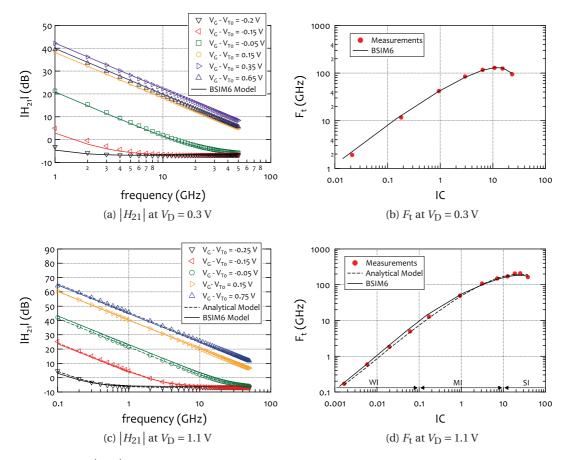

| 3.12 | <i>U</i> vs. frequency and its slope vs. <i>IC</i> at high frequencies of a minimum channel                                                                   |    |

|      | length RF nMOS DUT of a 40 nm CMOS process.                                                                                                                   | 41 |

| 3.13 | U vs. frequency and its slope vs. $IC$ at high frequencies of a minimum channel                                                                               |    |

|      | length RF nMOS DUT of a 28 nm CMOS process.                                                                                                                   | 42 |

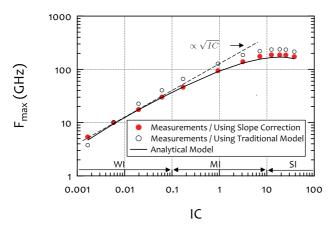

| 3.14 | $F_{\text{max}}$ vs. <i>IC</i> of minimum length RF nMOS DUTs of 40 nm and 28 nm CMOS                                                                         |    |

|      | processes.                                                                                                                                                    | 44 |

### List of Figures

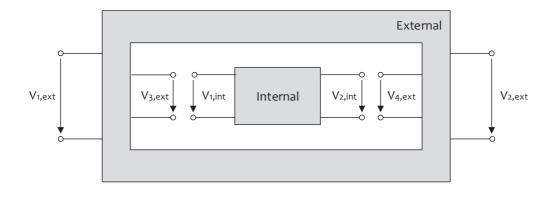

| 4.1 | A two-port DUT divided in two parts for the RF noise analysis $\ldots \ldots \ldots$                | 48  |

|-----|-----------------------------------------------------------------------------------------------------|-----|

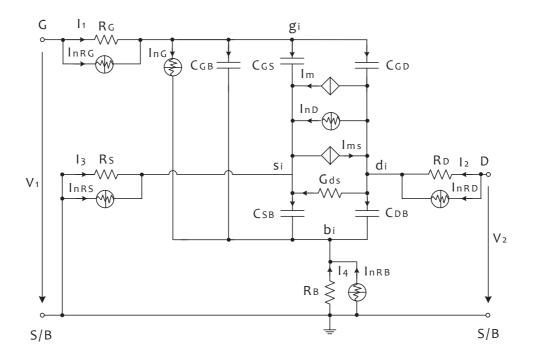

| 4.2 | Small-signal equivalent circuit of an RF MOSFET used for the RF noise analysis                      |     |

|     | in saturation.                                                                                      | 49  |

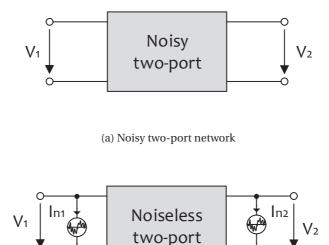

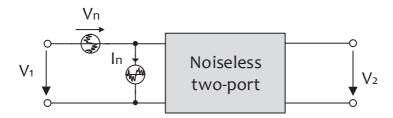

| 4.3 | Different representations of a linear noisy two-port                                                | 51  |

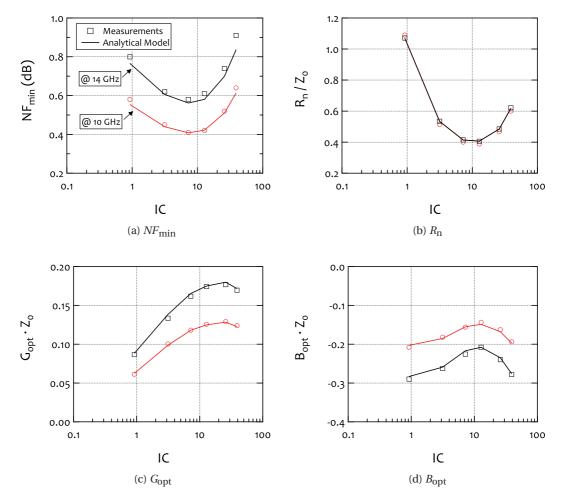

| 4.4 | Extracted values of the RF noise model parameters vs. <i>IC</i> of a minimum channel                |     |

|     | length RF nMOS DUT of a 40 nm CMOS process.                                                         | 61  |

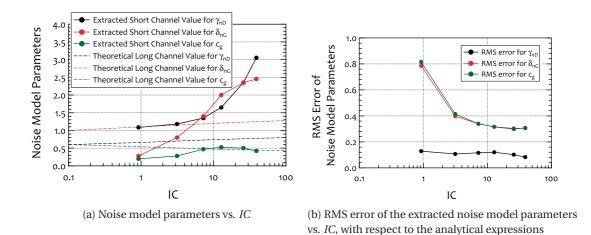

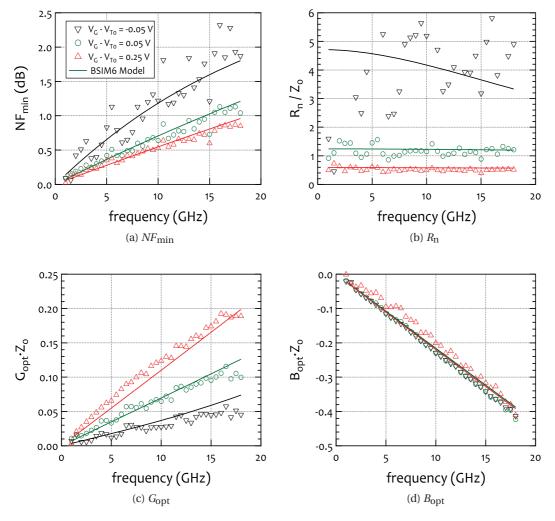

| 4.5 | The four RF noise parameters vs. frequency of a minimum channel length RF                           |     |

|     | nMOS DUT of a 40 nm CMOS process.                                                                   | 62  |

| 4.6 | The four RF noise parameters vs. <i>IC</i> of a minimum channel length RF nMOS                      |     |

|     | DUT of a 40 nm CMOS process.                                                                        | 63  |

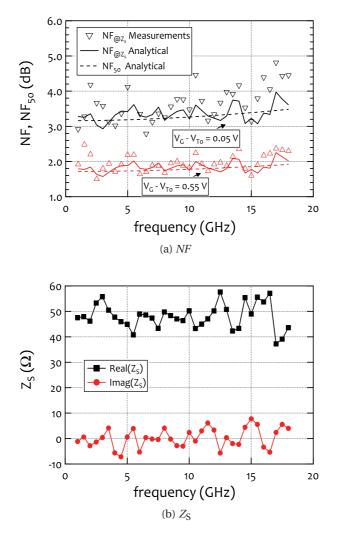

| 4.7 | <i>NF</i> and $Z_{\rm S}$ vs. frequency of a minimum channel length RF nMOS DUT of a                |     |

|     | 40 nm CMOS process.                                                                                 | 64  |

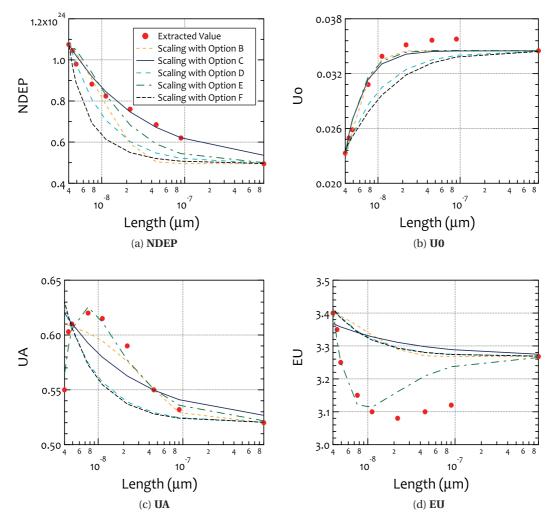

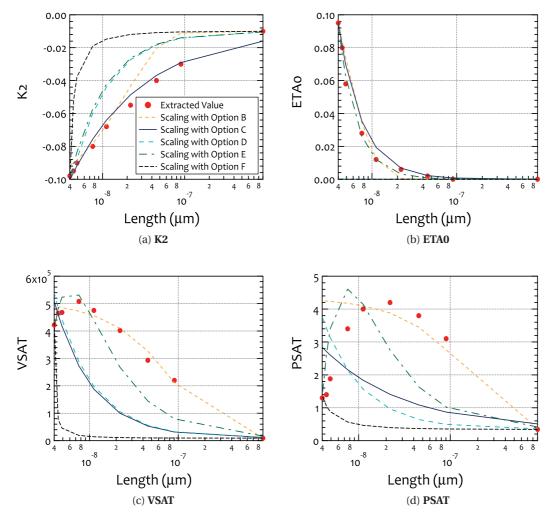

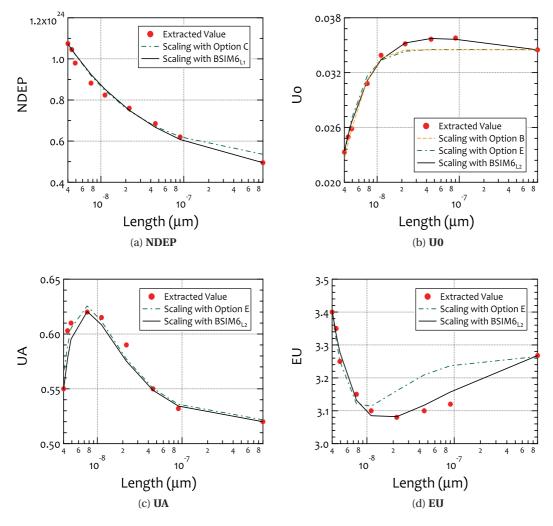

| 6.1 | Length scaling of a selection of model parameters of nMOS DUTS of a 40 nm                           |     |

|     | CMOS process - part A                                                                               | 77  |

| 6.2 | Length scaling of a selection of model parameters of nMOS DUTS of a 40 nm                           |     |

|     | CMOS process - part B                                                                               | 78  |

| 6.3 | Comparison of the new BSIM6 length scaling expressions with the best of the                         |     |

|     | already existing ones for a selection of model parameters of nMOS DUTS of a                         |     |

|     | 40 nm CMOS process - part A                                                                         | 80  |

| 6.4 | Comparison of the new BSIM6 length scaling expressions with the best of the                         |     |

|     | already existing ones for a selection of model parameters of nMOS DUTS of a                         |     |

|     | 40 nm CMOS process - part B                                                                         | 81  |

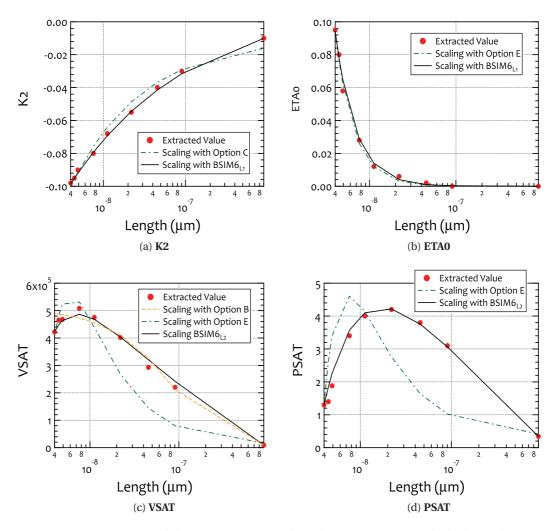

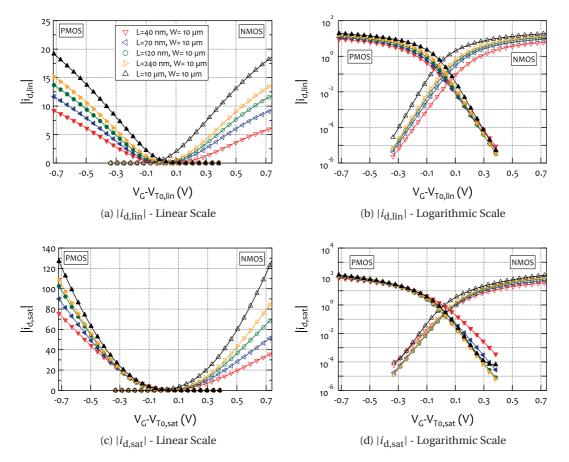

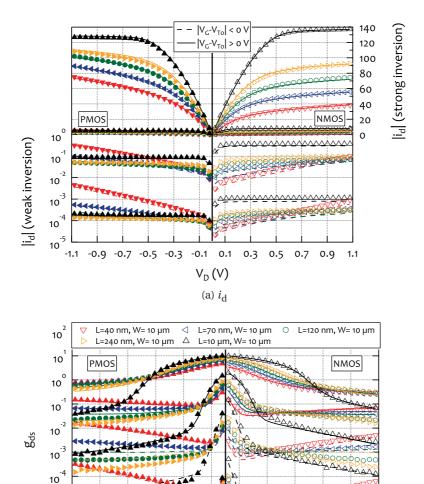

| 6.5 | Normalized drain current $ i_d $ vs. $V_G - V_{T0}$ for nMOS and pMOS DC DUTs of a                  |     |

|     | 40 nm CMOS process for different channel lengths                                                    | 84  |

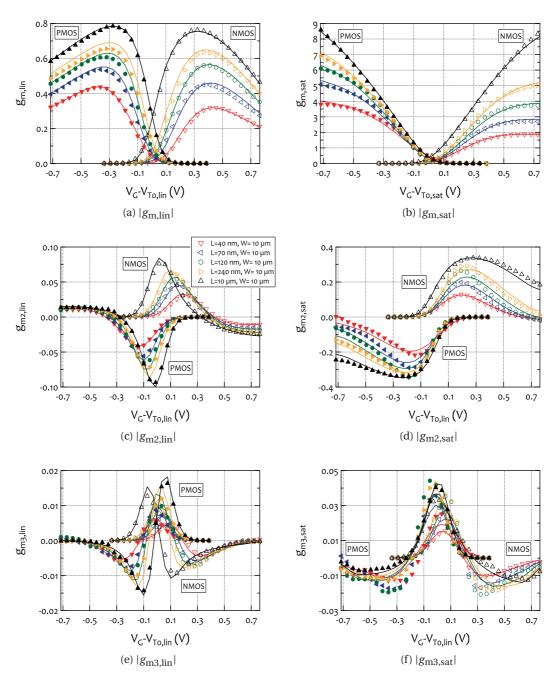

| 6.6 | Normalized drain current derivatives $ g_m $ , $ g_{m2} $ , $ g_{m3} $ vs. $V_G - V_{T0}$ for nMOS  |     |

|     | and pMOS DC DUTs of a 40 nm CMOS process for different channel lengths.                             | 85  |

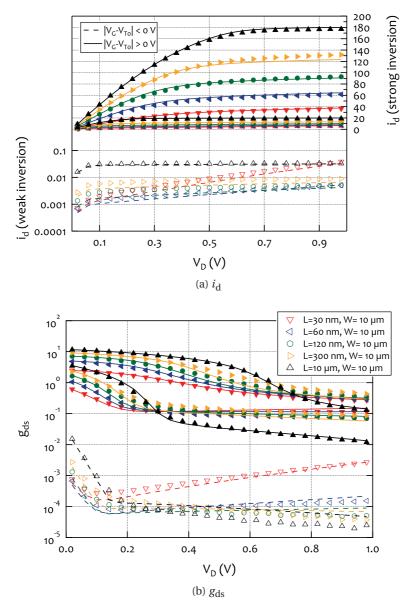

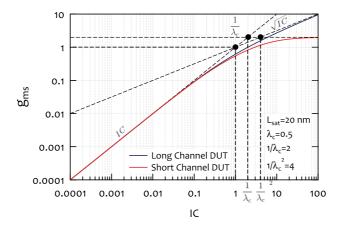

| 6.7 | Normalized drain current $ i_d $ and its derivative $g_{ds}$ vs. $V_D$ for nMOS and pMOS            |     |

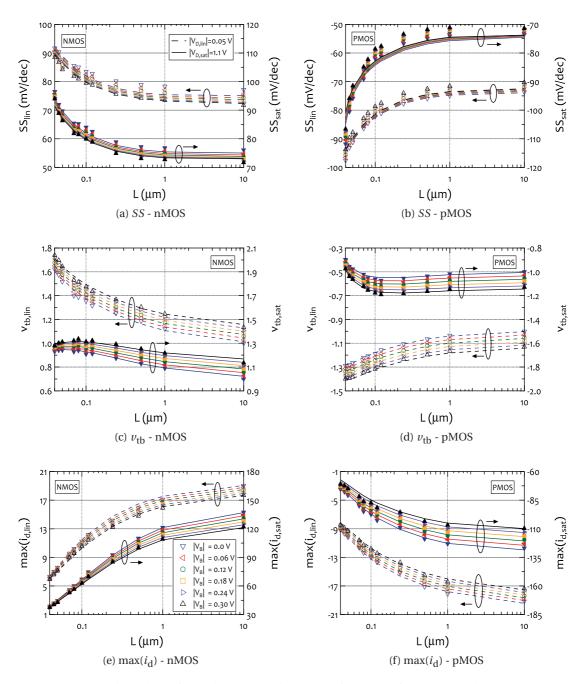

|     | DC DUTs of a 40 nm CMOS process for different channel lengths.                                      | 86  |

| 6.8 | Length Scaling of SS, $v_{tb}$ and max $(i_d)$ for nMOS and pMOS DC DUTs of 40 nm                   |     |

|     | CMOS process.                                                                                       | 87  |

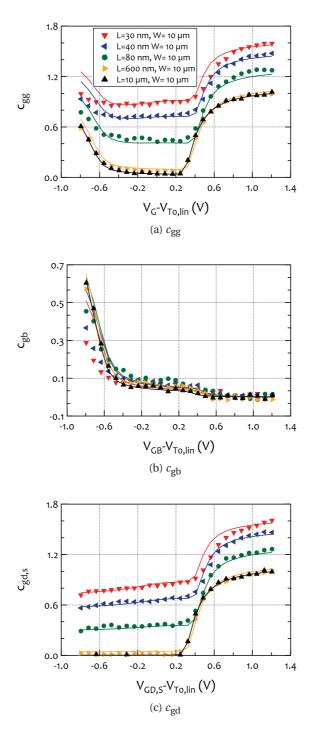

| 7.1 | BSIM6 parameter extraction flowchart - part A.                                                      | 107 |

| 7.2 | BSIM6 parameter extraction flowchart - part B                                                       | 108 |

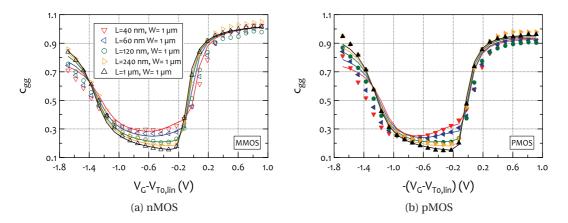

| 8.1 | Normalized total gate capacitance $c_{gg}$ vs. $ V_G - V_{T0,lin} $ for nMOS and pMOS DC            |     |

|     | DUTs of a 40 nm CMOS process for different channel lengths.                                         | 110 |

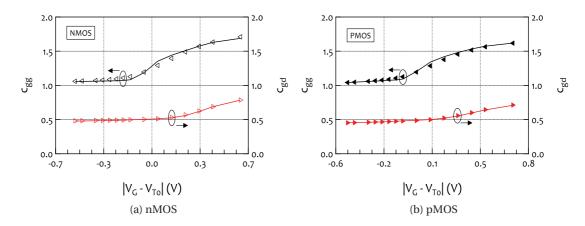

| 8.2 | Normalized capacitances $c_{gg}$ and $c_{gd}$ vs. $ V_G - V_{T0} $ , at $ V_D  = 0.3$ V for minimum |     |

|     | channel length nMOS and pMOS RF DUTs of a 40 nm CMOS                                                | 111 |

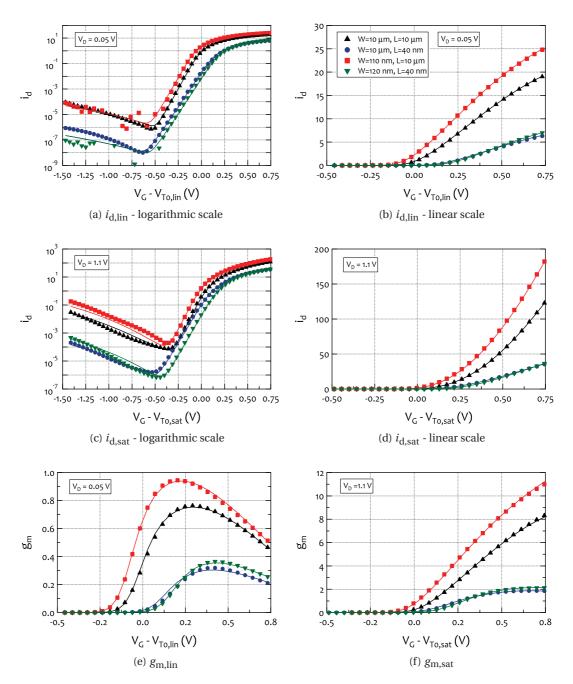

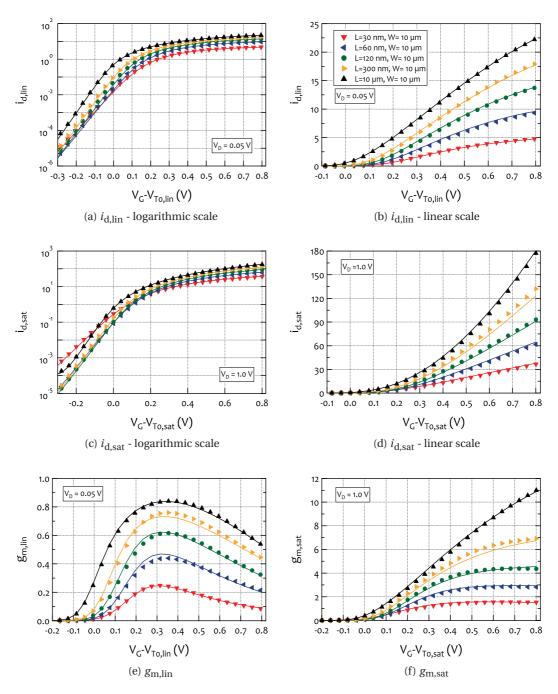

| 8.3 | Normalized drain current $i_d$ and gate transconcuctance $g_m$ vs. $V_G - V_{T0}$ for the           |     |

|     | corner nMOS DC DUTs of a 40 nm CMOS process.                                                        | 113 |

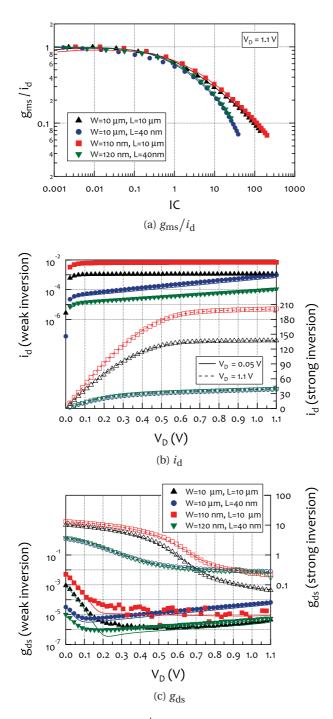

| 8.4  | Transconductance efficiency $g_{\rm ms}/i_{\rm d}$ vs. <i>IC</i> and normalized drain current $i_{\rm d}$ and |     |

|------|---------------------------------------------------------------------------------------------------------------|-----|

|      | output concuctance $g_{\rm ds}$ vs. $V_{\rm D}$ for the corner nMOS DC DUTs of a 40 nm CMOS                   |     |

|      | process                                                                                                       | 114 |

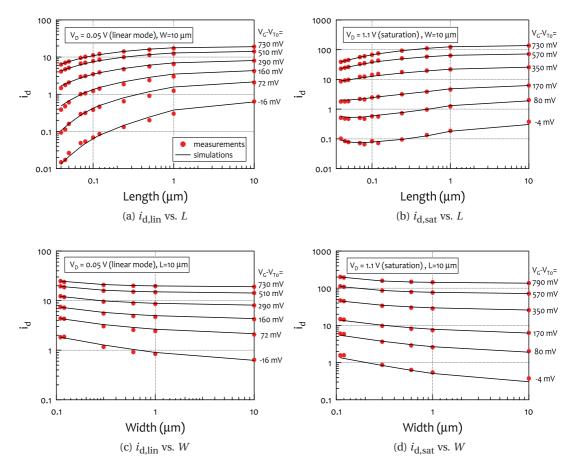

| 8.5  | Length and width scaling of the normalized drain current $i_d$ for various $V_G$ for                          |     |

|      | nMOS DC DUTs of a 40 nm CMOS process.                                                                         | 115 |

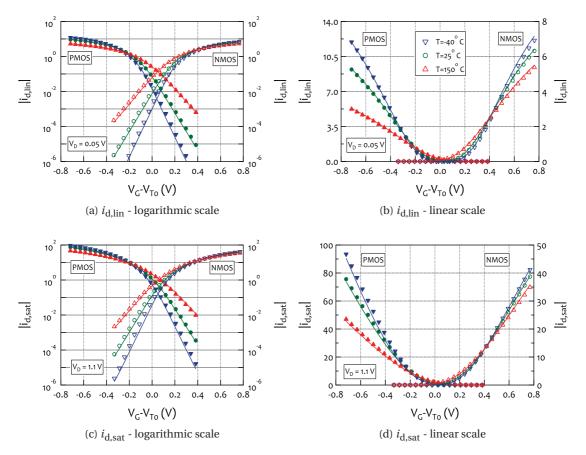

| 8.6  | Normalized drain current $ i_d $ vs. $V_G - V_{T0}$ at different temperatures, for the                        |     |

|      | shortest nMOS and pMOS DC DUTs of a 40 nm CMOS process.                                                       | 116 |

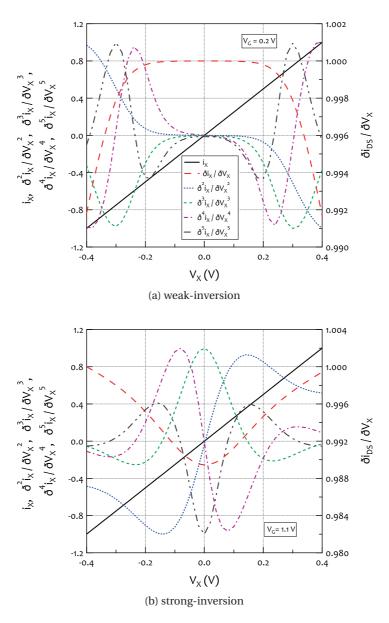

| 8.7  | Gummel symmetry test (GST) of BSIM6, in weak- and strong-inversion, using                                     |     |

|      | the model card derived for nMOS DC DUTs of a 40 $$ nm CMOS process. $$                                        | 117 |

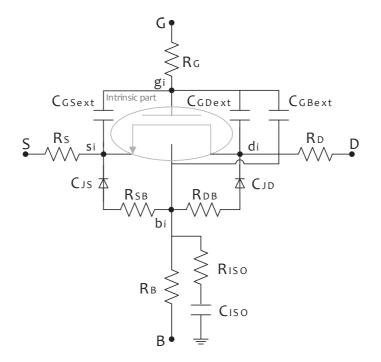

| 8.8  | RF MOSFET equivalent schematic including the parasitic contribution of the                                    |     |

|      | isolation layer.                                                                                              | 118 |

| 8.9  | Normalized real part of the Y-parameters vs. frequency of a minimum channel                                   |     |

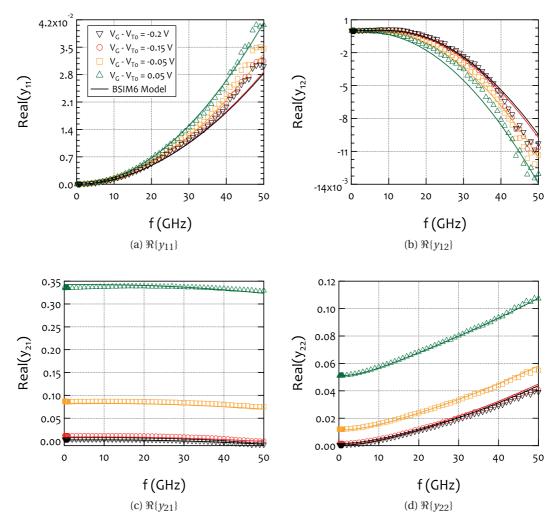

|      | length RF nMOS DUT of a 40 nm CMOS process, at $V_{\rm D}$ = 0.3 V                                            | 119 |

| 8.10 | Normalized imaginary part of the Y-parameters vs. frequency of a minimum                                      |     |

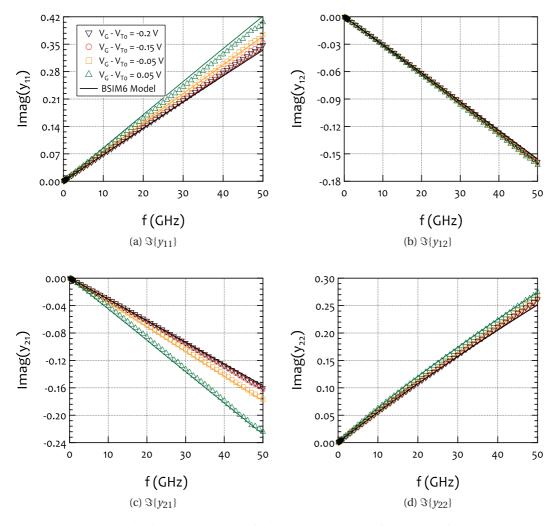

|      | channel length RF nMOS DUT of a 40 nm CMOS process, at $V_{\rm D}$ = 0.3 V                                    | 120 |

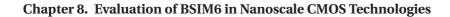

| 8.11 | Normalized Y-parameters vs. <i>IC</i> of a minimum channel length RF nMOS DUT                                 |     |

|      | of a 40 nm CMOS process, at $V_{\rm D}$ = 0.3 V                                                               | 121 |

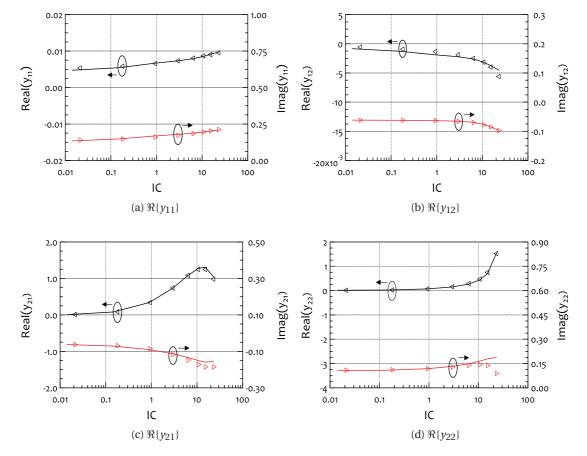

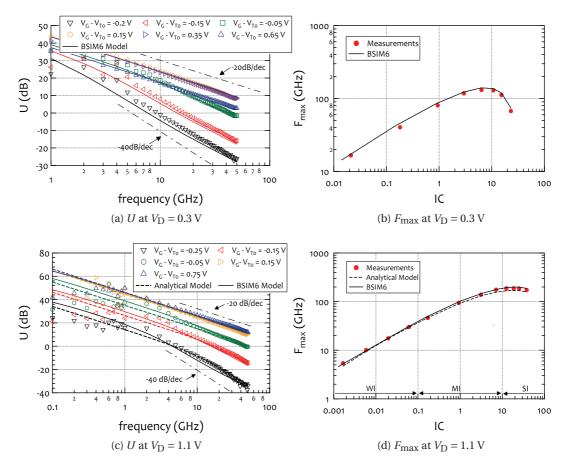

| 8.12 | Normalized real part of the Y-parameters vs. frequency of a minimum channel                                   |     |

|      | length RF nMOS DUT of a 40 nm CMOS process, at $V_{\rm D}$ = 1.1 V                                            | 122 |

| 8.13 | Normalized imaginary part of the Y-parameters vs. frequency of a minimum                                      |     |

|      | channel length RF nMOS DUT of a 40 nm CMOS process, at $V_{\rm D}$ = 1.1 V                                    | 123 |

| 8.14 | $ H_{21} $ vs. frequency and $F_t$ vs. <i>IC</i> of a minimum channel length RF nMOS DUT                      |     |

|      | of a 40 nm CMOS process.                                                                                      | 124 |

| 8.15 | $U$ vs. frequency and $F_{\rm max}$ vs. $IC$ of a minimum channel length RF nMOS DUT of                       |     |

|      | a 40 nm CMOS process.                                                                                         | 125 |

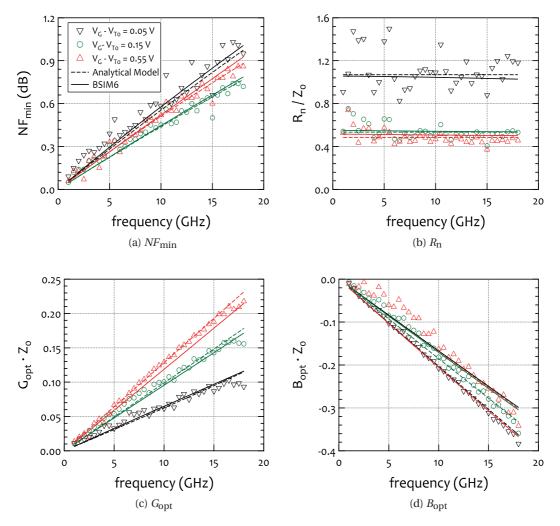

| 8.16 | The four RF noise parameters vs. frequency of a minimum channel length RF                                     |     |

|      | nMOS DUT of a 40 nm CMOS process, at $V_{\rm D}$ = 0.3 V                                                      | 126 |

| 8.17 | The four RF noise parameters vs. frequency of a minimum channel length RF                                     |     |

|      | nMOS DUT of a 40 nm CMOS process, at $V_{\rm D}$ = 1.1 V                                                      | 127 |

| 8.18 | $NF_{min}$ and $R_n$ vs. <i>IC</i> of a minimum channel length RF nMOS DUT of a 40 nm                         |     |

|      | CMOS process.                                                                                                 | 128 |

| 8.19 | Normalized capacitances $c_{gg}$ , $c_{gb}$ , $c_{gd}$ for nMOS DC DUTs of a 28 nm CMOS                       |     |

|      | process for different channel lengths.                                                                        | 129 |

| 8.20 | Normalized drain current $i_d$ and gate transconductance $g_m$ vs. $V_G - V_{T0}$ for                         |     |

|      | nMOS DC DUTs of a 28 $$ nm CMOS process for different channel lengths                                         | 131 |

| 8.21 | Normalized drain current $i_d$ and its derivative $g_{ds}$ vs. $V_D$ for nMOS and pMOS                        |     |

|      | DC DUTs of a 28 nm CMOS process for different channel lengths                                                 | 132 |

| 8.22 | Length Scaling of SS, $v_{tb}$ and max( $i_d$ ) for nMOS DC DUTs of a 28 nm CMOS                              |     |

|      | process                                                                                                       | 133 |

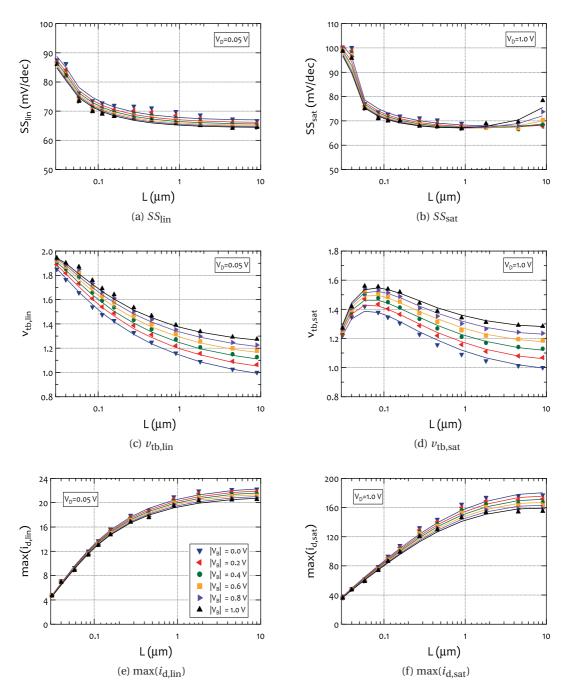

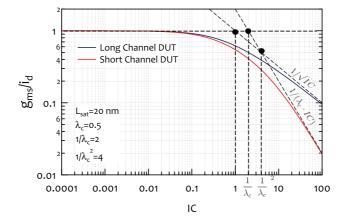

| 9.1  | $g_{\rm ms}$ vs. IC in saturation for a short and a long-channel device.                                      | 130 |

| 0.1  |                                                                                                               | 100 |

### List of Figures

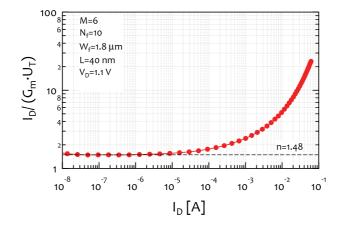

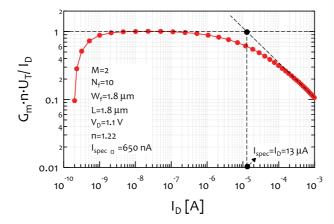

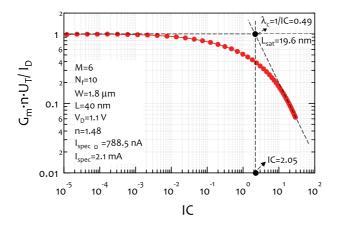

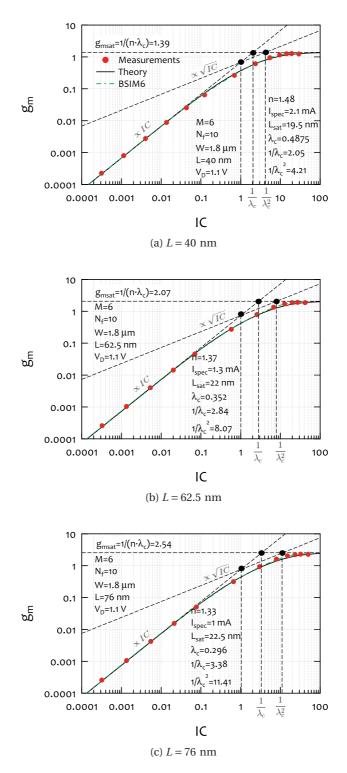

| 9.2  | $g_{ m ms}/i_{ m d}$ vs. IC in saturation for a short and a long-channel device                                 | 141 |

|------|-----------------------------------------------------------------------------------------------------------------|-----|

| 9.3  | Extraction of the slope factor <i>n</i>                                                                         | 142 |

| 9.4  | Extraction of the specific current $I_{\text{spec}}$ .                                                          | 143 |

| 9.5  | Extraction of the velocity saturation parameter $\lambda_c$                                                     | 144 |

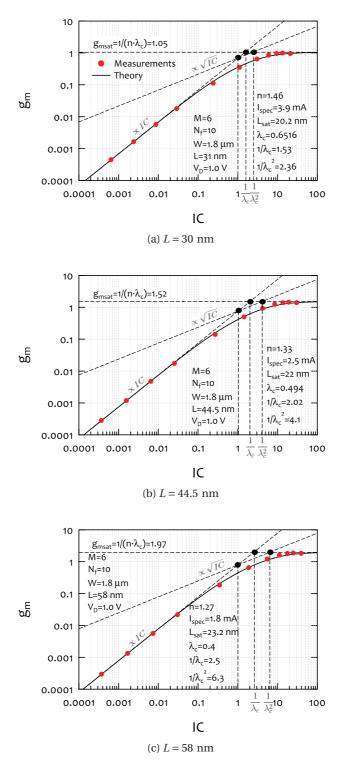

| 9.6  | Normalized transconductance $g_m$ vs. IC for three RF DUTs of a 40 nm CMOS                                      |     |

|      | process. Comparison between theory, measurements and BSIM6                                                      | 145 |

| 9.7  | Normalized transconductance $g_m$ vs. IC for three RF DUTs of a 28 nm CMOS                                      |     |

|      | process. Comparison between theory and measurements                                                             | 146 |

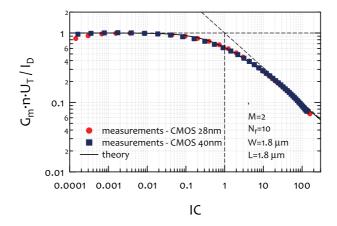

| 9.8  | Transconductance efficiency $G_{\rm m} \cdot n \cdot U_{\rm T} / I_{\rm D}$ vs. IC for long RF DUTs of 28 nm    |     |

|      | and 40 nm CMOS process.                                                                                         | 147 |

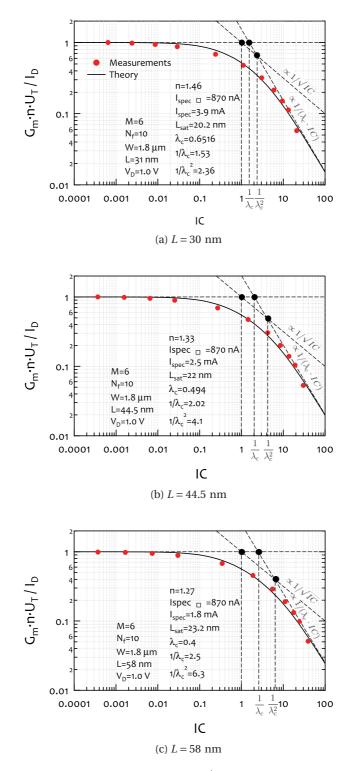

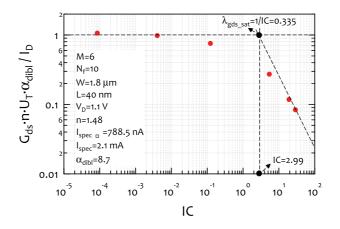

| 9.9  | Transconductance efficiency $G_{\rm m} \cdot n \cdot U_{\rm T} / I_{\rm D}$ vs. IC for three RF DUTs of a 40 nm |     |

|      | CMOS process. Comparison between theory, measurements and BSIM6                                                 | 148 |

| 9.10 | Transconductance efficiency $G_{\rm m} \cdot n \cdot U_{\rm T} / I_{\rm D}$ vs. IC for three RF DUTs of a 28 nm |     |

|      | CMOS process. Comparison between theory and measurements.                                                       | 149 |

| 9.11 | Extraction of the parameter $\lambda_{sat_gds}$                                                                 | 152 |

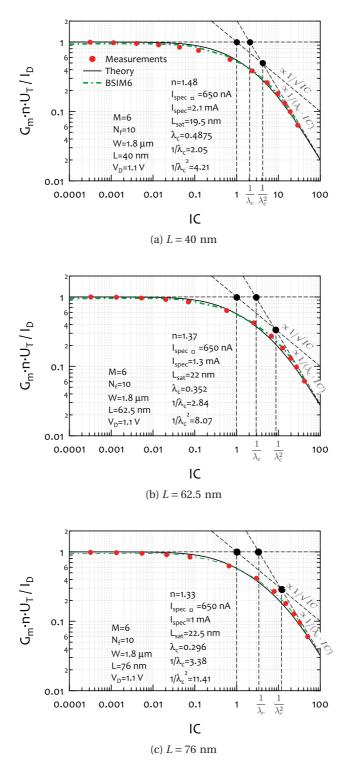

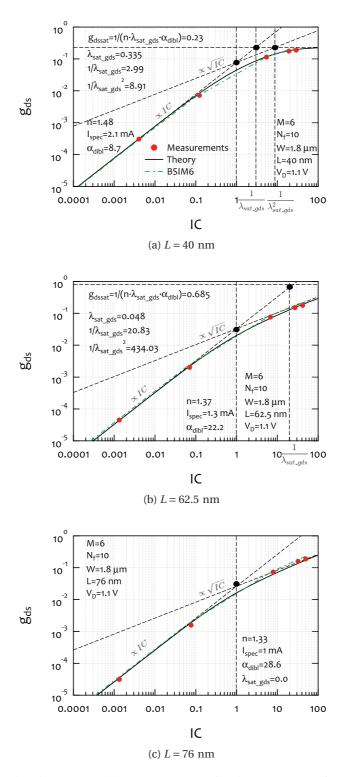

|      | Normalized output conductance $g_{ds}$ vs. IC for three RF DUTs of a 40 nm CMOS                                 |     |

|      | process. Comparison between theory, measurements and BSIM6                                                      | 153 |

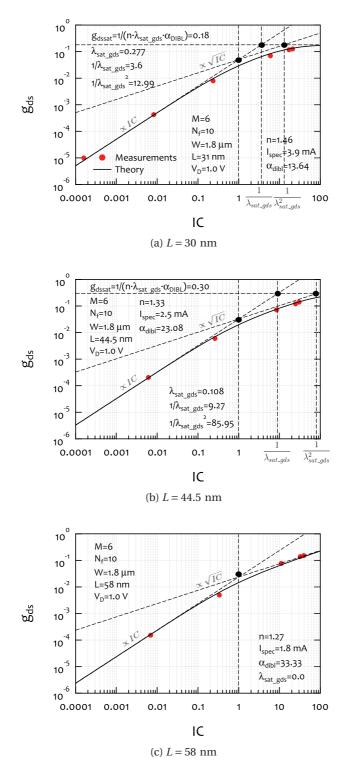

| 9.13 | Normalized output conductance $g_{ds}$ vs. IC for three RF DUTs of a 28 nm CMOS                                 |     |

|      | process. Comparison between theory and measurements                                                             | 154 |

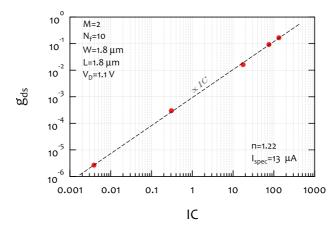

| 9.14 | Normalized output conductance $g_{ds}$ vs. IC for a long-channel RF DUT of a                                    |     |

|      | 40 nm CMOS process                                                                                              | 155 |

| 9.15 | Simple MOS amplifier in a CS configuration.                                                                     | 156 |

| 9.16 | 5 Intrinsic voltage gain $A_{v_i}$ vs. IC for three RF DUTs of a 40 nm CMOS process.                            |     |

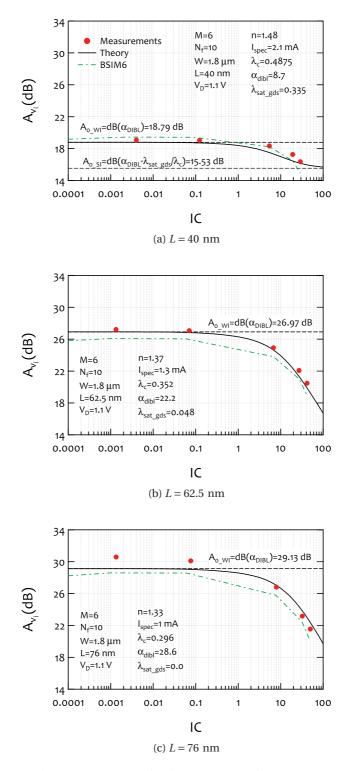

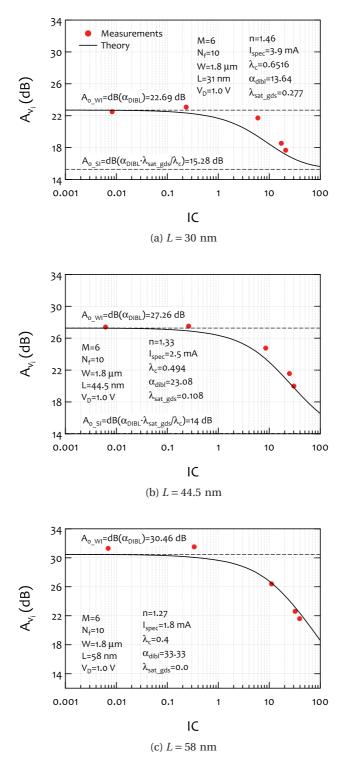

|      | Comparison between theory, measurements and BSIM6                                                               | 157 |

| 9.17 | Intrinsic voltage gain $A_{v_i}$ vs. IC for three RF DUTs of a 28 nm CMOS process.                              |     |

|      | Comparison between theory and measurements.                                                                     | 158 |

| 9.18 | Transit frequency $F_t$ vs. IC and extraction of the parameter $C_{G_{ew}}$ .                                   | 161 |

| 9.19 | Normalized transit frequency $f_t$ vs. IC for three RF DUTs of a 40 nm CMOS                                     |     |

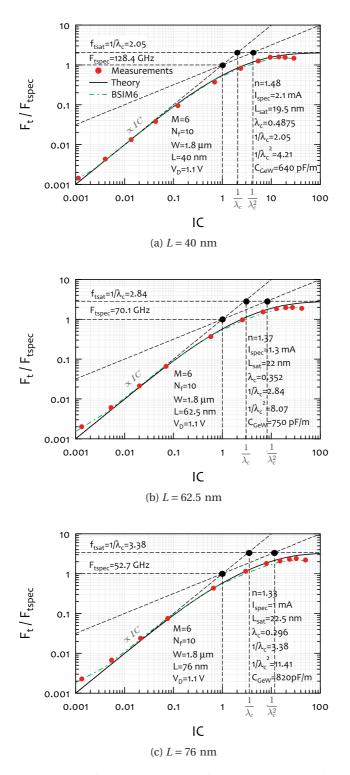

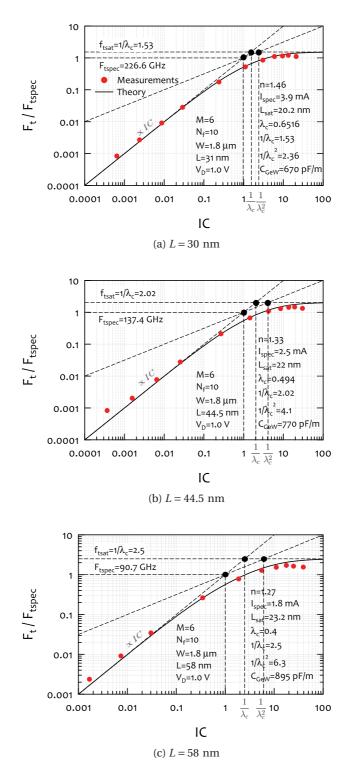

|      | process. Comparison between theory, measurements and BSIM6                                                      | 162 |

| 9.20 | Normalized transit frequency $f_t$ vs. IC for three RF DUTs of a 28 nm CMOS                                     |     |

|      | process. Comparison between theory and measurements                                                             | 163 |

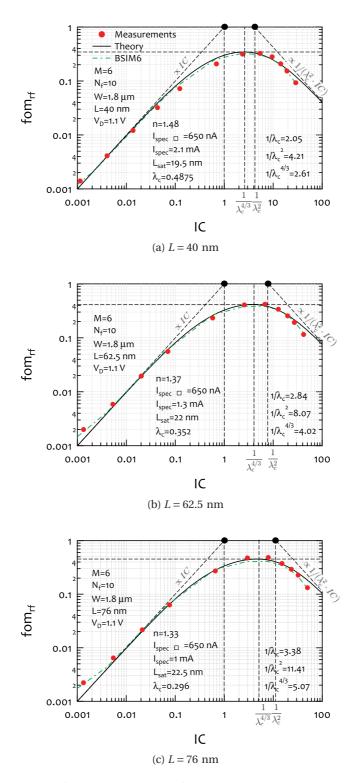

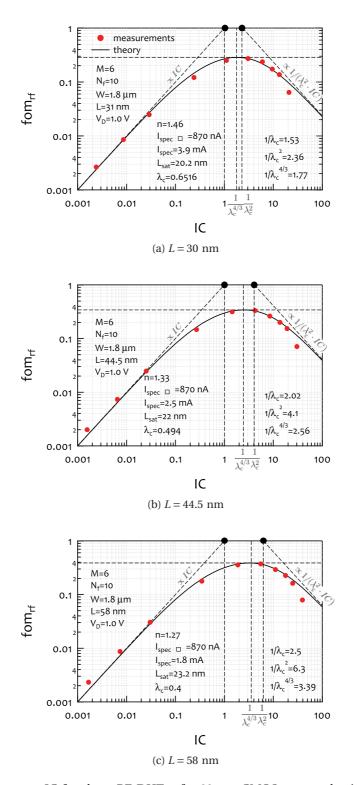

| 9.21 | $fom_{\rm rf}$ vs. IC for three RF DUTs of a 40 nm CMOS process. Comparison between                             |     |

|      | theory, measurements and BSIM6                                                                                  | 165 |

| 9.22 | $fom_{\rm rf}$ vs. IC for three RF DUTs of a 28 nm CMOS process. Comparison between                             |     |

|      | theory and measurements.                                                                                        | 166 |

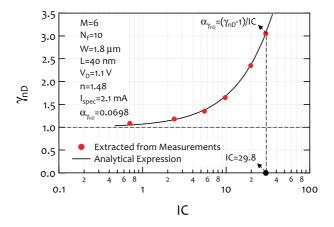

| 9.23 | $\gamma_{nD}$ vs. IC and extraction of the parameter $\alpha_{\gamma_{nD}}$                                     | 168 |

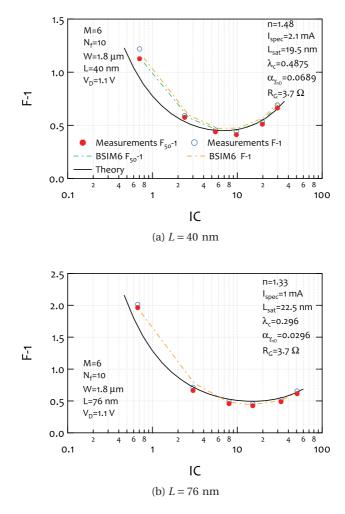

| 9.24 | RF noise $F - 1$ vs. IC for two RF DUTs of a 40 nm CMOS process. Comparison                                     |     |

|      | between theory, measurements and BSIM6                                                                          | 169 |

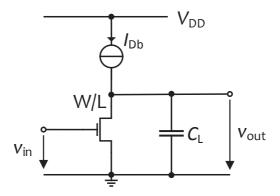

| 9.25 | Single-MOS capacitively loaded CS amplifier.                                                                    | 170 |

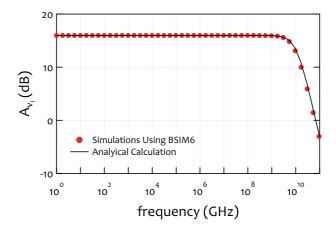

| 9.26 | $A_v$ vs. frequency of a single-MOS capacitively loaded CS amplifier at $IC_{spot}$ and                         |     |

|      | $I_{\mathrm{D}_{\mathrm{b}_{\mathrm{spot}}}}$ for a short channel device.                                       | 171 |

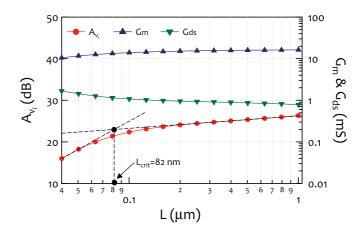

| 9.27    | $A_{v_i}$ , $G_m$ , $G_{ds}$ vs. L of a single-MOS capacitively loaded CS amplifier at $IC_{spot}$ and                        |     |

|---------|-------------------------------------------------------------------------------------------------------------------------------|-----|

|         | $I_{\mathrm{D}_{\mathrm{b}_{\mathrm{spot}}}}$                                                                                 | 171 |

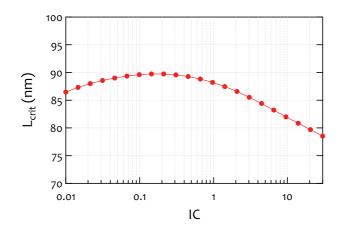

| 9.28    | $L_{\text{crit}}$ vs. <i>IC</i> of a single-MOS capacitively loaded CS amplifier at $I_{\text{D}_{b_{\text{spot}}}}$          | 173 |

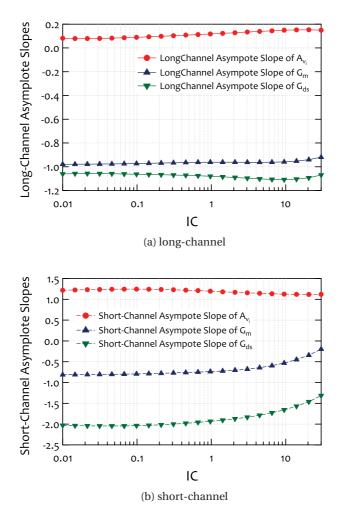

| 9.29 \$ | Slopes of the long- and short-channel asymptotes of $A_{v_i}$ , $G_m$ and $G_{ds}$ across $IC$                                |     |

| (       | of a single-MOS capacitively loaded CS amplifier at $I_{D_{b_{spot}}}$                                                        | 173 |

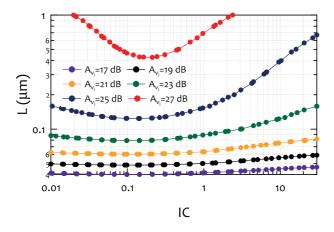

| 9.30    | $A_{v_i}$ contours for different <i>IC</i> and <i>L</i> of a single-MOS capacitively loaded CS am-                            |     |

| ]       | plifier at $I_{\mathrm{D}_{\mathrm{b}_{\mathrm{spot}}}}$ .                                                                    | 174 |

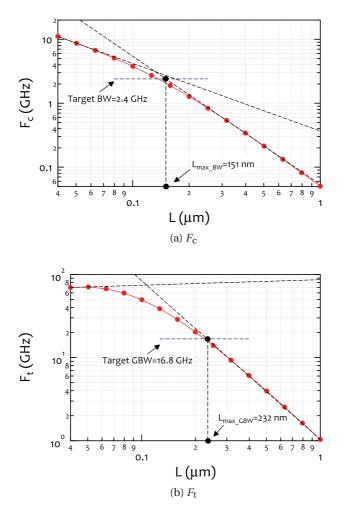

| 9.31    | $F_{\rm c}$ and $F_{\rm t}$ vs. L of a single-MOS capacitively loaded CS amplifier at $IC_{\rm spot}$ and                     |     |

|         | $I_{\mathrm{D}_{\mathrm{b}_{\mathrm{spot}}}}$                                                                                 | 176 |

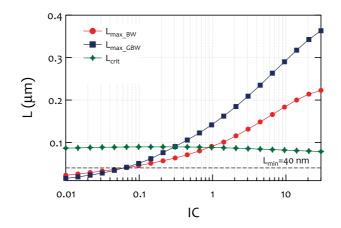

|         | $L_{\text{crit}}$ , $L_{\text{max}_{BW}}$ and $L_{\text{max}_{GBW}}$ vs. <i>IC</i> of a single-MOS capacitively loaded CS am- |     |

| ]       | plifier at $I_{\mathrm{D}_{\mathrm{b}_{\mathrm{spot}}}}$ .                                                                    | 176 |

# List of Tables

| 4.1 | Long-channel values of the three RF noise model parameters in saturation                                                                                                                                                     | 53 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.1 | Description of the normalization process                                                                                                                                                                                     | 82 |

| 7.1 | Process parameters which are recommended to be provided before starting the parameter extraction procedure with BSIM6. Parameters that are followed by an asterisk (*) should be considered as the most important among them | 90 |

# Symbols

### **Physical Parameters**

| k       | Boltzmann's Constant           |

|---------|--------------------------------|

| Т       | Absolute Temperature in Kelvin |

| $\mu_0$ | Low-field Mobility Constant    |

## Voltages

| $U_{\mathrm{T}}$ | Thermodynamic Voltage                         |

|------------------|-----------------------------------------------|

| V <sub>D</sub>   | Drain Voltage                                 |

| V <sub>G</sub>   | Gate Voltage                                  |

| VS               | Source Voltage                                |

| $V_{\rm B}$      | Bulk Voltage                                  |

| V <sub>T0</sub>  | Threshold Voltage at $V_{SB} = 0 V$           |

| V <sub>TB</sub>  | Threshold Voltage at $V_{\text{SB}} \neq 0 V$ |

#### Currents

| ID                | Drain Current               |

|-------------------|-----------------------------|

| I <sub>Dsat</sub> | Drain Current in Saturation |

| <i>i</i> d        | Normalized Drain Current    |

| IC                | Inversion Coefficient       |

|                   |                             |

## **Conductances and Transconductances**

| G <sub>m</sub>  | Gate Transconductance              |

|-----------------|------------------------------------|

| G <sub>ms</sub> | Source Transconductance            |

| G <sub>ds</sub> | Output Conductance                 |

| gm              | Normalized Gate Transconductance   |

| g <sub>ms</sub> | Normalized Source Transconductance |

| gds             | Normalized Output Conductance      |

### Symbols

## Capacitances and Transcapacitances

| Cox                             | Oxide Capacitance per Unit Area                        |

|---------------------------------|--------------------------------------------------------|

| C <sub>OX</sub>                 | Total Oxide Capacitance                                |

| $C_{ m GG}$                     | Total Gate Capacitance                                 |

| $C_{ m GG_i}$                   | Intrinsic Part of the Total Gate Capacitance           |

| $C_{\mathrm{GG}_{\mathrm{e}}}$  | Extrinsic Part of the Total Gate Capacitance           |

| $C_{\mathrm{GG}_{\mathrm{eW}}}$ | Extrinsic Part of the Total Gate Capacitance per Width |

| $C_{ m GS}$                     | Total Gate-to-Source Capacitance                       |

| $C_{GS_i}$                      | Intrinsic Part of the Total Gate-to-Source Capacitance |

| $C_{GS_e}$                      | Extrinsic Part of the Total Gate-to-Source Capacitance |

| $C_{ m GD}$                     | Total Gate-to-Drain Capacitance                        |

| $C_{ m GD_{WL}}$                | Total Gate-to-Drain Capacitance per Unit Area          |

| $C_{ m GD_i}$                   | Intrinsic Part of the Total Gate-to-Drain Capacitance  |

| $C_{\mathrm{GD}_{\mathrm{e}}}$  | Extrinsic Part of the Total Gate-to-Drain Capacitance  |

| $C_{ m GB}$                     | Total Gate-to-Bulk Capacitance                         |

| $C_{\mathrm{GB}_{\mathrm{i}}}$  | Intrinsic Part of the Total Gate-to-Bulk Capacitance   |

| $C_{\mathrm{GB}_{\mathrm{e}}}$  | Extrinsic Part of the Total Gate-to-Bulk Capacitance   |

| $C_{\rm SB}$                    | Total Source-to-Bulk Capacitance                       |

| $C_{\mathrm{SB}_{\mathrm{i}}}$  | Intrinsic Part of the Total Source-to-Bulk Capacitance |

| $C_{\mathrm{SB}_{\mathrm{j}}}$  | Source-to-Bulk Junction Capacitance                    |

| $C_{\mathrm{DB}}$               | Total Drain-to-Bulk Capacitance                        |

| $C_{\mathrm{DB}_{\mathrm{i}}}$  | Intrinsic Part of the Total Drain-to-Bulk Capacitance  |

| $C_{\mathrm{DB}_{\mathrm{j}}}$  | Drain-to-Bulk Junction Capacitance                     |

| $C_{\mathrm{BB}}$               | Total Bulk Capacitance                                 |

| C <sub>m</sub>                  | Intrinsic Gate Transcapacitance                        |

| C <sub>ms</sub>                 | Intrinsic Source Transcapacitance                      |

|                                 |                                                        |

#### Resistances

| R <sub>G</sub> | Gate Series Resistance   |

|----------------|--------------------------|

| R <sub>S</sub> | Source Series Resistance |

| R <sub>D</sub> | Drain Series Resistance  |

| R <sub>B</sub> | Bulk Series Resistance   |

## Frequencies

| Ft               | Transit or Cut-off Frequency            |

|------------------|-----------------------------------------|

| $f_{\mathrm{t}}$ | Normalized Transit or Cut-off Frequency |

| F <sub>max</sub> | Maximum Oscillation Frequency           |

| F <sub>c</sub>   | 3-dB Corner Frequency                   |

#### Noise

| F                                | Noise Factor                                        |

|----------------------------------|-----------------------------------------------------|

| F <sub>min</sub>                 | Minimum Noise Factor                                |

| NF                               | Noise Figure                                        |

| NF <sub>min</sub>                | Minimum Noise Figure                                |

| R <sub>n</sub>                   | Input-referred Thermal Noise Voltage Resistance     |

| Gs                               | Source Conductance                                  |

| Bs                               | Source Susceptance                                  |

| Y <sub>opt</sub>                 | Optimum Source Admittance                           |

| Gopt                             | Optimum Source Conductance                          |

| Bopt                             | Optimum Source Susceptance                          |

| $\gamma_{ m nD}$                 | Thermal Noise Excess Factor at the Drain            |

| $\delta_{ m nG}$                 | Thermal Noise Parameter at the Gate                 |

| Cg                               | Gate-Drain Thermal Noise Correlation Parameter      |

| $lpha_{\gamma_{ m nD}}$          | $\gamma_{\rm nD}$ Factor Parameter                  |

| I <sub>nD</sub>                  | Channel Thermal Noise                               |

| $S_{I_{nD}^2}$                   | Power Spectral Density of the Channel Thermal Noise |

| I <sub>nG</sub>                  | Induced Gate Noise                                  |

| $S_{\mathrm{I}^2_{\mathrm{nG}}}$ | Power Spectral Density of the Induced Gate Noise    |

## Other

| $E_{\mathbf{g}}$              | Energy Band-Gap                                              |

|-------------------------------|--------------------------------------------------------------|

| $E_{\rm x}$                   | Longitudinal Electric Field                                  |

| $E_{\mathbf{c}}$              | Critical Electric Field                                      |

| n                             | Slope Factor                                                 |

| $v_{ m drift}$                | Drift Velocity of the Carriers                               |

| $v_{\rm sat}$                 | Saturation Velocity of the Carriers                          |

| $\lambda_{ m c}$              | Velocity Saturation Parameter                                |

| L <sub>sat</sub>              | Channel Length Demonstrating Velocity Saturation             |

| $lpha_{ m dibl}$              | DIBL Parameter                                               |

| $\lambda_{\mathrm{sat\_gds}}$ | $G_{\rm ds}$ Saturation Parameter                            |

| $A_{ m v}$                    | Voltage Gain                                                 |

| $A_{ m v_i}$                  | Intrinsic Voltage Gain                                       |

| L <sub>crit</sub>             | Critical Length below which the $A_{v_i}$ is affected by SCE |

| $L_{\max\_BW}$                | Maximum Length to achieve a specific BW                      |

| $L_{\max\_\text{GBW}}$        | Maximum Length to achieve a specific GBW                     |

| H <sub>21</sub>               | Current Gain                                                 |

| U                             | Unilateral Gain                                              |

### Symbols

#### **Normalization Factors**

| $I_{	ext{spec}_{\Box}}$ | Specific Current per Square           |

|-------------------------|---------------------------------------|

| $I_{ m spec}$           | Specific Current                      |

| G <sub>spec</sub>       | Specific Conductance                  |

| R <sub>spec</sub>       | Specific Resistance                   |

| $F_{\mathrm{t_{spec}}}$ | Specific Transit or Cut-off Frequency |

# Main Acronyms and Abbreviations

| BJT    | Bipolar Junction Transistor                       |

|--------|---------------------------------------------------|

| BSIM   | Berkeley Short-channel IGFET Model                |

| BW     | Bandwidth                                         |

| GBW    | Gain-Bandwidth                                    |

| CLM    | Channel Length Modulation                         |

| CMOS   | Complementary Metal-Oxide-Semiconductor           |

| CS     | Common-Source                                     |

| DIBL   | Drain Induced Barrier Lowering                    |

| DITS   | Drain Induced Threshold Shift                     |

| DUT    | Device Under Test                                 |

| ECB    | Electron tunneling from Conduction Band           |

| FD-SOI | Fully-Depleted Silicon-on-Insulator               |

| FET    | Field Effect Transistor                           |

| FinFET | Fin Field-Effect-Transistor                       |

| FoM    | Figure-of-Merit                                   |

| GIDL   | Gate Induced Drain Leakage                        |

| GISL   | Gate Induced Source Leakage                       |

| IC     | Integrated Circuit                                |

| LUT    | Look-Up Table                                     |

| MI     | Moderate-Inversion                                |

| MOS    | Metal-Oxide-Semiconductor                         |

| MOSFET | Metal-Oxide-Semiconductor Field-Effect-Transistor |

| nMOS   | n-type Metal-Oxide-Semiconductor                  |

| NQS    | Non-Quasi-Static                                  |

| pMOS   | p-type Metal-Oxide-Semiconductor                  |

| PSD    | Power Spectral Density                            |

| QS     | Quasi-Static                                      |

| RF     | Radio-Frequencies                                 |

| SCE    | Sort-Channel Effects                              |

| SEM    | Scanning Electron Microscope                      |

| SI     | Strong-Inversion                                  |

|        |                                                   |

### Acronyms and Abbreviations

| Т    | Temperature                      |

|------|----------------------------------|

| TCAD | Technology Computer Aided Design |

| VSAT | Velocity Saturation              |

| WI   | Weak-Inversion                   |

# **1** Introduction

#### **1.1 Motivation**

Over the past decades, the microelectronics industry has managed to follow the Moore's law [1] by continuously scaling down the transistor's dimensions in order to improve its performance and reduce the power consumption and cost of the system. In recent years, the state-of-the-art downscaled CMOS processes provide smaller and faster devices, in the order of a few tens of nanometers in terms of the gate length. Although increasing the speed and density of integration of advanced Systems-on-Chip (SoCs) is important, reducing the power consumption remains a high priority for ultra-low-power applications like Internet-of-Things (IoT), Wireless-Sensor-Networks (WSN), Wireless-Body-Area-Networks (WBAN), self-powered and energy-harvesting systems, etc. These kinds of applications pose stringent constraints on power consumption, becoming the driving force towards low-power analog and RF circuit design.

Advanced nanoscale CMOS devices display very high peak transit frequency  $F_t$  of several hundreds of GHz and sub-1 dB minimum noise figure  $NF_{min}$  [2–4]. Nonetheless, the operating frequency of numerous RF applications remains significantly lower. Thanks to this very high  $F_t$  and the low  $NF_{min}$  the design of ultra-low-power RF applications has become feasible, with the nanoscale MOSFETs constituting the most attractive solution. The high transit frequency can be traded-off with lower power consumption, by shifting the operating point towards lower levels of inversion. In moderate-inversion, for advanced nanoscale devices, the transistor benefits from a minimum value of the  $NF_{min}$  while the  $F_t$  remains in the GHz range [5]. An even more aggressive policy, that would bring the operating point in weak-inversion, would further minimize the power consumption at the expense of a considerable degradation of the  $F_t$  and  $NF_{min}$ . Depending on the constraints of the application and the capabilities of the technologies, the designer is to search for the best trade-off in this design hunt.

In such extreme operating conditions, i.e. low current density and RF, an accurate and reliable description of the behavior of the MOS transistor is an indispensable tool for a successful

design. Compact models, thus, have to play their crucial role in facilitating the complex task of RF IC design. A lot of effort has already been put into characterization and modeling of the MOS transistor in RF, however, most of the published work is focused either on the high-performance strong-inversion region or on more mature processes with respect to the state-of-the-art.

The main motivation behind this research work, has been to explore whether the aggressive downscaling of MOSFET, along with the new fabrication techniques, has resulted in physical phenomena that cause a deviation from the "well-known" behavior of the transistor in state-of-the-art technologies, with a strong focus on the sub-threshold region. Towards this direction, different modeling aspects were investigated. First, there was the BSIM6 compact model which was evaluated thoroughly and enhanced where this was necessary. Then, a set of analytical expressions that allowed us to study the RF behavior of the nanoscale devices from weak- to strong-inversion, including the RF noise, were developed. Finally, we employed and further developed simple analytical expressions that can be used by designers to have a first insight in different Figures-of-Merit (FoMs) of advanced MOS transistors for the whole range of the inversion coefficient (*IC*), based on the *IC* design methodology. To fulfill this task, measurements of real devices of two commercial advanced CMOS technologies, namely 40 nm and 28 nm, were used.

#### 1.2 The MOS Transistor

Modern electronics is the natural evolution of a field the seeds of which may be found even millenia before today [6, 7]. However, the development of electronics boosted the last century and it has been exponentially progressing the last decades. Societal evolution, in all aspects and science included, is directed by the needs that emerge and have to be taken care of. More particularly, electronics have been used in order to support the needs of mankind in different ways like sensing, communicating and reproducing information over long distances or processing and storing information in heavy workloads. For the first kind of applications, it is mainly the analogue electronics that have found room of manifesting their capabilities, while for the latter, those are mainly performed by using digital electronics, a major spin-off of the electronics industry, which is big enough to deserve the title of a field on its own. Even though there is a wide common area between analogue and digital electronics, there are also important characteristics which differentiate the two fields and which result in their distinction.

One major development that drove significantly the advancement of electronics was the invention of a three-terminal device at the beginning of the 20<sup>th</sup> century [8,9]. This element was later called triode because of the fact that it was adding a third electrode to the already available diode devices. Practically, this third electrode was connected to a grid placed inside the electron tube and between the first two electrodes, and in this way was able to control the

conduction between the other two electrodes.

This evolution was revolutionary for the field. One could say that it practically gave birth to the electronics field in the form that we know it today. In any case, everyone would agree that this step brought the field to a totally new level with much more possibilities than before. The limitation of the two terminal devices limited the whole circuit design to passive topologies. The introduction of the third terminal primed the device with a pair of input and output ports. Subsequently, the operational capabilities were drastically multiplied giving space for amplification techniques of an input signal to the output, new possibilities for sensing of an event at the input and translating this electrically at the output of the device and processing signals and information.

Even though, qualitatively the triode, as a device, is a might element that did allow electronics to go into a wide range of applications, it also contained certain limitations that where not allowing the field of electronics to reveal its maximum potential. These issues were mostly related to fabrication characteristics, such as reliability and cost. The next step that expanded further the horizons of electronics was the introduction of solid-state semi-conducting materials, such as the Silicon ( $_{14}$ Si), as the core element of the electron devices [10], that came out at the 1950's. Progressively with time, this novel platform of materials was accompanied by advanced fabrication techniques that crucially mitigated reliability issues and drove the implementation cost to lower and lower levels.

The first successful transistor in solid-state electronics was the Bipolar Junction Transistor (BJT) [11]. The advantages that it brought to electronics were unforeseeable. Compared to its predecessor, the triode vacuum tube, it was characterized by a much smaller size, much more reliable performance, lower cost, and more convenient fabrication technique both in terms of a single device and in the perspective of a whole electronic system as well. Roughly speaking, the BJT is a current-controlled current source. Similarly to the electron tube based triode, its active nature of a three terminal device, where one port controls the conductive state of another, kept open all the topologies that were evolved with previous technologies. This time, the limit was set by a finer detail of the performance of the element, that was mainly the nature of its input gate. Between the base and the emitter the device is essentially a forward bias diode, which, even though can be used in order to control the much higher current of the collector, its power consumption is not negligible. On the course of time, its energy footprint became its Achilles' heal that needed to be dealt with.

At that time, the Field-Effect-Transistor, came to the rescue. The MOSFET as an architecture of a device had already been envisioned, in parallel to the evolution of the vacuum tubes [12, 13]. Yet, it was not till the 1970's that the device was introduced in a wide scale in the field of electronics. The major improvement that is characterizing the MOSFET is that it transforms the transistor from a current-controlled current source, such as the BJT is, to a voltage-controlled current source. This is done by introducing an oxide layer at the input node of the device,

#### **Chapter 1. Introduction**

which is the Gate in the MOSFET and the Base in the BJT. Apart from this addition, there is an important degree of similarities between the operation of the two transistors, even though, it must be underlined that the oxide layer reconstructs from the scratch all the physical mechanisms that take place in the transistor.

The MOSFET contained a key characteristic that allowed it to be the vessel that formed the electronics in the shape that we know it today and that is the vehicle that has brought the field into the modern age. The lithographic way that the crucial dimension of the device is designed, i.e. the gate length, allowed the fabrication processes to embark on a down-scaling quest that started from the very beginning of the CMOS technologies and which is still going on even today [1]. The observation that the amount of transistors per chip will follow a certain exponential trend with time was the first instantiation of the Moore's Law, which later on was updated to a certain trend of the exponential decrease of the gate length of the MOSFET with time. This trip allowed the technologies to shrink from a minimum gate length in the order of tens of micrometers during the first CMOS technologies in the 1960's to the deep sub-micrometer technologies of todays, where the minimum gate length is in the order of few tens of nanometers, if not even lower [14, 15].

In term of performance, the reduction of the gate length of the device has resulted into a major evolution. The speed of the transistor as a switch and its maximum operational frequency of the device as an analogue element is inversely proportional to the square of this characteristic dimension [16]. The aggressive downscaling has revealed a wide spectrum of capabilities and application on which the CMOS technologies can be an ideal tool to provide high-performance solutions. This benefits both the fields of digital and analogue electronics.