# Hybrid NRZ/Multi-Tone Signaling for High-Speed Low-Power Wireline Transceivers

## THÈSE Nº 6965 (2016)

PRÉSENTÉE LE 15 AVRIL 2016

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR

LABORATOIRE DE SYSTÈMES MICROÉLECTRONIQUES

PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

## ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

#### PAR

## Kiarash GHARIBDOUST

acceptée sur proposition du jury:

Dr J.-M. Sallese, président du jury Prof. Y. Leblebici, Dr S. A. Tajalli, directeurs de thèse Prof. P. K. Hanumolu, rapporteur Dr T. Toifl, rapporteur Prof. A. Shokrollahi, rapporteur

The only thing greater than the power of the mind is the courage of the heart. — John Nash

To my wife Haniyeh, my mother Parvaneh and to the memory of my father  $\dots$

# Acknowledgements

This thesis work would not have been possible without all the people that supported me throughout these years. I have been especially lucky to have had so many great people helping me out with different aspects of my life in EPFL.

I would first like to express my sincere gratitude to my advisor, Prof. Yusuf Leblebici for his endless support, for his patience, motivation, and immense knowledge. His guidance helped me to overcame the biggest obstacles I faced during my PhD, both on technical and non-technical sides. I would like to thank him for his tolerance and patience in letting me explore different ideas, and for always encouraging me to think revolutionary about the issues that I faced. I am extremely thankful to my co-advisor, Dr. Armin Tajalli, for his advices and the fruitful discussions during the entire length of my PhD studies. I do appreciate his interest, commitment and responsibility to my work. He has always been kind to me with any questions during the course of my PhD research.

I am very grateful towards the members of my thesis committee: Prof. Pavan Kumar Hanumolu, Dr. Thomas Toifl, Prof. Amin Shokrollahi and Dr. Jean-Michel Sallese for taking the time to read this manuscript and provide feedback. I would like to thank Dr. Alain Vachoux for his timeless support on CAD tools and Dr. Alexandre Schmid for his support with computing infrastructure.

I am indebted to my master thesis advisor, Prof. Mehrdad Sharif Bakhtiar for always encouraging me in finding new solutions and giving me the best advice. Most part of my PhD research relies on the analog design techniques, which I learned from this master. I am grateful to Prof. Sadegh Jamali, my undergraduate professor, for always supporting me and help me out in the most difficult time of my undergraduate study.

I am thankful towards my colleagues with whom discussions have been source of new ideas and solutions to difficult problems: Dr. Vahid Majidzadeh, Dr. Alessandro Cevrero, Dr. Hossein Afshari and Dr. Nikola Katic.

Many people in EPFL have contributed to this work. I acknowledge Gain Kim for his assistance on system level analysis and simulation. I should thank Masoud Shahshahani for his assistance in silicon measurements. I acknowledge Cosimo Aprile, Jonathan Narinx, Elmira Shahrabi and Jury Sandrini for their positive attitude and the useful discussions during all the coffee breaks. Having good friends like them made everything nicer in

EPFL for me. Thanks to Sylvain Hauser, for his patience and kind support for providing the test setups for prototype measurements. I would like to thank Dr. Mahbod Heidari and Dr. Omid Talebi for their great friendship and support.

I am grateful to my colleagues in Microelectronic Systems Laboratory (LSM) for their friendship, fruitful discussions and collaborations: Dr. Radisav Cojbasic, Dr. Vladan Popovic, Dr. Masha Shoaran, Reza Ranjandish, Sebastian Rodriguez, Seniz Kucuk and also amazing Kerem Seyid.

I am hugely indebted to my parents, my brother and other family members who always believed in me. Their timeless and countless supports were always motivating during all years of my education. I am very thankful to my brother Kianoosh for his constant love, and for filling in for me at home while I have been away.

My special thanks and enormous gratitude go to my mother Parvaneh for always believing in me, and supporting me with her infinite motherly love. Her unconditional love has been always the major source of motivation for me during all my life.

I would like to greatly thank my beloved wife Haniyeh for giving me the reason to be happy, and strength to work and live. I owe a special thanks to her for always supporting me with her patience and everlasting love, and bearing with times of my mental and physical absence. Without any doubt, she is the secret of my success. I am also very grateful to Haniyeh's family, and especially my mother-in-law Farideh, for being extremely kind and supportive to me in these years.

Going through my life period, I have had many great advisors and teachers. Without any doubt, my father was one of the greatest teacher and also my best friend among them all. Although I lost him many years ago, I can still get enormous motivation by his memory. I am hugely indebted to him and I just hope that some day I will repay the debt by trying to approach the parenting ideal that he set by his example.

Lausanne, 11 March 2016

Kiarash Gharibdoust.

# Abstract

Over the past few decades, incessant growth of Internet networking traffic and High-Performance Computing (HPC) has led to a tremendous demand for data bandwidth. Digital communication technologies combined with advanced integrated circuit scaling trends have enabled the semiconductor and microelectronic industry to dramatically scale the bandwidth of high-loss interfaces such as Ethernet, backplane, and Digital Subscriber Line (DSL). The key to achieving higher bandwidth is to employ equalization technique to compensate the channel impairments such as Inter-Symbol Interference (ISI), crosstalk, and environmental noise. Therefore, today's advanced input/outputs (I/Os) has been equipped with sophisticated equalization techniques to push beyond the uncompensated bandwidth of the system.

To this end, process scaling has continually increased the data processing capability and improved the I/O performance over the last 15 years. However, since the channel bandwidth has not scaled with the same pace, the required signal processing and equalization circuitry becomes more and more complicated. Thereby, the energy efficiency improvements are largely offset by the energy needed to compensate channel impairments. Moreover, as the supply voltage scaling has saturated in finer technology nodes, the power dissipation in digital circuits cannot benefit from voltage scaling, hence, the overall energy-efficiency improvement has diminished.

In this design paradigm, re-thinking about the design strategies in order to not only satisfy the bandwidth performance, but also to improve power-performance becomes an important necessity. It is well known in communication theory that coding and signaling schemes have the potential to provide superior performance over band-limited channels. However, the choice of the optimum data communication algorithm should be considered by accounting for the circuit level power-performance trade-offs.

In this thesis we have investigated the application of new algorithm and signaling schemes in wireline communications, especially for communication between microprocessors, memories, and peripherals. A new hybrid NRZ/Multi-Tone (NRZ/MT) signaling method has been developed during the course of this research. The system-level and circuit-level analysis, design, and implementation of the proposed signaling method has been performed in the frame of this work, and the silicon measurement results have proved the efficiency

and the robustness of the proposed signaling methodology for wireline interfaces.

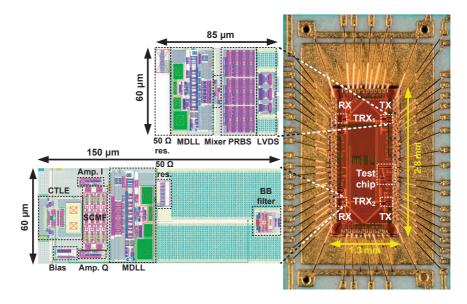

In the first part of this work, a 7.5 Gb/s hybrid NRZ/MT transceiver (TRX) for multi-drop bus (MDB) memory interfaces is designed and fabricated in 40 nm CMOS technology. Reducing the complexity of the equalization circuitry on the receiver (RX) side, the proposed architecture achieves 1 pJ/bit link efficiency for a MDB channel bearing 45 dB loss at 2.5 GHz. The measurement results of the first prototype confirm that NRZ/MT serial data TRX can offer an energy-efficient solution for MDB memory interfaces. The core size area is  $85 \times 60~\mu m^2$  and  $150 \times 60~\mu m^2$  for the transmitter (TX) and receiver (RX), respectively.

Motivated by the satisfying results of the first prototype, in the second phase of this research we have exploited the properties of multi-tone signaling, especially orthogonality among different sub-bands, to reduce the effect of crosstalk in high-dense wireline interconnects. A four-channel transceiver has been implemented in a standard CMOS 40 nm technology in order to demonstrate the performance of NRZ/MT signaling in presence of high channel loss and strong crosstalk noise. The proposed system achieves 1 pJ/bit power efficiency, while communicating over a MDB memory channel at 36 Gb/s aggregate data rate. The MT nature of the proposed transceiver helps to control the ISI and reduce the far-end crosstalk (FEXT), which results in a very energy-efficient implementation. The core size area is  $80 \times 60 \ \mu m^2$  and  $130 \times 60 \ \mu m^2$  for the TX and RX blocks (including the clock unit), respectively.

**Keywords:** Decision-feedback equalizer (DFE), differential signaling, inter-symbol interference (ISI), multi-drop bus (MDB), multi-tone signaling, nonreturn-to-zero (NRZ) signaling, far-end crosstalk (FEXT), source-synchronous architecture, dual in-line memory module (DIMM), double-data rate (DDR), Internet of Things (IoT), high-performance computing (HPC).

# Résumé

du calcul haute performance ("high performance computing") a conduit à une demande énorme de bande passante. Les technologies de communications digitales combinées avec les tendances de mise à l'échelle des circuits intégrés de haute performance ont permis l'industrie des semi-conducteurs et de la microélectronique à augmenter considérablement la bande passante des interfaces à taux élevé de perte telles que Ethernet, fond de panier (backplane) et ligne d'accès numérique (Digital Subscriber Line). La solution pour obtenir une augmentation radicale de bande passante est d'employer des techniques d'égalisation pour compenser les déficiences du canal de propagation telles que l'interférence intersymbole (inter-symbol interference), la diaphonie (crosstalk), et le bruit environnemental. Par conséquent, les entrées-sorties (I/Os) d'aujourd'hui ont été équipés avec des techniques d'égalisations sophistiquées pour repousser la limite en bande passante des systèmes. A cette fin, les avancées technologiques ont continuellement augmenté la capacité de calcul de donnée et amélioré les performances des entrées-sorties durant ces 15 dernières années. Cependant, étant donné que la bande passante du canal n'a pas été élargie au même rythme, le traitement du signal requis et les circuits électrique d'égalisations sont devenus de plus en plus compliqués. Ainsi, les améliorations de l'efficacité énergétique sont largement contrebalancées par l'énergie utilisée pour compenser les déficiences du canal. De plus, puisque la mise à l'échelle de la tension d'alimentation a saturé dans les nœuds technologiques les plus fins, la dissipation de puissance dans les circuits digitaux ne peut en bénéficier. De ce fait, les améliorations globales en terme d'efficacité énergétique ont été affaiblies. Dans ce paradigme de conception, une réévaluation des stratégies de design est devenue une importante nécessité dans le but non seulement de satisfaire les performances en terme de bande passante mais aussi en terme d'efficacité énergétique. Dans la théorie de la communication, il est bien connu que les systèmes de codage et de signalisation ont le potentiel de fournir des performances supérieures sur les canaux de communication limités en bande passante. Cependant, le choix de l'algorithme de communication de données optimal doit être considéré en tenant aussi compte des compromis sur les performances énergétique au niveau du circuit.

Au cours des dernières décennies, la croissance incessante du trafic du réseau internet et

Dans cette thèse, nous avons examiné l'application d'un nouvel algorithme et de système

de signalisation pour la communication filaire, particulièrement pour la communication entre microprocesseurs, mémoires et périphériques. Une nouvelle méthode de signalisation hybride NRZ/Multi-Tone (NRZ/MT) a été développée au cours de cette recherche. La conception, l'analyse et l'implémentation au niveau du système et du circuit de cette méthode de signalisation ont été accomplies dans le cadre de ce travail, et les résultats des mesures ont prouvé l'efficacité et la robustesse de cette méthodologie de signalisation pour des interfaces filaires.

Dans la première partie de ce travail, un émetteur-récepteur (TRX) hybride NRZ/MT fonctionnant à 7.5 Gb/s pour mémoire à interfaces bus multipoint (multi-drop bus) a été conçu et fabriquer avec la technologie CMOS 40mn. Tout en réduisant la complexité du circuit d'égalisation pour la partie du récepteur (RX), l'architecture proposée atteint une efficacité de lien de 1pJ/bit pour un canal MDB palliant une perte de 45 dB à 2.5GHz. Les résultats des mesures du premier prototype confirme que le NRZ/MT serial data TRX peut offrir une solution efficace en énergie pour les mémoires à interfaces MDB. La taille du cœur est respectivement de  $85 \times 60~\mu m^2$  et  $150 \times 60~\mu m^2$  pour le transmetteur (TX) et le receveur (RX).

Motivé par les résultats satisfaisants du premier prototype, dans la seconde phase de cette recherche, nous avons exploité les propriétés de signalisation multipoint, particulièrement l'orthogonalité parmi les différentes sous-bandes, pour réduire l'effet de diaphonie (crosstalk) dans les interconnexions filaires à haute densité. Un émetteur-récepteur 4-canaux a été implémenté dans une technologie CMOS standard 40nm dans le but de démontrer la performance de la signalisation NRZ/MT en présence d'un canal à haute perte et à forte diaphonie (crosstalk). Le système proposé atteint 1pJ/bit d'efficacité énergétique, tout en communiquant dans un canal d'une mémoire MDB à un débit de donnée de 36Gb/s. La nature MT de l'émetteur-récepteur proposé aide à contrôler l'interférence inter-symbole (inter-symbol interference) et réduire la diaphonie distante (far-end crosstalk), ce qui résulte à une implémentation d'une grande efficacité énergétique. La taille du cœur est respectivement de  $80 \times 60 \ \mu m^2$  et  $130 \times 60 \ \mu m^2$  pour les bloques TX et RX (en incluant l'unité d'horloge).

Mots clefs: Decision-feedback equalizer (DFE), differential signaling, intersymbol interference (ISI), multi-drop bus (MDB), multi-tone signaling, nonreturn-to-zero (NRZ) signaling, far-end crosstalk (FEXT), source-synchronous architecture, dual in-line memory module (DIMM), double-data rate (DDR), Internet of Things (IoT), high-performance computing (HPC).

# Contents

| A             | ckno   | vledgements                                                                   |   | V          |

|---------------|--------|-------------------------------------------------------------------------------|---|------------|

| $\mathbf{A}$  | bstra  | ct (English/Français)                                                         | , | vii        |

| Ta            | able ( | of Content                                                                    |   | xi         |

| $\mathbf{Li}$ | st of  | figures                                                                       | : | ΧV         |

| Li            | st of  | tables                                                                        | х | xi         |

| 1             | Intr   | oduction                                                                      |   | 1          |

|               | 1.1    | Thesis Goal                                                                   |   | 5          |

|               | 1.2    | Organization and Content of the Thesis                                        |   | 7          |

| 2             | Sta    | e-of-the-Art Link Systems and Preliminaries                                   |   | 9          |

|               | 2.1    | Contemporary Baseband Link Systems                                            |   | 10         |

|               |        | 2.1.1 State-of-the-art DFE Architecture                                       |   | 12         |

|               | 2.2    | Multi-Tone Link Systems                                                       |   | 15         |

|               | 2.3    | Preliminaries of Hybrid NRZ/Multi-Tone System-level Design $\ . \ . \ . \ .$  |   | 20         |

|               | 2.4    | Conclusion                                                                    |   | 21         |

| 3             | Hyl    | rid NRZ/Multi-Tone Signaling                                                  |   | <b>2</b> 3 |

|               | 3.1    | Multi-Drop Memory Interfaces: Overview                                        |   | 24         |

|               |        | 3.1.1 Multi-Drop Channel Characteristics                                      |   | 24         |

|               |        | 3.1.2 Baseband Signaling in Multi-Drop Interfaces                             |   | 28         |

|               | 3.2    | Hybrid NRZ/MT Signaling: System Design Overview                               |   | 30         |

|               |        | 3.2.1 Hybrid NRZ/MT TRX Statistical System-level Modeling $$                  |   | 32         |

|               |        | 3.2.2 Hybrid NRZ/MT TRX Detailed System Design                                |   | 35         |

|               | 3.3    | Hybrid NRZ/MT signaling: Circuit Design $\ \ldots \ \ldots \ \ldots \ \ldots$ |   | 37         |

|               |        | 3.3.1 Transmitter                                                             |   | 37         |

|               |        | 3.3.2 Receiver                                                                |   | 40         |

|               |        | 3.3.2.1 AFE Circuit Design                                                    |   | 41         |

xii Contents

|   |      |         | 3.3.2.2 Downconverting Mixer / Filter Unit                                  | 45 |

|---|------|---------|-----------------------------------------------------------------------------|----|

|   |      | 3.3.3   | Clock Generation Unit                                                       | 47 |

|   | 3.4  | Measur  | rement Results                                                              | 49 |

|   | 3.5  | Conclu  | sion                                                                        | 56 |

| 4 | Mu   | lti-Pha | se Clock Genaration for Hybrid NRZ/MT Transciever                           | 57 |

|   | 4.1  | MDLL    | -Based Clock and Data Recovery: Overview                                    | 57 |

|   | 4.2  | MDLL    | Circuit Design                                                              | 59 |

|   |      | 4.2.1   | Input Clock Buffer                                                          | 59 |

|   |      | 4.2.2   | Phase-Frequency Detector (PFD)                                              | 60 |

|   |      | 4.2.3   | Charge Pump (CP)                                                            | 61 |

|   |      | 4.2.4   | Voltgae-Controlled Delay Line (VCDL)                                        | 63 |

|   |      |         | 4.2.4.1 Delay cell (D-cell)                                                 | 63 |

|   |      |         | 4.2.4.2 V-to-I converter $\dots$                                            | 64 |

|   |      |         | 4.2.4.3 Edge combiner                                                       | 65 |

|   |      | 4.2.5   | Loop Filter Design                                                          | 65 |

|   | 4.3  | Measur  | rement results                                                              | 67 |

|   | 4.4  | Conclu  | sion                                                                        | 70 |

| 5 | Hyl  | orid NF | RZ/MT Signaling for Controlling ISI and Crosstalk in Dense                  |    |

|   | Inte | erconne | ects                                                                        | 71 |

|   | 5.1  | Analys  | is of ISI and FEXT for BB and NRZ/MT Signaling                              | 72 |

|   |      | 5.1.1   | Signal Integrity in Dense Interconnects: Introduction                       | 72 |

|   |      | 5.1.2   | Channel Configuration and BB signaling                                      | 73 |

|   |      | 5.1.3   | Hybrid NRZ/MT Signaling for Controlling ISI and FEXT $\ .$                  | 77 |

|   |      |         | 5.1.3.1 ISI Controlling Analysis                                            | 78 |

|   |      |         | 5.1.3.2 FEXT Controlling Analysis                                           | 80 |

|   | 5.2  | System  | Design Overview                                                             | 82 |

|   | 5.3  | Circuit | Design                                                                      | 83 |

|   |      | 5.3.1   | Transmitter                                                                 | 83 |

|   |      | 5.3.2   | Receiver                                                                    | 85 |

|   |      |         | 5.3.2.1  Downconverting Mixer  /  Filter Unit  .  .  .  .  .  .  .  .  .  . | 86 |

|   |      | 5.3.3   | Clock and Data Recovery                                                     | 88 |

|   | 5.4  | Measur  | rement Results                                                              | 89 |

|   | 5.5  | Conclu  | sion                                                                        | 95 |

| 6 | Cor  | clusion | 1                                                                           | 97 |

|   | 6.1  | Achiev  | ements                                                                      | 97 |

|   | 6.2  | Future  | Works                                                                       | 99 |

| Contents                                                       |     |  |

|----------------------------------------------------------------|-----|--|

| A System-Level Statistical BER Modeling for Hybrid NRZ/MT Link | 101 |  |

| B CDR Techniques for Hybrid NRZ/MT Link System                 | 105 |  |

| Bibliography                                                   | 120 |  |

| Curriculum Vitae                                               | 121 |  |

# List of Figures

| 1.1 | Data traffic forecast [1]. (a) Network traffic from 2014 to 2019. (b) Various             |    |

|-----|-------------------------------------------------------------------------------------------|----|

|     | application data traffic from 2014 to 2019                                                | 2  |

| 1.2 | Differnt serial link applications. (a) a data center in Oklahoma, USA [2].                |    |

|     | (b) a blade server containing different links [3]                                         | 2  |

| 1.3 | Wireline data rates over the years [4]                                                    | 3  |

| 1.4 | (a) Energy efficiency versus publication year [5]. (b) Data rate versus                   |    |

|     | technology node [6]. (c) Energy eficiency versus channel loss [6]                         | 3  |

| 1.5 | DRAM Data Bandwidth Trends [6]                                                            | 4  |

| 1.6 | (a) $7.5~\mathrm{Gb/s}~\mathrm{NRZ/multi}$ -tone transceiver first prototype. (b) The COB |    |

|     | used for testing the first prototype. (c) The $36~\mathrm{Gb/s}~\mathrm{NRZ/multi-tone}$  |    |

|     | second prototype                                                                          | 6  |

| 2.1 | A conventional state-of-the-art baseband transceiver with a FFE equalizer                 |    |

|     | at the transmitter, and a CTLE and a DFE at the receiver                                  | 10 |

| 2.2 | Serial link trend for the last 15 years. (a) Data rate versus year of publica-            |    |

|     | tion. (b) Energy-per-bit versus year of publication                                       | 11 |

| 2.3 | (a) A half-rate DFE architecture with speculative first (H1) tap, here the                |    |

|     | dashed red line shows a new critical timing path [7]. (b) DFE+Demux                       |    |

|     | slice presented in [8]                                                                    | 13 |

| 2.4 | 8-lane single-ended RX architecture with XDFE and cross CTLE reported                     |    |

|     | in [9]                                                                                    | 14 |

| 2.5 | Block Diagram of the DMT system studied in [10]                                           | 15 |

| 2.6 | (a) Conceptual multi-tone system with low-pass filters and mixers at the                  |    |

|     | transmitter and receiver to create band-limited sub-channels. (b) AMT                     |    |

|     | architecture with per-sub-channel linear N-times over-sampled equalizers                  |    |

|     | at the transmitter, and mixer and integrate-and-dump at the receiver [11].                | 17 |

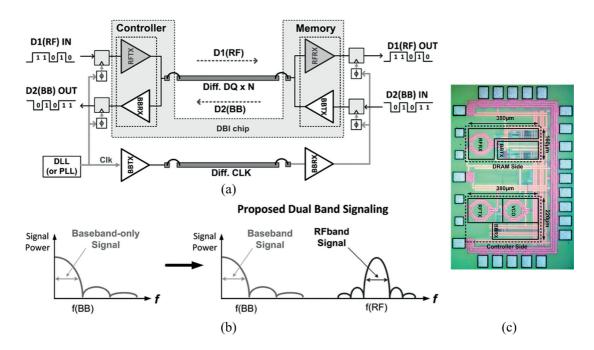

| 2.7 | (a) The proposed BB+RF architecture with forwarded-clock for simul-                       |    |

|     | taneous bidirectional signaling. (b) Dual-band signaling in frequency                     |    |

|     | domain [12]. (c) TRX chip die photo                                                       | 18 |

xvi List of Figures

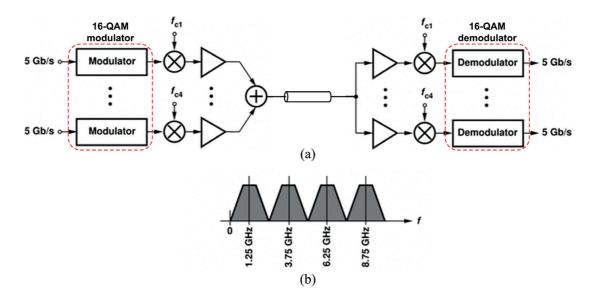

| 2.8  | (a) Proposed system architecture in [13]. (b) Proposed frequency planning with aggregate data rate of 20 Gb/s                                                                                                                                                |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

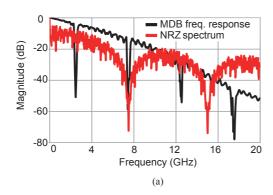

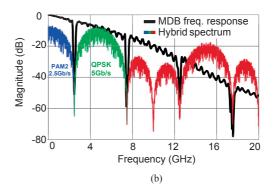

| 2.9  | Proposed mixed NRZ/MT signaling scheme. (a) NRZ spectrum over a multi-drop channel. (b) Hybrid NRZ/MT spectrum over a multi-drop                                                                                                                             |

|      | channel                                                                                                                                                                                                                                                      |

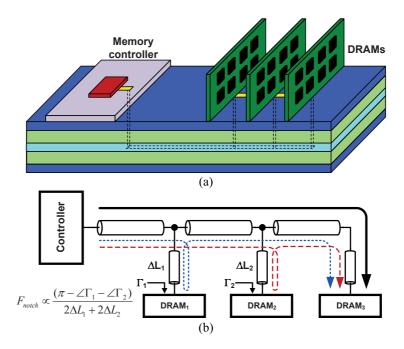

| 3.1  | (a) Controller to DRAM MDB interface. (b) Simplified block diagram of                                                                                                                                                                                        |

| 3.2  | interface in Fig. 3.1 (a) showing the multi-path fading                                                                                                                                                                                                      |

|      | MDB showing first notch at 2.5 GHz                                                                                                                                                                                                                           |

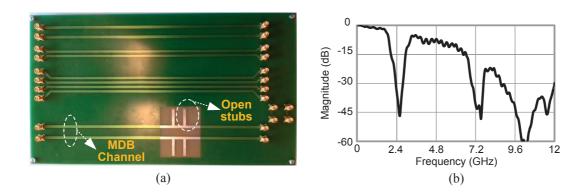

| 3.3  | The measured frequency response and the $3 \times F_{\rm notch}$ b/s single-bit pulse response for different stub lengths. (a) $F_{\rm notch}$ =660 MHz. (b) 2 GHz single-bit response. (c) $F_{\rm notch}$ =1.25 GHz. (d) 3.75 GHz single-bit response. (e) |

|      | $F_{\text{notch}} = 2.5 \text{ GHz}$ . (f) 7.5 GHz single-bit response. (g) $F_{\text{notch}} = 3.7 \text{ GHz}$ .                                                                                                                                           |

|      | (h) 11 GHz single-bit response                                                                                                                                                                                                                               |

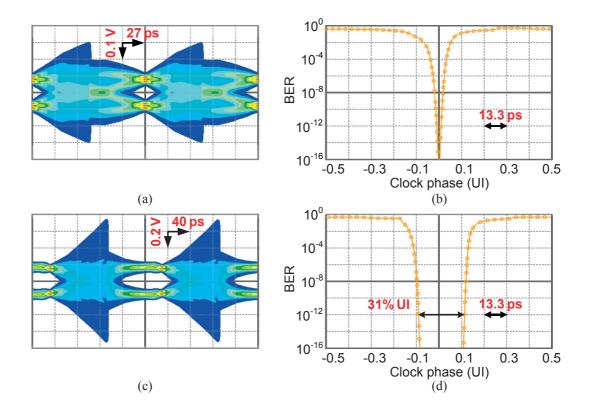

| 3.4  | (a) Conventional BB transceiver block diagram for communicating at                                                                                                                                                                                           |

|      | 7.5 Gb/s over MDB interface. System-level simulation results for the link                                                                                                                                                                                    |

|      | shown in Fig. 3.2 (b). (b) Eye diagram for 7.5 Gb/s data rate, (c) bathtub                                                                                                                                                                                   |

| 3.5  | curve, both after optimizing the CTLE and DFE response                                                                                                                                                                                                       |

| 5.5  | 0.5% jitter on both TX and RX. (a) Eye diagram for 7.5 Gb/s data rate,                                                                                                                                                                                       |

|      | (b) bathtub curve for 7.5 Gb/s data rate, both after optimizing the CTLE                                                                                                                                                                                     |

|      | and DFE response. System-level simulation results for the same interface.                                                                                                                                                                                    |

|      | (c) Eye diagram for 5 Gb/s data rate, (d) bathtub curve for 5 Gb/s data                                                                                                                                                                                      |

|      | rate, both after optimizing the CTLE and DFE response                                                                                                                                                                                                        |

| 3.6  | Transmitted spectrum in a MDB channel. (a) Conventional NRZ signaling.                                                                                                                                                                                       |

|      | (b) Hybrid NRZ/MT signaling                                                                                                                                                                                                                                  |

| 3.7  | Proposed mixed NRZ/MT system architecture                                                                                                                                                                                                                    |

| 3.8  | System-level statistical simulation for the proposed architecture in Fig. 2.9.                                                                                                                                                                               |

|      | (a) Baseband, (b) I sub-band, and (c) Q sub-band statistical eye diagram                                                                                                                                                                                     |

|      | and corresponding bathtub                                                                                                                                                                                                                                    |

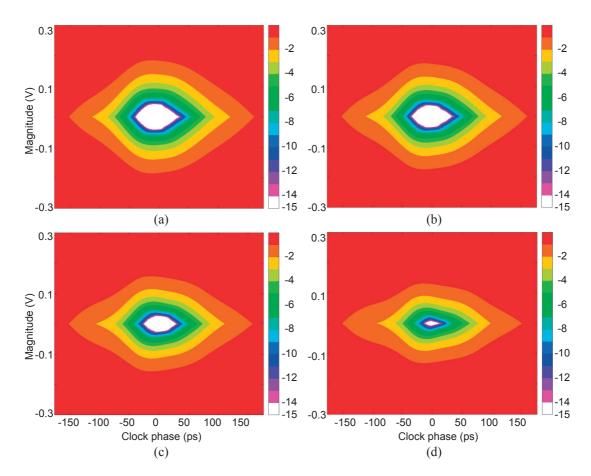

| 3.9  | Q sub-band eye diagram for different amount of clock phase mismatch. (a)                                                                                                                                                                                     |

|      | 5°, (b) 10°, (c) 15°, and (d) 20° I/Q phase mismatch                                                                                                                                                                                                         |

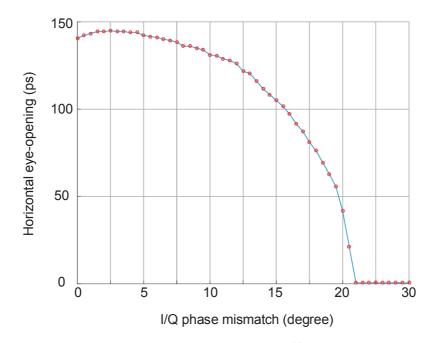

| 3.10 | Horizontal eye-opening at BER = $10^{-15}$ versus I/Q phase mismatch 3-                                                                                                                                                                                      |

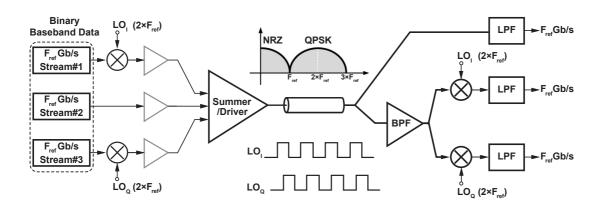

| 3.11 | Proposed hybrid NRZ/MT transceiver                                                                                                                                                                                                                           |

| 3.12 | The architecture of the proposed mixed NRZ/MT transmitter                                                                                                                                                                                                    |

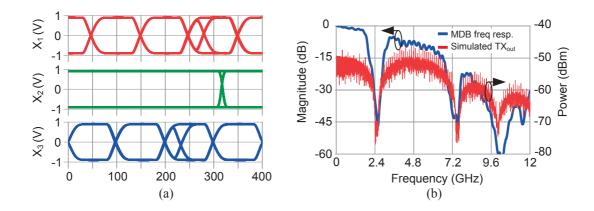

| 3.13 | (a) Eye diagram of the summer/driver input signals. (b) Simulated TX                                                                                                                                                                                         |

|      | output spectrum                                                                                                                                                                                                                                              |

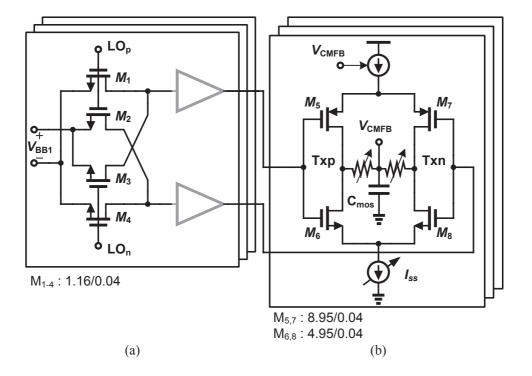

| 3.14 | (a) Upconversion passive mixer schematic. (b) Output driver schematic 38                                                                                                                                                                                     |

List of Figures xvii

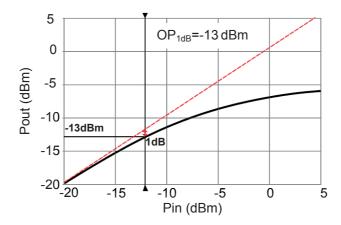

| 3. | .15 | Output power of the LVDS driver circuit with respect to the 5 GHz input                |    |

|----|-----|----------------------------------------------------------------------------------------|----|

|    |     | signal power level                                                                     | 39 |

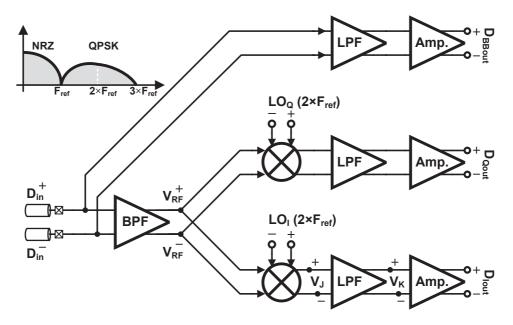

| 3. | .16 | The architecture of the proposed mixed NRZ/MT receiver                                 | 39 |

| 3. | .17 | Schematic of the BPF to pass QPSK sub-bands                                            | 40 |

| 3. | .18 | Transfer function of the BPF for different capacitor value, $C_2$ , settings. (a)      |    |

|    |     | TT corner at 27° C. (b) FF corner at -40° C. (c) SS corner at 27° C. (d)               |    |

|    |     | SS corner at 80° C                                                                     | 43 |

| 3. | .19 | BPF transfer function for different gain settings                                      | 43 |

| 3. | .20 | Schematic of the LPF used to select NRZ sub-band                                       | 44 |

| 3. | .21 | Transfer function of the BPF for different capacitor value, $C_2$ , settings. (a)      |    |

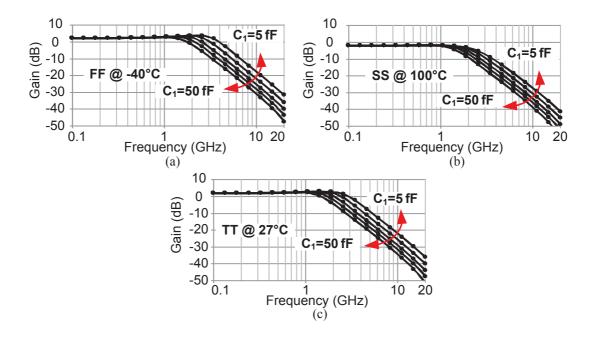

|    |     | FF corner at -40° C. (b) SS corner at $100^{\circ}$ C. (c) TT corner at $27^{\circ}$ C | 45 |

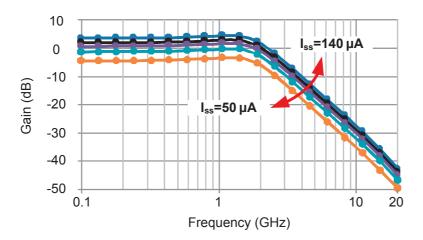

| 3. | .22 | LPF transfer function for different gain settings in TT corner                         | 46 |

| 3. | .23 | Half-circuit implementation of SCMF and baseband amplifier units                       | 47 |

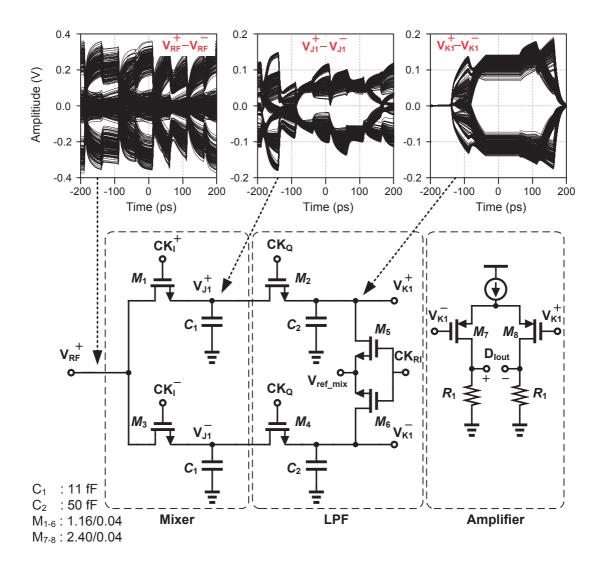

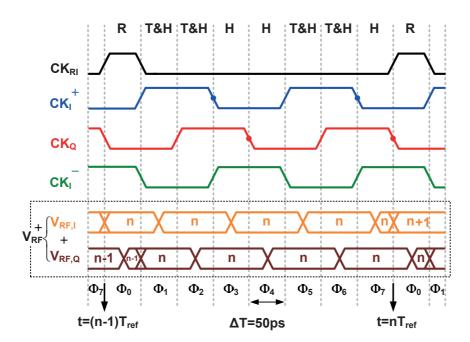

| 3. | .24 | The timing diagram of the proposed SCMF                                                | 48 |

| 3. | .25 | Clock generation system block diagram                                                  | 48 |

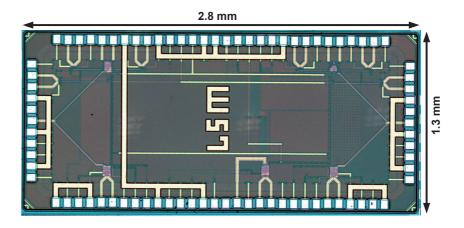

| 3. | .26 | Chip die photo.                                                                        | 49 |

| 3. | .27 | Micrograph and layout of the chip. The die size is $1.3 \times 2.8 \ mm^2$ . Two       |    |

|    |     | identical TRXs are placed at the top and bottom of the chip                            | 49 |

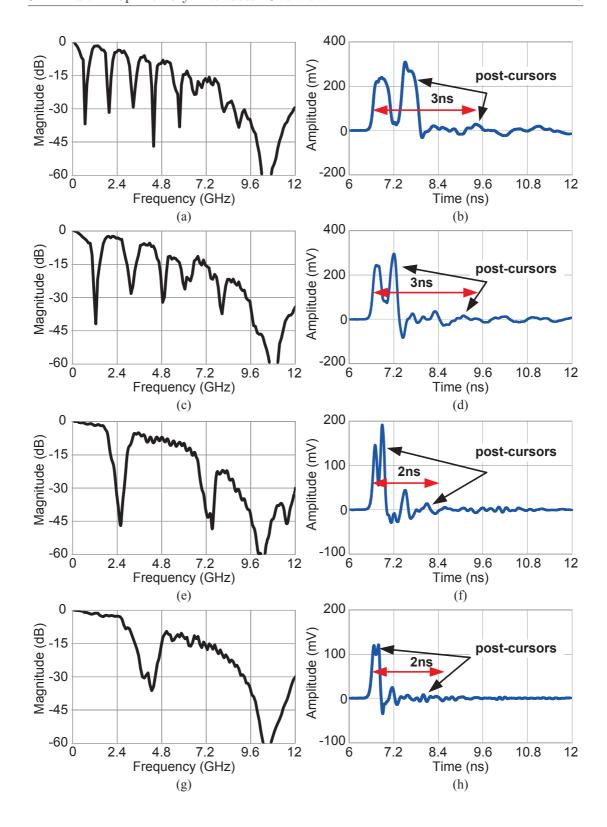

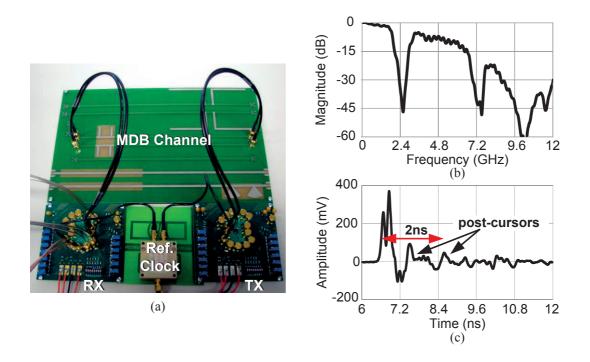

| 3. | .28 | (a) Test setup with MDB channel. (b) Measured channel frequency re-                    |    |

|    |     | sponse. (c) Measured channel 7.5 Gb/s single-bit pulse response                        | 50 |

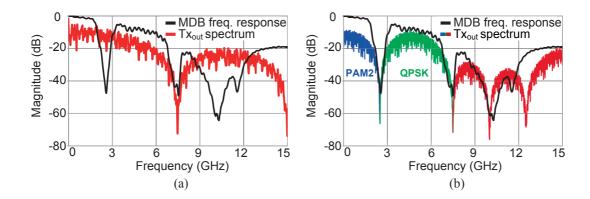

| 3. | .29 | (a) Measured TX output spectrum at different $F_{\text{ref}}$ settings. (b) Measured   |    |

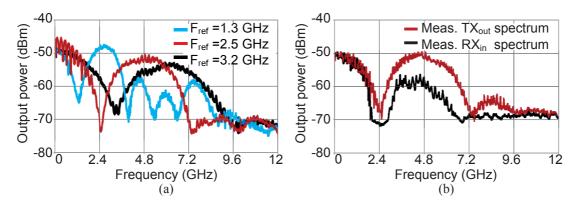

|    |     | spectrum at the input of RX                                                            | 50 |

| 3. | .30 | Measured RX eye diagram at 7.5 Gb/s data rate. (a) Q sub-band. (b)                     |    |

|    |     | I sub-band. (c) BB sub-band. Corresponding bathtub curve for (d) Q sub-                |    |

|    |     | band, (e) I sub-band, (f) BB sub-band, each operates at 2.5 Gb/s data                  |    |

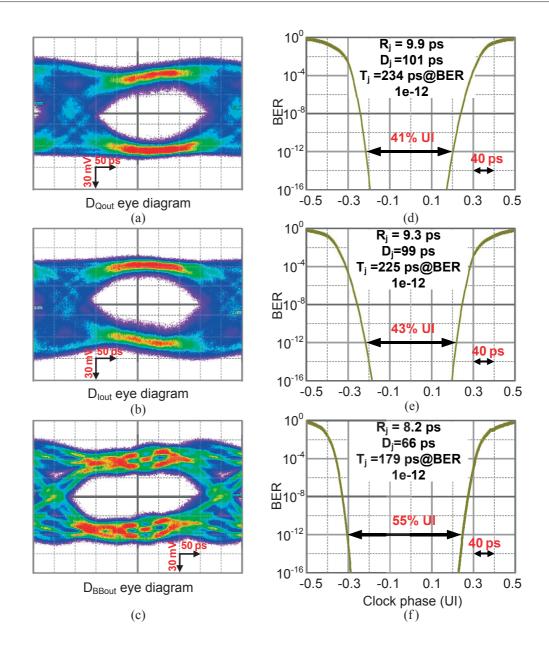

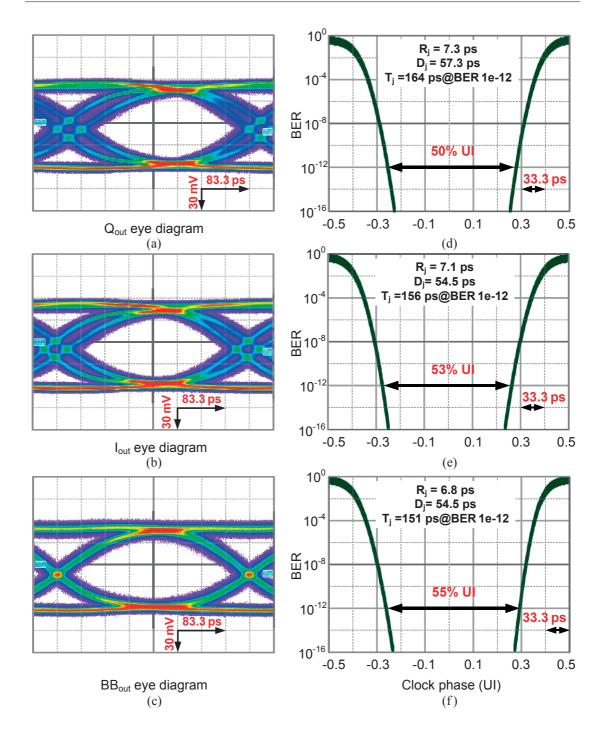

|    |     | rate                                                                                   | 51 |

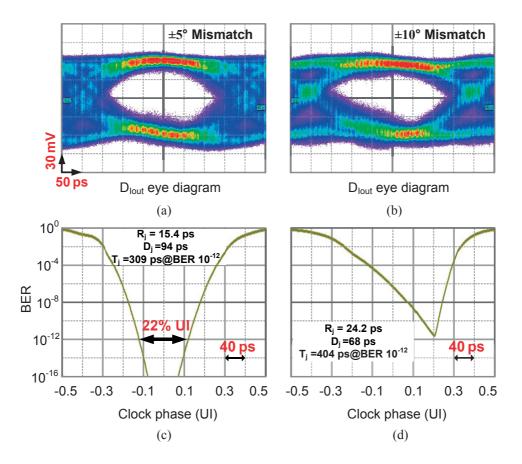

| 3. | .31 | Measured RX eye diagram sensitivity to phase-error. (a) $\pm 5^{\circ}$ , and (b)      |    |

|    |     | $\pm 10^{\circ}$ phase mismatch                                                        | 52 |

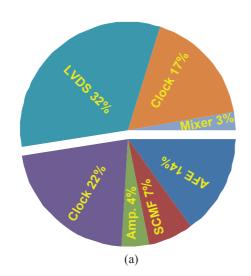

| 3. | .32 | (a) Power breakdown for the whole TRX. (b) TX power specification. (c)                 |    |

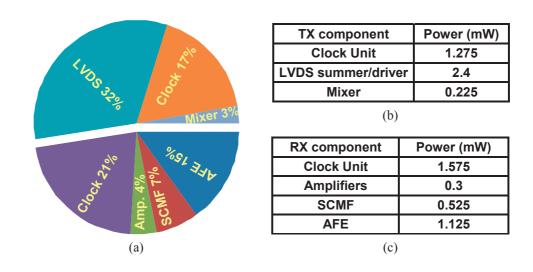

|    |     | RX power specification                                                                 | 53 |

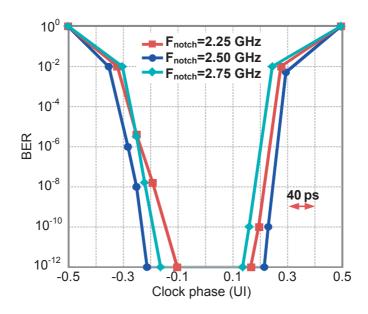

| 3. | .33 | I sub-band bathtub curve for different channel notches                                 | 53 |

|    |     |                                                                                        |    |

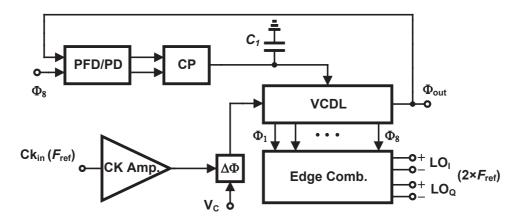

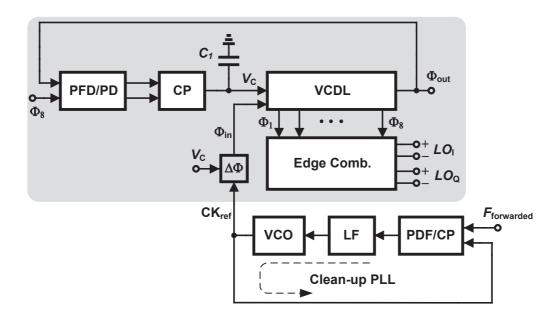

| 4. |     | Proposed MDLL-based CDR architecture                                                   | 58 |

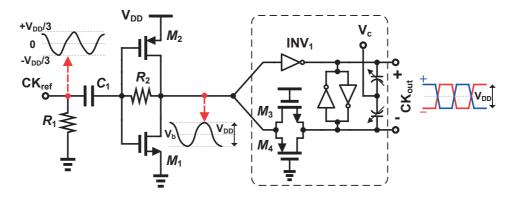

| 4. |     | Input clock buffer and single-to-differential stage schematic                          | 59 |

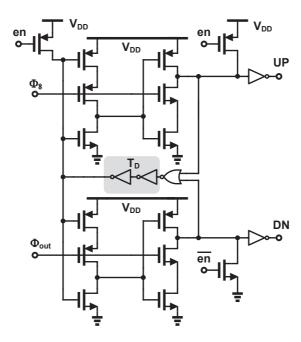

| 4. |     | The schemtic of the PFD circuit                                                        | 60 |

| 4. |     |                                                                                        | 61 |

| 4. |     | Proposed CP schematic with reduced mismatch                                            | 62 |

| 4. | .6  | (a) Schematic of the VCDL. (b) Schematic of the D-cell                                 | 63 |

xviii List of Figures

| 4.7  | (a) Schematic of the proposed V-I converter. (b) D-cell tunning curve                                                                              |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | using the proposed V-I convertor                                                                                                                   | 64 |

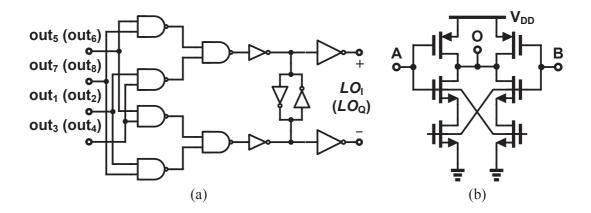

| 4.8  | (a) Edge combiner circuit. (b) Symmetrical NAND gate                                                                                               | 65 |

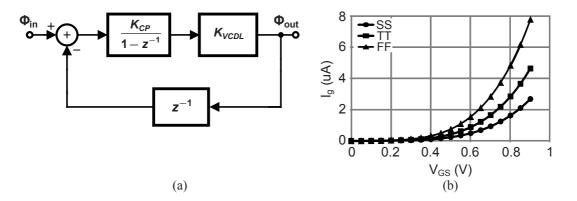

| 4.9  | (a) DLL discrete-time model. (b) Gate leakage current for 0.6 pF MOS                                                                               |    |

|      | capacitor in 40 nm                                                                                                                                 | 66 |

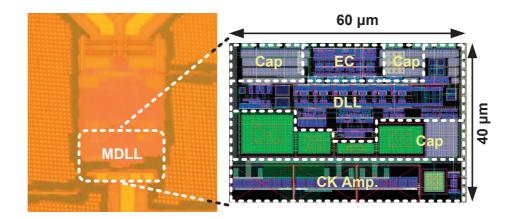

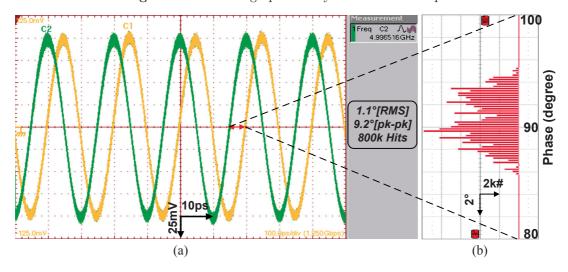

| 4.10 | Micrograph and layout of the test chip                                                                                                             | 67 |

| 4.11 | (a) Measured $I/Q$ clocks at 5 GHz output. (b) Measured long-term $I/Q$                                                                            |    |

|      | phase mismatch at 5 GHz output                                                                                                                     | 67 |

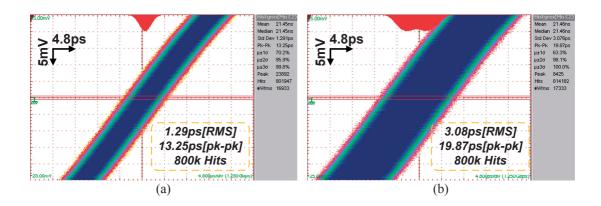

| 4.12 | (a) Measured long-term jitter histogram at 6 GHz MDLL output. (b) Measured long-term jitter histogram at 6 GHz MDLL output with 200 mV $_{\rm pp}$ |    |

|      | **                                                                                                                                                 | 68 |

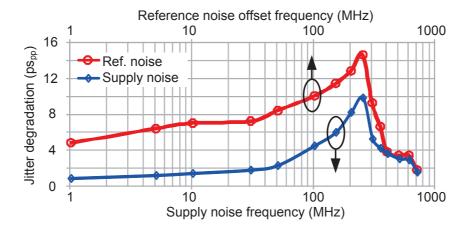

| 4.13 | Measured peak-to-peak jitter degradation versus supply noise and refer-                                                                            |    |

| 1.10 | ence offset noise frequency for 6 GHz output. The supply has 200 mV $_{\rm pp}$                                                                    |    |

|      | sinusoidal noise. The reference clock has -28 dBc single-tone sideband                                                                             | 68 |

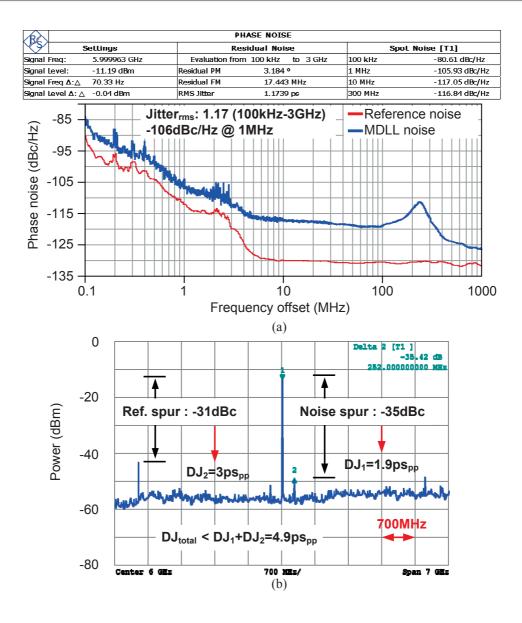

| 4.14 | (a) Measured phase noise at 6 GHz output. (b) Measured MDLL reference                                                                              |    |

|      | and spurs with 200 mV <sub>pp</sub> supply noise at jitter-peaking frequency                                                                       | 69 |

|      | r pp II v v I o I v                                                                                                                                |    |

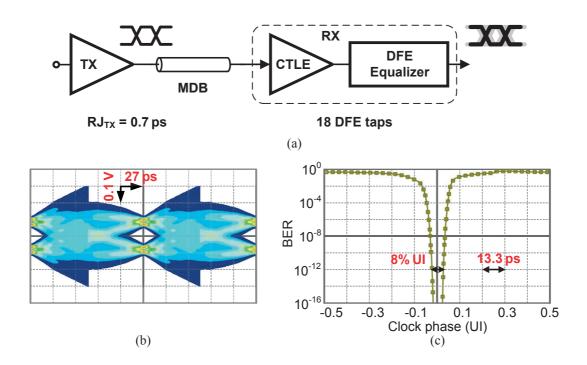

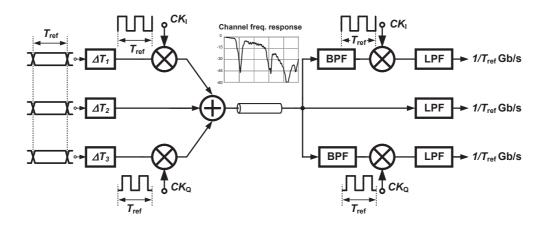

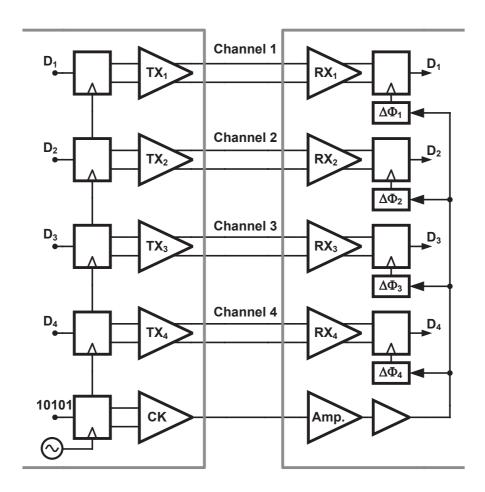

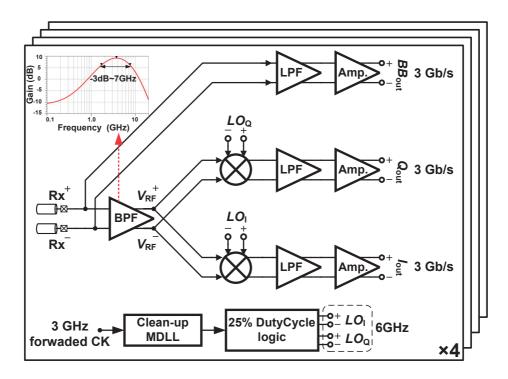

| 5.1  | Overall block diagram of the 4-channel TRX                                                                                                         | 73 |

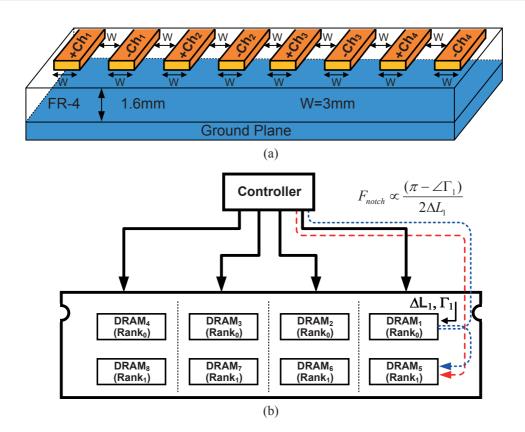

| 5.2  | (a) Stylized view of the 4 differential channels, side-by-side. (b) Simplified                                                                     |    |

|      | block diagram of a DIMM interface showing the multi-path fading                                                                                    | 74 |

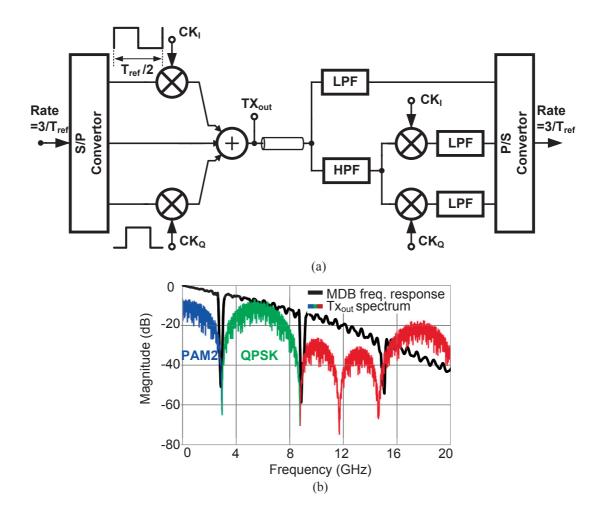

| 5.3  | (a) Measured channel frequency response. (b) Measured channel 9 $\mathrm{Gb/s}$                                                                    |    |

|      | single-bit pulse response                                                                                                                          | 75 |

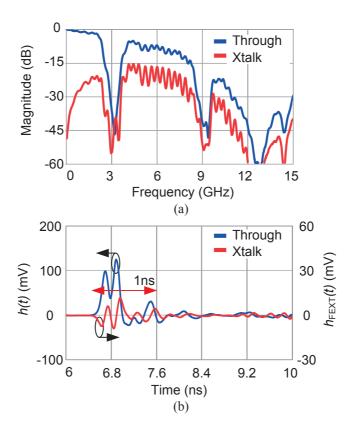

| 5.4  | (a) Conventional BB transceiver block diagram for communicating at 9                                                                               |    |

|      | Gb/s over MDB interface. System-level channel simulation eye diagrams                                                                              |    |

|      | for: (b) without, (c) with crosstalk, both after optimizing the CTLE and                                                                           |    |

|      | DFE blocks                                                                                                                                         | 76 |

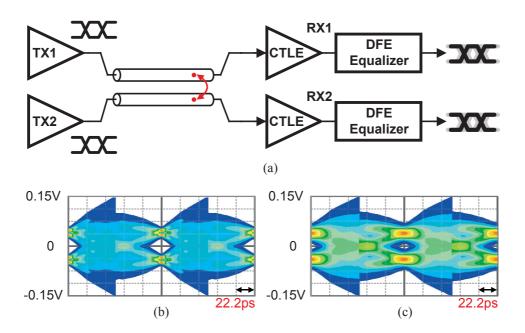

| 5.5  | (a) Hybrid NRZ/MT transceiver architecture. (b) Output TX spectrum                                                                                 |    |

|      | when $F_{\text{ref}} = 3 \text{ GHz.} \dots$                                                                                                       | 77 |

| 5.6  | (a) Hybrid NRZ/MT simplified block diagram. (b) The channel frequency                                                                              |    |

|      | response used in C2C communications. (c) PB channel construction                                                                                   | 78 |

| 5.7  | (a) 9 Gb/s single-bit pulse response for the C2C channel. (a), (b) BB and                                                                          |    |

|      | PB 3 Gb/s single-bit pulse response. (c) The eye diagram for 9 Gb/s NRZ                                                                            |    |

|      | signaling. (d), (e) BB and PB eye diagram for aggregate data rate of 9 Gb/s.                                                                       | 79 |

| 5.8  | FEXT generation mechanism in hybrid NRZ/MT signaling                                                                                               | 80 |

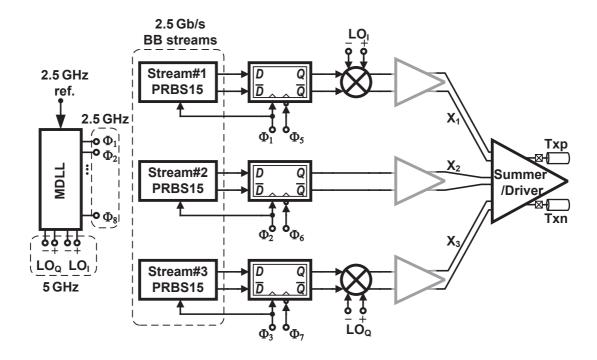

| 5.9  | Proposed 4×9 Gb/s TX architecture                                                                                                                  | 84 |

|      | Proposed $4\times9$ Gb/s mixed NRZ/MT receiver                                                                                                     | 85 |

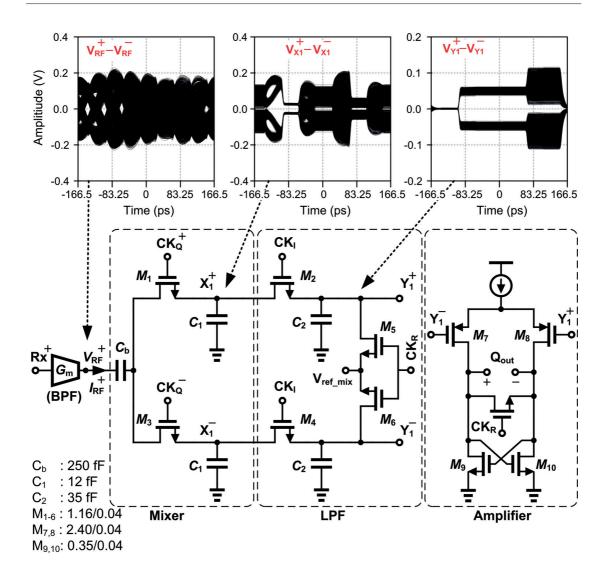

|      | •                                                                                                                                                  | 86 |

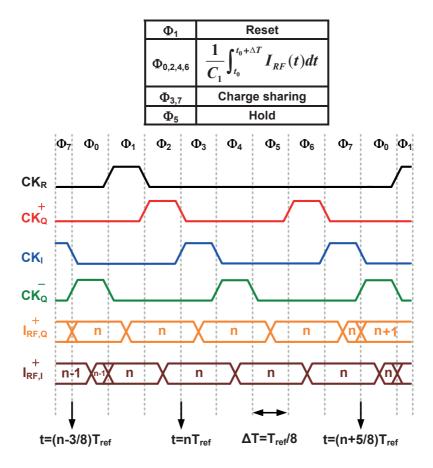

| 5.12 | The timing diagram of SCMF in Fig. 5.11                                                                                                            | 87 |

List of Figures xix

| 5.13 | (a) Test setup with MDB channel. (b) Chip die photo and layout in 40 nm           |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | CMOS                                                                              | 89  |

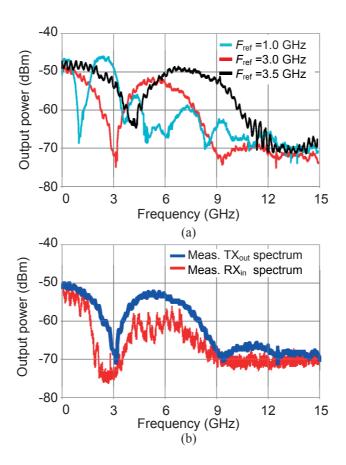

| 5.14 | (a) Measured TX output spectrum at different $F_{\rm ref}$ settings. (b) Measured |     |

|      | spectrum at the input of RX                                                       | 90  |

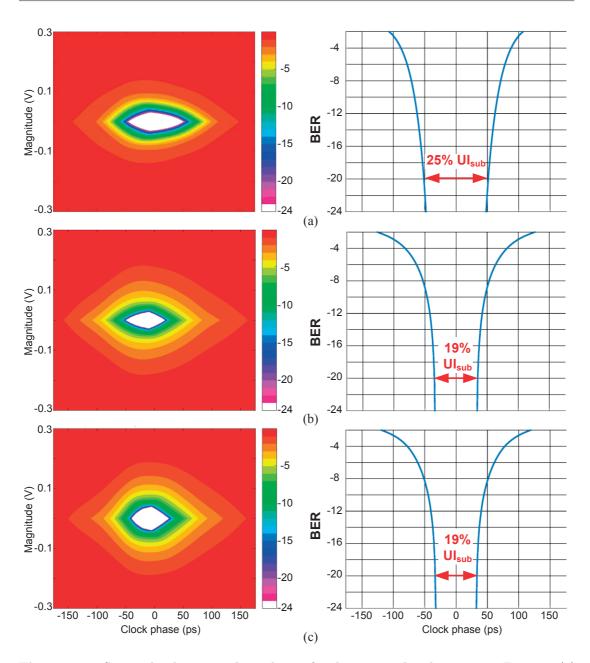

| 5.15 | Measured RX eye diagram at 9 Gb/s data rate. (a) Q sub-band. (b) I sub-           |     |

|      | band. (c) BB sub-band. Corresponding bathtub curve for: (d) Q sub-band,           |     |

|      | (e) I sub-band, (f) BB sub-band, each operates at 3 Gb/s data rate                | 91  |

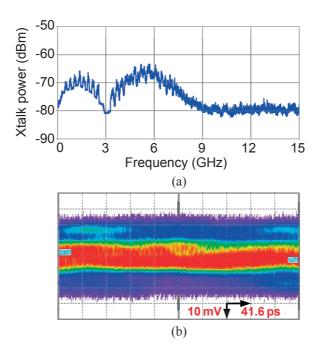

| 5.16 | Measured FEXT on Channel 3 (a) in frequency, and (b) in time domain               | 92  |

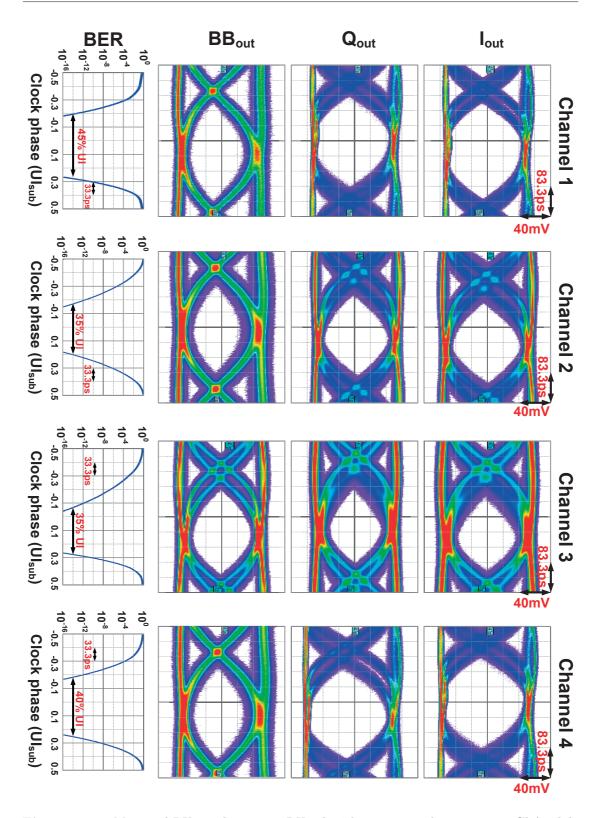

| 5.17 | Measured RX eye diagram at RX side. The aggregate data rate is $36~\mathrm{Gb/s}$ |     |

|      | while each sub-band operates at 3 Gb/s data rate                                  | 93  |

| 5.18 | (a) Power breakdown for the whole TRX. (b) TX power specification. (c)            |     |

|      | RX power specification                                                            | 94  |

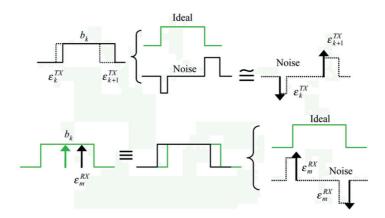

| A.1  | Transmitter and receiver jitter models                                            | 102 |

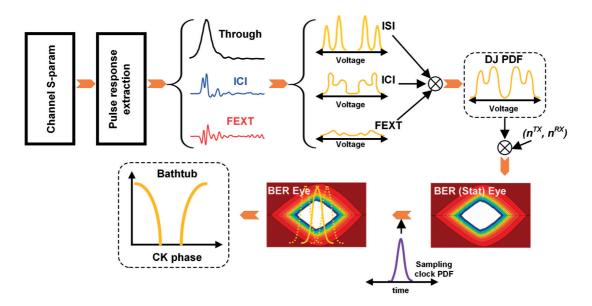

| A.2  | Flowchart of BER calculation using statistical eye                                | 104 |

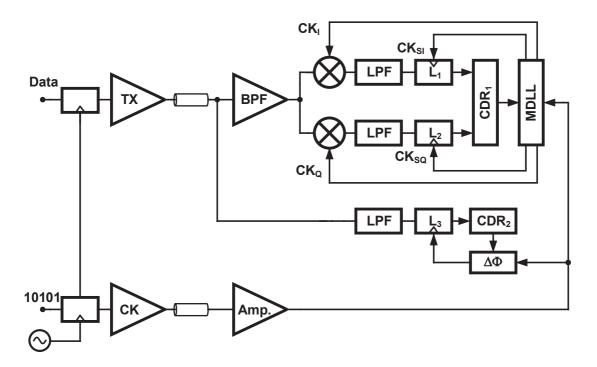

| B.1  | Forwarded clock CDR architecture for proposed hybrid $NRZ/MT$ link                |     |

|      | system                                                                            | 106 |

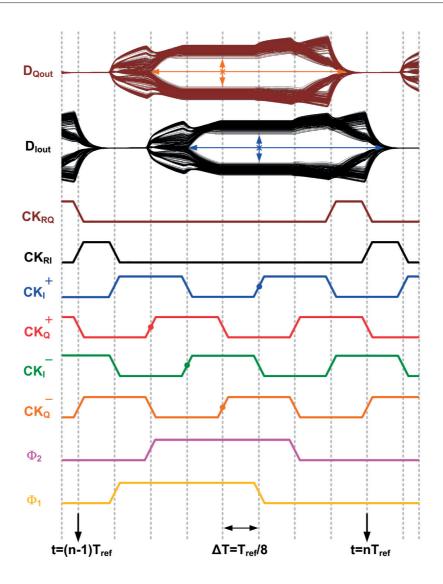

| B.2  | The timing diagram of the clock signals for recovering I sub-band, which          |     |

|      | presented in Fig 3.23                                                             | 107 |

| В.3  | The proposed CDR architecture for pass-band data                                  | 108 |

# List of Tables

| 2.1 | Required Transceiver Performance presented in Fig. 2.8 [13]           | 19 |

|-----|-----------------------------------------------------------------------|----|

| 3.1 | The hybrid NRZ/MT performance presented in Fig. 3.7                   | 34 |

| 3.2 | TRX Performance Comparison with State-of-the-art Memory Transceivers. | 54 |

| 3.3 | Silicon Performance Summary.                                          | 55 |

| 4.1 | Comparison of MDLL performance for frequency generation               | 70 |

| 5.1 | TRX Performance Comparison with State-of-the-art Memory Transceivers. | 94 |

# 1 Introduction

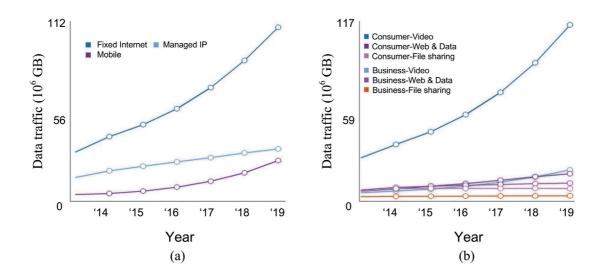

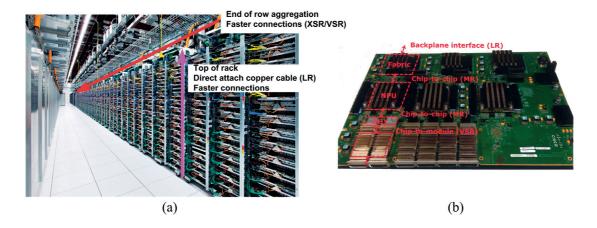

Internet networking traffic has experienced a tremendous growth in recent years, primarily driven by cloud computing, the Internet of Thing (IoT), high-performance computing systems, enterprise servers, flourishing of social media, recent explosive smart phone advancement, etc. As it has been estimated in [1], in year 2019 mobile IP traffic will be 10 times heavier than what it was in 2014, and the total Internet traffic will nearly triple from 2014 to 2019. Fig. 1.1 (a) illustrates this predications for different application types, whereas Fig. 1.1 (b) highlights the network traffic growth more specifically [1]. Among different applications, the greatest growth belongs to the consumer-video, which is indeed a results of dramatic increase of Internet networking traffic. The heart of the Internet network is the service providers' data centers, which should appropriately provide the content, files, data storage, and switching harbors [14]. Inside data centers, there are big racks containing many servers, storages, switches, and routers, which are all connected with cables. Fig. 1.2(a) shows an image of a data center located in Mayes County, in Pryor, Oklahoma, USA, which consists of such gigantic infrastructures. In order to connect all modules together, variety of cables with different specifications have been employed, and they can be categorized in several serial link standards, as it is shown in Fig. 1.2 (a). Likewise, in a PC blade server there are several units that should communicate together over copper channel, and depending on the channel length and other specifications of the corresponding link, they can be classified in various wireline standards, as shown in Fig. 1.2 (b) for a sample blade server [3].

In order to increase the network capacity, increasing the per-lane data rate has been a standard approach, and many standards have been developed by Optical Internetworking Forum (OIF), Common Electrical I/O (CEI), Joint Electron Device Engineering Council (JEDEC), and Institute of Electrical and Electronics Engineers (IEEE) to cope with the incessant data bandwidth demand. Thanks to the bandwidth demand explosion in

**Figure 1.1:** Data traffic forecast [1]. (a) Network traffic from 2014 to 2019. (b) Various application data traffic from 2014 to 2019.

**Figure 1.2:** Differnt serial link applications. (a) a data center in Oklahoma, USA [2]. (b) a blade server containing different links [3].

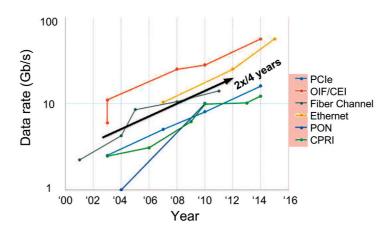

data centers and telecommunication infrastructures, the data rate growth for wireline transceivers has been consistently increasing at about twice per four years, as shown in Fig. 1.3 for the most-used standards. Hence, peripheral component interconnect express is used ubiquitously in almost all chip-to-chip and chip-to-module interfaces, and OIF, CEI, IEEE, and Ethernet usually come hand-in-hand for different serial link applications. Each standard has its own logic layer, however, the physical layer can be specified by several common parameters, such as data rate, reach (either distance or channel loss in dB), crosstalk, reflections. etc. As an example, multiple 25 Gb/s backplane standards such as CEI-25G long reach (LR) [15], ultra-short reach (VSR) [16], short reach (SR) [17], etc., are developed for various cable lengths. The specification is mainly a bridge among

Figure 1.3: Wireline data rates over the years [4].

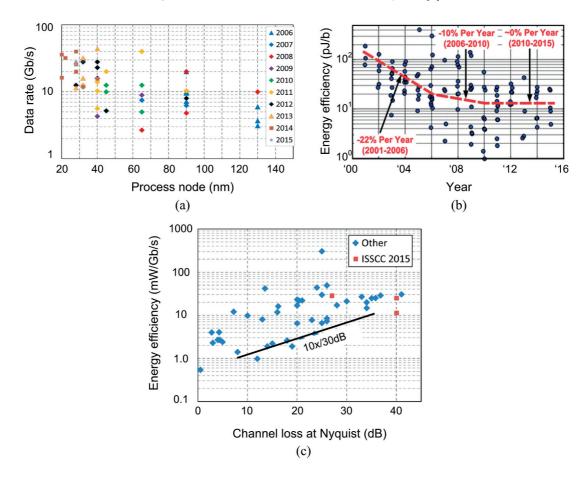

**Figure 1.4:** (a) Energy efficiency versus publication year [5]. (b) Data rate versus technology node [6]. (c) Energy efficiency versus channel loss [6].

transceiver and module vendors, connector vendors, and system houses so all parties can design their portion ahead of time, which is critical as most of the system and transceiver

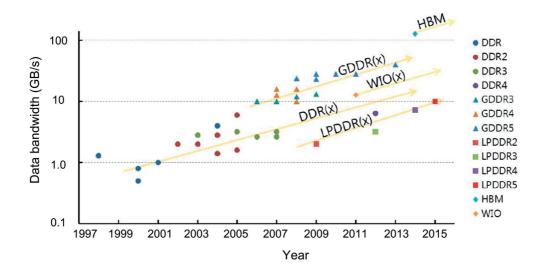

Figure 1.5: DRAM Data Bandwidth Trends [6].

development takes months or even years [4]. In this paradigm, the I/O performance becomes a major specification in practically any high-performance electronic system, from consumer products to enterprise servers. Any future progress in integrated circuit computational capability must naturally be matched with progress on I/O performance. As a result, in recent years there have been many researches for improving the I/O performance, and they have led to tremendous progress in the data rates communicated over different wireline links. Indeed, over the past decade the I/O speed improvement has been fueled by advanced CMOS technology scaling. Fig. 1.4 (a) highlights the important role technology scaling plays in supporting this trend, which has been reported over the past decade at the annual International Solid-State Circuits Conference (ISSCC) [6]. Recently, a 40/50/100 Gb/s Ethernet transceiver has been published in [18]. However, the higher data rate is not the only I/O characteristic that matters in IoT era, and the energy-efficiency should be also properly considered while the industry scales up the data bandwidth.

Power consumption for I/O circuits has been a first-order design constraint for systems ranging from cell phones to servers. As the pin count and per-pin data rate for I/Os has increased on a die, so has the percentage of total power that they consume. Over the past decade, voltage and process scaling have been the key contributors in improving I/O energy efficiency, and providing higher per-lane data rate. The ratio of I/O power consumption to data rate has become a popular figure of merit in evaluating an I/O performance. The power efficiency ratio is expressed in mW/Gb/s, or equivalently pJ/bit. It is plotted in Fig. 1.4 (b) for recent publications [5]. Moreover, the impact of interconnect channel loss has a great impact on the energy efficiency since advanced equalization techniques become

1.1. Thesis Goal 5

inevitable for proper link operation. Simply increasing per-pin baseband data rates with existing circuit architectures and channels is not always a viable path given fixed system power limits. Fig. 1.4 (c) plots the energy efficiency as a function of channel loss for recently reported transceivers. Looking at the provided data in Fig. 1.4 (c), the scaling factor between link power and channel loss is about unity, and shows ten times increase in power consumption for a 30 dB channel loss increase. Therefore, as the uncompensated part of the channel bandwidth is employed for the higher data rate communication, more sophisticated equalization circuits are required, hence, leveraging both power dissipation and occupied silicon die area. Moreover, since the supply voltage does not scale with transistor size in finer CMOS technology nodes, the I/O energy-efficiency improvement has been undermined in recent years, as shown in Fig. 1.4 (b).

Furthermore, from the vantage point of storage devices, the ever increasing data traffic necessitates a great progresses in computer memory business. Such a progress is only possible by constant improvements in area, power and performance of volatile and nonvolatile memories. In order to reduce the bandwidth gap between main memory and processor performance, DRAM data-rates continue to increase at the memory interface, and various standards such as double-data rate (DDR), low-power DDR (LPDDR) and graphics DDR (GDDR) have been developed. Fig. 1.5 plots the data rate for different memory application published in ISSCC in recent years [6]. Currently, DDR4 and GDDR5 memory I/Os operate around 3 Gb/s/pin and 7 Gb/s/pin, respectively, which represent aggregate rates of 6 GB/s and 28 GB/s, respectively. Likewise, a 9 Gb/s/pin for GDDR5 application is recently reported in [19]. Nevertheless, the channel impairment in memory interfaces has always been a bottleneck in computing system throughput improvement. Such a limiting factor has been the major reason for introducing new DDR and GDDR standards to avoid the channel impairments, however, employing a point-to-point interface instead of a multi-drop channel creates higher cost and restricts the system storage capacity.

#### 1.1 Thesis Goal

Generally speaking, in the wireline communication it has been known that the channel capacity, which Shannon theory predicts for wireline interfaces, has an order of magnitude (in some cases two order of magnitudes) gap from what contemporary baseband transceivers (TRXs) can practically achieve [20]. In order to bridge this gap, one should reappraise the traditional wireline techniques, both on system and circuit levels, and employ a more efficient system-level architecture, which is indeed realizable within a

<sup>&</sup>lt;sup>1</sup>Channel loss represents the channel attenuation at Nyquist frequency, i.e., half of the transmitted bit rate. More explanation is provided in Chapter 3 of this thesis.

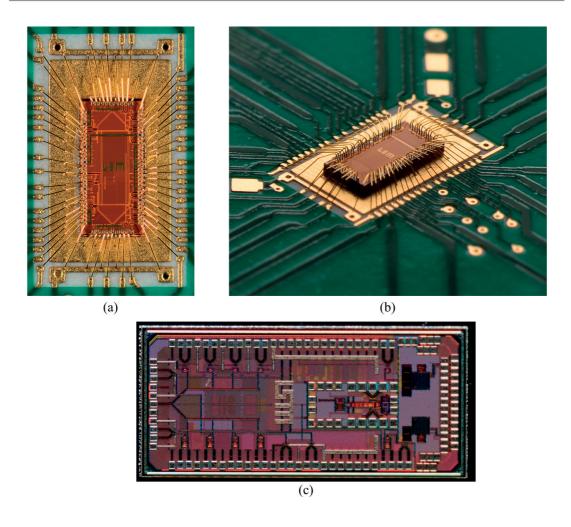

**Figure 1.6:** (a) 7.5 Gb/s NRZ/multi-tone transceiver first prototype. (b) The COB used for testing the first prototype. (c) The 36 Gb/s NRZ/multi-tone second prototype.

reasonable die area, circuit complexity, and power budget.

Therefore, the goal of this research is to develop a new family of wireline TRXs that can operate at high-speed and low-power over the communication channels, for which the conventional baseband TRX cannot provide a power-efficient solution. The fundamental challenge is to cope with severe channel impairments while meeting at the same time the stringent speed and power requirements. Moreover, the proposed coding scheme and system architecture should be optimize so as to the required circuit specifications become feasible on silicon without compromising the signaling scheme advantages. Fig. 1.6 shows the die photos of two prototype serial data TRXs, along with a chip-on-board (COB) package used for measurement purposes, which has been fabricated in the frame of this work. The first prototype includes a hybrid NRZ/multi-tone TRX that can efficiently communicate over a multi-drop memory channel at 7.5 Gb/s. The second prototype

incorporates the hybrid NRZ/multi-tone core in order to deliver an aggregate  $36~\mathrm{Gb/s}$  data rate over four differential lanes, while the power efficiency number remains at  $1\mathrm{pJ/b}$  for both prototypes. The prototypes have been implemented in  $40~\mathrm{nm}$  bulk CMOS and COB packaging has been used for testing purposes.

## 1.2 Organization and Content of the Thesis

### Chapter Two

In Chapter 2, we have provided a brief review of state-of-the-art contemporary baseband link systems in order to highlight the today's advanced SerDes trends and study some previously published researches, which have applied multi-tone signaling for wireline communication. Then, a preliminary for our proposed signaling scheme is presented. Moreover, system-level modeling and analysis of the proposed hybrid NRZ/multi-tone scheme is presented. The goal of this MATLAB-level modeling and simulation is to evaluate the proposed system performance in presents of different noise sources, and optimize it appropriately. Having modeled the system in MATLAB, the building block specifications that is required to have an error-free link operation is extracted in this chapter.

#### Chapter Three

In Chapter 3 we present a new signaling scheme, called hybrid NRZ/multi-tone (MT), which can shape the transmitted spectrum of the transmitter (TX) and be customized to the characteristics of the channel, thus, it provides a power efficient solution. Based on the proposed method, the design and implementation of a 7.5 Gb/s TRX for communicating over a multi-drop memory interface is explained in this chapter. The silicon measurement of the aforementioned TRX has been presented at the end of this chapter.

#### Chapter Four

Chapter 4 presents the design and analysis of the clocking unit, which has been employed in our hybrid NRZ/multi-tone TRX, in details. The measurement result of the clock unit, which is realized on silicon as an independent block from our TRX, is provided in this chapter.

### Chapter Five

This Chapter studies the properties of multi-tone signaling for controlling the effect of crosstalk in high-density and compact links constructed using low-cost material such as FR-4. The crosstalk reduction property of the NRZ/multi-tone signaling has been

described in this chapter, and a new TRX has been designed that can communicate at an aggregate 36 Gb/s over a four lane memory channel. Moreover, the inter-symbol interference reduction property of the proposed signaling method has been explained in details, which can be useful for very lossy backplane interfaces.

### Chapter Six

In the final chapter the achievements and the main contribution of this research has been summarized and the future works has been described.

### Apendix A

Appendix A explains the theoretical background for statistical eye diagram evaluation in details. Such an link estimation method has been employed in Chapter 2 for MATLAB simulations, and can provide great advantage over time-domain simulation.

### Apendix B

The clock and data recovery (CDR) algorithm, and circuit design, which is suitable for the proposed hybrid NRZ/multi-tone system in Chapter 3 and Chapter 5, is suggested in Appendix B.

# 2 State-of-the-Art Link Systems and Preliminaries

Over the past decade, widespread adoption of data-intensive applications such as video streaming and cloud-based computing, which has furnished the Internet of Things (IoT) era, has led to an explosive demand for data bandwidth. In order to satisfy this demand, the input/output (I/O) speed of communication systems such as routers and backplane-based servers should grow accordingly. Recent studies indicate that the I/O bandwidth of link systems must increase by 2-3 times every two years [21] so as to cope with the ever-increasing bandwidth requirement of IT systems. Moreover, to manage such drastic bandwidths with reasonable power dissipation, a power efficiency of around 1 pJ/b has been a long-held goal [22].

While the process technology scaling continues to improve on-chip circuit bandwidth, off-chip interconnect remains the bandwidth bottleneck. As the channel loss increases, the link power efficiency degrades due to the need for complex equalization, larger transmit swing, and low-jitter clock requirements. Additionally, I/O power (and consequently total system power dissipation) will grow if bandwidth demand is not accompanied by a proportional I/O power efficiency scaling [23]. In this paradigm, the majority of link systems traditionally employ a simple baseband signaling (e.g., NRZ, PAM-4, and duobinary) with limited feed-forward and feed-back equalization schemes to compensate for the dispersive nature of the communication channel. A study of the baseband signaling in wireline communication systems shows that the channel capacity predicted by Shannon theory has a large gap (one to two order of magnitudes) from what can be offered by contemporary baseband transceivers [20]. From communication system perspective, the coding schemes and multi-tone signaling are the key points to bridge the aforementioned gap [20, 11, 24, 25, 26].

In this chapter, firstly, we have provided a brief review of state-of-the-art contemporary baseband link systems. Then, the recent researches for employing multi-tone signaling

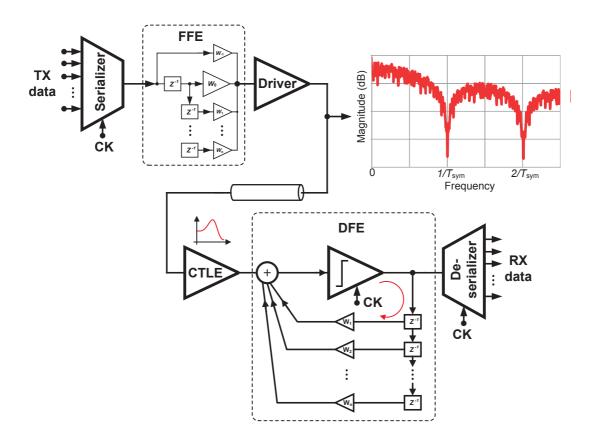

**Figure 2.1:** A conventional state-of-the-art baseband transceiver with a FFE equalizer at the transmitter, and a CTLE and a DFE at the receiver.

in wireline transceivers has been reviewed, and a preliminary for our proposed signaling scheme is presented.

# 2.1 Contemporary Baseband Link Systems

Fig. 2.1 presents the architecture of a baseband wireline transceiver, which is employed in the majority of state-of-the-art system links. This link uses non-return to zero (NRZ)<sup>1</sup> signaling with a Feed-Forward Equalizer (FFE) at the transmitter (TX) to cancel precursor Inter-Symbol Interference (ISI), a Continuous-Time Linear Equalizer (CTLE) at the receiver front-end to increase sensitivity and compensate for the high-frequency loss of the channel, and a Decision Feedback Equalizer (DFE) at the receiver to cancel post-cursor ISIs. In this architecture, the FFE and DFE do not require an addition analog to digital converter (ADC), which can be very power hungry at high-sampling rates. Moreover, having a limited number of voltage levels at the TX, the linearity requirements of the

<sup>&</sup>lt;sup>1</sup>Generally speaking, it can be duobinary, ENRZ, or PAM-N signaling. The sub-blocks might have different architectures, depending on the type of baseband signaling.

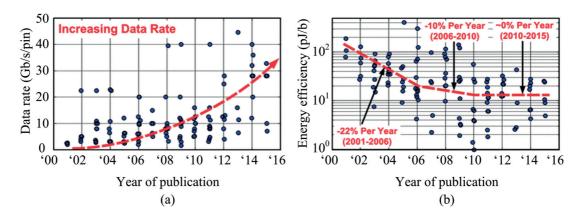

**Figure 2.2:** Serial link trend for the last 15 years. (a) Data rate versus year of publication. (b) Energy-per-bit versus year of publication.

output driver of TX and the input CTLE at the RX can be kept at a reasonable level so as to avoid power hungry topologies. Furthermore, error correction and detection coding is generally avoided in high-speed link design because of considerable power consumption and data latency that it can add to the system. From the frequency spectrum perspective, the transmitted output spectrum for all types of baseband transceiver (e.g., NRZ, PAM-4, ENRZ, doubinary, etc.) has a sinc-shaped<sup>2</sup> spectrum, as shown in the inset of Fig. 2.1, and it bears the first frequency null at  $f = 1/T_{\rm sym}$ , where  $T_{\rm sym}$  is the symbol period of the transmitted data. Indeed,  $T_{\rm sym}$  depends on the bit rate and the adopted baseband modulation scheme. For example, for a simple NRZ signaling  $T_{\rm sym} = 1/T_{\rm b}$ , where  $T_{\rm b}$  is the bit period, for duobinary, and PAM-4 modulations  $T_{\rm sym} = 0.5/T_{\rm b}$ . It can be shown that 90% of the TX energy spectrum is located below the first frequency null, whereas 77% of which is located below Nyquist rate, i.e.,  $f = 0.5/T_{\rm sym}$ .

Having the architecture of Fig. 2.1, the first challenge for baseband TRX in the IoT era is that the higher bandwidth requires increased signaling rate, thus, the data should be transmitted over lossy frequency regions of the communication channel. As a result, the baseband (BB) transceiver not only needs to have wider bandwidth but it should also satisfy a more challenging sensitivity requirement. Moreover, jitter becomes more important in lossy channels [27] necessitating a more sophisticated clock data recovery (CDR) circuit. These requirements push on both ends of the gain-bandwidth trade-off for circuits, which only scales linearly (to the first order) with technology scaling. A study of serial link specifications shows that although process technology scaling improves energy-per-bit efficiency, this measure has started to taper off in recent years [5]. Fig. 2.2 (a), and (b) present the per-pin data-rate and the energy-per-bit metric trends<sup>3</sup>, respectively [5].

$<sup>^{2}</sup>Sinc(x) = sin(\pi x)/(\pi x)$

<sup>&</sup>lt;sup>3</sup>The SerDes data is collected from papers published in ISSCC, VLSI symposium, CICC, ESSCIRC, and A-SSCC [5].

This can be explained, to the first order, as a consequence of supply voltage scaling saturation in finer CMOS technology nodes.

Another issue for the conventional BB transceiver in high-loss channels is the required complicated equalization schemes in order to reach the target bandwidth. Therefore, in addition to CTLE in such channels, it is also necessary to use a DFE in order to properly compensate the frequency-dependent channel-loss [27]. The DFE has to subtract a weighted sum of the received symbols from the incoming signal. In particular, to close the feedback loop for the first tap (as shown in Fig. 2.1), the entire operation of detecting the current symbol, multiplying it with the appropriate weight, and subtracting it from the incoming symbol should be performed in less than one symbol period. Having higher symbol-rate reduces the safe margin for closing this feedback loop, and increases the required circuit complexity. Although there have been several system and circuit techniques (e.g., loop-unrolling [28], half-rate/quarter-rate DFE [29], and charge-steering topology [29, 30]) to alleviate this problem, it still remains as one of the major concerns in DFE design for today's advanced CMOS technology. It is constructive to have a brief review of state-of-the-art DFE topology in order to better understand the design challenges arising in today's IoT and high-performance computing (HPC) era.

#### 2.1.1 State-of-the-art DFE Architecture

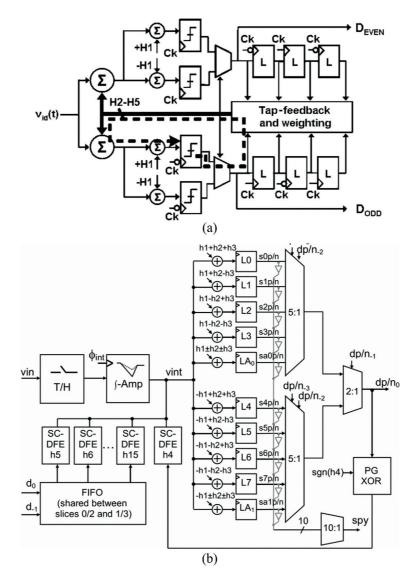

Unlike a linear equalizer (e.g., CTLE and FFE), a DFE is able to compensate for ISI without amplifying noise or crosstalk, and it is non-linear in nature. A DFE is also more effective than linear equalizers in dealing with reflections from impedance discontinuities, provided that the post-cursor ISI due to reflections falls within the time span of the DFE, i.e., the bit period multiplied by the number of DFE taps<sup>4</sup>. A key challenge in designing a high-speed DFE is ensuring that the feedback signals are accurately established at the slicer input by the time the data decision is made. The critical path, marked with a red line in Fig. 2.1, is the feedback loop, whose delay must be lower than 1 UI. Meeting this timing constraint becomes difficult at data rates above 20 Gb/s [31]. The timing constraint on this feedback path can be relaxed by adopting a technique known as speculation or loop-unrolling [32, 33]. Fig. 2.3(a) presents the block diagram of a half-rate DFE employing one tap of speculation. In this half-rate 5-tap DFE architecture, the previous bit decisions are weighted, fed back, and summed with the input signal such that post-cursor ISI is removed from the received data. The DFE employs a 1-tap loop-unrolled (or speculative) architecture and requires parallel paths in each half of the DFE [7].

<sup>&</sup>lt;sup>4</sup>This means that if the channel shows long-tail pulse response, more DFE taps is required to cancel the post-cursor, hence, the circuit complexity and power dissipation increase proportionally.

**Figure 2.3:** (a) A half-rate DFE architecture with speculative first (H1) tap, here the dashed red line shows a new critical timing path [7]. (b) DFE+Demux slice presented in [8].

Employing this architecture, the timing constrain for the first tap is relaxed, however, the second feedback lop becomes the critical path, whose delay must be lower than 2 bit period [or 2 unit intervals (UI)]. Therefore, it can be challenging to meet its time constrain for higher bandwidth. Although other DFE taps may be speculated to achieve higher speed operation, the additional circuitry creates significant cost in the hardware, as the number of parallel slicing paths grows exponentially  $(2^S)$  with the number (S) of speculative taps. The largest number of speculative taps reported to date is three [see Fig. 2.3(b)], which was used in implementing a 30-Gb/s 15-tap DFE, and it has 0.1 mW/Gb/tap power efficiency [8].

Figure 2.4: 8-lane single-ended RX architecture with XDFE and cross CTLE reported in [9].

The DFE concept can be equally applied to high-dense parallel I/Os to cancel the crosstalk noise in the same way that it removes the ISI. In [9] the cross DFE (XDFE) has been introduced in order to cancel the crosstalk in an 8-lane single-ended parallel I/O as shown in Fig. 2.4. In this work  $7 \times 8$  XDFE taps have been used for each lane, and they operate with the main 8-tap DFE block, resulting in 64-tap DFE per lane. A first-in first-out (FIFO) data from 7 aggressor lanes drives 56 XDFE taps. Providing a 7 Gb/s/pin in a closely-spaced 8-lane single-ended interface, the RX consumes 5.9 mW/Gb/s, whereas around 4.4 mW/Gb/s of which is used in DFE and XDFE circuits.

Overall, employing conventional baseband signaling, energy efficiency improvements provided by CMOS technology scaling has reached a plateau in recent years since higher channel loss and shorter timing margin for critical circuits necessitate more power consumption. This has largely offset the technology scaling advantages. Bearing in mind that in high-loss and multi-drop channels the number of DFE/XDFE taps should proportionally increase with the post-cursor ISI, the energy efficiency cannot scale with higher data rates. Thereby, re-thinking about design strategies is required to not only increase the bandwidth, but also improve the energy efficiency. From communication system perspective, the coding schemes and multi-tone signaling are to further improve the energy efficiency by optimal employment of the channel capacity [20]. In the next section we provide a brief review of the researches, which have applied a coding scheme or multi-tone signaling in wireline communications.

Figure 2.5: Block Diagram of the DMT system studied in [10].

### 2.2 Multi-Tone Link Systems

An alternative approach for wired communications is to employ multi-tone signaling, as originally performed in Digital Subscriber Line (DSL) systems and later used in wireless communication in the form of orthogonal frequency-division multiplexing (OFDM) [13]. The key advantage of this method is to communicate over a narrower frequency band, hence, less equalization circuits is required, and most of the critical transceiver building blocks (e.g., DFE, FFE, CDR) operate at lower speeds. Multi-tone signaling has promising characteristics for different type of interfaces [11, 24, 25, 26, 12, 13, 34]. However, many other aspects of the transceiver performance that are typically unimportant in binary systems become critical, and the link design requires major modifications to the well-known analysis methods applied to wireline communication systems.

The first research that well studied Multi-Tone (MT) techniques in the communication literature is [34], which has been proposed in 1975 and it was analog in nature. An analog parallel quadrature AM transmission system with overlapping orthogonal carriers and offset quadrature phase shift keying (OQPSK) was proposed in this work. Interestingly, it employs a frequency planning in which the sub-bands has 50% bandwidth overlap, and it shows that if the symbol period is an integer multiple of the sub-carrier period, it is possible to recover each sub-bands appropriately. However, the performance of the system was found to be very sensitive to communication channel variations, which changes the orthogonality between the system sub-channels. Moreover, such a modulation scheme would dictate high quadrature precision and very low phase noise so as to retain orthogonality of the sub-channels. Therefore, it would not be a power efficient and practical solution for high data rate links.

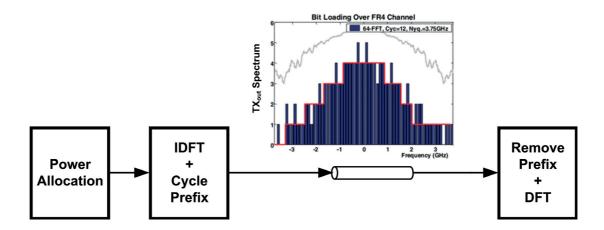

A digital implementation of a MT system has been the subject of many researches. In [35] a communication system based on frequency-division multiplexing (FDM) is presented, in which the discrete Fourier transform (DFT) are computed as part of the modulation and demodulation process. This work is known today as the OFDM or Discrete Multi-Tone (DMT) in communication systems. A more elaborated realization of digital implementation of an orthogonally multiplexed QAM (O-QAM) has been later presented in [36], where a combination of poly-phase filtering and N/2-point DFT processing was employed to perform the necessary filtering and mixing.

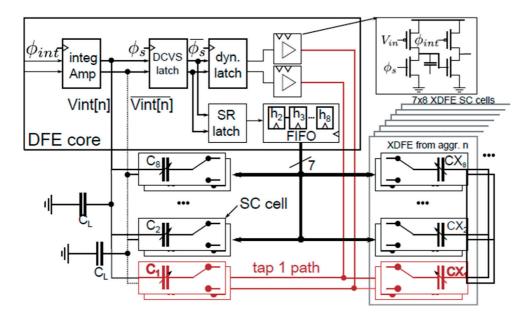

More recently, a study of the application of DMT to high-speed links has been presented in [10]. The simplified block diagram of the proposed DMT system in this work is shown in Fig. 2.5. The system-level simulation in this research, which has been performed for a sample 20" FR-4 interface, demonstrates that MT signaling has the potential for achieving high data rates in lossy channels, however, it would require high-speed DACs and ADCs with resolutions on the order of 6-7 bits, which add enormous power consumption to the link system. Moreover, this research indicates that the spectrum shaping at TX is the essence of MT approach, and having cyclic prefix in DFT/IDFT algorithm is just a clever way to simplify the implementation. The inset of Fig. 2.5 shows the TX spectrum when the optimum bit loading is adopted, and it illustrates that the TX spectrum has a different shape from conventional Sinc-shaped TX spectrum of Fig. 2.1. Therefore, if one can reduce the DMT block size (i.e., decrease the number of orthogonal carriers) while employing the spectrum shaping, then a MT architecture becomes the most efficient solution for the links in which dispersion and channel loss can be mitigated by independent number of tones.

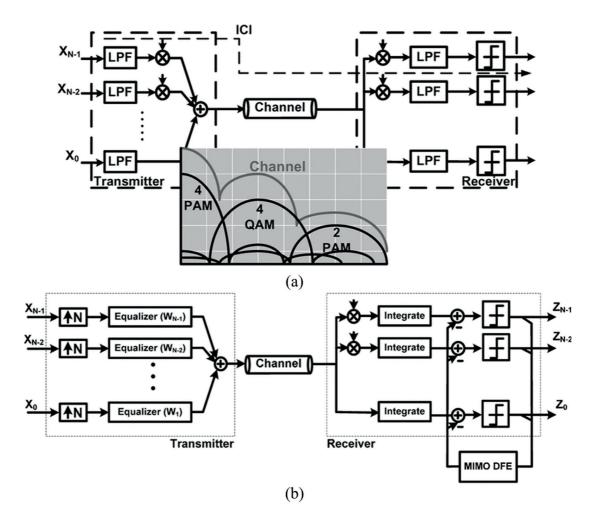

An analog implementation of the MT link system has been studied in [11], where the insight for TX spectral shaping is leveraged and power hungry ADC and DACs are avoided. The proposed TRX architecture in this work is shown in Fig. 2.6. In this research, a 24 Gb/s transmitter employing analog multi-tone (AMT) signaling with 18 pJ/b energy efficiency is introduced. The proposed TX can be customized to the link characteristics and has the potential to achieve a superior performance compared to conventional baseband (BB) transceivers. Having identical symbol rate for all subchannels, it has been shown that since the carrier frequencies are the integer multiples of the symbol rate, ICI can be canceled in the same way as ISI; through equalization. Moreover, in the MT architecture the equalization building blocks (e.g., DFE, XDFE, FFE, etc.) runs at sub-stream symbol rate, which is a fraction of the total system bit rate, therefore, the timing constrains are relieved. However, in this research, the receiver is not implemented on silicon, and mixing and integration was performed in MATLAB to generate the eyes.

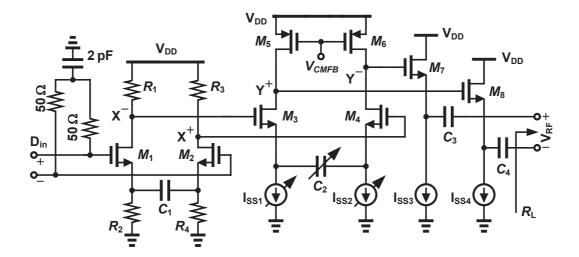

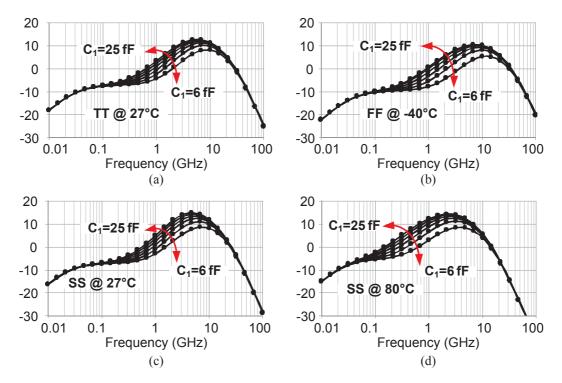

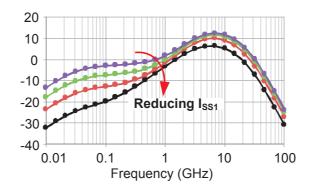

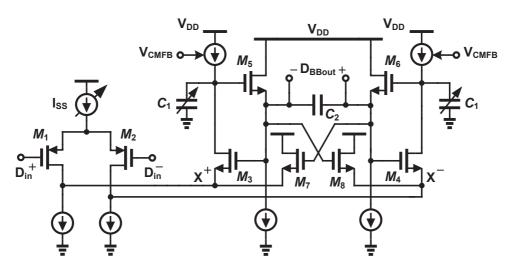

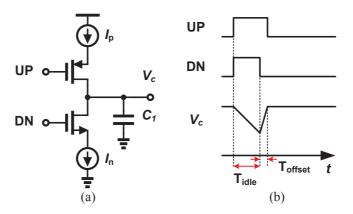

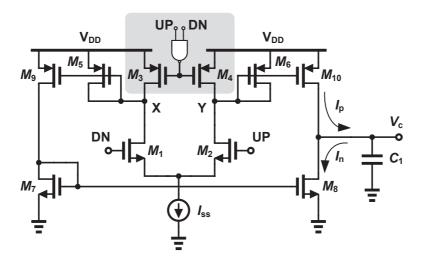

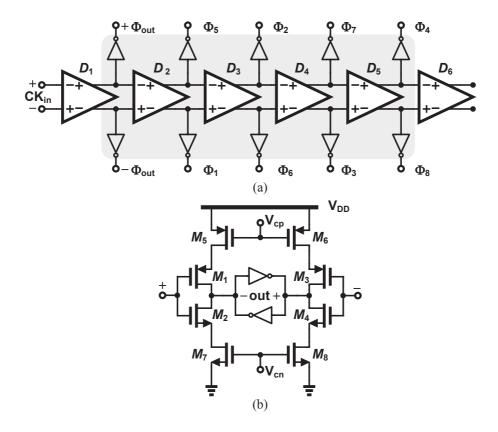

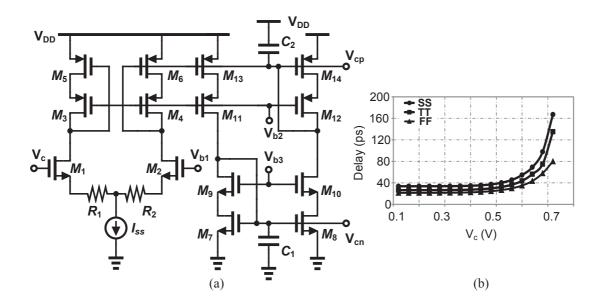

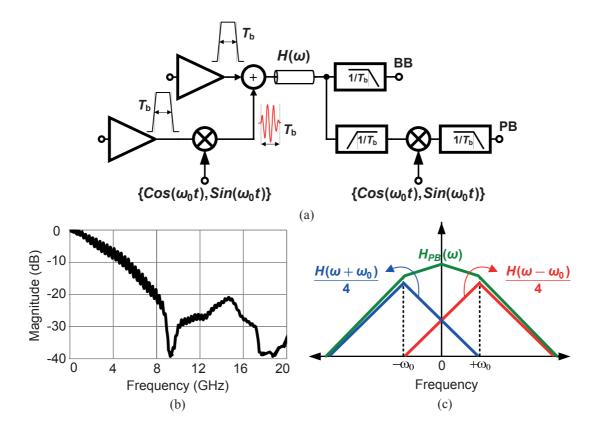

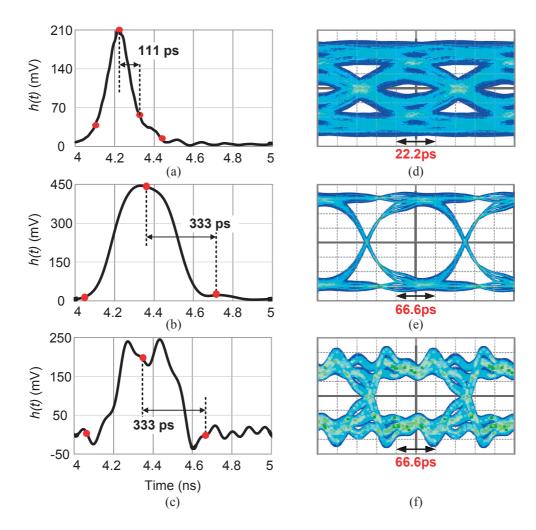

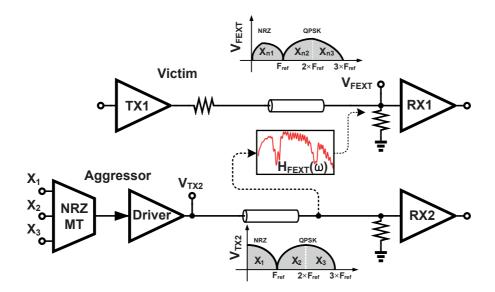

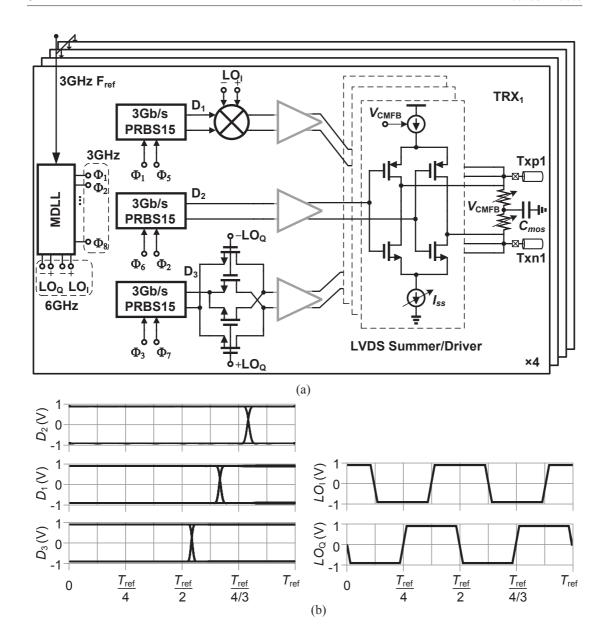

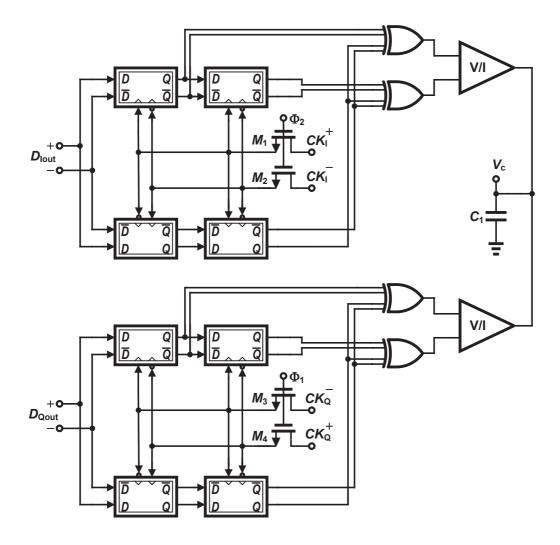

Figure 2.6: (a) Conceptual multi-tone system with low-pass filters and mixers at the transmitter and receiver to create band-limited sub-channels. (b) AMT architecture with per-sub-channel linear N-times over-sampled equalizers at the transmitter, and mixer and integrate-and-dump at the receiver [11].