# Fast Simulation of Electromagnetic Transients in Power Systems: Numerical Solvers and their Coupling with the Electromagnetic Time Reversal Process

#### THÈSE Nº 6903 (2016)

PRÉSENTÉE LE 21 MARS 2016

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR LABORATOIRE DES SYSTÈMES ÉLECTRIQUES DISTRIBUÉS - CHAIRE EOS HOLDING

ET

LABORATOIRE DE COMPATIBILITÉ ÉLECTROMAGNÉTIQUE PROGRAMME DOCTORAL EN GÉNIE ÉLECTRIQUE

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

Reza RAZZAGHI

acceptée sur proposition du jury:

Dr S.-R. Cherkaoui, président du jury

Prof. M. Paolone, Prof. F. Rachidi-Haeri, directeurs de thèse

Prof. J. Mahseredjian, rapporteur

Prof. X. Guillaud, rapporteur

Prof. A. Skrivervik, rapporteuse

### Acknowledgements

This work would not have been completed without the help and support of many kind people around me, to only some of whom it is possible to give particular mention here.

First and foremost, I would like to express my deepest gratitude to my thesis directors, Prof. Mario Paolone and Prof. Farhad Rachidi for giving me the opportunity to pursue my PhD thesis under their supervision. Their deep knowledge, kindness, invaluable guidance, scientific enthusiasm, excellent support, and endless encouragement made the PhD period a wonderful experience. It has been truly an honor to work with them during the past few years. Thanks Mario, thanks Farhad!

My sincere thanks go to the members of my jury, Prof. Jean Mahseredjian, Prof. Xavier Guillaud, Prof. Anja Skrivervik, and Dr. Rachid Cherkaoui for their encouraging and insightful comments. I am in particular grateful to Prof. Jean Mahseredjian for offering me the unique opportunity to do an internship in his lab at École Polytechnique de Montréal.

I would like also to acknowledge the Swiss National Science Foundation (Grant 200021\_146414) for funding this dissertation.

I would like to address my heartfelt thanks to Prof. Majid Sanaye-Pasand and Dr. Mahdi Davarpanah my supervisors during my Master's project at UT for their constant help, support and encouragement.

I am deeply grateful to Mrs. Andrée Moinat and Mrs. Sophie Flynn secretaries of the Laboratory, for all their constant availability, sympathy, and kindness. Merci Andrée et Sophie!

My time at EPFL was made enjoyable by an amicable environment in the laboratory. Tremendous thanks to all the members of ELL building for the friendly atmosphere and the priceless moments (listed without order): Jean-Michel Buemi, Dr. Keyhan Sheshyekani, Dr. Lazar Bizumic, Dr. Carlos Alberto Romero, Dr. Alexander Smorgonskiy, Dr. Felix Vega, Nicolas Mora, Gaspar Lugrin, Dr. Ali Ahmadi-Khatir, Dr. Paolo Romano, Dr. Stela Sarri, Dr. Omid Alizadeh Mousavi, Dr. Mokhtar Bozorg, Mostafa Nick, Maryam Bahramipanah, Mohammad Azadifar, Dr. Konstantina Christakou, Dr. Dimitri Torregrossa, Marco Pignati, Lorenzo Reyes, Lorenzo Zanni, Georgios Sarantakos, Dr. Fabrizio Sossan, Asja Derviskadic, Emil Namor, Dr. Daniele Colangelo, David Becerra, Zhaoyang Wang, Asia Codino, Enrica Scolari, Andrea Polini, and Sylvain Robert. Special thanks go to my dear colleague, Andreas Kettner, for helping me to translate the thesis abstract in German.

During my stay in Lausanne, I was fortunate to meet wonderful people with whom I have shared incredible moments. Here, I would like to thank my special friends in Lausanne for their friendship, supports, and kind helps; Elahe, Sina, Majid, Arizu, Ali, Mahdi, Ali, Razieh, Farhang, Leili.

Last but not least, my deepest and forever thanks to my beloved parents for their dedication and many years of support, for their endless love and infinite patience and compassion. I wish to express my heartfelt thanks to my sister, Mahsa for being an important part of my life. This thesis is dedicated to them.

Lausanne, January 29, 2016

Reza Razzaghi

### **Abstract**

The development of modern and future power systems is associated with the definition of new approaches for their simulation, control, and protection. To give an example, the increasing connection of massive renewable energy conversion systems is justifying the integration of DC infrastructures (eventually, multiterminal HVDC) in the current AC power grids. Furthermore, the existing passive distribution networks are evolving by integration of decentralized and intermittent generation units which results in Active Distribution Networks (ADNs). As a consequence, complex power system topologies are emerging requiring adequate simulation tools capable to reproduce, possibly in real-time, their dynamic behavior. In this context, future operation/protection practices of power networks might rely on the availability of chip-scale real-time simulators (RTS) that will enable the implementation of efficient protection/fault location processes that, in principle, should be capable to comply with the restrictive constraints associated with these complex systems.

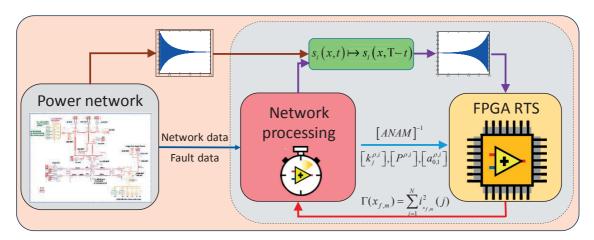

Within this context, the work presented in the thesis contributes to the integration of new concepts of the fault location in AC/DC systems that can be deployed in chip-scale real-time simulation hardware represented by Field Programmable Gate Arrays (FPGAs). The development of the proposed fault location platform is done in two steps.

First, an original fault location method based on the Electromagnetic Time Reversal (EMTR) theory is proposed. The proposed method is validated for the case of various power networks topologies and its performance is assessed. Compared to the existing fault location methods, the proposed approach is suitably applicable to different topologies including MTDCs and ADNs.

Next, a new automated FPGA-based solver for RTS is proposed. The developed FPGA-RTS uses a specific automated procedure to couple the simulation platform with an offline simulation environment (EMTR-RV) without the need for Hardware Description Language (HDL). It is able to simulate both power electronics converters and power system grids and thanks to the use of particular parallel computational algorithms, it can accurately simulate, in real-time, Electromagnetic Transient (EMT) phenomena taking place in power converters and travelling wave propagation along multi-conductor transmission lines within very small simulation time steps (in the order of some hundreds of nanoseconds). To overcome the limitations associated with the Fixed Admittance Matrix Nodal Method (FAMNM), a method to assess the optimal value of the parameter of the Associated Discrete Circuit (ADC) switch model used by FAMNM is proposed.

Finally, a specific application of the developed FPGA-RTS is explored for the development of a fault location platform by leveraging the EMTR theory. To this end, the proposed EMTR-based fault location method is integrated with the FPGA-RTS to develop an efficient fault location platform. Thanks to the fast EMT simulation capability of the FPGA-RTS, the developed fault location platform is able to estimate the accurate fault location within very short time scales. Moreover, the developed platform is compatible with the constraints characterizing complex topologies such as MTDC networks (e.g., the ultra-fast operation of the protection systems). The developed fault location platform is validated by making reference to an MTDC grid and an ADN, and it is shown to exhibit remarkable fault location accuracy as well as robustness against uncertainties such as fault type, the presence of noise, measurement systems delay, and fault impedance.

**Keywords-** Power systems protection, Fault location, Electromagnetic time reversal, Electromagnetic transients simulation, Real-time simulation, Field Programmable Gate Array, Fixed Admittance Matrix Nodal Method, Associated Discrete Circuit, Hardware-in-the-loop, Multi-terminal HVDC, Power electronics.

### Résumé

Le développement des systèmes électriques modernes est associé à la définition de nouvelles approches pour leur simulation, leur contrôle et leur protection. L'utilisation croissante des systèmes de conversion d'énergie renouvelable justifie, par exemple, l'intégration des infrastructures en courant continu (et même HVDC multi-terminaux) dans les réseaux électriques AC actuels. En outre, les réseaux de distribution passifs existants sont en train d'évoluer grâce à l'intégration d'unités de production décentralisées et intermittentes et deviennent ainsi des réseaux de distribution actifs (ADNs). Par conséquent, des structures complexes de systèmes électriques émergent, nécessitant des outils de simulation adéquats capables de reproduire leurs comportements dynamiques, de préférence en temps réel. Dans ce contexte, les pratiques futures dans l'exploitation ou la protection des réseaux électriques devraient compter sur la disponibilité de simulateurs en circuit intégré fonctionnant en temps réel (RTS) qui permettront la mise en œuvre de processus efficaces de localisation des défauts et de protection qui, en principe, devraient être capables de respecter les contraintes restrictives associées à ces systèmes complexes.

Dans ce cadre, le travail présenté dans cette thèse contribue à l'intégration de nouveaux concepts de localisation des défauts dans les systèmes AC/DC qui puissent être déployés en temps réel sur du matériel à échelle réduite en utilisant un FPGA (Field Programmable Gate Arrays). Le développement de la plate-forme proposée pour la localisation des défauts se fait en deux étapes.

Tout d'abord, on propose une méthode innovante de localisation des défauts basée sur la théorie du retournement temporel (Electromagnetic Time Reversal - EMTR). La méthode proposée est validée en considérant différentes topologies de réseaux électriques pour lesquelles les performances de cette méthode sont évaluées.

Comparée aux méthodes de localisation de défaut existantes, la méthode proposée est parfaitement applicable aux réseaux en courant continu MTDC et les réseaux de distribution actifs (ADN).

On propose par la suite un nouveau solveur automatisé pour un simulateur en temps réel (RTS) basé sur FPGA. Le simulateur FPGA-RTS développé utilise une procédure automatisée spécifique pour coupler la plate-forme de simulation avec un environnement de simulation hors ligne (EMTR-RV) sans avoir besoin de recourir à un langage de programmation bas-niveau (Hardware Description Language - HDL). Le solveur proposé est capable de simuler aussi bien des convertisseurs de puissance que des réseaux électriques, et grâce à l'utilisation d'algorithmes de calcul parallèles spécifiques il peut simuler avec précision et en temps réel les phénomènes transitoires qui se produisent dans les convertisseurs de puissance, ainsi que les phénomènes de propagation d'ondes dans les lignes de transmission multi-conductrices, le tout en employant des temps de simulation de l'ordre de quelques centaines de nanosecondes.

Pour faire face aux limites associées à la méthode dite de Fixed Admittance Matrix Nodal (FAMNM), on propose une méthode capable d'évaluer la valeur optimale du paramètre du modèle ADC (Associated Discrete Circuit) d'interrupteur utilisé par FAMNM.

Enfin, la méthode basée sur le retournement temporel proposée dans ce travail est intégrée dans le solveur FPGA-RTS afin de développer une plateforme efficace de localisation des défauts. Grâce à la capacité de simulation rapide des transitoires électromagnétiques du FPGA-RTS, la plate-forme de localisation des défauts développée est en mesure d'établir avec précision et dans de très brefs délais le lieu du défaut. En outre, la plateforme développée est compatible avec les contraintes spécifiques liées aux topologies complexes comme celles des réseaux MTDC (par exemple, la contrainte liée au déclenchement rapide des systèmes de protection). La plateforme de localisation des défauts développée est validée en faisant référence à un réseau MTDC et à un réseau de distribution actif. Il a été démontré que la plateforme développée est caractérisée par une remarquable précision dans la localisation des défauts et une robustesse face aux incertitudes liées au type de panne, à la présence du bruit, au retard des systèmes de mesure, et à l'impédance du défaut.

Mots-clés: Protection des réseaux haute tension, Localisation des défauts, Retournement temporel, Simulation de transitoires électromagnétiques, Simulation en temps réel, Field Programmable Gate Array, Fixed Admittance Matrix Nodal Method, Associated Discrete Circuit, Hardware-in-the-loop, Multi-terminal HVDC, Électronique de puissance.

### Zusammenfassung

Für die Entwicklung des elektrischen Energiesystems der Zukunft werden neue Ansätze für Simulation, Regelung und Netzschutz benötigt. Das hat verschiedene Gründe. Zum einen ist es durch die Eingliederung erneuerbarer Energiesysteme im grossen Stil sinnvoll, das bestehende Wechselstromnetz mit neuen, auf Gleichstrom basierten Technologien zu ergänzen (zum Beispiel Multi-Terminal HVDC, MTDCs). Zum anderen findet durch das Aufkommen dezentraler Energieerzeugungseinrichtungen Wandel ein von passiven Verteilnetzen (Active Distribution Networks, ADNs) statt. Die sich daraus ergebenden Systemtopologien sind äusserst kompliziert und erfordern geeignete Simulationsmethoden, damit sich das dynamische Verhalten überhaupt in Echtzeit simulieren lässt. In diesem Zusammenhang stellen sogenannte Chip-Scale Echtzeitsimulatoren (Real-Time Simulators, RTS) eine attraktive Lösung dar. Diese ermöglichen nämlich die Verwirklichung effizienter Fehlerlokalisierungsmethoden, welche auch solch anspruchsvollen Anforderungen, wie sie die obig genannten Systeme mit sich bringen, Rechnung tragen können.

Die vorliegende Arbeit einen Beitrag zur Umsetzung neuer Fehlerlokalisierungskonzepte für Wechsel- und Gleichstromsysteme, die sich in Chip-scale Echtzeitsimulationshardware, oder genauer gesagt Field-Programmable Gate Arrays (FPGAs), implementieren lassen. Die Entwicklung der hier vorgestellten Plattform für Fehler-lokalisierung gliedert sich in zwei Schritte.

Zunächst wird eine neue Lokalisierungsmethode, die auf der Electromagnetic Time Reversal Theory (EMTR) basiert, vorgestellt. Deren Wirksamkeit wird anhand verschiedener Arten von Netzwerken untersucht. Im Gegensatz zu existierenden Ansätzen ist dieser neue Ansatz auch für MTDCs und ADNs bestens geeignet.

Des Weiteren wird ein neuer, FPGA basierter Solver für RTS vorgestellt. Der in dieser Arbeit entwickelte FPGA-RTS nutzt ein automatisches Verfahren, um die Simulatorplattform mit einem Offline Simulation Environment (EMTR-RV) zu koppeln, ohne dass dafür eine Hardware Description Language (HDL) notwendig wäre. Dadurch können sowohl leistungselektronische Konverter als auch elektrische Energiesysteme simuliert werden. Die Nutzung bestimmter parallelisierter Algorithmen können sogar elektromagnetische Transiente (EMT), die sich Konvertern ereignen, sowie Wellenausbreitung entlang Mehrleiterkabeln mit hoher zeitlicher Auflösung (in der Grössenordnung von einigen hundert Nanosekunden) in Echtzeit simuliert werden. Um die Einschränkungen, die sich aus der Fixed Admittance Matrix Nodal Method (FAMNM) ergeben, zu überwinden, wurde eine Methode entwickelt, mit der sich die Parameter des Associated Discrete Circuit (ADC) Switch Models der FAMNM optimal berechnen lassen.

Schliesslich wird eine besondere Anwendung des entwickelten FPGA-RTS nämlich die Entwicklung einer effizienten Fehlerlokalisierung, welche sich die EMTR Theorie zunutze macht. Zu diesem Zweck wird die hier vorgestellte EMTR-basierte Methode in den FPGA-RTS integriert. Dank der hohen Leistungsfähigkeit des FPGA-RTS bezüglich EMT Simulationen, ist es möglich, einen Fehler binnen sehr kurzer Zeit genau zu lokalisieren. Insbesondere eignet sich die Plattform dafür, komplexe Topologien wie MTDC Netzwerke (mit ultra-schnellem Betrieb der Schutzsysteme) abzubilden. Die Validierung orientiert sich an einem an einem MTDC Netz wie auch an einem ADN Netz. Wie dargelegt wird, kann ein Fehler mit hoher Genauigkeit lokalisiert werden, wobei die Methode eine hohe Robustheit gegenüber Unsicherheitsfaktoren wie Fehlertypus, Rauschen, Measurement System Delay und Fault Impedance aufweist.

Stichworte: Netzschutz, Fehlerlokalisierung, Electromagnetic time reversal, Simulation elektromagnetischer Transiente, Echtzeitsimulation, Field Programmable Gate Array, Fixed Admittance Matrix Nodal Method, Associated Discrete Circuit, Hardware-in-the-loop, Multi-Terminal Hochspannungsgleichstrom, Leistungselektronik.

# Contents

|    |               | ledgementsvi<br>(English, /Français/ Deutsch)vi:                                           |

|----|---------------|--------------------------------------------------------------------------------------------|

| Co | ontent        | sxiii                                                                                      |

| Li | st of F       | iguresxvii                                                                                 |

| Li | st of T       | ablesxxiii                                                                                 |

| Li | st of A       | .cronymsxxv                                                                                |

| 1  | Intro         | oduction1                                                                                  |

|    | 1.1           | Motivation of the Thesis                                                                   |

|    | 1.1.1         | The Issue of Fault Location                                                                |

|    | 1.1.2         | Need for FPGA-Based RTS for Power Electronics and Power Systems Applications 3             |

|    | 1.2           | Objectives and Contributions of the Thesis                                                 |

|    | 1.2.1<br>(EM  | Fault location in Power Networks Based on Electromagnetic Time Reversal TR) Theory         |

|    | 1.2.2<br>Powe | Automated FPGA-RTS for the EMT Simulations of Power Electronic Devices and er System Grids |

|    | 1.3           | Thesis Outline6                                                                            |

| 2  | Faul          | t Location in Power Networks Based on Electromagnetic Time-Reversal 9                      |

|    | 2.1           | Introduction 10                                                                            |

|    | 2.2           | Review of the Existing Fault Location Methods for Power Networks                           |

|    | 2.2.1         | Phasor-Based Methods 12                                                                    |

| 2.2.2        | Travelling Wave-Based Methods                                        | 13       |

|--------------|----------------------------------------------------------------------|----------|

| 2.2.3        | Knowledge-Based Methods                                              | 15       |

| 2.3          | Time Reversal Theory                                                 | 15       |

| 2.3.1        | Time Reversal Cavity, Time Reversal Mirror                           | 15       |

| 2.3.2        | Electromagnetic Time Reversal (EMTR)                                 | 18       |

| 2.4          | EMTR Application to the Fault Location Problem                       | 20       |

| 2.5          | Proposed EMTR-Based Fault Location Method                            | 22       |

| 2.5.1        | Frequency-Domain Derivation                                          | 23       |

| 2.5.2        | Time-Domain Algorithm                                                | 28       |

| 2.6          | The Issue of Losses                                                  | 30       |

| 2.6.1        | Inverted-Loss Back-Propagation Model                                 | 31       |

| 2.6.2        | Lossless Back-Propagation Model                                      | 31       |

| 2.6.3        | Lossy Back-Propagation Model                                         | 32       |

| 2.6.4        | Comparison of the Back-Propagation Models                            | 32       |

| 2.7          | Experimental Validation.                                             | 36       |

| 2.8          | Application Examples and Performance Evaluation                      | 40       |

| 2.8.1        | Inhomogeneous Network Composed of Mixed Overhead- Coaxial Cable L    | ines 40  |

| 2.8.2        | Radial Distribution Network: IEEE 34-Bus Test Distribution Feeder    | 43       |

| 2.8.3        | Series-Compensated Transmission Line                                 | 46       |

| 2.9          | Conclusion                                                           | 50       |

| 3 Impi<br>53 | roved EMT Simulations Based on Fixed Admittance Matrix Nodal         | . Method |

| 3.1          | Introduction                                                         | 54       |

| 3.2          | State-of-the-Art of the RTSs for Power Electronics and Power Systems | 56       |

| 3.3          | Review of the EMT Simulation Principles                              | 61       |

| 3.3.1        | State-Space Method                                                   | 62       |

| 3.3.2        | Nodal Analysis                                                       | 62       |

| 3.3.3        | Numerical Integration Methods                                        | 63       |

| 3.3.4        | EMT simulation Models for Network Elements                           | 66       |

| 3.4          | Optimal Assessment of the ADC Switch Model Used by FAMNM             | 74       |

| 3 4 1        | FAMNM                                                                | 74       |

| 3.4.2          | Problem Definition                                                                                                                      | 74  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.4.3          | The Proposed Methodology                                                                                                                | 76  |

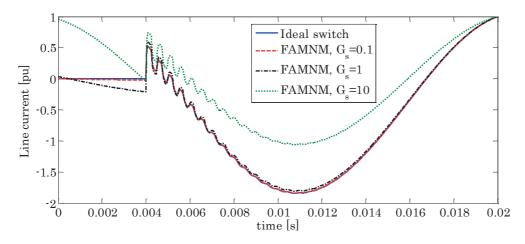

| 3.4.4          | Method Verification towards Error and Losses Functions                                                                                  | 80  |

| 3.4.5          | Validation Examples                                                                                                                     | 82  |

| 3.5            | Conclusion                                                                                                                              | 92  |

| 4 FPG          | A-RTS for Power Electronics and Power Systems EMT Simulations                                                                           | 93  |

| 4.1            | Introduction                                                                                                                            | 94  |

| 4.2            | Proposed Architecture for the FPGA-RTS                                                                                                  | 95  |

| 4.3            | Pre-Processing Unit                                                                                                                     | 97  |

| 4.3.1          | Data_ext                                                                                                                                | 97  |

| 4.3.2          | Values_sim                                                                                                                              | 98  |

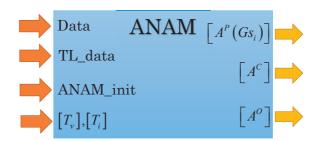

| 4.3.3          | ANAM                                                                                                                                    | 99  |

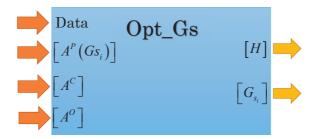

| 4.3.4          | Opt_Gs                                                                                                                                  | 101 |

| 4.3.5          | TL_coeff                                                                                                                                | 101 |

| 4.4            | FPGA-Based Real-Time Solver                                                                                                             | 102 |

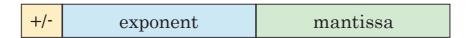

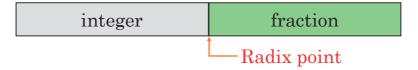

| 4.4.1          | Numerical Representation                                                                                                                | 103 |

| 4.4.2          | Efficient Matrix-to-Vector Multiplier                                                                                                   | 104 |

| 4.4.3          | RHS Vector Update                                                                                                                       | 108 |

| 4.5            | Validation Examples                                                                                                                     | 112 |

| 4.5.1          | HIL Validation of a Two-Level Three-Phase Converter                                                                                     | 112 |

| 4.5.2          | Fault Originated Transients in Multi-Terminal HVDC Network                                                                              | 119 |

| 4.5.3          | Fault Originated Transients in a Three-Phase AC Network                                                                                 | 123 |

| 4.6            | Conclusion                                                                                                                              | 125 |

| _              | gration of the EMTR in the Proposed FPGA-RTS for the Development<br>Efficient Fault Location System                                     |     |

| 5.1            | Introduction                                                                                                                            | 128 |

| 5.1.1          | Fault Location Challenges in HVDC-MTDC Networks                                                                                         | 128 |

| 5.1.2          | Fault Location Challenges in ADNs                                                                                                       | 130 |

| 5.1.3          | The Proposed Approach                                                                                                                   | 130 |

| 5.2            | EMTR-Based Fault Location with Limited Time Reversal Window                                                                             | 131 |

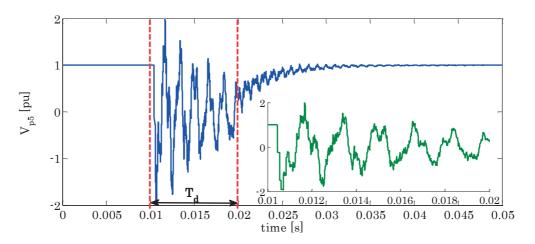

| 5.2.1<br>Netwo | Example of the Application of EMTR-Based Fault Location Method for Norks with Limited Time Reversal Window and Single Observation Point |     |

|    | 5.3           | Integration of the EMTR with the Developed FPGA-RTS                            | 135    |

|----|---------------|--------------------------------------------------------------------------------|--------|

|    | 5.4           | Application of the Developed Fault Location Platform for a Meshed MTDC Net 138 | etwork |

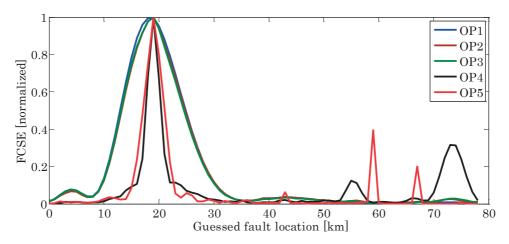

|    | 5.4.1         | Performance Assessment With Respect to the Fault Location and Fault Type       | 140    |

|    | 5.4.2         | Performance Assessment with Respect to Noise                                   | 142    |

|    | 5.4.3         | Performance Assessment of Time-Shifted Time Reversed Windows                   | 143    |

|    | 5.4.4         | Performance Assessment with Respect to Fault Impedance                         | 145    |

|    | 5.5           | Application of the Developed Fault Location Platform for a Radial ADN          | 146    |

|    | 5.5.1         | Performance Assessment with Respect to the Fault Location and Fault Type       | 148    |

|    | 5.5.2         | Performance Assessment with Respect to Noise                                   | 150    |

|    | 5.5.3         | Performance Assessment of Time-Shifted Time Reversed Windows                   | 151    |

|    | 5.5.4         | Performance Assessment with Respect to Fault Impedance                         | 152    |

|    | 5.6           | Conclusion                                                                     | 153    |

| 6  | Con           | clusions                                                                       | 155    |

|    | 6.1           | Summary and Conclusions                                                        | 155    |

|    | 6.1.1         | Fault Location in Power Networks Based on EMTR Theory                          | 155    |

|    | 6.1.2         | Efficient EMT Simulations Based on FAMNM                                       | 157    |

|    | 6.1.3<br>Simu | Automated FPGA-RTS for Power Electronics and Power Systems lations.            |        |

|    | 6.1.4         | FPGA-Based Fault Location Platform Based on the EMTR                           | 158    |

| (  | 6.2           | Contributions                                                                  | 159    |

|    | 6.3           | Future Works                                                                   | 159    |

| Bi | bliogr        | aphy                                                                           | 161    |

| Cı | ırricu        | lum Vitae                                                                      | 177    |

# List of Figures

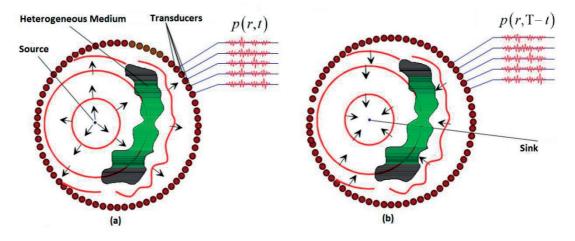

| Figure 2.1. Time reversal cavity illustration (adapted from [46]). (a) Divergent propagation from the source. (b) Convergent back-propagation to the source17     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

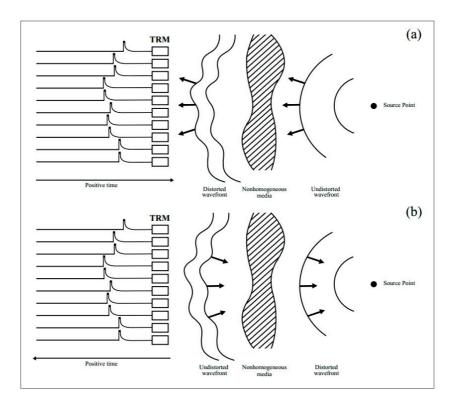

| Figure 2.2. The TRM focusing procedure (adapted from [46]). (a) Divergent incident wave from the source. (b) Convergent back-injected waves into the source18     |

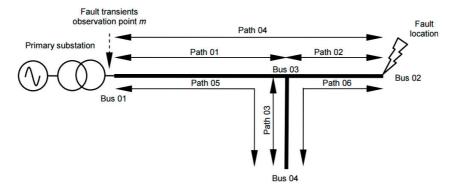

| Figure 2.3. Paths covered by travelling waves caused by a fault at Bus 0222                                                                                       |

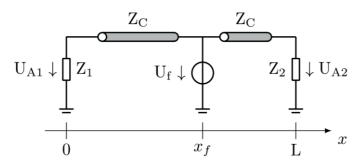

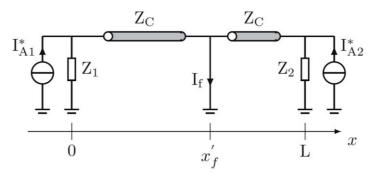

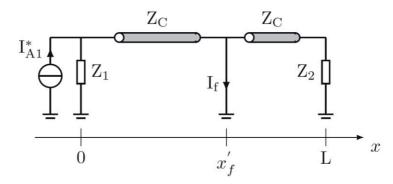

| Figure 2.4. Simplified representation of the post-fault line configuration for the EMTR analytical validation                                                     |

| Figure 2.5. Representation of the EMTR applied to the single-line model25                                                                                         |

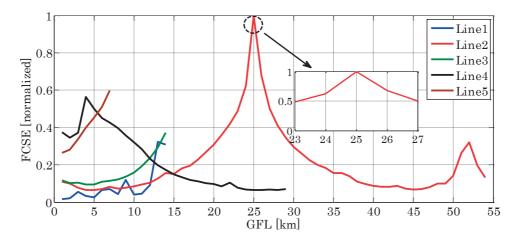

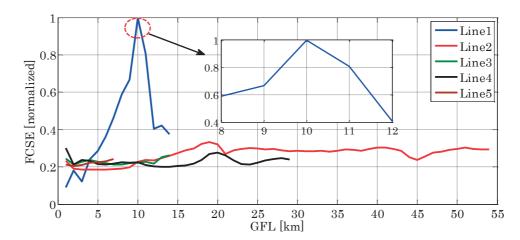

| Figure 2.6. Normalized FCSE as a function of the GFL $x_f$ with multiple observation points. The real fault location is at $x_f$ =8 km                            |

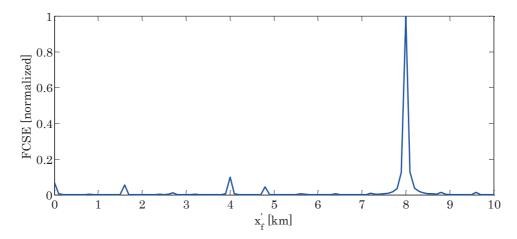

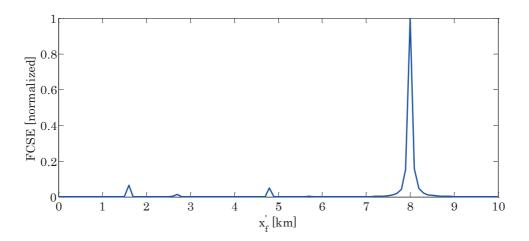

| Figure 2.7. Representation of the EMTR applied to the single-line model of Figure 2.4 where a single observation point is placed at the beginning of the line. 27 |

| Figure 2.8. Normalized FCSE as a function of the GFL $x_f$ with single observation                                                                                |

| point. The real fault location is at $x_f$ =8 km                                                                                                                  |

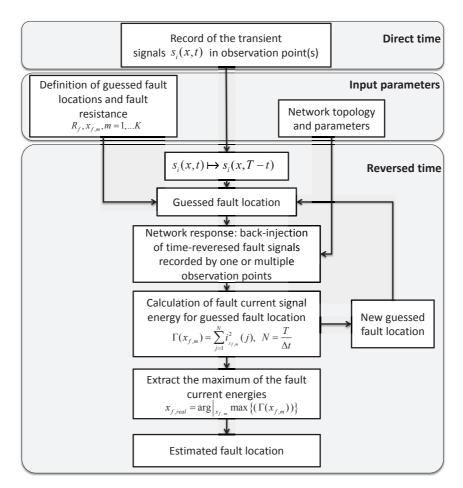

| Figure 2.9. Flow-chart of the proposed EMTR-based fault location method29                                                                                         |

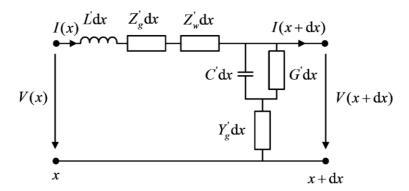

| Figure 2.10. Equivalent circuit of a single-wire line above a ground plane31                                                                                      |

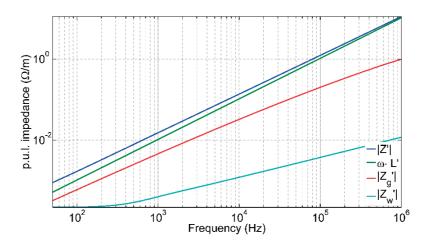

| Figure 2.11. Magnitude of the per-unit-length longitudinal impedance as a function of frequency. The ground conductivity is $\sigma_g$ = 0.001 S/m                |

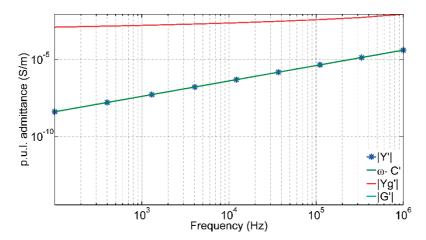

| Figure 2.12. Magnitude of the per-unit-length transverse admittance as a function of frequency. Ground conductivity is $\sigma_g$ = 0.001 S/m34                   |

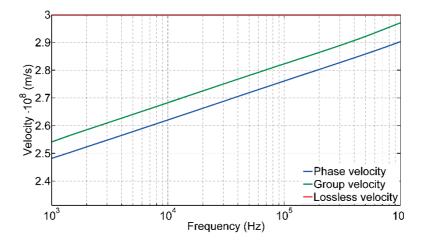

| Figure 2.13. Phase and group velocities as a function of the frequency. Ground conductivity is $\sigma_g$ = 0.001 S/m                                             |

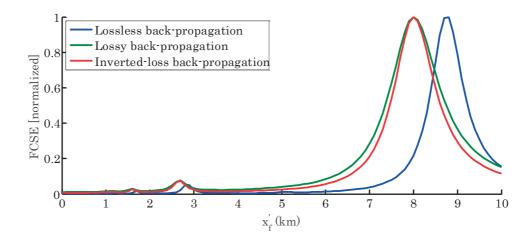

| Figure 2.14. Fault current energy normalized to its maximum, for the three backpropagation models. Ground conductivity $\sigma_g$ = 0.01 S/m                      |

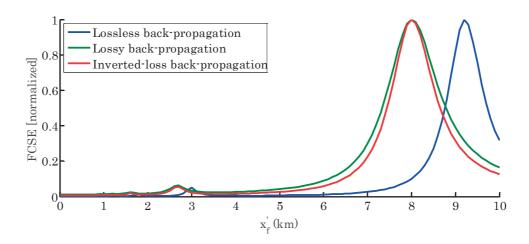

| Figure 2.15. Fault current energy normalized to its maximum, for the three backpropagation models. Ground conductivity $\sigma_g$ = 0.001 S/m                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

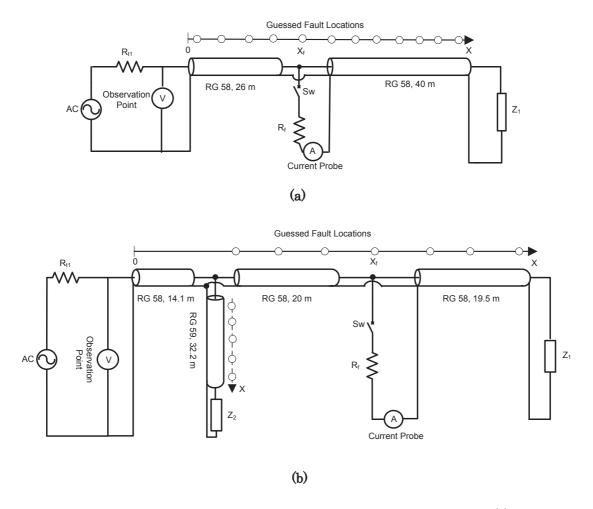

| Figure 2.16. Topologies adopted for the reduced-scale experimental setup: (a) a single transmission line configuration (RG-58 coaxial cable), (b) a T-shape network made of both RG-58 and RG-59 coaxial cables                                                                                                                                                                                                 |

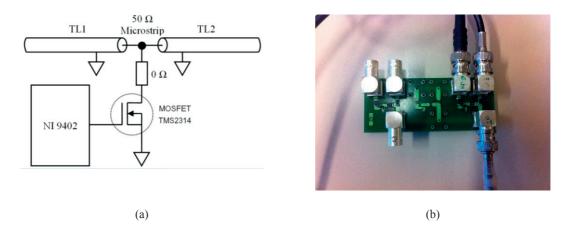

| Figure 2.17. MOSFET-emulated fault adopted in the reduced-scale experimental setup: (a) schematic representation, (b) built PCB board                                                                                                                                                                                                                                                                           |

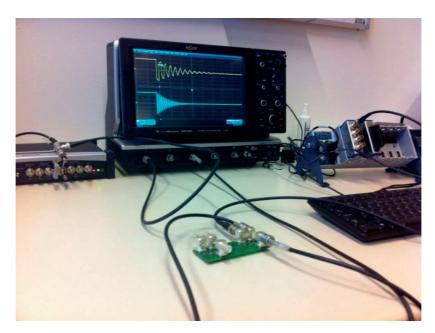

| Figure 2.18. The experimental setup used for the EMTR-based fault location method validation                                                                                                                                                                                                                                                                                                                    |

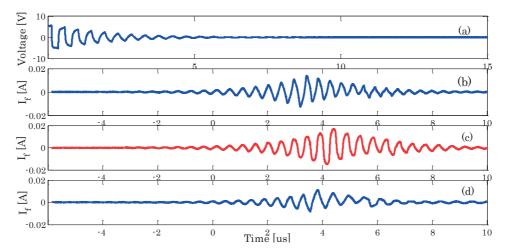

| Figure 2.19. Experimentally measured waveforms for a fault location $x_f$ = 26 m for the topology of Figure 2.16-(a); (a) direct-time voltage measured at the observation point located at the beginning of the line. Measured fault currents as a result of the injection of time-reversed signal at guessed fault locations (b) $x_f'$ = 23 m, (c) $x_f'$ = 26 m (real fault location) and (d) $x_f'$ = 28 m. |

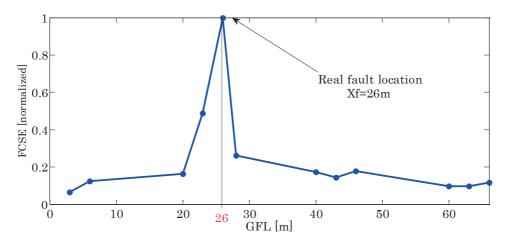

| Figure 2.20. Normalized FCSE as a function of the position of the GFL for the configuration shown in Figure 2.16 (a). The real fault location is at $x_f = 26$ m 39                                                                                                                                                                                                                                             |

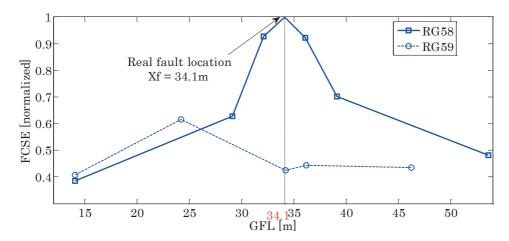

| Figure 2.21. Normalized FCSE as a function of the position of the GFL for the topology presented in Figure 2.16-b. The real fault is at $x_f = 34.1$ m in RG-58 40                                                                                                                                                                                                                                              |

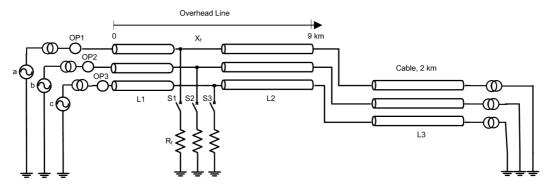

| Figure 2.22. Schematic representation of the inhomogeneous network under study implemented in the EMTP-RV simulation environment                                                                                                                                                                                                                                                                                |

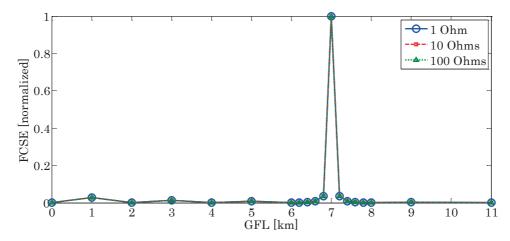

| Figure 2.23. Normalized FCSE as a function of the GFL and for different guessed fault resistance values. The real fault location is at $x_f = 7$ km and real fault impedance is $0 \Omega$ .                                                                                                                                                                                                                    |

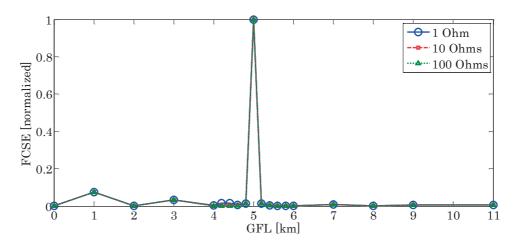

| Figure 2.24. Normalized FCSE as a function of the GFL and for different guessed fault resistance values. The real fault location is at $x_f = 5$ km and real fault impedance is $100 \Omega$ .                                                                                                                                                                                                                  |

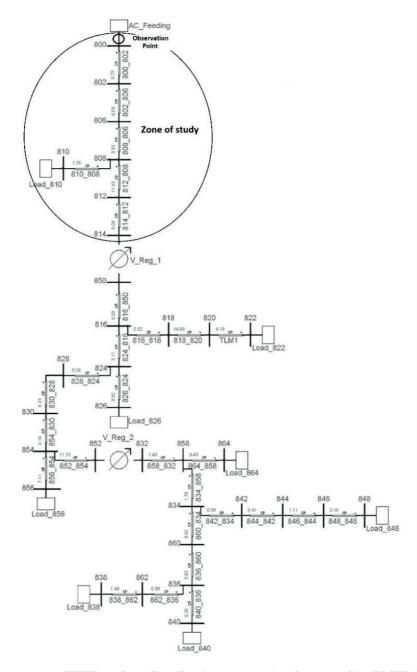

| Figure 2.25. IEEE 34-bus distribution system implemented in EMTP-RV                                                                                                                                                                                                                                                                                                                                             |

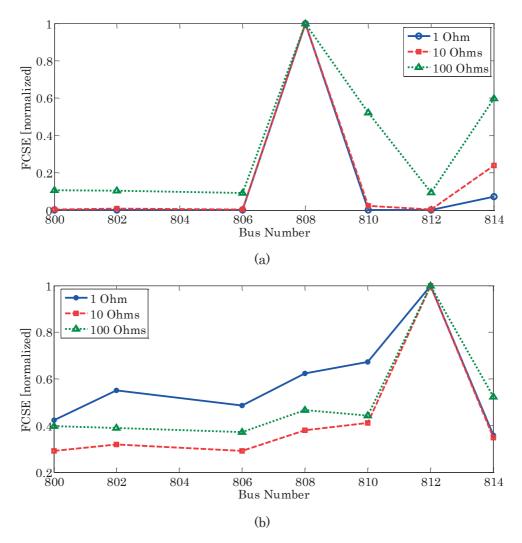

| Figure 2.26. Normalized FCSE as a function of the GFL and for different guessed fault resistance values: a) three-phase-to-ground solid fault (0 $\Omega$ ) at Bus 808, b) three-phase-to-ground high-impedance fault (100 $\Omega$ ) at Bus 812                                                                                                                                                                |

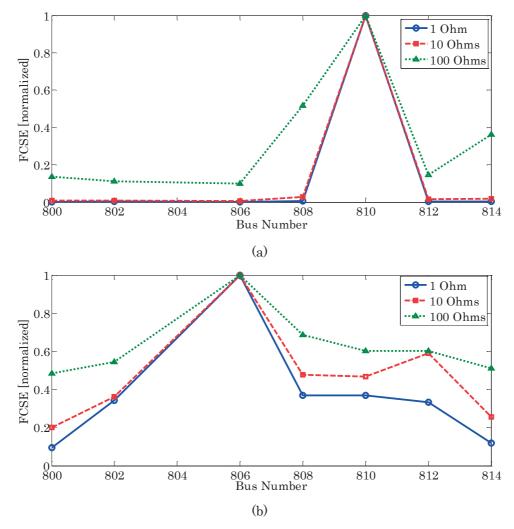

| Figure 2.27. Normalized FCSE as a function of the GFL and for different guessed fault resistance values: a) single-phase-to-ground solid fault (0 $\Omega$ ) at Bus 810, b) single-phase-to-ground high-impedance fault (0 $\Omega$ ) at Bus 806                                                                                                                                                                |

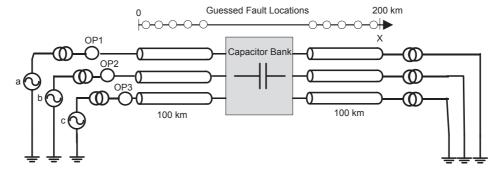

| Figure 2.28. Schematic representation of the series-compensated three-conductor transmission line system implemented in the EMTP-RV                                                                                                                                                                                                                                                                             |

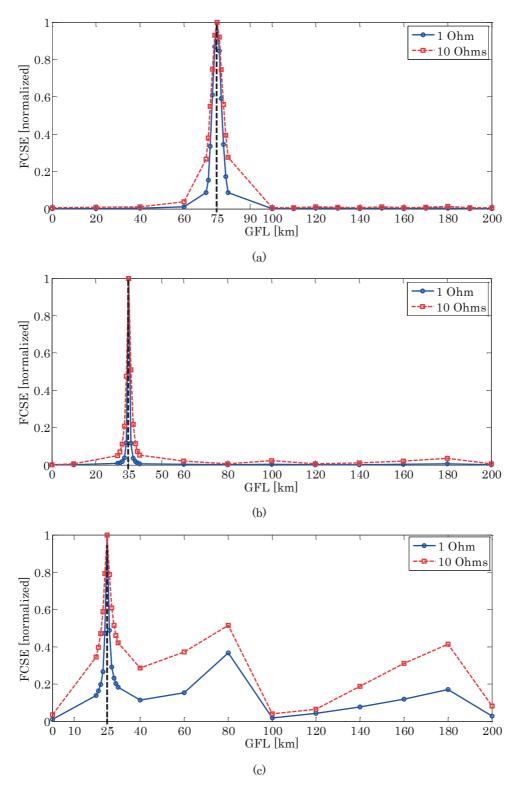

| Figure 2.29. Normalized energy of the fault current as a function of GFLs and for different guessed fault resistance values (i.e., 1 and 10 Ohms); (a) three-phase-to-ground fault at $x_f = 75$ km, (b) double-phase-to-ground fault at $x_f = 35$ km, (c) single-phase-to-ground fault at $x_f = 25$ km |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

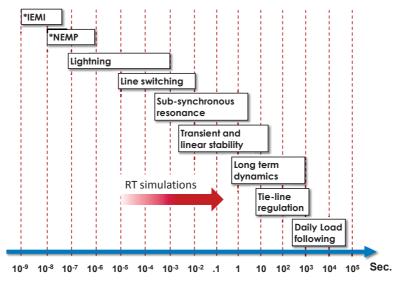

| Figure 3.1. Time frame of various transient phenomena (adapted from [74])55                                                                                                                                                                                                                               |

| Figure 3.2. Schematic representation of HIL test by means of RTDS56                                                                                                                                                                                                                                       |

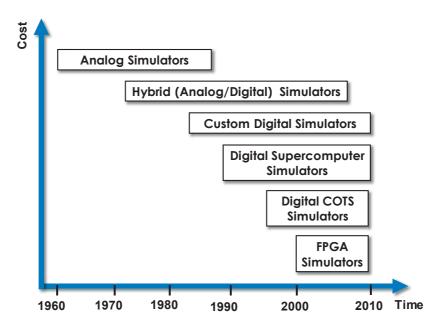

| Figure 3.3. Evolution of Real-Time Simulation Technologies                                                                                                                                                                                                                                                |

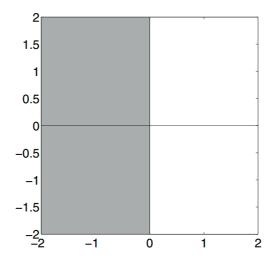

| Figure 3.4. Stability region of BE method (adapted from [121])65                                                                                                                                                                                                                                          |

| Figure 3.5. Stability region of trapezoidal method (adapted from [121])66                                                                                                                                                                                                                                 |

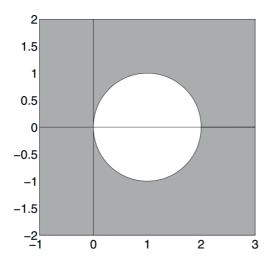

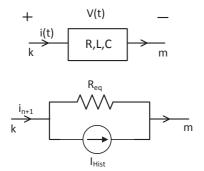

| Figure 3.6. Lumped elements (R, L, C) and relevant companion model68                                                                                                                                                                                                                                      |

| Figure 3.7. Single line representation of a single conductor transmission line connecting nodes $k$ and $m$ (adapted from [74])70                                                                                                                                                                         |

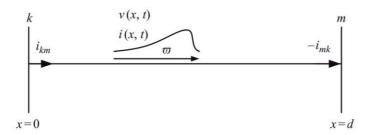

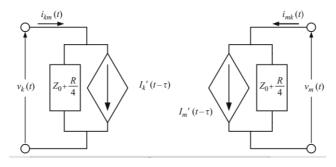

| Figure 3.8. Bergeron transmission line model (adapted from [74])70                                                                                                                                                                                                                                        |

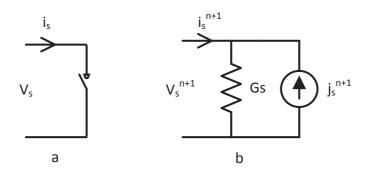

| Figure 3.9. ADC switch model (adapted from [130])73                                                                                                                                                                                                                                                       |

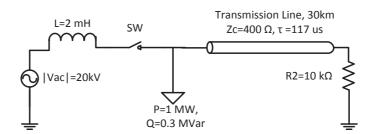

| Figure 3.10. Schematic representation of the test case composed of a single-conductor transmission line and a switch                                                                                                                                                                                      |

| Figure 3.11. Line current at the beginning of the line for four switch representation models (i) ideal switch, (ii) FAMNM for $G_s$ = 0.1, and (iii) FAMNM for $G_s$ = 1, and (iv) FAMNM for $G_s$ = 10                                                                                                   |

| Figure 3.12. Definition of Euclidian distance between eigenvalues of the network admittance matrix based on FAMNM and those associated with the admittance matrices of two reference networks                                                                                                             |

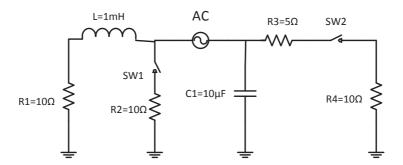

| Figure 3.13. Schematic of the RLC case study including one switch83                                                                                                                                                                                                                                       |

| Figure 3.14. Objective, error, and switch-losses functions for the case of the RLC test case of Figure 3.13.                                                                                                                                                                                              |

| Figure 3.15. Objective, error, and switch-losses functions for the case of transmission line test case (Figure 3.10) with variable $G_s$                                                                                                                                                                  |

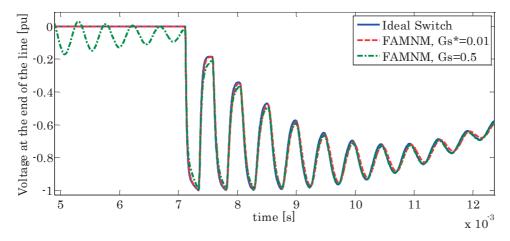

| Figure 3.16. Time-domain simulated waveforms for voltage at the end of the transmission line (second test case of Figure 3.10 for different values of $G_s$ . 84                                                                                                                                          |

| Figure 3.17. Schematic of the RLC case study including two switches85                                                                                                                                                                                                                                     |

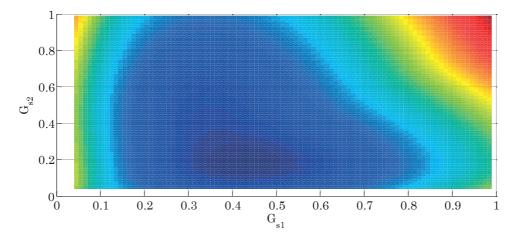

| Figure 3.18. Objective function used to assess the optimal <i>Gs</i> values for the case of RLC circuit with two switches shown in Figure 3.1785                                                                                                                                                          |

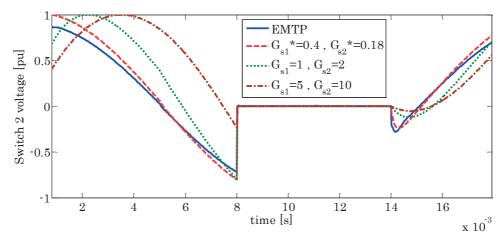

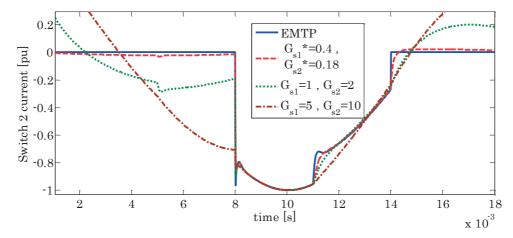

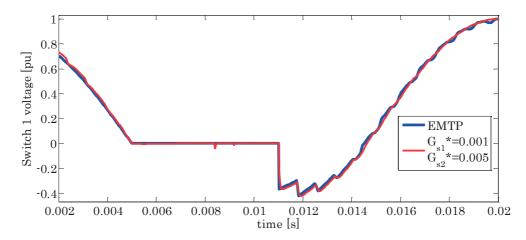

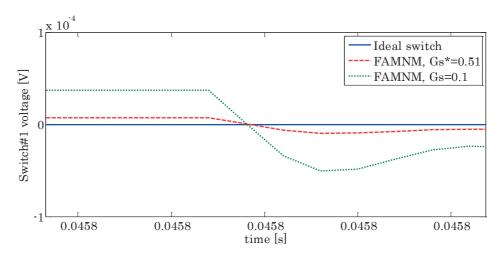

| Figure 3.19. Time-domain simulated waveforms for switch #2 voltage for the optimal values of $Gs_1$ , $Gs_2$ for the circuit composed of RLC elements and two switches    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

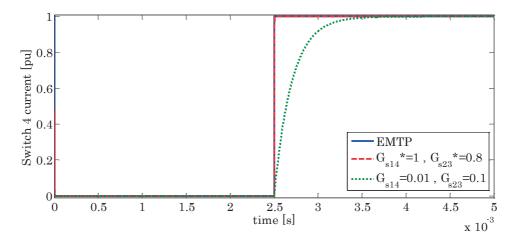

| Figure 3.20. Time-domain waveforms for switch #2 current for the optimal values of $Gs_1$ , $Gs_2$ for the circuit composed of RLC elements and two switches              |

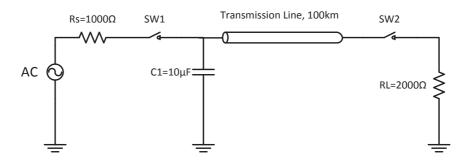

| Figure 3.21. Schematic representation of the test case composed of a single conductor transmission line and two switches                                                  |

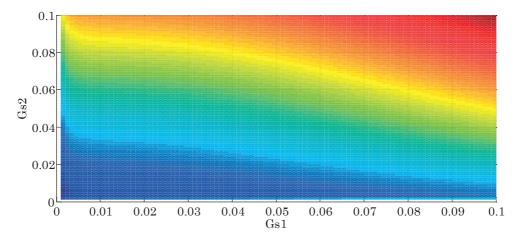

| Figure 3.22. Objective used to assess the optimal $Gs$ values for the case of a single conductor transmission line with two switches shown in Figure 3.21                 |

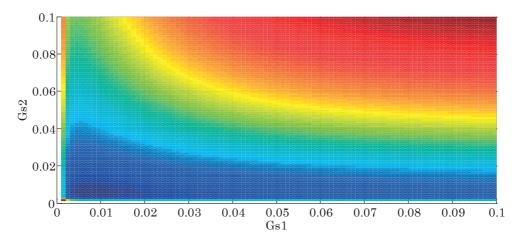

| Figure 3.23. Error functions used to assess the optimal $Gs$ values for the case of a single-conductor transmission line with two switches shown in Figure 3.21 87        |

| Figure 3.24. Time-domain waveforms for switch #1 voltage for the optimal values of $Gs_1$ , $Gs_2$ for the case of a single-conductor transmission line with two switches |

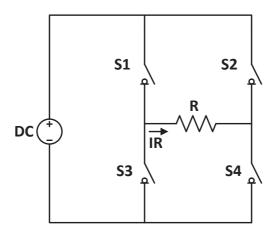

| Figure 3.25. Schematic representation of single phase DC/AC converter                                                                                                     |

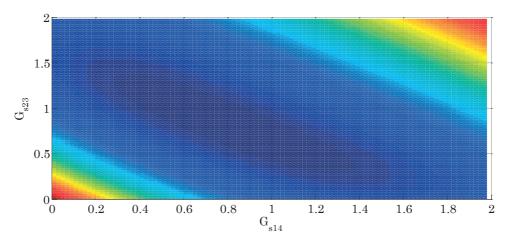

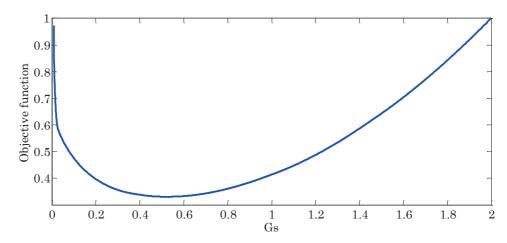

| Figure 3.26. Objective function used to assess the optimal $G_s$ values for the case of single phase power converter with four switches shown in Figure 3.25 89           |

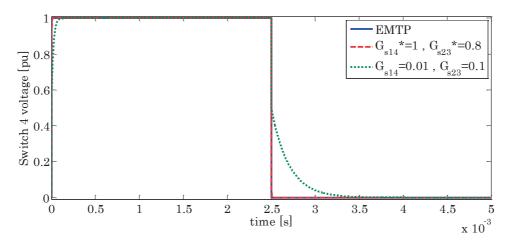

| Figure 3.27. Time-domain simulated waveforms for switch #4 voltage for two sets of switches parameters values including the optimal ones optimal                          |

| Figure 3.28. Time-domain simulated waveforms for switch #4 current for two sets of switches parameters values including the optimal ones optimal                          |

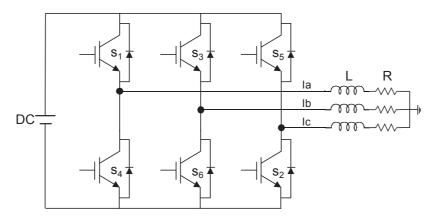

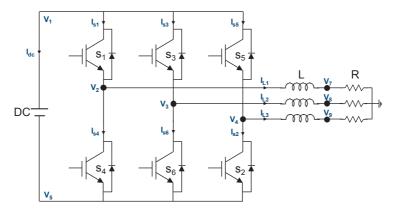

| Figure 3.29. Schematic representation of the two-level three-phase inverter 90                                                                                            |

| Figure 3.30. The calculated objective function for the optimal assessment of the switch conductance values of the two-level three-phase inverter                          |

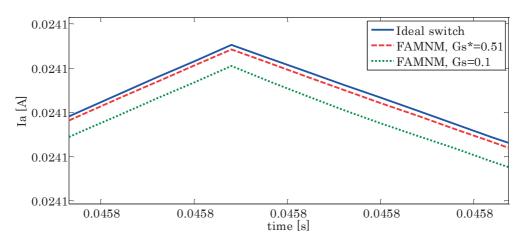

| Figure 3.31. Time-domain simulated waveforms of the load current for ideal switch representation and FAMNM based optimal <i>Gs</i> and non-optimal one                    |

| Figure 3.32. Time-domain simulated waveforms of the switch#1 voltage for ideal switch representation and FAMNM based optimal <i>Gs</i> and non-optimal one 91             |

| Figure 4.1. Schematic representation of NI CompactRIO platform                                                                                                            |

| Figure 4.2. Hardware architecture of developed FPGA RTS based on NI 9033 96                                                                                               |

| Figure 4.3. The flowchart of the algorithm in Data_ext to read <i>netlist</i> files 98                                                                                    |

| Figure 4.4. Values_sim module input/outputs. 99                                                                                                                           |

| Figure 4.5. ANAM module inputs/outputs                                                                                                                                    |

| Figure 4.6. Opt_Gs module inputs/outputs101                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.7. FP numerical representation                                                                                                                                                                                                             |

| Figure 4.8. FXP numerical representation                                                                                                                                                                                                            |

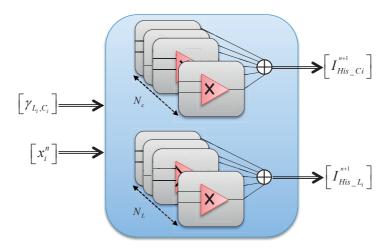

| Figure 4.9. RHS computation module for lumped elements                                                                                                                                                                                              |

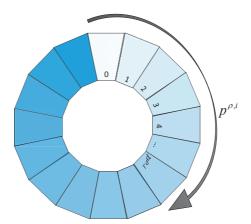

| Figure 4.10. Structure of the transmission lines circular buffers using FIFOs111                                                                                                                                                                    |

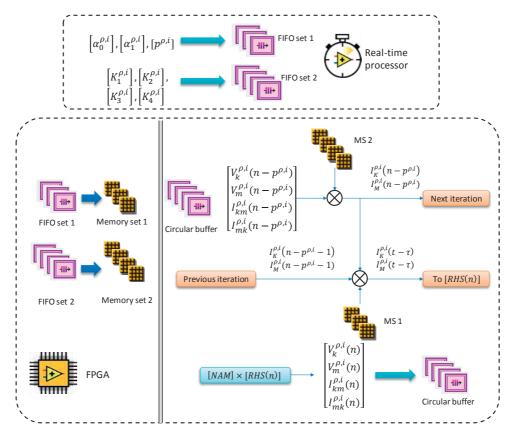

| Figure 4.11. RHS computation for the transmission lines                                                                                                                                                                                             |

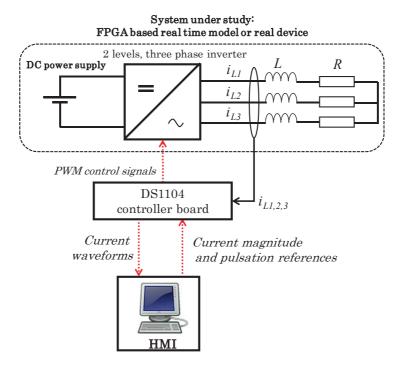

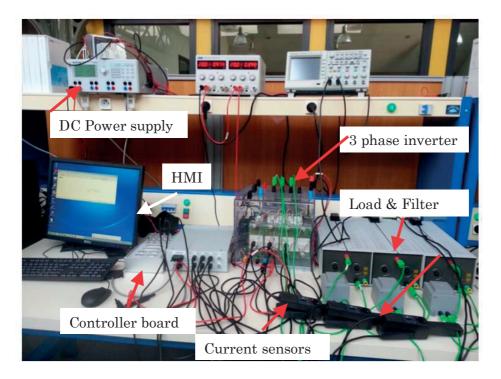

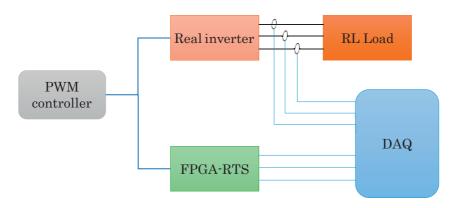

| Figure 4.12. Schematic representation of the HIL setup                                                                                                                                                                                              |

| Figure 4.13. Schematic of the considered inverter and MANA variables                                                                                                                                                                                |

| Figure 4.14. HIL test setup                                                                                                                                                                                                                         |

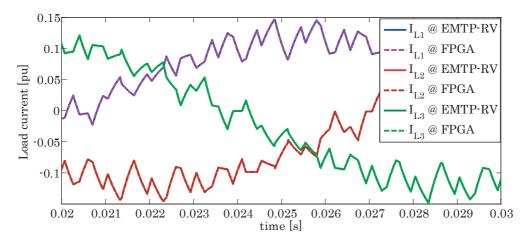

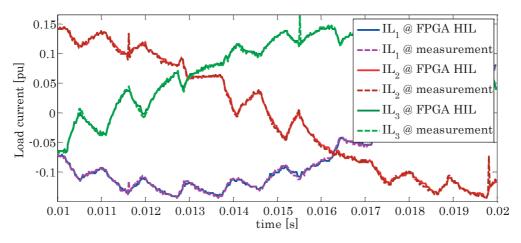

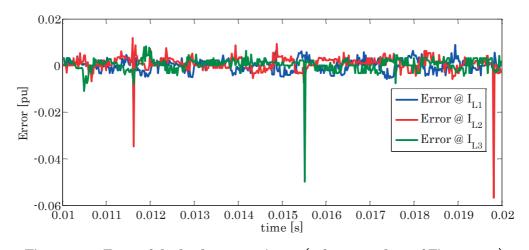

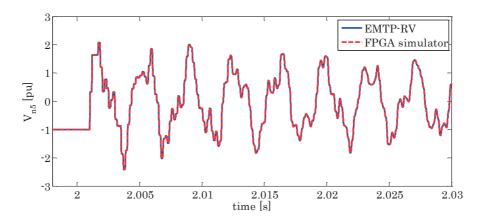

| Figure 4.15. Comparison of the FPGA-RTS results with the EMTP-RV ones116                                                                                                                                                                            |

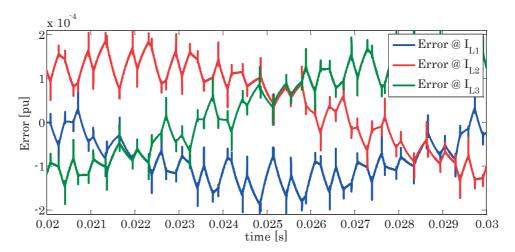

| Figure 4.16. Error of the load currents (reference values of Figure 4.15)117                                                                                                                                                                        |

| Figure 4.17. The schematic of the HIL validation setup                                                                                                                                                                                              |

| Figure 4.18. Comparison of the FPGA-HIL test results with the measured ones. 118                                                                                                                                                                    |

| Figure 4.19. Error of the load currents in pu. (reference values of Figure 4.18)118                                                                                                                                                                 |

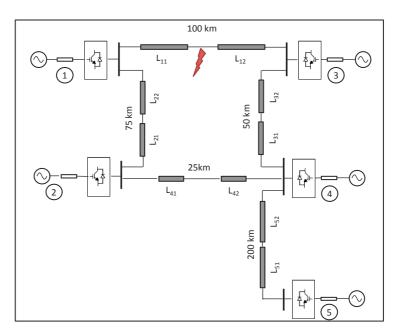

| Figure 4.20. Schematic representation of the MTDC network under study119                                                                                                                                                                            |

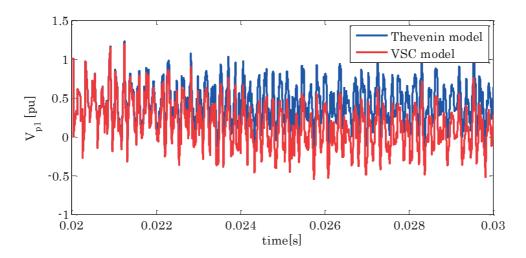

| Figure 4.21. Comparison between the simulation results obtained using Thevenin equivalent and VSC models for the positive pole voltage at Station 1                                                                                                 |

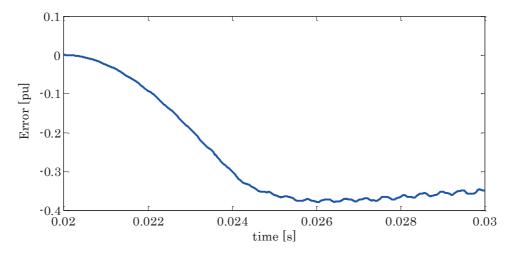

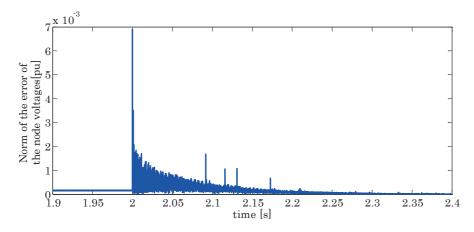

| Figure 4.22. Error between the simulation results obtained using Thevenin equivalent and VSC models for the positive pole of Station 1                                                                                                              |

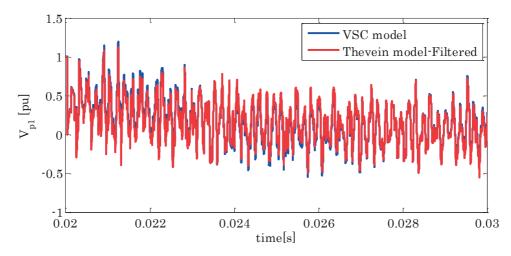

| Figure 4.23. Comparison between the simulation results obtained using Thevenin and VSC models for the positive pole voltage at Station 1. A first-order high-pass filter is applied for the results obtained by Thevenin equivalent model           |

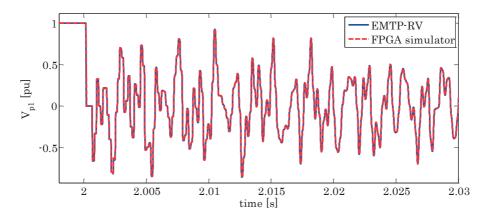

| Figure 4.24. Comparison between the FPGA-based simulations with respect to the EMTP-RV ones: phase-to-ground voltage observed in the positive pole of the station 1 subsequent to a solid p2p fault in the middle of the first transmission line122 |

| Figure 4.25. Comparison between the FPGA-based simulations with the EMTP-RV ones: phase-to-ground voltage observed in the negative pole of the station 5 subsequent to a solid p2p fault in the middle of the first transmission line122            |

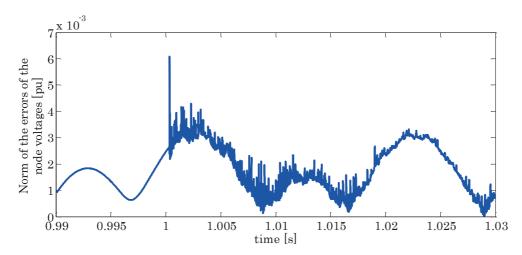

| Figure 4.26. Norm of the error of the node voltages computed with the FPGA-simulator vs the EMTP-RV ones                                                                                                                                            |

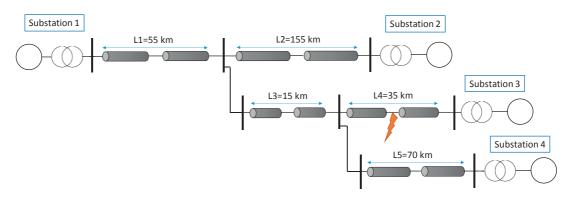

| Figure 4.27. Schematic representation of the considered AC network                                                                                                                                                                                  |

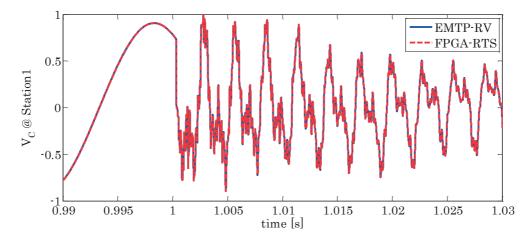

| Figure 4.28. Comparison between the FPGA-based simulations with respect to the EMTP-RV ones: phase-to-ground voltage observed in phase c of substation 1, for a solid three-phase fault in the 30 km of the 4 transmission line |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.29. Norm of the errors of the voltages observed at station 1                                                                                                                                                           |

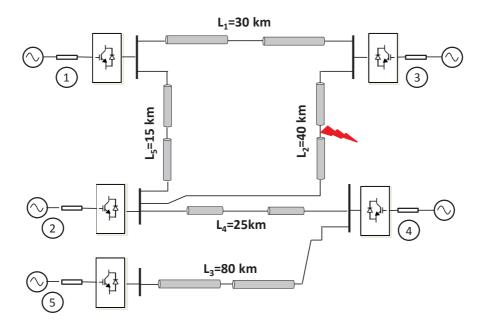

| Figure 5.1. Schematic representation of the MTDC network under study 134                                                                                                                                                        |

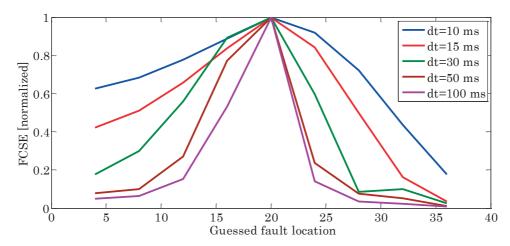

| Figure 5.2. Impact of time reversal window length on the accuracy of the proposed EMTR-based fault location method (the real fault location is in line 2 at $20 \text{ km}$ ). $134 \text{ m}$                                  |

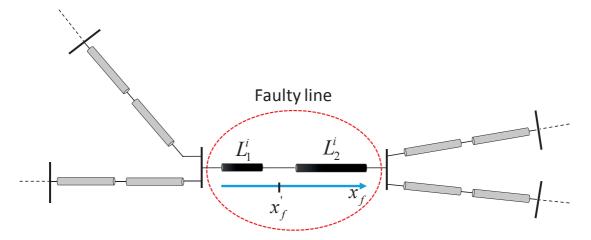

| Figure 5.3. A faulty line in a network in which EMTR-fault location is applied. $136$                                                                                                                                           |

| Figure 5.4. Structure of the developed fault location platform                                                                                                                                                                  |

| Figure 5.5. Transient signals in station 5 for positive pole. The green waveform corresponds to time window from the fault occurrence to the breakers openings. 139                                                             |

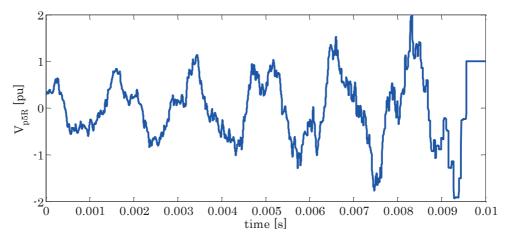

| Figure 5.6. Time-reversed voltage signal recorded at station 5 for positive pole $139$                                                                                                                                          |

| Figure 5.7. Example of FCSE as a function of guessed fault location along the line 3 for different observation point back-injections. The fault is p2p at 20 km 141                                                             |

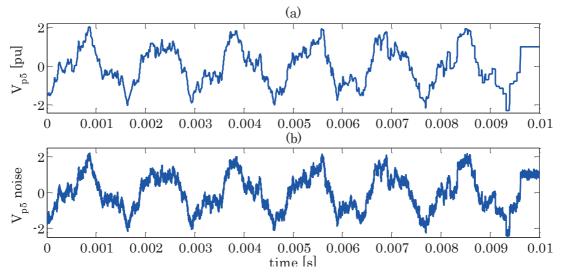

| Figure 5.8. (a) The time-reversed voltage signal recorded at station 5 for positive pole; (b) the same signal by adding 20 dB noise                                                                                             |

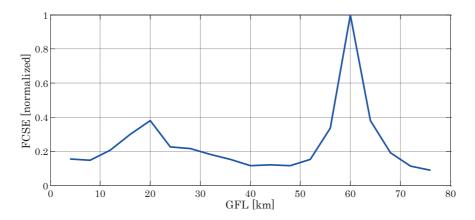

| Figure 5.9. FCSE as a function of GFL for a p2p fault at 60km of line 3. The fault impedance is $100 \ \Omega$ .                                                                                                                |

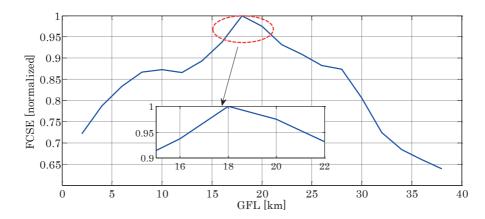

| Figure 5.10. FCSE as a function of GFL for a p2g fault at 18 km of line 2. The fault impedance is $50~\Omega$ .                                                                                                                 |

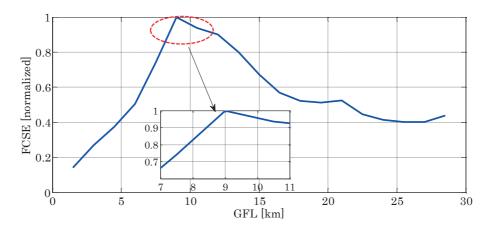

| Figure 5.11. FCSE as a function of GFL for a p2p fault at 9km of line 1. The fault impedance is $50~\Omega$ .                                                                                                                   |

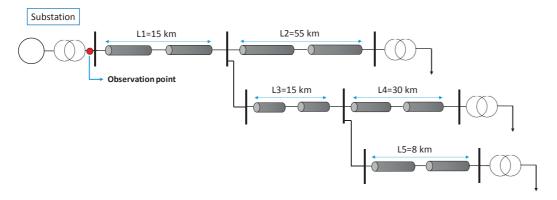

| Figure 5.12. Radial distribution network composed of 5 transmission lines 146                                                                                                                                                   |

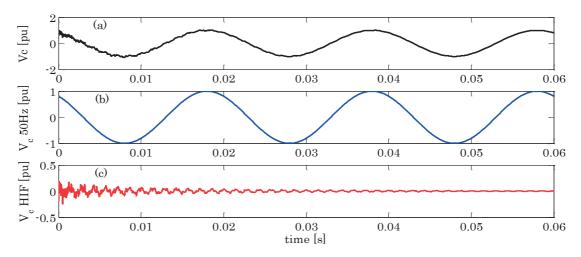

| Figure 5.13. (a) Observed post-fault voltage waveform for phase c for a a-b-g fault at $5  \text{km}$ of Line1, (b) $50  \text{Hz}$ component, (c) extracted high frequency transients $147  \text{m}$                          |

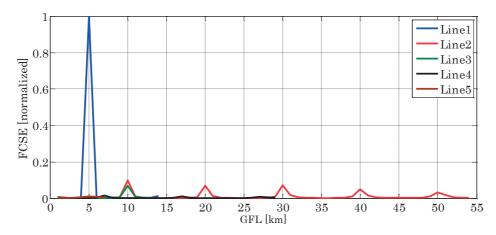

| Figure 5.14. FCSE as a function of GFLs along all the lines. The real fault is at 5km of the Line1 and the fault type is a-b-g                                                                                                  |

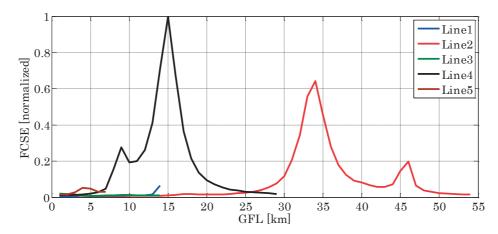

| Figure 5.15. FCSE as a function of GFLs along all the lines. The real fault is at 15km of the Line4 and the fault type is a-g                                                                                                   |

| Figure 5.16. FCSE as a function of GFL for a 3ph fault at 25km of line 2. The fault impedance is $100\Omega$ .                                                                                                                  |

| Figure 5.17. FCSE as a function of GFL for a ph-ph fault at 10km of line 1. The fault impedance is $100 \Omega$ .                                                                                                               |

## List of Tables

| Table 2.1. Parameters of the Line.                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2.2. Location error according to the three Models of Back-Propagation35                                                                             |

| Table 3.1. Companion models parameters associated with RLC elements68                                                                                     |

| Table 4.1. CompactRIO-9033 specifications96                                                                                                               |

| Table 4.2. Decomposed ANAM <sup>-1</sup>                                                                                                                  |

| Table 4.3. Decomposed RHS105                                                                                                                              |

| Table 4.4. ANAM <sup>-1</sup> mapping based on RHS elements                                                                                               |

| Table 4.5. ANAM <sup>-1</sup> and RHS elements mapping by removing redundant information                                                                  |

| Table 4.6. ANAM <sup>-1</sup> and RHS elements mapping with respect to the number of iterations in each row                                               |

| Table 4.7. ANAM <sup>-1</sup> and RHS elements mapping for the fixed size iterations by adding zeros                                                      |

| Table 4.8. Performance and hardware usage comparison of the sparse and non-sparse matrix to vector multipliers                                            |

| Table 4.9. FPGA hardware usage for the HIL test case                                                                                                      |

| Table 4.10. FPGA hardware usage for the MTDC network case study121                                                                                        |

| Table 4.11. FPGA hardware usage for the three-phase power network case study.                                                                             |

| Table 5.1. Performance assessment of the developed fault location platform by considering different fault types at different locations along the lines141 |

| Table 5.2. Performance assessment of the developed fault location platform by considering different fault types at different locations along the lines. The time reversed signals are contaminated with 40 dB SNR noise                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 5.3. Performance assessment of the developed fault location platform by considering different fault types at different locations along the lines. The time reversed signals are contaminated with 20 dB SNR noise                                |

| Table 5.4. Performance assessment of the developed fault location platform by considering different fault types at different locations along the lines. The measurement systems time delay to start recording the signals is 1 ms                      |

| Table 5.5. Performance assessment of the developed fault location platform by considering different fault types at different locations along the lines. The measurement systems time delay to start recording the signals is 2 ms                      |

| Table 5.6. Performance assessment of the developed fault location platform for the case of ADN by considering different fault types at different locations along the lines.                                                                            |

| Table 5.7. Performance assessment of the developed fault location platform for the case of ADN by considering different fault types at different locations along the lines. The recorded transient signals are contaminated with 40 dB noise 150       |

| Table 5.8. Performance assessment of the developed fault location platform for the case of ADN by considering different fault types at different locations along the lines. The recorded transient signals are contaminated with 20 dB noise 150       |

| Table 5.9. Performance assessment of the developed fault location platform for the case of ADN by considering different fault types at different locations along the lines. The measurement systems time delay to start recording the signals is 1 ms  |

| Table 5.10. Performance assessment of the developed fault location platform for the case of ADN by considering different fault types at different locations along the lines. The measurement systems time delay to start recording the signals is 2 ms |

### List of Acronyms

ADN Active Distribution Network

ALE Average Location Error

ANAM Augmented Nodal Admittance Matrix

ANN Artificial Neural Network

BAF Bode's Asymptotic Fitting

BE Backward Euler

CP Constant Parameter

CHIL Controller Hardware-In-the-Loop

CWT Continuous Wavelet Transform

DFR Digital Fault Recorder

DG Distributed Generation

DMA Direct Access Memory

DSP Digital Signal Processor

DWT Discrete Wavelet Transform

EMTP Electromagnetic Transient Program

EMTR Electromagnetic Time Reversal

FCSE Fault Current Signal Energy

FD Frequency Dependent

FE Forward Euler

FIFO First-In First-Out

**FP** Floating Point

**FXP** Fixed Point

GFL Guessed Fault Location

GPS Global Positioning System

GUI Graphical User Interface

IED Intelligent Electronic Device

LCC Line Commutated Converters

LTE Local Truncation Error

MANA Modified Augmented Nodal Analysis

NEMP Nuclear Electromagnetic Pulse

PCM Phase-Conjugate Mirror

RHS Right Hand Side

RTS Real-Time Simulator

SNR Signal to Noise Ratio

TNA Transient Network Analyzer

TR Time Reversal

TRM Time Reversal Mirror

ULM Universal Line Model

VSC Voltage Source Converter

WT Wavelet Transform

### Introduction

#### 1.1 Motivation of the Thesis

Fundamental changes are taking place in the monitoring, control and protection of modern power grids where an increasing amount of renewable energy sources are progressively and massively hosted. It is generally acknowledged that such integration of renewables into existing grids depends on the successful combination of specific control processes and availability of new technologies. This last element is motivating the emergence of complex power systems and power electronics architectures in order to interface sources at various voltage levels of DC and AC grids.

In this context, high-performing electromagnetic transient (EMT) simulation tools capable to study, possibly in real-time, the dynamic behavior of these complex systems are needed to study, and develop, new solutions for the monitoring, control and protection of modern power grids.

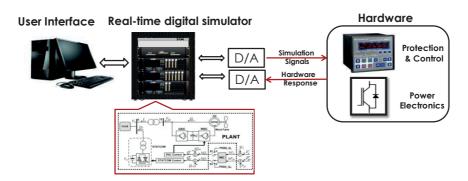

Real-time simulators (RTSs) are specific simulation platforms able to replicate, in real-time, the exact behavior of the system under study. This peculiarity enables their coupling with real (hardware) controllers and protection systems making possible the fast prototyping of new solutions via hardware-in-the-loop (HIL) analysis.

At the same time, the growing complexity of power converters topologies (e.g., multi-modular converters - MMC) and the need for the definition of their controls, calls for more accurate and faster RTS capable to accurately simulate the switching transients and perform realistic HIL simulations. In this respect, conventional RTSs are characterized by major limitations which bound their application for

particular cases. Therefore, there is the need to develop faster RTS platforms which are able to accurately simulate complex topologies within much lower simulation time steps (i.e., in the range of hundreds of nanoseconds).

At the same time, there is an unexplored field related to the coupling of RTSs with the real-time operation of power grids. One of the typical application examples refers to fault management and, more specifically, to the possibility of merging fault location and relaying functionalities in complex systems (especially multi-terminal DC – MTDC – grids and active distribution networks (ADN)).

#### 1.1.1 The Issue of Fault Location

The fault location problem has been extensively studied in the literature for many years and numerous methods have been proposed for both transmission and distribution networks. Nevertheless, despite the vast amount of literature, the problem of fault location still represents a challenge for both transmission and distribution networks. In general, the accuracy of the existing fault location methods are affected by several factors including: pre-fault system condition, load flow, power swing, communication link accuracy (for the case of multi-end methods), fault impedance, and presence of noise. In particular, for the case of MTDC grids and ADNs, the problem is more critical and requires more in-depth studies.

Indeed, the massive integration of new types of generation units (i.e., renewable energy resources) available in remote locations (e.g., offshore wind farms) requires new grid topologies mainly based on the MTDC topology. The protection and fault location in such networks is a challenging task and represents the major obstacle to pervasive deployment of such networks. The transmission lines in MTDC networks are generally long and spread over seas which limits the accessibility of the maintenance team. Furthermore, since the lines in such networks are considered to transfer bulk power over long distances, the loss of a line might cause overloading and congestion in other lines.

Existing methods for point-to-point HVDC links cannot be applied to MTDC networks due to more complex topology and characteristics of these networks. Therefore, more sophisticated fault location techniques are necessary for the case of MTDC network. In this respect, few fault location methods have been proposed in the literature. However, the investigations are in their early stages and more studies are necessary to be carried out.

On the other hand, typical fault location methods based on the estimation of the post-fault impedance, are not applicable in the case of ADNs. With the hypothesis of having a fully passive power system, such estimation could provide useful

information to locate the fault when compared with the line impedance. However, the presence of other sources (e.g. associated with the increasing penetration of dispersed generation (DG)s) can largely affect the accuracy of these procedures. Therefore, travelling wave-based methods (which are not affected by the presence of DGs) might be preferred to locate faults in these networks. Nevertheless, one of the main limitations associated with these methods is that, in general, they require multi-end measurements in order to provide a reasonable accuracy. Therefore, there is an associated need for installing several measurement stations and fast communication links that add a non-negligible amount of complexity and might impair the reliability of the system. On the other hand, the use of a single measurement station might not allow to obtain the required level of accuracy.

# 1.1.2 Need for FPGA-Based RTS for Power Electronics and Power Systems Applications

Existing RTSs are mainly based on digital signal processors (DSP) or general purpose CPU-based platforms where the real-time simulation is achieved by partitioning large networks into smaller sub-systems and processing them in parallel. For these type of RTSs, the minimum achievable real-time simulation time step is in the range of few tens of microseconds. The main reason for this relatively large simulation time step is the partial sequential operations that the CPU architectures need to deploy. The growing complexity of the power systems and power electronic devices and the need for accurate EMT simulations of fast transients, require a higher frequency bandwidth of the real-time simulators. The relatively large simulation time steps required by these simulators do not allow to represent in real-time high frequency phenomena such as EMTs in power converters or travelling wave transients taking place in transmission lines (e.g., fault and switching transients).

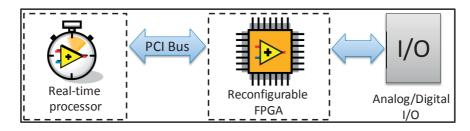

FPGA is a suitable alternative to be used as a real-time simulator computational core. The main advantage of FPGA over CPU or DSP is its hardwired parallel processing that enables the implementation of specific methodologies that dramatically reduce the sequencing of the operations taking place in CPUs or DSPs. Furthermore, In FPGAs the latency associated with the import/export of the I/Os are lower compared to the CPUs. Finally, FPGAs are fully configurable chips, which allow to be configured for specific applications.

The existing FPGA-based RTSs are mainly dedicated to the power electronics applications and their HIL tests where the switches are represented by means of associated discrete circuit (ADC) model in which the switch is represented by a constant conductance in parallel with a controlled current source. This specific switch model enables adapting the so-called fixed admittance matrix nodal method (FAMNM), which is widely used in the proposed FPGA-RTSs in the literature. This

method, irrespective of the number of the switches and their states, allows obtaining a fixed nodal admittance matrix during switching transitions. Therefore, it results in accelerating the EMT simulation of switching devices and performing the real-time simulation of these circuits within very small simulation time steps in the order of hundreds of nanoseconds. However, this simple model introduces artificial oscillations and non-negligible errors in the simulation results. In particular, the considered value for the conductance can dramatically impact the simulation results accuracy and it is essential to calculate the optimal conductance value to minimize the relevant simulation errors. Nevertheless, the existing FPGA-RTSs adopting this switch model do not consider this impact and, in general, the quantitative error assessments are not provided.

Another important drawback of FPGA-RTSs is their difficult programming associated with the use of hardware description languages (HDL). This low level programming, limits the scalability of the solvers and, as a consequence, the representation of complex circuits. Additionally, any modification in the implemented algorithm/model requires, in general, a time-consuming recompilation of the HDL code. A few automated FPGA-based RTSs have been proposed to avoid the difficulties of the FPGAs programming. However, the applications of these simulators are mainly dedicated to power electronics HIL simulations. Therefore, these studies have not accounted for the possibility to simulate power networks including propagative transmission lines.

#### 1.2 Objectives and Contributions of the Thesis

The aim of this thesis is to address the above-mentioned challenges regarding the problems of fault location in power networks and FPGA-based real-time simulators for power electronic and power grids. In this thesis, a new automated general purpose FPGA-based RTS is developed that solves the problem of switch models and variable grid topologies. Furthermore, a specific application of this FPGA-based RTS is explored in order to merge relaying and fault location functionalities by leveraging the electromagnetic time reversal (EMTR) theory. In what follows, the main contributions of the thesis are summarized by making reference to the two steps accomplished to develop the fault location platform.

### 1.2.1 Fault location in Power Networks Based on Electromagnetic Time Reversal (EMTR) Theory

An original fault location technique based on the EMTR theory is presented. The proposed method takes advantage of the time reversal invariance of the telegraphers' equations describing the wave propagation in transmission lines. The approach is successfully applied to different types of transmission and distribution

networks and is able to overcome several limitations associated to existing fault location methods. More specifically, the proposed method can be used in the case of inhomogeneous networks composed of different transmission lines with different characteristic impedances and propagation constants (for example, networks comprising overhead lines and underground cables). A further advantage of the developed EMTR-based fault location method is that it minimizes the number of observation points required to perform the measurement of the transient signals. In particular, it is shown that a single observation point located at the secondary winding of a substation transformer is enough to correctly identify the fault location, even for complex topologies. In addition, the performance of the method is very robust to the topology of the system, fault type and impedance, presence of series compensation, presence of noise, and delay of the measurement systems.

# 1.2.2 Automated FPGA-RTS for the EMT Simulations of Power Electronic Devices and Power System Grids

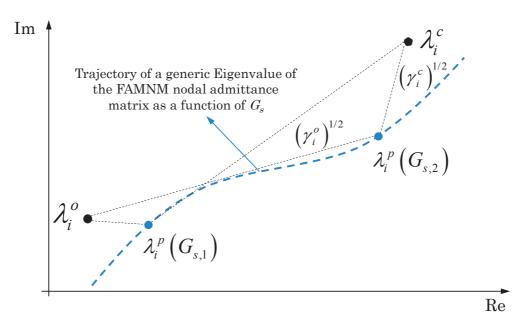

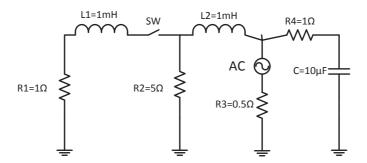

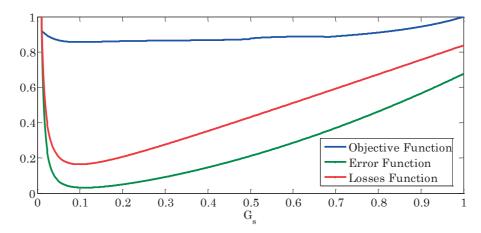

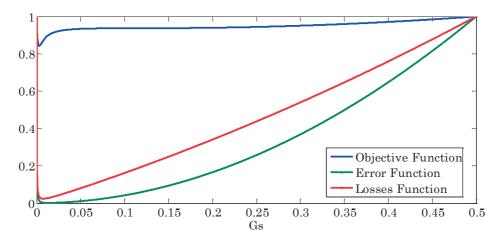

In order to develop an automated FPGA-RTS dedicated to high-performance EMT simulations, the thesis proposes an efficient method for an accurate simulation of switching devices. In particular, by considering the drawback of the classical ADC switch model, a novel method for the optimal assessment of the parameters of the ADC model is presented. The proposed method is based on the minimization of the Euclidian distance between the eigenvalues of the network admittance matrix based on FAMNM, and those associated with the admittance matrices of reference networks corresponding to all possible switching permutations. To prove the correctness of the proposed method, a comparison between the proposed metric and specifically defined error functions is presented and discussed. Several validation examples are considered to prove the performance of the proposed method.

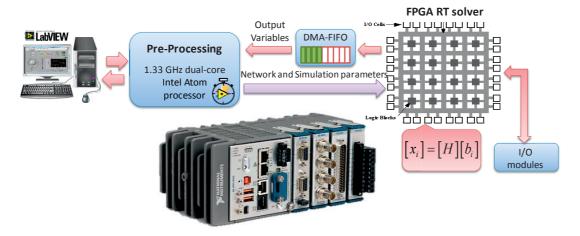

Then, an automated FPGA-based real-time EMT simulator is proposed which integrates the developed model for switching devices. An automated procedure is used to overcome the limitations of current FPGA-RTSs.

The proposed RTS is implemented into an industrial real-time embedded system (the National Instruments CompactRio real-time platform) and has the following features: (i) it makes use of the modified augmented nodal analysis (MANA) method, (ii) it integrates the FAMNM together with the optimal selection of the switch conductance parameter, (iii) it enables the possibility of accurately reproducing electromagnetic switching transients taking place in power electronic switching devices together with electromagnetic wave propagation in transmission lines, and (iv) it enables to reach extremely low integration time steps and provides an automated procedure to directly translate the schematic representation of the electrical circuits designed in the EMTP-RV simulation environment to the relevant FPGA solver by avoiding the need of HDL programing languages. Such

peculiarity enables a straightforward applicability of the proposed FPGA-based RTS to various power electronics and power systems applications.

The performance of the developed FPGA-RTS is assessed by considering three validation examples. They refer to (i) a two-level three-phase inverter, (ii) a multi-terminal HVDC network, and (iii) a three-phase AC network. The comparison of the obtained results with offline benchmark simulations and HIL results showed an excellent agreement together with a high computation efficiency.

#### 1.3 Thesis Outline

The structure of the thesis dissertation is as follows.