# MULTILEVEL-CELL PHASE-CHANGE MEMORY - MODELING AND RELIABILITY FRAMEWORK

## THÈSE Nº 6801 (2016)

PRÉSENTÉE LE 14 JANVIER 2016

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR LABORATOIRE DE SYSTÈMES MICROÉLECTRONIQUES PROGRAMME DOCTORAL EN GÉNIE ÉLECTRIQUE

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

#### PAR

## Aravinthan ATHMANATHAN

acceptée sur proposition du jury:

Prof. G. De Micheli, président du jury Prof. Y. Leblebici, Dr M. Stanisavljevic, directeurs de thèse Dr E. Eleftheriou, rapporteur Dr R. Bez, rapporteur Dr J. Brugger, rapporteur

All birds find shelter during a rain ...

But eagle avoids rain by flying above the clouds ...

Problems are common, but attitude makes the difference ...

— Dr. A. P. J. Abdul Kalam

To my parents and wife...

# Acknowledgements

This accomplishment would not have been possible without the wonderful people who have inspired me on my journey towards the PhD. This PhD challenge would have been more of an academic title than a great adventure if not for them. I consider myself fortunate to have spent the last four years of my life in a great research atmosphere for learning, and also working with some exceptional individuals during the course of my doctoral studies.

I am greatly indebted to my supervisor, Prof. Yusuf Leblebici, who gave me the independence to pursue my ideas freely, while at the same time mentoring by example. I am especially grateful to my manager, Dr. Evangelos Eleftheriou, for giving me this wonderful opportunity to pursue my PhD thesis with IBM Research. His energy and enthusiasm have been an inspiration for me to aim ever higher in my pursuits. I am also thankful to my manager, Dr. Haralampos Pozidis, for his constant motivation and guidance throughout the course of my PhD thesis. I would also like to thank my thesis co-advisor, Dr. Milos Stanisavljevic, who has been my mentor and guide from the very beginning of my PhD studies, and has constantly provided me with help and encouragement on both professional and personal fronts. I would also like to thank my second co-advisor, Dr. Daniel Krebs, for his constant efforts in shaping me for my PhD.

Research in engineering is an extremely collaborative effort. I would like to acknowledge here my amazing colleagues and collaborators whose contributions helped in various aspects of my research.

- 1. Dr. Milos Stanisavljevic at IBM Research Zurich- in the design and implementation of the various programming and readout architectures for MLC PCM.

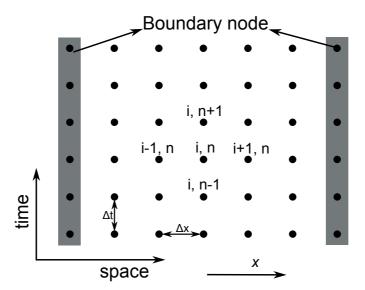

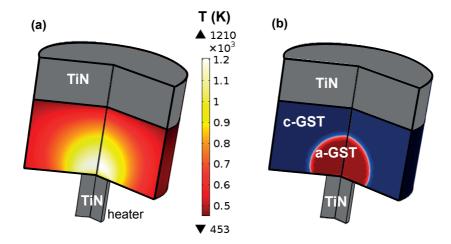

- 2. Dr. Daniel Krebs at IBM Research Zurich in the development of the finite-element method based thermoelectric model using COMSOL Multiphysics software.

- 3. Dr. Haralampoz Pozidis at IBM Research Zurich in the design and analysis of the drift-tolerant coding and detection schemes which are used for the demonstration of reliable triple-level cell storage.

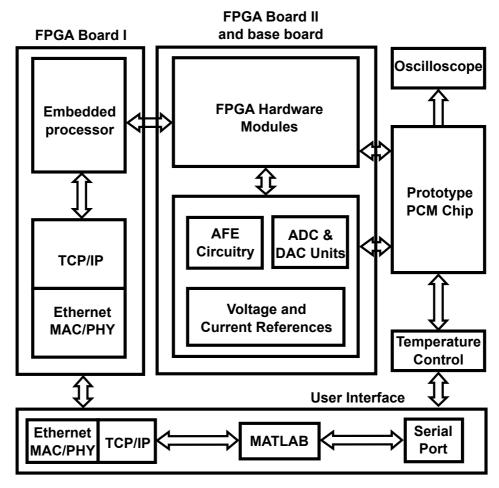

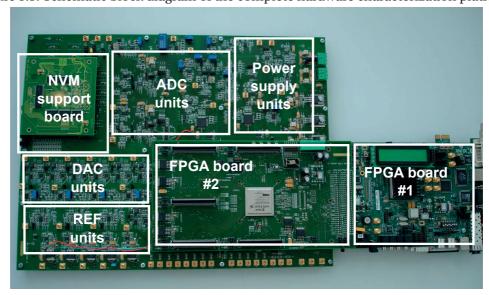

- 4. Dr. Nikolaos Papandreou and Mr. Urs Egger at IBM Research Zurich in the implementation of the embedded FPGA-based hardware characterization platform for the reliability experiments performed on the prototype PCM chip.

- 5. Dr. Abu Sebastian and Mr. Manuel Le Gallo at IBM Research Zurich in the development of the thermoelectric model by providing their valuable insights and experimental measurements.

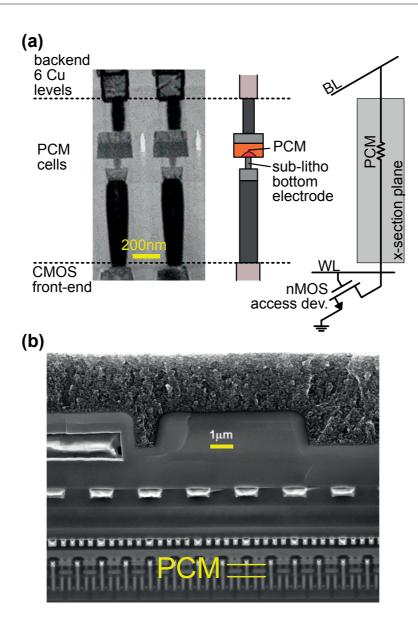

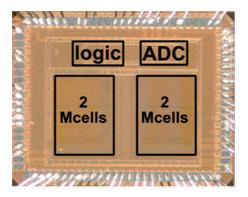

- 6. Dr. Chung H. Lam and Dr. Matt Brightsky at IBM T. J. Watson Research center for the fabrication and development of the prototype chips which were essentially used for the characterization experiments.

The IBM-SK Hynix joint-development agreement for PCRAM development, which funded a portion of my doctoral research, enabled me to collaborate with the various industrial research laboratories (IBM T. J. Watson Research in Yorktown Heights, USA, and Next Generation Memories research at SK-Hynix, South Korea), and provided a platform to exchange ideas with leading researchers from the PCM research community. I would like to thank my thesis jury members – Prof. Giovanni De Micheli, Prof. Jürgen Brugger, Dr. Roberto Bez and Dr. Evangelos Eleftheriou – for evaluating my thesis and providing valuable feedback and insights.

I would like to thank my colleagues of the Non-volatile memory systems group at IBM Research – Zurich - Thomas Parnell, Thomas Mittelholzer, Tobias Blätter and Nikolaos Papandreou - for their friendship and support, and for constantly inspiring me with their accomplishments. Thanks to Haralampos Pozidis, Milos Stanisavljevic and Charlotte Bolliger for proof-reading my thesis.

I would also thank the friends I made from IBM and EPFL — Arvind Raj, Vinodh, Viswanathan, Prasad, Nirmalraj, Jelena, Kazim, Jayant, Nicola, Rakesh and Felix - for the many enjoyable and intellectual conversations. I would also like to thank my friends Kumaran, Harish, Sailokesh, Mukund, Sindhuja, Siddharth, Ashwin Kumar, Vijayabalaji, Aishwarya, Vamsi Krishna who, despite living in far-away lands, always made me feel close to their hearts.

I am truly indebted to my loving parents for everything I achieved. I would like to thank my mom and dad, Mangalam and Athmanathan, for being everything in my life, my sister Anusha and my brother-in-law Vinodh for their love, care and support during my studies and beyond.

I am grateful to my wife Anuradha for being my soulmate, and source of my happiness. Her presence has added significant meaning to my life. Her unconditional love and care helped and motivated me to get through all tough times of my PhD thesis. I enjoy sharing my research experience with her and I dedicate this dissertation to my beloved lovely wife, Anuradha.

Finally, a special note of thanks to the beautiful town of Adliswil, in the canton of Zürich for giving me many wonderful memories, which I can cherish for the rest of my life, and for making the last four years some of the happiest of my life.

Lausanne, 14 August 2015

Aravinthan Athmanathan

# **Abstract**

In the modern digital era of big data applications, there is an ever-increasing demand for higher memory capacity that is both reliable and cost effective. In the domain of non-volatile memory systems, Flash-based storage devices have dominated the consumer space for the past 15 years and have also entered the enterprise storage system in the past 2-3 years. However, with Flash memory devices facing serious scalability limits, there is an imminent need to explore the viability of other non-volatile memory technologies that can replace or complement Flash-based storage in the near future. Significant research efforts have been invested by various universities and research organization across the globe into realizing the so-called next-generation memories (NGMs). Phase-change memory is one such technology, which is viewed as the most promising candidate among the emerging technologies.

Phase-Change Memory (PCM) technology is not new as the principle of storing information in chalcogenide-based materials was first explored in the 1960s. However, with the predominance of charge-based memory technology (DRAM, Flash storage, etc) thriving thanks to the technological advancements of metal-oxide semiconductor field-effect transistor (MOSFET) based devices, it was not until the late 90s that renewed interest in the class of phase-change materials was ignited. This is the same genre of materials as have been widely used in laser-driven optical storage (rewritable CDs and DVDs) during the past 20 years or so. Although PCM chips have already been mass-produced by companies like Micron and Samsung, their capacity was limited as they were based on single-level cell (SLC) storage. The primary research focus of this thesis is on increasing the memory capacity by storing more than one bit of information per device, known as multilevel-cell (MLC). Achieving MLC capability is quite challenging, and we disclose some of our significant achievements in the realization of MLC PCM in the past few years.

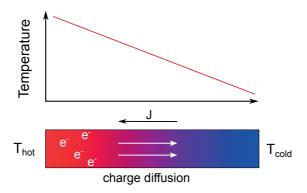

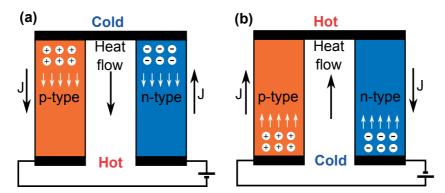

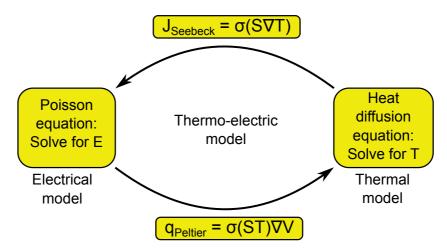

One of the main concerns for the sustainability of PCM technology is the power-hungry RE-SET process. Thermoelectric physics in nano-scale PCM devices is shown to play a significant role in the programming of these devices. Interestingly, these effects result in better thermal confinement and can even pave the way for more power-efficient devices. Therefore, it is high time that the thermoelectric physics within the devices is completely understood. Reliability is the other major concern for PCM technology, especially in the realization of multilevel-cell storage at highly dense PCM arrays. Several MLC-enabling technological advancements that suppress the drift phenomenon and array variability have been explored in the recent past.

Although a small number of demonstrations of MLC PCM feasibility have been performed, there is a need for the holistic application of enabling technologies in order to fully address the major reliability issues.

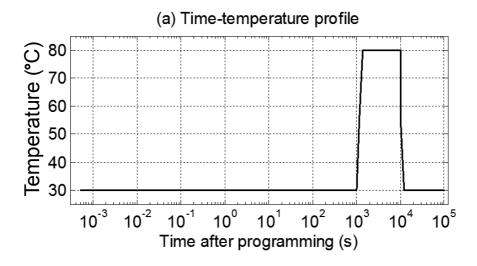

In this thesis, a comprehensive thermoelectric model is proposed for investigating the thermoelectrics physics in PCM device operation. With the increasing role of thermoelectrics at the smaller technology nodes, the proposed model provides valuable insights for a complete understanding of device operation. The model is validated by comparing the simulation results with experimental measurements. The model can also be used for fine-tuning the material properties, device design and geometry to improve the efficacy of these devices. In the second part of the thesis, the dominant reliability concerns in PCM technology are addressed, particularly focusing on MLC operation. We present a readout circuit for PCM specifically designed for drift resilience in MLC operation. Drift resilience is achieved through the use of specific non-resistance-based cell-state metrics which, in contrast to the traditional cell-state metric, i.e., the low-field electrical resistance, have built-in drift robustness. By employing novel MLC-enabling techniques, we succeeded in demonstrating for the first time, reliable 3-bits/cell memory density with a data retention of 1 week at temperatures ranging from 30°C to 80°C on devices that had been pre-cycled one million times.

**Keywords:** Phase-change memory, Multilevel-cell storage, Finite-element method based thermoelectric modeling of PCM, Drift resilience, Non-resistance cell-state-based readout metrics for MLC storage, Reliability and data retention analysis at elevated temperature, Reliable TLC data storage in PCM.

# Zusammenfassung

Im Zeitalter von Big-Data-Anwendungen besteht ein dauernd steigender Bedarf an zuverlässigen und preisgünstigen Datenspeichern mit hoher Kapazität. Im Bereich der nichtflüchtigen Speicher dominieren Flash-basierte Halbleiterspeicher seit 15 Jahren in der Unterhaltungselektronik und bei Konsumgütern. Seit 2-3 Jahren werden sie vermehrt auch im Serverbereich eingesetzt. Jedoch stossen Flash-basierte Speicher an Grenzen bezüglich ihrer Skalierbarkeit, deshalb sind Speichertechnologien, die auf anderen Halbleitern basieren und in naher Zukunft Flash ablösen oder ergänzen können, ein sehr aktives Forschungsgebiet. Weltweiten forschen Universitäten und industrielle Forschungslabors daran, diese so genannten Next-Generation Memories (NGM) zu kommerzieller Reife zu bringen. Eine dieser neuen Technologien — und aus heutiger Sicht der erfolgversprechendste Kandidat — ist die so genannte Phase-Change Memory (PCM, bzw. Phasenwechselsspeicher) Technologie.

Das Konzept der PCM-Speichertechnologie ist grundsätzlich nicht neu, wurden doch erste Ideen zur Datenspeicherung in Chalkogeniden bereits in den 1960er Jahren erprobt. Ladungsbasierte Speichertechnologien, wie DRAM, Flash und andere, waren jedoch aufgrund des technischen Fortschritts der MOSFET-Transistoren bis in die frühen 90er Jahre vorherrschend und sehr erfolgreich. In den späten 90er Jahren stiessen dann phasenwechselnde Materialien wieder auf vermehrtes Interesse. Dies ist die gleiche Art von Materialien, wie sie für die Speicherschicht der vor etwa 20 Jahren eingeführten optischen Speichermedien (wiederbeschreibbare CDs, DVD und BluRay-Disks), die mit Laser beschrieben werden, verwendet wurden. PCM-Chips werden bereits kommerziell hergestellt, zum Beispiel von Micron und Samsung, weisen aber typischerweise eine beschränkte Speicherkapazität auf, da sie auf einem gespeicherten Datenbit pro Speicherzelle, also so genannten Single-Level Cell (SLC) Speichern, beruhen. Der Hauptfokus der vorliegenden Doktorarbeit liegt in der Erhöhung der Speicherdichte durch die Speicherung mehrerer Datenbits pro Speicherzelle, also so genannte Multi-Level Cell (MLC) Speicher. Speicherung mittels MLC ist technisch sehr anspruchsvoll, aber wir haben in den vergangenen Jahren bereits Fortschritte erzielt und wichtige Ergebnisse hinsichtlich ihrer Realisierung veröffentlicht.

Einer der Gründe für die erwähnten Bedenken gegenüber der PCM-Technologie ist der RESET-Vorgang der Speicherzellen, welcher einen hohen Energiebedarf aufweist und somit

#### Zusammenfassung

die Lebensdauer der Speicherzellen beeinflusst. Thermoelektrische Vorgänge im Nanometer-Grössenbereich innerhalb der PCM-Zellen spielen nicht nur eine wichtige Rolle bei deren Programmierung, sondern sind auch ein wesentlicher Faktor bezüglich der Energieeffizienz. Daher ist wichtig, zu einem umfassenden Verständnis der thermoelektrisch-physikalischen Aspekte und Vorgänge in den PCM-Zellen zu gelangen. Ein weiterer kritischer Faktor in der PCM-Technologie ist die Zuverlässigkeit, speziell bei MLC-Anwendungen für hohe Speicherdichten. Verschiedene technologische Fortschritte wurden erzielt, welche die Empfindlichkeit in Bezug auf Drift und Zellvariationen verringerten. Ebenso wurde die prinzipielle Machbarkeit von MLC PCM bereits gezeigt, allerdings sind umfassende anwendungsnahe Messungen notwendig, um die kommerzielle Reife und Brauchbarkeit der MLC-PCM-Technologie zu demonstrieren.

In der vorliegenden Arbeit wird ein umfassendes, thermoelektrisches Simulationsmodell vorgestellt, das die physikalischen Vorgänge innerhalb der PCM-Zellen erklärt. Da thermoelektrische Vorgänge bei immer kleineren Technologiedimensionen eine immer wichtigere Rolle spielen, erlaubt es dieses Simulationsmodell, die Vorgänge besser zu verstehen und vorauszusagen. Das Modell und dessen Simulationsergebnisse wurden mit experimentellen Messungen verifiziert. Das Modell ermöglicht eine genau Abstimmung von Materialeigenschaften, Zellgeometrie und Zellstruktur, um die Funktionalität und die Effizienz der PCM-Zellen zu verbessern.

Wir stellen insbesondere auch einen Ausleseschaltkreis (readout circuitry) für PCM vor, der speziell hinsichtlich seiner Resilienz gegenüber Drift für MLC-Anwendungen entworfen wurde. Diese Resilienz wird durch die Verwendung einer Cell-State-Metrik erzielt, die nicht auf Basis des Widerstands beruht und somit eine inhärente Robustheit gegenüber Drift aufweist. Herkömmliche Cell-State-Metriken basieren auf dem elektrischen Widerstand bei schwachen Feldern. Im zweiten Teil der Doktorarbeit werden wichtige Aspekte, die die Zuverlässigkeit der PCM-Technologie beeinflussen, speziell auch für die MLC Anwendung, diskutiert. Durch die Anwendung neuartiger Techniken zur Ansteuerung der PCM-Zellen konnte erstmals die Zuverlässigkeit von PCM zur Speicherung von 3+ Bits/Zelle bei einer Datenerhaltung 1 Woche im erhöhten Temperaturbereich zwischen 30°C bis 80°C demonstriert werden — und zwar mit PCM Zellen, die bereits eine 1 Million Zyklen durchlaufen hatten.

**Keywords:** Phase-Change Memory, Multilevel-Cell storage, Finite-element method based thermoelectric modeling of PCM, Drift resilience, Non-resistance cell-state-based readout metrics for MLC storage, Reliability and data retention analysis at elevated temperature, Reliable TLC data storage in PCM.

# Contents

| A  | cknov  | wledge  | ments                                                                 | i    |

|----|--------|---------|-----------------------------------------------------------------------|------|

| A  | bstra  | ct (Eng | lish)                                                                 | iii  |

| Z  | usam   | menfa   | ssung (German)                                                        | v    |

| Li | ist of | figures |                                                                       | xiii |

| Li | ist of | tables  |                                                                       | xix  |

| 1  | Intr   | oducti  | on                                                                    | 1    |

| Ir | itrod  | uction  |                                                                       | 1    |

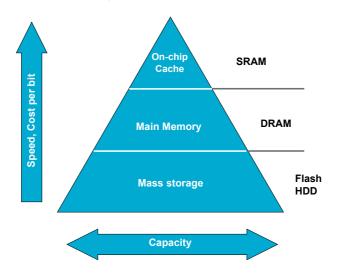

|    | 1.1    | Semio   | conductor Memory                                                      | 2    |

|    | 1.2    | Classi  | fication of Memory Hierarchy                                          | 2    |

|    |        | 1.2.1   | Volatile Memory                                                       | 3    |

|    |        |         | 1.2.1.1 Static-RAM                                                    | 3    |

|    |        |         | 1.2.1.2 Dynamic-RAM                                                   | 4    |

|    |        |         | 1.2.1.3 Applications                                                  | 4    |

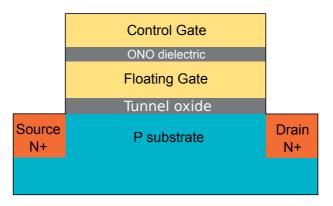

|    |        | 1.2.2   | Read-Only Memory                                                      | 4    |

|    |        |         | 1.2.2.1 Flash memory                                                  | 5    |

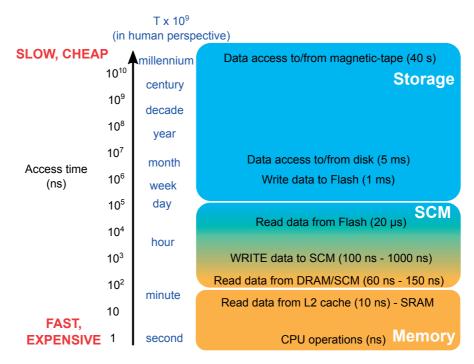

|    |        | 1.2.3   | Need for universal memory                                             | 6    |

|    |        |         | 1.2.3.1 Storage Class Memory (SCM)                                    | 7    |

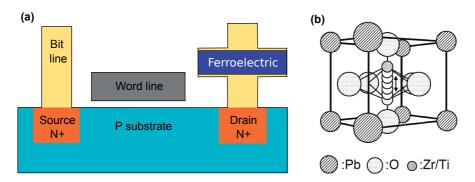

|    | 1.3    | Emerg   | ging non-volatile memory technologies                                 | 8    |

|    |        | 1.3.1   | Ferroelectric Random Access Memory (FRAM)                             | 8    |

|    |        | 1.3.2   | Magneto-resistive Random Access Memory (MRAM)                         | 9    |

|    |        |         | 1.3.2.1  Spin-Transfer Torque Random Access Memory (STT-RAM)  .  .  . | 9    |

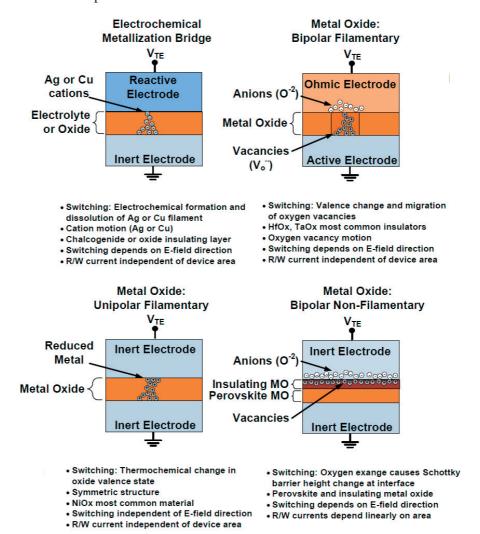

|    |        | 1.3.3   | Resistive Random Access Memory (RRAM)                                 | 10   |

|    |        | 1.3.4   | Phase-Change Random Access Memory (PCRAM)                             | 12   |

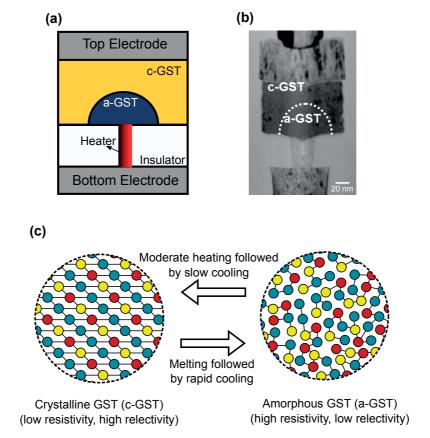

|    | 1.4    | Phase   | -Change Memory Technology                                             | 13   |

|    |        | 1.4.1   | Concept                                                               | 13   |

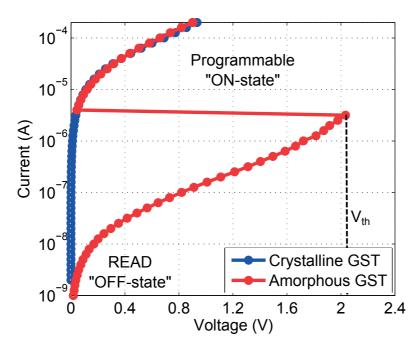

|    |        | 1.4.2   | Basic characteristics of PCM                                          | 14   |

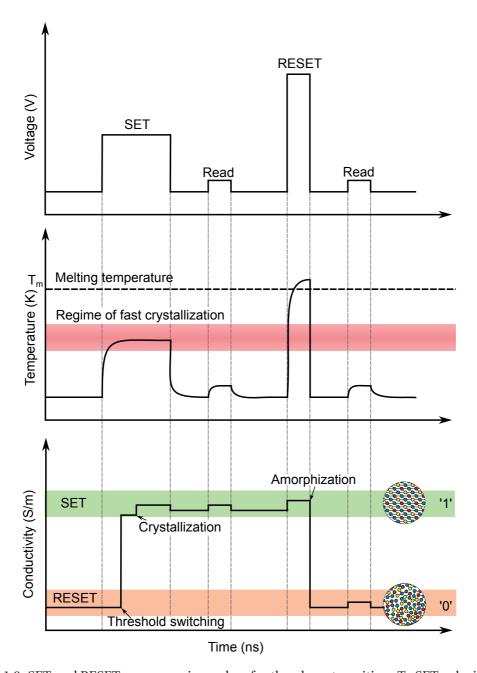

|    |        | 1.4.3   | SET and RESET Operation                                               | 15   |

|    |        |         | 1.4.3.1 Crystallization temperature                                   | 15   |

|    |        |         | 1.4.3.2 Threshold switching voltage                                   | 15   |

#### **Contents**

|   |          | 1.4.4 Properties of Phase-Change Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 17 |

|---|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |          | 1.4.5 Comparison of PCM properties with those of other memory technologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18 |

|   |          | 1.4.5.1 PCM vs. Flash storage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19 |

|   |          | 1.4.5.2 PCM vs. DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 21 |

|   |          | 1.4.5.3 PCM as Storage Class Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21 |

|   | 1.5      | Multi-level cell (MLC) storage in PCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 22 |

|   |          | 1.5.1 Factors limiting reliable MLC operation in PCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22 |

|   | 1.6      | Research focus area: State of the art                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 22 |

|   |          | 1.6.1 Modeling of PCM devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22 |

|   |          | 1.6.2 Reliability of MLC PCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23 |

|   | 1.7      | Thesis Goal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 24 |

|   | 1.8      | Summary of contributions in this thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25 |

|   | 1.9      | Thesis Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 26 |

| _ | <b>T</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 2 |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29 |

|   | 2.1      | o de la companya de l | 31 |

|   |          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31 |

|   |          | · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31 |

|   |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34 |

|   | 2.2      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35 |

|   |          | 0 0 1 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35 |

|   | 2.3      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36 |

|   |          | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 36 |

|   |          | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 36 |

|   |          | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 37 |

|   |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39 |

|   |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 43 |

|   | 2.4      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45 |

|   |          | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 45 |