# **Graphene for Nanoelectronic Applications**

## THÈSE N° 6886 (2015)

PRÉSENTÉE LE 14 DÉCEMBRE 2015

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR LABORATOIRE DES DISPOSITIFS NANOÉLECTRONIQUES PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

#### PAR

# Pankaj SHARMA

acceptée sur proposition du jury:

Prof. G. De Micheli, président du jury Prof. M. A. Ionescu, directeur de thèse Prof. T. Palacios, rapporteur Prof. G. Fiori, rapporteur Dr A. Magrez, rapporteur

You must be the change you wish to see in the world.

— Mahatma Gandhi

To my parents...

# Acknowledgements

First and foremost, I would like to sincerely thank my supervisor Prof. Adrian Ionescu for giving me the opportunity to be part of his group. Your guidance, not only in terms of giving ideas and solving research problems, but also in terms of giving freedom to do research in my own way has proved to be useful and invaluable. I greatly appreciate his visionary foresight, his inspiring personality and his vast knowledge in a wide range of topics. It's truly been a privilege to work with him and I am deeply grateful for his support, confidence, open-mindedness and for having introduced me to the world of electron device research. Next, I would like to thank late Prof. Julien Perruisseau-Carrier who was my co-advisor for first 3 years of my PhD; he tragically died in mid-2014. I will be ever grateful for his support, encouragement and am sorry that he has not lived to see me graduate. Julien was an extremely supportive supervisor and all in all a wonderful person.

I would like to acknowledge the members of the jury for having accepted to review my PhD thesis: Prof. T. Palacios from Massachusetts Institute of Technology, USA, Prof. G. Fiori from University of Pisa, Italy, Dr. A. Magrez from EPFL and Prof. G. De Micheli, president of the jury, from EPFL.

I would like to express my sincere thanks to Dr. Arnaud Magrez and Laurent Bernard from crystal growth facility, EPFL. Thanks for the fruitful collaboration and for providing graphene samples, Raman data and useful suggestions. Special thanks to Laurent for teaching me how to transfer graphene and for giving invaluable tips in the graphene fabrication process. For the help in device measurements, I would like to thank: Dr. Antonios Bazigos and Dr. Wladek Grabinski. Special thanks to Antonios for sharing with me his extensive knowledge about semiconductor device measurements, and for useful suggestions while preparing different manuscript together. Special thanks also to Juan Sebastián Gómez-Díaz for his immense help in the beginning of my PhD years in terms of his advices and guidance in developing my skills in academic writing and in microwave engineering.

Furthermore, I wish to thank Isabelle, Karin, Marie and Lucie for taking care of the administrative procedures. I am also thankful to the funding sources: Grafol; and to the staffs of EPFL Center of MicroNanoTechnology (CMi) for their support in the device fabrication. I thank all my colleagues in Nanolab for their cheerful characters, kindness and willingness to help.

Finally, special thanks go to my family and friends, in Switzerland and in India, and especially to my parents, for always believing in me, and for their unconditional love, support and encouragement. Last but not least, I would like to thank my wife Preeti, for always being there for me, and for her love and encouragement that was always available when I needed it the

most.

Lausanne, 09 Septembre 2015

P.S.

# **Abstract**

During the past decade, graphene — a monolayer of carbon atoms — has attracted enormous interest for its use in nanoelectronic device applications. The absence of bandgap, however, has stalled its use both in logic (inability to turn off) and radio frequency (poor power gain) applications. Graphene nanoelectronic devices based on alternative and complementary approaches, which yet exploit its fundamental properties rather than trying to change them, are needed for realistic applications. The work in this thesis proposes two such alternative approaches for graphene's application.

The first approach examines the use of graphene as a membrane of radio frequency (RF) nanoelectromechanical systems (NEMS) capacitive switches. Owing to its extreme thinness and exceptional mechanical properties, the use of graphene in RF NEMS switches could enable lower actuation voltages and faster switching. To evaluate its electromagnetic performance, a framework for the full-wave simulation of graphene-based RF NEMS switch is developed for the first time. A rigorous modeling approach for graphene NEMS switch taking into account both its frequency-dependent conductivity, and the variation of conductivity in the up- and down-state is presented. Our results show that RF NEMS switches based on graphene with lower sheet resistivity values can deliver superior isolation and reduced losses at micro and millimeter wave frequencies, and their isolation can also be tuned with bias voltage. An attempt is also made to characterize the fabricated switches.

The second approach deals with the negative differential resistance (NDR) phenomenon in planar graphene solid-state devices. The key advantage of planar graphene-based NDR devices is their ability to exhibit NDR at higher current levels, thanks to its high mobility and saturation velocity. The observation of NDR is reported in the output characteristics of graphene field effect transistors for various channel lengths and dielectric thicknesses at room temperature. The transistors are fabricated using chemical vapor deposition graphene with a top gate oxide down to 2.5 nm of equivalent oxide thickness. To understand the NDR phenomenon in graphene transistors, we perform extensive theoretical studies based on drift-diffusion model. This understanding allows us to design a novel graphene circuit which shows enhanced NDR characteristics and is more relevant for applications. Finally, the potential of this graphene NDR circuit is evaluated for RF reflection amplifiers application.

Key words: Graphene, Nanoelectromechanical systems (NEMS), RF NEMS (MEMS) switch, microwave, millimeter waves, negative differential resistance (NDR), field effect transistor,

negative differential conductance (NDC), GFET.

# Résumé

Au cours de la dernière décennie, le graphène — une monocouche d'atomes de carbone — a attiré un grand intérêt pour son utilisation dans des applications de dispositifs nanoélectroniques. Cependant, l'absence de bande interdite a entravé son utilisation à la fois dans des applications de logique (incapacité à s'éteindre) et de radiofréquence (gain de puissance faible). Des dispositifs nanoélectroniques de graphène basés sur des approches alternatives et complémentaires, qui exploitent ses propriétés fondamentales plutôt que d'essayer de les changer, sont nécessaires pour des applications réalistes. Le travail de cette thèse propose deux de ces approches alternatives pour des applications du graphène.

La première approche examine l'utilisation du graphène comme une membrane de commutateurs capacitifs de systèmes nanoélectromécaniques (NEMS) radiofréquences (RF). En raison de sa minceur extrême et de ses propriétés mécaniques exceptionnelles, l'utilisation du graphène dans les commutateurs RF NEMS pourrait permettre des tensions d'actionnement inférieures et une commutation plus rapide. Pour évaluer son rendement électromagnétique, un cadre pour la « simulation d'onde complète » de l'interrupteur RF NEMS à base sur le graphène a été développé pour la première fois. Une modélisation rigoureuse des commutateurs NEMS de graphène est effectuée en tenant compte à la fois de sa conductivité dépendante de la fréquence, et de la variation de conductivité dans les états haut et bas. Nos résultats montrent que le graphène avec une résistivité de surface inférieure peut fournir une isolation supérieure et des pertes réduites dans la plage de fréquences des micro-ondes et des ondes millimétriques, aussi l'isolation peut également être réglée avec la tension de polarisation. Une tentative de caractérisation des interrupteurs fabriqués est également menée.

La seconde approche traite du phénomène de résistance différentielle négative (RDN) dans les dispositifs semi-conducteurs planaires en graphène. Le principal avantage des dispositifs planaires RDN à base de graphène est leur capacité à présenter une RDN à des niveaux de courant plus élevés, grâce à la grande mobilité et à la vitesse de saturation du matériau. L'observation de la RDN est rapportée dans les caractéristiques de sortie des transistors à effet de champ en graphène pour différentes longueurs de canal et épaisseurs de diélectrique à température ambiante. Les transistors sont fabriqués en utilisant un dépôt chimique en phase vapeur de graphène avec un oxyde de la grille supérieure allant jusqu'à 2.5 nm d'épaisseur d'oxyde équivalente. Pour comprendre le phénomène RDN dans les transistors de graphène, nous effectuons des études théoriques approfondies basées sur le modèle de dérive-diffusion. Cette compréhension nous permet de concevoir de nouveaux circuits de graphène qui montrent des caractéristiques supérieures de RDN et sont plus pertinents pour des applications. Enfin,

la RDN de ce circuit de graphène est évaluée pour l'application des amplificateurs à réflexion.

Mots clefs : graphène, nanoélectromécaniques systèmes (NEMS), RF NEMS (MEMS) commutateur, micro-ondes, des ondes millimétriques, résistance différentielle négative, Transistor à effet de champ, conductance différentielle négative, GFET.

# **Contents**

| A  | cknov | vledgements                                                    | j    |

|----|-------|----------------------------------------------------------------|------|

| Al | bstra | ct (English/Français)                                          | ii   |

| C  | onter | nts                                                            | vi   |

| Li | st of | figures                                                        | X    |

| Li | st of | tables                                                         | xiii |

| 1  | Intr  | roduction                                                      | 1    |

|    | 1.1   | The Need of Alternative Device Principles and New Materials    | ]    |

|    | 1.2   | Overview of Graphene Research                                  | 2    |

|    | 1.3   | Graphene Properties Relevant for Nanoelectromechanical Devices | 4    |

|    |       | 1.3.1 Mechanical Properties                                    | 4    |

|    |       | 1.3.2 Thermal Properties                                       | 4    |

|    |       | 1.3.3 Other Properties                                         | 5    |

|    | 1.4   | Graphene Properties Relevant for Solid-State Devices           | 5    |

|    |       | 1.4.1 Graphene Bandstructure                                   | 5    |

|    |       | 1.4.2 Density of States                                        | 6    |

|    |       | 1.4.3 Carrier Density                                          | 6    |

|    | 1.5   | Thesis Outline                                                 | 8    |

| 2  | Gra   | phene Nanoelectromechanical Microwave Shunt Switch             | 11   |

|    | 2.1   | Introduction                                                   | 11   |

|    | 2.2   | Graphene as a membrane of the RF NEMS shunt switch             | 13   |

|    | 2.3   | Design of Graphene based capacitive shunt switch               | 16   |

|    |       | 2.3.1 Working Principle                                        | 16   |

|    |       | 2.3.2 Equivalent Circuit Model                                 | 17   |

|    | 2.4   | Modeling                                                       | 18   |

|    |       | 2.4.1 Frequency Dependent Conductivity                         | 18   |

|    |       | 2.4.2 Conductivities in Up- and Down-state positions           | 18   |

|    | 2.5   | Simulation, Results and Discussion                             | 20   |

|    | 2.6   | Device Fabrication, Characterization and Discussion            | 26   |

|    |       | 2.6.1 Device Fabrication                                       | 26   |

#### **Contents**

|   |      | 2.6.2 Device Characterization and Discussion             | 1                                  | 26 |

|---|------|----------------------------------------------------------|------------------------------------|----|

|   | 2.7  | 7 Summary                                                |                                    | 30 |

| 3 | Gra  | raphene Solid-State Device Physics and Technol           | ogy                                | 33 |

|   | 3.1  | Graphene Device Physics                                  |                                    | 33 |

|   |      | 3.1.1 Drift-Diffusion Model                              |                                    | 33 |

|   |      | 3.1.2 Small-Signal and RF Model                          |                                    | 36 |

|   |      | 3.1.3 Model Validation and Circuit Simulation            | n Approach                         | 38 |

|   | 3.2  | 2 Graphene Synthesis                                     |                                    | 40 |

|   |      | 3.2.1 Mechanical Exfoliation                             |                                    | 40 |

|   |      | 3.2.2 Epitaxial Growth on SiC                            |                                    | 40 |

|   |      | 3.2.3 Chemical vapor deposition                          |                                    | 41 |

|   | 3.3  | B Device Fabrication                                     |                                    | 43 |

|   |      | 3.3.1 Top-gate GFET                                      |                                    | 43 |

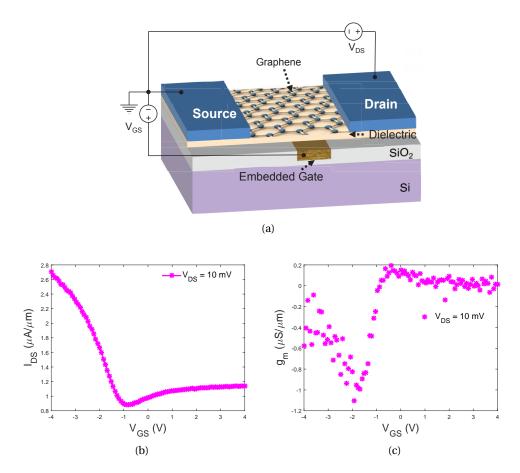

|   |      | 3.3.2 Embedded-gate GFET                                 |                                    | 46 |

|   | 3.4  | 4 Low-Field Measurements                                 |                                    | 49 |

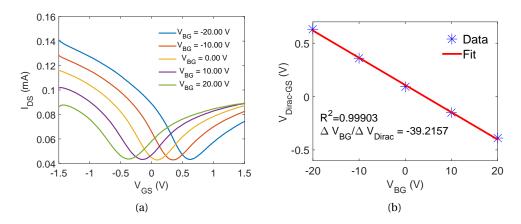

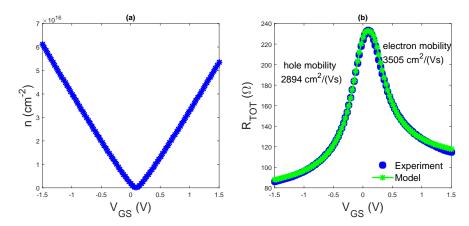

|   |      | 3.4.1 Graphene on Si/SiO <sub>2</sub> without top-gating | g                                  | 49 |

|   |      | 3.4.2 Top-gate GFET                                      |                                    | 51 |

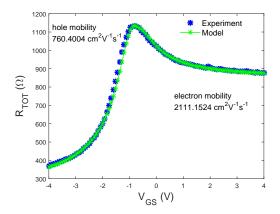

|   |      | 3.4.3 Embedded-gate GFET                                 |                                    | 52 |

|   | 3.5  | 5 Summary                                                |                                    | 53 |

| 4 | Neg  | egative Differential Resistance in Graphene Solic        | l-State Devices                    | 57 |

|   | 4.1  | I Introduction                                           |                                    | 57 |

|   |      | 4.1.1 Negative Differential Resistance Phenor            | menon                              | 57 |

|   |      | 4.1.2 Figures of Merit                                   |                                    | 59 |

|   |      | 4.1.3 Negative Differential Resistance Based of          | on 2-D Materials                   | 60 |

|   | 4.2  | Negative Differential Resistance in Graphene T           | ransistors                         | 61 |

|   |      | 4.2.1 Room-temperature high-field electrical             | measurements                       | 61 |

|   |      | 4.2.2 Mechanism                                          |                                    | 66 |

|   |      | 4.2.3 Top-Gate Oxide Thickness Dependence                |                                    | 68 |

|   | 4.3  | Negative Differential Resistance in 3-Transisto          | r Graphene Circuit                 | 70 |

|   |      | 4.3.1 Operation Principle                                |                                    | 70 |

|   |      | 4.3.2 Measurement Results                                |                                    | 73 |

|   |      | 4.3.3 Discussion                                         |                                    | 74 |

|   | 4.4  | 4 Summary                                                |                                    | 75 |

| 5 | Refl | eflection Amplifiers based on Graphene Negative          | Differential Resistance Solid-Stat | te |

|   | Dev  | evices                                                   |                                    | 77 |

|   | 5.1  | I Introduction: Reflection Amplifiers                    |                                    | 77 |

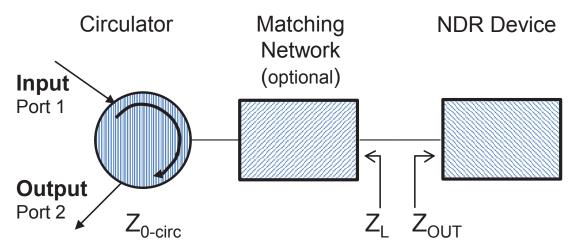

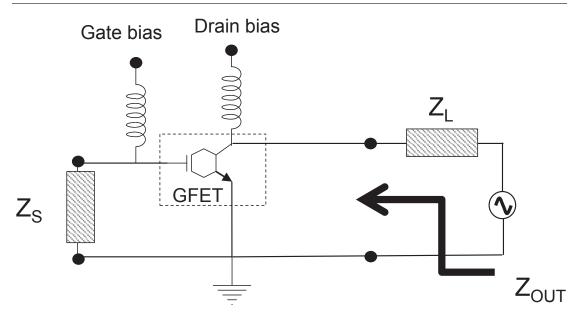

|   | 5.2  | 2 Theory of Operation                                    |                                    | 78 |

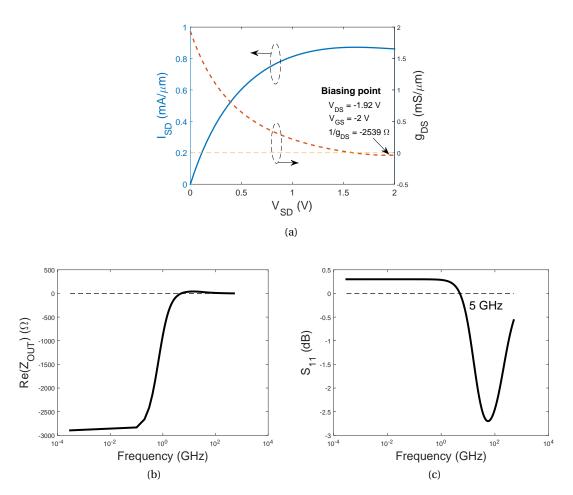

|   | 5.3  | 3 Simulation of 1-GFET NDR Reflection amplifie           | r                                  | 78 |

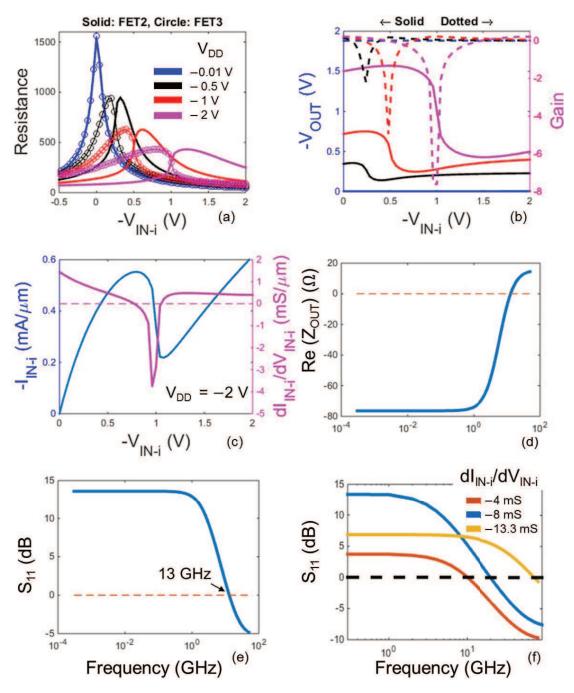

|   | 5.4  | 4 Simulation of 3-GFET NDR Reflection amplifie           | r                                  | 81 |

|   | 5.5  | 5 Measurements of 3-GFET NDR Reflection amp              | lifier                             | 83 |

|    |       | Conte                               | ents |

|----|-------|-------------------------------------|------|

|    | 5.6   | Summary                             | 87   |

| 6  | Con   | nclusion and Perspective            | 89   |

|    | 6.1   | Conclusion                          | 89   |

|    | 6.2   | Perspective                         | 91   |

| A  | Mu    | lti-Layer Graphene Characterization | 93   |

| Bi | bliog | graphy                              | 119  |

| Li | st of | Publications                        | 121  |

| Cı | urric | ulum Vitae                          | 123  |

# **List of Figures**

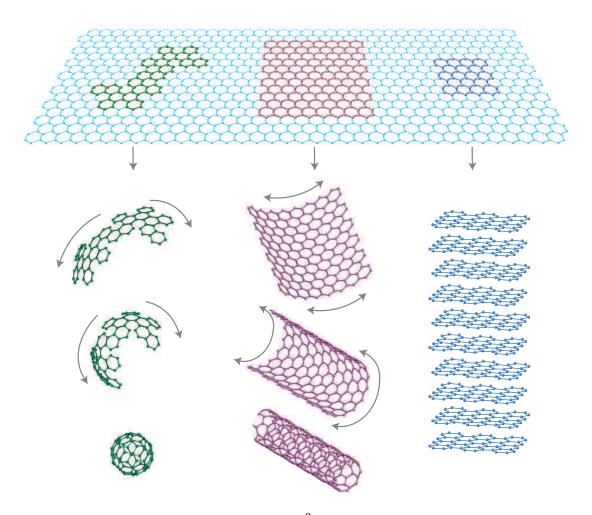

| 1.1  | Graphene — The Mother of 2-D Materials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3  |  |  |  |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

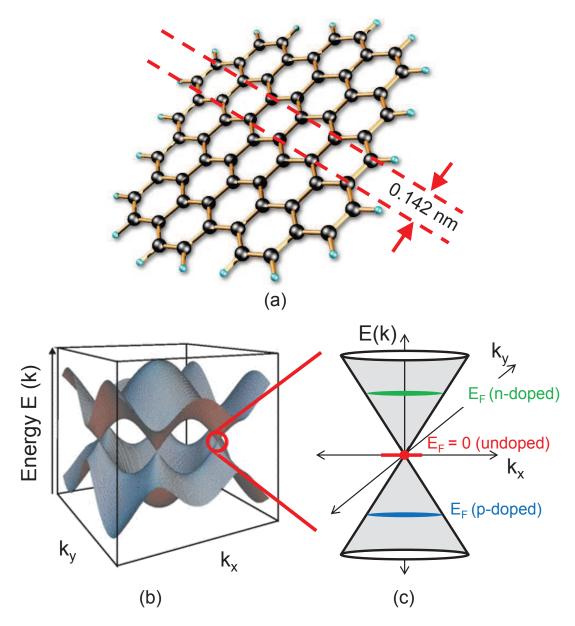

| 1.2  | Graphene's 2-D structure and its unique energy band structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7  |  |  |  |  |

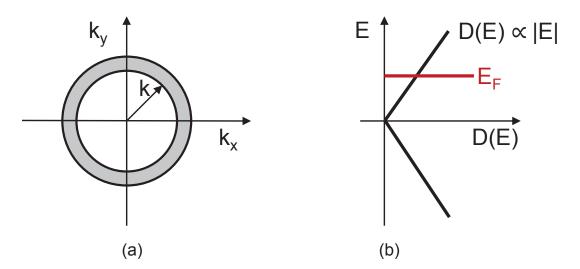

| 1.3  | Graphene density of states                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |  |  |  |  |

| 0.1  | DEMENC de contracto de la contracto de contracto de la contrac | 10 |  |  |  |  |

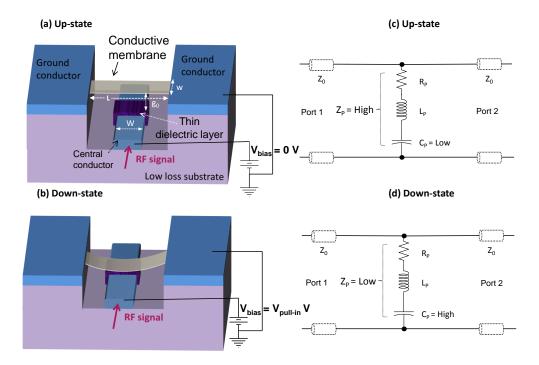

| 2.1  | RF MEMS shunt switch: operation princple                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13 |  |  |  |  |

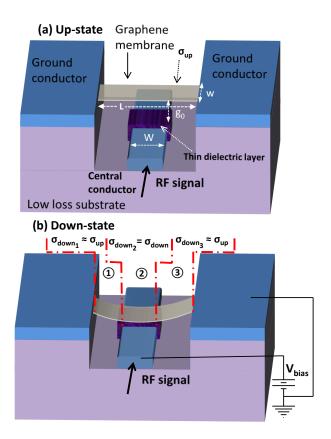

| 2.2  | Graphene RF NEMS shunt switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16 |  |  |  |  |

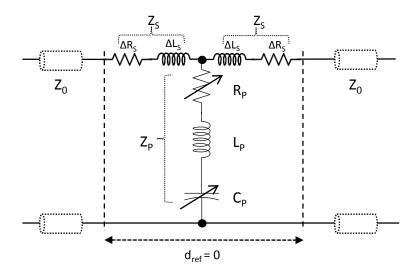

| 2.3  | Equivalent circuit model of graphene RF NEMS shunt switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17 |  |  |  |  |

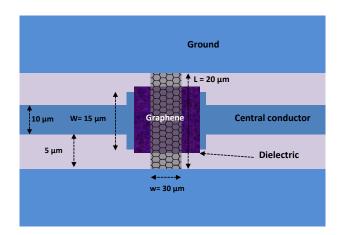

| 2.4  | Top view with specifications of graphene NEMS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21 |  |  |  |  |

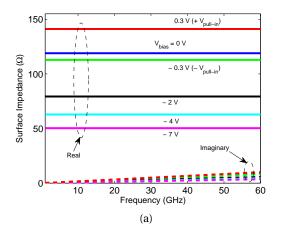

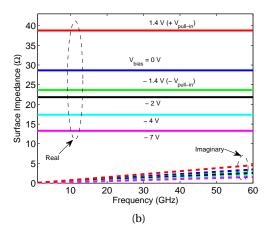

| 2.5  | Frequency-dependent surface impedance of graphene.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22 |  |  |  |  |

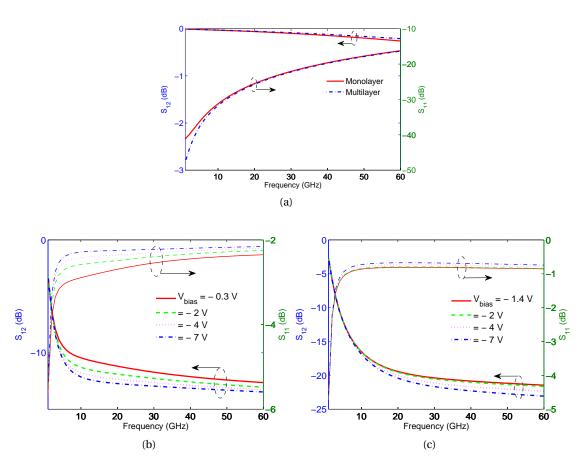

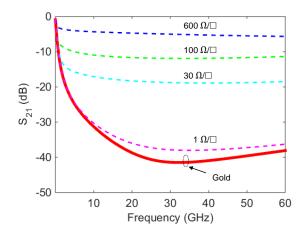

| 2.6  | Simulated S-parameters of graphene RF-NEMS switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 23 |  |  |  |  |

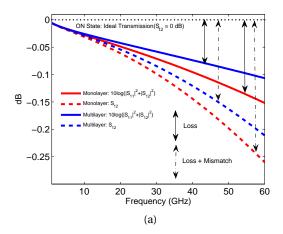

| 2.7  | Contribution of losses in graphene RF NEMS switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 24 |  |  |  |  |

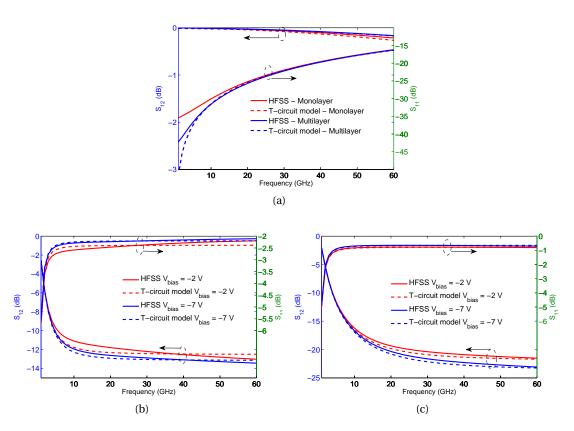

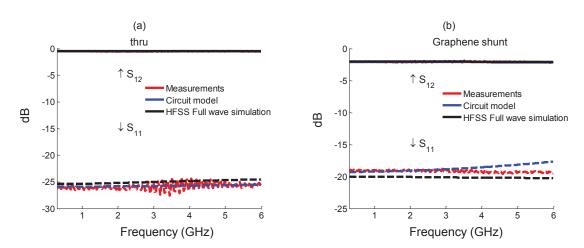

| 2.8  | Validation of full-wave simulation with circuit-model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25 |  |  |  |  |

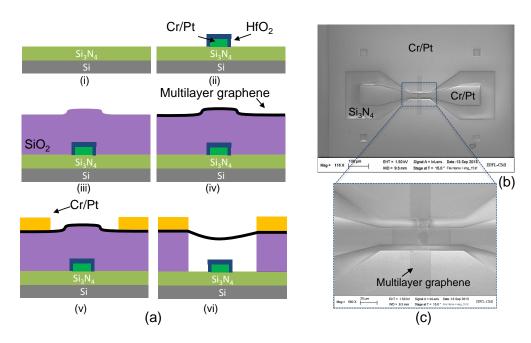

| 2.9  | Fabrication process of the graphene RF NEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27 |  |  |  |  |

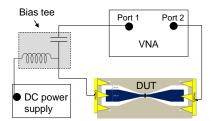

|      | Measurement setup of graphene RF NEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27 |  |  |  |  |

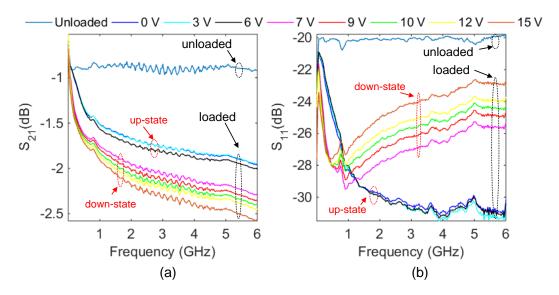

| 2.11 | Measured S-parameters of graphene RF NEMS switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 28 |  |  |  |  |

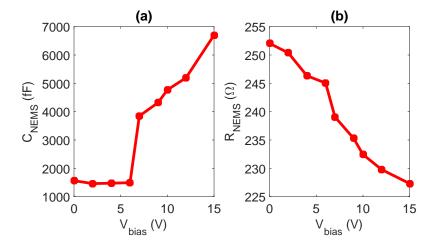

| 2.12 | Extracted circuit-model parameters from measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29 |  |  |  |  |

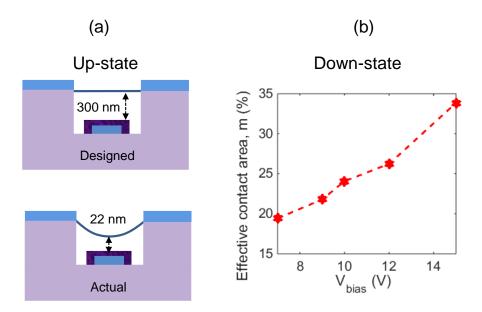

| 2.13 | Interpretation of measurements: Up-state position                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 30 |  |  |  |  |

| 2.14 | Comparison of RF perforamance of graphene with metal membrane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 31 |  |  |  |  |

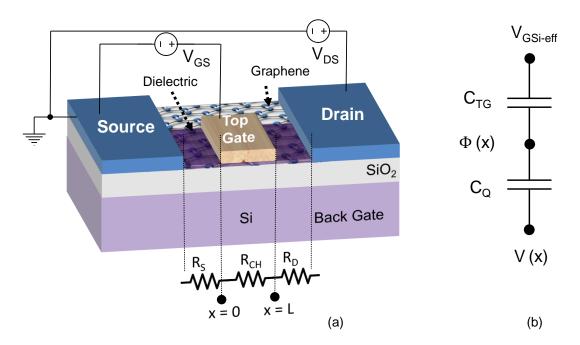

| 3.1  | Top-gated GFET schematic and capacitive divider circuit model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 34 |  |  |  |  |

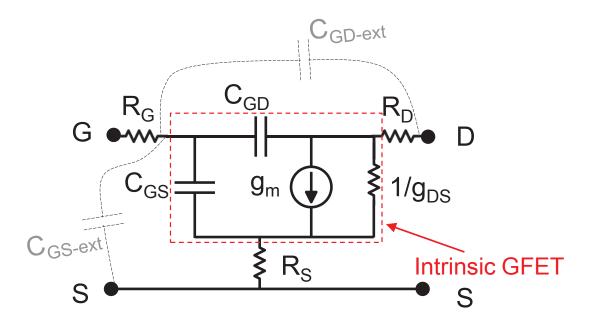

| 3.2  | Small-signal equivalent circuit of GFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36 |  |  |  |  |

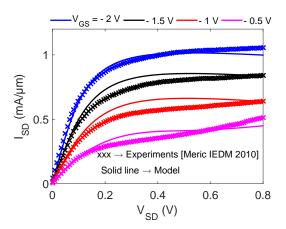

| 3.3  | Modeled GFET output characteristics validation with experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38 |  |  |  |  |

| 3.4  | Simulated small-signal parameters: $g_m$ and $g_{DS}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38 |  |  |  |  |

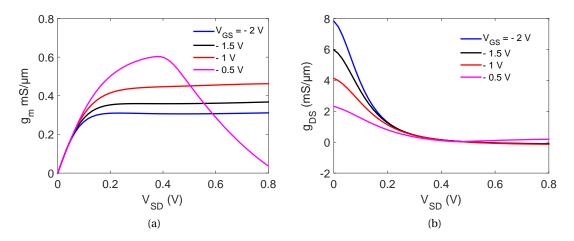

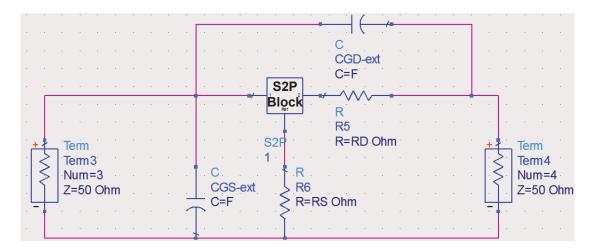

| 3.5  | Simulated small-signal parameters: $C_{GS}$ and $C_{GD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 39 |  |  |  |  |

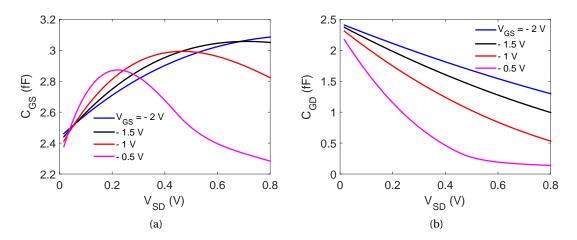

| 3.6  | Model implementation in Agilent ADS for circuit level simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39 |  |  |  |  |

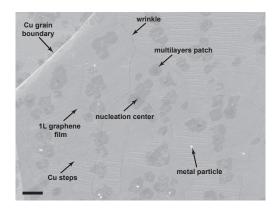

| 3.7  | SEM image of as-grown graphene on Cu foils                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 41 |  |  |  |  |

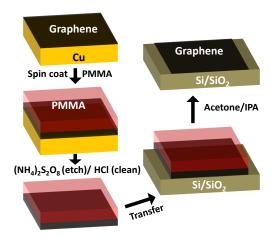

| 3.8  | Graphene transfer process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 43 |  |  |  |  |

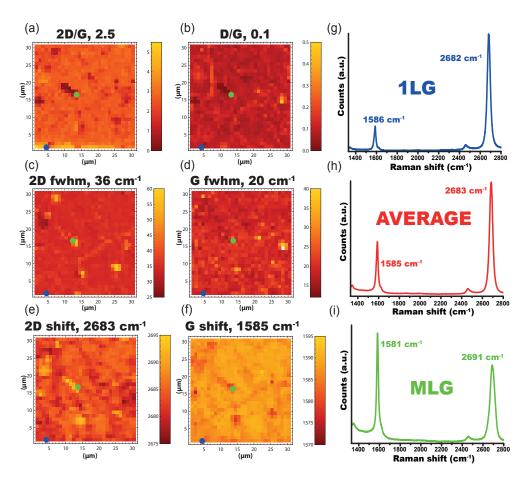

| 3.9  | Micro-Raman mapping of graphene.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 43 |  |  |  |  |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |  |

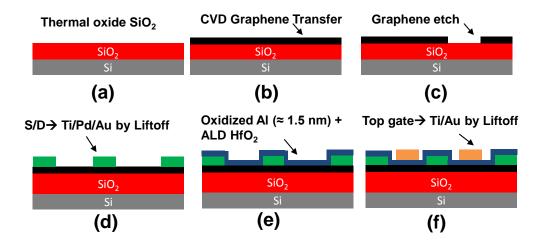

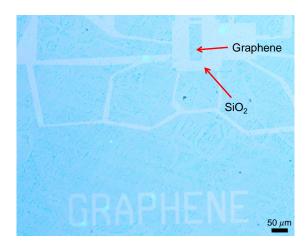

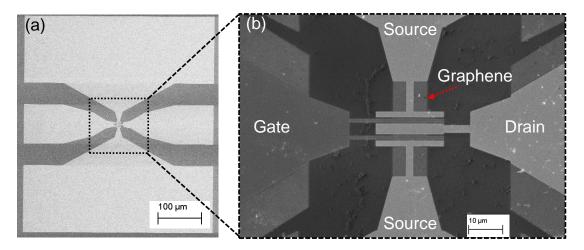

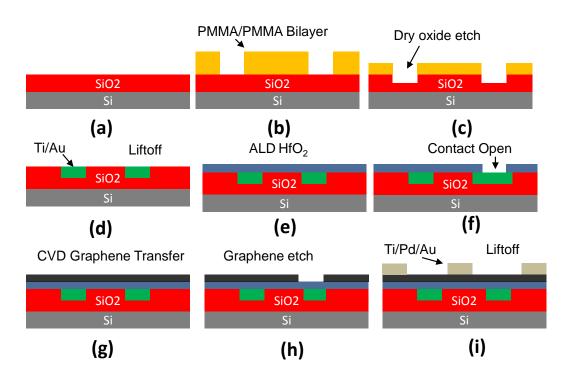

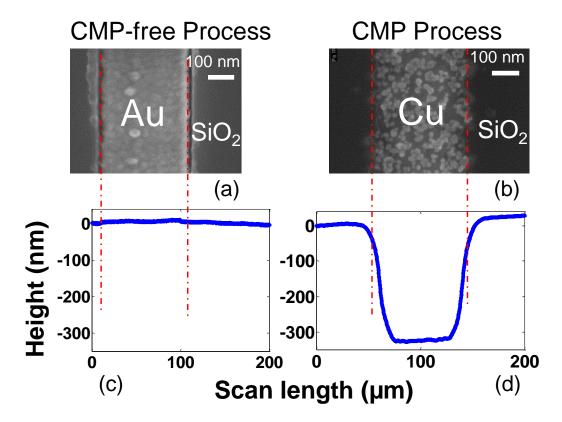

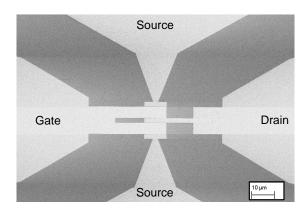

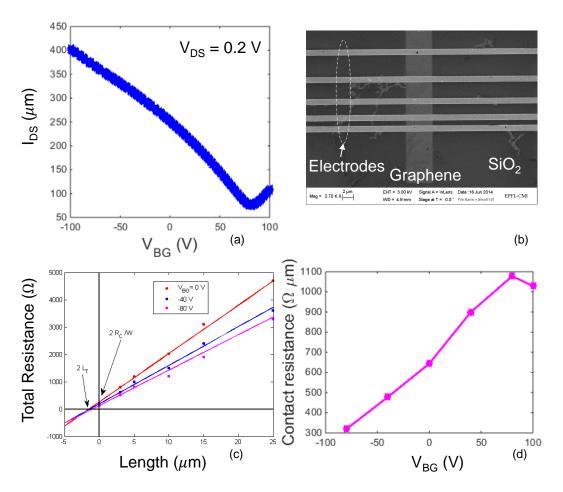

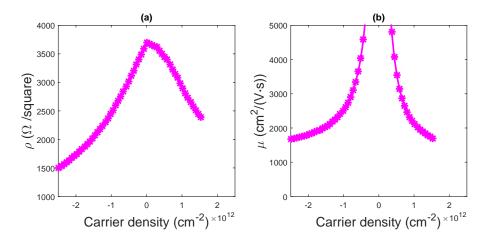

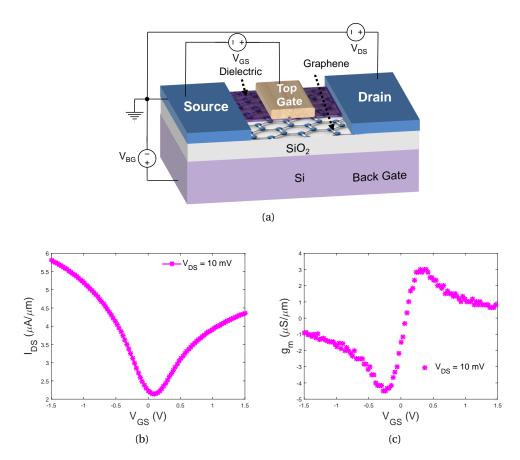

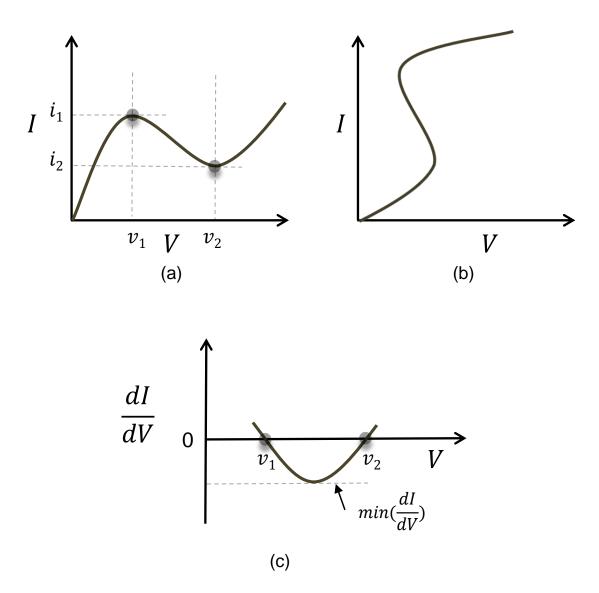

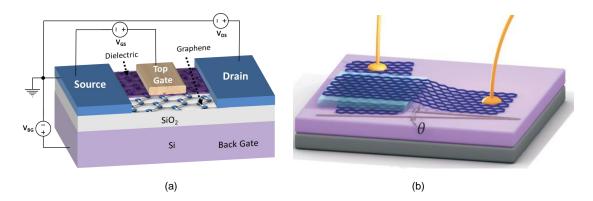

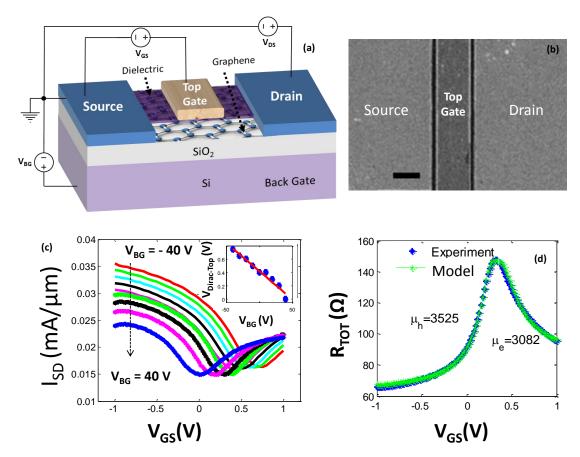

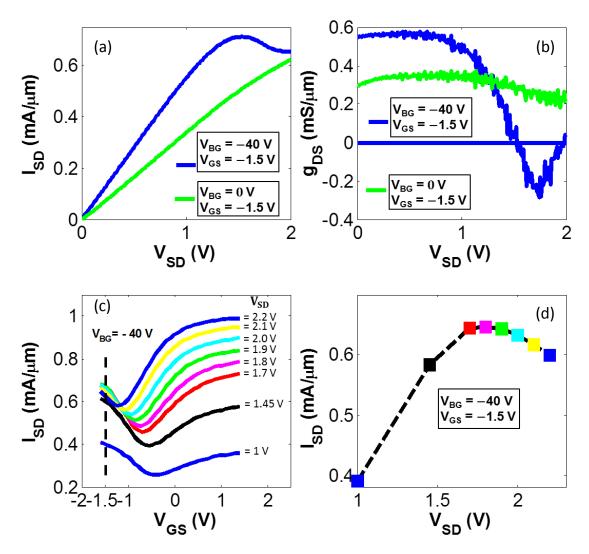

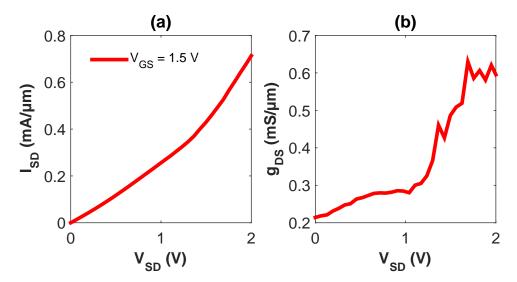

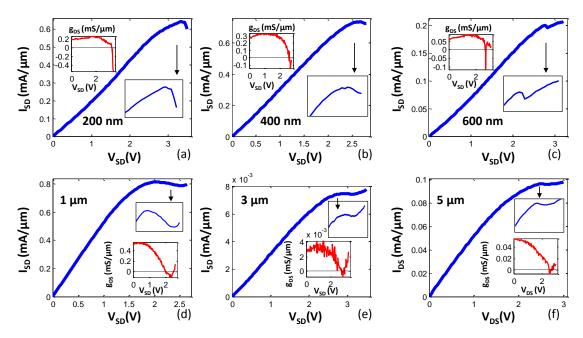

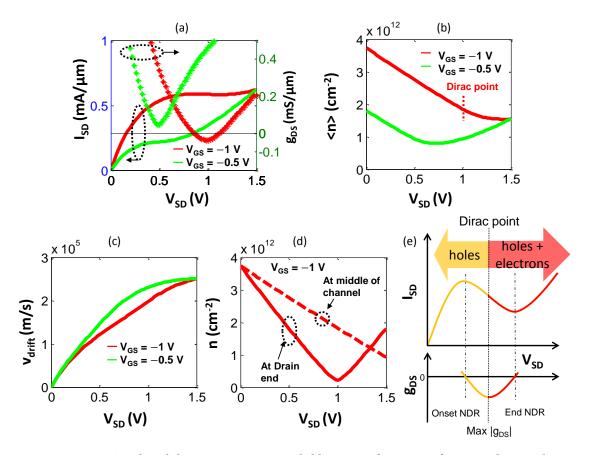

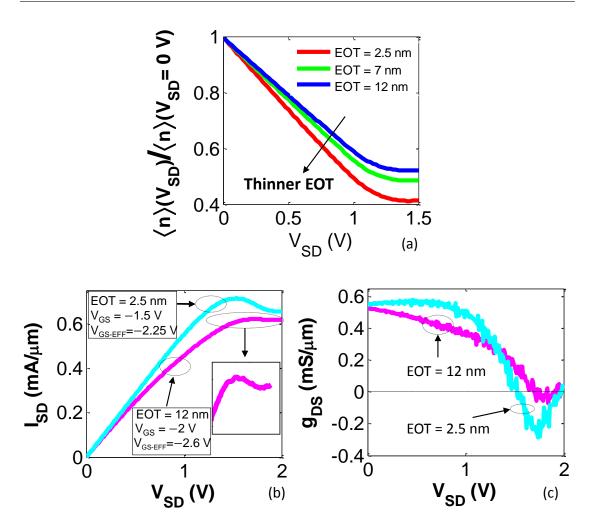

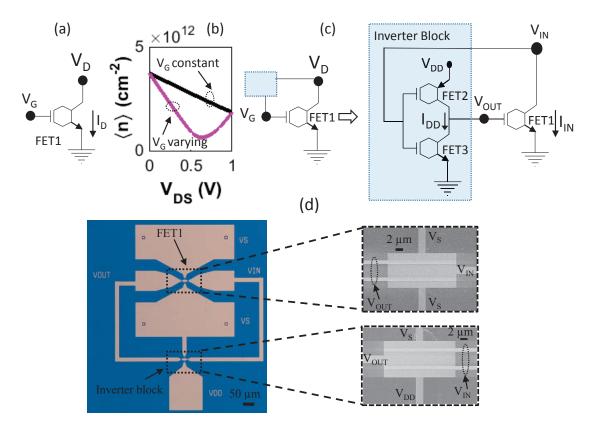

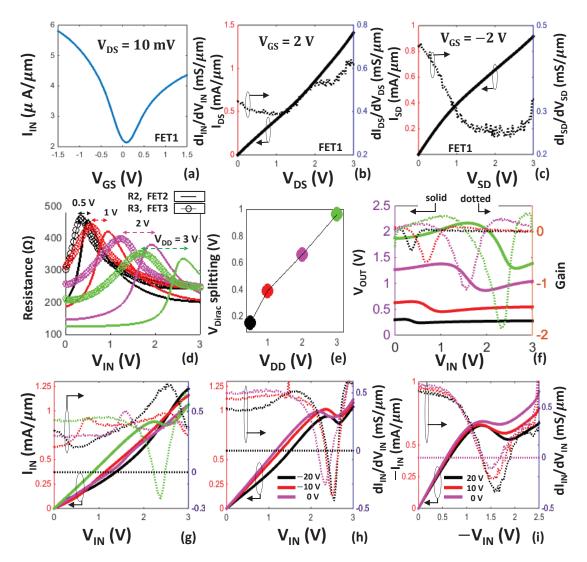

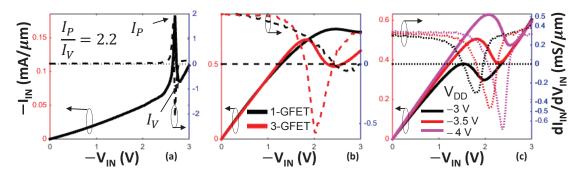

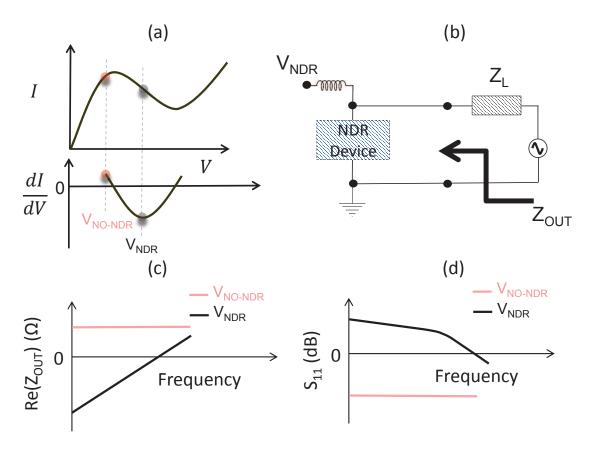

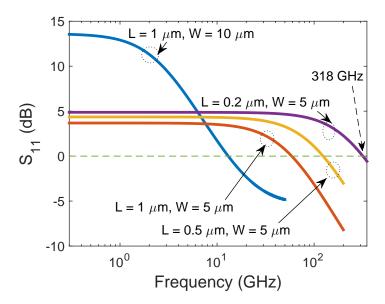

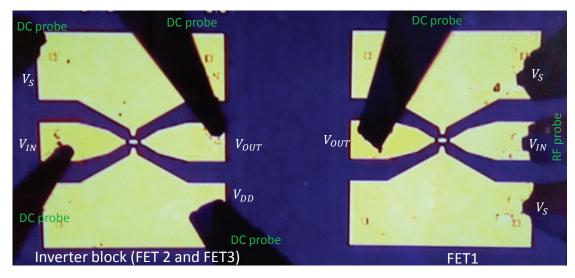

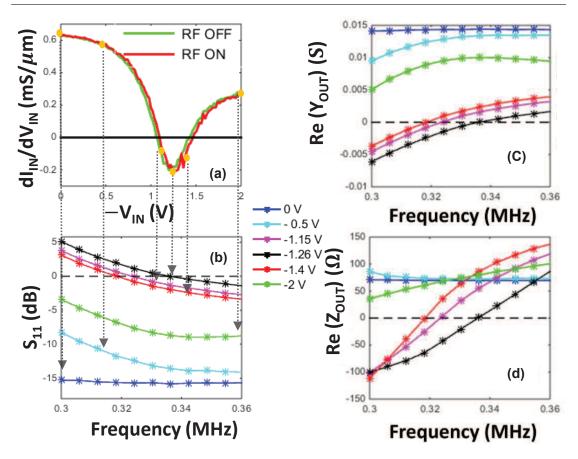

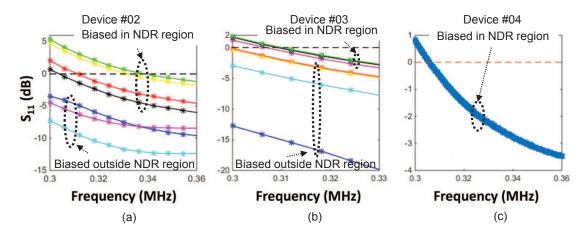

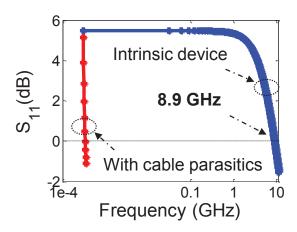

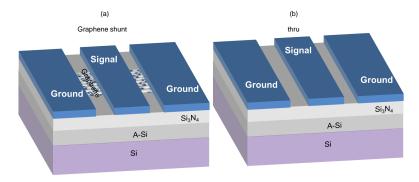

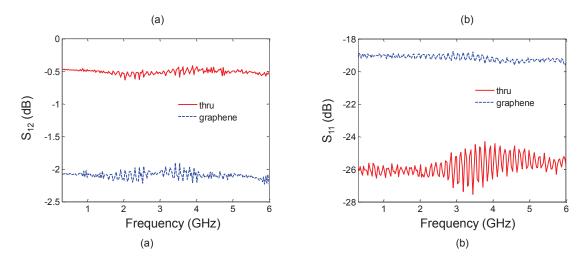

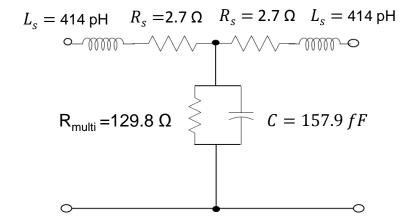

|      | Process flow of top-gated GFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45 |  |  |  |  |