### A Miniaturized Insect Eye Inspired Multi-camera Real-time Panoramic Imaging System

### THÈSE Nº 6844 (2015)

PRÉSENTÉE LE 20 NOVEMBRE 2015

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR

LABORATOIRE DE SYSTÈMES MICROÉLECTRONIQUES

PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

Ömer ÇOĞAL

acceptée sur proposition du jury:

Prof. C. Dehollain, présidente du jury Prof. Y. Leblebici, directeur de thèse Prof. J.-I. Guo, rapporteur Prof. R. Dekker, rapporteur Prof. J.-Ph. Thiran, rapporteur

"..don't forget that on top of everything, you are engineers and electronic engineers, think about the chip design, analog or digital design just as your different hobbies.."

Prof. Duran Leblebici

(from a talk during the technical trip to YITAL, 2005)

best things come in small packages

To my parents, sister and wife... Anneme babama, ablama ve eşime...

# Acknowledgements

I would never have been able to finish my dissertation without the guidance of my advisor, help from friends, and support from my family and wife.

First of all, I would like to thank my thesis director Prof. Yusuf Leblebici not only for the opportunity he gave to start this PhD work but also being supportive and giving advises not only by words but also by life examples. Simply, a great leader.

I would like to thank my thesis committee members Prof. Catherine Dehollain, Prof. Ronald Dekker, Prof. Jiun In Guo, Prof. Jean-Philippe Thiran for evaluating my work and their constructive comments and discussions.

I would like to thank to the Master and Bachelor degree students to whom I have collaborated in different parts of my PhD work; Mattia Cacciotti for his collaboration on ASIC design of the miniature panoramic imaging system and Jonathan Narinx for his help during the ASIC design, Nicola Gerber for his contributions on the research for analysis of different Bayer demosaicing and white balancing algorithms. I would like to thank to Abdulkadir Uzun, for his work on the virtual stereo construction study. I would like to thank to our Professors at LSM, Alain Vachoux and Alexandre Schmid. Being their lab assistant in various classes was a great experience and pleasure for me. I also would like to thank tou Sylvain Hauser for help in the mechanical and PCB assemblies and Peter Brühlmeier for PCB designs. Thanks to our two lab secretaries at LSM, Patricia Volanthen and Melinda Mischler, for supporting in all the paper works and solving many issues in daily life during my PhD work.

I would like to thank to many collaborators from outside of the EPFL, Alban Kakulya for his great artistic photo shootings of our prototypes that we created at LSM. Thanks to the armasuisse team, Beat Ott and Peter Wellig, for their collaboration on the development and field test of the Giga-Eye system. Thanks to the University of Geneve Hospital Service of Gastroenterology and Hepatology division and especially to the head of the division Prof. MD Jean-Louis Frossard for discussions on their needs related to colonoscopy applications. I would like to thank to Kurt Müller from Fiberoptic P&P AG company from Zürich for fabrication of my fiber-optic illumination designs.

I would like to thank to my friends from Turkey, TUBITAK, Salih Ergün, Tevfik Nur, Halil Özçiçek who have encouraged and helped me to start my journey in Switzerland.

I would like to thank to my friends from EPFL and LSM: To the Serbian Gang; (Brate) Radisav Cojbasic, (Professor Lazar) Nikola Katic, to Vladan Popovic for his friendship and collaboration on technical issues on panoramic imaging systems. To Hossein Afshari for sharing past knowledge on the Panoptic camera systems. To Abdulkadir Akın, for not only extensive collaboration during our joint work on the Giga-Eye system but also his great friendship during my last 4 years of PhD life. To Tuğba Demirci for her great support in revisions of the thesis script and also being a very good friend during the past years. Special thanks to Kerem Seyid for all of his jokes and funny videos from various resources. Thanks to my friends Oğuz&Bilge Atasoy for helping me during my application to the EPFL as an intern. Thanks to my friends for sharing memorable moments in Switzerland; Gülperi Özsema, Gözen Köklü&Ali Galip Bayrak, Tuna&Yasemin Çiftlik, Selman&Şerife Ergünay, Mustafa&Züleyha Kılıç, Şeniz&Deniz Küçük, İpek Baz, Can Baltacı, İrem Boyabat, Zuhal Taşdemir, Ziya Köstereli, Enver Gürhan Kilinc, Okan Yılmaz, Ece Boran, Baran Gözcü, Kiarash Gharibdoust, Elmira Shahrabi&Mahmoud Hadad, Behnoush Attarimashalkoubeh, Reza Ranjandish, Halima Najibi, Cosimo Aprile, Jury Sandrini, Juan Sebastian Rodriguez, Gain Kim, Clemens Nyffeler, Davide Sacchetto, Yüksel Temiz, Alessandro Cevrero, Giulia Beanato, Vahid Majidzadeh, Mahsa Shoran.

Of course, thanks a lot to my parents and sister; my mother Cemile Çoğal, my father Hüseyin Çoğal and my sister İlknur Çoğal. I would like to thank to them not only being a very supportive family during all my life and during this PhD work but also when I was a kid, giving me opportunity to crash things and also repair them at home. I think this was one of the key points lead to my engineering life.

Finally, to my life time team mate, my wife Betül Emgin Çoğal: For standing with me during these challenging times, for being indulgent and supportive during the times that I was too busy with my work and studies, extensive help in the revision process of the thesis and correcting my other English texts, giving her love and devoting herself to our life-time friendship, making this world a meaningful place for me.

06 November 2015 Lausanne

Ömer Çoğal

### **Abstract**

During the last 50 years miniaturization became a key element in human history, since it opens doors for manufacturing new devices that enhances the quality of human life. Camera and imaging systems are following this miniaturization trend as well. Meanwhile, in the imaging domain, usage of multiple aperture camera systems are gaining significance in every aspects of daily life such as entertainment, surveillance, and medical imaging field. Many works focus on multiple camera panoramic and wide field of view imaging systems in industry and academia. Insect vision is the magnificent example of natural multi-aperture wide angle of view imaging systems. There are many attempts to mimic the insect vision capabilities. Current multi-camera systems that are utilizing off-the-shelf components are big in scale and the miniaturization limits are not explored. On the other hand, the multi-aperture systems fabricated using micro-machining techniques cannot meet high resolution requirements due to the micro-machining precision and optical limitations.

This thesis discloses a set of methods to enable development of miniaturized, multiple camera, large angle of view imaging systems. A second target is to explore the smart vision capabilities of the proposed imaging system such as detection of object boundaries by using multiple camera overlapping field of views.

The main methodology is combining the real-time image processing techniques with off-the-shelf miniature cameras. The presented work includes the methods for combining many miniature cameras mechanically to have a compact vision system similar to the insect eyes. Moreover, image processing techniques for creating high quality panoramic images and extracting useful information from the multiple camera images are applied.

Furthermore, digital hardware system design methodologies are implemented for real-time panoramic video generation from the multiple camera video streams. FPGA implementation of the methods are performed and tested. Migration of the system from FPGA to ASIC design is achieved in 40 nm technology node.

In the scope of the thesis work, the proposed methods are implemented and tested by constructing a 5 mm radius hemispherical compound eye, which is capable of imaging a  $180^{\circ} \times 180^{\circ}$  field of view at 18 mm radial distance.

An FPGA implementation of the image processing system is performed, which is able to generate 25 fps panoramic video with  $1080 \times 1080$  pixel resolution at a 120 MHz processing clock frequency. When compared to the insect eye mimicking systems in literature, the system proposed features more than  $1000 \times$  resolution increase within the same or even smaller physical dimensions.

What is more, by utilizing fiber-optic technology, a built-in illumination capability is added to the compound eye. This is the first time that a compound eye with built-in illumination idea is reported.

With this work, the current limits of off-the-shelf component based methods in terms of physical dimension and resolution are explored for multiple aperture, miniature insect eye mimicking vision systems. The system is tested inside a human colon model for endoscopic applications like colonoscopy where there is a need for large field of view high definition imagery. The possible applications are not limited to medical domain and due to its miniature size and high quality video capabilities, the proposed methods and the system built can be utilized in search and rescue systems and robotic applications.

**Keywords:** real time, image processing, FPGA, ASIC, multiple camera, insect eye, compound eye, miniaturization, colonoscopy.

### Résumé

Au cours des 50 dernières années, la miniaturisation est devenu un élément clé dans l'histoire de l'homme puisqu'elle permet la fabrication de nouveaux dispositifs augmentant sa qualité de vie. Les caméras et systèmes d'imageries actuels suivent aussi cette tendance de miniaturisation. Entretemps, l'utilisation de systèmes à caméras multiples gagne en importance dans tous les aspects de la vie quotidienne de l'homme tels que le divertissement, la surveillance et l'imagerie médicale. En effet, beaucoup de travaux sont concentrés sur le développement de systèmes d'imagerie panoramiques à caméras multiples et à large champs de vision. La vision des insectes est l'exemple parfait d'un système d'imagerie à ouvertures multiples et à grand angle de champ. Il y a d'ailleurs beaucoup de tentatives à imiter les capacités de la vision des insectes. Les systèmes multi-camera actuels utilisant des composants du commerce sont volumineux et les limites de la miniaturisation ne sont pas explorées. Or, d'un autre côté, les systèmes à ouvertures multiples fabriqués par des techniques de microfabrication ne peuvent atteindre une haute résolution dues à leurs imprécisions et aux limitations optiques. Ce travail de thèse divulgue un ensemble de méthodes permettant le développement de systèmes d'imageries miniaturisés à caméras multiples et à grand angle de champs. Un second objectif est d'explorer les capacités de visions intelligentes du système proposé tel que la détection automatique d'objets d'intérêt.

La principale méthodologie est de combiner les techniques de traitements d'images temps réel avec des caméras miniatures disponibles dans le commerce. Le travail pésenté inclus les méthodes permettant de combiner mécaniquement une multitude de caméras miniatures et d'avoir un système de vision compact similaire aux yeux composés d'insectes. De plus, des techniques de traitement d'images sont appliqués afin de créer des images panoramiques de hautes qualités puis d'en extraire des informations utiles.

Par ailleurs, des méthodes de conception matérielle numérique on été implémentées pour la génération de vidéos panoramiques à partir de multiple flux video des caméras. Ces méthodes ont été implémentés et testés sur FPGA, puis une conception ASIC du système a été réalisé. Dans le cadre de ce travail de thèse, les méthodes proposées ont été implémentées et testées en construisant un œil composé hémisphérique de 5mm de rayon, capable d'acquérir des images selon un angle de champ de  $180^{\circ} \times 180^{\circ}$  à une distance radiale de 18 mm.

#### Résumé

Une implémentation du système de traitement d'image a été réalisé sur FPGA, capable de générer de la vidéo panoramique à 25 images par secondes avec une résolution de  $1080 \times 1080$  pixel, cadencée à une fréquence d'horloge de 120 MHz. Comparé aux autres systèmes imitant l'œil composé publiés jusqu'à maintenant, le système proposé présente une amélioration de la résolution d'un facteur 1000 pour une même taille physique, voir plus petite.

De plus, une illumination intégrée a été rajoutée à l'œil composé en utilisant la technologie fibre optique. C'est la première fois que l'idée d'un œil composé avec sa propre illumination intégrée est rapportée.

Avec ce travail, les limites actuels en termes de dimensions physiques et de résolution des méthodes basés sur des composants du commerce sont explorés pour des systèmes de vision imitant l'œil d'insecte. Le système a été testé à l'intérieur d'un modèle de colon humain pour des applications endocopiques tel que la colonoscopie qui requiert une imagerie avec un grand angle de champ et une résolution élevé. Les possibles applications ne se limitent pas seulement au domaine médicale. La taille miniature et la capacité à acquérir des vidéos de haute qualité de ce système peuvent aussi être utilisés pour des systèmes de secours et sauvetage ou des applications robotiques.

Mots clefs : temps réel, traitement d'image, FPGA, ASIC, caméras multiples, yeux d'insectes, œil composé, miniaturisation, colonoscopie.

### **Abbreviations**

2D Two-Dimensional3D Three-Dimensional

**AGC** Automatic Color Gain Controller

**AOV** Angle of View

**APCO** Artificial Apposition Compound Eyes

**ARM** Acorn RISC Machine

ASIC Application-Specific Integrated Circuit

ASW Automatic Shutter Width Controller

AXI Advanced eXtensible Interface

**BRAM** Block Random-Access Memory

**CCD** Charge Coupled Device

**CIF** Common Intermediate Format

**CLF** Constant Light Flux

**CMOS** Complementary Metal Oxide Semiconductor

**CNC** Computer Numerical Control

CPU Central Processing UnitCVT Central Voronoi Tessellation

DDR Double Data RateDDR3 Double Data Rate 3

**DE** Data Enable**DFF** D Flip-Flop

**DMA** Direct Memory Access

**DRAM** Dynamic Random Access Memory

DRC Design Rule CheckDSP Digital Signal ProcessorDVI Digital Visual Interface

**EDA** Electronic Design Automation

#### **Abbreviations**

**EDK** Embedded Development Kit

**EV** Expected Value

FIFO First In First Out

FMC FPGA Mezzanine Card

**FPGA** Field Programmable Gate Array

FPS Frames Per Second FSM Finite State Machine

**GB** Gigabyte

GI Gastro Intestinal

HD High Definition

HDD Hard Disk Drive

**HDMI** High Definition Multimedia Interface

I<sup>2</sup>C Inter-Integrated Circuit

**IO** Input Output

IP Intellectual Property

**ISE** Integrated Synthesis Environment

**ISP** Image Signal Processor

JTAG Joint Test Action Group

LED Light Emmiting Diode

LEF Layout Exchange Format

**LUT** Look-Up-Table

**LVDS** Low Voltage Differential Signal

MAP Maximum a PosterioriMATLAB Matrix LaboratoryM-FPGA Master FPGAMB Megabyte

MLE Maximum Likelihood Estimation

MHz MegahertzMP Megapixel

MPMC Multi-Port Memory Controller

MRF Markov Random Field

MSB Most Significant Bit

MSE Mean Square Error

NPI Native Port Interface

**P&R** Place And Route

PC Personal Computer

PCB Printed Circuit Board

POF Plastic Optical Fiber

PLB Processor Local Bus

PSNR Peak Signal to Noise Ratio

PTZ Pan Tilt Zoom

**RAM** Random-Access Memory

**RGB** Red Green Blue

**RISC** Reduced Instruction Set Computing

ROM Read-Only Memory

RTL Register Transfer Level

**S-FPGA** Slave FPGA

**SAD** Sum of Absolute Difference

SATA Serial Advanced Technology Attachment

SCL Serial Clock

SCLK Serial Clock

**SCI** Serial Communication Interface

SDA Serial Data

SDF Standard Delay Format

SDK Software Development Kit

**SDRAM** Synchronous Dynamic Random Access Memory

**SIFT** Scale Invariant Feature Transform

**SMA** Sub-Miniature Version A

**SRAM** Static Random-Access Memory

**SSD** Solid State Drive

**SURF** Speeded-up Robust Features

**TB** Terabyte

TCL Tool Command Language

**TSMC** Taiwan Semiconductor Manufacturing Company

**UART** Universal Asynchronous Receiver/Transmitter

**USB** Universal Serial Bus

**XGA** Extended Graphics Array

**VGA** Video Graphics Array

**VDMA** Video Direct Memory Access

VHDCI Very High Density Cable InterconnectVHDL VHSIC Hardware Description Language

### Abbreviations

VHSIC Very High Speed Integrated Circuit

VO Virtual Ommatidia

YCbCr Luminance Chrominance-Blue Chrominance-Red

# **Contents**

| Ac | knov  | vledgemen    | ts                                                               | j           |

|----|-------|--------------|------------------------------------------------------------------|-------------|

| Ał | ostra | ct (English/ | Français)                                                        | iii         |

| Ał | brev  | iations      |                                                                  | <b>vi</b> i |

| Li | st of | igures       |                                                                  | X           |

| Li | st of | ables        |                                                                  | xxi         |

| 1  | Intr  | oduction     |                                                                  | 1           |

|    | 1.1   | Multi-can    | nera panoramic imaging                                           | 2           |

|    | 1.2   | Miniaturi    | zed panoramic imaging                                            | 2           |

|    | 1.3   | Insect Eye   | s                                                                | 5           |

|    | 1.4   | Bio-mimio    | cking problem of insect eyes                                     | 6           |

|    | 1.5   | Contributi   | ion of the Thesis                                                | 7           |

|    | 1.6   | Thesis org   | anization                                                        | 8           |

| 2  | Stat  | e of the Art | and Preliminaries                                                | 9           |

|    | 2.1   | Wide Field   | l of View Imaging                                                | g           |

|    | 2.2   | Multi-aper   | rture imaging                                                    | 10          |

|    |       | 2.2.1 Mir    | niaturized insect eye mimicking systems based on micro-machining |             |

|    |       | tecl         | hniques                                                          | 10          |

|    |       | 2.2.2 Cor    | mponent integration based methods and image processing for       |             |

|    |       | -            | norama generation                                                | 12          |

|    | 2.3   | -            | 'imaging for medical endoscopy                                   | 13          |

|    | 2.4   |              | ries of Multi-camera image formation and processing              | 15          |

|    |       |              | hole camera model and camera calibration                         | 15          |

|    |       |              | noptic camera                                                    | 16          |

|    | 2.5   | Thesis Go    | als                                                              | 20          |

| 3  | Opt   | o-Mechani    | cal Aspects for Insect Eye Model                                 | 23          |

|    | 3.1   | 11 0         | of insect eye to camera type eye                                 |             |

|    | 3.2   | Effect of si | ngle camera dimensions                                           | 24          |

### **Contents**

|                                                          | 3.3 | Analy  | rsis for camera placement                                         | 26 |

|----------------------------------------------------------|-----|--------|-------------------------------------------------------------------|----|

| 3.4 Proposed camera placement for miniaturized camera mo |     | •      | osed camera placement for miniaturized camera model               | 27 |

|                                                          |     | 3.4.1  | Method for minimizing the number of cameras for a certain overlap |    |

|                                                          |     |        | distance                                                          | 29 |

|                                                          |     | 3.4.2  | Method for maximizing the number of cameras in a limited volume   | 33 |

|                                                          |     | 3.4.3  | Generalized solution by using uniform distribution                | 35 |

|                                                          | 3.5 |        | osal of illuminating compound eye                                 | 37 |

|                                                          | 3.6 |        | ration and Software Based Stitching Analysis                      | 39 |

|                                                          | 0.0 |        | Discussion                                                        | 41 |

|                                                          | 3.7 |        | lusion                                                            | 42 |

| _                                                        |     |        |                                                                   |    |

| 4                                                        |     | •      | cessing Techniques developed for Multi-camera systems             | 43 |

|                                                          | 4.1 | _      | Field Imaging for a Neural Superposition Virtual Ommatidia        | 43 |

|                                                          | 4.2 |        | r quality panorama generation with probabilistic methods          | 45 |

|                                                          |     | 4.2.1  | Panorama generation as an Inference problem                       | 45 |

|                                                          |     | 4.2.2  | Proposed approach                                                 | 47 |

|                                                          |     | 4.2.3  | Experimental results                                              | 51 |

|                                                          |     |        | Discussion                                                        | 52 |

|                                                          | 4.3 | Inter- | Camera pixel intensity differences and its applications           | 52 |

|                                                          |     | 4.3.1  | Object boundary detection                                         | 53 |

|                                                          |     | 4.3.2  | Inter-camera pixel intensity differences as inference evidences   | 55 |

|                                                          |     | 4.3.3  | Inter-Camera Pixel Intensity Differences as a Quality Measure     | 56 |

|                                                          |     | 4.3.4  | Discussion                                                        | 57 |

|                                                          | 4.4 | Concl  | lusion                                                            | 57 |

| 5                                                        | FPG | A Emb  | pedded System Design                                              | 63 |

|                                                          | 5.1 | Single | e Camera Interface and Image Processing Blocks                    | 63 |

|                                                          |     | 5.1.1  | Interface Printed Circuit Board (PCB)                             | 64 |

|                                                          |     | 5.1.2  | Single Camera Image processing pipeline                           | 66 |

|                                                          |     | 5.1.3  | Camera Model for Test Environment                                 | 71 |

|                                                          | 5.2 | Memo   | ory and Resource Analysis for Full System Implementation          | 73 |

|                                                          |     | 5.2.1  | Xilinx FPGA Board                                                 | 73 |

|                                                          | 5.3 | Syster | m Level Design Considerations                                     | 73 |

|                                                          | 5.4 |        | rama Image Processing Hardware                                    | 74 |

|                                                          |     | 5.4.1  | Pipeline Building blocks                                          | 75 |

|                                                          |     | 5.4.2  | Implementation for the probabilistic method for evidences         | 78 |

|                                                          |     | 5.4.3  | System Implementation                                             | 80 |

|                                                          |     | 5.4.4  | Design for pipeline throughput increase                           | 83 |

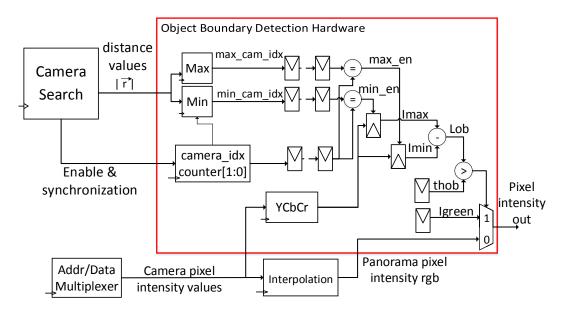

|                                                          |     | 5.4.5  | Hardware implementation for object boundary detection             | 86 |

|                                                          | 5.5 |        | iments and Results                                                | 88 |

|                                                          |     | 5.5.1  | Visual Results                                                    | 89 |

|                                                          |     | 5.5.2  | Efficiency of the system size                                     | 90 |

|                                                          |     |        | Comparison with Different Insect Eve Based Systems                | 91 |

|   | 5.6  | Conclusion                                                                  | 91  |

|---|------|-----------------------------------------------------------------------------|-----|

| 6 | ASI  | C Design for Miniature Insect Eye Inspired Image Processing System          | 93  |

|   | 6.1  | Introduction                                                                | 93  |

|   | 6.2  | ASIC Specifications                                                         | 93  |

|   |      | 6.2.1 Design Constraints                                                    | 94  |

|   | 6.3  | I/Os Analysis                                                               | 94  |

|   |      | 6.3.1 Memory Analysis                                                       | 97  |

|   | 6.4  | FPGA to ASIC Conversion                                                     | 99  |

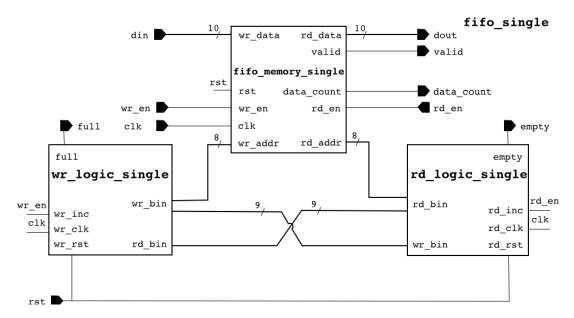

|   |      | 6.4.1 FIFO Design                                                           | 99  |

|   |      | 6.4.2 Dual-Clock FIFO                                                       | 100 |

|   |      | 6.4.3 Single-Clock FIFO                                                     | 101 |

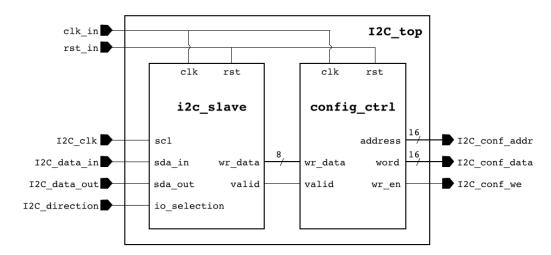

|   |      | 6.4.4 Serial Communication Interfaces                                       | 102 |

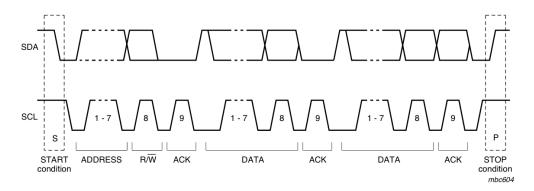

|   |      | 6.4.5 $I^2C$ Design                                                         | 103 |

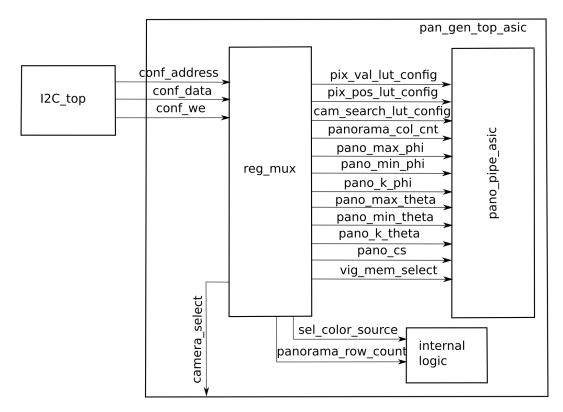

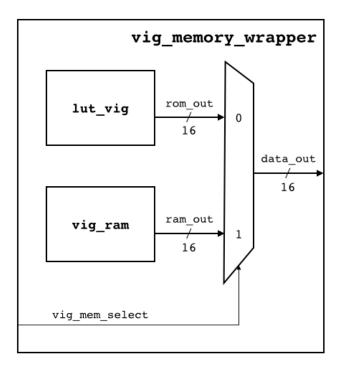

|   |      | 6.4.6 Memory Wrappers                                                       | 105 |

|   | 6.5  | ASIC Design                                                                 | 106 |

|   |      | 6.5.1 RTL Synthesis                                                         | 106 |

|   |      | 6.5.2 Place and Route                                                       | 107 |

|   | 6.6  | Logic Simulations                                                           | 110 |

|   |      | 6.6.1 RTL Simulation                                                        | 110 |

|   | 6.7  | Conclusion                                                                  | 110 |

| 7 | Mul  | ti-camera large FOV or panoramic imaging system design in macro scale       | 119 |

|   | 7.1  | System Parameters and Requirements                                          |     |

|   | 7.2  | System Architecture                                                         |     |

|   | 7.3  | Implementation Results                                                      |     |

|   | 7.4  | Conclusion                                                                  |     |

|   |      |                                                                             |     |

| 8 |      | clusion                                                                     | 131 |

|   | 8.1  | A model for miniaturization of insect eye inspired imaging system by using  |     |

|   |      | off-the-shelf components                                                    |     |

|   | 8.2  | Image processing for seamless compound image generation                     |     |

|   | 8.3  | Digital system design for image processing                                  |     |

|   | 8.4  | ASIC Implementation                                                         |     |

|   | 8.5  | Future Directions                                                           | 132 |

| A | Ana  | lysis and implementations of different Bayer Demosaicing and Automatic Whit | e   |

|   | Bala | ancing Methods                                                              | 135 |

|   | A.1  | Analyzed and implemented Bayer to RGB methods                               | 135 |

|   |      | A.1.1 Gradient Based Methods                                                | 135 |

|   |      | A.1.2 Adam and Hamilton's Method                                            | 136 |

|   |      | A.1.3 Improved Gradient Estimation                                          | 138 |

|   | A.2  | Hybrid Method                                                               | 139 |

### **Contents**

|    | A.3        | Automatic White Balancing                                                | 141 |

|----|------------|--------------------------------------------------------------------------|-----|

|    | A.4        | Gray World Assumption                                                    | 143 |

|    | A.5        | White Patch                                                              | 144 |

|    | A.6        | Implementation Details                                                   | 145 |

|    | A.7        | Results                                                                  | 146 |

|    | <b>A.8</b> | Bayer to RGB                                                             | 146 |

|    |            | A.8.1 Optical Analysis                                                   | 147 |

|    |            | A.8.2 Measurements                                                       | 148 |

|    |            | A.8.3 Resource Usage                                                     | 150 |

|    | A.9        | Automatic White Balancing                                                | 151 |

|    |            | A.9.1 Optical Analysis                                                   | 151 |

|    |            | A.9.2 Resource Usage                                                     | 152 |

|    | A.10       | O Visual Results from the implemented single camera system               | 153 |

| В  | Det        | ails of sub blocks FPGA to ASIC conversion                               | 155 |

|    | B.1        | Details of the dual clock FIFO design                                    | 155 |

|    | B.2        | Details of serial communication interface choice                         | 157 |

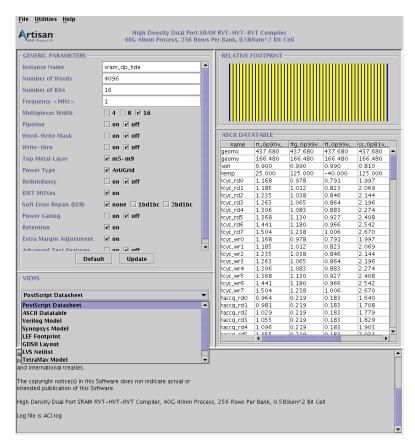

|    | B.3        | The memory generator used for custom memory blocks for ASIC design       | 159 |

|    | B.4        | $I^2C$ Communication Protocol                                            | 159 |

| C  | Exa        | mple video output links for the miniaturized compound eye imaging system | 161 |

| Bi | bliog      | graphy                                                                   | 171 |

| Cı | ırricı     | ulum Vitae                                                               | 173 |

# **List of Figures**

| 1.1 | drone from photosiphone company, image from [6] (b) different panoramic                                                                                         |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | imaging solutions with wide angle optical systems, from GoPano [7], Kogeto [8],                                                                                 | 1  |

|     | and the Bubblepix [9] companies from left to right.                                                                                                             | 3  |

| 1.2 | The problem of narrow field of view in colonoscopy applications                                                                                                 | 4  |

| 1.3 | Anatomy of an insect eye, image from [20]                                                                                                                       | 5  |

| 1.4 | Insect eye types according to their image formation, image redrawn from [19] (a) apposition (b) optical superposition (c) neural superposition type             | 6  |

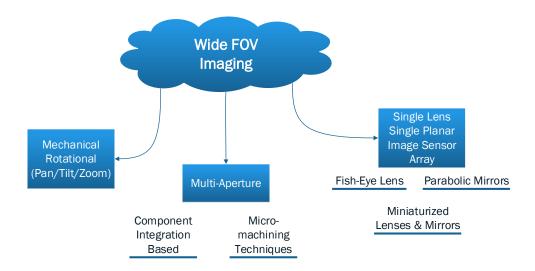

| 2.1 | Wide FOV imaging classification                                                                                                                                 | 10 |

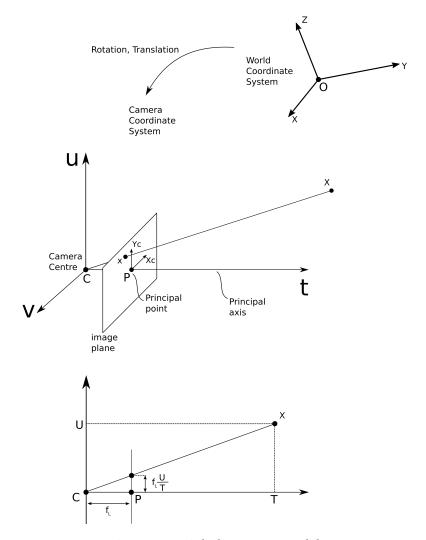

| 2.2 | Pinhole Camera Model                                                                                                                                            | 14 |

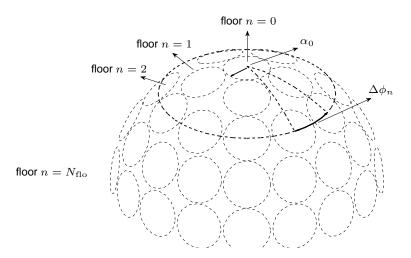

| 2.3 | An example arrangment of circular faces as individual cameras on a hemisphere.                                                                                  | 16 |

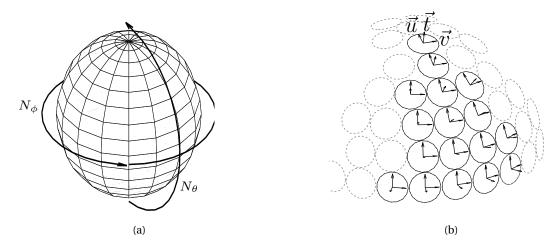

| 2.4 | (a) Example pixelization of the spherical surface, (b) 3 vectors $\vec{t}$ , $\vec{u}$ , $\vec{v}$ representing camera orientation and positions                | 17 |

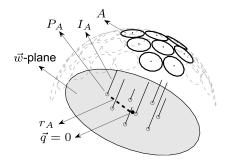

| 2.5 | Projections of camera centers contributing in direction $\vec{\omega}$ onto planar surface                                                                      |    |

|     | normal to $\vec{\omega}$                                                                                                                                        | 18 |

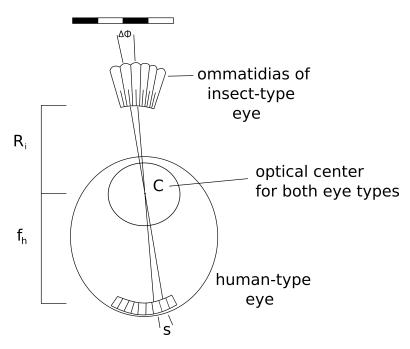

| 3.1 | The relation between insect and human eye resolving capability                                                                                                  | 24 |

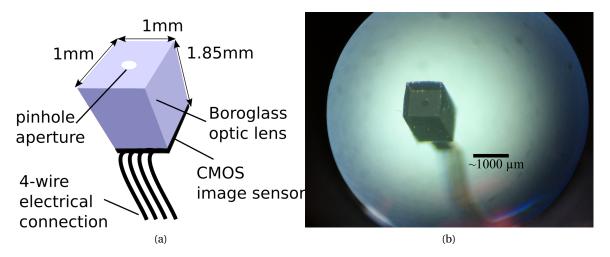

| 3.2 | The camera chosen for the implementation, (a) illustration for the physical dimensions of the single camera (b) a close photo view of the camera taken          |    |

|     | under a microscopic lens                                                                                                                                        | 25 |

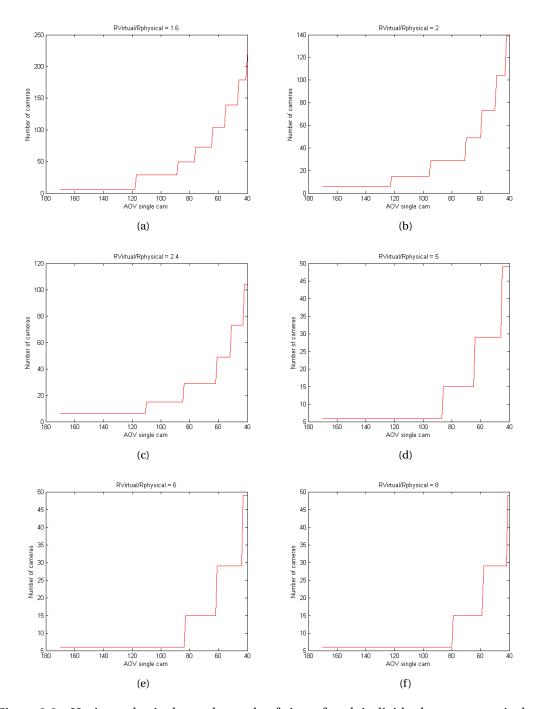

| 3.3 | Horizontal axis shows the angle of view of each individual camera, vertical axis shows the required number of cameras for having virtual ommatidias at distance |    |

|     | $R_{virtual} = 8, 10, 12, 25, 30, 40 \text{ mm with a } R_{physical} = 5 \text{mm.}$                                                                            | 28 |

| 3.4 | New camera placement model (a) single camera circular surface model on dome y-z plane (b) Geometrical relations of the cameras in one quarter of the dome in    |    |

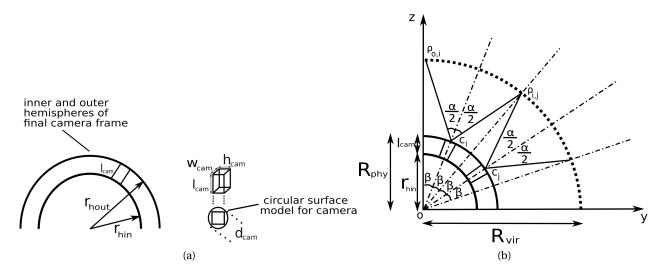

|     | y-z plane                                                                                                                                                       | 29 |

| 3.5 | Illustration for the layers for extending the camera placement around the                                                                                       |    |

|     | hemisphere                                                                                                                                                      | 31 |

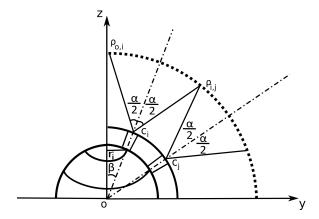

| 3.6 | Illustration for the overlap analysis for 3 cameras positioned at layer 0 with                                                                                  |    |

|     | $\beta_0$ = 15°. The smallest latitudinal angle from the north-pole that is not seen by                                                                         |    |

|     | any camera is $\theta_{-}uc_0 = 19.6^{\circ}$                                                                                                                   | 32 |

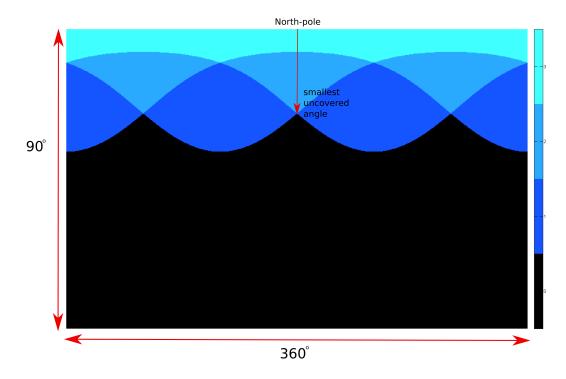

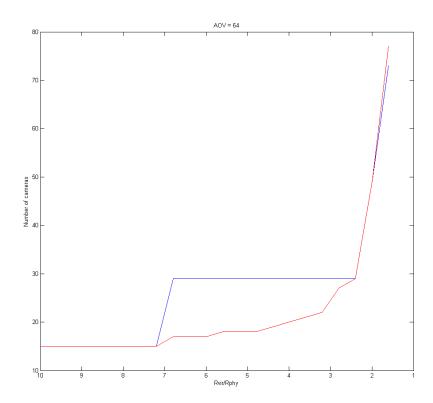

| 3.7  | Analysis of the growth of the camera positions for single camera AOV=64°, starting in a overlap range $R_{vir}/R_{phy} = 50/5 : 8/5$ . The proposed method is | 00  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | plotted in red color and the method in [65] in blue color                                                                                                     | 33  |

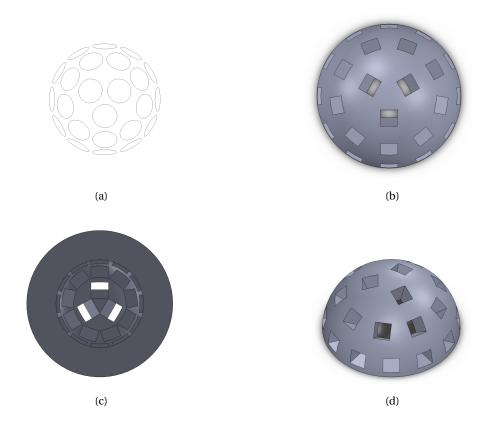

| 3.8  | The camera positions on the final design for prototyping, (a) 24 camera positions,                                                                            | 0.5 |

|      | (b),(c) and (d) the mechanical model drawing from different viewing angles                                                                                    | 35  |

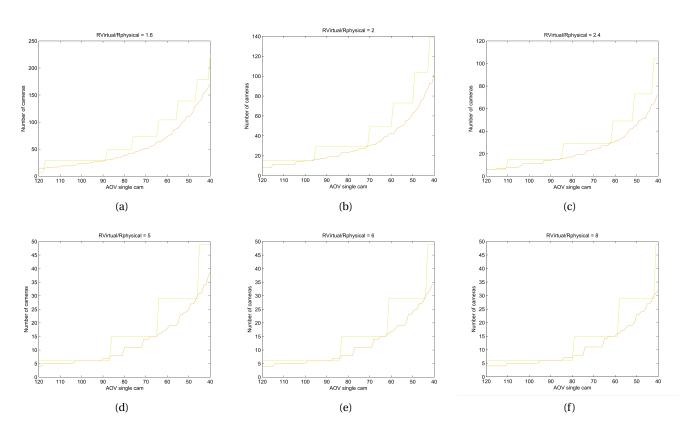

| 3.9  | The comparison of the growth of the number of cameras for previous method                                                                                     |     |

|      | [64] and the CVT based method proposed. Horizontal axis shows the angle                                                                                       |     |

|      | of view of each individual camera, vertical axis shows the required number of                                                                                 |     |

|      | cameras for having virtual ommatidias at distance $R_{virtual} = 8, 10, 12, 25, 30, 40$                                                                       | 20  |

| 0.10 | mm with a $R_{physical}$ =5 mm.                                                                                                                               | 36  |

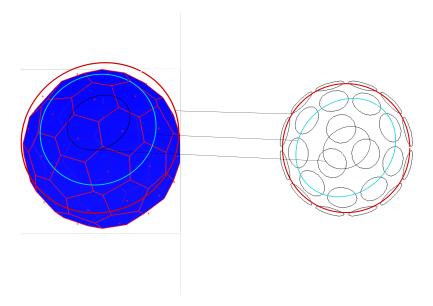

| 3.10 | An example for the camera positions obtained from CVT based method for                                                                                        |     |

|      | $R_{vir} = 18 \ mm$ and $R_{vir} = 5 \ mm$ , and matching the approximate positions with                                                                      | 37  |

| 2 11 | our final design                                                                                                                                              | 31  |

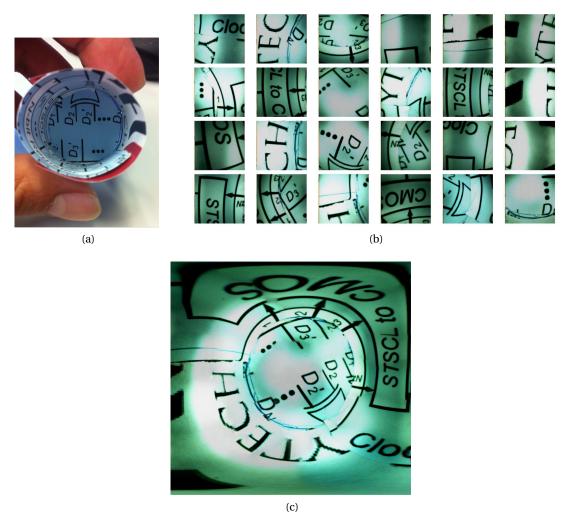

| 3.11 | ,(c) and (d) the fabricated and assembled prototype                                                                                                           | 38  |

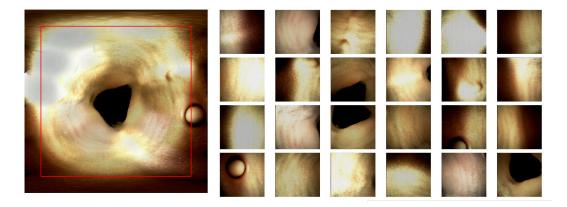

| 2 12 | The calibration environment and single camera frames of the prototype (a)                                                                                     | 30  |

| 3.12 | calibration tube with 35 mm diameter (b) 24-camera single frames used                                                                                         |     |

|      | in calibration (c) $180^{\circ} \times 180^{\circ}$ image generated from the 24 single frames at                                                              |     |

|      | calibration procedure                                                                                                                                         | 41  |

|      | F                                                                                                                                                             |     |

| 4.1  | Virtual ommatidia sampling concept with the proposed prototype                                                                                                | 44  |

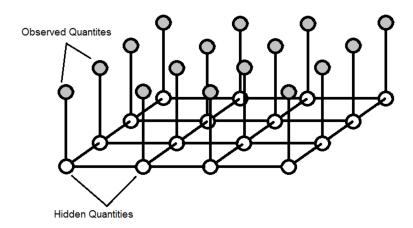

| 4.2  | Example graph representation for the panoramic image                                                                                                          | 49  |

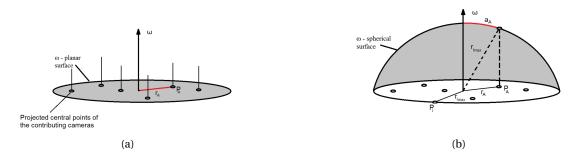

| 4.3  | The proposed method for accurate prior estimation from spherical model, (a)                                                                                   |     |

|      | the previous planar model, (b) proposed spherical arrangement for estimating                                                                                  |     |

|      | the priors                                                                                                                                                    | 51  |

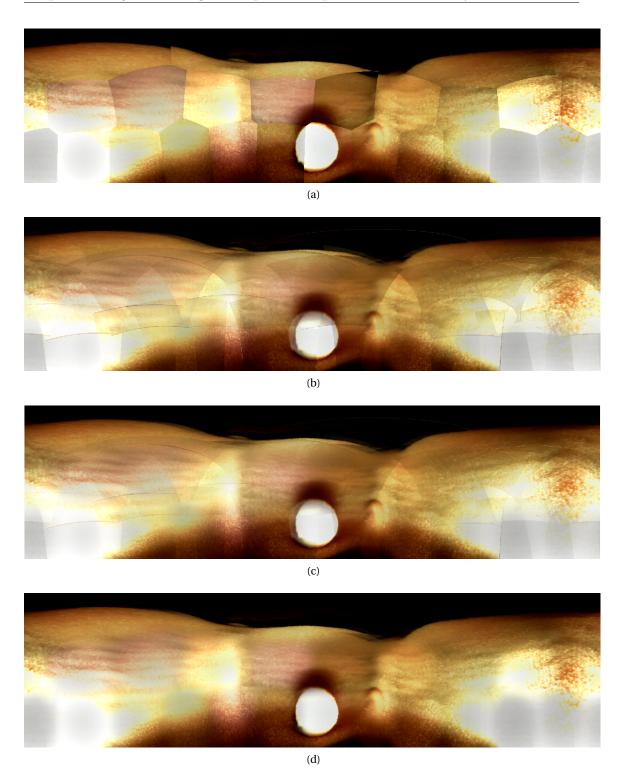

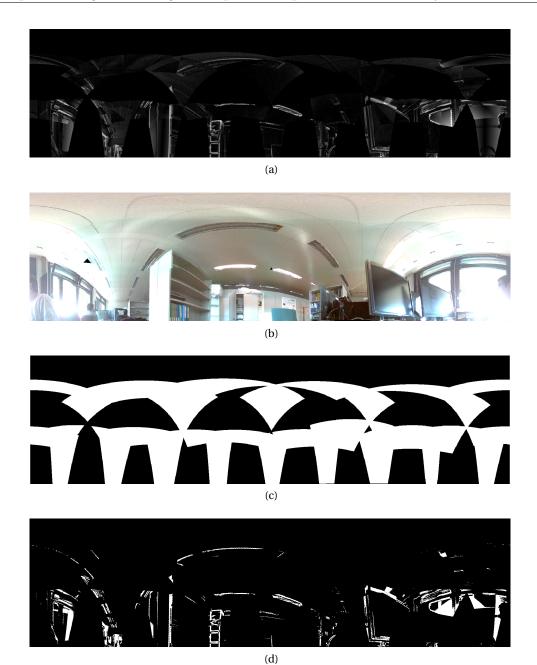

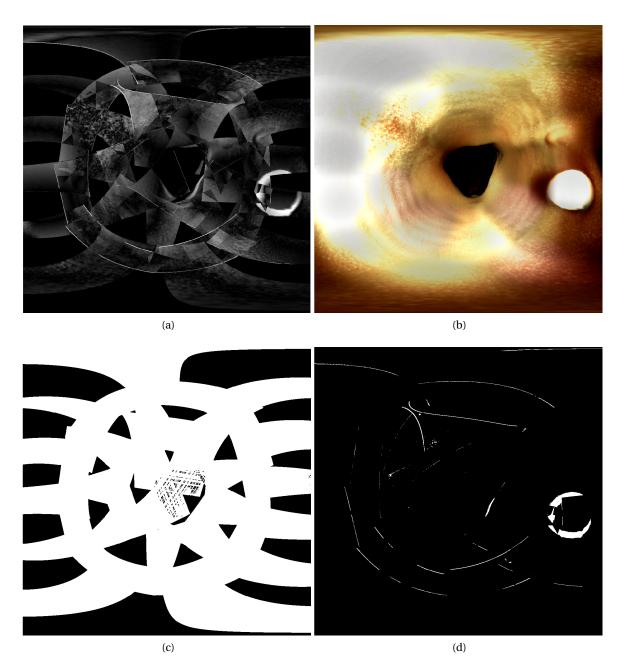

| 4.4  | The comparison of the probabilistic inference method (d) with nearest neighbor                                                                                |     |

|      | method [64](a), linear blending method [70](b), linear blending with Gaussian                                                                                 |     |

|      | smoothed weights [66] (c). The images have 1920x512 resolution, generated in                                                                                  |     |

|      | MATLAB using the output images from our miniaturized 24-camera system                                                                                         | 58  |

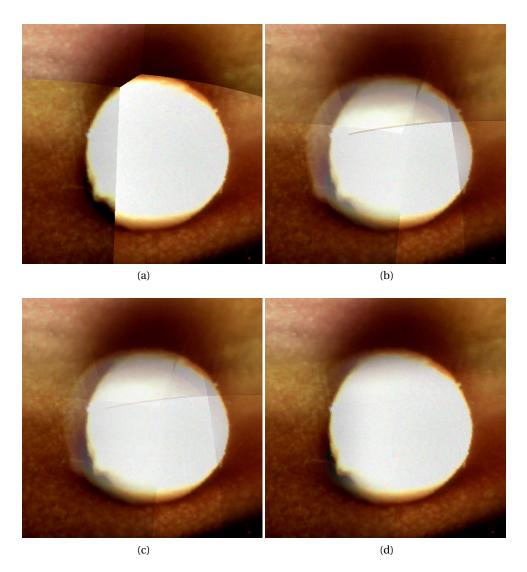

| 4.5  | The comparison for 2x zoomed on the polyp to show the effect on object                                                                                        |     |

|      | boundaries. nearest neighbor(a), linear blending(b), gaussian smoothed linear blending (c) and proposed probabilistic inference method (d). The images have   |     |

|      | 512x512 resolution, generated in MATLAB using the output images from our                                                                                      |     |

|      | miniaturized 24-camera system                                                                                                                                 | 59  |

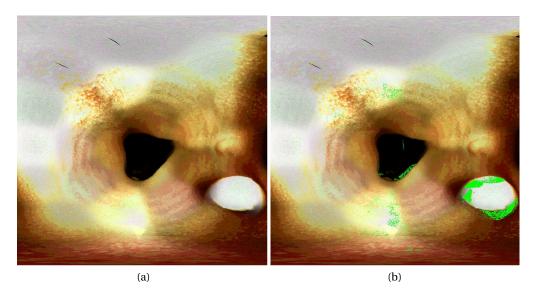

| 4.6  | The results obtained from the proposed method for object boundary detection.                                                                                  | 55  |

| 1.0  | (a) The object boundary map in gray scale, (b) Constructed panorama image (c)                                                                                 |     |

|      | the regions seen only one camera in shown in black (d) final object boundary                                                                                  |     |

|      | map with a threshold $th_{ob} = 0.2$                                                                                                                          | 60  |

| 4.7  | The results obtained from the proposed method for object boundary detection.                                                                                  |     |

|      | (a) The object boundary map in gray scale, (b) Constructed panorama image (c)                                                                                 |     |

|      | the regions seen only one camera in shown in black (d) final object boundary                                                                                  |     |

|      | map with a threshold $th_{ob} = 0.6$                                                                                                                          | 61  |

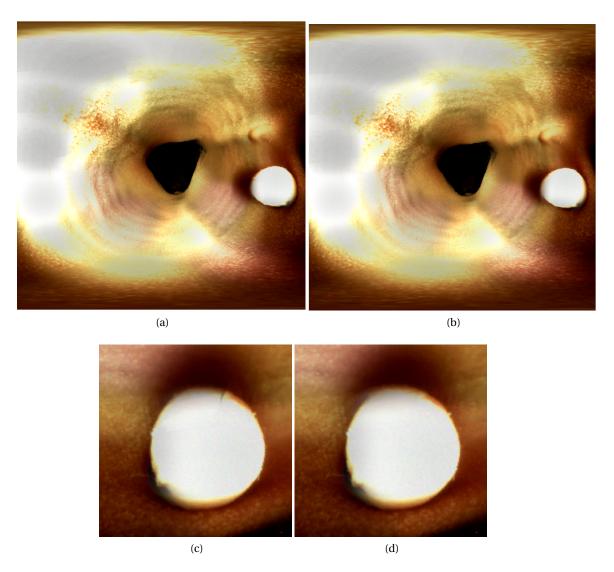

| 4.8         | The results obtained from the proposed method for SAD based interpolation. (a) The resulting image in $180^{\circ} \times 180^{\circ}$ angle of view $1080x1080p$ resolution, (b) The same reconstruction with method in [74] (c) the zoomed image on the polyp object for SAD based method (d) the zoomed image with previous method | 62 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

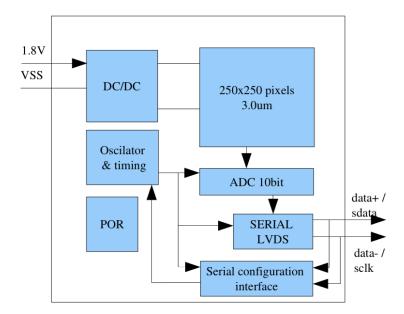

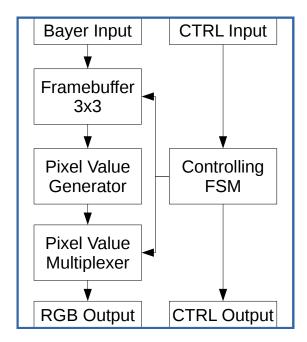

| 5.1         | Single image sensor block diagram                                                                                                                                                                                                                                                                                                     | 64 |

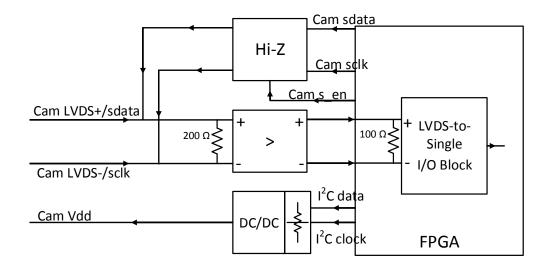

| 5.2         | Circuit block diagram for the PCB, simplified view for one camera interfacing.                                                                                                                                                                                                                                                        | 65 |

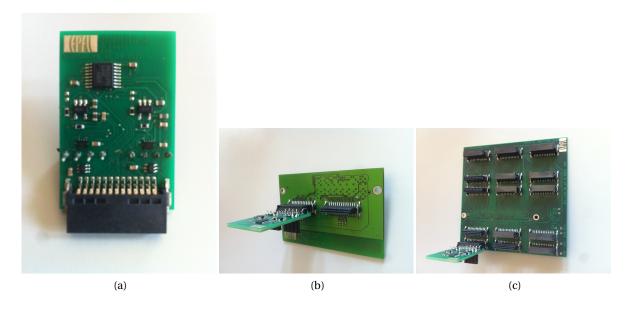

| 5.3         | The custom PCB designs for camera interfacing. (a) camera interface PCB for 2                                                                                                                                                                                                                                                         |    |

|             | cameras, (b) and (c) main board PCB supporting 4 and 30 cameras respectively.                                                                                                                                                                                                                                                         | 65 |

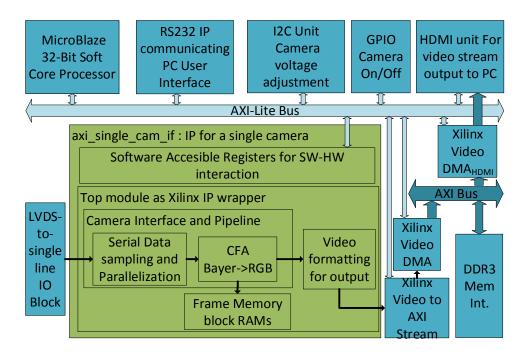

| 5.4         | The custom single camera pipeline as an FPGA AXI slave IP, and the embedded                                                                                                                                                                                                                                                           |    |

|             | system designed for testing the interface                                                                                                                                                                                                                                                                                             | 66 |

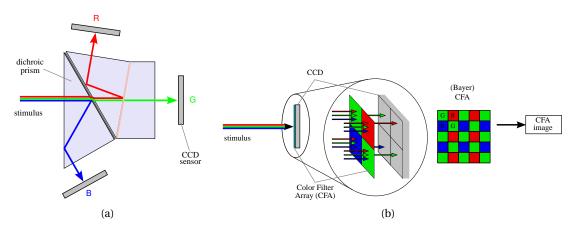

| 5.5         | Two possible configuration for color image sensing [85] (a) three sensors                                                                                                                                                                                                                                                             |    |

|             | arrangement for capturing R,G,B channels separately, (b) using Bayer pattern                                                                                                                                                                                                                                                          |    |

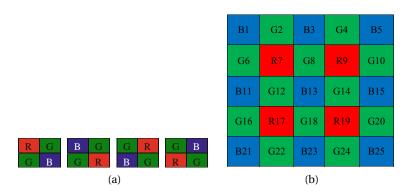

|             | with a single sensor                                                                                                                                                                                                                                                                                                                  | 68 |

| 5.6         | Individual and combined representation of Bayer patterns (a) Possible regular                                                                                                                                                                                                                                                         |    |

|             | Bayer patterns [86] (b) A 5x5 bayer matrix [87]                                                                                                                                                                                                                                                                                       | 69 |

| 5.7         | Schematic of the bilinear Bayer to RGB converter architecture                                                                                                                                                                                                                                                                         | 71 |

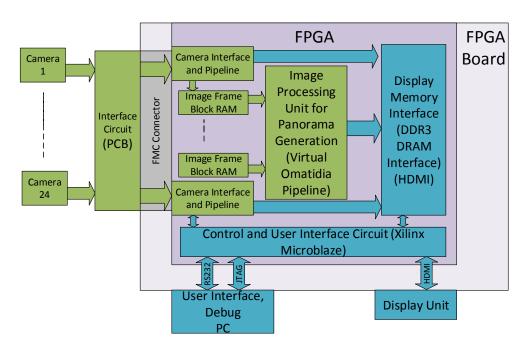

| 5.8         | The embedded system block diagram                                                                                                                                                                                                                                                                                                     | 74 |

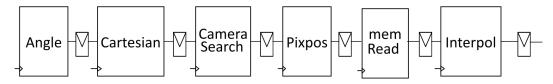

| 5.9         | The panorama pixel generation pipeline                                                                                                                                                                                                                                                                                                | 75 |

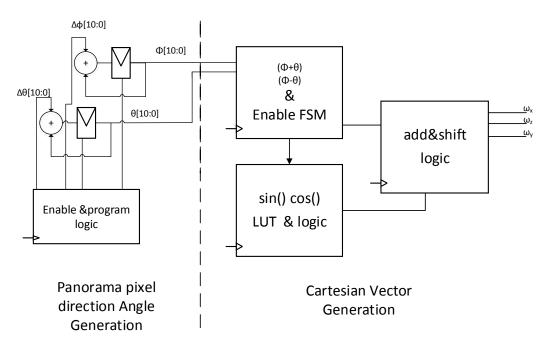

|             | The block diagram used for angle and Cartesian vector calculation                                                                                                                                                                                                                                                                     | 76 |

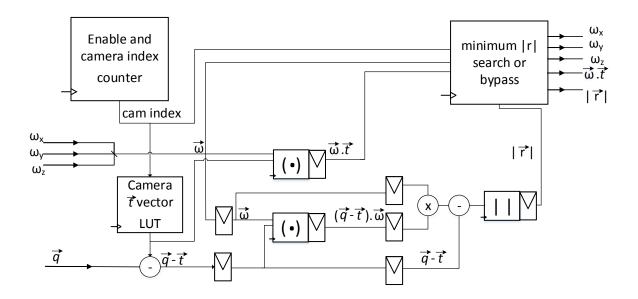

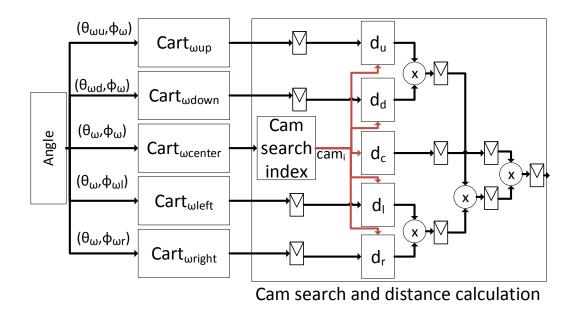

|             | The block diagram used for camera search and distance calculation                                                                                                                                                                                                                                                                     | 77 |

|             | The block diagram for implementation of the probabilistic evidence calculation                                                                                                                                                                                                                                                        | 79 |

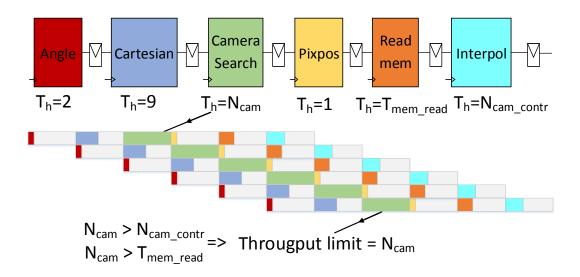

|             | The pipeline analysis of the system                                                                                                                                                                                                                                                                                                   | 80 |

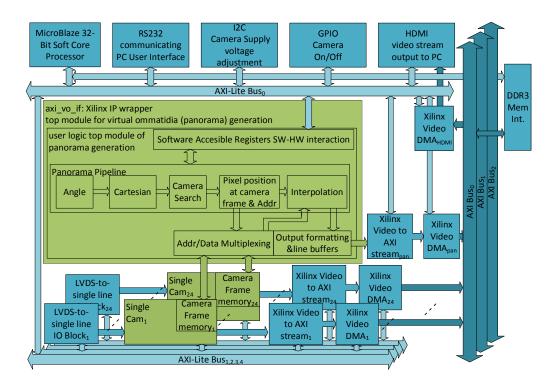

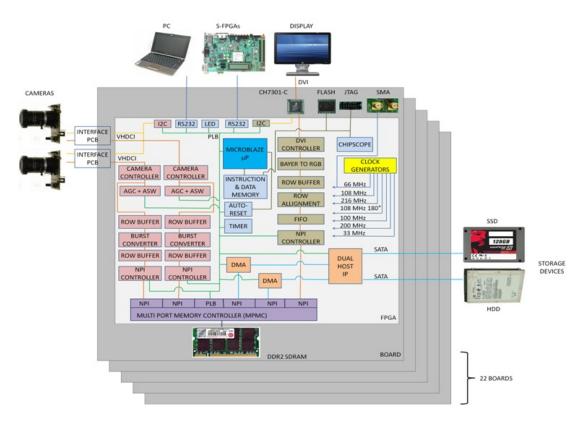

|             | FPGA system block diagram                                                                                                                                                                                                                                                                                                             | 81 |

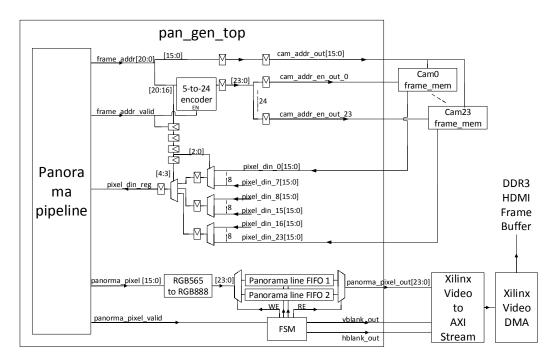

| 5.15        | Interface of the panorama generation pipeline with camera frame memories                                                                                                                                                                                                                                                              | 00 |

| <b>5.10</b> | and video DMA output for DDR3 RAM                                                                                                                                                                                                                                                                                                     | 82 |

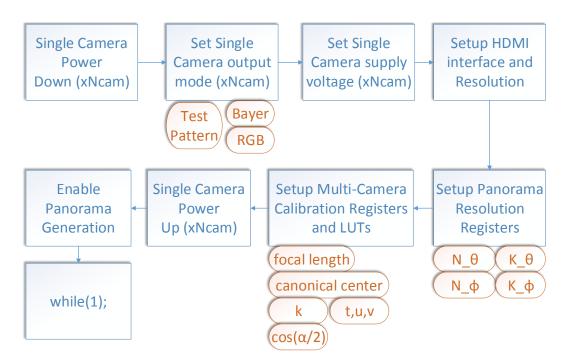

|             | The tasks and the flow of the Microblaze embedded processor firmware                                                                                                                                                                                                                                                                  | 83 |

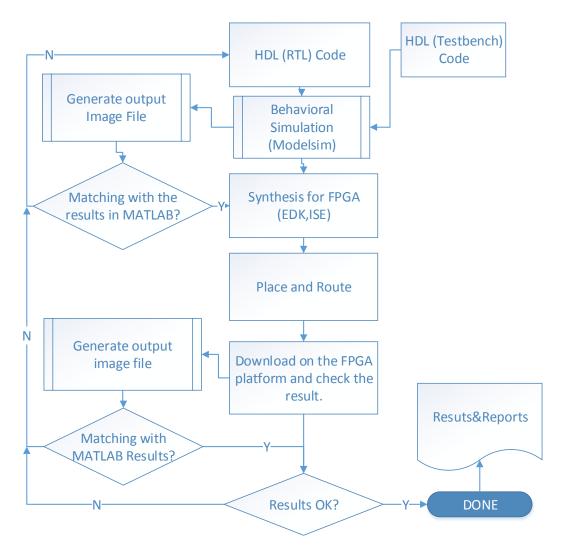

|             | The design and test flow methodology followed during development and tests.  The proposed hardware for object/poylp boundary detection                                                                                                                                                                                                | 84 |

|             | An example of the hardware generated output image for colon boundary                                                                                                                                                                                                                                                                  | 86 |

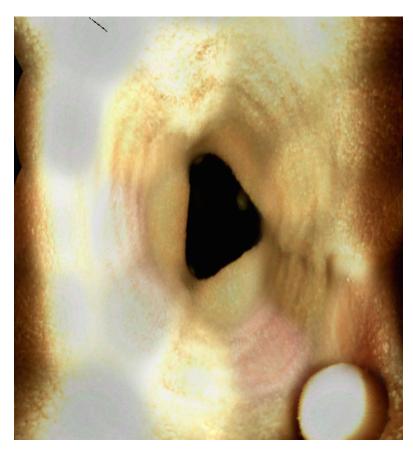

| 3.19        | detection. (a) the $180^{\circ} \times 180^{\circ}$ panoramic image in $1024 \times 1024$ resolution (b) the                                                                                                                                                                                                                          |    |

|             | possible boundary regions are marked with green color by the hardware described.                                                                                                                                                                                                                                                      | ΩΩ |

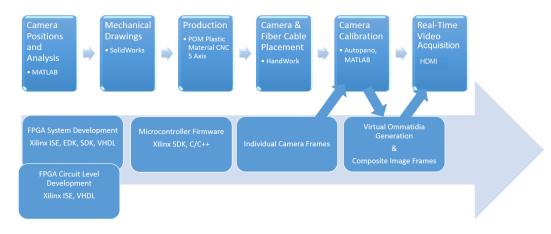

| 5 20        | The complete prototyping chain used for the implementation of system                                                                                                                                                                                                                                                                  | 88 |

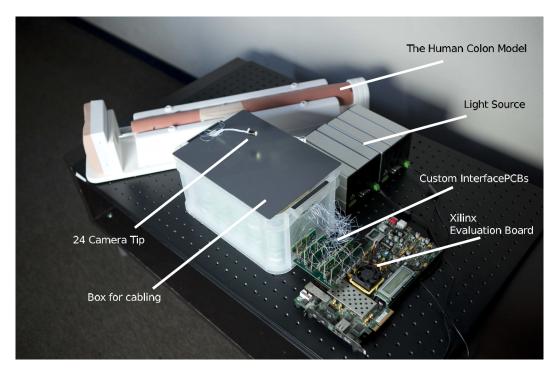

|             | The complete system built and used for experiments                                                                                                                                                                                                                                                                                    | 89 |

|             | An example of the output image from the system                                                                                                                                                                                                                                                                                        | 89 |

|             | An example image for the USAF 1951 measurements, the image is captured in                                                                                                                                                                                                                                                             | 00 |

|             | 1024x1024 resolution, at 25 mm distance from the hemispherical camera center.                                                                                                                                                                                                                                                         | 91 |

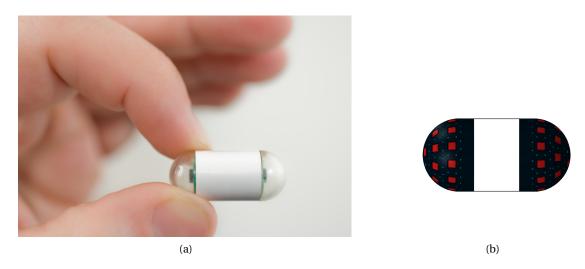

| 6.1         | Capsule Endoscopy concept with miniaturized insect eye imaging system                                                                                                                                                                                                                                                                 | 94 |

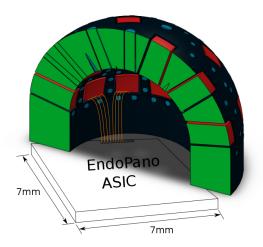

| 6.2         | ASIC design conceptual illustration with EndoPano imaging tip                                                                                                                                                                                                                                                                         | 95 |

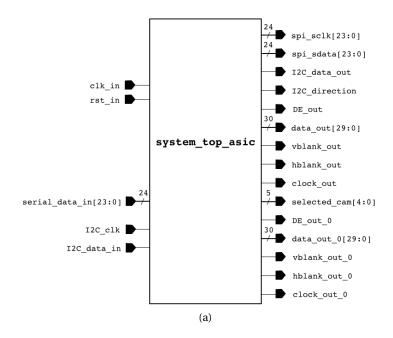

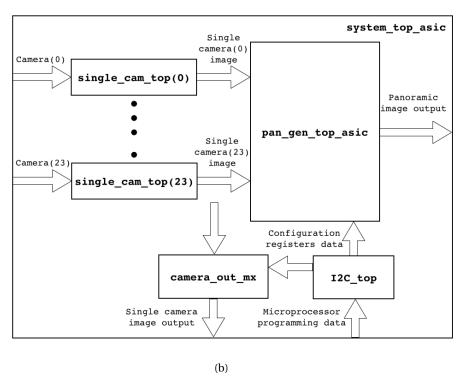

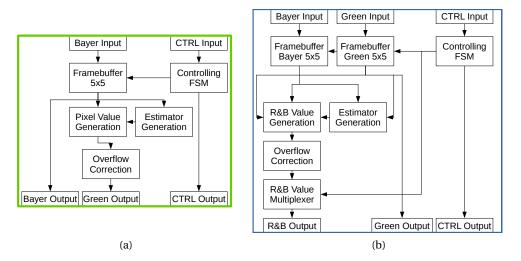

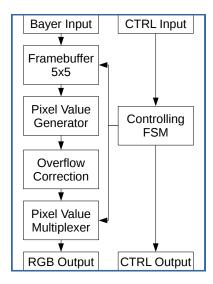

| 6.3         | ASIC design top level (a) and block diagram (b)                                                                                                                                                                                                                                                                                       | 96 |

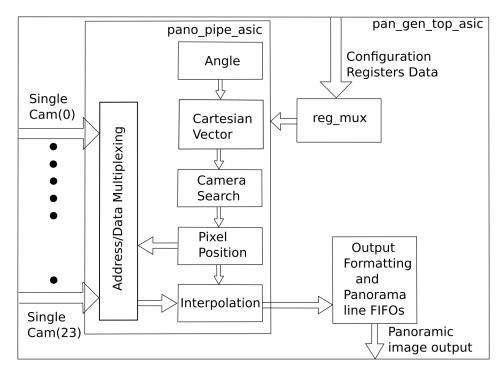

| 6.4         | Panorama generation block diagram                                                                                                                                                                                                                                                                                                     | 97 |

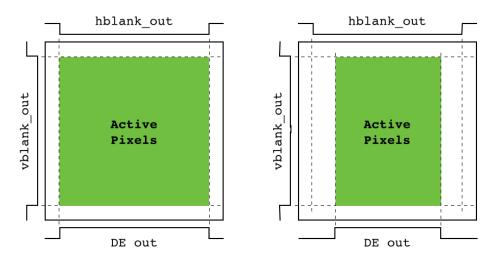

| 6.5         | Raster scanning principle for different DE_out pulse width                                                                                                                                                                                                                                                                            | 97 |

### **List of Figures**

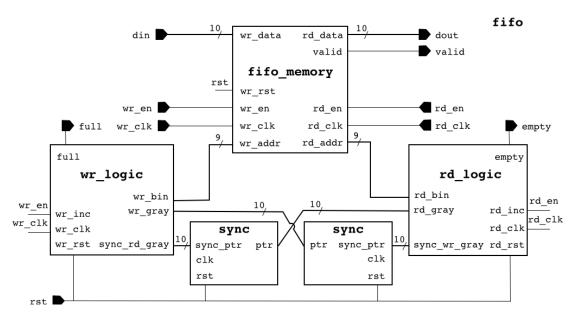

| 6.6  | Dual-clock FIFO block diagram                                                     | 101  |

|------|-----------------------------------------------------------------------------------|------|

| 6.7  | Single-clock FIFO block diagram                                                   | 102  |

| 6.8  | $I^2C$ block diagram                                                              | 103  |

| 6.9  | Register update process                                                           | 104  |

| 6.10 | Register array structure                                                          | 105  |

| 6.11 | Memory wrapper example                                                            | 106  |

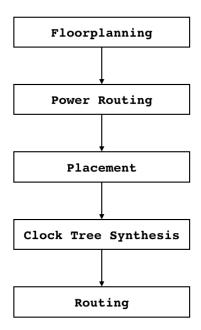

| 6.12 | Physical design steps                                                             | 108  |

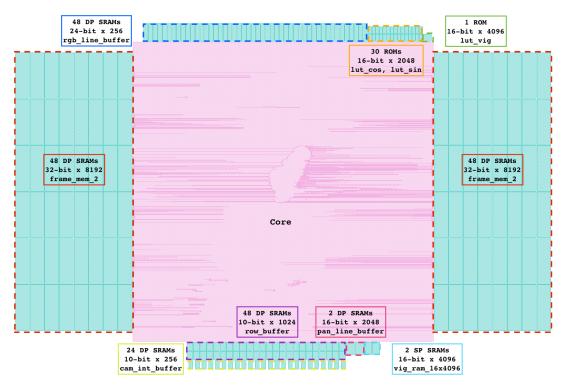

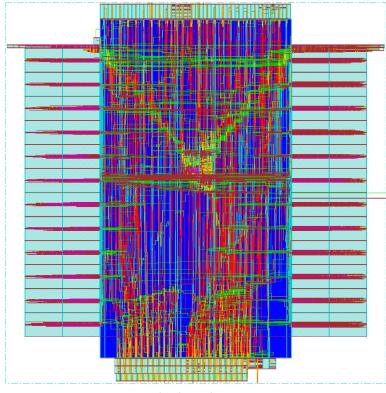

| 6.13 | First P&R design                                                                  | 114  |

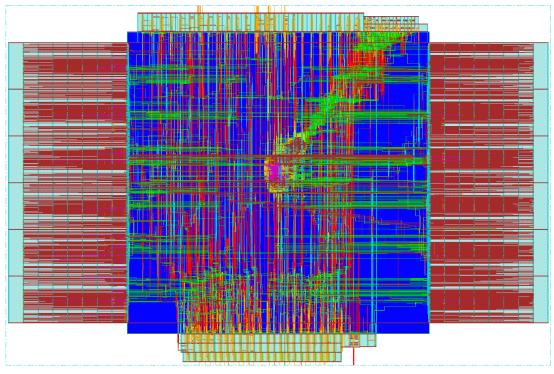

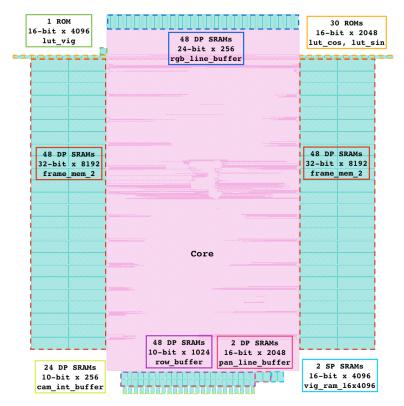

| 6.14 | Second P&R design                                                                 | 116  |

| 6.15 | An example of panoramic frame obtained through RTL logic simulation of the        |      |

|      | ASIC system                                                                       | 117  |

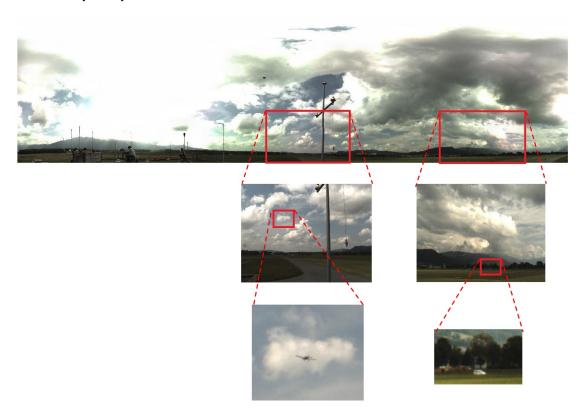

| 7.1  |                                                                                   | 124  |

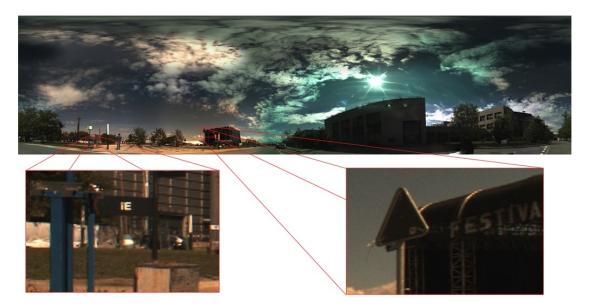

| 7.2  | The complete omnidirectional imaging and recording system (Giga-Eye), overall     |      |

|      | system dimensions are 56x48x78 cm                                                 | 127  |

| 7.3  | Omnidirectional image obtained with the Giga-Eye system at 21.6 MP resolution     |      |

|      | showing the central campus square of EPFL, and two selected details               |      |

|      | (sub-regions) in this image. This omnidirectional image corresponds to one        |      |

|      | · · ·                                                                             | 128  |

| 7.4  | Omnidirectional image obtained with the Giga-Eye system at 82.3 MP resolution.    |      |

|      | This omnidirectional image corresponds to one single frame of the 9.5 fps video   | 100  |

|      | obtained by the system. Flying plane and the moving car are shown in sub-windows  | 3128 |

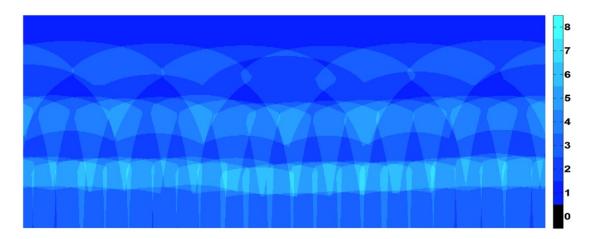

| 7.5  | Measured coverage map of the omnidirectional imaging system showing a high        |      |

|      | pixel redundancy especially close to the equator. The color labels indicate the   | 100  |

|      | number of the overlapping individual camera AOVs                                  | 129  |

| A.1  | , , , , , , , , , , , , , , , , , , ,                                             | 140  |

| A.2  | Block diagram of the hybrid Bayer to RGB converter architecture                   | 141  |

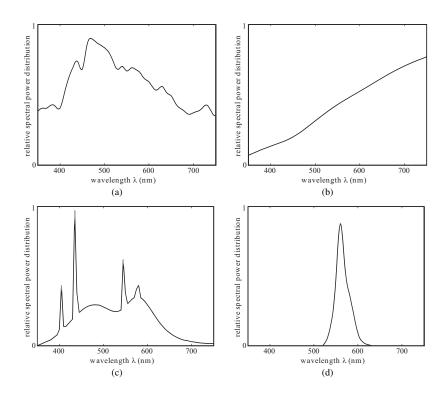

| A.3  | Spectral power distribution of various common types of illuminations: (a)         |      |

|      | sunlight, (b) tungsten light, (c) fluorescent light, and (d) LED [100]            | 142  |

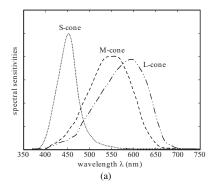

| A.4  | Spectral sensitivities of: (a) the three types of cones in a human eye, and (b) a |      |

|      | typical digital camera [100]                                                      | 143  |

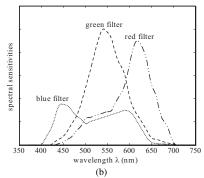

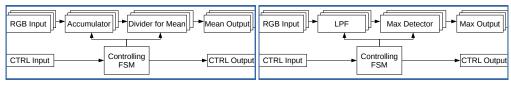

| A.5  | Block diagram of a part of the gray and the white patch automatic white           |      |

|      | balancing algorithm                                                               | 146  |

| A.6  | Block diagram of the common part of the gray and white patch automatic white      |      |

|      | balancing algorithm                                                               | 146  |

| A.7  | Interpolation results using a $3 \times 3$ window                                 | 147  |

| A.8  | Bayer CFA interpolation results using a $5 \times 5$ window                       | 149  |

|      | White balance comparison for images taken under a tungsten light source           | 152  |

|      | Image taken in human guts with balanced light                                     | 152  |

| A.11 | Image taken with a live system with different AWB methods                         | 154  |

| B.1  | Multi-flop synchronizer [103]                                                     | 156  |

| List | of | Fig | ures |

|------|----|-----|------|

|      |    |     |      |

| B.2        | Example of data incoherency [103] | 157 |

|------------|-----------------------------------|-----|

| B.3        | ARM Artisan Physical IP GUI       | 159 |

| <b>B.4</b> | $I^2C$ data transfer [106]        | 160 |

# **List of Tables**

| 1.1  | Current solutions for panoramic colonoscopy                                                | 4   |

|------|--------------------------------------------------------------------------------------------|-----|

| 2.1  | Summary of curved optics/electronics based solutions for multi-aperture insect eye imaging | 12  |

| 3.1  | Single image sensor opto-mehcanical specifications                                         | 25  |

| 5.1  | Single image sensor electrical specifications                                              | 63  |

| 5.2  | Programmable features for single camera IP                                                 | 67  |

| 5.3  | Specifications of VC707 FPGA board chosen for embedded system and image                    |     |

|      | processing hardware implementation                                                         | 73  |

| 5.4  | Resource overview of Virtex-7 XC7VX485T FPGA chosen for embedded system                    |     |

|      | and image processing hardware implementation                                               | 74  |

| 5.5  | List of critical resource consuming blocks in the camera search and distance               |     |

|      | calculation module                                                                         | 79  |

| 5.6  | The resource usage results of the sub blocks and the full system on the Virtex7            |     |

|      | FPGA for the first implementation                                                          | 82  |

| 5.7  | The resource usage results of the sub blocks and the full system on the Virtex7            |     |

|      | FPGA for the increased throughput pipeline                                                 | 86  |

| 5.8  | Virtex-7 FPGA resource usage overhead for object boundary detection method                 | 87  |

| 5.9  | Comparison with insect eye systems in terms of resolution and size                         | 92  |

| 6.1  | System inputs for ASIC design                                                              | 98  |

| 6.2  | System outputs for the ASIC design                                                         | 98  |

| 6.3  | Possible pins configurations for ASIC design                                               | 99  |

| 6.4  | List of ASIC memory elements                                                               | 100 |

| 6.5  | FIFOs present in the ASIC design                                                           | 100 |

| 6.6  | Channels bits partition for configuring the internal register arrays and memories,         |     |

|      |                                                                                            | 105 |

| 6.7  | Configuration registers specifications for the ASIC design                                 | 112 |

| 6.8  | Memory wrappers implemented for the ASIC design                                            | 113 |

| 6.9  | Critical paths for different synthesized gate-level net-lists of the ASIC design .         | 113 |

| 6.10 | Core area percentage occupied by macro cells of the first ASIC design configuration        | 113 |

### **List of Tables**

| 6.11 | First ASIC design P&R summary reports                                                    | 115 |

|------|------------------------------------------------------------------------------------------|-----|

| 6.12 | First ASIC design power dissipation report for a slow/slow corner VDD=0.81V,             |     |

|      | $T_j$ =125 °C                                                                            | 115 |

| 6.13 | Second ASIC design P&R summary reports                                                   | 115 |

|      |                                                                                          |     |

| 7.1  | Properties of the omnidirectional imaging system                                         | 120 |

| 7.2  | System Constraints to generate 30 fps 21.6 MP Omnidirectional Video. $\ \ldots \ \ldots$ | 122 |

| 7.3  | System Constraints to generate 9.5 fps 82.3 MP Omnidirectional Video                     | 122 |

| 7.4  | Comparison of the Giga-Eye with existing high-resolution omnidirectional                 |     |

|      | camera systems                                                                           | 129 |

| Δ 1  | PSNR comparison of the Kodak image set 19th image for different Bayer CFA                |     |

| Λ.1  |                                                                                          |     |

|      | interpolation methods                                                                    | 150 |

| A.2  | Resource usage of the different Bayer-to-RGB algorithms                                  | 150 |

| A.3  | Resource usage of the different AWB algorithms                                           | 153 |

| R 1  | Comparison for different serial communication interfaces                                 | 158 |

| 2.1  | comparison to amercia communication interfaces.                                          | 100 |

## 1 Introduction

In World War II, during the bloody Normandy landings, famous with the name D-day, number of lives lost was estimated as 10000. Today, each year, in 1 week that many people are dying because of bowel cancer. This means while you are reading these lines for a minute time interval, 1 person lost his/her life because of colon cancer. In last 50 years there are many efforts focused on offering new vision systems to have a better vision inside human body to solve such problems. For improving the detection rate of the cancer suspicious tissues, which are named as *Polyps*, large angle field of view (FOV) vision systems with smart vision capabilities are one of the key directions. Multiple aperture camera systems are one of the members of the vision systems family which offer large angle and smart vision features. Since they are not only providing large angle of view but also offering unique information by providing images from different view points, they are becoming alternative to the single camera large optic imaging systems.

During the last 50 years, miniaturization became a key element in human history since it opens doors for manufacturing new devices that enhance the quality of human life. Camera and imaging systems are following this miniaturization trend as well. Meanwhile, in the imaging domain, usage of multiple aperture camera systems are gaining significance in every aspects of daily life such as entertainment, surveillance, and medical imaging fields. Many works are focused on multiple camera panoramic and wide field of view imaging systems in industry and academia. As in every scientific development, nature is the first place to investigate for miniaturized multiple aperture vision as well. Insect vision is a magnificent example of multi-aperture wide angle of view imaging systems. There are many attempts to mimic the insect vision capabilities. Current multi-camera systems that are utilizing off-the-shelf components are big in scale and the miniaturization limits are not explored. On the other hand, the multi-aperture systems fabricated using micro-machining techniques, cannot meet high resolution requirements due to the micro-machining precision and optical limitations.

This thesis discloses a set of methods to enable development of miniaturized, multiple camera,

large angle of view imaging systems. A second target is to explore the smart vision capabilities of the proposed imaging system such as detection of objects boundaries by using multiple camera overlapping field of views. In the remaining of this chapter, recent developments in the field and the sources of inspiration for this work with some specific life problems are explained in brief.

### 1.1 Multi-camera panoramic imaging

Panoramic imaging with multiple cameras has become a trend in the recent years. There is a wide variety of multi-camera panoramic imaging systems used in different applications such as large area surveillance,  $360^{\circ}$  video capturing or telepresence. Examples for such kind of systems are: Ladybug5 camera from Pointgrey [1], which is a 6 camera system with a 197 mm diameter cylindrical case with 160 mm height. The system can provide  $2048 \times 2448 \ 360^{\circ} \times 162^{\circ}$  panoramic video stream at 10fps with 6 cameras of each 5 MP. Another recent system is from Nokia named as ozo [2],  $360^{\circ} \times 180^{\circ}$  full spherical camera with 8 2Kx2K resolution cameras. Another semi-panoramic camera is Panacast [3] from Altia systems, with around 10 cm diameter, 3 cameras giving an output of 4K resolution at  $180^{\circ} \times 54^{\circ}$  field of view (FOV). There are also different applications with spherical cameras for entertainment purposes like [4, 5]. In all these solutions dimensions are ranging from 60 mm-200 mm in diameter. They are bulky systems and designed for far field imaging, and they cannot be considered for the applications which need miniaturized panoramic imaging systems.

### 1.2 Miniaturized panoramic imaging

Miniaturization in general is the key trend for many years in different areas of interest in human life. Different aspects of miniaturization in different fields are driven by these trends and needs. In imaging and vision systems, with the interest in mobile applications, robotics and medical systems, the miniaturization concepts have been developed and improved in the last century.

In the field of robotics the recent developments of the drones bring new requirements for machine vision systems utilized in drone applications [10]. Since such flying vehicles are light-weight, power-limited systems and requires large FOV imaging, miniaturized panoramic imaging solutions are becoming crucial for such systems. Likewise, in the mobile phone and handheld-devices industry, there are many new systems attempted to add the panoramic imaging capabilities to the new generation mobile devices [11]. Again, the device sizes are becoming the key aspect in this area. Hence, there is a need for panoramic miniaturized imaging solutions in this field. Some of the example solutions from different providers to the applications in the drone and smart phone fields are illustrated in Fig.1.1.

In addition to the mentioned applications above there are also certain applications in the medical imaging field, which requires panoramic imaging. Colonoscopy and Laparoscopic

(b) The current solutions for panoramic imaging in smart phones

Figure 1.1 – Different areas of interest for panoramic miniaturized imaging systems (a)  $360^{\circ}$  drone from photosiphone company, image from [6] (b) different panoramic imaging solutions with wide angle optical systems, from GoPano [7], Kogeto [8], and the Bubblepix [9] companies from left to right.

surgery are very well defined applications as an example of these applications. In Laparoscopic or minimal invasive surgery (MIS) where an imaging device is inserted into human body trough a minimal hole, it is crucial to have miniaturized imaging and capability of large FOV to be able to see the whole surgery area. Therefore, the need for miniaturized panoramic imagery is a desired requirement. Current systems in MIS domain utilize relatively small field of view cameras and need movement of the imaging equipment during operation to see certain areas on the area of interest.

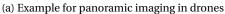

Each year, over six hundred thousand people lose their lives due to the colon cancer in the world [12], which means more than 10000 deaths per week in average. Even though the colonoscopy examination procedures are applied, there is a certain amount of miss rate in colonoscopy procedures due to narrow field of view (FOV) imagery employed in current systems. To illustrate the problem in colonoscopy, in Fig.1.2 a simplified sketch is represented for the problem of narrow field of view in the colonoscopy applications. Since the human colon has a folded structure, while the colonoscope moves toward the colon, it misses the behind-fold regions at the peripheral areas with respect to the forward and backward movement of the colonoscope.

In Table-1.1, a feature comparison of the current colonoscopy devices from different

Figure 1.2 – The problem of narrow field of view in colonoscopy applications.

companies, Olympus, Avantis, Endochoice, Naviaid and Giview is given. For example, the solutions from Endochoice [13] and Avantis [14] utilize 3 cameras and do not have a compound panoramic image which ends up with 3 separated windows. Hence it results in difficulty for the operator to follow the whole imaging area. Other solutions from Naviaid [15] and Giview [16], utilize parabolic-like mirror solutions. Their monolithic optical solution occupies the whole diameter of the colonoscopy device due to their size and does not allow any working channels, which is required to remove the polyps or make small operations during examination. A recent solution from Olympus [17] accommodates a forward large angle of view lens and a surrounding parabolic mirror. The solution has a large FOV reflected onto a single image sensor, which makes it limited to the single image sensor's resolution. Therefore, the works and attempts from different companies show that there is a certain need for wide FOV imaging in colonoscopy domain.

Table 1.1 – Current solutions for panoramic colonoscopy

| Company    | Solution         | #<br>cameras | FOV         | multi-camera<br>image processing | Main Drawbacks     |

|------------|------------------|--------------|-------------|----------------------------------|--------------------|

| Olympus    | large FOV optics | 1            | N/A         | no                               | single camera      |

| [17]       | large rov opties | <b>1</b>     | 11/71       | 110                              | limited resolution |

| Endochoice | multi-camera     | 3            | 330° × 330° | no                               | seperated windows  |

| [13]       |                  |              |             |                                  | hard to follow     |

| Avantis    | multi-camera     | 3            | 330° × 330° | no                               | seperated windows  |

| [14]       |                  |              |             |                                  | hard to follow     |

| Naviaid    | large FOV mirror | 1            | 180° × 180° | no                               | size doesn't allow |

| [15]       |                  |              |             |                                  | working channel    |

| Giview     | large FOV mirror | 1            | 180° × 180° | no                               | size doesn't allow |

| [16]       |                  |              |             |                                  | working channel    |

From the applications and needs from the real-world problems, the first question seeking for an immediate answer is how to have a wide FOV or (panoramic) imaging system, which has relatively high resolution in a limited volume that can fit into commercial applications like flying drones, smart phones and medical applications like colonoscopy and minimal invasive

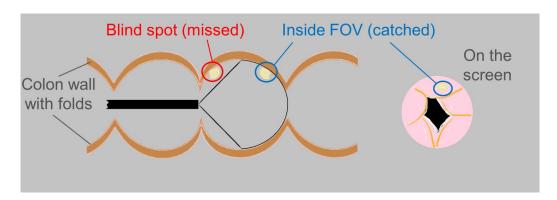

Figure 1.3 – Anatomy of an insect eye, image from [20]

surgery.

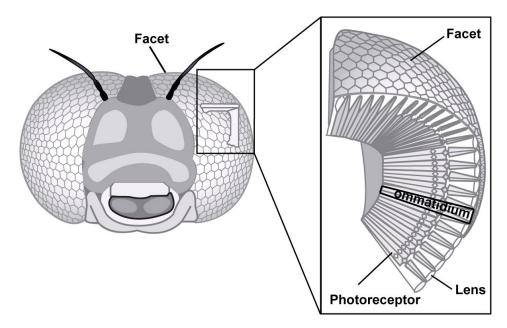

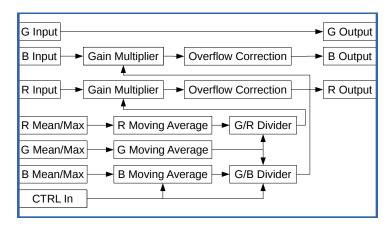

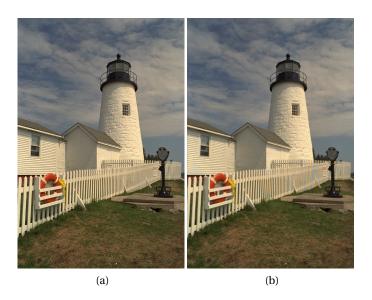

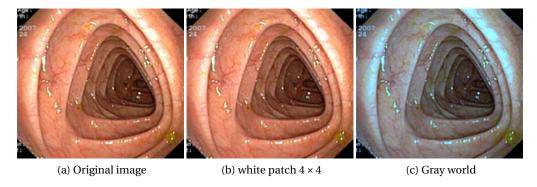

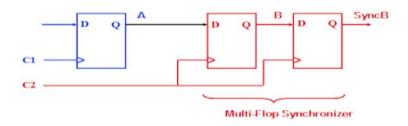

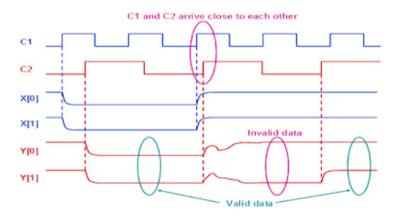

### 1.3 Insect Eyes