# Advanced Architectures and Processing for High-Efficiency Silicon Heterojunction Solar Cells

#### THÈSE Nº 6819 (2015)

PRÉSENTÉE LE 27 NOVEMBRE 2015

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR LABORATOIRE DE PHOTOVOLTAÏQUE ET COUCHES MINCES ÉLECTRONIQUES PROGRAMME DOCTORAL EN SCIENCE ET GÉNIE DES MATÉRIAUX

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

#### PAR

### Jonas GEISSBÜHLER

acceptée sur proposition du jury:

Prof. F. Nüesch, président du jury Prof. C. Ballif, Dr S. De Wolf, directeurs de thèse Prof. S. Glunz, rapporteur Dr D. Lachenal , rapporteur Prof. A. Tiwari, rapporteur

### Résumé

Les cellules solaires basées sur un substrat de silicium cristallin représentent de nos jours la majeure partie du marché du photovoltaïque. Afin de répondre à la demande croissante pour des dispositifs à plus haut rendement, la technologie dite des hétérojonctions silicium, basée sur une plaquette de silicium cristallin et sur de fines couches de silicium amorphes (a-Si:H) qui permettent la réalisation de contacts dits passivants, peut être considérée comme étant l'une des approches les plus prometteuse pour la prochaine génération de cellules photovoltaïques. Ces cellules solaires ont démontré des efficacités record rendues possible par la grande qualité de la passivation de surface conduisant à une tension de circuit ouvert proche des limites théoriques. Cependant, malgré de bonnes propriétés électroniques, les couches a-Si:H induisent d'importantes pertes optiques causées par la faible largeur de bande interdite de ce matériau. Le but de cette thèse est de limiter ces pertes en développant de nouvelles architectures de cellule et de nouveaux procédés de fabrication.

Les principaux résultats de ce travail se déclinent en quatre parties : Premièrement, une nouvelle structure découplant les propriétés optiques et électroniques des couches avants grâce à l'introduction de contacts localisés est étudiée. En utilisant une technique de masquage pour la structuration de ces couches, nous avons démontré la faisabilité d'une telle cellule si une surface de contact suffisamment importante est maintenue. Deuxièmement, en vue de la structuration des couches a-Si:H, nous avons développé un procédé d'attaque basé sur un plasma hydrogène dans un réacteur PECVD. En outre, nous avons démontré l'existence d'une épaisseur critique de la couche a-Si:H intrinsèque nécessaire afin de protéger l'interface amorphe/cristallin. Ainsi, cette technique permet la structuration de couche de a-Si:H avec une précision nanométrique tout en préservant la passivation de surface. Le troisième résultat important de cette thèse est le développement d'une métallisation à l'avant-habituellement réalisée par sérigraphie d'une pâte d'argent—par une électrode déposée par galvanoplastie de cuivre. Afin d'assurer une bonne adhésion de cette métallisation, un premier procédé basé sur une double couche de nickel et cuivre est étudié. D'importants gains optiques sont obtenus par ce biais grâce à la réduction de la taille des géométries de 70  $\mu$ m à 15  $\mu$ m conduisant à une amélioration du courant de court-circuit de 1.1 mA cm<sup>-2</sup>. Dans un deuxième temps, un procédé simplifié basé sur une couche d'accroche en cuivre est proposé et révèle une meilleure adhésion de la métallisation ainsi qu'une bonne compatibilité avec des oxydes transparents conducteurs (TCO) sensibles aux attaques chimiques tels que les matériaux basés sur l'oxyde de zinc. Le quatrième résultat notable de ce travail est le remplacement de la couche de a-Si:H dopée p formant le collecteur de trou par un film hautement transparent

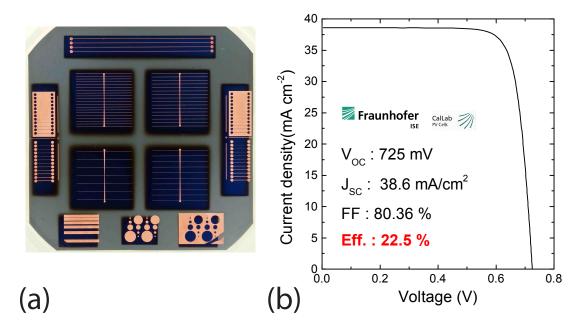

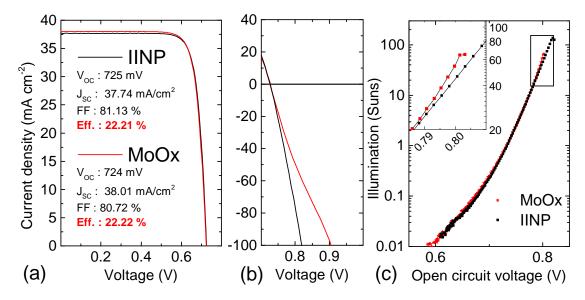

d'oxyde de molybdène  $(MoO_x)$ . Nous avons montré que ce matériau agit efficacement comme collecteur de trou si les procédés ultérieurs à sa déposition ne dépassent pas les 130°C. D'un point-de-vue optique, cette couche permet une amélioration équivalente à 0.8 mA cm $^{-2}$  de la réponse de la cellule dans la partie bleue du spectre solaire. Cependant, ce gain est réduit par la modification du  $MoO_x$  induite par la déposition du TCO conduisant à une absorption parasite de la lumière. Finalement, en combinant un collecteur de trou en  $MoO_x$  avec une métallisation à l'avant en cuivre électrodéposée, un impressionnant facteur de forme de la courbe courant-tension de 80.3% est obtenu permettant une efficacité certifiée de 22.5% pour une cellule de 4 cm $^2$ .

**Mots clefs :** cellule solaire en silicium, haute efficacité, hétérojonctions silicium, PECVD, sputtering, électrodéposition de cuivre, gravure par plasma d'hydrogène, oxyde de molybdène, oxyde transparent conducteur, transport de porteur de charge, silicium amorphe.

## **Abstract**

Crystalline silicon solar cells currently represent the largest part of the photovoltaic market. In response to the demand for higher efficiency devices, silicon heterojunction technology, which merges a crystalline silicon wafer with thin amorphous silicon (a-Si:H) films enabling the achievement of passivating contacts, may be considered as one of the most promising approaches for the next generation of industrial solar cells. These cells demonstrate record energy conversion efficiency enabled by excellent surface passivation leading to open-circuit voltages close to the theoretical limit. Despite the remarkable electronic properties of a-Si:H, its narrow bandgap induces significant parasitic light absorption. The aim of this thesis is to mitigate this loss through novel cell architectures and new fabrication processes.

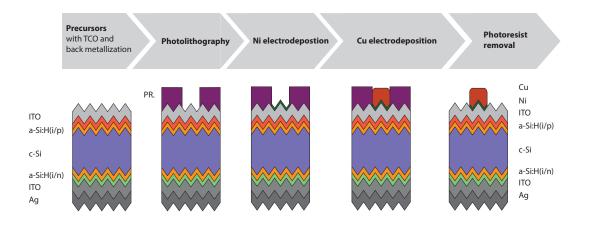

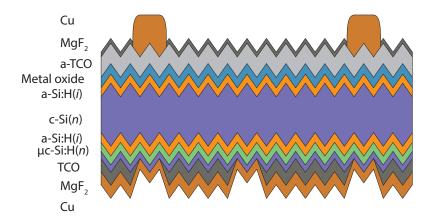

The outcome of this work is four-fold: First, a new silicon heterojunction solar cell structure is investigated that decouples the optical and electrical properties of the window layers through localized front contacts. By using shadow masking for the film patterning, we demonstrate the feasibility of the new cell structure under the condition that a sufficiently high contact coverage be maintained. Second, for the patterning of a-Si:H layers, we develop a hydrogen plasma etching technique carried out in a PECVD reactor. In particular, we show that a critical thickness of the intrinsic a-Si:H layer is needed to provide sufficient shielding of the amorphous/crystalline interface to ensure good passivation. This technique enables the patterning of a-Si:H layers with nanometric accuracy while preserving the surface passivation. A third important outcome of this thesis is the replacement of the front metallization—usually made by screen-printing of a silver paste—with a copper front grid formed by electrodeposition. To ensure sufficient adhesion of the metallic fingers, a first process based on a double electrodeposition of a nickel/copper stack is presented. Important improvements in light management are realized with this metallization scheme, reducing the finger width from 70  $\mu$ m to 15  $\mu$ m which leads to a short-circuit gain of 1.1 mA cm<sup>-2</sup>. In a second step, a simplified process based on a copper seed layer is proposed, further improving the metallization adhesion and making this technique compatible with chemically sensitive transparent conductive oxides such as zinc-oxide-based materials. The fourth outcome of this work is the replacement of the p-doped a-Si:H hole collector with a highly transparent molybdenum oxide  $(MoO_x)$  film. We show that this material is an efficient hole collector if the post-deposition processes are carried out below 130 °C. From an optical point of view, this layer enables an improvement equivalent to 0.8 mA cm<sup>-2</sup> of the cell's response in the blue part of the spectrum. Nevertheless, this gain is reduced by the modification of the MoO<sub>x</sub> film induced during the TCO sputtering process, which leads to broadband parasitic light absorption. Finally, by merging this  $MoO_x$

hole collector with the electrodeposited copper front metallization, remarkable fill factors of 80.3% are obtained leading to a certified efficiency of 22.5% for a  $4~\rm cm^2$  solar cell.

**Key words:** silicon solar cells, high-efficiency, silicon heterojunction, PECVD, sputtering, copper electrodeposition, hydrogen plasma etching, molybdenum oxide, transparent conductive oxide, charge carrier transport, amorphous silicon.

| Al | Abstract (Français/English) |         |                                                                |    |

|----|-----------------------------|---------|----------------------------------------------------------------|----|

| Ta | ıble o                      | of Cont | ents                                                           | ix |

| Li | st of                       | abbrev  | riations and symbols                                           | X  |

| 1  | Intr                        | oducti  | on                                                             | 1  |

|    | 1.1                         | Gene    | ral context                                                    | 1  |

|    |                             | 1.1.1   | Photovoltaics as a major contributor to electricity production | 1  |

|    |                             | 1.1.2   | Brief historical overview                                      | 2  |

|    |                             | 1.1.3   | Semiconductor physics in solar cells                           | 4  |

|    |                             | 1.1.4   | Fundamental operation of a solar cell                          | 8  |

|    |                             | 1.1.5   | Photovoltaic limitations                                       | 11 |

|    |                             | 1.1.6   | Overview of the technology                                     | 16 |

|    |                             | 1.1.7   | High-temperature crystalline silicon solar cell                | 16 |

|    |                             | 1.1.8   | Silicon heterojunction solar cells                             | 20 |

|    | 1.2                         | Motiv   | rations                                                        | 21 |

|    | 1.3                         | Objec   | ctives and structure                                           | 22 |

|    |                             | 1.3.1   | Objectives                                                     | 22 |

|    |                             | 1.3.2   | Structure                                                      | 23 |

|    | 1.4                         | Contr   | ibution to the field                                           | 23 |

| 2  | Exp                         | erime   | ntal processes and characterization                            | 25 |

|    | 2.1                         | SHJ b   | aseline process flow overview                                  | 25 |

|    | 2.2                         | Silico  | n heterojunction solar cell fabrication equipments             | 26 |

|    |                             | 2.2.1   | Wafer texturing and cleaning                                   | 26 |

|    |                             | 2.2.2   | Plasma-enhanced chemical vapor deposition                      | 26 |

|    |                             | 2.2.3   | Transparent conductive oxides and metal sputtering deposition  | 28 |

|    |                             | 2.2.4   | Zinc oxide low-pressure chemical vapor deposition              | 28 |

|    |                             | 2.2.5   | Metals and dielectrics thermal evaporation                     | 29 |

|    |                             | 2.2.6   | Silver paste screen-printing metallization                     | 29 |

|    |                             | 2.2.7   | Photolithography                                               | 29 |

|    | 2.3                         | Layer   | characterization                                               | 30 |

|    |                             | 231     | Line-sheet-and contact-resistance measurements                 | 30 |

|   |       | 2.3.2  | Spectroscopic ellipsometery                                                                        | 30 |

|---|-------|--------|----------------------------------------------------------------------------------------------------|----|

|   |       | 2.3.3  | Spectrophotometer                                                                                  | 31 |

|   | 2.4   | Solar  | cell characterization                                                                              | 31 |

|   |       | 2.4.1  | Minority-carrier lifetime measurement                                                              | 31 |

|   |       | 2.4.2  | Illuminated $J$ - $V$                                                                              | 32 |

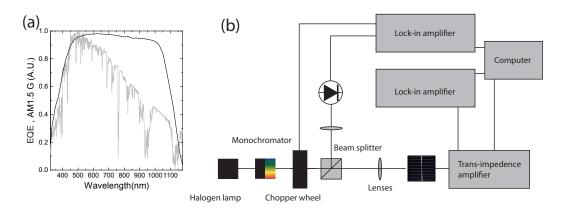

|   |       | 2.4.3  | External and internal quantum efficiency                                                           | 33 |

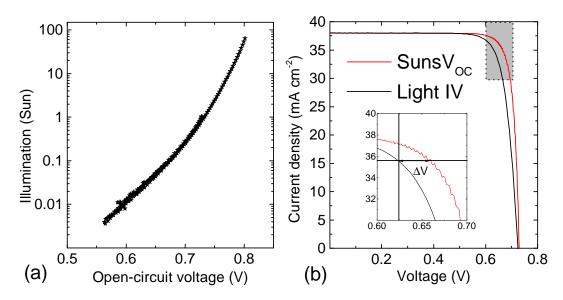

|   |       | 2.4.4  | SunsV <sub>OC</sub> measurement                                                                    | 35 |

|   |       | 2.4.5  | Photoluminescence                                                                                  | 35 |

| 3 | Silio | con He | terojunction solar cells front-metallization by copper electrodeposition                           | 37 |

|   | 3.1   | Introd | duction and motivation                                                                             | 37 |

|   |       | 3.1.1  | Motivation <sup>†</sup>                                                                            | 38 |

|   |       | 3.1.2  | State-of-the-art of Cu electrodeposition techniques for SHJ solar $\operatorname{cells}^\dagger$ . | 39 |

|   | 3.2   | Photo  | olithography processes for electrodeposition patterning                                            | 40 |

|   |       | 3.2.1  | Photoresist dispensing                                                                             | 41 |

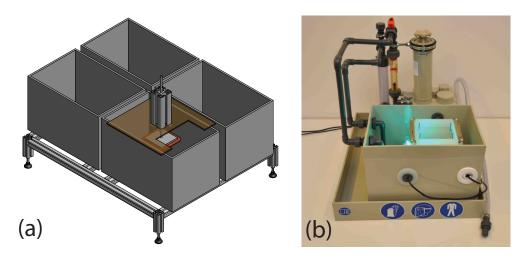

|   | 3.3   | Electr | odeposition setups                                                                                 | 42 |

|   | 3.4   | Nicke  | l-Copper front electrodes                                                                          | 43 |

|   |       | 3.4.1  | Experimental $^{\dagger}$                                                                          | 43 |

|   |       | 3.4.2  | Results and discussions $^{\dagger}$                                                               | 44 |

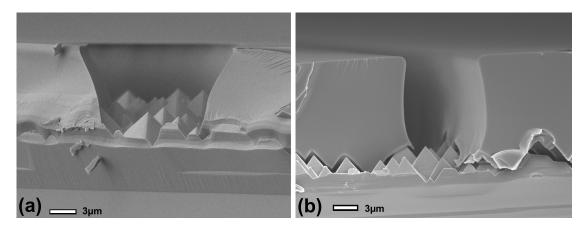

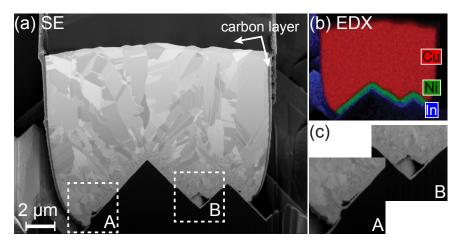

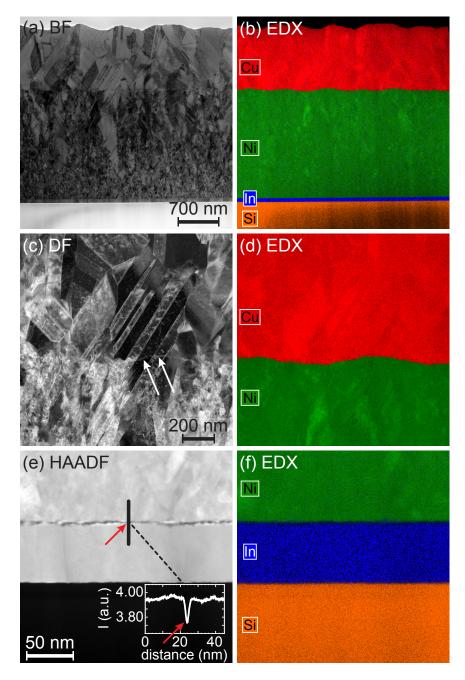

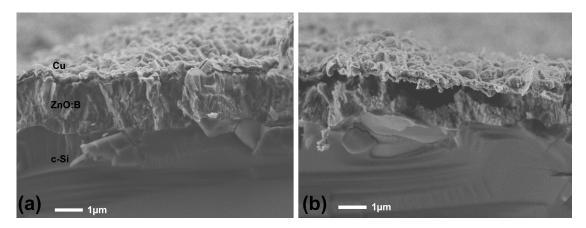

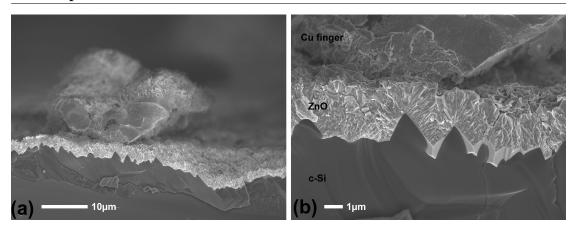

|   |       | 3.4.3  | Characterization of Ni-Cu metallization by electron microscopy $^{\dagger}  \dots $                | 48 |

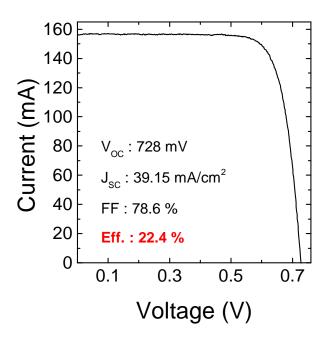

|   |       | 3.4.4  | Implementation in high-efficiency SHJ solar $\operatorname{cells}^{\dagger} \ldots \ldots$         | 50 |

|   |       | 3.4.5  | Conclusions <sup>†</sup>                                                                           | 52 |

|   | 3.5   | Towa   | rds more versatility and reliability in electrodeposited front-contact                             | 53 |

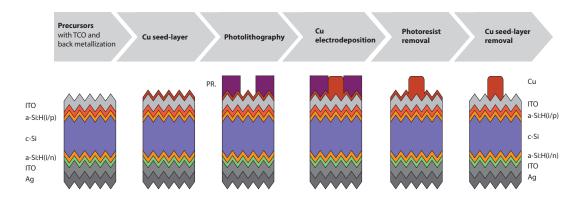

|   |       | 3.5.1  | Cu-seed layer based electrodeposition process                                                      | 53 |

|   |       | 3.5.2  | Cu seed-layer back-etching optimization                                                            | 53 |

|   |       | 3.5.3  | Impact of the Cu seed-layer removal on the a-Si:H surface passivation $$ .                         | 55 |

|   | 3.6   | Electr | rodeposited Cu front-grid on IZO front TCO                                                         | 55 |

|   |       | 3.6.1  | Motivation for IZO as the front-TCO                                                                | 55 |

|   |       | 3.6.2  | Experimental                                                                                       | 56 |

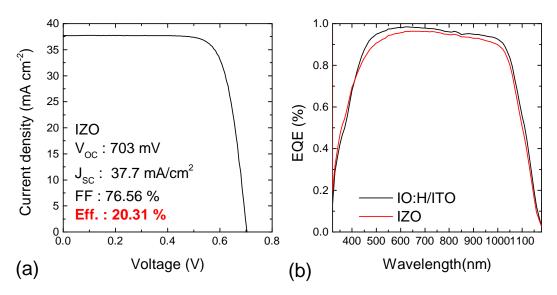

|   |       | 3.6.3  | Results and discussions                                                                            | 56 |

|   |       | 3.6.4  | Conclusions                                                                                        | 58 |

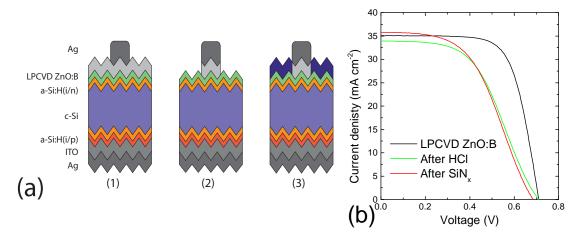

|   | 3.7   | Electr | rodeposited Cu front-grid on LPCVD ZnO:B front-TCO                                                 | 58 |

|   |       | 3.7.1  | Motivation                                                                                         | 58 |

|   |       | 3.7.2  | Experimental                                                                                       | 59 |

|   |       | 3.7.3  | Conclusion                                                                                         | 61 |

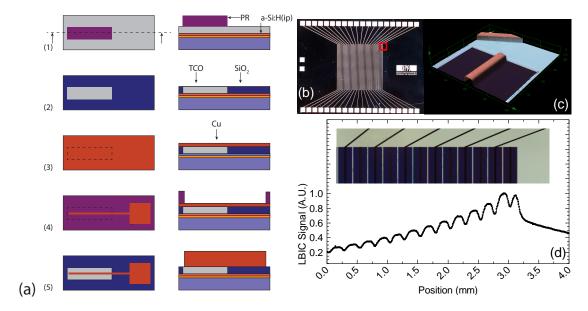

|   | 3.8   | Metal  | lization of interdigitated back-contacted silicon heterojunction solar cells                       | 62 |

|   |       | 3.8.1  | Motivation                                                                                         | 62 |

|   |       | 3.8.2  | Results and discussion                                                                             | 63 |

|   |       | 3.8.3  | Conclusion                                                                                         | 63 |

|   | 3.9   | Gener  | ral conclusions on metallization by copper electroplating                                          | 63 |

| 4                                                                                 | Patt | terning | g amorphous silicon layers by hydrogen plasma and wet chemical etching                       | 65 |

|-----------------------------------------------------------------------------------|------|---------|----------------------------------------------------------------------------------------------|----|

|                                                                                   | 4.1  | Intro   | luction and motivation                                                                       | 65 |

|                                                                                   | 4.2  | a-Si:F  | I patterning by wet chemical etching                                                         | 68 |

|                                                                                   |      | 4.2.1   | Introduction                                                                                 | 68 |

|                                                                                   |      | 4.2.2   | Experimental                                                                                 | 68 |

|                                                                                   |      | 4.2.3   | Results and discussions                                                                      | 68 |

|                                                                                   |      | 4.2.4   | Conclusions                                                                                  | 69 |

| 4.3 Selective etching of doped a-Si:H layers by $H_2$ plasma etching <sup>†</sup> |      |         |                                                                                              | 70 |

|                                                                                   |      | 4.3.1   | Introduction <sup>†</sup>                                                                    | 70 |

|                                                                                   |      | 4.3.2   | Experimental <sup>†</sup>                                                                    | 71 |

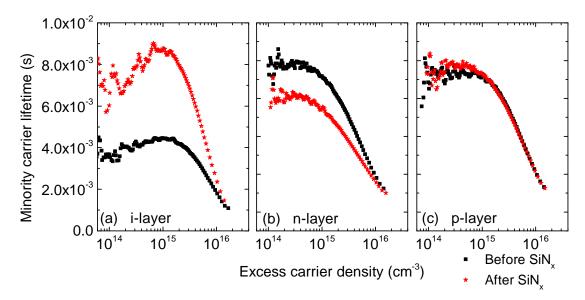

|                                                                                   |      | 4.3.3   | Effect of hydrogen plasma on surface passivation $^{\dagger}$                                | 71 |

|                                                                                   |      | 4.3.4   | High resolution transmission electron microscopy investigation of the                        |    |

|                                                                                   |      |         | a-Si:H/c-Si interface <sup>†</sup>                                                           | 73 |

|                                                                                   |      | 4.3.5   | Study of a-Si:H film microstructure by attenuated total reflectance Fourier                  |    |

|                                                                                   |      |         | transform infrared spectroscopy $^{\dagger}$                                                 | 74 |

|                                                                                   |      | 4.3.6   | Study of hydrogen incorporation in a-Si:H films by H <sub>2</sub> and D <sub>2</sub> thermal |    |

|                                                                                   |      |         | desorption spectroscopy $^{\dagger}$                                                         | 76 |

|                                                                                   |      | 4.3.7   | Conclusions <sup>†</sup>                                                                     | 76 |

|                                                                                   | 4.4  | Influe  | ence of H <sub>2</sub> plasma etching on SHJ device performance                              | 77 |

|                                                                                   |      | 4.4.1   | Introduction                                                                                 | 77 |

|                                                                                   |      | 4.4.2   | Study of charge-carrier transport in a-Si: $H(i)$ layers exposed to $H_2$ plasma             |    |

|                                                                                   |      |         | etching                                                                                      | 78 |

|                                                                                   |      | 4.4.3   | Doped a-Si:H layer patterning by H <sub>2</sub> plasma etching on wafers with ran-           |    |

|                                                                                   |      |         | dom pyramids texture                                                                         | 79 |

|                                                                                   |      |         | Conclusion                                                                                   | 79 |

|                                                                                   | 4.5  | Gene    | ral conclusions on a-Si:H film patterning                                                    | 80 |

| 5                                                                                 | Loc  | alized  | front contact silicon heterojunction solar cells                                             | 83 |

|                                                                                   |      |         | luction                                                                                      | 84 |

|                                                                                   |      | 5.1.1   | Motivations                                                                                  | 84 |

|                                                                                   |      | 5.1.2   | Localized contacts in SHJ devices                                                            | 85 |

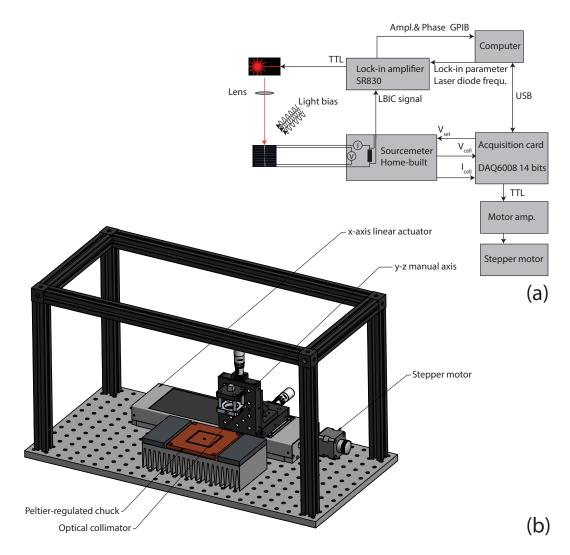

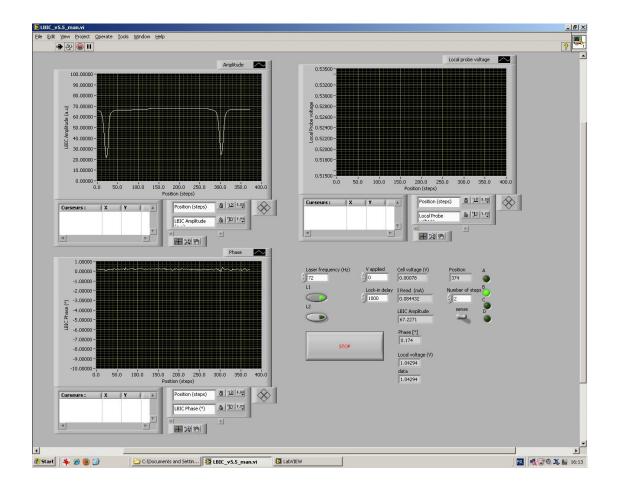

|                                                                                   | 5.2  |         | -beam-induced current measurement setup                                                      | 86 |

|                                                                                   |      | 5.2.1   | Introduction                                                                                 | 86 |

|                                                                                   |      | 5.2.2   | Experimental setup                                                                           | 86 |

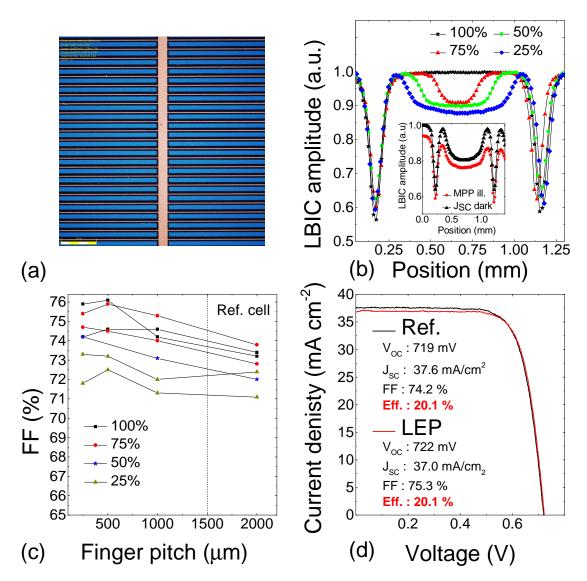

|                                                                                   | 5.3  | LEP d   | evices with a patterned front TCO                                                            | 88 |

|                                                                                   |      | 5.3.1   | Introduction                                                                                 | 88 |

|                                                                                   |      | 5.3.2   | Experimental                                                                                 | 88 |

|                                                                                   |      | 5.3.3   | Results and discussion                                                                       | 89 |

|                                                                                   |      | 5.3.4   | Conclusions                                                                                  | 91 |

|                                                                                   | 5.4  | Rear l  | nole collector configuration                                                                 | 91 |

|                                                                                   |      | 5.4.1   | Motivation                                                                                   | 91 |

|                                                                                   |      | 5.4.2   | Experimental                                                                                 | 92 |

|   |      | 5.4.3   | Results and discussion                                                                                 | 92  |

|---|------|---------|--------------------------------------------------------------------------------------------------------|-----|

|   |      | 5.4.4   | Conclusions                                                                                            | 93  |

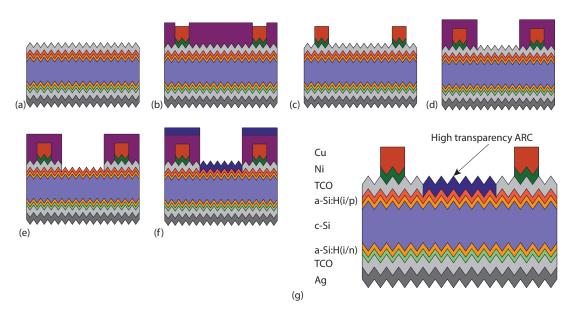

|   | 5.5  | LEP d   | evices with a patterned front a-Si:H layer                                                             | 94  |

|   |      | 5.5.1   | Introduction                                                                                           | 94  |

|   |      | 5.5.2   | Experiments                                                                                            | 95  |

|   |      | 5.5.3   | Results and discussion                                                                                 | 95  |

|   |      | 5.5.4   | Electrical model and simulations                                                                       | 97  |

|   |      | 5.5.5   | Conclusions                                                                                            | 99  |

|   | 5.6  | Low-c   | contact-coverage LEP devices                                                                           | 100 |

|   |      | 5.6.1   | Self-masked ZnO etching                                                                                | 101 |

|   |      | 5.6.2   | Impact of silicon nitride deposition on surface passivation $\ \ldots \ \ldots$                        | 101 |

|   |      | 5.6.3   | Conclusions                                                                                            | 102 |

|   | 5.7  | Modu    | lar LEP devices                                                                                        | 103 |

|   |      | 5.7.1   | Experimental                                                                                           | 103 |

|   |      | 5.7.2   | Results and discussion                                                                                 | 103 |

|   |      | 5.7.3   | Conclusions                                                                                            | 104 |

|   | 5.8  | Gener   | al conclusions on LEP-SHJ devices                                                                      | 104 |

| 6 | Trar | ncition | metal oxide films as a-Si: $H(p)$ replacement                                                          | 107 |

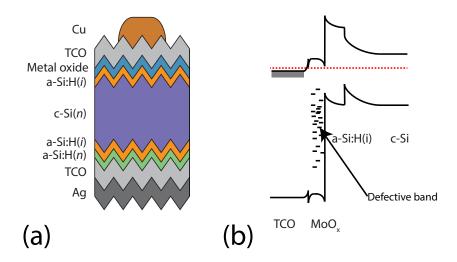

| Ū | 6.1  |         | luction and motivation                                                                                 |     |

|   | 0.1  | 6.1.1   |                                                                                                        |     |

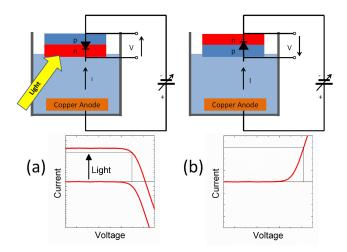

|   |      |         | Band diagram and carrier extraction in TMO-based hole-collector SHJ                                    | 100 |

|   |      | 0.1.2   | solar cells                                                                                            | 108 |

|   | 6.2  | Exper   | imental                                                                                                | 109 |

|   | 6.3  |         | al properties and films microstructure of $MoO_x$ -based hole-collector                                | 110 |

|   |      | 6.3.1   | Annealing and TCO sputtering impact on $MoO_x$ optical properties <sup>†</sup>                         | 110 |

|   |      | 6.3.2   | Impact of plasma treatments on TMO thin films                                                          |     |

|   |      | 6.3.3   | Molybdenum oxide film microstructure and interfaces <sup>†</sup>                                       | 113 |

|   | 6.4  | Surfac  | be passivation of a-Si:H( $i$ )/ MoO <sub>x</sub> hole collector and impact of annealing .             | 115 |

|   |      |         | Annealing impact on un-capped $MoO_x$ hole collector $^{\dagger}$                                      |     |

|   |      |         | Annealing impact on TCO-capped $MoO_x$ hole collector                                                  |     |

|   |      | 6.4.3   | Annealing impact on the open-circuit voltage                                                           | 117 |

|   | 6.5  | Molyb   | odenum oxide based SHJ solar cells                                                                     | 117 |

|   |      | 6.5.1   | Impact of the annealing on the device performance $^{\dagger}$                                         | 117 |

|   |      | 6.5.2   | Impact of a-Si:H( $i$ ) layer thickness on hole collection in MoO <sub><math>x</math></sub> -based SHJ |     |

|   |      |         | solar cells                                                                                            | 118 |

|   |      | 6.5.3   | Comparison of $MoO_x$ - and a-Si: $H(p)$ -based SHJ device performance <sup>†</sup>                    | 119 |

|   |      | 6.5.4   | Temperature dependence of the efficiency for $MoO_x$ -based SHJ devices                                | 120 |

|   | 6.6  | Altern  | native TCOs for $MoO_x$ hole collector                                                                 | 121 |

|   |      | 6.6.1   | LPCVD ZnO:B as $MoO_x$ hole-collector contact                                                          | 121 |

|   |      |         |                                                                                                        | 123 |

|   |      | 6.6.2   | Sputtered IZO as $MoO_x$ hole collector contact                                                        | 123 |

|   | 6.7  |         | FF and -efficiency Molybdenum oxide-based devices $\dots$                                              |     |

|    |       |         | Con                                                           | tents |

|----|-------|---------|---------------------------------------------------------------|-------|

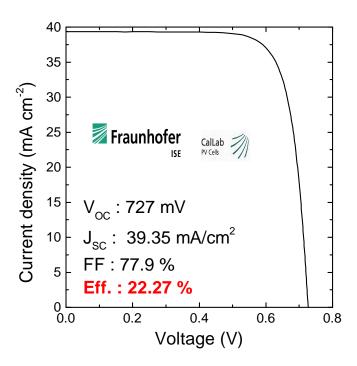

|    |       | 6.7.1   | 22.5% certified efficiency $MoO_x$ solar $cell^{\dagger}$     | 124   |

|    |       | 6.7.2   | <i>J-V</i> curve behavior in forward polarization             | 126   |

|    | 6.8   | Gene    | ral conclusions metal oxide films as a-Si:H $(p)$ replacement | 126   |

| 7  | Con   | clusio  | ns and perspectives                                           | 129   |

|    | 7.1   | Concl   | lusions                                                       | 129   |

|    |       | 7.1.1   | Device architecture performance summary                       | 130   |

|    |       | 7.1.2   | Light management                                              | 131   |

|    |       | 7.1.3   | Electrical performance                                        | 131   |

|    |       | 7.1.4   | Manufacturing and industrialization                           | 132   |

|    | 7.2   | Persp   | ectives                                                       | 133   |

|    |       | 7.2.1   | Standard SHJ devices                                          | 133   |

|    |       | 7.2.2   | Electrodeposited metal front grid                             | 133   |

|    |       | 7.2.3   | LEP-SHJ architecture                                          | 134   |

|    |       | 7.2.4   | TMO-based SHJ solar cells                                     | 134   |

|    |       | 7.2.5   | High-efficiency SHJ solar cell suggestion                     | 135   |

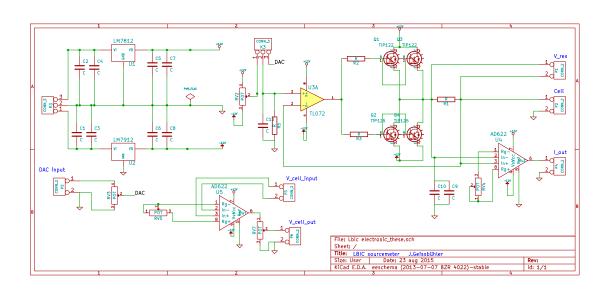

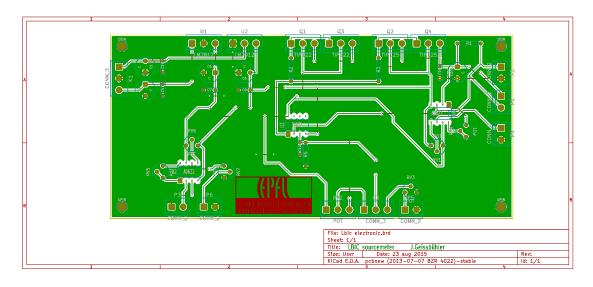

| A  | LBI   | C circu | it diagram and software                                       | 141   |

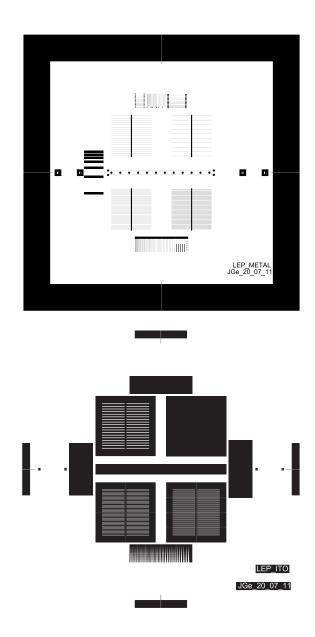

| В  | LEP   | -SHJ p  | hotolithography masks                                         | 143   |

| Bi | bliog | graphy  |                                                               | 166   |

| Re | mer   | ciemeı  | nts                                                           | 167   |

**Curriculum Vitae**

169

## List of abbreviations and symbols

#### Semiconductor

n Electron density

p Hole density

$\Delta_n$  Excess electron density  $\Delta_p$  Excess hole density

$S_{eff}$  Effective surface recombination velocity

$\mathbf{E}_f$  Fermi level WF Work function

FCA Free carrier absorption

$au_{ ext{eff}}$  Effective minority carrier lifetime

$E_{\rm g}$  Bandgap

#### Materials and depositions

TCO Transparent conductive oxide ZnO:B Boron-doped zinc oxide

ITO Indium tin oxide

IO:H Hydrogenated indium oxide

IZO Indium- zinc-oxide

PR Photoresist

TMOTransition metal oxide $MoO_x$ Molybdenum oxide $WO_x$ Tungsten oxide $NiO_x$ Nickel oxide $VO_x$ Vanadium oxide

a-Si:H Hydrogenated amorphous silicon

a-Si:H(i) Intrinsic hydrogenated amorphous silicon a-Si:H(n) n-doped hydrogenated amorphous silicon a-Si:H(p) p-doped hydrogenated amorphous silicon  $\mu$ c-Si:H Hydrogenated microcrystalline silicon

c-Si Crystalline silicon

PECVD Plasma enhanced chemical vapor deposition

LPCVD Low pressure chemical vapor deposition

LIP Light induced plating

#### Characterizations and cells

$\eta$  Energy conversion efficiency

FF Fill-factor

J<sub>sc</sub> Short-circuit-current density

$V_{\rm oc}$  Open-circuit voltage

J-V Current-voltage measurement

J Current density

MPP Maximum power point

$R_s$  Series resistance

$ho_c$  Specific contact resistivity EQE External quantum efficiency IQE Internal quantum efficiency

PL Photoluminence

LBIC Light beam induced current SE Spectroscopic ellipsometery

ATR-FTIR Attenuated total reflectance Fourier transform infrared spectroscopy

TDS Thermal desorption spectroscopy

TLM Transfer length method

SEM Scanning electron microscopy

TEM Transmission electron microscopy

HR-TEM High resolution transmission electron microscopy

SHJ Silicon heterojunction

FHC Front hole collector

RHC Rear hole collector

LEP-SHJ Localized extraction and passivated SHJ cell

IBC Interdigitated back-contact

## 1 Introduction

#### 1.1 General context

#### 1.1.1 Photovoltaics as a major contributor to electricity production

Energy is now one of the main challenges of our societies due to our constantly increasing demand. Between 1973 and 2012, the world total primary energy supply increased from 6.1 to 13.4 billion of tons of equivalent oil. Among this energy, 18.1% of the total final energy world consumption is consumed as electricity. [IEA 2014a] Importantly, a major part of this electricity is produced from non-renewable energy sources such as oil, natural gas, coal and nuclear. As a direct consequence of the use of fossil fuels, a massive quantity of  $CO_2$  estimated at 31.7 billion tons are released each year into Earth's atmosphere with a catastrophic impact on the climate. [IEA 2014a] Although, the production of electricity from nuclear plants releases less  $CO_2$  than other non-renewable energy sources, the danger posed by plant failures and the disposal of the waste raise the question of using this technology to produce electricity. Moreover, all these non-renewable energy sources rely on fuels available only in some specific parts of the world. It is therefore of primary importance to ensure the sustainability of our economies by modifying our energy sources, giving preference to renewables such as hydro-, wind- or solar-generation.

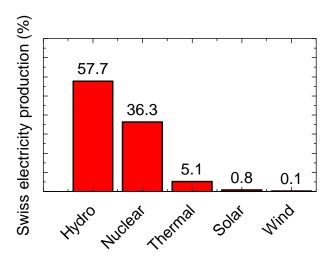

In Switzerland, the current market share between the different energy sources is shown in Fig. 1.1. It can be seen that nuclear electricity accounts for more than 36% of our electricity production. [OFEN 2014] After the nuclear disasters that happened in Three Mile Island, Chernobyl and more recently Fukushima, the Swiss government decided in 2011 to progressively abandon nuclear as an electricity production source. [Admin 2011] In this perspective, the new energy strategy of Switzerland towards 2050 is based on several aspects such as: i) lowering the overall energy consumption, ii) implementation of "smart-grid" electricity networks allowing a more clever usage of the electricity, iii) development of hydroelectricity and new renewable energy sources such as wind turbines and solar panels and iv) strengthening of the scientific research to achieve these goals. [Admin 2011].

Figure 1.1: Production of the Swiss electricity in 2014. Data from [OFEN 2014]

Even though this challenge may seem difficult to overcome, an example of rapid growth of the solar market was given by Germany where during the 2007–2012 period, photovoltaics' share of the market grew from 0.5% to 6% demonstrating the feasibility of a rapid and radical change in our methods to produce electricity. [Bundesministerium 2014]

#### 1.1.2 Brief historical overview

The first demonstration of the photovoltaic effect was made in 1839 by the French physicist Edmond Becquerel. In his experiment, electricity was generated when noble metal electrodes dipped into an acidic solution were exposed to sunlight. This experiment was the first demonstration of the direct conversion of light into electricity. [Green 1990a] Several decades after Becquerel's discovery, important findings were made by scientists working on the photoconductivity of selenium. In 1883, Charles Fritts realized a solar cell made of a selenium absorber sandwiched in between a gold and a brass electrode forming two Schottky contacts. [Green 1990a] [Nelson 2003]

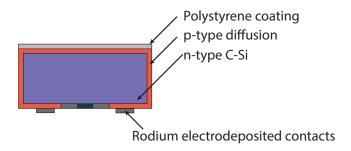

Figure 1.2: Schematic of the 1954 Bell Labs solar cell developed by Chapin, Pearson and Fuller. Schematic made from [Chapin 1957].

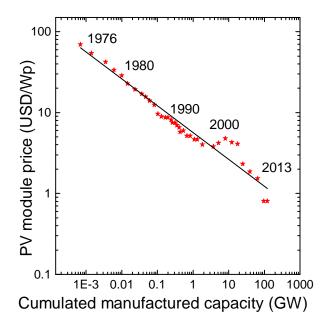

Figure 1.3: Learning curve of the PV module price as a function of the cumulative manufacturing capacity. Data from [IEA 2014b] [ITRPV 2015].

The "birth" of the silicon photovoltaic device as it is known nowadays happened in 1954 at Bell Laboratories. Chapin, Pearson and Fuller realized a revolutionary device based on a p-n junction made by boron diffusion in an n-type silicon wafer. [Chapin 1954] Figure 1.2 shows schematically the structure of this solar cell. Interestingly, this device already featured numerous concepts of advanced solar cells which were developed several decades later as for instance the use of an n-type silicon wafer, a fully back-contacted structure, an emitter wrap-around and electrodeposited contacts (see section 1.1.6). Even more remarkably, Chapin et al. reported in their 1954 paper that the solar cell energy-conversion efficiency is limited by recombination of charge carriers, light coupling into the absorber and ohmic losses. [Chapin 1954] More than 60 years later, these limitations are still the center of interest of photovoltaic research. Despite an impressive energy-conversion efficiency of 6% for this pioneer solar cell, its commercial interest was limited due to its high manufacturing cost. As a consequence, the main development of this technology during the next decades was restricted to space applications. [De Wolf 2012] In fact, due to the process complexity and especially the difficulty to purify silicon at a large scale, the price of a solar module was \$70 per Watt peak (Wp) in 1978, 24 years after the discovery of Chapin, Pearson an Fuller. However, the technology improvements made after the late 70s enabled the prices of solar energy to fall following a well-established learning curve as seen in Fig.1.3. [Swanson 2006] This learning curve implies that the photovoltaic production cost is reduced by 20% each time the production capacity is doubled. [ITRPV 2015] Nowadays, the cumulative shipped PV module power is estimated to be  $\approx$  184 GWp with an average PV module price of 0.62 \$/Wp in 2014. [ITRPV 2015] [IEA 2014b]

#### 1.1.3 Semiconductor physics in solar cells

In this section, we review the main semiconductor physics relevant for the understanding of the solar cell operation.

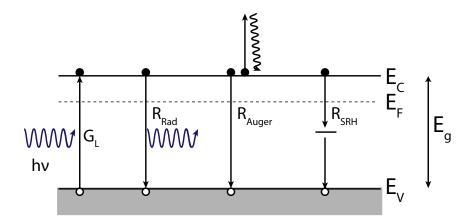

**Generation in semiconductors** Figure 1.4 shows the generation of an electron-hole pair which takes place into a semiconductor material with a bandgap  $E_{\rm g}$ . In this process, an electron leaves the valence band to reach the conduction band. To reach the conduction band, the electron must acquire at least the energy equivalent to  $E_{\rm g}$ . This electron-hole pair generation can be induced either by thermal excitation or by absorption of a photon with an energy  $hv \geq E_{\rm g}$ . The excess energy  $hv - E_{\rm g}$  is thermally lost in the semiconductor. We note here that this photogeneration process is extremely efficient in *direct* bandgap semiconductor material—direct transition from the valence to the conduction band such as in gallium arsenide or indium phosphide—compared to *indirect* bandgap semiconductor material—indirect transition requiring a phonon such as in silicon—which requires a thicker absorber. [Sze 2001] [Green 1982] At thermal equilibrium, the electron and hole density  $n_0$  and  $p_0$  can be expressed as:

$$n_0 = N_c e^{\frac{E_f - E_c}{kT}}$$

$p_0 = N_v e^{\frac{E_v - E_f}{kT}}$  (1.1)

where  $E_f$ ,  $E_v$  and  $E_c$  are the Fermi energy, the valence band and the conduction band energy and  $N_v$  and  $N_c$  are the effective density of states in the valence band and the conduction band respectively. k is the Boltzmann constant and T is the temperature of the semiconductor.

As photogeneration leads to excess carrier concentration  $\Delta_n = \Delta_p$ , Eq. 1.1 can be rewritten as:

$$n = \Delta_n + n_0 = n = N_c e^{\frac{E_{fn} - E_c}{kT}} = n_0 e^{\frac{q\phi_n}{kT}}$$

$$p = \Delta_p + p_0 = n = N_v e^{\frac{E_v - E_{fp}}{kT}} = p_0 e^{\frac{q\phi_p}{kT}}$$

(1.2)

where  $E_{fn}$  and  $E_{fp}$  are the *quasi-Fermi levels* and  $\phi_{n,p}$  represent their deviation from  $E_f$ . The splitting of these quasi-Fermi levels can be directly linked to an implied potential:

$$iV = \phi_p - \phi_n = \frac{kT}{q} ln \left( \frac{(n_0 + \Delta n)(p_0 + \Delta n)}{n_i^2} \right)$$

(1.3)

Figure 1.4: Generation and recombination processes occurring in a semiconductor.

**Bulk recombination in semiconductors** Recombination is the inverse process of generation where an electron falls from the conduction band to the valence band. In the bulk of a semiconductor, we can distinguish three recombination processes as shown in Fig. 1.4. [Sze 2001]

• Radiative recombination is the exact inverse of the photogeneration previously described. Here, the electron falls from the conduction band to the valence band and a photon with an energy  $E_{\rm g}$  is generated. The probability that this process happens is higher in direct bandgap material than in indirect bandgap material as the minimum and the maximum of the conduction and valence band are aligned and no phonon is required. The radiative recombination rate is given by Eq.1.4, where B is a constant depending of the material: [Green 1982]

$$U_{Rad} = B(np - n_i^2) \tag{1.4}$$

• Auger recombination is a three-particle process where an electron recombines with a hole and transfers its energy to another electron which then thermalizes as shown in Fig. 1.4. Equivalently, this process can happen with a hole transferring its energy to a second hole. The Auger recombination rate is given by: [De Wolf 2005]

$$U_{Auger} = C_n(n^2p - n_0^2p_0) + C_p(np^2 - n_0p_0^2)$$

(1.5)

• **Recombination through traps** is a two-step process in which an electron first reaches a defect state located in the bandgap and then reaches the valence band. The recombi-

nation rate is expressed by the Shockley-Read-Hall formalism: [Sze 2001]

$$U_{SRH} = \frac{v_{th}N_{t}(np - n_{i}^{2})}{\frac{1}{\sigma_{p}}(n + n_{i}e^{\frac{E_{i} - E_{t}}{kT}}) + \frac{1}{\sigma_{n}}(p + p_{i}e^{\frac{E_{t} - E_{i}}{kT}})}$$

(1.6)

where  $\sigma_{n,p}$  are the capture cross section of the trap,  $N_t$  is the trap density,  $E_t$  is the energy level of the trap and  $v_{th}$  is the thermal velocity.

From these recombination rates, we can associate a carrier lifetime  $\tau_{n,p}$  reflecting the average time before a charge carrier recombines:

$$U \equiv \frac{\Delta_n}{\tau_n} \Rightarrow \frac{1}{\tau_n} \equiv \Delta_n U \tag{1.7}$$

Since recombination rates are additive, the three recombination mechanisms yield a bulk lifetime expressed as [Nelson 2003]

$$\frac{1}{\tau_{n \ bulk}} = \frac{1}{\tau_{n \ Rad}} + \frac{1}{\tau_{n \ Auger}} + \frac{1}{\tau_{n \ SRH}}$$

$$\tag{1.8}$$

**Surface recombination** In addition to the recombination taking place into the bulk of the semiconductor, recombination can also happen at the surface of semiconductor due to the discontinuity of the lattice (i.e. dangling bonds) introducing surface energy states. The surface recombination rate is given by :

$$U_s \equiv S\Delta_n|_{surf} \tag{1.9}$$

Where S is the surface recombination velocity. However, due to the bands bending in the surface vicinity, an effective surface recombination velocity  $S_{eff}$  can be defined from the recombination rate and the excess carrier density at a distance d from the surface where the bands are flat:

$$S_{eff} \equiv \frac{U_{x=d}}{\Delta n_{x=d}} \tag{1.10}$$

where  $S_{\it eff}$  typically ranges between  $10^7~{\rm cm}~{\rm s}^{-1}$  for a direct metal/silicon contact down to

< 10 cm s $^{-1}$  for a passivated silicon surface. [Cuevas 1996] [Olibet 2007] [Hoex 2006] If S $_{eff}$  is sufficiently small, the *effective* carrier lifetime  $\tau_{eff}$  taking into account the bulk and the surface recombinations can be expressed as: [Schroder 2006]

$$\frac{1}{\tau_{eff}} = \frac{1}{\tau_{bulk}} + \frac{2S_{eff}}{w} \tag{1.11}$$

where, w is the wafer thickness. We can note here that good surface passivation (i.e small a  $S_{eff}$  value) is of extreme importance in the case of thin wafers. Importantly, two ways can be used to maximize  $\tau_{eff}$  by lowering the surface recombination. First, the surface recombination centre density can be lowered by *chemically* passivating the dangling bonds at the wafer surface. This can be achieved for instance by linking hydrogen atoms to the dangling bonds or by growing a thermal oxide that will terminate the dangling bonds. [Olibet 2007] [Kerr 2002a] The second approach is to reduce the minority-carrier concentration at the surface. This can be achieved either by doping the region close to the surface or by placing a material with trapped charges creating an electrical field (as for instance silicon nitride (SiN $_x$ ) for positive trapped charges or aluminium oxide (Al $_2$ O $_3$ ) for negative trapped charges). [Green 1982]

**Charge-carrier transport in semiconductors** Two charge-carrier transport mechanisms are important in solar cells: [Wurfel 2015]

• The drift transport where an electrical field  $\epsilon$  acts on the charge carriers. The current density is given by

$$J_{drift n} = q\mu_n n\epsilon \qquad J_{drift p} = q\mu_p p\epsilon \qquad (1.12)$$

• **The diffusion transport** where carriers flow from the region where their concentration is the highest towards a region with a weaker concentration. The diffusion current density is given by the Fick's law:

$$J_{diff n} = D_n \frac{dn}{dx} \qquad J_{diff p} = D_p \frac{dp}{dx} \qquad D_{n,p} = \frac{kT}{q} \mu_{n,p} \quad (1.13)$$

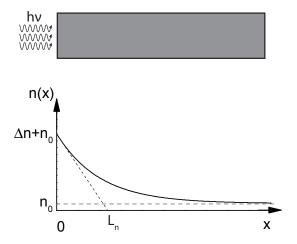

Importantly, due to the finite lifetime of minority carriers, the length that a minority carrier can diffuse before recombining is as well finite. Figure 1.5 shows an example of how the minority-carrier concentration decays exponentially in a p-type semiconductor when generation occurs exclusively at the surface. Eq. 1.14 expresses the minority-carrier concentration profile at

Figure 1.5: P-type semiconductor rod with generation occurring only at the surfaces and associated minority-carrier profile. Figure made from [Sze 2001]

steady state where the characteristic length  $L_n$  is called the *diffusion length* and corresponds to the average length that a minority carrier can travel. [Sze 2001]

$$n(x) = n_0 + \Delta_n e^{\frac{-x}{\sqrt{D_n \tau_{eff n}}}} \qquad L_n = \sqrt{D_n \tau_{eff n}}$$

(1.14)

When both drift and diffusion take place in the semiconductor, the total current is given by the sum of both contributions (expressed here for the electrons):

$$J_{tot\ n} = J_{drift\ n} + J_{diff\ n} = q\mu_n n\epsilon + D_n \frac{dn}{dx} \qquad \qquad D_n = \frac{kT}{q}\mu_n$$

(1.15)

An equivalent way to express the forces acting on charge carriers leading to their transport is to refer to the gradient of their quasi-Fermi levels. Equation 1.15 can be rewritten as [Wurfel 2015]

$$J_{tot\ n} = \mu_n n \frac{d}{dx} E_{Fc} \qquad J_{tot\ p} = \mu_p p \frac{d}{dx} E_{Fv}$$

(1.16)

#### 1.1.4 Fundamental operation of a solar cell

A photovoltaic device can be divided into two distinct parts:

• The absorber, which converts the incident photons into electron-hole pairs. After their

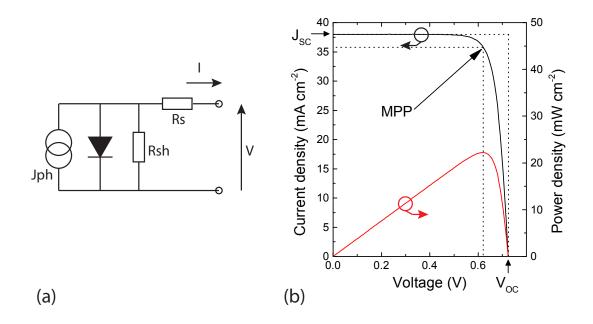

Figure 1.6: (a) Electrical equivalent circuit of the one-diode model of a solar cell (b) Light J-V curve and power-density curve.

generation, charge carriers are transported according to Eq. 1.16 towards their respective contacts. [Demaurex 2014b]

• Two contacts, (one for electron, one for hole), which selectively extract one kind of charge carrier. [Cuevas 2013]

One of the most obvious structures to make the latter in silicon is to form a p-n junction. By doing this the p-side will have a significantly higher conductivity for holes than for electrons, which consequently creates a selective hole contact, and the inverse in the case for the electron collector. [Wurfel 2015].

Insight into how the current density J is extracted out of the solar cell depends on the voltage V at its terminals and can be gained by rewriting Eq. 1.3 as:

$$np = n_0 p_0 e^{\frac{qV}{kT}} \tag{1.17}$$

The current density J is the superposition of the photogenerated current  $J_{ph}$  and the recombination current  $J_{rec}$ . By assuming only radiative recombinations, it yields

$$J = J_{ph} - J_{rec} = J_{ph} - qwB(np - n_i^2)$$

(1.18)

By inserting Eq. 1.17 into Eq. 1.18, we obtain

$$J = J_{ph} - qwBn_i^2(e^{\frac{qV}{kT}} - 1) = J_{ph} - J_0(e^{\frac{qV}{kT}} - 1)$$

(1.19)

where  $J_0$  is the saturation current density reflecting the recombinations. We note here that this method does not replace the traditional derivation of the continuity equation of the p-n junctions as it does not explain how the carrier extraction selectivity is obtained. However, this method shows that the typical exponential behavior is a direct consequence of the Fermi-Dirac statistic and does not depend on how carriers are extracted.

The equivalent electric circuit of a solar cell is shown in Fig. 1.6 (a). From this electric circuit, the current density J as a function of the voltage V taking into account the parasitic resistors  $R_s$  and  $R_{sh}$  is given by the diode equation:

$$J(V) = J_{ph} - J_0 \left( e^{\frac{q(V + J(V)R_s)}{nkT}} - 1 \right) + \frac{V + J(v)R_s}{R_{sh}}$$

(1.20)

where n is the ideality factor of the diode. Figure 1.6 (b) shows the plot of the J-V curve of an illuminated solar cell. It is then obvious to see that the extracted power P(V) = J(V)V exhibits a maximum for an operating point of the device called the maximum power point (MPP).

Four parameters describing the performance of a solar cell can be extracted:

- The open-circuit voltage ( $V_{\rm oc}$ ) is the potential of the device when no current is extracted from the solar cell. In this condition, the excess carrier concentration within the cell is dictated exclusively by the recombination processes. As a consequence, the  $V_{\rm oc}$  gives a direct indication of the bulk lifetime and the surface recombination.

- The short-circuit current density ( $J_{sc}$ ) is the maximum current extracted from the solar cell when its terminals are in short-circuit condition (i.e. V = 0). This parameter is directly influenced by the optical losses and by the collection losses.

• **The fill factor** (*FF*) which defines the squareness of the *J-V* curves is defined as:

$$FF = \frac{V_{mpp}J_{mpp}}{V_{oc}I_{sc}} \tag{1.21}$$

This parameter is influenced by the recombination and by the series and shunt resistance (see section 1.1.5).

• The energy conversion efficiency ( $\eta$ ) is defined as the ratio of the extracted power at the MPP ( $P_{out}$ ) to the incident power of the light ( $P_{in}$ ,  $1000\frac{W}{m^2}$  under A.M.1.5 G conditions). The efficiency can be expressed as

$$\eta = \frac{P_{out}}{P_{in}} = V_{oc} J_{sc} FF \tag{1.22}$$

In the following section, the impacts of the recombination processes and the optical and ohmic losses on these parameters are discussed.

#### 1.1.5 Photovoltaic limitations

A fundamental limit for silicon solar cells The maximum energy conversion efficiency of a solar cell strongly depends on the model and the assumptions used in its determination and has therefore been debated since the beginning of research on solar cells. [Swanson 2005] The first main achievement in the determination of the maximum efficiency was made by Shockley and Queisser in 1961. Their approach was based on a thermodynamic balance between an incident photon flux produced by the radiation of a 6000K blackbody—where all photons with an energy  $\geq E_g$  are assumed to create an electron-hole pair in the semiconductor—and the re-emitted radiative photon flux. [Shockley 1961] [Swanson 2005] In this model, a semiinfinite semiconductor piece and no Auger recombination were assumed. Remarkably, the optimum semiconductor bandgap found by Schockley and Queisser was 1.2 eV; we note that this value is quite close to the 1.12 eV bandgap of silicon. Converted to the A.M. 1.5G spectrum, this approach gives a maximum efficiency of 33%. [Swanson 2005] This approach was further investigated by Tiedje and Yablonovitch who additionally assumed a finite wafer thickness with a perfect Lambertian rear reflector and non-radiative Auger recombination. We note that Auger recombination is an unavoidable process in indirect semiconductors such as silicon. With this, the maximum efficiency was found to be 29.8% for silicon with an optimum wafer thickness of  $100 \ \mu m$ . [Tiedje 1984] A new parametrization of the Auger recombination was proposed by Kerr and Cuevas in 2002. [Kerr 2002b] From this and by assuming a 90- $\mu m$ -thick wafer absorber, a maximum efficiency of 29.05% was deduced. We note here that an improved parameterization for the Auger recombination was proposed by Richter in 2012 leading to a maximum efficiency of 29.43% for a 110- $\mu$ m-thick wafer. [Richter 2012] [Richter 2013]

In the following paragraphs, we investigate qualitatively how the different losses impact the

*J-V* curve and the  $V_{oc}$ ,  $J_{sc}$ , FF and  $\eta$ .

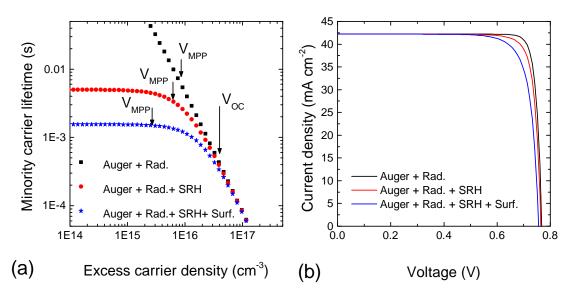

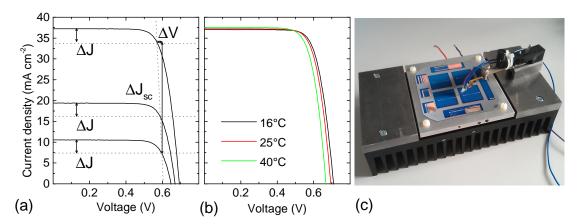

**Recombination losses** In this paragraph, we investigate the impact of the recombination processes on the solar cell performances. Figure 1.7 (a) shows the minority-carrier lifetime  $\tau_{eff}$  as a function of the  $\Delta_n$  with: i) only radiative recombination and Auger recombination, ii) with the addition of SRH recombination, and iii) with the subsequent addition of surface recombination. From these lifetime curves, an *implied J-V* curve can be deduced as follows: [Sinton 1996]

$$iV = \frac{kT}{q} ln \left( \frac{\Delta n(N_A + \Delta n)}{n_i^2} + 1 \right)$$

(1.23)

$$iJ = J_{sc}(1 - equSuns) \tag{1.24}$$

$$equSuns = q \times G \times w \tag{1.25}$$

where G is the generation rate and w is the wafer thickness. When only radiative recombination and Auger recombination are considered, a maximum efficiency close to 29% and a maximum  $V_{\rm oc}$  of 769 mV are extracted. [Kerr 2002b] Interestingly, by introducing a relatively modest contributions of SRH recombination and surface recombination, a weak influence on the  $\tau_{\rm eff}$  at the carrier injection level corresponding to the open-circuit condition is seen. This is explained by the dominance of the Auger recombination at this regime. Consequently, the  $V_{\rm oc}$  is as well only weakly reduced. However, SRH recombination and surface recombination considerably reduce the minority-carrier lifetime at lower injection. As a consequence, the  $V_{\rm mpp}$  is shifted toward lower voltages and leads to lower FF as observed in Fig. 1.7.

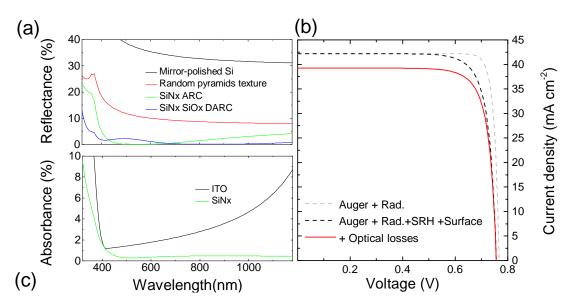

**Optical losses** Several effects lead to optical losses in solar cells. The list below gives the main contributors to optical losses in silicon solar cells

• Light reflection at the primary interface: As shown in Fig. 1.8 (a), a bare silicon wafer with a polished surface reflects about 30% of the incident light. A simple and cost-effective way to reduce this is to create random pyramids inducing a second rebound of the light. This reduces the light reflection to about 10%. Additionally this texture increases the optical path in the wafer. One or two materials with the appropriate refractive index can be inserted between the silicon and the air to act as  $\frac{\lambda}{4}$  anti-reflective coating (ARC). The light reflection is then reduced to a few percent along the solar

Figure 1.7: (a) Minority-carrier lifetime curves as a function of the excess carrier density for various combinations of recombination processes (b) Implied J-V curves related to the minority-carrier lifetime curves of (a).

spectrum. [Nelson 2003]

• Parasitic light absorption in the front layers: When transmitted through the front layers, which do not act as active absorbers (as for instance the ARC layers, see Fig. 1.8 (c)), part of the light is absorbed following the Beer-Lambert law which depends on the absorption coefficient  $\alpha = \frac{4\pi k}{\lambda}$  and the film thickness t:

$$I_{tranmitted} = I_0 \times e^{\alpha t} \tag{1.26}$$

- Near-IR free-carrier absorption: This phenomenon is especially important with a transparent conductive oxide (TCO). As the FCA coefficient is proportional to the free-carrier concentration, heavily doped TCO leads to significant IR absorption (see Fig. 1.8 (c)). Therefore, high mobilities are required to obtain highly transparent TCOs with high conductivity. [Barraud 2013][Koida 2007]

- Front-grid reflection: The metallic front grid directly induces a shadowing of 2 to 6%. [Geissbuhler 2014]. Highly conductive material helps to reduce as much as possible the finger width while avoiding excessive ohmic losses (see chapter 3). The finger geometry is also important as it may partially reflect part of the incident light towards the cell. [Woehl 2008]

- **Back side IR losses:** Infrared light can reach the rear side of the solar cell and be lost by being reflected to the front side or parasitically absorbed by plasmonic effect induced by the metallic rear reflector. [Holman 2013]

Figure 1.8: (a) Example of reflection losses occurring at the front side of a solar cell with different anti-reflection techniques (obtained by using OPAL [PVLighthouse 2015]) (b) Impact on the J-V curves of optical losses (c) Example of absorbance of different materials (obtained by using OPAL [PVLighthouse 2015]).

Figure 1.8 shows the impact of optical losses on the *J-V* curve. *J-V* curves with the recombination contributions previously explained are given for the purpose of comparison.

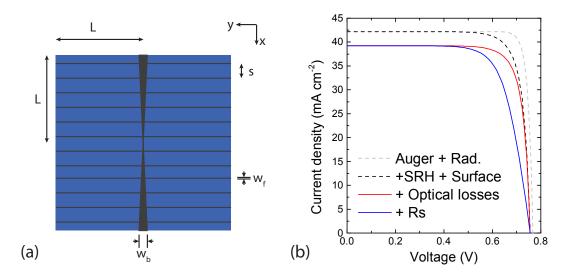

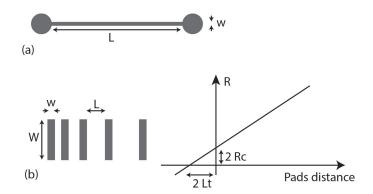

**Ohmic losses** The resistivity of the material conducting the charge carrier leads to a series resistance as shown in Fig. 1.6 (a). A significant part of this series resistance is induced by the front electrode. With a typical H-pattern front-grid design for fingers and busbar as shown in Fig. 1.9 (a), three main power losses can be extracted and normalized to the extracted power: [Green 1982]

#### • Lateral transport towards the grid:

$$P_{TCO} = \int_0^{\frac{s}{2}} I^2(x) dR = LJ^2 R_{\square} \int_0^{\frac{s}{2}} x^2 dx = \frac{1}{24} LJ^2 R_{\square} s^3$$

(1.27)

$$P_{TCO\ norm.} = \frac{P_{TCO}}{P_{unit}} = \frac{\frac{1}{24}LJ^2R_{\Box}s^3}{VJL_{\frac{s}{2}}} = \frac{JR_{\Box}s^2}{12V}$$

(1.28)

#### • Transport in the finger:

$$P_{finger} = \int_0^L I^2(y) dR = \frac{\rho}{t w_f} s^2 J^2 \int_0^L y^2 dy = \frac{1}{3} \frac{\rho}{t \times w_f} s^2 J^2 L^3$$

(1.29)

Figure 1.9: (a) Schematic of an H-pattern metallic front grid (b) Impact on the *J-V* curves of the series resistance.

$$P_{finger\ norm.} = \frac{P_{finger}}{P_{unit}} = \frac{\frac{1}{3} \frac{\rho}{t w_f} s^2 J^2 L^3}{VJLS} = \frac{1}{3} \frac{\rho s J L^2}{t w_f V}$$

(1.30)

#### • Transport in the busbar:

$$P_{BB} = \int_0^L I^2(x)dx = L^2 J^2 \rho \frac{2L}{w_h t} \int_0^L x dx = J_{ph}^2 \rho \frac{L^5}{w_h t}$$

(1.31)

$$P_{BB\ norm.} = \frac{P_{BB}}{P_{unit}} = \frac{J^2 \rho \frac{L^5}{w_b t}}{VJL^2} = \frac{J\rho L^3}{Vw_b t}$$

(1.32)

where  $R_{\square}$  is the sheet resistance of the material conducting the carriers to the front grid,  $\rho$  is the electric resistivity of the metal used for the front grid and J and V are the current density and the voltage of the cell. The impact of the series resistance on the J-V curve is a characteristic variation of the curve's slope close to the open-circuit condition and is directly related to the FF: [Khanna 2015]

$$\Delta F F_{Rs} = \frac{J_{mpp}^2 R_s}{V_{oc} I_{sc}} \tag{1.33}$$

As seen in Fig. 1.6 (a), the equivalent circuit of a solar cell also includes a shunt resistor, which can possibly be induced by parasitic contact between the two terminals of the device. The

typical signature of such losses is the appearance of a tilted *J-V* curve near short circuit.

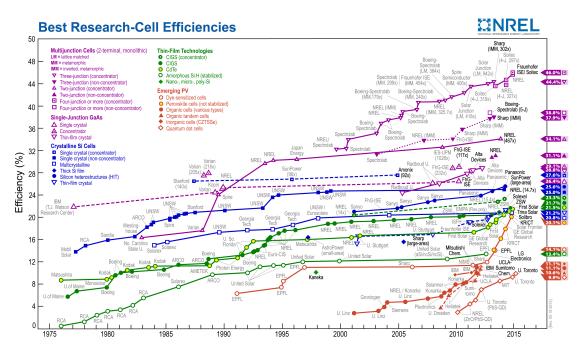

#### 1.1.6 Overview of the technology

Figure 1.10 presents the record-efficiency chart over the last 40 years for the main photovoltaic technologies. Starting with the best energy conversion ever obtained for a photovoltaic device, an efficiency of 46% was obtained with a four-junction solar cell based on III-V materials under 508 suns concentration. [Green 2015][Dimroth 2014] Without concentration, similar cell structures demonstrated efficiencies of up to 38.8%. However, their complex processing, including molecular beam epitaxy, makes these technologies far too costly for terrestrial deployment.

For single-junction crystalline silicon solar cells, it is interesting to notice that recently silicon heterojunction (SHJ) solar cells have surpassed the conversion efficiency of diffused-junction devices. These devices will be further discussed in the following paragraphs.

Thin-film technologies offer the important benefits of monolithically interconnecting the different cells of a module during module manufacturing and facilitating the building integration due to their uniform aspect. [Boccard 2014][Heinstein 2013] Among these thin-film technologies, the most industrially spread are CIGS, CdTe, and thin-film silicon made of amorphous silicon or microcrystalline silicon possibly integrated in the micromorph tandem architecture.[Chiril 2011] [Romeo 2004] [Boccard 2014].

More recently, the scientific community has grown interested in perovskite solar cells with their record efficiency of 20.1%. [Yang 2015] Due to their high bandgap and high voltage potential, these solar cells are nowadays investigated as the top cell of tandem devices that have a silicon solar cell as the bottom cell. However, the high-sensitivity of this material against humidity and oxygen leads to important stability issues for such cells. [Loper 2014] [De Wolf 2014]

#### 1.1.7 High-temperature crystalline silicon solar cell

This section discusses solar cell structures based on diffused-junctions in crystalline silicon wafers.

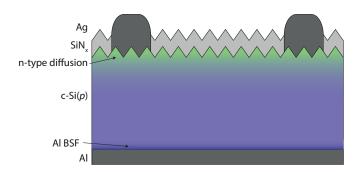

**Aluminum-diffused back-surface-field c-Si solar cell** The aluminum-diffused back-surface-field (Al-BSF) is the most industrially spread silicon solar cell architecture due to its extreme simplicity of fabrication. [Glunz 2012] To achieve the structure as presented in Fig. 1.11, silicon wafers are first textured to maximize light coupling. This can be realized either by anisotropic wet etching in the case of mono-crystalline wafers (see section 2.2.1) or by acidic etching in the case of multi-crystalline wafers. Usually, the wafer is lightly p-doped with a typical boron concentration of  $N_A \approx 10^{16}$  cm<sup>-3</sup>. [Fellmeth 2011] Next, a POCL<sub>3</sub> thermal diffusion is

Figure 1.10: Record-efficiency chart over the last 40 years for various photovoltaic technologies. This plot is courtesy of the National Renewable Energy Laboratory, Golden, CO, USA [NREL 2015]

carried at the front side to form the electron collector having a sheet resistance usually ranging between 60 and 100  $\Omega_{\square}$ . [Schultz 2008] After the removal of the phosphorus glass grown during the diffusion and the etching of the diffused layer on the wafer edges, an  $SiN_x$  ARC is deposited by plasma-enhanced chemical vapor deposition (PECVD). An aluminium-based metallic paste is screen-printed at the rear side and dried prior to the screen-printing of the silver front-grid. Finally, both contacts are co-fired which respectively creates an aluminium doping at the back side and allows the silver paste to locally dissolve the  $SiN_x$  to contact the front n-type diffusion. [Ballif 2003] Despite the attractiveness of this simple process, this architecture suffers from significant recombination losses as both contacts rely on a direct metal-semiconductor contact. This recombination are nevertheless reduced by the front diffusion and the BSF which minimize the minority-carrier density in the contact vicinities. However, these doping concentrations follow a trade-off as a too important doping level will introduce excessive Auger recombination.

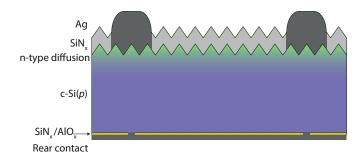

**Passivated emitter and rear cell (PERC) solar cell** To overcome the latter trade-off, the passivated emitter and rear cell structure was proposed in the late 1980s. [Blakers 1986] In this cell structure, the highly recombinative hole contact formed at the rear side by the Al-BSF is restricted to a few points by the addition of a passivating thermal oxide layer locally opened for the metal contact. The contact formation can be typically be carried out by a laser firing process. [Benick 2011] This cell structure is shown in Fig. 1.12 and is considered as the next

Figure 1.11: Schematic cross-section of an aluminum-diffused back-surface-field c-Si solar cell. Adapted from [De Wolf 2012].

generation for industrial solar cells with an  $Al_2O_3$  layer as a passivating layer. [Burger 2015] An advantage of this structure is the possibility to "update" the existing production facilities by adding specific tools for the passivation layers its opening by laser.

Passivated emitter rear locally diffused (PERL) solar cell A further improvement of the PERC device structure is the passivated emitter rear-locally diffused devices proposed by UNSW in the late 1990s. The key difference is the introduction of a highly p-doped region above the point contacts at the rear side in order to reduce the recombination induced by the metal-semiconductor contact. Additionally, several advanced techniques were used to further increase the cell efficiency such as inverted pyramids, [Blakers 1986] double ARC, electrodeposited front-contact and a more lightly doped electron collector at the front side and locally reinforced under the contact. [Green 1990b] [Zhao 1998]

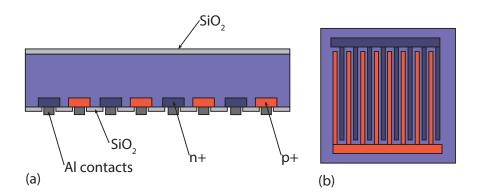

**Interdigitated-back-contacted solar cell (IBC)** In the previous cell structures, all layers of the front side are optimized in order to induce as few optical losses as possible (see section

Figure 1.12: Schematic cross-section of a passivated emitter and rear cell structure. Adapted from [Seif 2015a].

Figure 1.13: Schematic cross-section of a passivated emitter rear locally diffused (PERL) solar cell of UNSW [Zhao 1995]. Adapted from [Seif 2015a].

1.1.5). To overcome this issue, another cell structure was proposed by Lammert and Schwartz in 1975. [Lammert 1977] They proposed to place both electron and hole collectors at the rear side of the device forming two opposite combs. This design leads to the ultimate degree of freedom in the optimization of the front side for optical and passivation purposes exclusively. As minority carriers have to travel laterally to reach the contact, it is crucial to keep this distance smaller than their diffusion length in order to prevent their recombination leading to a  $J_{\rm sc}$  loss. This potential loss is called *electrical shading*. [Reichel 2011] Furthermore, majority carriers generated above the opposite contact must as well travel laterally inducing an additional series resistance. [Tomasi 2014] [Granek 2010] [Franklin 2014]

This cell structure is currently industrially produced and commercialized by the company Sunpower. In these device, excessive recombination induced by a direct metal-semiconductor contact are avoided by the use of point-passivated contact enabling  $V_{\rm oc}$  up to 725 mV. [Smith 2012] [Smith 2014] At the R&D scale, Sunpower demonstrated a remarkable efficiency of 25% by using this design. [Smith 2014]

Figure 1.14: (a) Schematic cross-section of an interdigitated-back-contacted solar cell as proposed by [Lammert 1977] and (b) view of the rear-side.

Figure 1.15: Schematic cross-section of a TOPCon cell as proposed by [Feldmann 2014b].

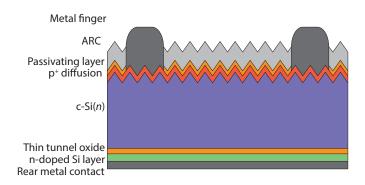

**Tunnel oxide passivated contact (TOPCon)** A recent demonstration of a passivating contact in high efficiency silicon solar cells was made by the tunnel oxide passivated contact (TOPCon) demonstrated by Feldmann *et al.*. [Feldmann 2014b] Figure, 1.15 shows a schematic cross-section of a TOPCon structure. The passivated contact is formed by ultra-thin silicon oxide usually 14-Å-thick grown by a wet chemical process allowing the transport of charge carrier by tunneling process. Then, to form an electron selective contact, a phosphorus-doped polysilicon layer is deposited and annealed above 600°C to activate the passivation. [Feldmann 2014b] This electron contact—in combination with a hole contact made by a front boron diffusion—demonstrated outstanding *FF* values above 82% leading to recent demonstration of cell efficiencies as high as 24.4% and 24.9%. [Feldmann 2014c] [Moldovan 2015] We note that both contacts can be realized with this approach by respectively using boron- and phosphorus-doped polysilicon layers. This latter structure showed promising device results with *FF* values above 81% demonstrating the effectiveness of such contact. [Feldmann 2014a]

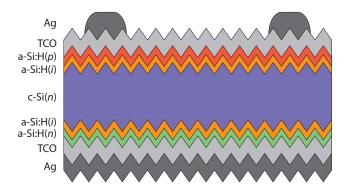

#### 1.1.8 Silicon heterojunction solar cells

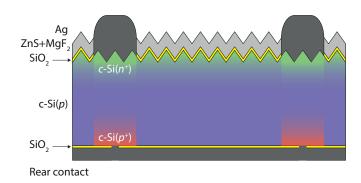

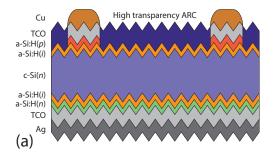

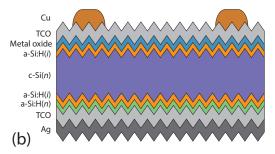

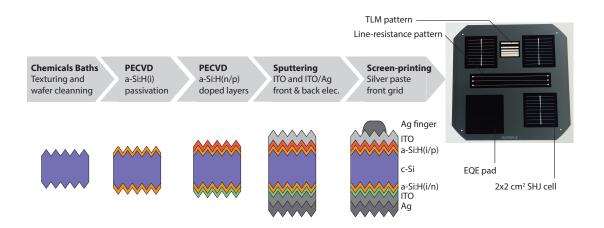

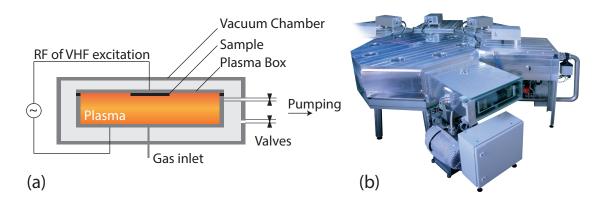

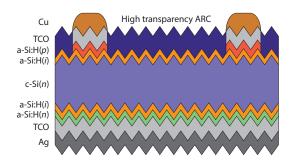

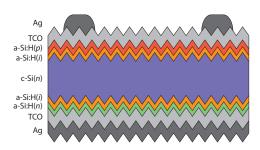

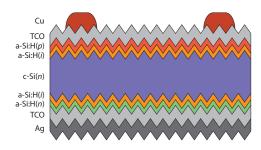

As seen in the previous paragraphs describing diffused-junction c-Si solar cells, increasingly more complex cell structures have been proposed to optimize the electron and hole contacts with a global trend going to localized contacts. In silicon heterojunction (SHJ) solar cells, a completely different contacting approach is used relying on planar deposited passivating contacts made of amorphous silicon (a-Si:H). Figure 1.16 shows a schematic of the SHJ device structure. A mono-crystalline silicon wafer with random pyramids is used as the photon absorber. To ensure high-quality surface passivation,  $\approx$  5-nm-thick intrinsic a-Si:H [denoted a-Si:H(i)] layers are deposited on both sides of the wafer. [Descoeudres 2011] To form the electron and hole collectors, n- and p-doped a-Si:H films are deposited on the a-Si:H(i) passivating layers. Due to their very low lateral conductivity, a transparent conductive oxide (TCO) is sputtered at the front side to efficiently contact the a-Si:H(ip) films, to conduct the charge carrier laterally and to provide an ARC at the front side. [De Wolf 2012] For the rear side, a TCO is used as well to contact the a-Si:H(in) and to provide a displaced back reflector in

Figure 1.16: Schematic cross-section of a silicon heterojunction solar cell. Adapted from [De Wolf 2012].

combination with a sputtered silver film. [Holman 2013] The lateral conductivity of the front TCO is further reinforced by a screen-printed silver grid. Due to the low stability of a-Si:H layers above 200 °C, special silver pastes with a low curing temperature are used. [De Wolf 2012] A description of the complete process sequence to make a SHJ device is made in section 2.1.

The first demonstration of a SHJ solar cell with a structure as it is known nowadays was demonstrated in 1992 by Tanaka *et al.* from Sanyo (now Panasonic) with an efficiency of 18.1%. [Tanaka 1992] Recently, an increasing interest coming from both academia and industry was experienced for SHJs. This is explained by the outstanding results obtained for this technology notably by Panasonic with an efficiency for a front-contacted SHJ device of 24.7%. [Taguchi 2014] By using an IBC configuration, the efficiency was further increased to 25.6% becoming the new world record for c-Si solar cells. [Masuko 2014] In addition, the simple processing of SHJ devices associated with their high efficiency can make them cost-competitive compared to other solar cell technologies. [Ballif 2014] [Meyer-Burger 2014b]

#### 1.2 Motivations

As previously discussed in section 1.1.5, several losses impact the efficiency of a solar cell. To overcome these losses, various device architectures based on c-Si wafers have been proposed. Table 1.1 gives an overview of the  $V_{\rm oc}$ ,  $J_{\rm sc}$ , FF and efficiency for the different advanced c-Si solar cell architectures discussed in the previous sections. It can be seen that front-contacted SHJ devices have by far the lowest  $J_{\rm sc}$  compared to diffused-junction devices. This is explained by the parasitic light absorption in the front a-Si:H and TCO layers and—in this case—by the screen-printed metallic front grid, which results in shadow losses. As a consequence, alternative structures and processes have to be developed in order to solve the latter issue.

| Cell                               | $V_{\rm oc}({ m mV})$ | $J_{\rm sc}$ (mA cm <sup>-2</sup> ) | <i>FF</i> (%) | Efficiency (%) |

|------------------------------------|-----------------------|-------------------------------------|---------------|----------------|

| PERL [Zhao 1998]                   | 706                   | 42.7                                | 82.8          | 25.0           |

| PERC [Blakers 1989]                | 688                   | 40.8                                | 82.1          | 23.1           |

| IBC diffused-junction [Smith 2014] | 726                   | 41.53                               | 82.84         | 25.0           |

| TOPCon [Feldmann 2014c]            | 715                   | 41.5                                | 82.1          | 24.4           |

| SHJ front contacted [Taguchi 2014] | 750                   | 39.5                                | 83.2          | 24.7           |

| SHJ IBC [Masuko 2014]              | 740                   | 41.8                                | 82.7          | 25.6           |

Table 1.1:  $V_{0c}$ ,  $J_{sc}$ , FF and efficiency of different c-Si solar cell architectures.

Figure 1.17: Schematic cross-section of novel devices investigated in this thesis: (a) SHJ device with localized contacts (b) SHJ device with metal oxide as a replacement of the a-Si:H(p) hole collector. Both devices feature an advanced metallization made by electrodeposited copper.

#### 1.3 Objectives and structure

#### 1.3.1 Objectives

The objectives of this thesis are to further enhance the optical response of SHJ solar cells by developing new architectures and processing techniques.

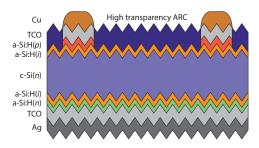

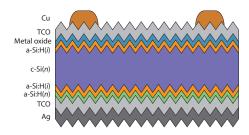

The scientific goal of this work is the investigation of the two new device architectures shown in Fig. 1.17. The first structure relies on localized front contacts in order to limit the coverage of a-Si:H layers and the parasitic light absorption. The second structure is based on the replacement of the a-Si:H(p) hole collector layer by a highly transparent metal oxide as proposed by Battaglia *et al.* [Battaglia 2014a] To realize these structures, a technological goal is the development of several micro-fabrication techniques dedicated to SHJ solar cells. First, an accurate technique capable of patterning a-Si:H layers with a high accuracy and preserving the surface passivation is needed. Secondly, a replacement technique of the silver paste screen-printing is required in order to form a highly conductive front grid with narrower fingers width. Ultimately, these structures or processing techniques can be possibly merged together or applied to other device architectures such as IBC-SHJ.

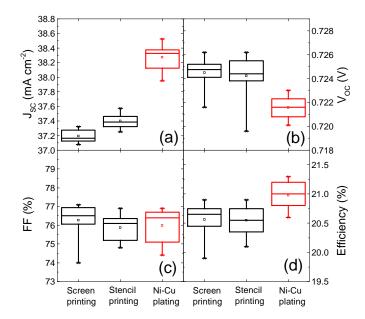

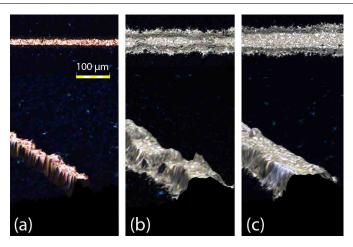

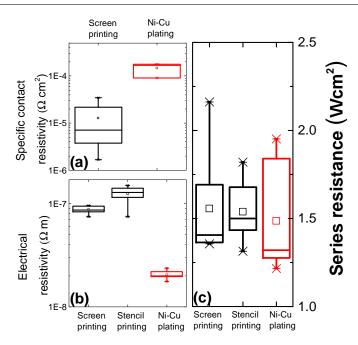

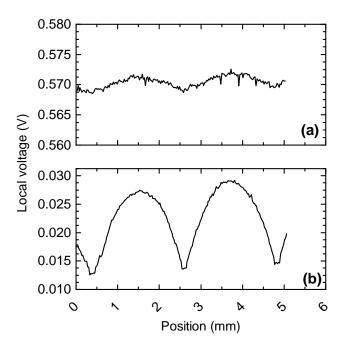

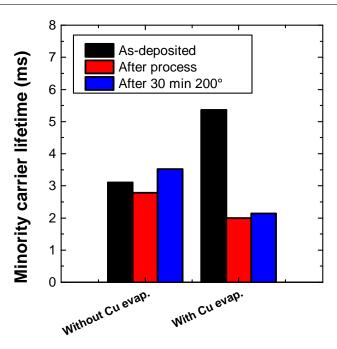

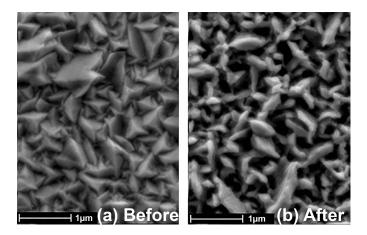

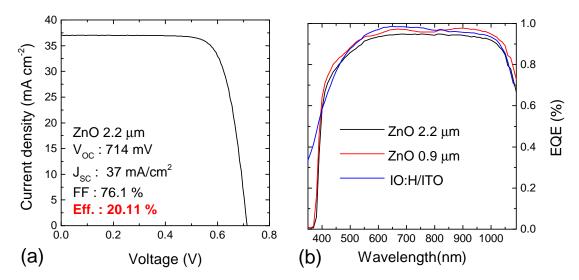

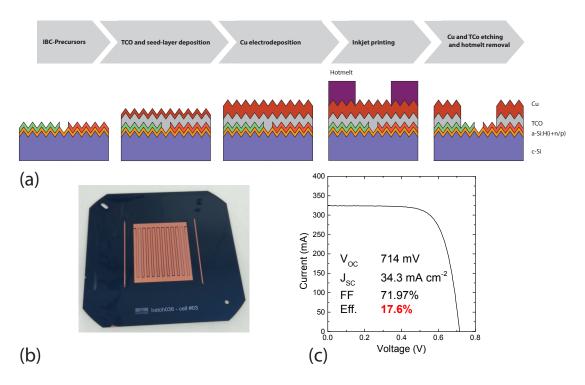

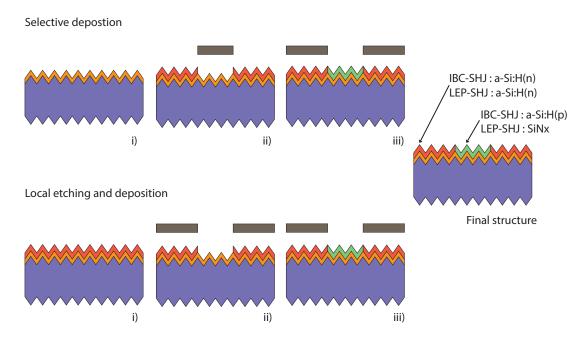

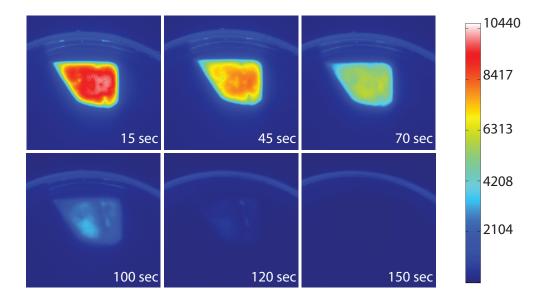

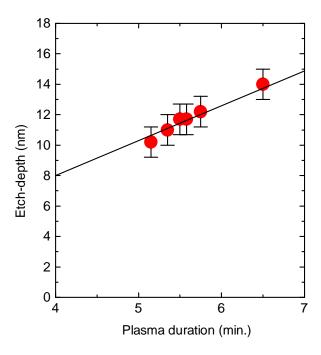

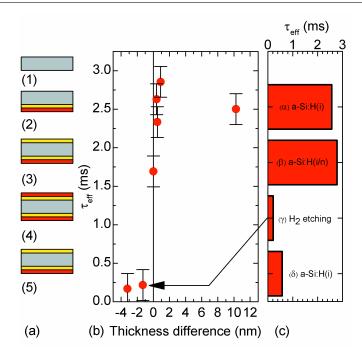

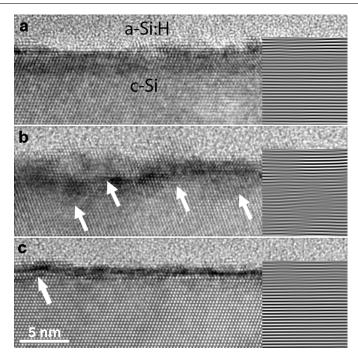

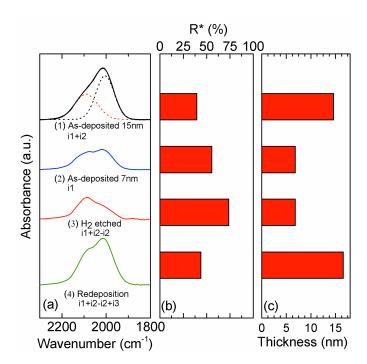

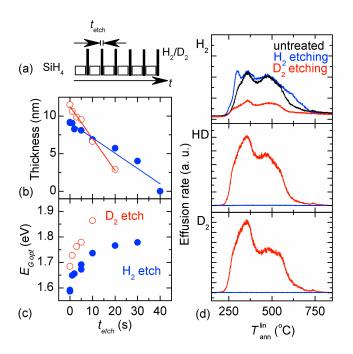

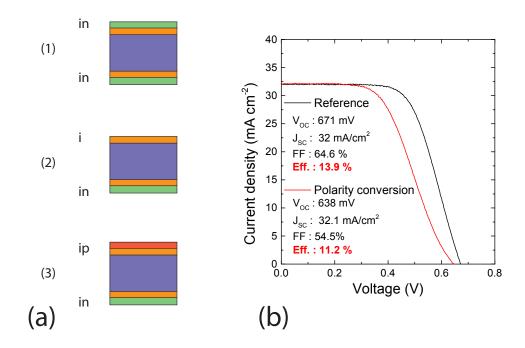

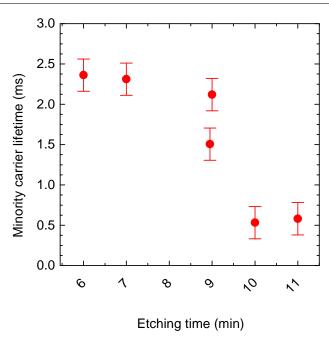

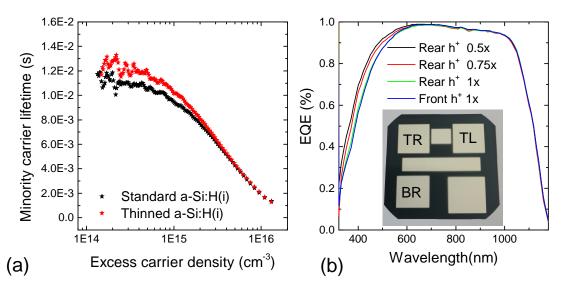

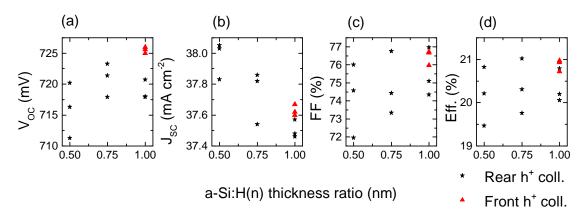

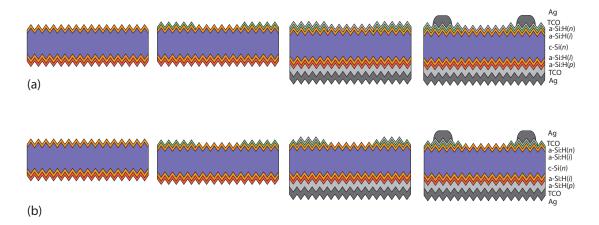

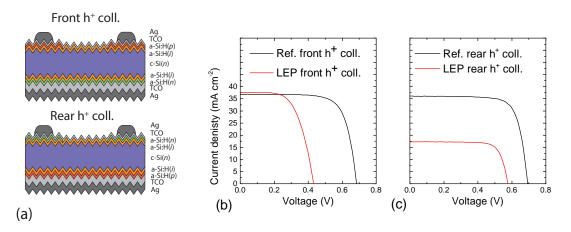

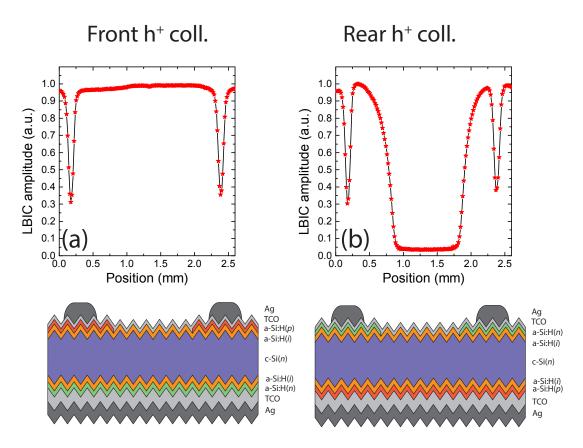

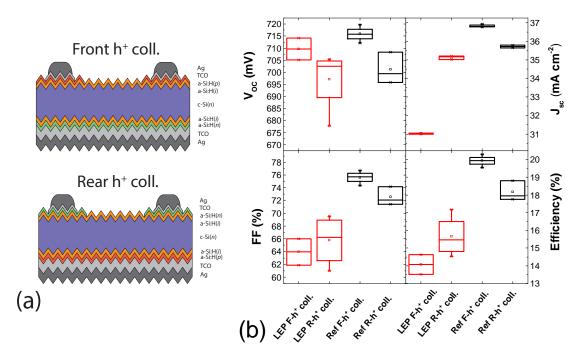

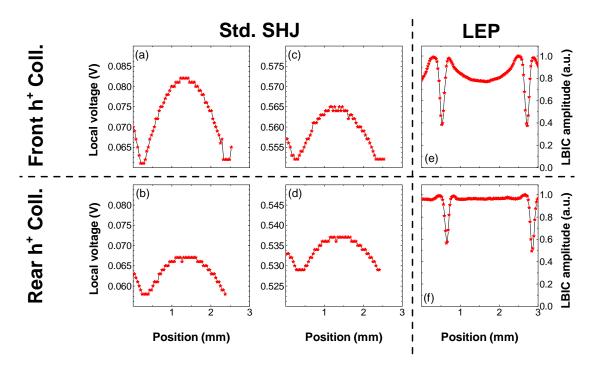

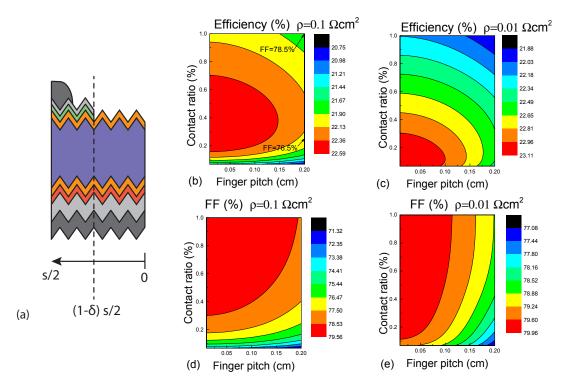

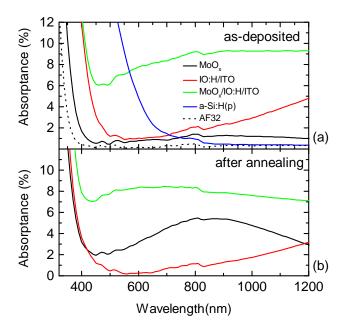

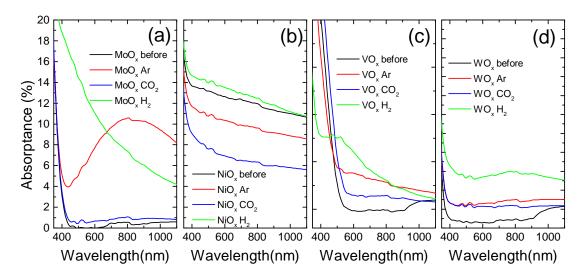

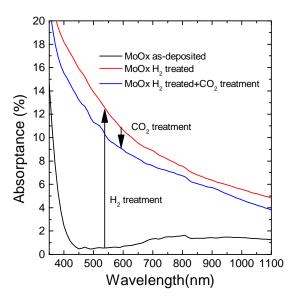

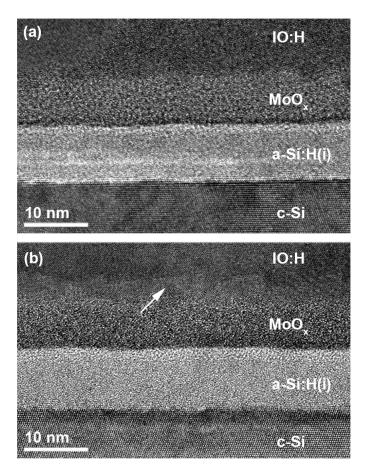

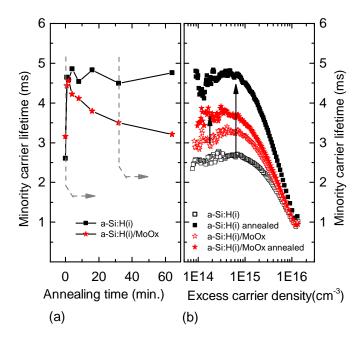

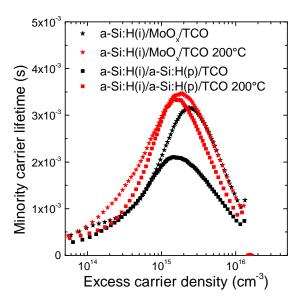

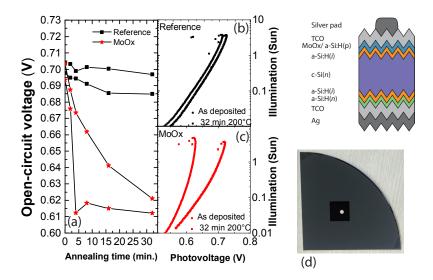

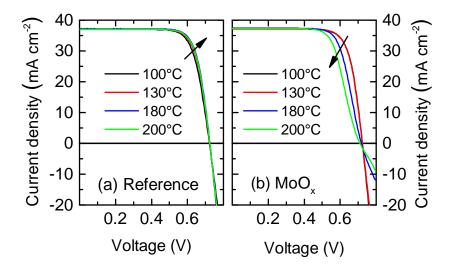

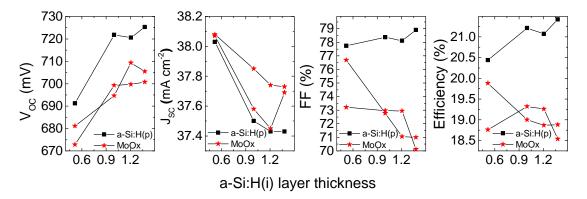

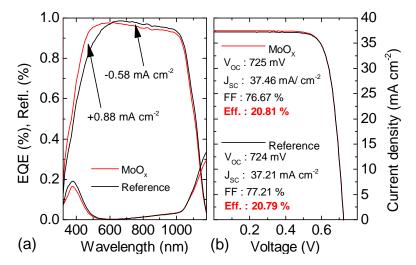

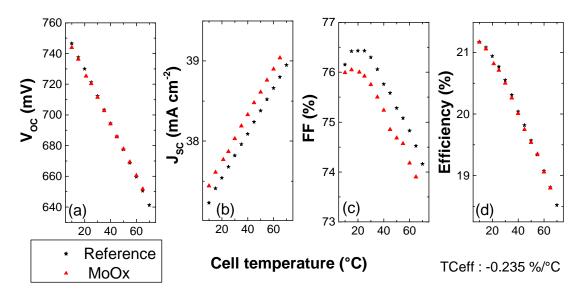

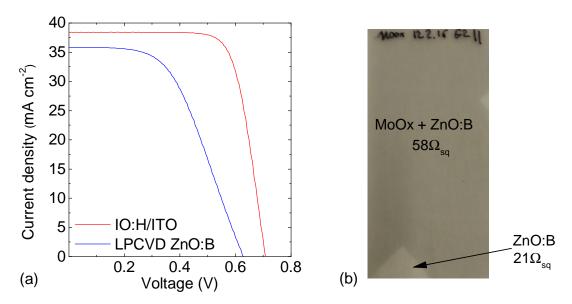

#### 1.3.2 Structure